LP38691-ADJ/LP38693-ADJ

500mA Low Dropout CMOS Linear Regulators with

Adjustable Output

Stable with Ceramic Output Capacitors

General Description

The LP38691/3-ADJ low dropout CMOS linear regulators

provide 2.0% precision reference voltage, extremely low

dropout voltage (250mV

@

500mA load current, V

OUT

= 5V)

and excellent AC performance utilizing ultra low ESR ce-

ramic output capacitors.

The low thermal resistance of the LLP and SOT-223 pack-

ages allow the full operating current to be used even in high

ambient temperature environments.

The use of a PMOS power transistor means that no DC base

drive current is required to bias it allowing ground pin current

to remain below 100 µA regardless of load current, input

voltage, or operating temperature.

Dropout Voltage: 250 mV (typ)

@

500mA (typ. 5V out).

Ground Pin Current: 55 µA (typ) at full load.

Adjust Pin Voltage: 2.0% (25∞C) accuracy.

Features

n

Output voltage range of 1.25V - 9V

n

2.0% adjust pin voltage accuracy (25∞C)

n

Low dropout voltage: 250mV

@

500mA (typ, 5V out)

n

Wide input voltage range (2.7V to 10V)

n

Precision (trimmed) bandgap reference

n

Guaranteed specs for -40∞C to +125∞C

n

1µA off-state quiescent current

n

Thermal overload protection

n

Foldback current limiting

n

SOT-223 and 6-Lead LLP packages

n

Enable pin (LP38693-ADJ)

Applications

n

Hard Disk Drives

n

Notebook Computers

n

Battery Powered Devices

n

Portable Instrumentation

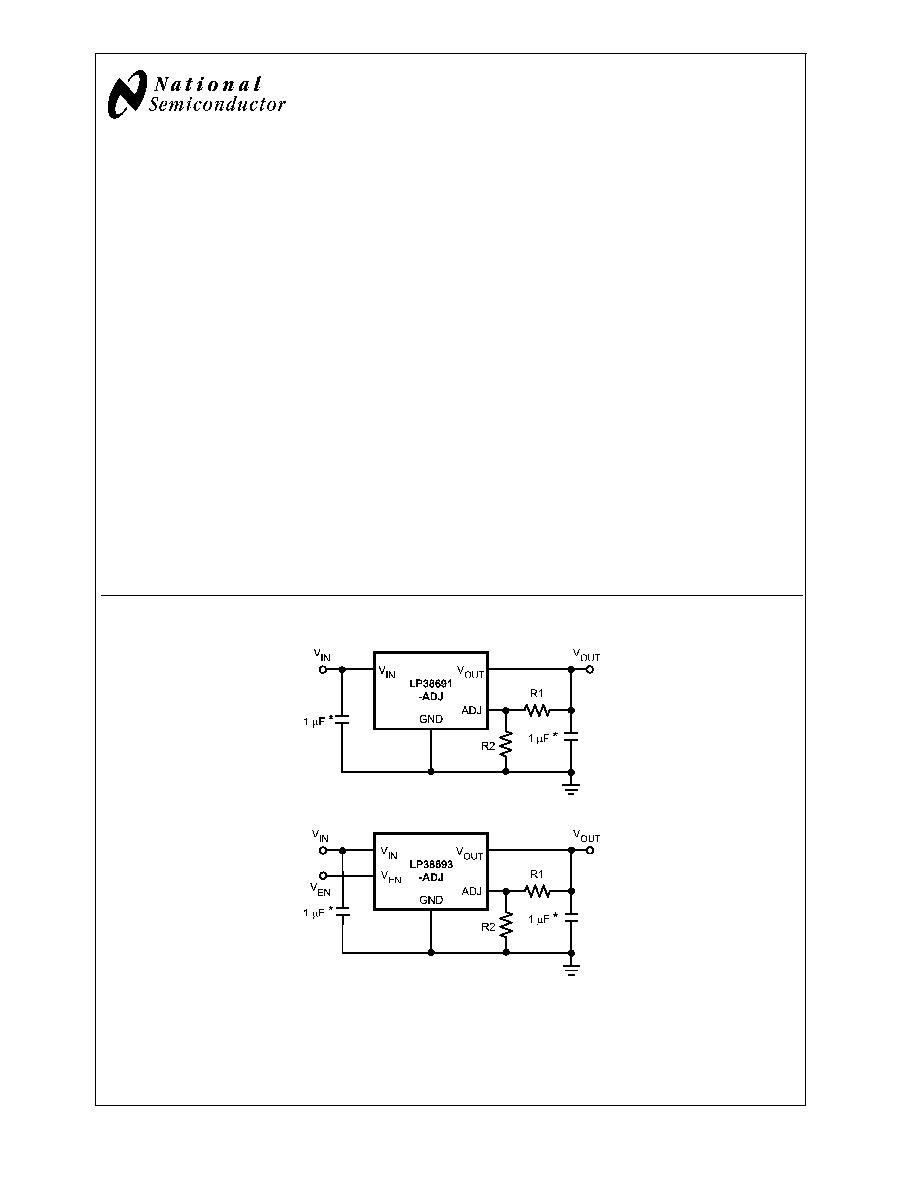

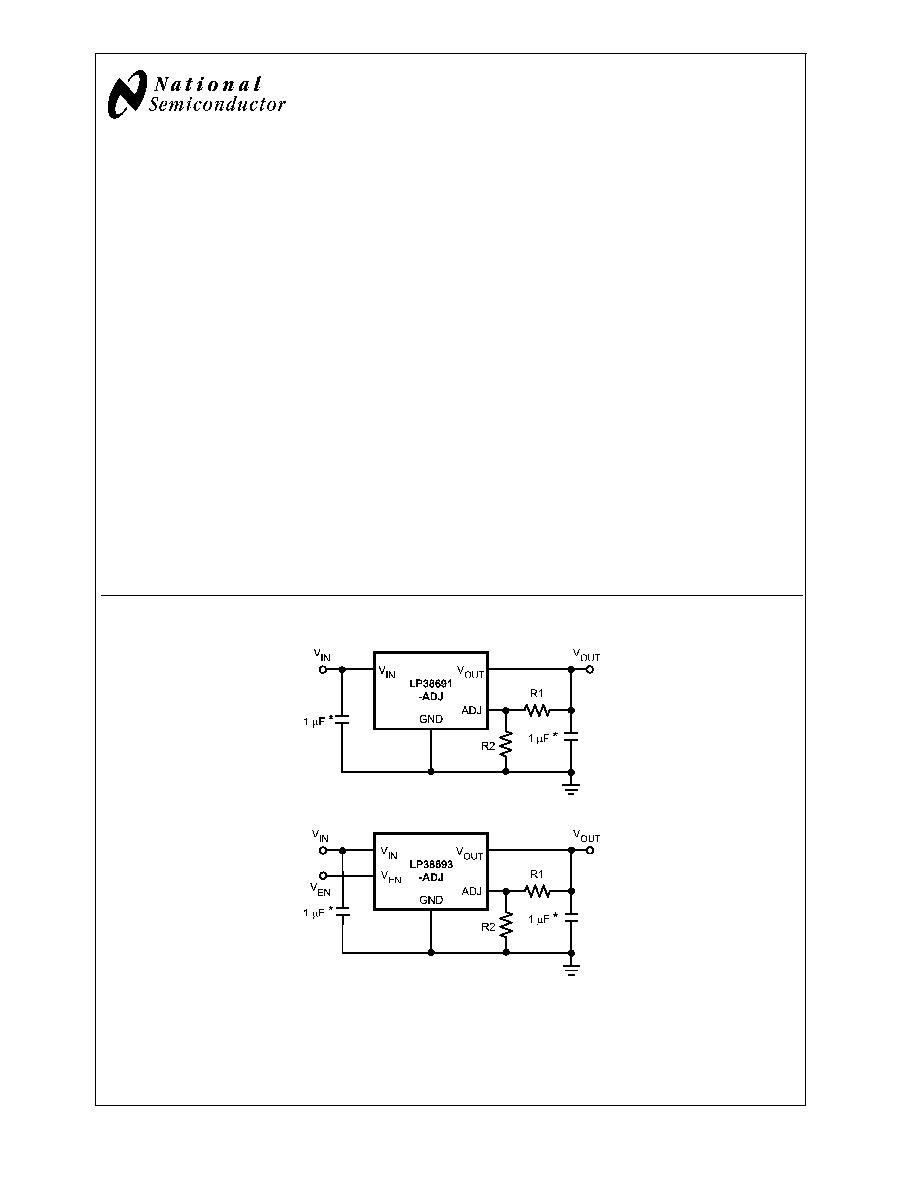

Typical Application Circuits

20126801

20126802

V

OUT

= V

ADJ

x (1 + R1/R2)

Note: *Minimum value required for stability.

PRELIMINARY

January 2005

LP38691-ADJ/LP38693-ADJ

500mA

Low

Dropout

CMOS

Linear

Regulators

with

Adjustable

Output

Stable

with

Ceramic

Output

Capacitors

© 2005 National Semiconductor Corporation

DS201268

www.national.com

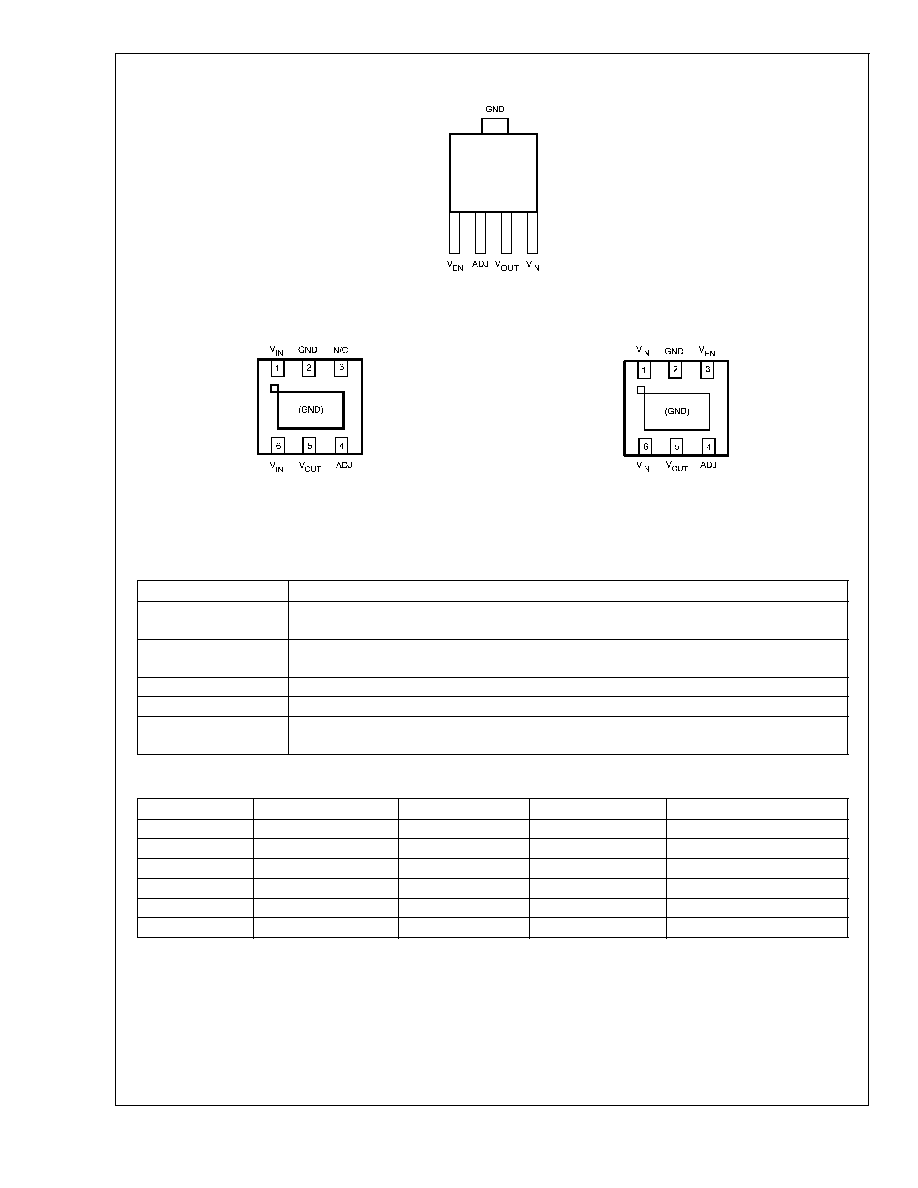

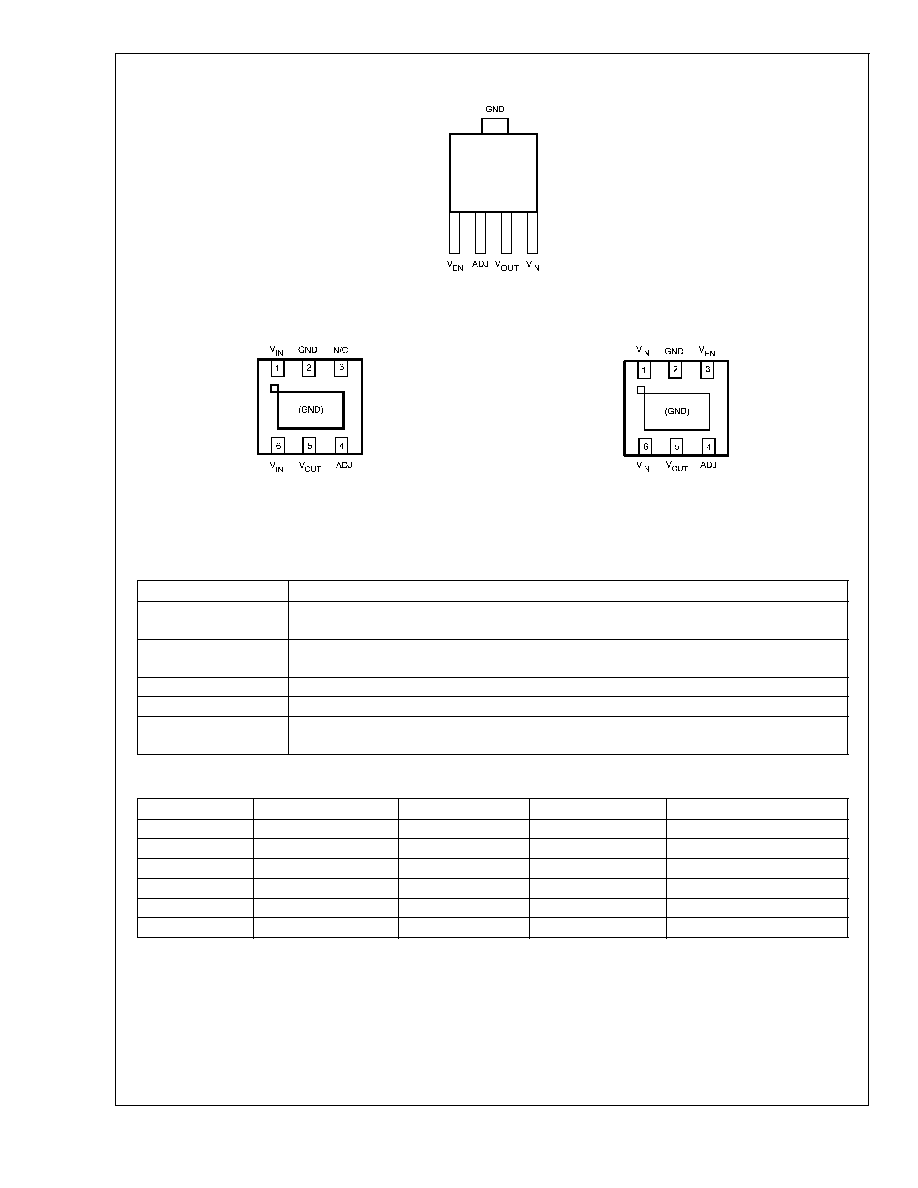

Connection Diagrams

20126803

SOT-223, Top View

LP38693MP-ADJ

20126804

6-Lead LLP, Bottom View

LP38691SD-ADJ

20126805

6-Lead LLP, Bottom View

LP38693SD-ADJ

Pin Description

PIN

DESCRIPTION

V

IN

This is the input supply voltage to the regulator. For LLP package devices, both V

IN

pins must be

tied together for full current operation (250mA maximum per pin).

GND

Circuit ground for the regulator. This is connected to the die through the lead frame, and also

functions as the heat sink when the large ground pad is soldered down to a copper plane.

V

OUT

Regulated output voltage.

V

EN

The enable pin allows the part to be turned ON and OFF by pulling this pin high or low.

ADJ

The adjust pin is used to set the regulated output voltage by connecting it to the external

resistors R1 and R2 (see Typical Application Circuit).

Ordering Information

Order Number

Package Marking

Package Type

Package Drawing

Supplied As

LP38691SD-ADJ

L117B

6-Lead LLP

SDE06A

1000 Units Tape and Reel

LP38693SD-ADJ

L127B

6-Lead LLP

SDE06A

1000 Units Tape and Reel

LP38693MP-ADJ

LJUB

SOT-223

MP05A

1000 Units Tape and Reel

LP38691SDX-ADJ

L117B

6-Lead LLP

SDE06A

4500 Units Tape and Reel

LP38693SDX-ADJ

L127B

6-Lead LLP

SDE06A

4500 Units Tape and Reel

LP38693MPX-ADJ

LJUB

SOT-223

MP05A

2000 Units Tape and Reel

LP38691-ADJ/LP38693-ADJ

www.national.com

2

Absolute Maximum Ratings

(Note 1)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

Storage Temperature Range

-65∞C to +150∞C

Lead Temp. (Soldering, 5 seconds)

260∞C

ESD Rating (Note 3)

2 kV

Power Dissipation (Note 2)

Internally Limited

V(max) All pins (with respect to GND)

-0.3V to 12V

I

OUT

Internally Limited

Junction Temperature

-40∞C to +150∞C

Operating Ratings

V

IN

Supply Voltage

2.7V to 10V

Operating Junction

Temperature Range

-40∞C to +125∞C

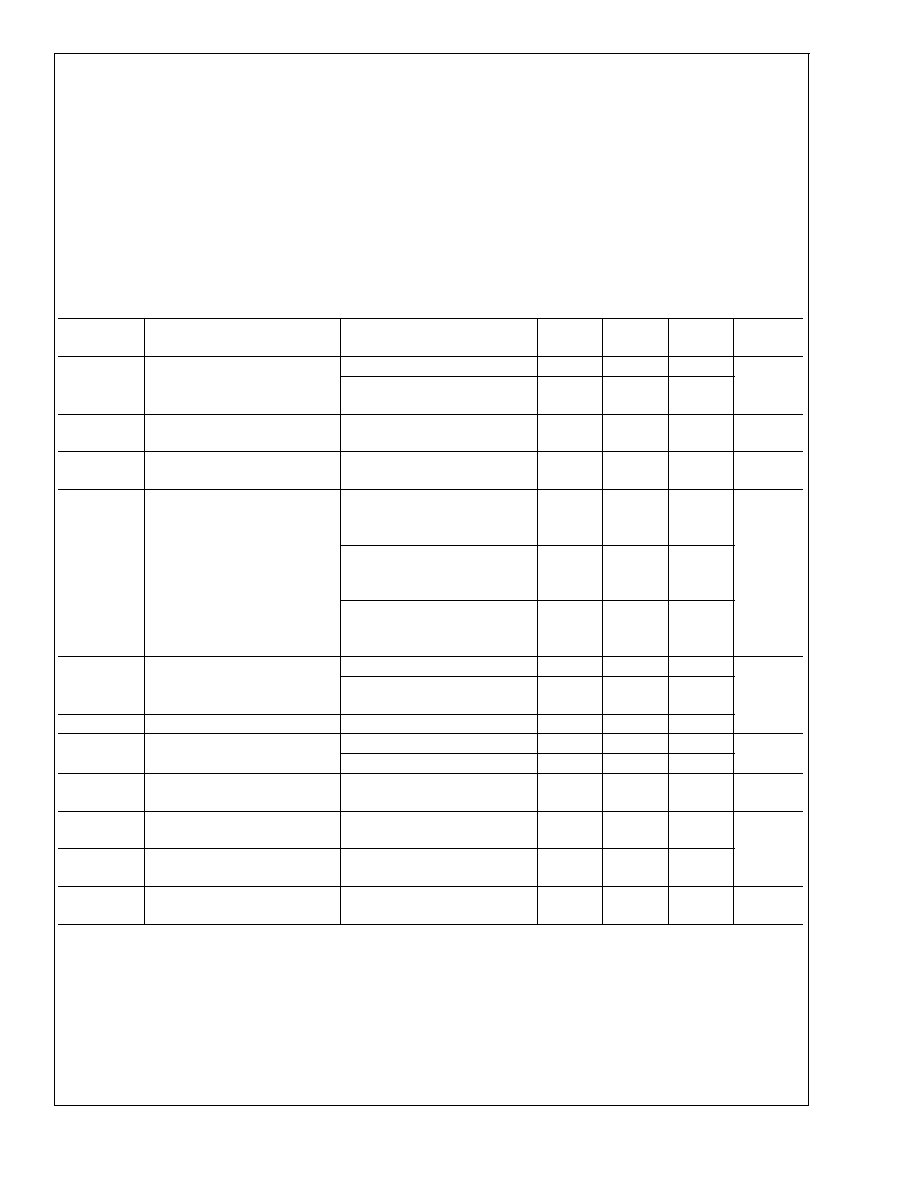

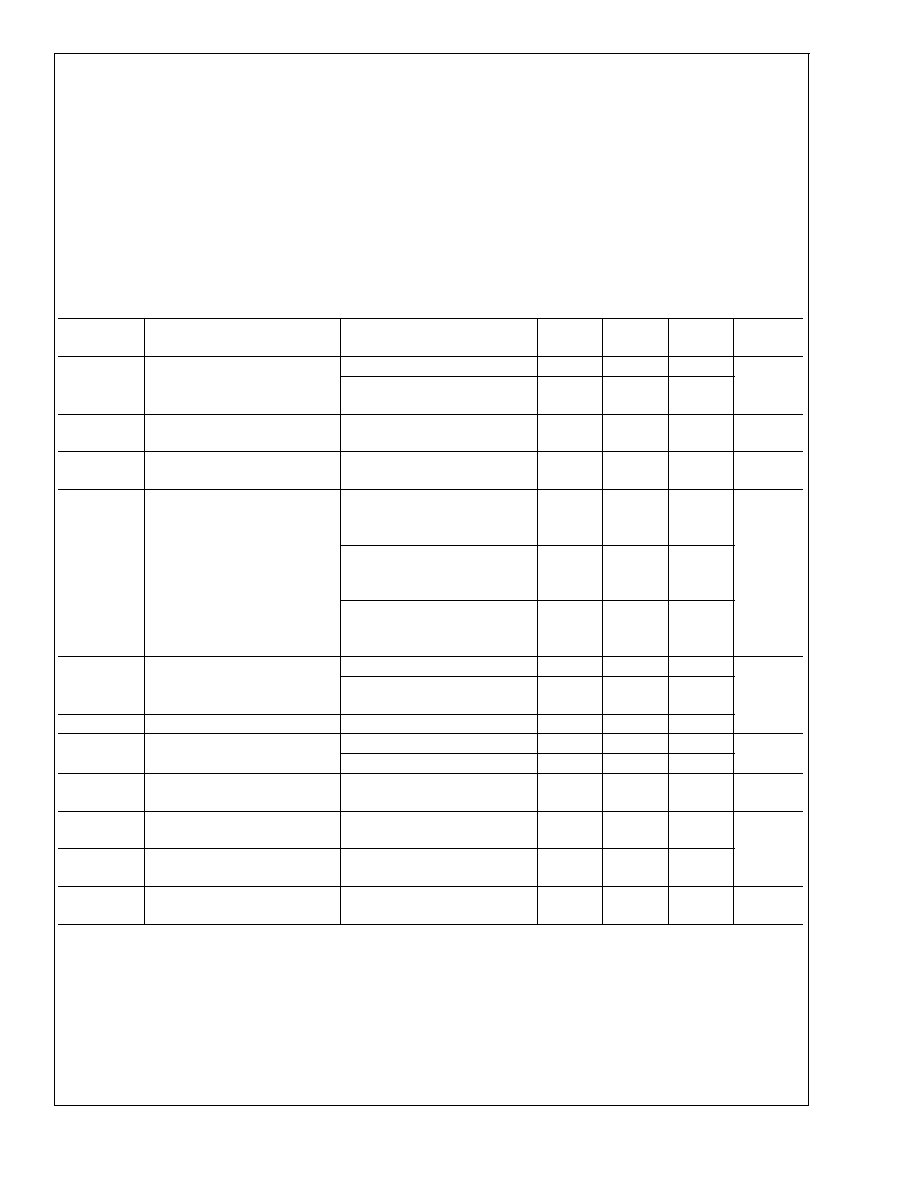

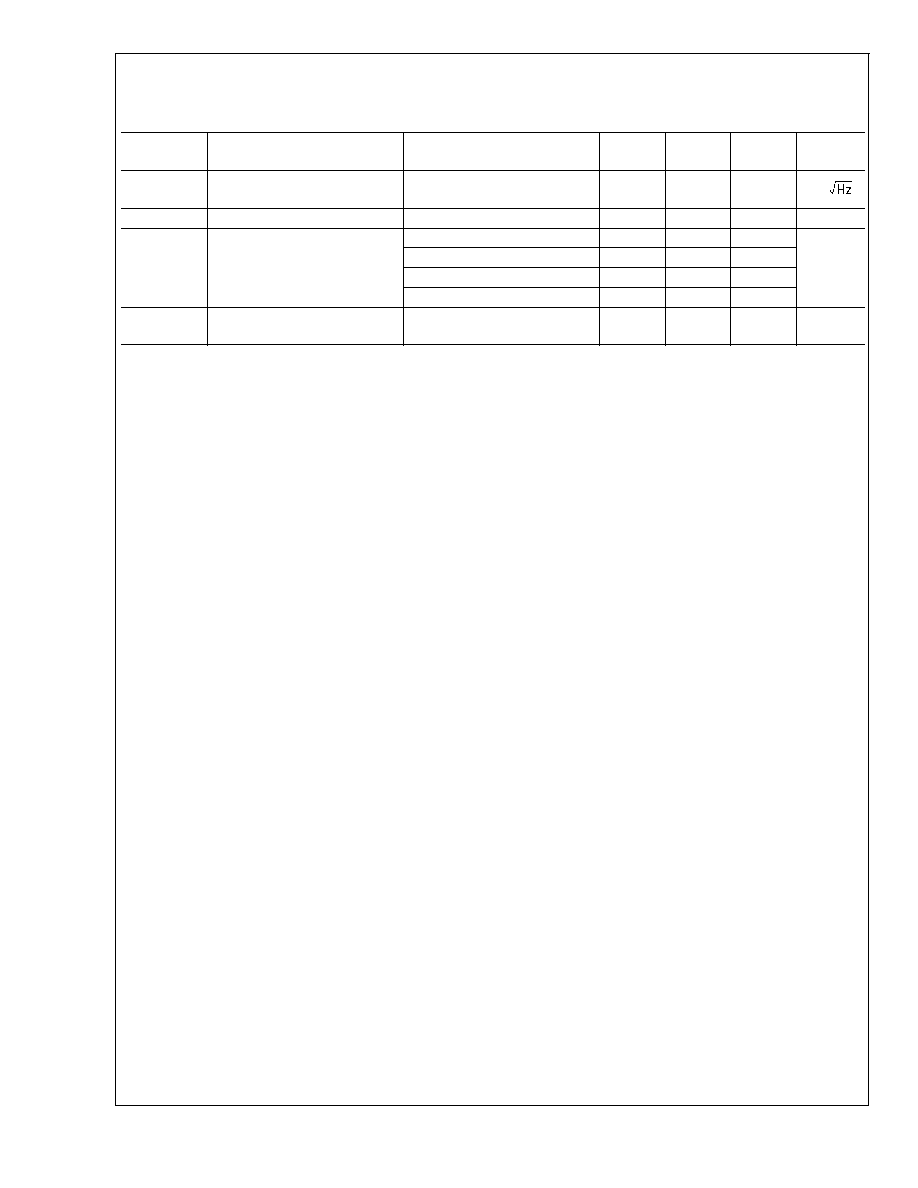

Electrical Characteristics

Limits in standard typeface are for T

J

= 25∞C, and limits in boldface type apply

over the full operating temperature range. Unless otherwise specified: V

IN

= V

OUT

+ 1V, C

IN

= C

OUT

= 10 µF, I

LOAD

= 10mA.

Min/Max limits are guaranteed through testing, statistical correlation, or design.

Symbol

Parameter

Conditions

Min

Typ

(Note 4)

Max

Units

V

ADJ

ADJ Pin Voltage

V

IN

= 2.7V

1.225

1.25

1.275

V

3.2V

V

IN

10V

100 µA

<

I

L

<

0.5A

1.200

1.25

1.300

V

O

/

V

IN

Output Voltage Line Regulation

(Note 6)

V

O

+ 0.5V

V

IN

10V

I

L

= 25mA

0.03

0.1

%/V

V

O

/

I

L

Output Voltage Load Regulation

(Note 7)

1 mA

<

I

L

<

0.5A

V

IN

= V

O

+ 1V

1.8

5

%/A

V

IN

- V

O

Dropout Voltage (Note 8)

(V

O

= 2.5V)

I

L

= 0.1A

I

L

= 0.5A

80

430

145

725

mV

(V

O

= 3.3V)

I

L

= 0.1A

I

L

= 0.5A

65

330

110

550

(V

O

= 5V)

I

L

= 0.1A

I

L

= 0.5A

45

250

100

450

I

Q

Quiescent Current

V

IN

10V, I

L

= 100 µA - 0.5A

55

100

µA

V

EN

0.4V,

(LP38693-ADJ Only)

0.001

1

I

L

(MIN)

Minimum Load Current

V

IN

- V

O

4V

100

I

FB

Foldback Current Limit

V

IN

- V

O

>

5V

350

mA

V

IN

- V

O

<

4V

850

PSRR

Ripple Rejection

V

IN

= V

O

+ 2V(DC), with 1V(p-p)

/ 120Hz Ripple

55

dB

T

SD

Thermal Shutdown Activation

(Junction Temp)

160

∞C

T

SD

(HYST)

Thermal Shutdown Hysteresis

(Junction Temp)

10

I

ADJ

ADJ Input Leakage Current

V

ADJ

= 0 - 1.5V

V

IN

= 10V

-100

0.01

100

nA

LP38691-ADJ/LP38693-ADJ

www.national.com

3

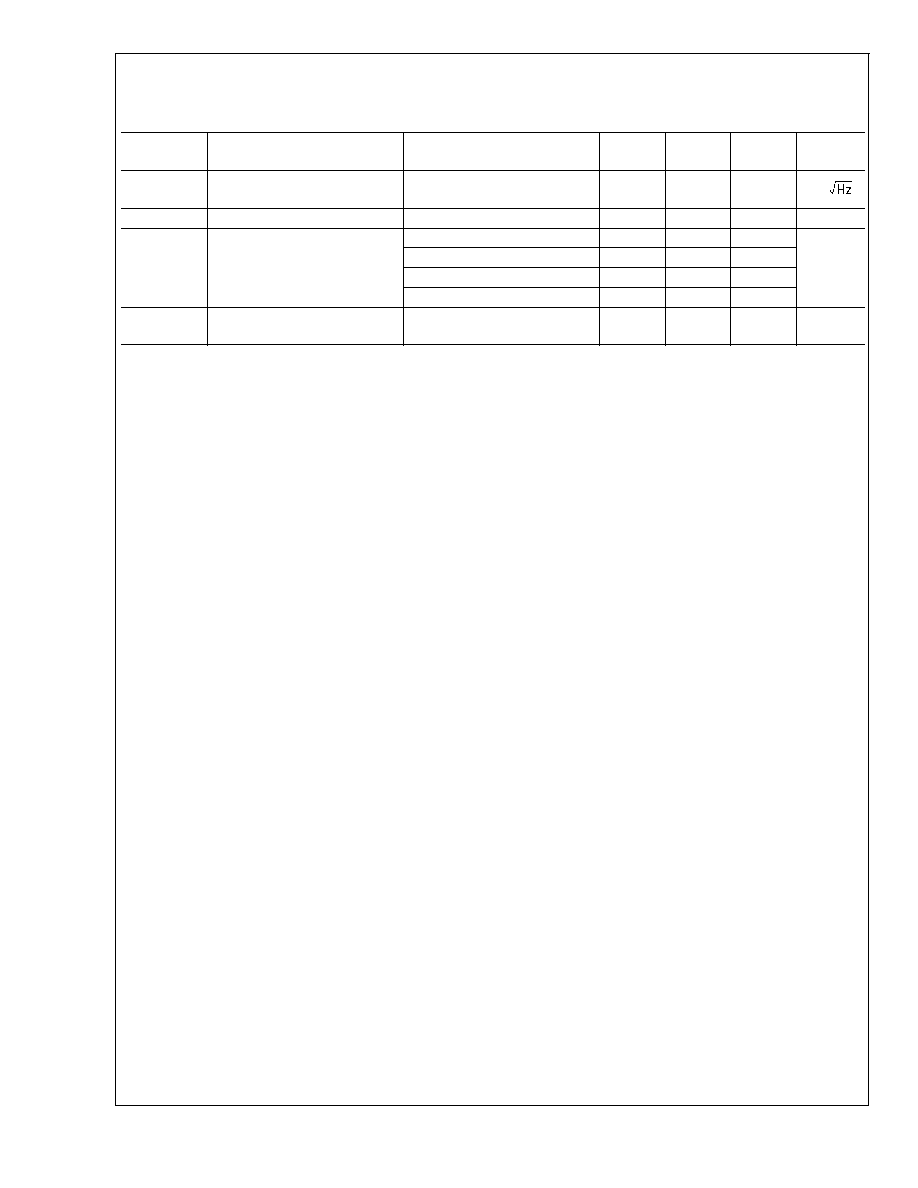

Electrical Characteristics

Limits in standard typeface are for T

J

= 25∞C, and limits in boldface type apply

over the full operating temperature range. Unless otherwise specified: V

IN

= V

OUT

+ 1V, C

IN

= C

OUT

= 10 µF, I

LOAD

= 10mA.

Min/Max limits are guaranteed through testing, statistical correlation, or design. (Continued)

Symbol

Parameter

Conditions

Min

Typ

(Note 4)

Max

Units

e

n

Output Noise

BW = 10Hz to 10kHz

V

O

= 3.3V

0.7

µV/

V

O

(LEAK)

Output Leakage Current

V

O

= V

O

(NOM) + 1V

@

10V

IN

0.5

2

µA

V

EN

Enable Voltage (LP38693-ADJ

Only)

Output = OFF

0.4

V

Output = ON, V

IN

= 4V

1.8

Output = ON, V

IN

= 6V

3.0

Output = ON, V

IN

= 10V

4.0

I

EN

Enable Pin Leakage

(LP38693-ADJ Only)

V

EN

= 0V or 10V, V

IN

= 10V

-1

0.001

1

µA

Note 1: Absolute maximum ratings indicate limits beyond which damage to the component may occur. Operating ratings indicate conditions for which the device

is intended to be functional, but do not guarantee specific performance limits. For guaranteed specifications, see Electrical Characteristics. Specifications do not

apply when operating the device outside of its rated operating conditions.

Note 2: At elevated temperatures, device power dissipation must be derated based on package thermal resistance and heatsink values (if a heatsink is used). The

junction-to-ambient thermal resistance (

J-A

) for the SOT-223 is approximately 125 ∞C/W for a PC board mounting with the device soldered down to minimum copper

area (less than 0.1 square inch). If one square inch of copper is used as a heat dissipator for the SOT-223, the

J-A

drops to approximately 70 ∞C/W. The

J-A

values

for the LLP package are also dependent on trace area, copper thickness, and the number of thermal vias used (refer to application note AN-1187). If power disspation

causes the junction temperature to exceed specified limits, the device will go into thermal shutdown.

Note 3: ESD is tested using the human body model which is a 100pF capacitor discharged through a 1.5k resistor into each pin.

Note 4: Typical numbers represent the most likely parametric norm for 25∞C operation.

Note 5: If used in a dual-supply system where the regulator load is returned to a negative supply, the output pin must be diode clamped to ground.

Note 6: Output voltage line regulation is defined as the change in output voltage from nominal value resulting from a change in input voltage.

Note 7: Output voltage load regulation is defined as the change in output voltage from nominal value as the load current increases from 1mA to full load.

Note 8: Dropout voltage is defined as the minimum input to output differential required to maintain the output within 100mV of nominal value.

LP38691-ADJ/LP38693-ADJ

www.national.com

4

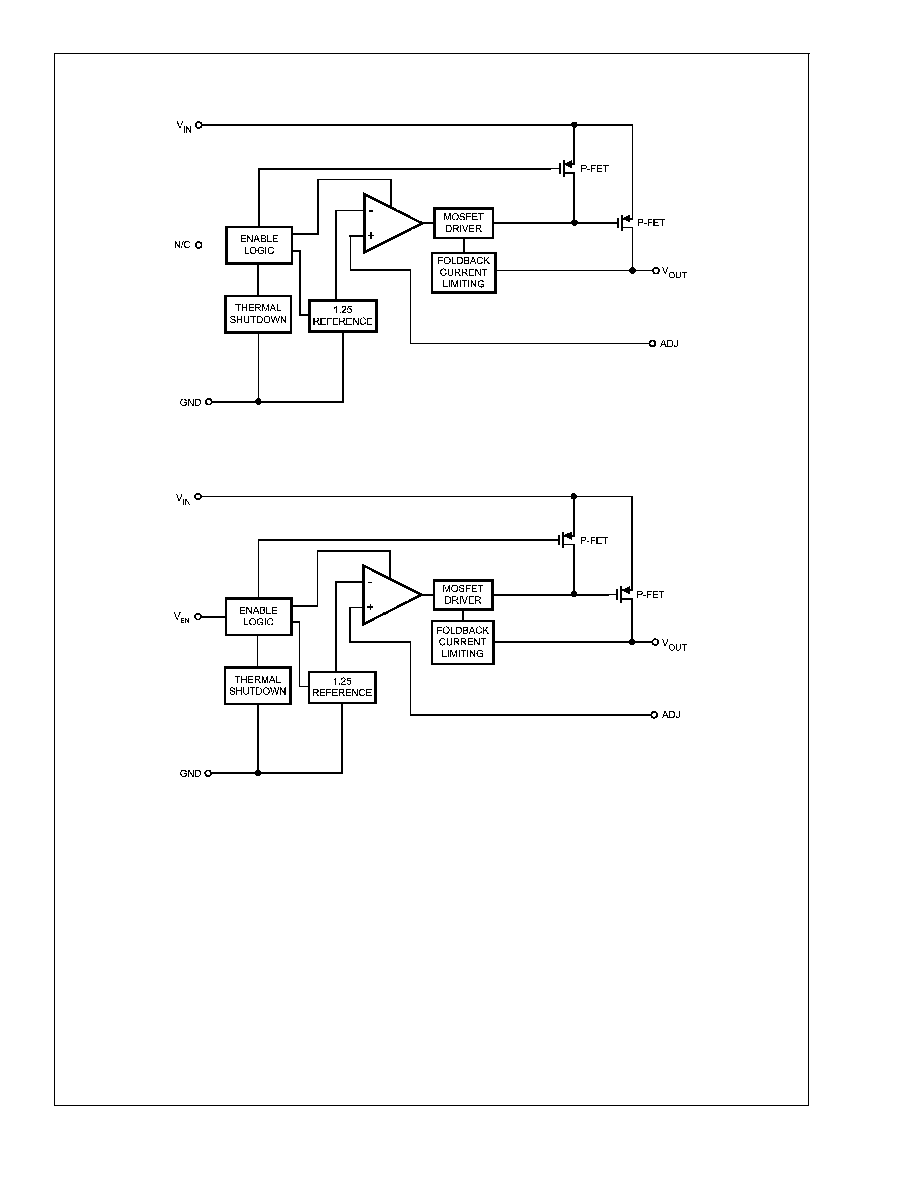

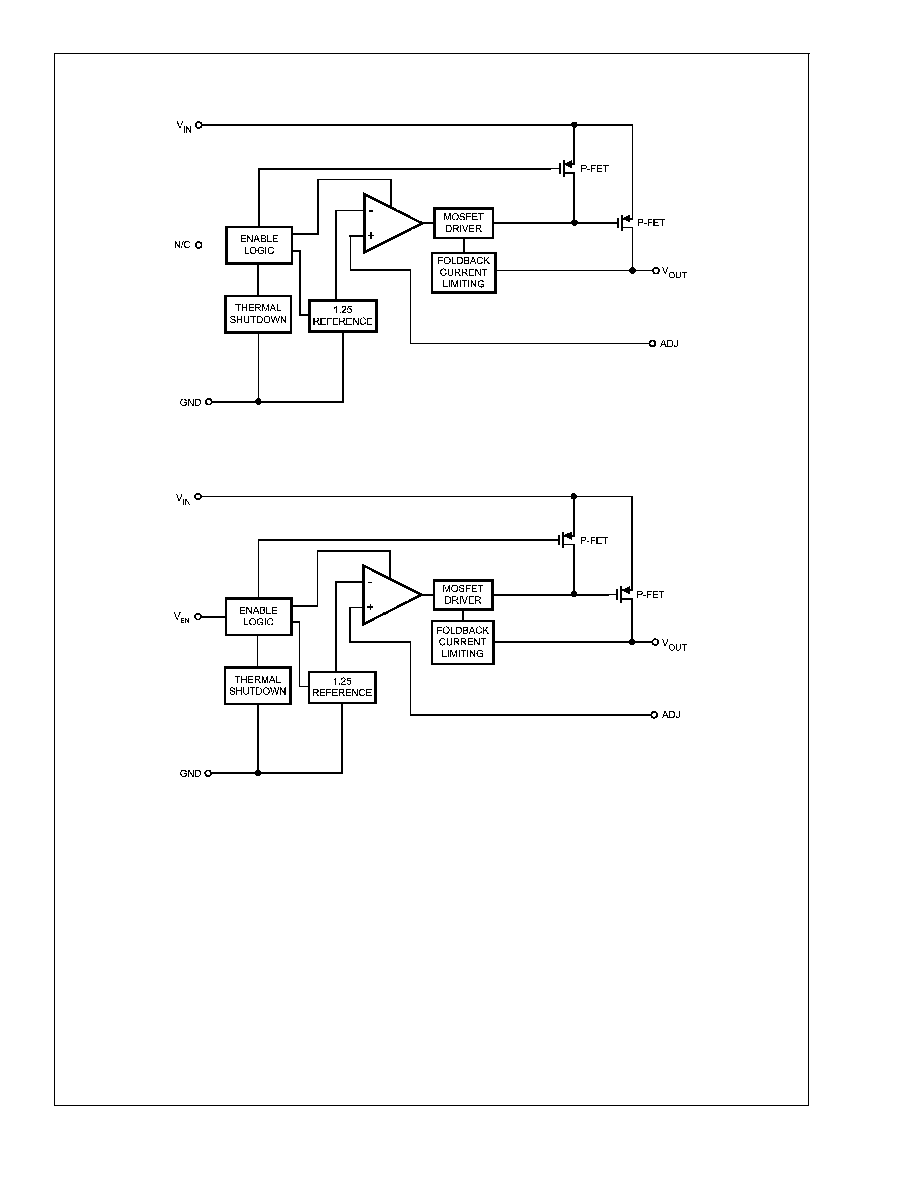

Block Diagrams

20126806

FIGURE 1. LP38691-ADJ Functional Diagram (LLP)

20126807

FIGURE 2. LP38693-ADJ Functional Diagram (SOT-223, LLP)

LP38691-ADJ/LP38693-ADJ

www.national.com

5