NTE6850

Integrated Circuit

NMOS, Asynchronous Communications

Interface Adapter

Description:

The NTE6850 Asynchronous Communications Interface Adapter provides the data formatting and

control to interface serial asynchronous data communications information to bus organized systems

such as the NTE6800 Microprocessing Unit.

The bus interface of the NTE6850 includes select, enable, read/write, interrupt and bus interface logic

to allow data transfer over an 8≠bit bidirectional data bus. The parallel data of the bus system is serial-

ly transmitted and received by the asynchronous data interface, with proper formatting and error

checking. The functional configuration of the ACIA is programmed via the data bus during system

initialization. A programmable control register provides variable word lengths, clock division ratios,

transmit control, receive control, and interrupt control. For peripheral or modem operation, three con-

trol lines are provided. These lines allow the ACIA to interface directly with the NTE6860 0≠600 bps

digital modem.

Features:

D

8≠Bit and 9≠Bit Transmission

D

Optional Even and Odd Parity

D

Parity, Overrun and Framing Error Checking

D

Programmable Control Register

D

Optional

˜

1,

˜

16, and

˜

64 Clock Modes

D

Up to 1.0 Mbps Transmission

D

False Start Bit Deletion

D

Peripheral/Modem Control Functions

D

Double Buffered

D

One≠Stop or Two≠Stop Bit Operation

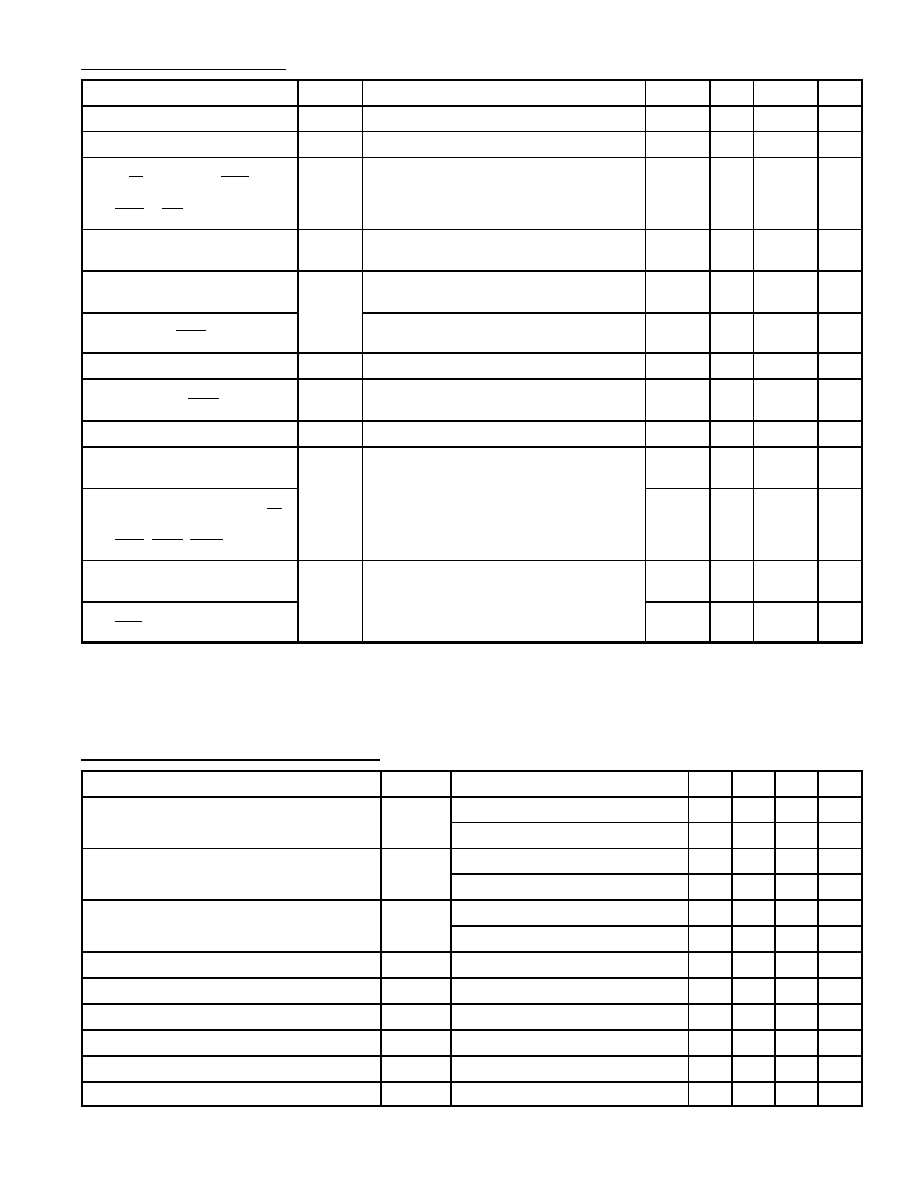

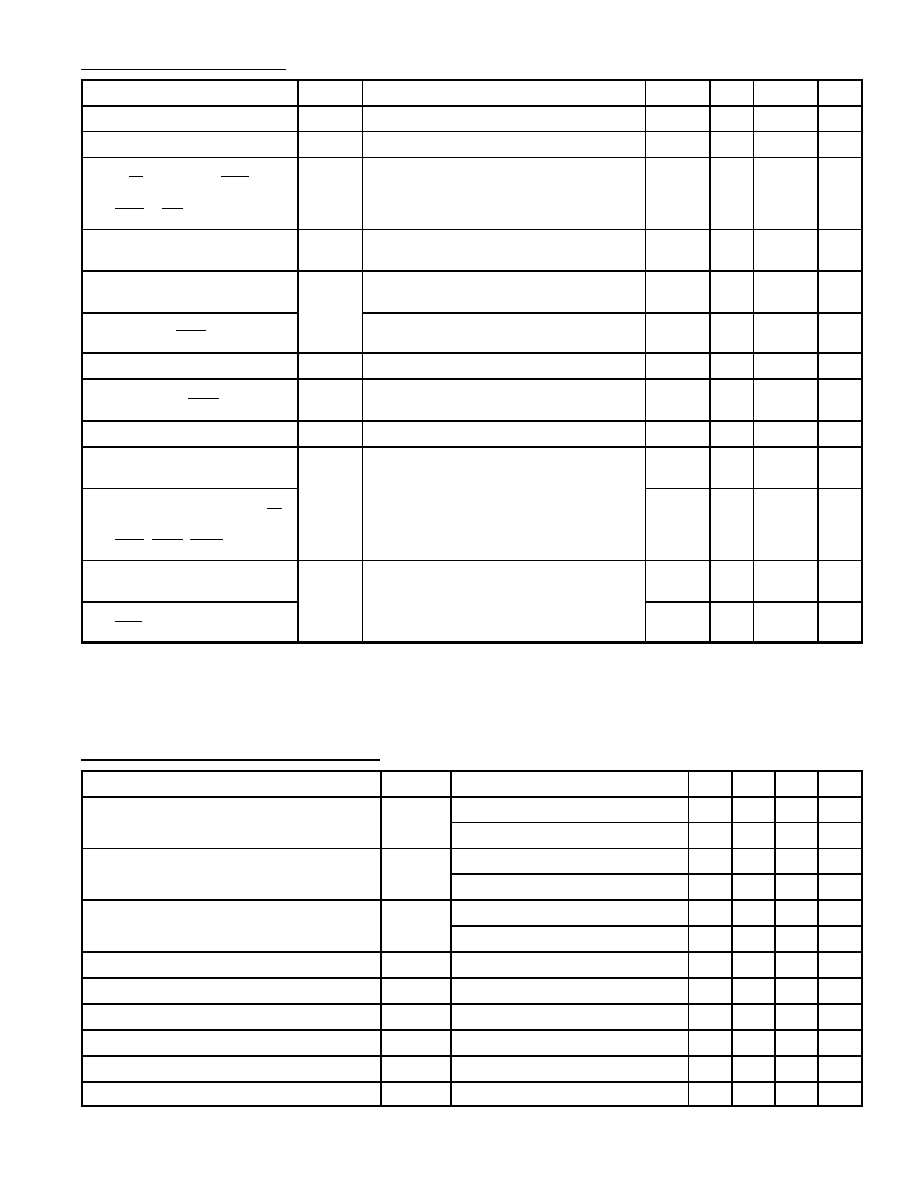

Absolute Maximum Ratings:

Supply Voltage, V

CC

≠0.3 to +7.0V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input Voltage, V

in

≠0.3 to +7.0V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operating Temperature Range, T

A

0

∞

to 70

∞

C

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage Temperature Range, T

stg

≠55

∞

to +150

∞

C

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Thermal Resistance, Junction≠to≠Ambient, R

thJA

120

∞

C/W

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Note 1. This device contains circuitry to protect the inputs against damage due to high static voltages

or electric fields; however, it is advised that normal precautions be taken to avoid application

of any voltage higher than maximum rated voltages to this high impedance circuit. Reliability

of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (e.g.

either V

SS

or V

CC

).

Electrical Characteristics: (V

CC

= 5V

±

5%, V

SS

= 0, T

A

= 0

∞

to +70

∞

C unless otherwise specified)

Parameter

Symbol

Test Conditions

Min

Typ

Max

Unit

Input High Voltage

V

IH

V

SS

+2.0

≠

V

CC

V

Input Low Voltage

V

IL

V

SS

≠0.3

≠

V

SS

+0.8

V

Input Leakage Current

R/W, CS0, CS1, CS2,

Enable, RS, R

X

D, R

X

C,

CTS, DCD

I

in

V

in

= 0 to 5.25V

≠

1.0

2.5

µ

A

Hi≠Z (Off≠State) Input Current

D0 ≠ D7

I

TSI

V

in

= 0.4 to 2.4V

≠

2.0

10.0

µ

A

Output High Voltage

D0 ≠ D7

V

OH

I

Load

= 205

µ

A, Enable Pulse Width < 25

µ

s

V

SS

+2.4

≠

≠

V

Output High Voltage

T

X

Data, RTS

I

Load

= 100

µ

A, Enable Pulse Width < 25

µ

s

V

SS

+2.

≠

≠

V

Output Low Voltage

V

OL

I

Load

= 1.6A, Enable Pulse Width < 25

µ

s

≠

≠

V

SS

+0.4

V

Output Leakage Current

(Off≠State) IRQ

I

LOH

V

OH

= 2.4V

≠

1.0

10

µ

A

Internal Power Dissipation

P

INT

T

A

= 0

∞

C, Note 2

≠

300

525

mW

Internal Input Capacitance

D0 ≠ D7

C

in

V

in

= 0, T

A

= +25

∞

C, f = 1MHz

≠

10.0

12.5

pF

Internal Input Capacitance

E, T

X

CLK, R

X

CLK, R/W,

RS, R

X

Data, CS0, CS1,

CS2, CTS, DCD

≠

7.0

7.5

pF

Output Capacitance

RTS, T

X

Data

C

out

V

in

= 0, T

A

= +25

∞

C, f = 1MHz

≠

≠

10

pF

Output Capacitance

IRQ

≠

≠

5

pF

Note 2. For temperatures less than T

A

= 0

∞

C, P

INT

maximum will increase.

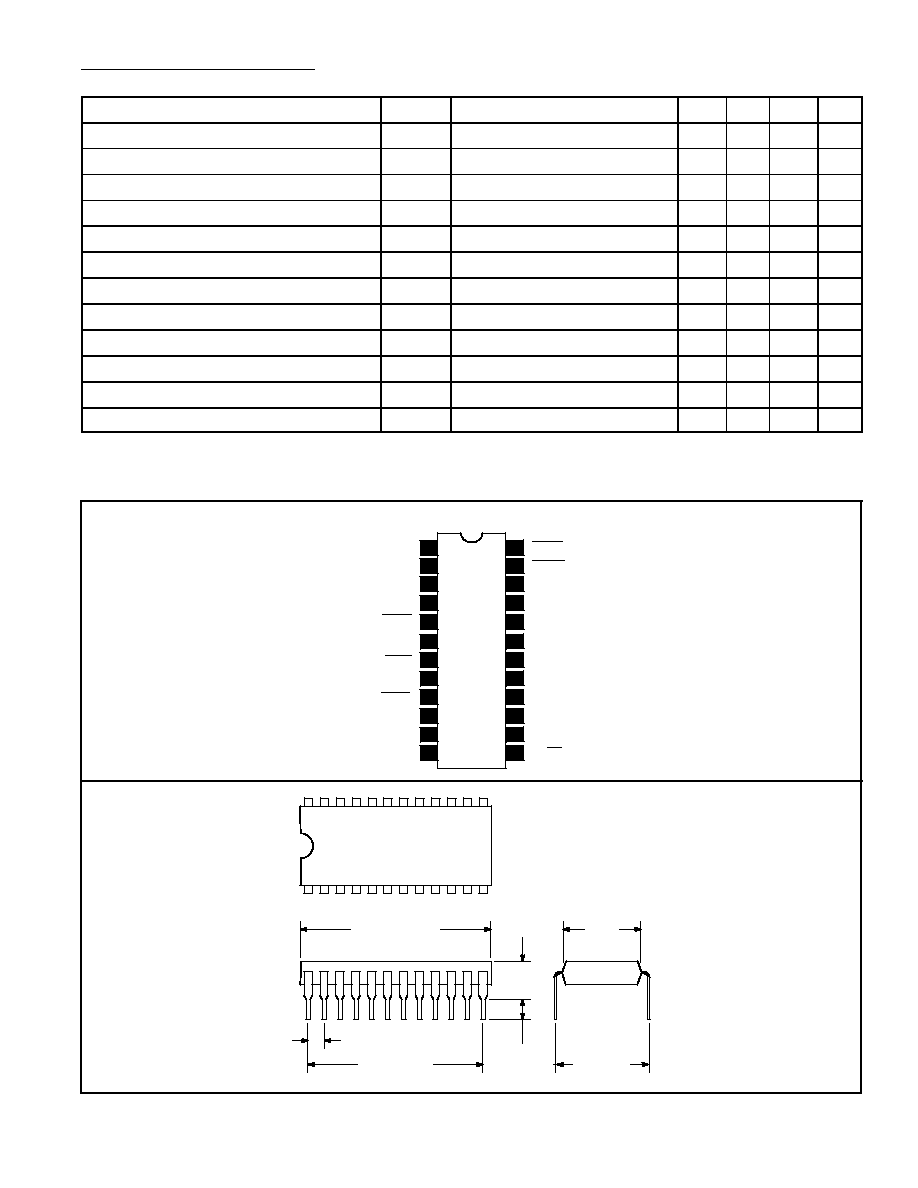

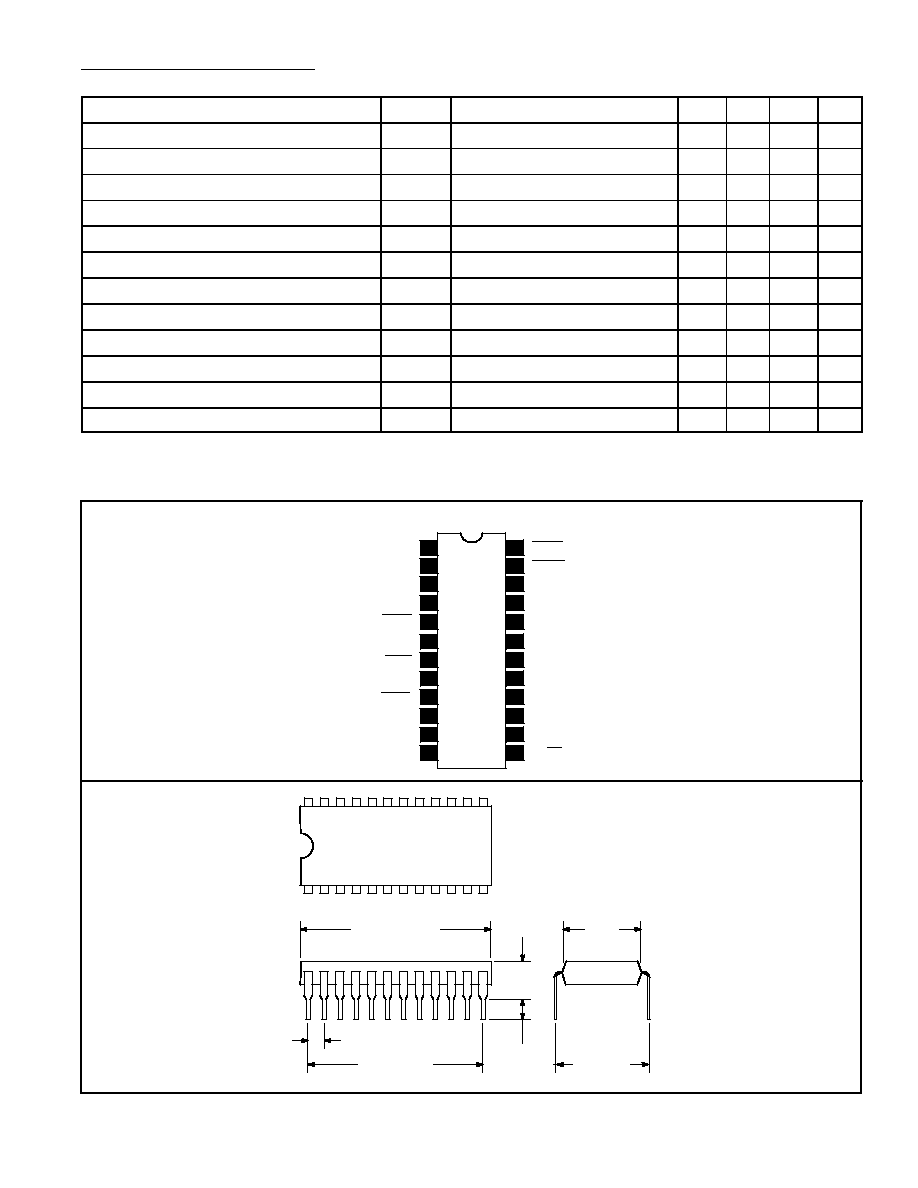

Serial Data Timing Characteristics:

Parameter

Symbol

Test Conditions

Min

Typ

Max Unit

Data Clock Pulse Width, Low

PW

CL

B

16,

B

64 Modes

600

≠

450

ns

B

1 Mode

900

≠

650

ns

Data Clock Pulse Width, High

PW

CH

B

16,

B

64 Modes

600

≠

450

ns

B

1 Mode

900

≠

650

ns

Data Clock Frequency

f

C

B

16,

B

64 Modes

≠

≠

0.8

MHz

B

1 Mode

≠

≠

500

kHz

Data Clock≠to≠Data Delay for Transmitter

t

TDD

≠

≠

600

ns

Receive Data Setup Time

t

RDS

B

1 Mode

250

≠

≠

ns

Receive Data Hold Time

t

RDH

B

1 Mode

250

≠

≠

ns

Interrupt Request Release Time

t

R

≠

≠

1.2

µ

s

Request≠to≠Send Delay Time

t

RTS

≠

≠

560

ns

Input Rise and Fall Times

t

r

, t

f

or 10% of the pulse width if smaller

≠

≠

1.0

µ

s

Bus Timing Characteristics: (V

L

4V, V

H

2.4V, measurement points 0.8V and 2V unless

otherwise specified)

Parameter

Symbol

Test Conditions

Min

Typ

Max

Unit

Cycle Time

t

cyc

1.0

≠

10.0

µ

s

Pulse Width, E Low

PW

EL

430

≠

9500

ns

Pulse Width, E High

PW

EH

450

≠

9500

ns

Clock Rise and Fall Time

t

r

, t

f

≠

≠

25

ns

Address Hold Time

t

AH

10

≠

≠

ns

Address Setup Time Before E

t

AS

80

≠

≠

ns

Chip Select Setup Time Before E

t

CS

80

≠

≠

ns

Chip Select Hold Time

t

CH

10

≠

≠

ns

Read Data Hold Time

t

DHR

Note 3

20

≠

50

ns

Write Data Hold Time

t

DHW

10

≠

≠

ns

Output data Delay Time

t

DHW

≠

≠

290

ns

Input Data Setup Time

t

DSW

165

≠

≠

ns

Note 3. The data bus output buffers are no longer sourcing or sinking current by t

DHR

max (High

Impedance).

V

DD

CTS

DCD

R/W

CS2

IRQ

RTS

Pin Connection Diagram

V

SS

D4

D2

D6

D5

1

2

3

4

Rx Data

Cx Clk

Tx Clk

5

6

Tx Data

7

8

CS0

24

23

22

21

D0

D1

20

19

D3

18

17

9

16

D7

E

10

CS1

11

RS

15

14

12

13

1

12

24

13

1.300 (33.02)

Max

.520

(13.2)

.600

(15.24)

1.100 (27.94)

.100 (2.54)

.225

(5.73)

Max

.126

(3.22)

Min