PRODUCT SPECIFICATION

Main office: Nordic VLSI ASA - Vestre Rosten 81, N-7075 Tiller, Norway - Phone +4772898900 - Fax +4772898989

Branch office: Nordic VLSI ASA - P.O.Box 436 Sk¯yen, N-0212 Oslo, Norway - Phone +4722511050 - Fax +4722511099

Revision: 2.1

Page 1 of 11

February 8th, 2001

10-Bit 40MSPS Sampling

Analog-to-Digital Converter

FEATURES

∑

2.5V power supply

∑

SNR typ 60dB for (f

in

= 10MHz)

∑

Low power (79mW@2.5V)

∑

Sample rate:10 - 40MSPS

∑

Frequency dependent biasing

∑

Internal/sample hold

∑

Differential input

∑

Low input capacitance

∑

Evaluation Board Available

APPLICATIONS

∑

Imaging

∑

Test equipment

∑

Computer scanners

∑

Communications

∑

Set top boxes

∑

Video products

GENERAL DESCRIPTION

The nAD1040-25 is a compact, high-speed, low power 10-bit monolithic analog-to-

digital converter, implemented in the TSMC Mixed-Signal MiM CMOS process. It

has 10-bit resolution with 9.5 effective bits, and close to 11 bit dynamic range for

video frequency signals. The converter includes a high bandwidth sample and hold.

The full scale range is

±

1V. The full scale range can be set between

±

0.5V and

±

1V.

It operates from a single 2.5V supply. Its low distortion and high dynamic range offers

the performance needed for demanding imaging, multimedia, telecommunications and

instrumentation applications.

The bias current level for the ADC is automatically adjusted based on the clock input

frequency. Hence, the power dissipation of the device is continuously minimised for

the current operation frequency.

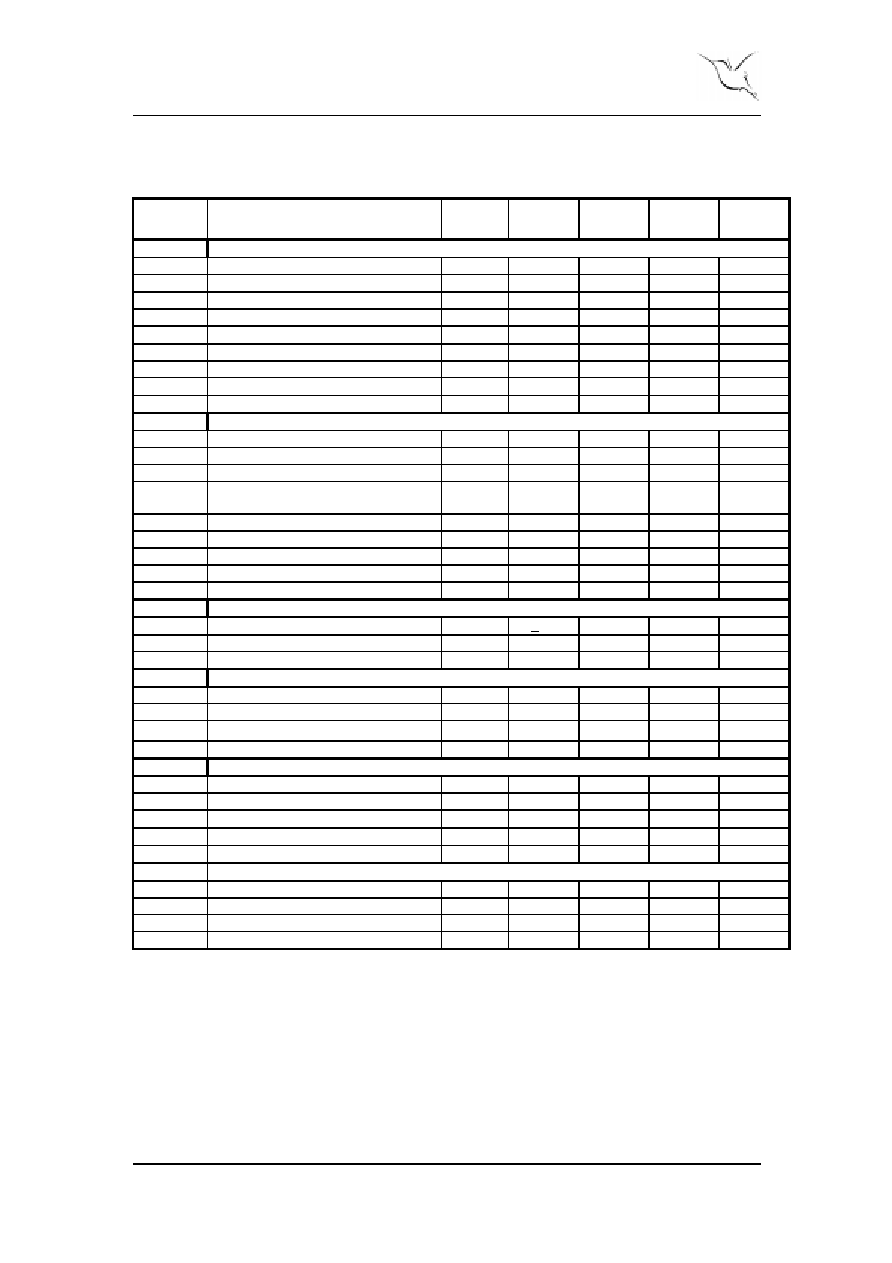

QUICK REFERENCE DATA

Symbol

Parameter

Conditions

Min.

Typ.

Max.

Unit

V

DD

supply voltage

2.25

2.5

2.75

V

I

DD

supply current

(40 MSPS)

28

mA

P

D

power dissipation

(40 MSPS)

Except digital

output drivers

70

mW

P

D

power dissipation

(10 MSPS)

Except digital

output drivers

20

mW

P

D

power dissipation

(sleep mode)

Except digital

output drivers

1.5

mW

DNL

differential nonlinearity

f

IN

=0.9991MHz

±0.5

LSB

INL

integral nonlinearity

f

IN

=0.9991MHz

±

1

LSB

f

S

conversion rate

10

40

MHz

N

resolution

10

bit

Table 1. Quick reference data

nAD1040-25

PRODUCT SPECIFICATION

nAD1040-25 10 Bit 40 MSPS Sampling ADC

Main office: Nordic VLSI ASA - Vestre Rosten 81, N-7075 Tiller, Norway - Phone +4772898900 - Fax +4772898989

Branch office: Nordic VLSI ASA - P.O.Box 436 Sk¯yen, N-0212 Oslo, Norway - Phone +4722511050 - Fax +4722511099

Revision: 2.1

Page 2 of 11

February 8th, 2001

GENERAL DESCRIPTION (Continued)

The nAD1040-25 has a pipelined architecture - resulting in low input capacitance.

Digital error correction of the 9 most significant bits ensures good linearity for input

frequencies approaching Nyquist. The nAD1040-25 is compact. The core occupies

less than 1mm

2

of die area in TSMC Mixed Signal MiM 0.25

µ

m CMOS process. The

fully differential architecture makes it insensitive to substrate noise. Thus it is ideal as

a mixed signal ASIC macro cell.

BLOCK DIAGRAM

Figure 1. Block diagram nAD1040-25

C O R R _ L O G

ANCLOCK

B I T < 9 : 0 >

I N _ C O R R < 1 7 : 0 >

C K B U S < 3 : 0 >

C L K

I N N

I N P

REFP

REFN

B I A S 0

B I A S 1

CLOCKBUF

EXTREF

C K C O R R < 1 : 0 >

C K 0

C K 0 B

C K 2

C K 2 B

n A D 1 0 4 0 - 2 5

ANALOG 1040

C M

PRODUCT SPECIFICATION

nAD1040-25 10 Bit 40 MSPS Sampling ADC

Main office: Nordic VLSI ASA - Vestre Rosten 81, N-7075 Tiller, Norway - Phone +4772898900 - Fax +4772898989

Branch office: Nordic VLSI ASA - P.O.Box 436 Sk¯yen, N-0212 Oslo, Norway - Phone +4722511050 - Fax +4722511099

Revision: 2.1

Page 3 of 11

February 8th, 2001

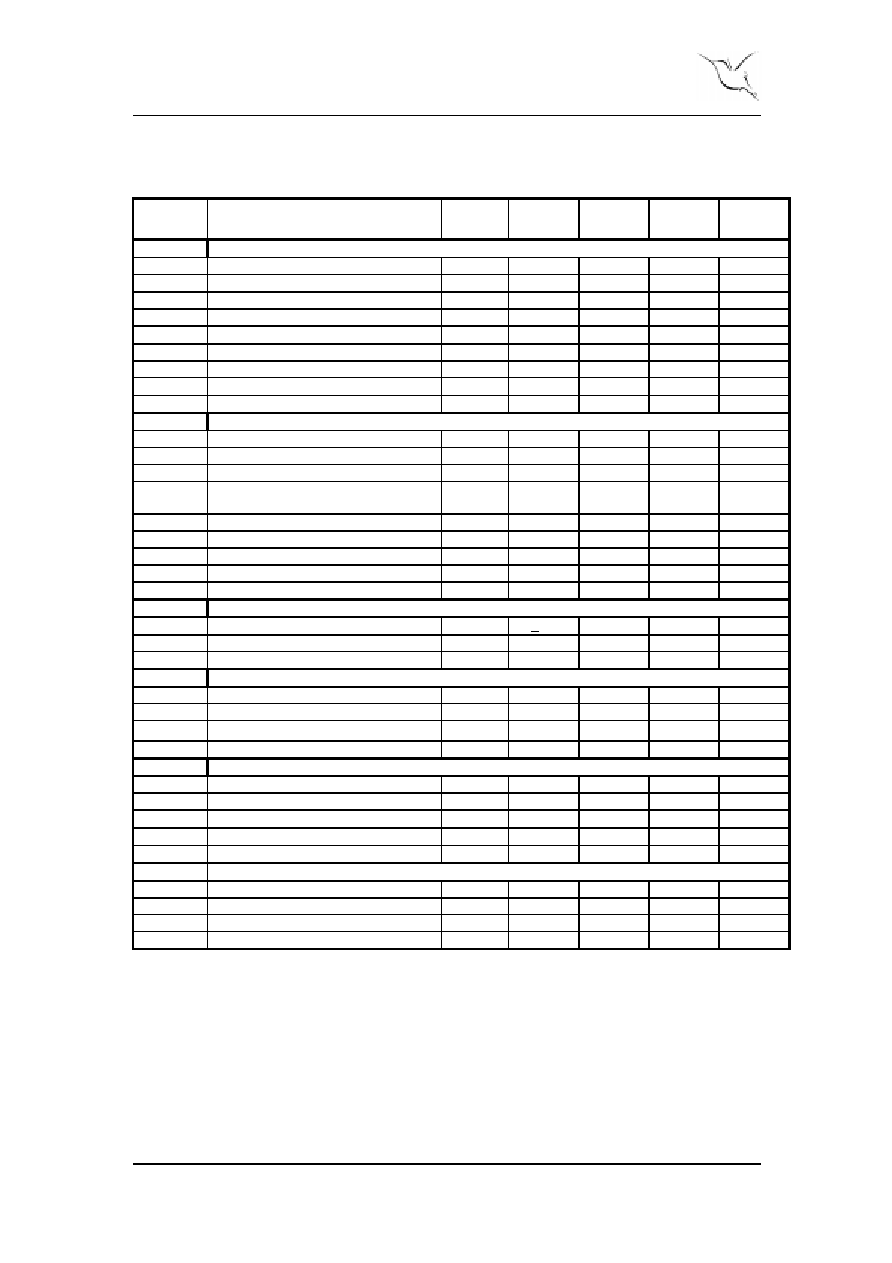

ELECTRICAL SPECIFICATIONS

(

At T

A

= 25

∞

C, V

DD

= 2.5V, Sampling Rate = 40MHz, Input frequency = 10MHz dBFS, Differential

input signal, 50% duty cycle clock unless otherwise noted).

Symbol Parameter (condition)

Test

Level

Min.

Typ.

Max.

Units

DC Accuracy

DNL

Differential Nonlinearity

f

IN

= 0.9991 MHz

III

±

0.5

±

1.0

LSB

INL

Integral Nonlinearity

f

IN

= 0.9991 MHz

III

±

1.0

±

3.0

LSB

V

OS

Midscale offset

III

±

5.9

mV

CMRR

Common Mode Rejection Ratio (of V

OS

)

-65

dB

Dynamic Performance

SINAD

Signal to Noise and Distortion Ratio

f

IN

= 1 MHz

III

57

60

dBFS

f

IN

= 10 MHz

III

56

59

dBFS

SNR

Signal to Noise Ratio (without

harmonics)

f

IN

= 10 MHz

III

57

60

dBFS

SFDR

Spurious Free Dynamic Range

f

IN

= 1 MHz

III

60

72

dBFS

f

IN

= 10 MHz

III

60

66

dBFS

PSRR

Power Supply Rejection Ratio (of V

OS

)

III

-55

dB

Analog Input

V

FSR

Input Voltage Range (differential)

IV

+0.5

±

1.2

V

V

CMI

Common mode input voltage

III

1

1.2

1.35

V

C

INA

Input Capacitance (differential)

III

2.5

pF

Reference Voltages

V

REFN

Negative Input Voltage

III

0.7

0.85

V

V

REFP

Positive Input Voltage

III

1.60

1.7

V

V

RR

Reference input voltage range

1

III

0.5

0.75

1

V

V

CM

Common mode output voltage

III

1.2

V

Digital Inputs

V

IL

Logic "0" voltage

IV

0.4

V

V

IH

Logic "1" voltage

IV

AV

DD

-0.4

V

I

IL

Logic "0" current (V

I

=V

SS

)

IV

±

10

µ

A

I

IH

Logic "1" current (V

I

=V

DD

)

IV

±

10

µ

A

C

IND

Input Capacitance

IV

5

pF

Digital Outputs

V

OL

Logic "0" voltage (I = 2 mA)

IV

0.2

0.4

V

V

OH

Logic "1" voltage (I = 2 mA)

IV

85% OV

DD

90% OV

DD

V

t

H

Output hold time

V

1.9

ns

t

D

Output delay time

V

4.8

ns

(table continued on next page)

1

See "Input Signal Range" section

PRODUCT SPECIFICATION

nAD1040-25 10 Bit 40 MSPS Sampling ADC

Main office: Nordic VLSI ASA - Vestre Rosten 81, N-7075 Tiller, Norway - Phone +4772898900 - Fax +4772898989

Branch office: Nordic VLSI ASA - P.O.Box 436 Sk¯yen, N-0212 Oslo, Norway - Phone +4722511050 - Fax +4722511099

Revision: 2.1

Page 4 of 11

February 8th, 2001

Switching Performance

f

S

Conversion Rate

V

10

40

MSPS

Pipeline Delay

IV

6

Clocks

AP

Aperture jitter

V

TBD

ps

t

AP

Aperture delay

V

1.4

ns

Power Supply

V

DD

supply voltage

V

2.25

2.5

2.75

V

I

DD

supply current (except digital output)

IV

28

mA

P

D

power dissipation (except digital output)

(60 MSPS)

IV

70

mW

P

D

power dissipation (except digital output)

(10 MSPS)

IV

20

mW

P

D

power dissipation (except digital output)

(sleep mode)

1)

IV

1.5

mW

V

SS

supply voltage

GND

AV

DD

-

DV

DD1

analog power ≠ digital power pins

-0.2

+0.2

V

OV

DD

Output driver supply voltage

III

2.25

2.5/3.0

3.3

V

T

Ambient operating temperature

IV

-40

+85

∞

C

Table 3. Electrical specifications

1)

Power Down Mode ("zero" power dissipation) available for IP version of nAD1040-25

Test Levels

Test Level I: 100% production tested at +25∞C

Test Level II: 100% production tested at +25∞C and sample tested at specified

temperatures

Test Level III: Sample tested only

Test Level IV: Parameter is guaranteed by design and characterisation testing

Test Level V: Parameter is typical value only

Test Level VI: 100% production tested at +25∞C. Guaranteed by design and

characterisation testing for industrial temperature range

ABSOLUTE MAXIMUM RATINGS

Supply voltages

AV

DD

...............................- 0.3V to +3V

DV

DD1

..................- 0.3V to V

DD

+ 0.3V

OV

DD

...................- 0.3V to V

DD

+ 0.3V

Input voltages

Analog In.......... - 0.3V to AV

DD

+ 0.3V

Digital In..............- 0.3V to V

DD

+ 0.3V

REF

P

................. - 0.3V to AV

DD

+ 0.3V

REF

N

................. - 0.3V to AV

DD

+ 0.3V

CLOCK ...............- 0.3V to V

DD

+ 0.3V

Temperatures

Operating Temperature....-40 to +85

∞

C

Storage Temperature.....-65 to +125

∞

C

Note: Stress above one or more of the limiting values may cause permanent damage

to the device.

PRODUCT SPECIFICATION

nAD1040-25 10 Bit 40 MSPS Sampling ADC

Main office: Nordic VLSI ASA - Vestre Rosten 81, N-7075 Tiller, Norway - Phone +4772898900 - Fax +4772898989

Branch office: Nordic VLSI ASA - P.O.Box 436 Sk¯yen, N-0212 Oslo, Norway - Phone +4722511050 - Fax +4722511099

Revision: 2.1

Page 5 of 11

February 8th, 2001

PIN FUNCTIONS

Pin Name

Description

INP INN

Differential input signal pins. Common mode voltage: 1.2V

REFP REFN

Reference input pins. Bypass with 100nF || 1nF capacitors close to the pins. See

Application Information below.

BIAS0, BIAS1

Digital inputs for max. sampling rate programming.

BIAS1=0, BIAS0=0: Sleep mode (power save)

BIAS1=0, BIAS0=1: - 12.5% bias

BIAS1=1, BIAS0=0: +12.5% bias

BIAS1=1, BIAS0=1: Typ. Bias

The bias current is automatically scaled based on the clock input frequency.

CLK

Clock input

CM

Common mode voltage output

BIT9 - BIT0

Digital outputs ( MSB to LSB)

OUTEN

Enable digital outputs

EXTREF

Disable internal references

V

DD

Power pins for chip core

V

SS

Ground pins

OV

DD

Power pins for output drivers

Table 4. Pin functions

PIN ASSIGNMENT

Figure 2. Pin assignment for the 28 pin package

n A D 1 0 4 0 - 0 2 5

2 8 P I N S S O P

1

2

3

4

5

6

7

8

9

1 0

1 1

1 2

1 3

1 4

B I T 9

B I T 8

B I T 7

B I T 6

B I T 5

O V

D D

O V

D D

V

S S

V

S S

B I T 4

B I T 3

B I T 2

B I T 1

B I T 0

2 8

2 7

2 6

2 5

2 4

2 3

2 2

2 1

2 0

1 9

1 8

1 7

1 6

1 5

C M

B I A S 1

R E F N

R E F P

B I A S 0

C L K

V

D D

V

S S

V

V

O U T E N

I N P

I N N

D D

S S

E X T R E F