PRELIMINARY PRODUCT SPECIFICATION

nAD12110-18a

12-bit 110 MSPS Analog-to-Digital Converter IP

Nordic VLSI ASA - Vestre Rosten 81, N-7075 Tiller, Norway - Phone +4772898900 - Fax +4772898989

Revision: 1.0A

Page 1 of 14

2003-04-10

FEATURES

∑

12-bit ADC

∑

Up to 110 MSPS Conversion Rate

∑

Single 1.8 V Power Supply

∑

1.5 V p-p Differential Input

∑

Excellent Dynamic Performance

67 dBc SNR at F

IN

= 10 MHz

70 dBc SFDR at F

IN

= 10 MHz

∑

600 MHz Analog Input Bandwidth

∑

Low Power Consumption

105 mW at 110 MSPS

30 mW at 25 MSPS

∑

Dynamic Power Scaling

∑

Power Saving Idle Modes

∑

Internal Voltage Reference

∑

0.86 mm

2

Core Area

APPLICATIONS

∑

Communication Receive Channel

WLAN / HiperLan / 802.11x

∑

Digital Imaging / Video

∑

TV / Video / Radio Decoders

∑

Graphic Capture

GENERAL DESCRIPTION

The nAD12110-18a is a monolithic, high-speed,

low power, analog-to-digital converter silicon IP. It

uses a fully differential multistage pipeline

architecture with digital error correction to provide

12-bit accuracy from 15 to 110 MSPS conversion

speed. The core includes a wide-band sample-and-

hold and an internal voltage reference that provides

a nominal full-scale range of 1.5 V peak-to-peak.

The IP is designed for high dynamic performance

at input frequencies up to Nyquist and beyond. It

thus represents an ideal solution for

PIPELINE

ADC

DI

GIT

A

L

CO

RREC

T

I

O

N

DYNAMIC

BIAS

VOLTAGE

REFERENCE

BITO[11:0]

RFLAG[2:0]

OPM[1:0]

CLK

EXTREF

TIMING GENERATOR

DIGITAL CONTROL

INP

VCM

INN

REFP

REFN

Figure 1. Functional block diagram

demanding applications like broadband

communication, digital imaging and multimedia.

The ADC consumes only 105 mW at 110 MSPS

operation. Dynamic power scaling means that the

power consumption is scaled with the operating

frequency resulting in only 30 mW consumption at

25 MSPS operation. Combined with power saving

idle modes the ADC is suitable for battery powered

devices.

The conversion is controlled by the single-ended

clock input. Output data is available in a binary

offset coded format. Three out-of-range indicator

bits are also available for determining if the input

signal is over-range, under-range or out-of-range.

Implemented in a generic 0.18

µ

m CMOS process,

operating from a single 1.8 V supply and

employing a fully differential architecture it

represents an ideal ADC for highly integrated

mixed-signal systems.

QUICK REFERENCE DATA

IP Type / Technology

Hard Macro / TSMC Generic, 6 Metal 0.18

µ

m CMOS

IP Area / Dimensions

0.86 mm

2

/ 1.310

◊

0.65 mm

Parameter

Min.

Typ.

Max.

Unit

Supply Voltage

1.6

1.8

2.0

V

Power Dissipation, @ F

CLK

= 110 MHz

105

mW

Differential Non Linearity

±

0.5

LSB

Integral Non Linearity

±

1.5

LSB

Signal-to-Noise Ration, F

IN

= 10 MHz

67

dB

Spurious-Free-Dynamic Range, F

IN

= 10 MHz

70

dB

Table 1. nAD12110-18a quick reference data

PRELIMINARY PRODUCT SPECIFICATION

nAD12110-18a - 12-bit 110 MSPS Analog-to-Digital Converter IP

Nordic VLSI

Page 2 of 14

Revision: 1.0A

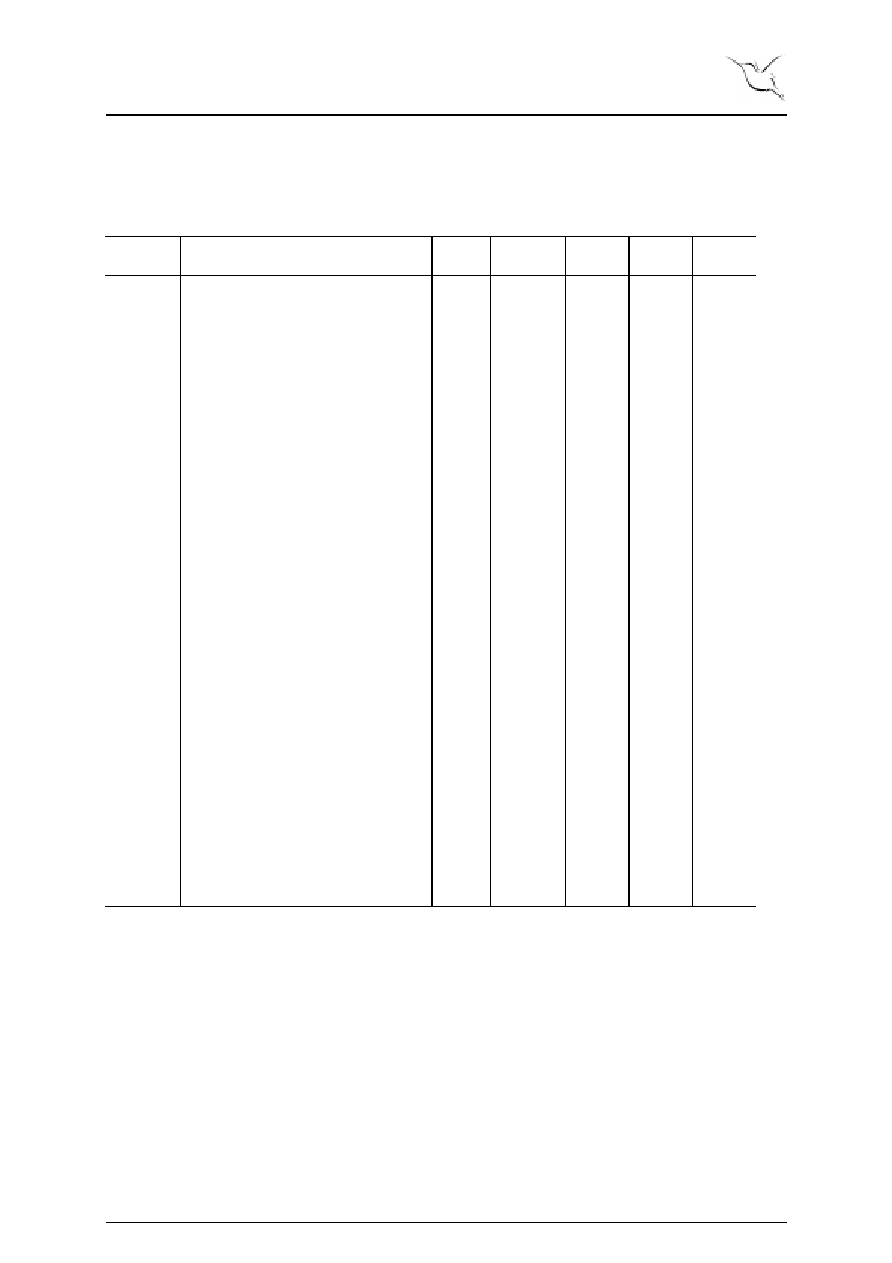

ELECTRICAL SPECIFICATIONS

DC SPECIFICATIONS

( At T

A

= 25 ∫C, V

AVDD

= V

VDD

= 1.8 V, F

CLK

= 110 MHz, F

IN

= 10 MHz, internal references, differential full-scale

input signal, 50 % duty cycle clock, and 10nF reference decoupling unless otherwise noted )

Symbol

Parameter (condition)

Test

level

Min.

Typ.

Max.

Unit

DC ACCURACY

N

Resolution

12

Bits

NMC

No Missing Codes Guaranteed

12

Bits

MON

Monotonicity Guaranteed

12

Bits

INL

Integral Non Linearity

±

1.5

LSB

DNL

Differential Non Linearity

±

0.5

LSB

G

Gain Error

±

1.0

% FSR

V

OS

Offset Error

±

1.0

% FSR

ANALOG INPUT

V

FSR

Input Differential Voltage Range

±

0.75

V

V

VCM,EXT

Input Common Mode Voltage

0.8

0.9

1.0

V

Input Impedance

2.2

pF

AIBW

Analog Input Bandwidth

600

MHz

REFERENCE VOLTAGES

V

REFP

Internal Positive Voltage Reference

1.275

V

V

REFN

Internal Negative Voltage Reference

0.525

V

V

RR

Internal Reference Range

0.75

V

FSR

Internal Differential Full-scale Range

1.5

V p-p

V

VCM

Internal Reference Common Mode Voltage

0.9

V

Internal Voltage Reference Drift

100

ppm /

∞

C

V

RR,EXT

External Reference Range

0.5

0.75

V

FSR

EXT

External Differential Full Scale Range

1

1.5

V p-p

V

RCM,EXT

External Reference Common Mode Voltage

0.8

0.9

1.0

V

POWER SUPPLY

V

AVDD

Positive Analog Supply Voltage

1.6

1.8

2.0

V

V

VDD

Positive Digital Supply Voltage

1.6

1.8

2.0

V

V

SS

Negative Supply Voltage

GND

I

DD

Supply Current, Active

58

mA

Supply Current, Standby

2.2

mA

Supply Current, Sleep

1.7

mA

Supply Current, Power down

2.2

µ

A

P

DD

Power Dissipation, Active

105

mW

Power Dissipation, Standby

4

mW

Power Dissipation, Sleep

3

mW

Power Dissipation, Power down

4

µ

W

OPERATING CONDITIONS

T

A

Junction Operating Temperature

-40

125

∞

C

Table 2. nAD12110-18a DC Specifications

PRELIMINARY PRODUCT SPECIFICATION

nAD12110-18a - 12-bit 110 MSPS Analog-to-Digital Converter IP

Nordic VLSI

Page 3 of 14

Revision: 1.0A

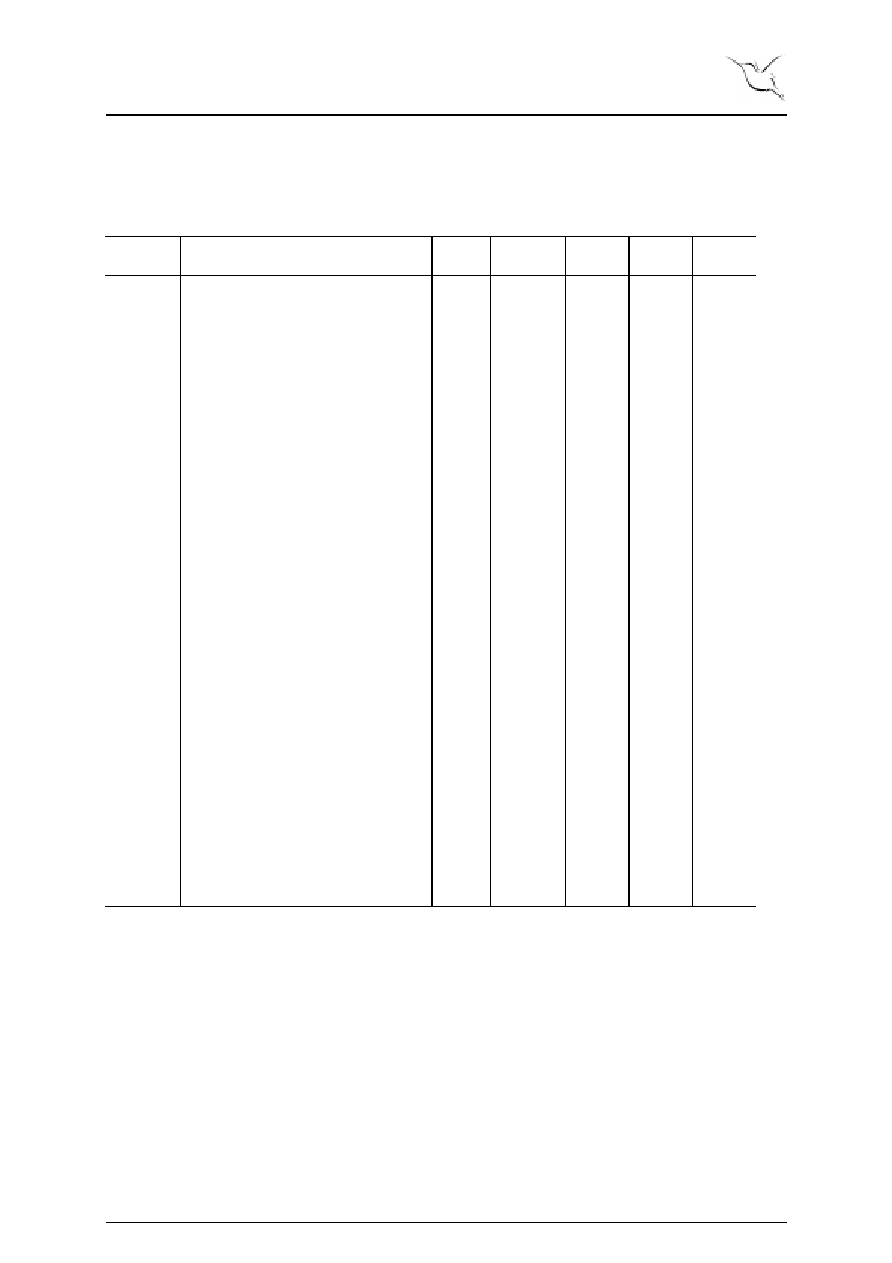

DYNAMIC SPECIFICATIONS

( At T

A

= 25 ∫C, V

AVDD

= V

VDD

= 1.8 V, F

CLK

= 110 MHz, F

IN

= 10 MHz, internal references, differential full-scale

input signal, 50 % duty cycle clock, and 10nF reference decoupling unless otherwise noted )

Symbol

Parameter (condition)

Test

level

Min.

Typ.

Max.

Unit

SWITCHING PERFORMANCE

F

CLK,MAX

Maximum Conversion Rate

110

MSPS

F

CLK,MIN

Minimum Conversion Rate

15

MSPS

Input Clock Duty Cycle

45

50

55

%

t

pd

Pipeline Delay ( Latency )

6

clocks

t

d

Output Data Delay Time

2

ns

t

h

Output Data Hold Time

1

ns

t

ad

Aperture Delay Time

0.9

ns

t

jitter

Aperture Uncertainty ( Jitter )

1.3

ps rms

t

standby

Start-up Time from Standby Mode

5

clocks

t

sleep

Start-up Time from Sleep Mode

0.5

µ

s

t

power down

Start-up Time from Power Down Mode

5

µ

s

t

out-of-range

Out-of-Range Recovery Time

SNR

SIGNAL-TO-NOISE RATIO

110 MSPS, F

IN

= 10 MHz

67

dBFS

110 MSPS, F

IN

= 40 MHz

65

dBFS

110 MSPS, F

IN

= 72 MHz

62

dBFS

SINDR

SIGNAL-TO-NOISE-AND DISTORTION

RATIO

110 MSPS, F

IN

= 10 MHz

64

dBFS

110 MSPS, F

IN

= 40 MHz

62

dBFS

110 MSPS, F

IN

= 72 MHz

59

dBFS

SFDR

SPURIOUS FREE DYNAMIC RANGE

110 MSPS, F

IN

= 10 MHz

70

dBc

110 MSPS, F

IN

= 40 MHz

63

dBc

110 MSPS, F

IN

= 72 MHz

50

ENOB

EFFECTIVE NUMBER OF BITS

110 MSPS, F

IN

= 5 MHz

10.3

bit

110 MSPS, F

IN

= 10 MHz

10.3

bit

110 MSPS, F

IN

= 40 MHz

9.8

bit

110 MSPS, F

IN

= 72 MHz

9.3

bit

Table 3. nAD12110-18a Dynamic Specifications

PRELIMINARY PRODUCT SPECIFICATION

nAD12110-18a - 12-bit 110 MSPS Analog-to-Digital Converter IP

Nordic VLSI

Page 4 of 14

Revision: 1.0A

DEFINITIONS OF SPECIFICATIONS

Integral Non Linearity ( INL )

The deviation of the ADC transfer function from

the ideal transfer function. The ideal transfer

function is defined as a straight line between the

end points of the transfer characteristic corrected

for gain and offset. INL for each code is calculated

at the code transitions.

Differential Non Linearity ( DNL )

In an ideal ADC every code transition to its

neighbours equals to 1 LSB. DNL is the deviation

of each code transition from the ideal value.

Gain Error

The deviation of the actual difference between the

first and last code transition and the ideal

difference.

Offset Error

Mid code ideally occurs for zero differential input.

The offset error is the differential input voltage that

gives mid code.

Analog Input Bandwidth

The analog input frequency for which the measured

input signal power has dropped by 3 dB.

Temperature Drift

The temperature drift specifies the maximum

change from the nominal junction temperature to

the minimum and maximum junction temperature.

Maximum Conversion Rate

The maximum conversion rate is the conversion

rate at which electrical specifications are tested.

Minimum Conversion Rate

The minimum conversion rate is the slowest

conversion rate where the ADC is functional.

Pipeline Delay ( Latency )

The pipeline delay is the time it takes from a

sample is taken at the input to the sample is

converted and put on the digital output.

Output Data Delay Time

Output data delay time is the time from the clock

edge that defines valid output data to all data

outputs have reached valid logical levels for the

next data sample.

Output Data Hold Time

Output data hold time is the time from the clock

edge that defines valid output data to the output

data is no longer valid.

Aperture Delay Time

The delay between the sampling clock edge and the

time when the input signal is held for conversion.

Aperture Uncertainty ( Jitter )

Aperture uncertainty or jitter is the variation of the

aperture delay time for successive samples.

Clock Duty Cycle

The fraction of the time the clock spends above the

logic threshold.

Start-up Time from Idle Mode

The time it takes to reach full performance after a

transition from an idle mode to active mode.

Out of Range Recovery Time

The time required for the ADC to return to

specified characteristics after an out-of-range

sample.

Signal-to-Noise Ratio ( SNR )

SNR is the rms ratio of the measured input signal

to the sum of all other spectral components

excluding the dc and the first eight harmonics.

Spurious-Free Dynamic Range ( SFDR )

SFDR is the amplitude difference between the

measured input signal and the highest harmonic

component.

Signal-to-Noise and Distortion Ratio ( SNDR )

SNDR is the rms ratio of the measured input signal

to the sum of all other spectral harmonics

excluding the dc component.

Effective Number of Bits ( ENOB )

Effective number of bits specifies the total rms

noise in terms of bits of resolution the ADC

effectively performs. Generally ENOB depends on

the amplitude and frequency of the input signal

used to test it. The ENOB can be calculated

directly from the SNDR as follows:

6.02

1.76

SNDR

ENOB

-

=

PRELIMINARY PRODUCT SPECIFICATION

nAD12110-18a - 12-bit 110 MSPS Analog-to-Digital Converter IP

Nordic VLSI

Page 5 of 14

Revision: 1.0A

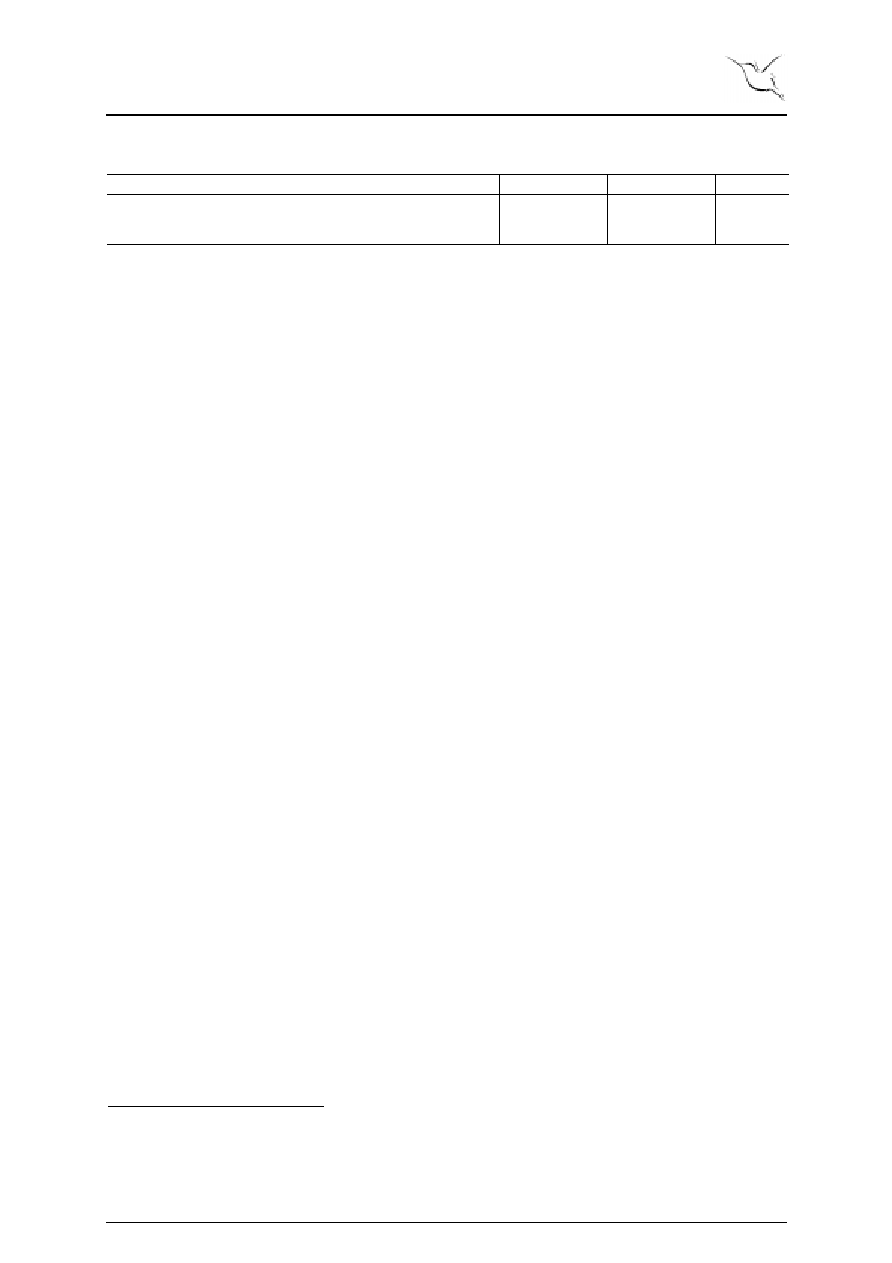

ABSOLUTE MAXIMUM RATINGS

1

Pin / Condition

Min

Max

Unit

All pins referred to AVSS pin

-0.2

2.2

V

Operating Junction Temperature

-40

125

∞

C

Storage Temperature

-65

125

∞

C

Table 4. Absolute maximum ratings

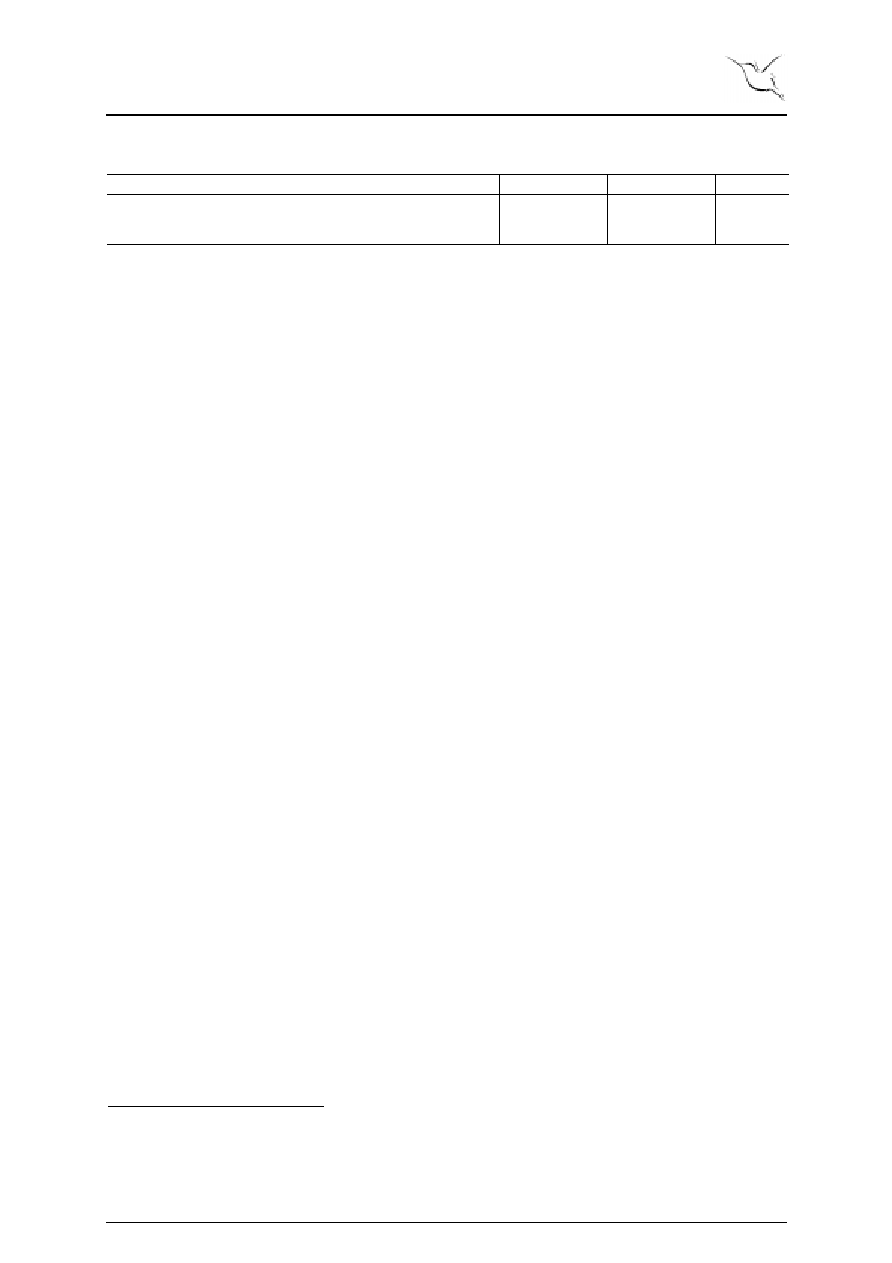

EXPLANATION OF TEST LEVELS

Test Level I:

100% production tested at +25∞C

Test Level II:

100% production tested at +25∞C and sample tested at specified temperatures

Test Level III:

Sample tested only

Test Level IV:

Parameter is guaranteed by design and characterization testing

Test Level V:

Parameter is typical value only

Test Level VI:

100% production tested at +25∞C. Guaranteed by design and characterization testing for

industrial temperature range

1

Stress above one or more of the limiting values may cause permanent damage to the device