PEDL60851C-02

1Semiconductor

This version: Dec. 1999

ML60851C

Preliminary

USB Device Controller

1/67

GENERAL DESCRIPTION

The ML60851C is a general purpose Universal Serial Bus (USB) device controller. The ML60851C provides a

USB interface, control/status block, application interface, and FIFOs. The FIFO interface and two types of

transfer have been optimized for BulkOut devices such as printers and BulkIn devices such as digital still cameras

and image scanners. In addition, Mass Storage devices are also applicable to this device.

FEATURES

∑

USB 1.0 compliant

∑

Built-in USB transceiver circuit

∑

Full-speed (12 Mb/sec) support

∑

Supports printer device class, image device class, and Mass Storage device class

∑

Supports three types of transfer; control transfer, bulk transfer, and interrupt transfer

∑

Built-in FIFOs for control transfer

Two 8-byte FIFOs (one for receive FIFO and the other for transmit FIFO)

∑

Built-in FIFOs for bulk transfer (available for either receive FIFO or transmit FIFO)

One 64-byte FIFO

Two 64-byte FIFOs

∑

Built-in FIFO for interrupt transfer

One 8-byte FIFO

∑

Supports one control endpoint, two bulk endpoint addresses, and one interrupt endpoint address

∑

Two 64-byte FIFOs enable fast BulkOut transfer and BulkIn transfer

∑

Supports 8 bit/16 bit DMA transfer

∑

V

CC

is 3.0 V to 3.6 V

∑

Supporting dual power supply enables 5 V application interface

∑

Built-in 48 MHz oscillator circuit

∑

Package options:

44-pin plastic QFP (QFP44-P-910-0.80-2K)

(Product name: ML60851CGA)

44-pin plastic TQFP (TQFP44-P-1010-0.80-K)

(Product name: ML60851CTB)

PEDL60851C-02

1Semiconductor

ML60851C

2/67

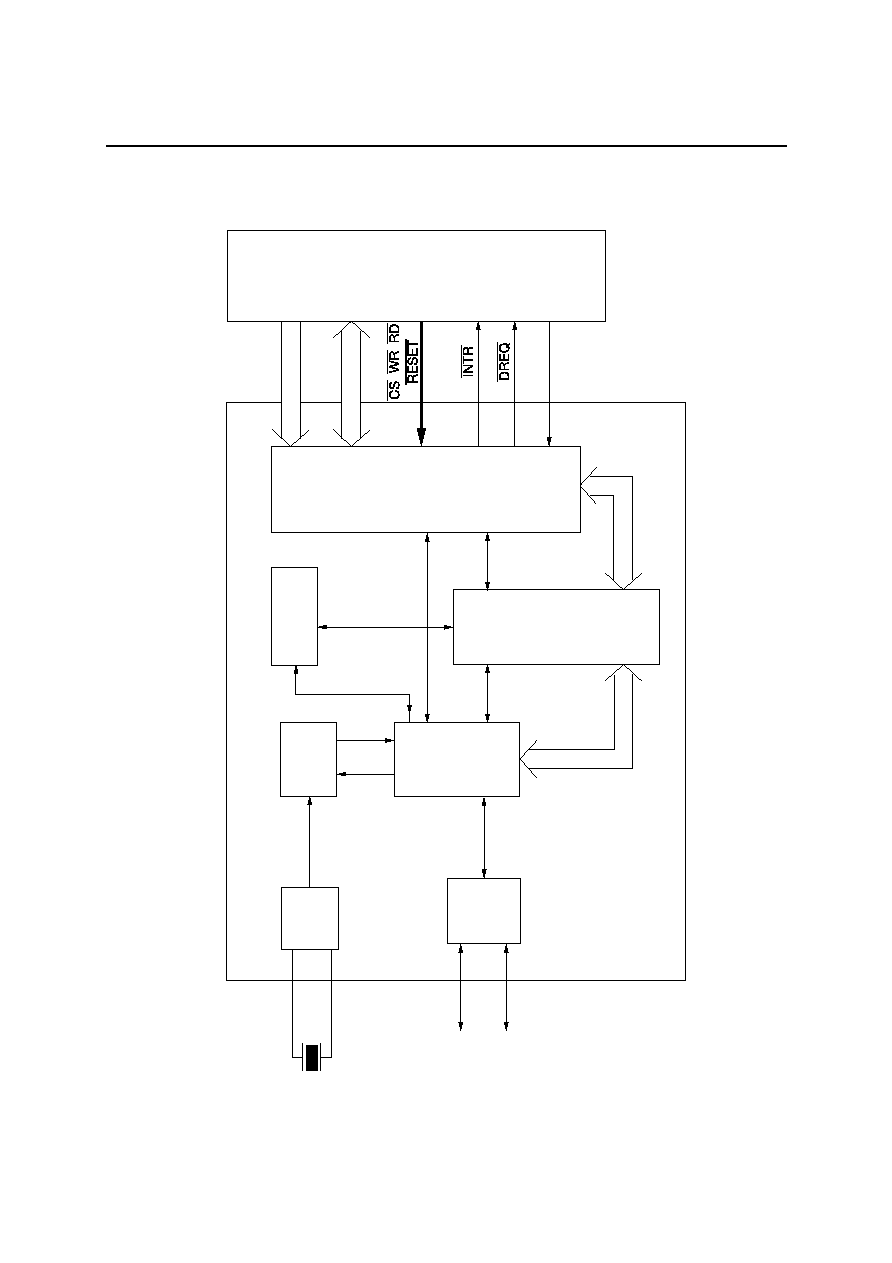

BLOCK DIAGRAM

48 MHz

XIN

XOUT

D+

D-

USB Bus

Oscillator

USB

Transceiver

DPLL

Protocol

Engine

Status/Control

Endpoint FIFO/

8-byte Setup Register

Application

Interface

Application

Module

(Local MCU)

A7:A0

D15:D0

,

,

DACK

ML60851C

PEDL60851C-02

1Semiconductor

ML60851C

3/67

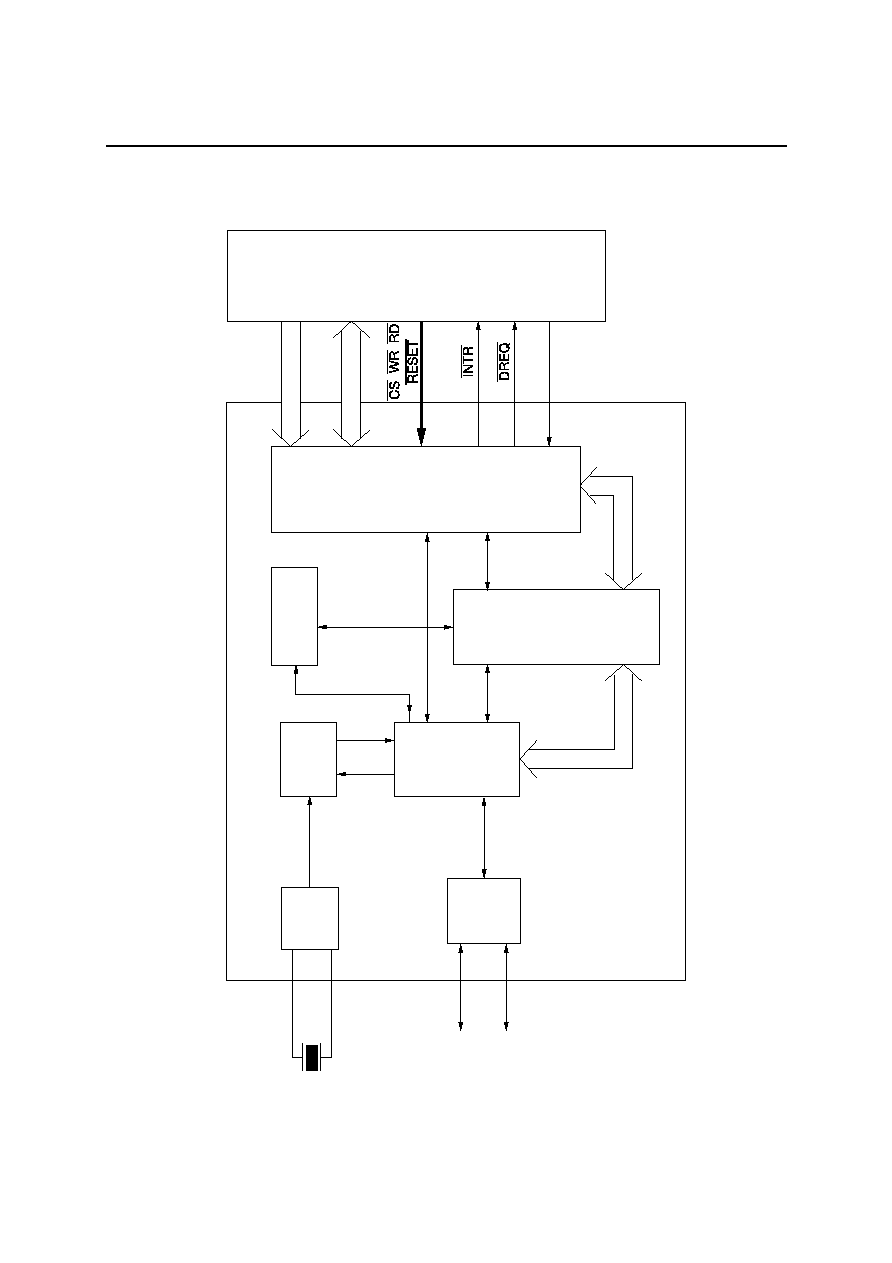

PIN CONFIGURATION (TOP VIEW)

1

2

3

4

5

6

7

8

9

10

11

23

24

25

26

27

28

29

30

31

32

33

;;

D+

D-

V

CC3

TEST1

TEST2

XIN

XOUT

CS

RD

WR

RESET

INTR

D15

D14

D13

D12

GND

V

CC5

D11

D10

D9

D8

ALE

ADSEL

A7

A6

A5

A4

A3

A2

A1

A0

DACK

DREQ

AD7

AD6

AD5

AD4

GND

V

CC5

AD3

AD2

AD1

AD0

44

43

42

41

40

39

38

37

36

35

34

12

13

14

15

16

17

18

19

20

21

22

44-Pin Plastic QFP

1

2

3

4

5

6

7

8

9

10

11

23

24

25

26

27

28

29

30

31

32

33

;

D+

D-

V

CC3

TEST1

TEST2

XIN

XOUT

CS

RD

WR

RESET

INTR

D15

D14

D13

D12

V

SS

V

CC5

D11

D10

D9

D8

ALE

ADSEL

A7

A6

A5

A4

A3

A2

A1

A0

DACK

DREQ

AD7

AD6

AD5

AD4

V

SS

V

CC5

AD3

AD2

AD1

AD0

44

43

42

41

40

39

38

37

36

35

34

12

13

14

15

16

17

18

19

20

21

22

44-Pin Plastic TQFP

PEDL60851C-02

1Semiconductor

ML60851C

4/67

PIN DESCRIPTION

Pin

Symbol

Type

Description

1,2

D+, D-

I/O

USB data

6, 7

XIN, XOUT

--

Pins for external crystal oscillator

4, 5

TEST14, 2

I

Test pins (normally "L")

13 to 16,

19 to 22

D15 to D18

I/O

Data bus (MSB)

35 to 38,

41 to 44

AD7 to AD0

I/O

Data bus (LSB)/address inputs

25 to 32

A7 to A0

I

Address inputs

8

CS

I

Chip select signal input pin. LOW active

9

RD

I

Read signal input pin. LOW active

10

WR

I

Write signal input pin. LOW active

12

INTR

O

Interrupt request signal output pin

34

DREQ

O

DMA request output pin

33

DACK

I

DMA acknowledge signal input pin

23

ALE

I

Address latch enable signal input pin

24

ADSEL

I

Address input mode select input pin. "H": address/data multiplex

11

RESET

I

System reset signal input pin. LOW active.

PEDL60851C-02

1Semiconductor

ML60851C

5/67

INTERNAL REGISTERS

Addresses and Names of Registers

Addresses

Register

Page

A5:A0

Read

A7, A6

Write

A7, A6

Symbol

Register name

00h

01b

--

EP0RXFIFO

Endpoint 0 Receive FIFO Data

7

01h

01b

--

EP1RXFIFO

Endpoint 1 Receive FIFO Data

7

02h

01b

--

EP2RXFIFO

Endpoint 2 Receive FIFO Data

8

03h

01b

--

Reserved

00h

--

11b

EP0TXFIFO

Endpoint 0 Transmit FIFO Data

9

01h

--

11b

EP1TXFIFO

Endpoint 1 Transmit FIFO Data

9

02h

--

11b

EP2TXFIFO

Endpoint 2 Transmit FIFO Data

10

03h

--

11b

EP3TXFIFO

Endpoint 3 Transmit FIFO Data

10

00h

11b

01b

DVCADR

Device Address Register

11

01h

11b

01b

DVCSTAT

Device Status Register

11

02h

11b

--

PKTERR

Packet Error Register

13

03h

11b

--

FIFOSTAT1

FIFO Status Register 1

13

04h

11b

--

FIFOSTAT2

FIFO Status Register 2

14

08h

11b

01b

PKTRDY

Endpoint Packet-Ready Register

15

09h

11b

--

EP0RXCNT

Endpoint 0 Receive-Byte Count Register

19

0Ah

11b

--

EP1RXCNT

Endpoint 1 Receive-Byte Count Register

19

0Bh

11b

--

EP2RXCNT

Endpoint 2 Receive-Byte Count Register

20

0Ch

11b

--

Reserved

0Dh

11b

--

REVISION

Revision Register

21

0Eh

--

01b

CLRFIFO

Transmit FIFO Clear Register

21

0Fh

--

01b

SYSCON

System Control Register

22

10h

11b

--

bmRequestType

bmRequestType Setup Register

23

11h

11b

--

bRequest

bRequest Setup Register

23

12h

11b

--

wValueLSB

wValueLSB Setup Register

24

13h

11b

--

wValueMSB

wValueMSB Setup Register

24

14h

11b

--

wIndexLSB

wIndexLSB Setup Register

24

15h

11b

--

wIndexMSB

wIndexMSB Setup Register

24

16h

11b

--

wLengthLSB

wLengthLSB Setup Register

25

17h

11b

--

wLengthMSB

wLengthMSB Setup Register

25

1Ah

11b

01b

POLSEL

Assertion Select Register

26

1Bh

11b

01b

INTENBL

Interrupt Enable Register

27

1Ch

11b

--

INTSTAT

Interrupt Status Register

28

1Dh

11b

01b

DMACON

DMA Control Register

30

1Eh

11b

01b

DMAINTVL

DMA Interval Register

31

1Fh

--

--

Reserved