OKI Semiconductor

FEDL7074-003DIGEST-01

Issue Date: Oct. 27, 2003

ML7074-003 GA

VoIP CODEC

1/31

GENERAL DESCRIPTION

The ML7074-003GA is a speech CODEC for VoIP. This LSI allows selection of G.729.A, G.726, or G.711

standard as a speech CODEC. The LSI is optimum for adding VoIP functions to TAs, routers, etc., since it has the

functions of an echo canceller for 32 msec delay, DTMF detection, tone detection, tone generation, etc.

FEATURES

� Single 3.3 V power supply operation (DV

DD

0, 1, 2, AV

DD

: 3.0 to 3.6 V)

� Speech CODEC:

Selectable among G.729.A (8 kbps), G726 (32 kbps), G.711 (64 kbps)

�-law, and A-law

Mutual conversion function between G.729.A (8 kbps) and G.726 (32 kbps).

� Echo canceller for 32 ms delay

� DTMF detect function

� Tone detect function: 2 systems (1650 Hz, 2100 Hz: Detect frequency can be changed.)

� Tone generate function

� FSK generate function

� Dial pulse detect function

� Dial pulse transmit function

� Internal 1-channel 16-bit timer

� Built-in FIFO buffers (640 bytes) for transferring transmit and receive data

Frame/DMA (slave) interface selectable.

� Master clock frequency: 4.096 MHz (crystal oscillation or external input)

� Hardware or software power down operation possible.

� Analog input/output type:

Two built-in input amplifiers, 10 M

driving

Two built-in output amplifiers, 10 k

driving

� Package:

64-pin plastic QFP (QFP64-P-1414-0.80-BK)

� Ordering part number:

ML7074-003GA

FEDL7074-003FULL-01

OKI Semiconductor

ML7074-003 GA

4/31

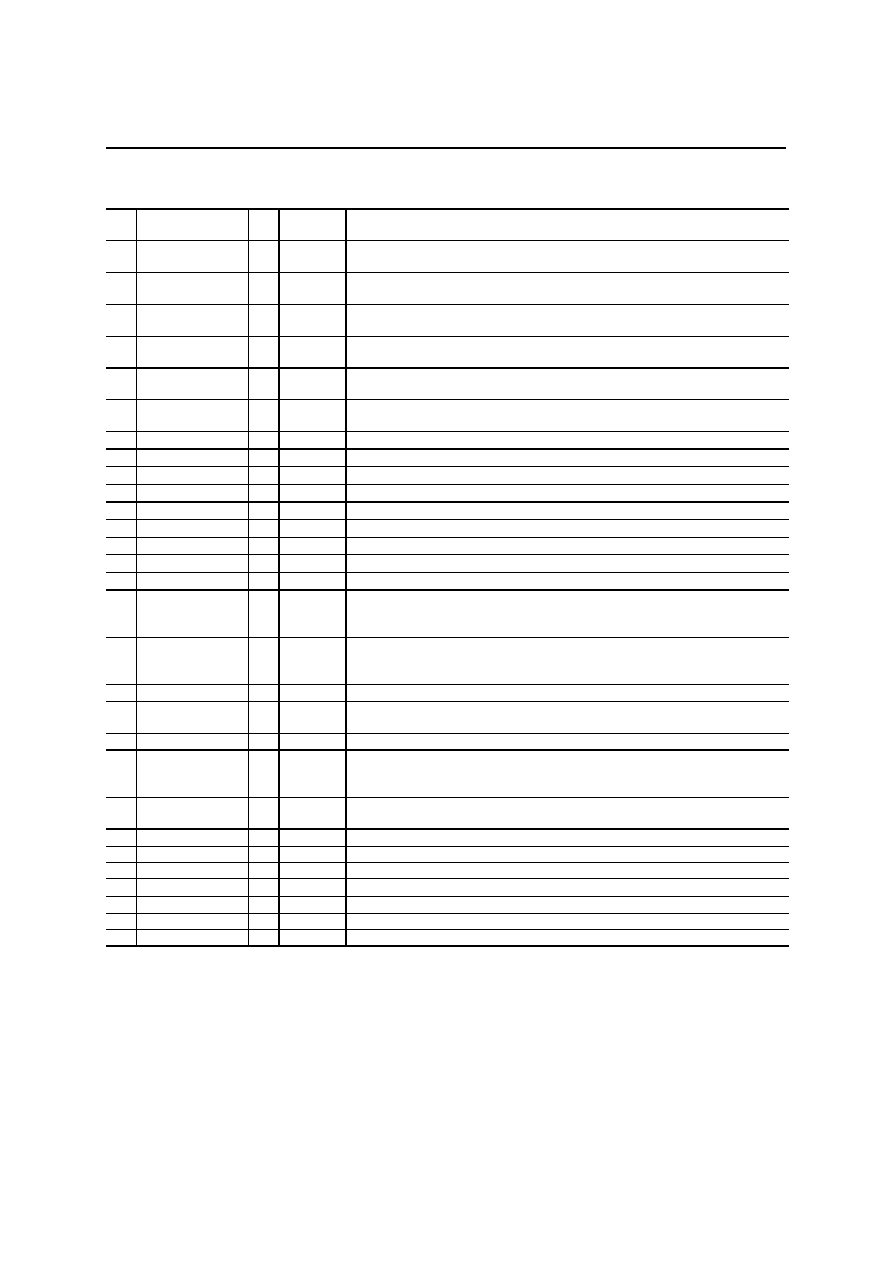

PIN DESCRIPTIONS

Pin

No.

Symbol

I/O PDNB = "0"

Description

1

TST1

I

"0"

Test control input 1: Normally input "0".

2

TST0

I

"0"

Test control input 0: Normally input "0".

3

PCMO

O

"Hi-z"

PCM data output

4

PCMI

I

I

PCM data input

I

CLKSEL = "0"

PCM shift clock input

5 BCLK I/O

"L"

CLKSEL = "1"

PCM shift clock output

I

CLKSEL = "0"

PCM sync signal 8 kHz input

6 SYNC I/O

"L"

CLKSEL = "1"

PCM sync signal 8 kHz output

7 DV

DD

0

Digital power supply

8

ACK0B

I

I

Transmit buffer DMA access acknowledge signal input

9

ACK1B

I

I

Receive buffer DMA access acknowledge signal input

10

FR0B

(DMARQ0B)

O "H"

FR0B: (CR11-B7 = "0")

Transmit buffer frame signal output

DMARQ0B: (CR11-B7 = "1")

Transmit buffer DMA access request signal output

11

FR1B

(DMARQ1B)

O "H"

FR1B: (CR11-B7 = "0")

Receive buffer frame signal output

DMARQ1B: (CR11-B7 = "1")

Receive buffer DMA access request signal output

12 INTB O

"H"

Interrupt request output

"L" level is output for about 1.0

�

sec when an interrupt is generated.

13

CSB

I

I

Chip select control input

14

RDB

I

I

Read control input

15

WRB

I

I

Write control input

16

DGND0

I

Digital ground (0.0 V)

17 D0 I/O

I

Data

input/output

18 D1 I/O

I

Data

input/output

19 D2 I/O

I

Data

input/output

20 D3 I/O

I

Data

input/output

21 D4 I/O

I

Data

input/output

22 D5 I/O

I

Data

input/output

23 D6 I/O

I

Data

input/output

24 D7 I/O

I

Data

input/output

25 D8 I/O

I

Data input/output

Fix to input state when using in 8-bit bus access (CR11-B5 = "1").

FEDL7074-003FULL-01

OKI Semiconductor

ML7074-003 GA

5/31

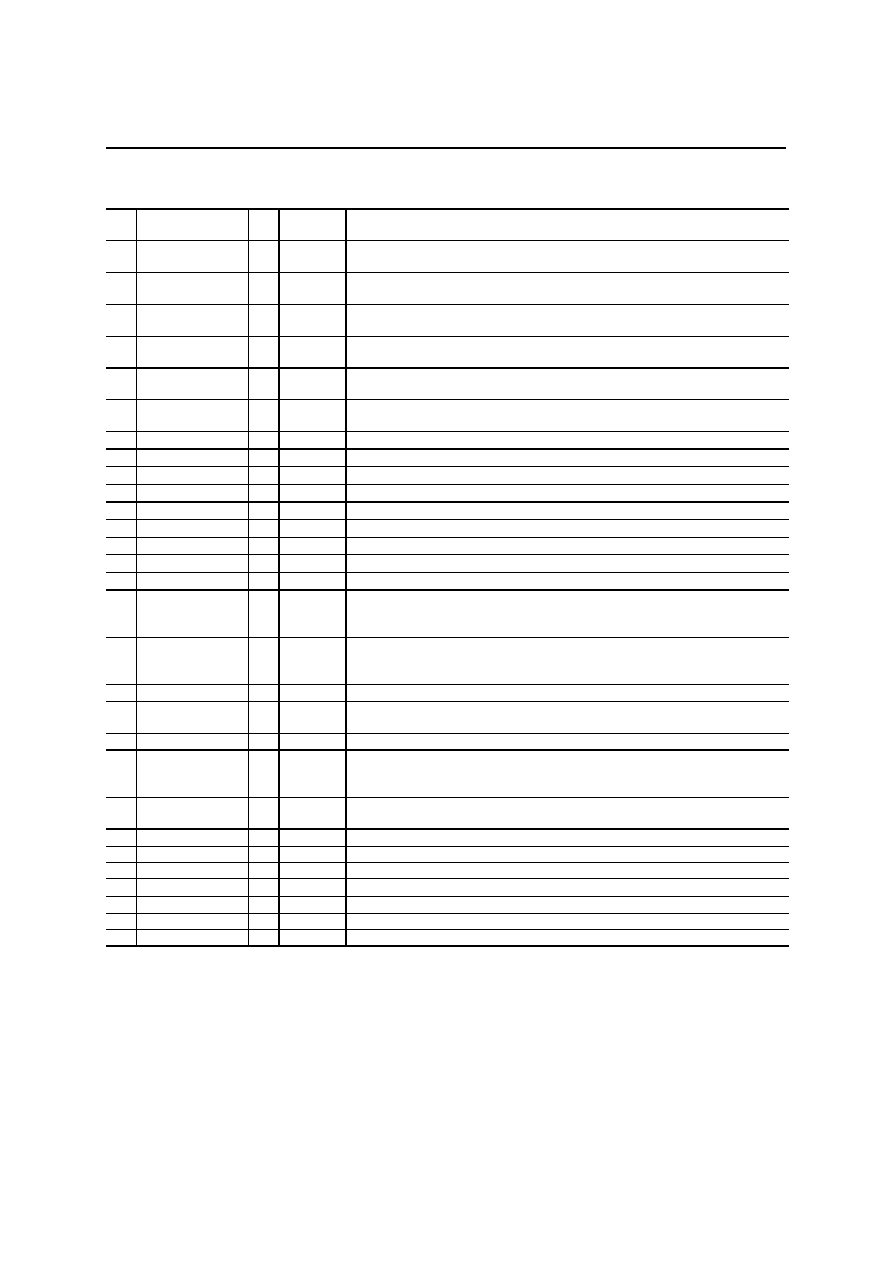

26 D9 I/O

I

Data input/output

Fix to input state when using in 8-bit bus access (CR11-B5 = "1").

27 D10 I/O

I

Data input/output

Fix to input state when using in 8-bit bus access (CR11-B5 = "1").

28 D11 I/O

I

Data input/output

Fix to input state when using in 8-bit bus access (CR11-B5 = "1").

29 D12 I/O

I

Data input/output

Fix to input state when using in 8-bit bus access (CR11-B5 = "1").

30 D13 I/O

I

Data input/output

Fix to input state when using in 8-bit bus access (CR11-B5 = "1").

31 D14 I/O

I

Data input/output

Fix to input state when using in 8-bit bus access (CR11-B5 = "1").

32 D15 I/O

I

Data input/output

Fix to input state when using in 8-bit bus access (CR11-B5 = "1").

33 DV

DD

1

Digital power supply

34 A0 I

I

Address

input

35 A1 I

I

Address

input

36 A2 I

I

Address

input

37 A3 I

I

Address

input

38 A4 I

I

Address

input

39 A5 I

I

Address

input

40 A6 I

I

Address

input

41 A7 I

I

Address

input

42 PDNB I "0"

Power down input

"0": Power down reset

"1": Normal operation

43 CLKSEL I I

SYNC and BCLK I/O control input

"0": SYNC and BCLK become inputs

"1": SYNC and BCLK become outputs

44 DGND1

Digital ground (0.0 V)

45 GPI0 I I

General-purpose input pin 0 (5 V tolerant input)

/Secondary function: Dial pulse detect input pin

46 GPI1 I I

General-purpose

input pin 1 (5 V tolerant input)

47 GPO0 O

"L"

General-purpose output pin 0 (5 V tolerant output, can be pulled up

externally)

/Secondary function: Dial pulse transmit pin

48 GPO1 O

"L"

General-purpose output pin 1 (5 V tolerant output, can be pulled up

externally)

49 AV

DD

Analog power supply

50

AIN0P

I

I

AMP0 non-inverted input

51

AIN0N

I

I

AMP0 inverted input

52 GSX0 O

"Hi-z"

AMP0 output (10 k

driving)

53 GSX1 O

"Hi-z"

AMP1 output (10 k

driving)

54

AIN1N

I

I

AMP1 inverted input

55

AVREF

O

"L"

Analog signal ground (1.4 V)