| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: MSM63238 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

° Semiconductor

MSM63238

1/32

GENERAL DESCRIPTION

The MSM63238 is a CMOS 4-bit microcontroller with a built-in POCSAG (Post Office Code

Standardization Advisory Group) decoder.

The MSM63238 employs Oki's original nX-4/250 CPU core and is suitable for pager applications.

The MSM63P238 is a one-time-programmable ROM-version product having one-time PROM

(OTP) as internal program memory.

The specifications of the MSM63P238 are equal to those of the MSM63238 except for electrical

characteristics, packaging (only 80-pin flat package is available for the MSM63P238), and some

functions.

FEATURES

∑ Rich instruction set

439 instructions

Transfer, rotate, increment/decrement, arithmetic operations, comparison, logic operations,

mask operations, bit operations, ROM table reference, external memory transfer, stack

operations, flag operations, branch, conditional branch, call/return, control.

∑ Rich selection of addressing modes

Indirect addressing of four data memory types, with current bank register, extra bank

register, HL register and XY register.

Data memory bank internal direct addressing mode.

∑ Processing speed

Two clocks per machine cycle, with most instructions executed in one machine cycle.

Minimum instruction execution time

: 61 ms (@ 32.768 kHz system clock)

1 ms (@ 2 MHz system clock)

∑ Clock generation circuit

Low-speed clock

: 32.768 kHz/38.4 kHz/76.8 kHz crystal oscillator

High-speed clock

: 2 MHz (Max.) RC or ceramic oscillator select

∑ Program memory space

16K words

Basic instruction length is 16 bits/1 word

∑ Data memory space

1K nibbles

∑ External data memory space

64 Kbytes (expandable by using an I/O port)

° Semiconductor

MSM63238

4-Bit Microcontroller with Built-in POCSAG Decoder and Melody Circuit, Operating at

0.9 V (Min.)

E2E0027-38-95

This version: Sep. 1998

Previous version: Mar. 1996

° Semiconductor

MSM63238

2/32

∑ Stack level

Call stack level

: 16 levels

Register stack level

: 16 levels

∑ POCSAG decoder

Data rate

: 512 bps/1200 bps/2400 bps

User frame

: 3 types

User address

: 6 types

Battery saving mode (for controlling intermittent operations of RF receiver)

∑ I/O ports

Input ports: Selectable as input with pull-up resistance/input with pull-down resistance/

high-impedance input

Output ports: Selectable as P-channel open drain output/N-channel open drain output/

CMOS output/high-impedance output

Input-output ports: Selectable as input with pull-up resistance/input with pull-down

resistance/high-impedance input

Selectable as P-channel open drain output/N-channel open drain

output/CMOS output/high-impedance output

Can be interfaced with external peripherals that use a different power supply than this device

uses.

Number of ports:

Input port

: 1 port • 4 bits

Output port

: 6 ports • 4 bits

Input-output port

: 5 ports • 4 bits

1 port • 2 bits

∑ Melody output function

Melody sound frequency

: 529 to 2979 Hz

Tone length

: 63 types

Tempo

: 15 types

Note data

: Resides in the program memory

Buzzer drive signal output

: 4 kHz

∑ Reset function

Reset through RESET pin

Power-on reset

Reset by low-speed oscillation halt

∑ Battery check

Low-voltage supply check

Criterion voltage

: Can be selected as 1.05

±

0.10 V, 1.30

±

0.15 V,

2.20

±

0.20 V or 2.80

±

0.30 V

∑ Power supply backup

Backup circuit (voltage multiplier) enables operation at 0.9 V minimum

° Semiconductor

MSM63238

3/32

∑ Timers and counter

8-bit timer • 4

Selectable as auto-reload mode/capture mode/clock frequency measurement mode

Watchdog timer • 1

15-bit time base counter • 1

1, 2, 4, 8, 16, 32, 64, and 128 Hz signals can be read

∑ Serial port

Mode

: UART mode, synchronous mode

UART communication speed

: 1200 bps, 2400 bps, 4800 bps, 9600 bps

Clock frequency in synchronous mode

: 32.768 kHz (internal clock mode), external

clock frequency

Data length

: 5 to 8 bits

∑ Interrupt sources

External interrupt

: 3

Internal interrupt

: 15 (watchdog timer interrupt is a nonmask-

able interrupt)

∑ Operating voltage

When backup used

: 0.9 to 2.7 V

(Low-speed clock operating)

1.2 to 2.7 V

(Operating frequency: 300 to 500 kHz)

1.5 to 2.7 V

(Operating frequency: 200 kHz to 1 MHz)

When backup not used

: 1.8 to 5.5 V

(Operating frequency: 300 to 500 kHz)

2.2 to 5.5 V

(Operating frequency: 300 kHz to 1 MHz)

2.7 to 5.5 V

(Operating frequency: 200 kHz to 2 MHz)

∑ Package options:

80-pin plastic QFP (QFP80-P-1420-0.80-BK)

: (Product name: MSM63238-xxxGS-BK)

100-pin plastic TQFP (TQFP100-P-1414-0.50-K) : (Product name: MSM63238-xxxTS-K)

Chip

: MSM63238-xxx

xxx indicates a code number.

° Semiconductor

MSM63238

4/32

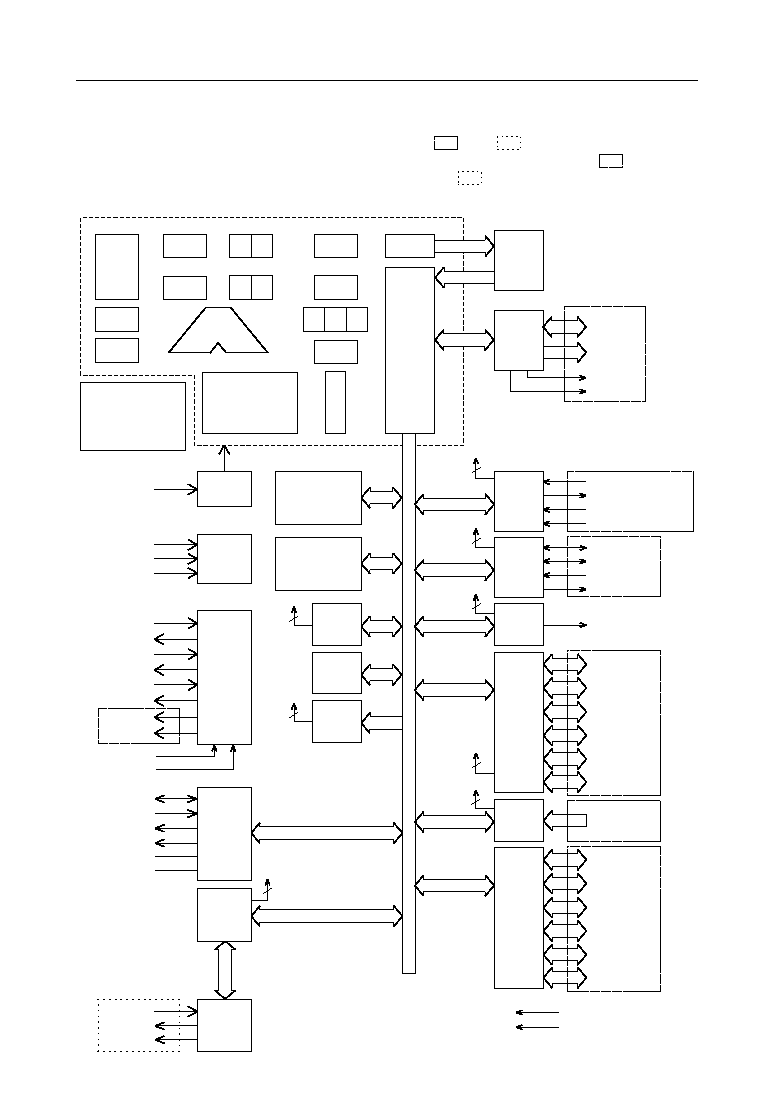

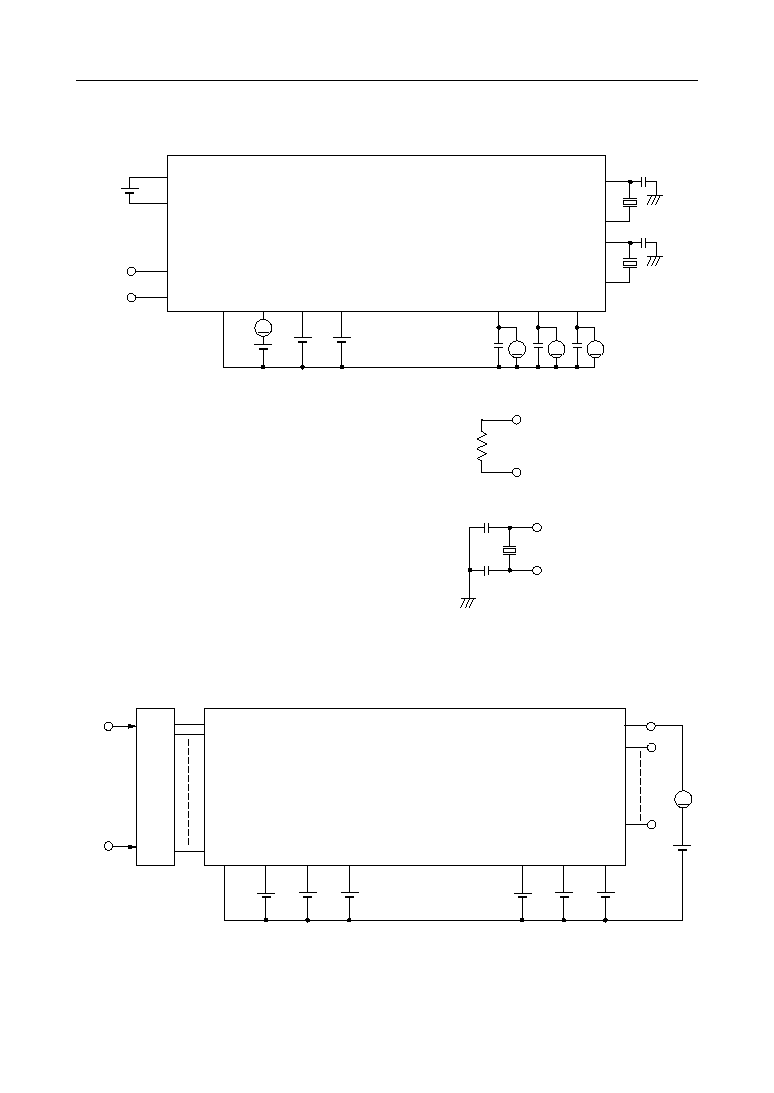

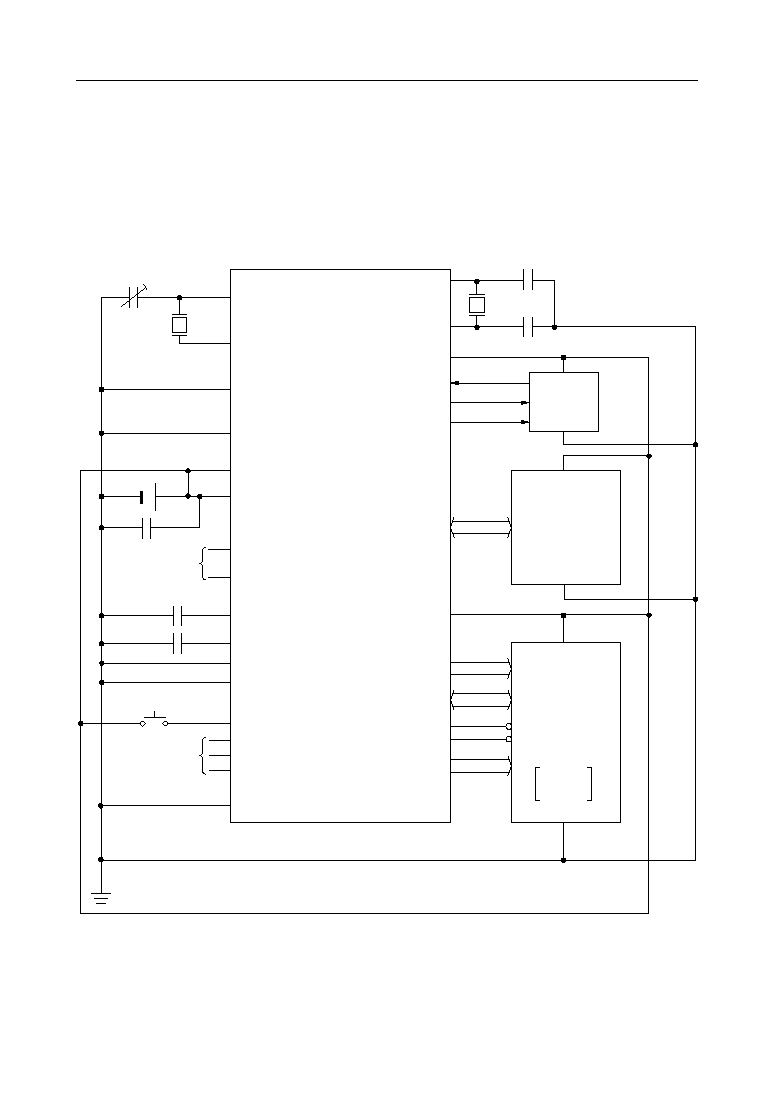

BLOCK DIAGRAM

An asterisk (*) indicates the port secondary function. and indicate that the power is

supplied from V

DDI

to the circuits corresponding to the signal names inside , and from

V

DDR

to the circuits corresponding to signal names inside . (V

DDI

and V

DDR

: power supply

for interface)

ROM

16KW

EXTMEM

BUS

CON-

TROL

MIE

XTM0

XTM1

XT0

XT1

OSC0

OSC1

TBCCLK

*

HSCLK

*

RESET

OSC

CBR

EBR

L

C G

Z

ALU

RA

A

IR

INSTRUCTION

DECODER

RAM

1024N

D0-7

*

A0-15

*

RD

*

WR

*

nX-4/250

MELODY

MD

I/O

PORT

P8.0, P8.1

P9.0-P9.3

PA.0-PA.3

PB.0-PB.3

PC.0-PC.3

PD.0-PD.3

RST

TST1

TST

TST2

V

DDI

3

INT

PC

H

Y

X

TIMING

CON-

TROL

SP

RSP

STACK

CAL.S: 16-level

REG.S: 16-level

INT

TIMER

8bit • 4

RXC

*

TXC*

RXD

*

TXD

*

4

INT

SIO

TM0CAP/TM1CAP

*

TM0OVF/TM1OVF

*

T02CK

*

T13CK

*

2

INT

1

INT

TST3

XTSEL0

XTSEL1

V

DDH

V

DD

V

DDL

V

DD2

CB1

CB2

BACKUP

P0.0-P0.3

P8.2, P8.3

PE.0-PE.3

PF.0-PF.3

Internal

PORT

POCSAG

Dec

INPUT

PORT

P1.0-P1.3

P7.0-P7.3

P6.0-P6.3

P5.0-P5.3

P4.0-P4.3

P3.0-P3.3

P2.0-P2.3

1

INT

OUTPUT

PORT

DATA BUS

TBC

4

INT

BLD

WDT

1

INT

3

INT

SIGIN

BS1

BS2

V

DDR

° Semiconductor

MSM63238

5/32

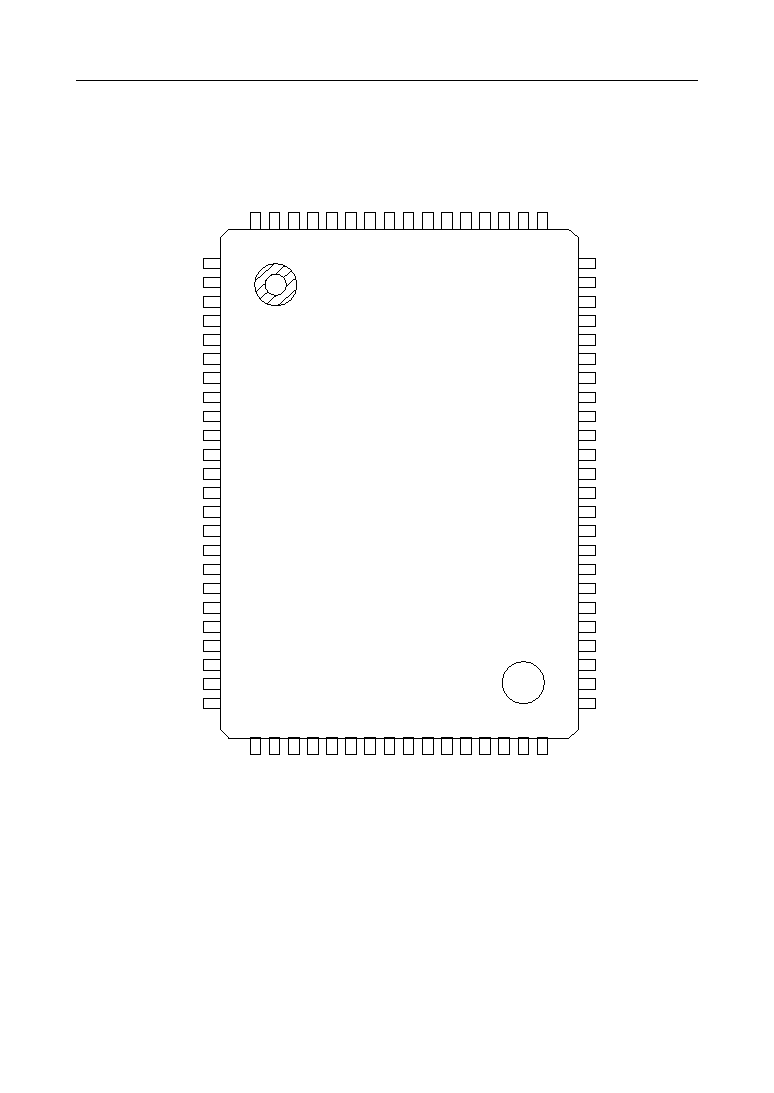

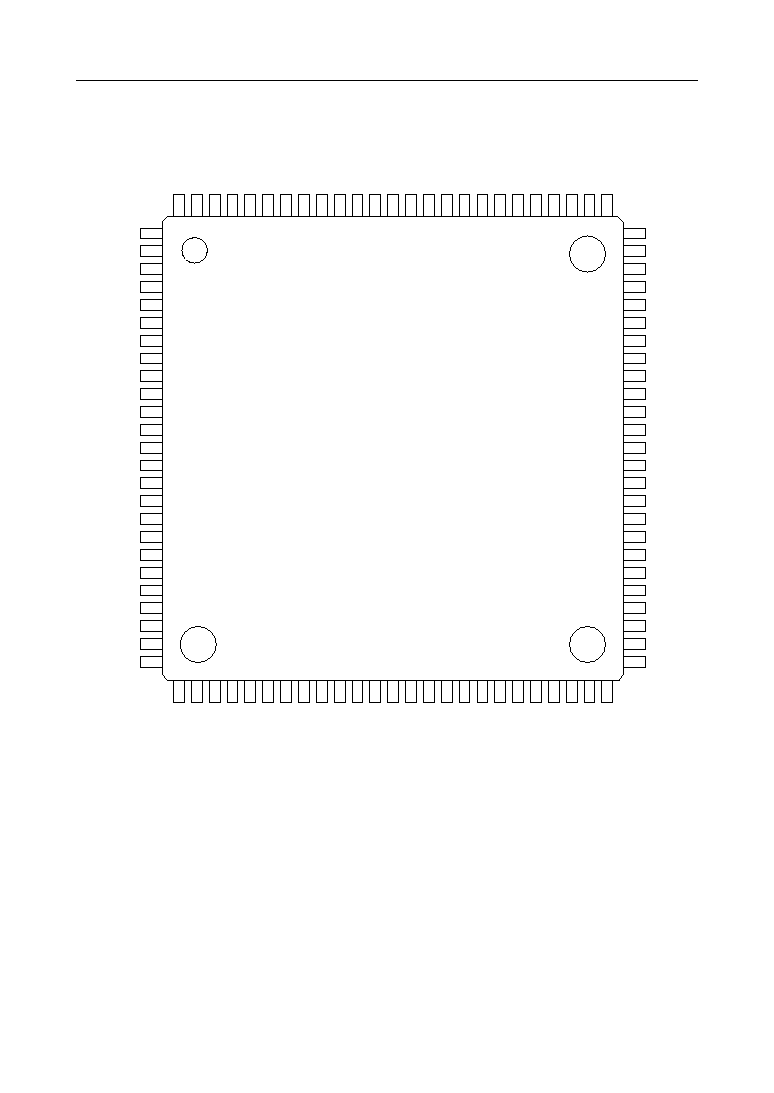

PIN CONFIGURATION (TOP VIEW)

80-Pin Plastic QFP

Note: Pins marked as (NC) are no-connection pins which are left open.

(NC)

41

PC.0

42

PC.1

43

PC.2

44

PC.3

45

PB.0

46

PB.1

47

PB.2

48

PB.3

49

P1.0

50

P1.1

51

P1.2

52

P1.3

53

P2.0

54

P2.1

55

P2.2

56

P2.3

57

P3.0

58

P3.1

59

P3.2

60

P3.3

61

P8.0

62

(NC)

63

P8.1

64

PD.3

40

PD.2

39

PD.1

38

PD.0

37

V

DDI

36

(NC)

35

RESET

34

MD

33

V

SS

32

V

DD

31

CB2

30

CB1

29

V

DDH

28

V

DDL

27

V

DD2

26

(NC)

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

XTM1

XTM0

XTSEL1

XTSEL0

OSC1

OSC0

TST3

TST2

TST1

XT1

XT0

V

DDR

SIGIN

BS2

BS1

P7.3

P7.2

P7.1

P7.0

P6.3

P6.2

P6.1

P6.0

(NC)

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

P9.0

P9.1

P9.2

P9.3

PA.0

PA.1

PA.2

PA.3

P4.0

P4.1

P4.2

P4.3

P5.0

P5.1

P5.2

P5.3

° Semiconductor

MSM63238

6/32

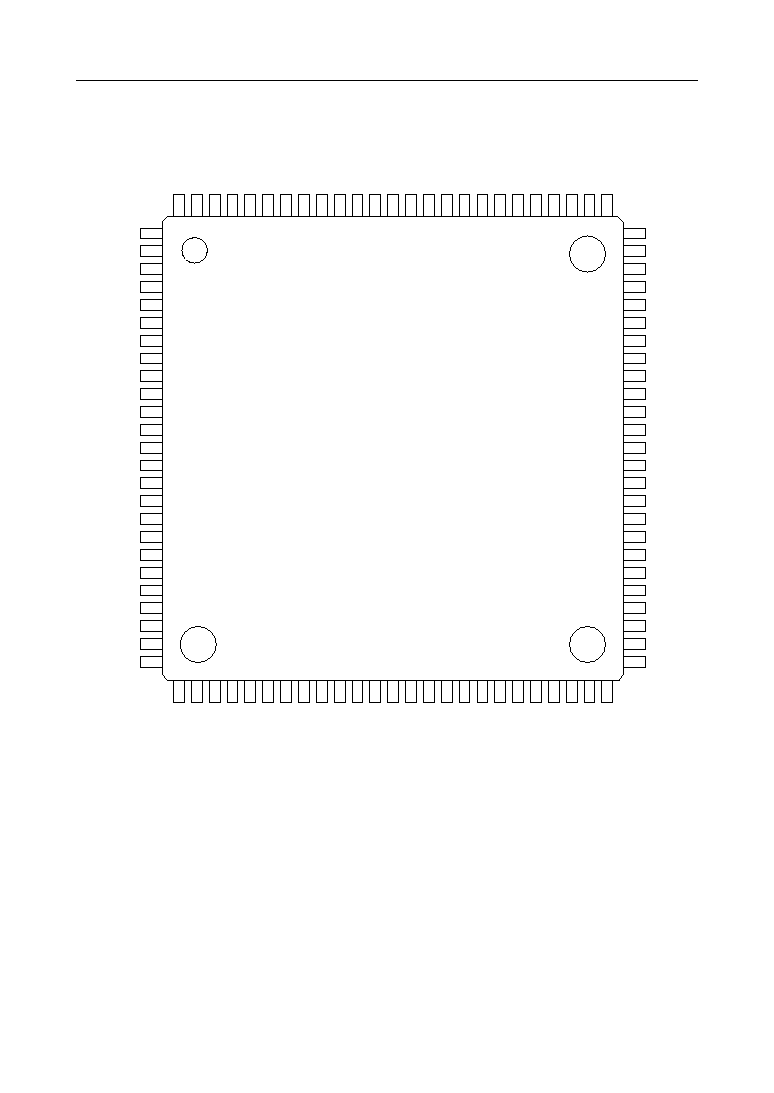

100

99

98

97

96

95

94

93

92

91

90

(NC)

P6.0

(NC)

P5.3

(NC)

P5.2

P5.1

P5.0

P4.3

P4.2

P4.1

75

74

73

72

71

70

69

68

67

66

65

P8.0

P3.3

P3.2

P3.1

(NC)

P3.0

P2.3

P2.2

P2.1

(NC)

P2.0

1

2

3

4

5

6

7

8

9

10

11

P6.1

P6.2

P6.3

P7.0

P7.1

(NC)

P7.2

P7.3

(NC)

BS1

BS2

89

P4.0

88

(NC)

87

PA.3

86

PA.2

85

PA.1

12

SIGIN

13

(NC)

14

V

DDR

15

XT0

16

XT1

64 P1.3

63 (NC)

62 P1.2

61 P1.1

60 (NC)

84

PA.0

83

(NC)

82

P9.3

81

P9.2

26

27

28

29

30

31

32

33

34

35

36

(NC)

XTM0

XTM1

(NC)

(NC)

V

DD2

V

DDL

V

DDH

CB1

CB2

V

DD

37

V

SS

38

MD

39

RESET

40

(NC)

41

(NC)

42

V

DDI

43

PD.0

44

PD.1

45

PD.2

17

(NC)

18

TST1

19

TST2

20

TST3

59 P1.0

58 PB.3

57 PB.2

56 PB.1

80

P9.1

79

P9.0

78

(NC)

77

P8.1

76

(NC)

46

PD.3

47

(NC)

48

PC.0

49

(NC)

50

(NC)

21

OSC0

55 (NC)

22

OSC1

23

XTSEL0

24

XTSEL1

25

(NC)

54 PB.0

53 PC.3

52 PC.2

51 PC.1

,

100-Pin Plastic TQFP

Note: Pins marked as (NC) are no-connection pins which are left open.

PIN CONFIGURATION (TOP VIEW) (continued)

° Semiconductor

MSM63238

7/32

PC.2

39

PC.3

40

PB.0

41

PB.1

42

PB.2

43

PB.3

44

P1.0

45

P1.1

46

P1.2

47

P1.3

48

P2.0

49

P2.1

50

P2.2

51

P2.3

52

P3.0

53

P3.1

54

P3.2

55

P3.3

56

P8.0

57

P8.1

58

P9.0

59

P9.1

60

P9.2

61

P9.3

62

PA.0

63

PA.1

64

PA.2

65

PA.3

66

P4.0

67

P4.1

68

P4.2

69

P4.3

70

P5.0

71

P5.1

72

P5.2

73

P5.3

74

P6.0

75

P6.1

1

P6.2

2

P6.3

3

P7.0

4

P7.1

5

P7.2

6

P7.3

7

BS1

8

BS2

9

SIGIN

10

V

DDR

11

XT0

12

XT1

13

TST1

14

TST2

15

TST3

16

OSC0

17

OSC1

18

XTSEL0

19

PC.1

38

PC.0

37

PD.3

36

PD.2

35

PD.1

34

PD.0

33

V

DDI

32

RESET

31

MD

30

V

SS

29

V

DD

28

CB2

27

CB1

26

V

DDH

25

V

DDL

24

V

DD2

23

XTM1

22

XTM0

21

XTSEL1

20

Y

X

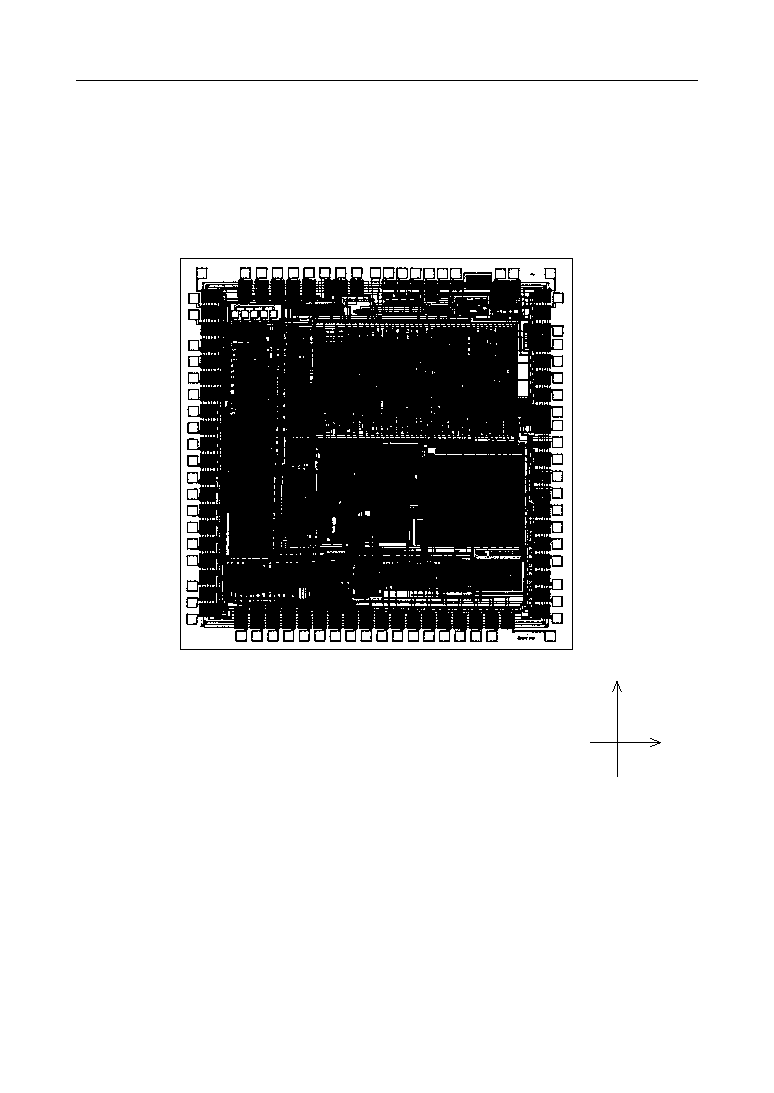

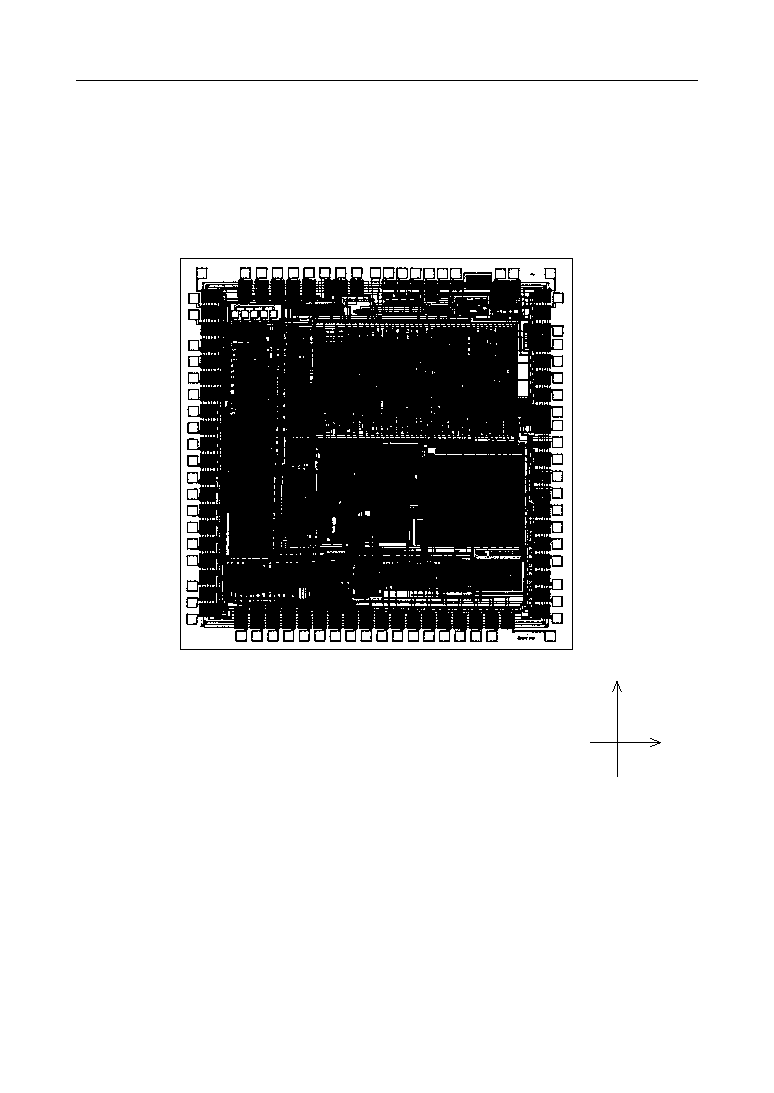

PAD CONFIGURATION

Pad Layout

Chip Size

: 4.55 mm • 4.55 mm

Chip Thickness

: 350 mm (typ.)

Coordinate Origin

: Chip center

Pad Hole Size

: 110 mm • 110 mm

Pad Size

: 120 mm • 120 mm

Minimum Pad Pitch

: 150 mm

Note: The chip substrate voltage is V

SS

.

° Semiconductor

MSM63238

8/32

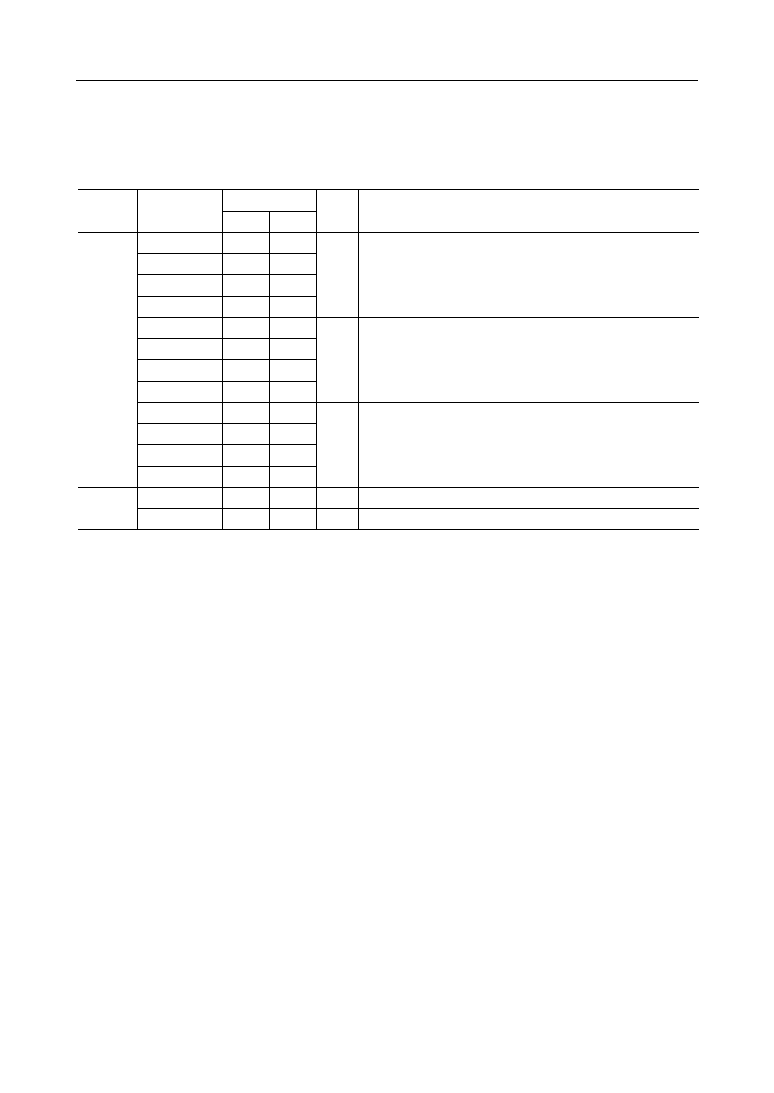

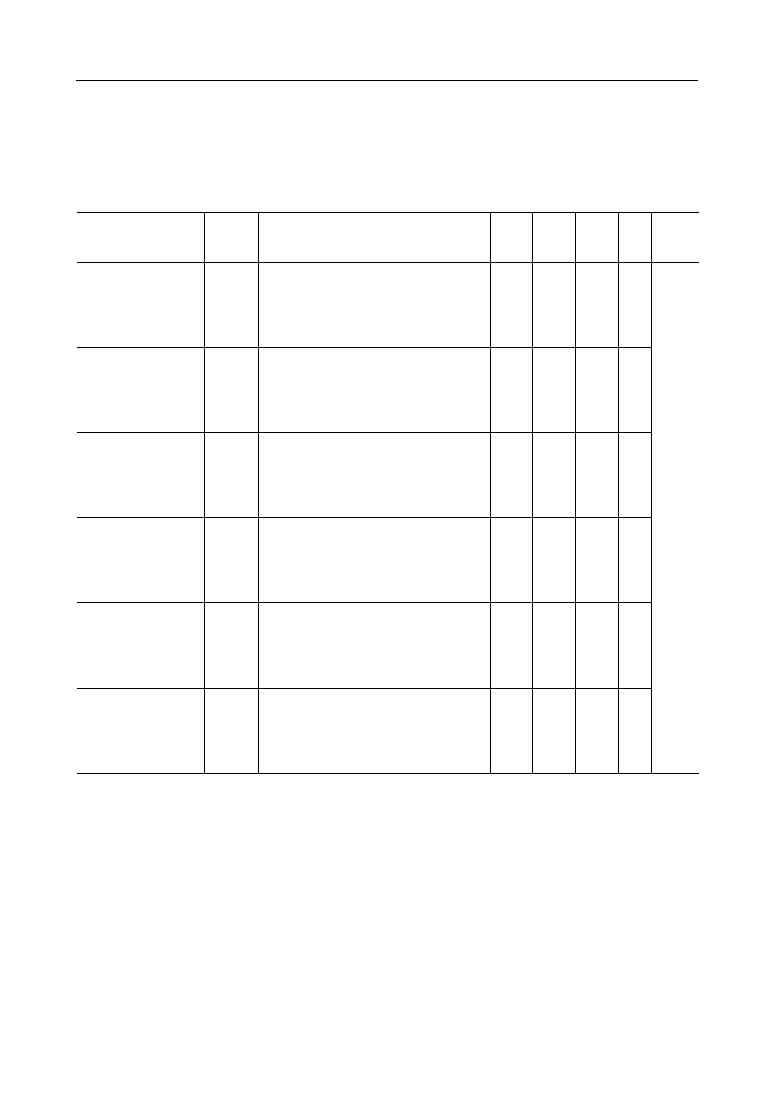

Pad No.

Y (µm)

X (µm)

Pad Name

1

≠1897.7

2123.6

P6.1

2

≠1701.4

P6.2

3

≠1505.4

P6.3

4

≠1231.1

P7.0

5

≠1034.8

P7.1

6

≠838.8

P7.2

7

≠642.5

P7.3

8

≠446.2

BS1

9

≠250.2

BS2

10

≠54.0

SIGIN

11

142.0

V

DDR

12

338.3

XT0

13

495.0

XT1

14

691.3

TST1

15

887.2

TST2

16

1083.6

TST3

17

1279.8

OSC0

18

1436.5

OSC1

19

1819.3

XTSEL0

20

2031.2

XTSEL1

21

1609.4

XTM0

22

1452.8

XTM1

23

938.6

V

DD2

24

782.0

V

DDL

25

625.3

V

DDH

26

468.6

CB1

27

312.0

CB2

28

155.4

V

DD

29

≠1.3

V

SS

30

≠219.4

MD

31

≠405.6

RESET

32

≠592.2

V

DDI

33

≠778.4

PD.0

34

≠964.9

PD.1

35

≠1151.2

PD.2

36

≠1337.7

PD.3

37

≠1523.9

PC.0

38

≠2031.2

PC.1

2107.3

Pad No.

Y (µm)

X (µm)

Pad Name

39

1810.6

≠2123.6

PC.2

40

1618.5

PC.3

41

1264.2

PB.0

42

1072.2

PB.1

43

880.1

PB.2

44

688.0

PB.3

45

496.0

P1.0

46

303.9

P1.1

47

111.8

P1.2

48

≠80.6

P1.3

49

≠272.7

P2.0

50

≠464.8

P2.1

51

≠656.8

P2.2

52

≠848.9

P2.3

53

≠1041.0

P3.0

54

≠1233.1

P3.1

55

≠1529.1

P3.2

56

≠1721.2

P3.3

57

≠1913.3

P8.0

58

≠1552.5

P8.1

59

≠1370.2

P9.0

60

≠1187.6

P9.1

61

≠1005.2

P9.2

62

≠822.9

P9.3

63

≠640.6

PA.0

64

≠458.2

PA.1

65

≠275.9

PA.2

66

≠93.6

PA.3

67

88.7

P4.0

68

271.0

P4.1

69

453.4

P4.2

70

635.7

P4.3

71

818.0

P5.0

72

1000.3

P5.1

73

1182.7

P5.2

74

1365.0

P5.3

75

2042.0

P6.0

≠2107.3

2123.6

2107.3

≠2123.6

≠2107.3

2123.6

2107.3

≠2123.6

≠2107.3

2123.6

2107.3

≠2123.6

≠2107.3

2123.6

2107.3

≠2123.6

≠2107.3

2123.6

2107.3

≠2123.6

≠2107.3

2123.6

2107.3

≠2123.6

≠2107.3

2123.6

2107.3

≠2123.6

≠2107.3

2123.6

2107.3

≠2123.6

≠2107.3

2123.6

2107.3

≠2123.6

≠2107.3

2123.6

2107.3

≠2123.6

≠2107.3

2123.6

2107.3

≠2123.6

≠2107.3

2123.6

2107.3

≠2123.6

≠2107.3

2123.6

2107.3

≠2123.6

≠2107.3

2123.6

2107.3

≠2123.6

≠2107.3

2123.6

2107.3

≠2123.6

≠2107.3

2123.6

2107.3

≠2123.6

≠2107.3

2123.6

2107.3

≠2123.6

≠2107.3

2123.6

2107.3

≠2123.6

Pad Coordinates

° Semiconductor

MSM63238

9/32

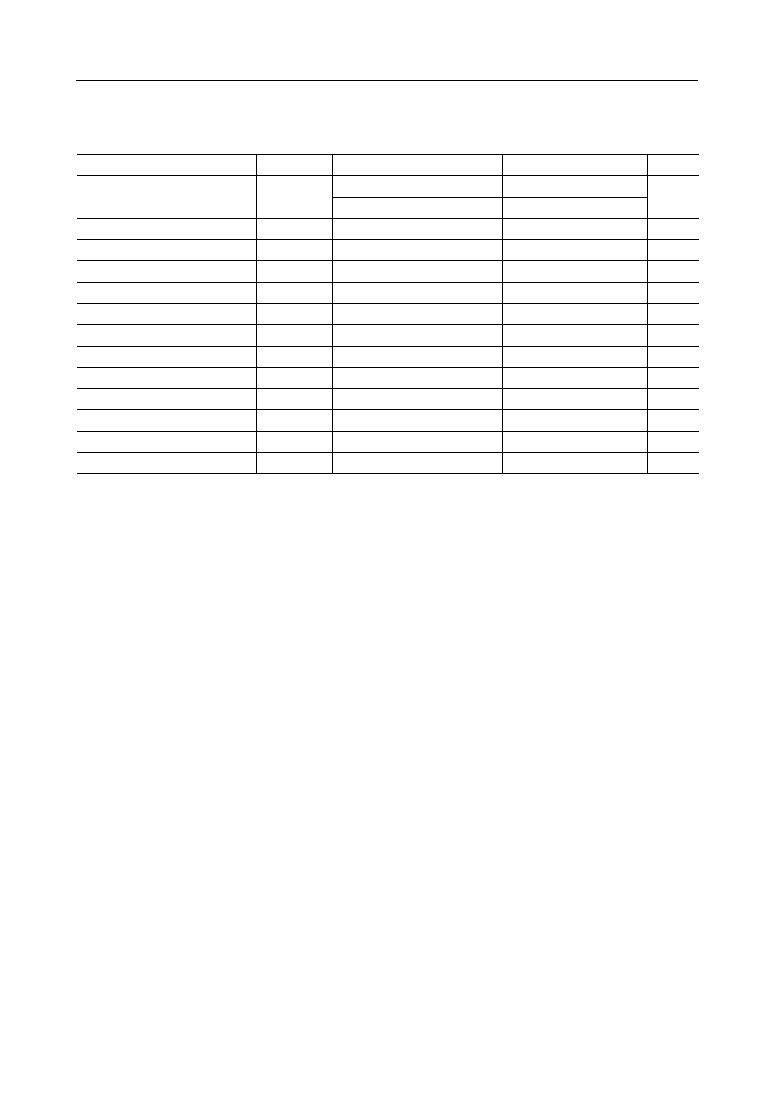

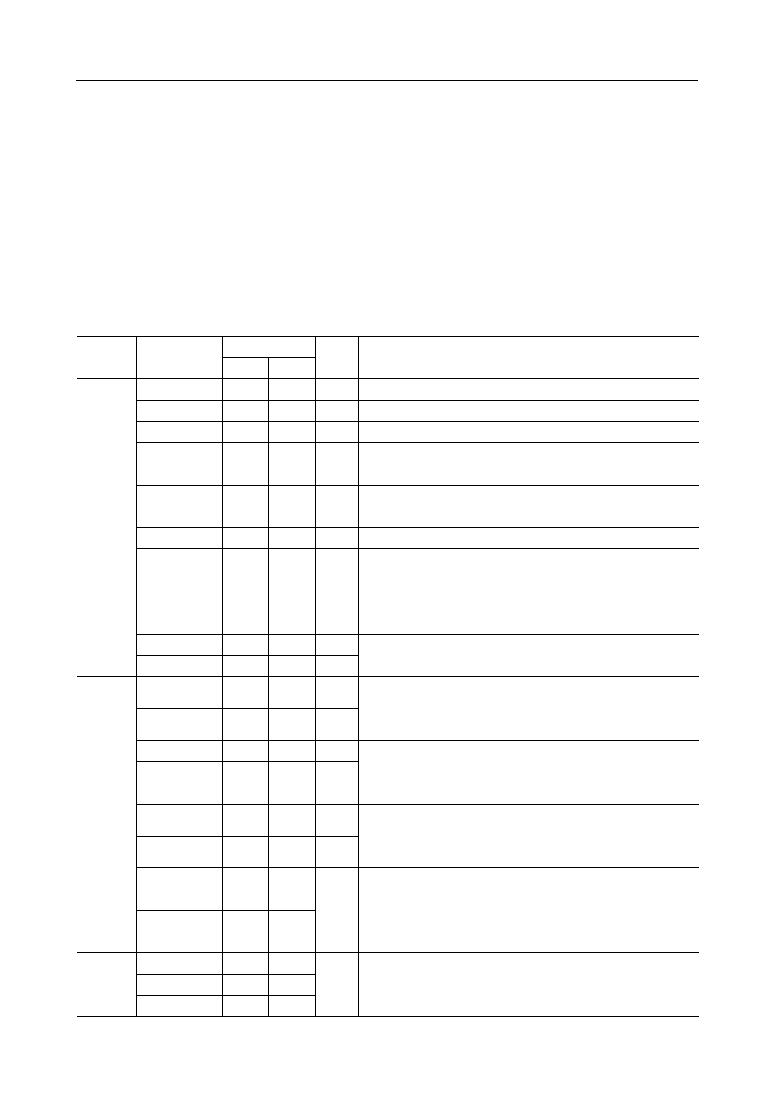

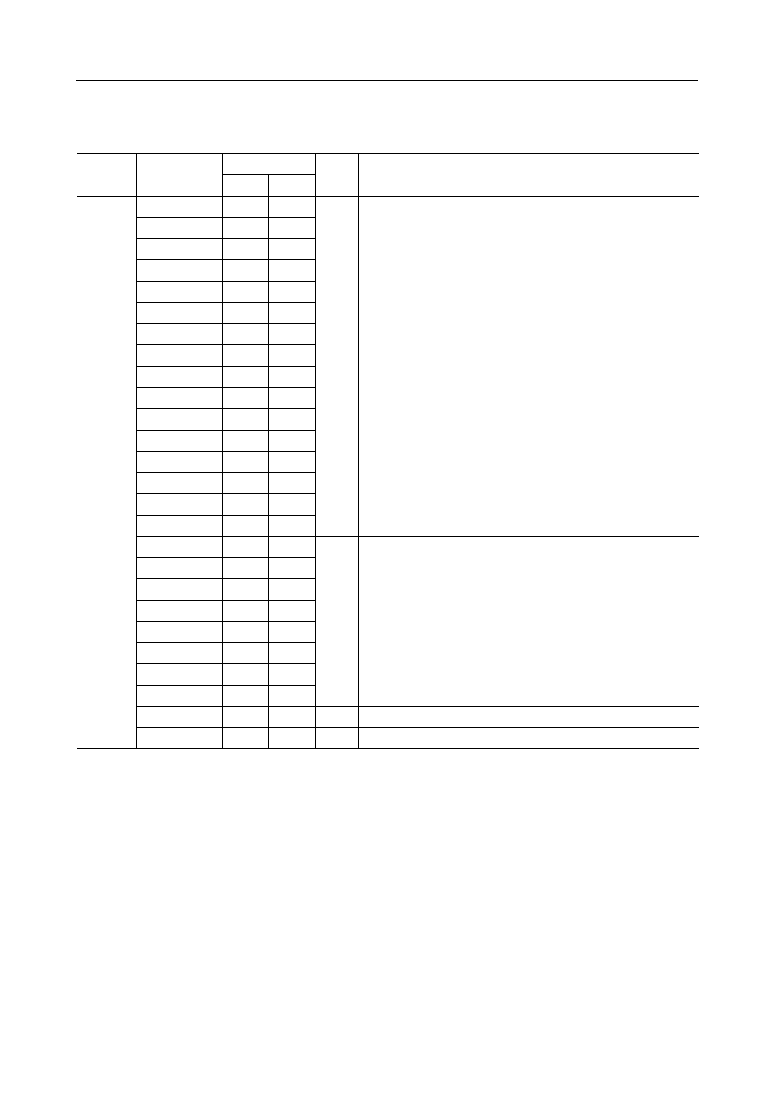

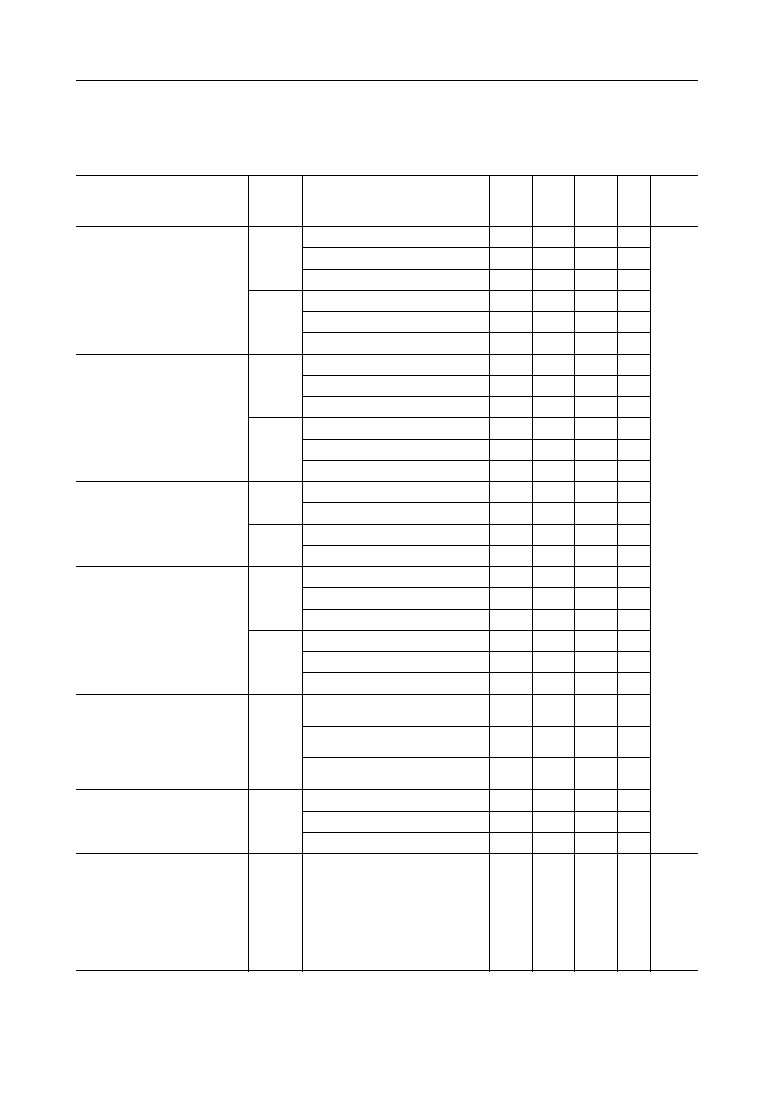

PIN DESCRIPTIONS

The basic functions of each pin of the MSM63238 are described in Table 1.

A symbol with a slash (/) denotes a pin that has a secondary function.

Refer to Table 2 for secondary functions.

For type, "--" denotes a power supply pin, "I" an input pin, "O" an output pin, and "I/O" an input-

output pin.

For pin, "GS-BK" denotes an 80-pin flat package (80QFP) and "TS-K" a 100-pin flat package

(100TQFP).

Table 1 Pin Descriptions (Basic Functions)

Function

Symbol

Type

Description

V

DD

Positive power supply

V

SS

Negative power supply

V

DDR

Interface power supply for SIGIN, BS1, BS2

V

DDI

Positive power supply pin for external interface

(power supply for input, output, and I/O ports)

V

DDL

Positive power supply pin for internal logic (internally generated).

A capacitor (0.1 mF) should be connected between this pin and V

SS

.

V

DDH

Voltage multiplier pin for power supply backup

(internally generated).

A capacitor (1.0 mF) should be connected between this pin

and V

SS

.

CB1

Pins to connect a capacitor for voltage multiplier.

A capacitor (1.0 mF) should be connected between CB1 and CB2.

CB2

XT0

I

Clock oscillation pins for POCSAG decoder.

A 32.768 kHz, 38.4 kHz, or 76.8 kHz crystal and capacitor (C

G

)

should be connected to these pins.

XT1

O

XTM0

I

XTM1

O

OSC0

I

High-speed clock oscillation pins.

A ceramic resonator and capacitors (C

L0

, C

L1

) or external

oscillation resistor (R

OS

) should be connected to these pins.

OSC1

O

XTSEL0

I

Low-speed CPU clock select pins.

These pins are used to select a low-speed CPU clock.

Because these are high impedance inputs, be sure to tie these

pins to V

DD

or V

SS

.

XTSEL1

TST1

Input pins for testing.

Pull-down resistors are internally connected to these pins.

The user cannot use these pins.

TST2

I

TST3

Low-speed clock oscillation pins for CPU.

A 32.768 kHz crystal and capacitor (C

GM

) should be connected

to these pins.

Power

Supply

Oscillation

Test

V

DD2

Positive power supply pin for low-speed clock (internally generated)

31

32

13

36

27

26

28

29

30

14

15

23

24

19

20

21

22

16

17

18

Pin

--

--

--

--

--

--

--

--

--

TS-K

GS-BK

36

37

14

42

32

31

33

34

35

15

16

27

28

21

22

23

24

18

19

20

° Semiconductor

MSM63238

10/32

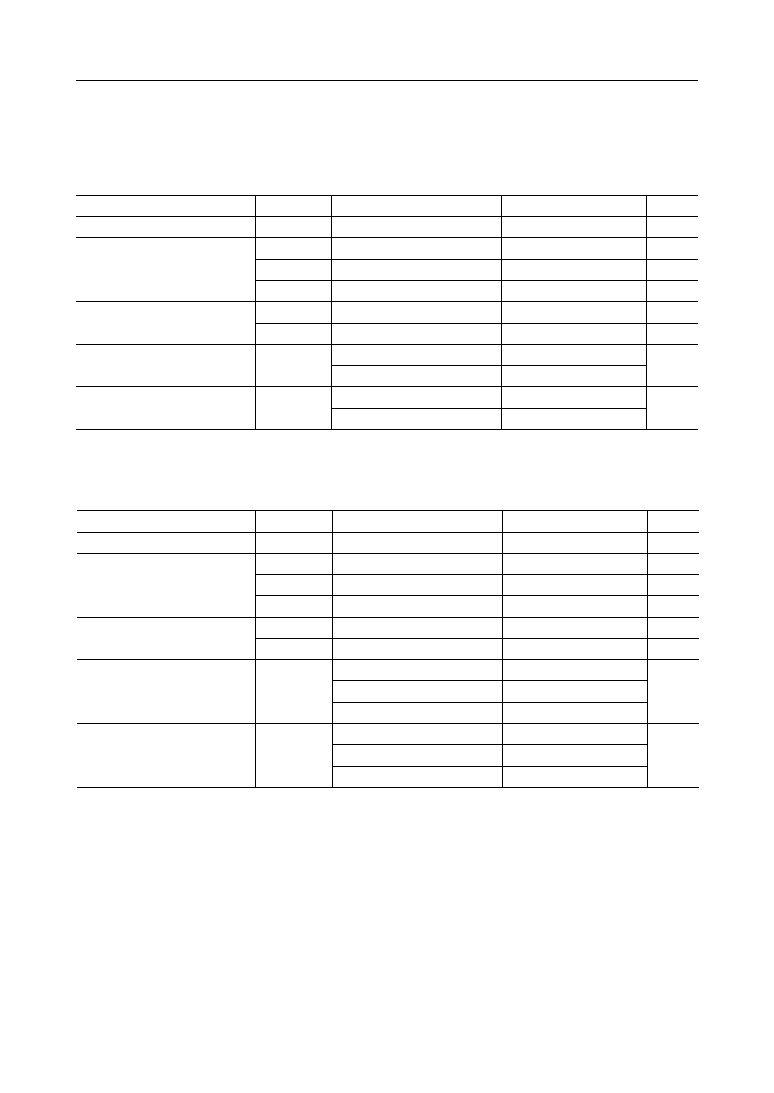

Table 1 Pin Descriptions (Basic Functions) (continued)

RESET

I

Reset input pin.

Setting this pin to "H" level puts this device into a reset state.

Then, setting this pin to "L" level starts executing an instruction

from address 0000H.

A pull-down resistor is internally connected to this pin.

Reset

34

Function

Symbol

Type

Description

MD

O

Melody output pin (normal phase)

BS1

O

Battery saving outputs.

Signals to control intermittent operations of RF receiver.

BS2

SIGIN

I

Receive data input pin.

Input pin for receive data from RF receiver.

Melody

POCSAG

Decoder

33

10

11

12

Pin

P1.0/INT5

50

P1.1/INT5

51

P1.2/INT5

52

P1.3/INT5

53

I

4-bit input port.

Pull-up resistor input, pull-down resistor input, or

high-impedance input is selectable for each bit.

P2.0

54

P2.1

55

P2.2

56

P2.3

57

P3.0

58

P3.1

59

P3.2

60

P3.3

61

P4.0/A0

73

P4.1/A1

74

P4.2/A2

75

P4.3/A3

76

P5.0/A4

77

P5.1/A5

78

P5.2/A6

79

P5.3/A7

80

P6.0/A8

2

P6.1/A9

3

P6.2/A10

4

P6.3/A11

5

P7.0/A12

6

P7.1/A13

7

P7.2/A14

8

P7.3/A15

9

O

Port

4-bit output ports.

P-channel open drain output, N-channel open drain output,

CMOS output, or high-impedance output is selectable for each

bit.

O

O

O

O

O

39

38

10

11

12

59

61

62

64

65

67

68

69

70

72

73

74

89

90

91

92

93

94

95

97

99

1

2

3

4

5

7

8

TS-K

GS-BK

° Semiconductor

MSM63238

11/32

Table 1 Pin Descriptions (Basic Functions) (continued)

Function

Symbol

Type

Description

Pin

P8.0/RD

62

P8.1/WR

64

P9.0/D0

65

P9.1/D1

66

P9.2/D2

67

P9.3/D3

68

PA.0/D4

69

PA.1/D5

70

PA.2/D6

71

PA.3/D7

72

PB.0/INT0/

TM0CAP/

TM0OVF

46

PB.1/INT0/

TM1CAP/

TM1OVF

47

PB.2/INT0/

T02CK

48

PB.3/INT0/

T13CK

49

PC.0/INT1/

RXD

42

I/O

Port

2-bit input-output port and 4-bit input-output ports.

In input mode, pull-up resistor input, pull-down resistor input,

or high-impedance input is selectable for each bit.

In output mode, P-channel open drain output, N-channel open

drain output, CMOS output, or high-impedance output is

selectable for each bit.

PC.1/INT1/

TXC

43

PC.2/INT1/

RXC

44

PC.3/INT1/

TXD

45

PD.0

37

PD.1

38

PD.2

39

PD.3

40

I/O

I/O

I/O

I/O

I/O

75

77

79

80

81

82

84

85

86

87

54

56

57

58

48

51

52

53

43

44

45

46

GS-BK TS-K

° Semiconductor

MSM63238

12/32

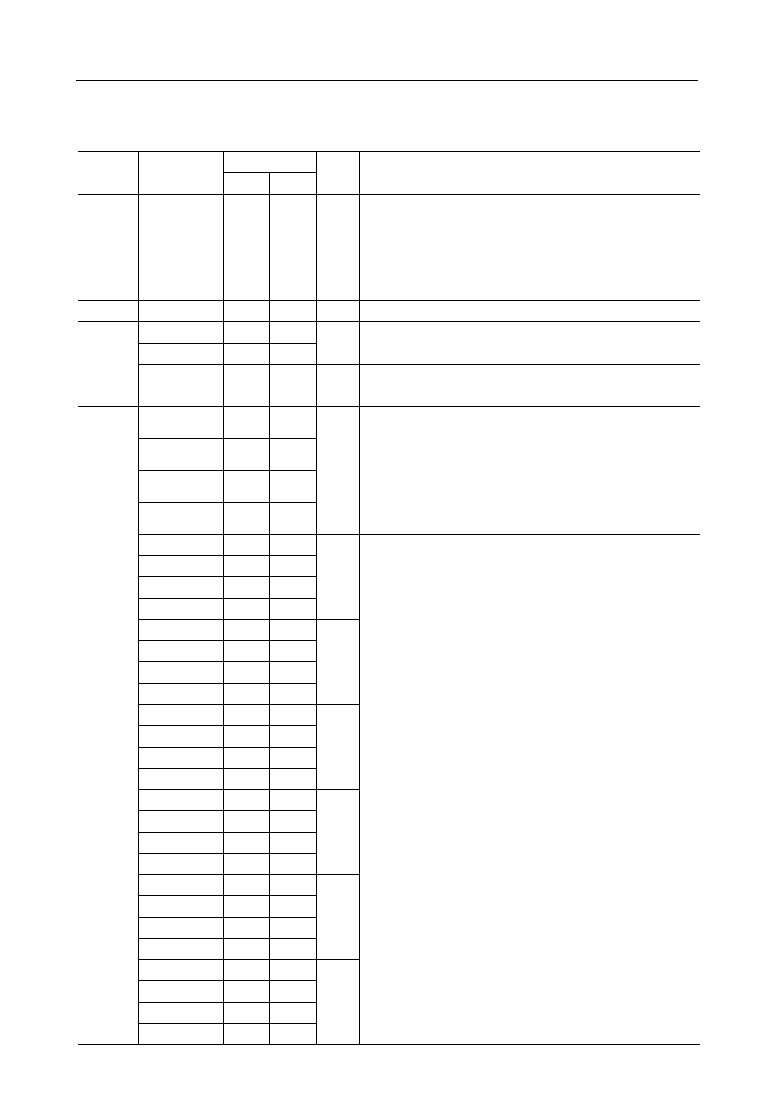

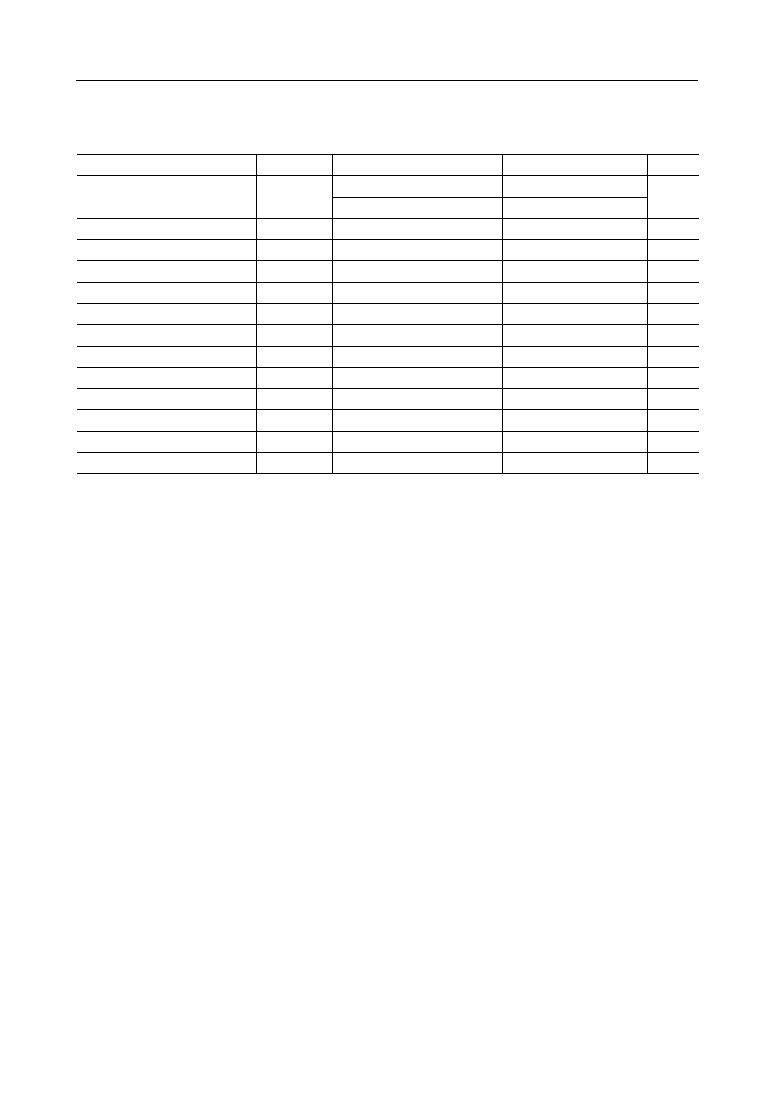

Table 2 shows the secondary functions of each pin of the MSM63238.

Table 2 Pin Descriptions (Secondary Functions)

Function

Symbol

Type

Description

Pin

PB.0/INT0

46

Capture

External 0 interrupt input pins.

The change of input signal level causes an interrupt to occur.

The Port B Interrupt Enable register (PBIE) enables or

disables an interrupt for each bit.

PB.1/INT0

47

PB.2/INT0

48

PB.3/INT0

49

I

PC.0/INT1

42

External 1 interrupt input pins.

The change of input signal level causes an interrupt to occur.

The Port C Interrupt Enable register (PCIE) enables or

disables an interrupt for each bit.

PC.1/INT1

43

PC.2/INT1

44

PC.3/INT1

45

I

P1.0/INT5

50

External 5 interrupt input pins.

The change of input signal level causes an interrupt to occur.

The Port 1 Interrupt Enable register (P1IE) enables or

disables an interrupt for each bit.

P1.1/INT5

51

P1.2/INT5

52

P1.3/INT5

53

I

PB.0/TM0CAP

46

I

Timer 0 capture trigger input pin.

PB.1/TM1CAP

47

I

Timer 1 capture trigger input pin.

External

Interrupt

54

56

57

58

48

51

52

53

59

61

62

64

54

56

GS-BK TS-K

° Semiconductor

MSM63238

13/32

Table 2 Pin Descriptions (Secondary Functions) (continued)

Function

Symbol

Type

Description

Pin

PB.0/TM0OVF

46

O

Timer 0 overflow flag output pin.

PB.1/TM1OVF

47

O

Timer 1 overflow flag output pin.

PB.2/T02CK

48

I

External clock input pin for timer 0 and timer 2.

PB.3/T13CK

49

I

External clock input pin for timer 1 and timer 3.

Timer

PD.2/TBCCLK

39

O

Low-speed oscillation clock output pin

PD.3/HSCLK

40

O

High-speed oscillation clock output pin

Oscillation

Output

PC.0/RXD

42

I

Serial port receive data input pin

Sync serial port clock input-output pin.

Transmit clock output when this device is used as a master

processor.

Transmit clock input when this device is used as a slave

processor.

PC.1/TXC

43

I/O

Sync serial port clock input-output pin.

Receive clock output when this device is used as a master

processor.

Receive clock input when this device is used as a slave

processor.

PC.2/RXC

44

I/O

PC.3/TXD

45

O

Serial port transmit data output pin.

Serial

Port

54

56

57

58

45

46

48

51

52

53

GS-BK TS-K

° Semiconductor

MSM63238

14/32

Table 2 Pin Descriptions (Secondary Functions) (continued)

Function

Symbol

Type

Description

Pin

P4.0/A0

73

Address output bus for external memory

External

Memory

Read signal output pin for external memory (negative logic)

O

P4.1/A1

74

P4.2/A2

75

P4.3/A3

76

P5.0/A4

77

P5.1/A5

78

P5.2/A6

79

P5.3/A7

80

P6.0/A8

2

P6.1/A9

3

P6.2/A10

4

P6.3/A11

5

P7.0/A12

6

P7.1/A13

7

P7.2/A14

8

P7.3/A15

9

P9.0/D0

65

P9.1/D1

66

P9.2/D2

67

P9.3/D3

68

PA.0/D4

69

PA.1/D5

70

PA.2/D6

71

PA.3/D7

72

P8.0/RD

62

Write signal output pin for external memory (negative logic)

O

P8.1/WR

64

Data bus for external memory

I/O

O

89

90

91

92

93

94

95

97

99

1

2

3

4

5

7

8

79

80

81

82

84

85

86

87

75

77

GS-BK TS-K

° Semiconductor

MSM63238

15/32

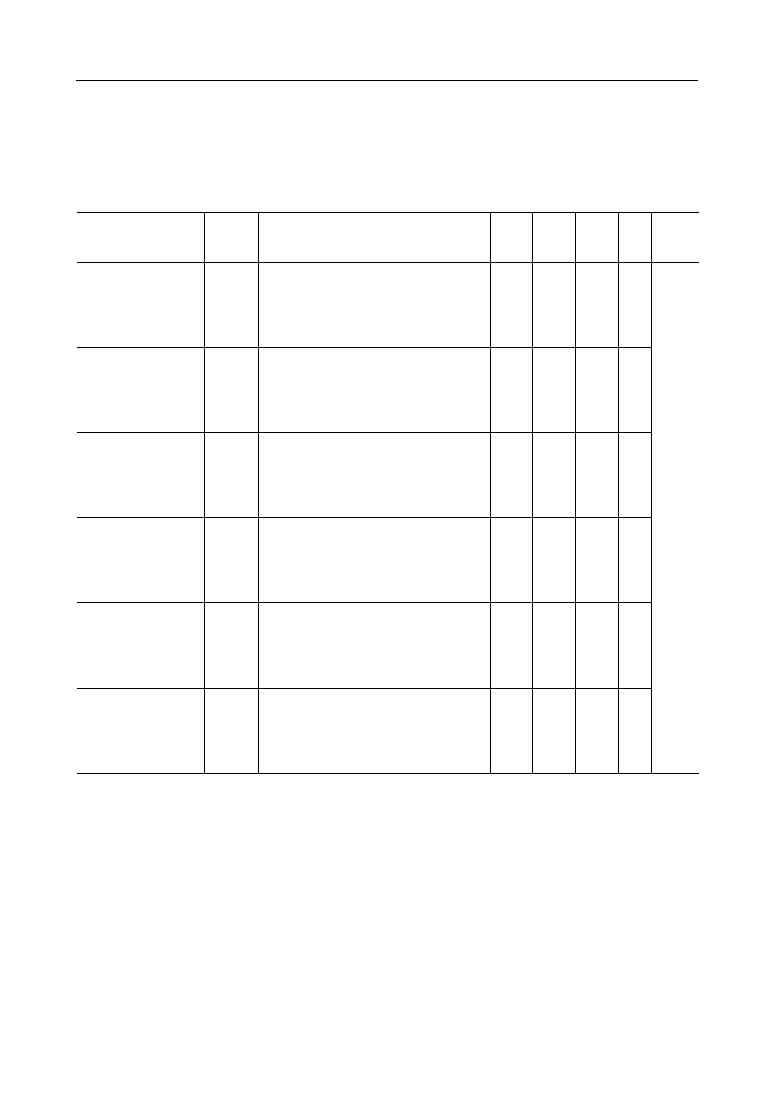

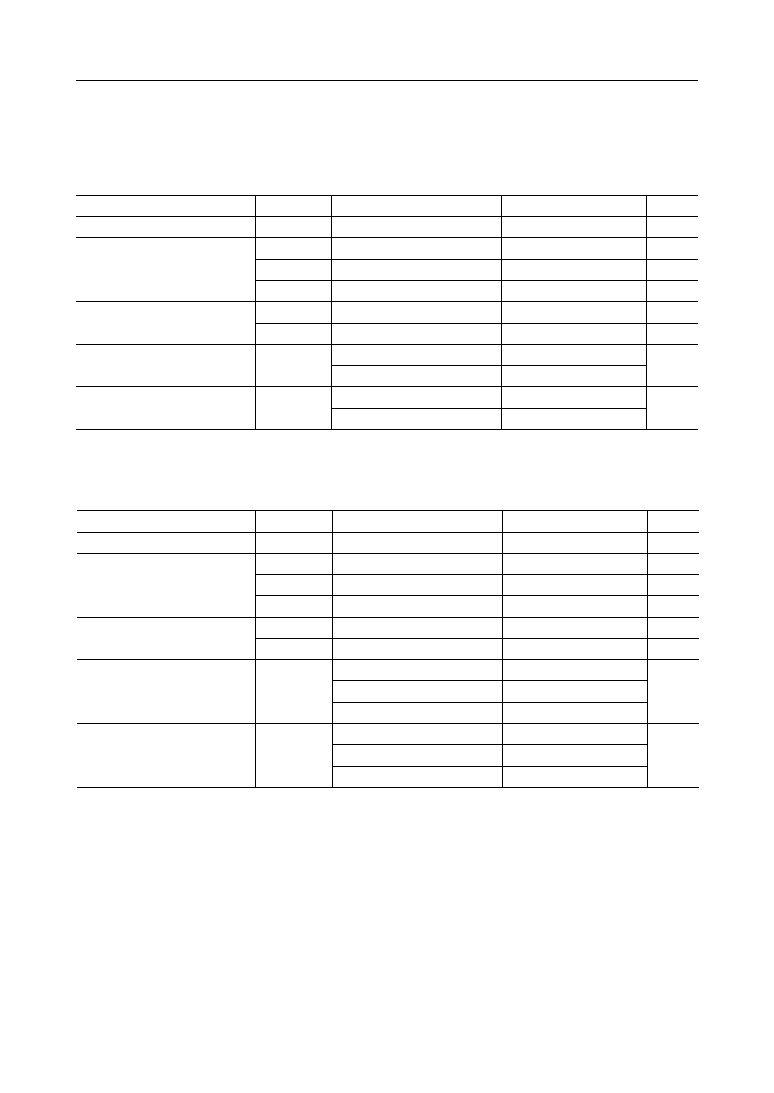

ABSOLUTE MAXIMUM RATINGS

Parameter

Symbol

Condition

Rating

Unit

Power Supply Voltage 1

V

DD

Backup used, Ta = 25∞C

≠0.3 to +3.0

V

Power Supply Voltage 2

V

DDI

Ta = 25∞C

≠0.3 to +6.0

V

Power Supply Voltage 3

V

DDR

Ta = 25∞C

≠0.3 to +6.0

V

Power Supply Voltage 4

V

DDH

Ta = 25∞C

≠0.3 to +6.0

V

Power Supply Voltage 5

V

DDL

Ta = 25∞C

≠0.3 to +6.0

V

Input Voltage 1

V

IN1

V

DD

Input, Ta = 25∞C

≠0.3 to V

DD

+ 0.3

V

Input Voltage 2

V

IN2

V

DDI

Input, Ta = 25∞C

≠0.3 to V

DDI

+ 0.3

V

Output Voltage 1

V

IN3

V

DDR

Input, Ta = 25∞C

≠0.3 to V

DDR

+ 0.3

V

Output Voltage 2

V

OUT1

V

DD

output, Ta = 25∞C

≠0.3 to V

DD

+ 0.3

V

Output Voltage 3

V

OUT2

V

DDI

output, Ta = 25∞C

≠0.3 to V

DDI

+ 0.3

V

Output Voltage 4

V

OUT3

V

DDR

output, Ta = 25∞C

≠0.3 to V

DDR

+ 0.3

V

Storage Temperature

V

OUT4

V

DDH

output, Ta = 25∞C

≠0.3 to V

DDH

+ 0.3

V

≠55 to +150

∞C

Input Voltage 3

T

STG

(V

SS

= 0 V)

Backup not used, Ta = 25∞C

≠0.3 to +6.0

--

° Semiconductor

MSM63238

16/32

RECOMMENDED OPERATING CONDITIONS

∑ When backup is used

V

DDI

0.9 to 5.5

V

V

DDR

0.9 to 5.5

V

Crystal Oscillation Frequency

f

XT

30 to 80

kHz

f

XTM

30 to 35

kHz

Ceramic Oscillation Frequency

f

CM

200k to 1M

V

DD

= 1.5 to 2.7 V

--

--

--

--

Parameter

Symbol

Condition

Range

Unit

Operating Temperature

T

op

≠20 to +70

∞C

V

DD

--

0.9 to 2.7

V

Operating Voltage

(V

SS

= 0 V)

--

External RC Oscillator Resistance

R

OS

50 to 300

V

DD

= 1.5 to 2.7 V

300k to 500k

Hz

V

DD

= 1.2 to 2.7 V

100 to 300

kW

V

DD

= 1.2 to 2.7 V

V

DDI

1.8 to 5.5

V

V

DDR

1.8 to 5.5

V

Crystal Oscillation Frequency

f

XT

30 to 80

kHz

f

XTM

30 to 35

kHz

Ceramic Oscillation Frequency

f

CM

300k to 1M

Hz

V

DD

= 2.2 to 5.5 V

--

--

--

--

Parameter

Symbol

Condition

Range

Unit

Operating Temperature

T

op

≠20 to +70

∞C

V

DD

--

1.8 to 5.5

V

Operating Voltage

(V

SS

= 0 V)

--

External RC Oscillator Resistance

R

OS

50 to 300

kW

V

DD

= 2.2 to 5.5 V

200k to 2M

V

DD

= 2.7 to 5.5 V

30 to 300

V

DD

= 2.7 to 5.5 V

300k to 500k

V

DD

= 1.8 to 5.5 V

100 to 300

V

DD

= 1.8 to 5.5 V

∑ When backup is not used

° Semiconductor

MSM63238

17/32

ELECTRICAL CHARACTERISTICS

DC Characteristics

Parameter

Symbol

Condition

Mea-

suring

Circuit

(V

DD

= V

DDI

= V

DDR

= 0.9 to 5.5 V, V

SS

= 0 V, Ta = ≠20 to +70∞C unless otherwise specified)

Unit

Max.

Typ.

Min.

1

V

DDL

Voltage

V

DDL

High speed clock stop

1.0

1.5

2.0

V

High speed clock oscillation

(V

DD

= 1.2 to 5.5 V)

1.2

5.5

V

Crystal Oscillation Start

Voltage

V

STA

Oscillation start time: within

5 seconds

1.2

V

Crystal Oscillation Hold Voltage V

HOLD

1.7

V

Crystal Oscillation Stop Detect

Time

T

STOP

0.1

5.0

ms

External Crystal Oscillator

Capacitance

C

G

, C

GM

5

25

pF

Internal Crystal Oscillator

Capacitance

C

D

, C

DM

20

25

30

pF

Internal RC Oscillator

Capacitance

POR Voltage

Non-POR Voltage

C

OS

8

12

16

pF

V

POR1

V

DD

= 1.5 V

0.0

0.4

V

V

POR2

V

DD

= 1.5 V

1.2

1.5

V

2.0

3.0

V

0.0

0.7

V

V

DD

= 3.0 V

V

DD

= 3.0 V

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

V

DD2

Voltage

V

DD2

--

1.0

2.0

V

1.5

Backup not used

V

DDH

Voltage (Backup used)

V

DDH

High speed clock stop

V

DD

= 1.5 V

C

h

, C

12

= 1 mF

2.8

--

3.0

V

High speed clock oscillation

(Ceramic oscillation, 1 MHz)

V

DD

= 1.5 V

C

h

, C

12

= 1 mF

2.0

--

2.7

V

1.0

V

--

--

Backup used

0.9

V

--

--

Backup used (Ta = 25∞C)

Notes: 1. "T

STOP

" indicates that if the crystal oscillator stops over the value of T

STOP

, the system

reset occurs.

2. "POR" denotes Power On Reset.

3. "V

POR1

" indicates that POR occurs when V

DD

falls from V

DD

to V

POR1

and again rises

up to V

DD

.

4. "V

POR2

" indicates that POR does not occur when V

DD

falls from V

DD

to V

POR2

and

again rises up to V

DD

.

° Semiconductor

MSM63238

18/32

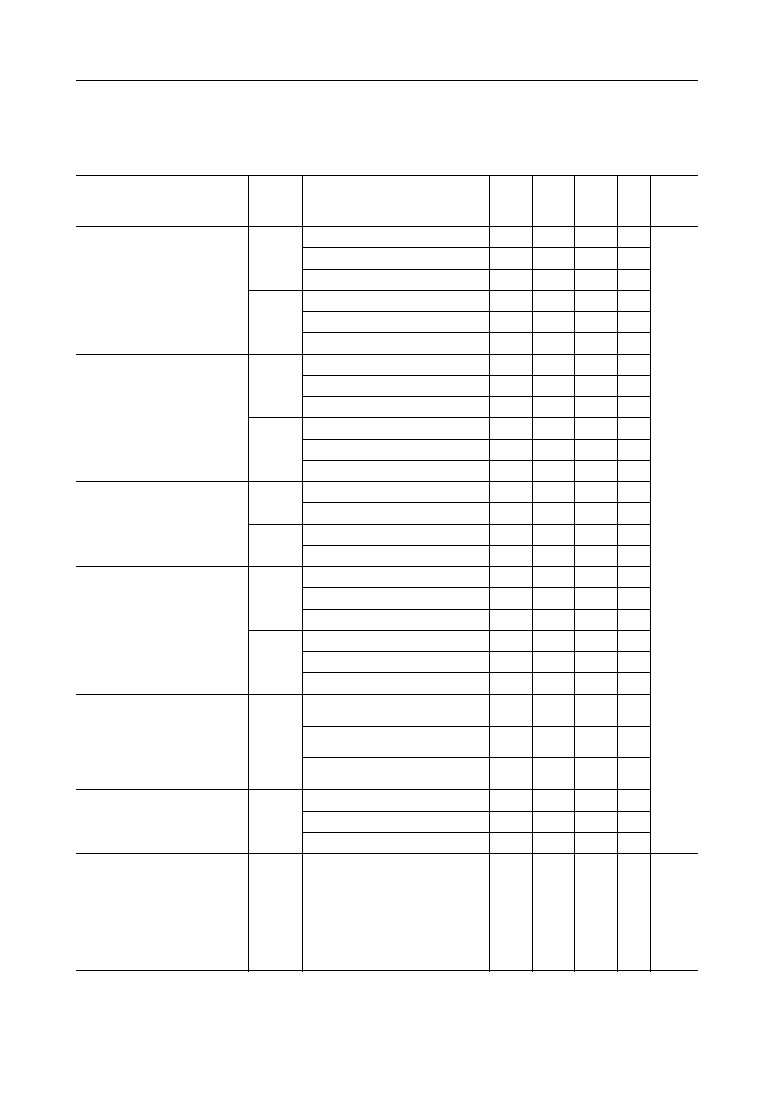

DC Characteristics (continued)

∑ When backup is used

Parameter

Symbol

Condition

Mea-

suring

Circuit

(V

DD

= V

DDI

= 1.5 V, V

SS

= 0 V, Ta = ≠20 to +70∞C unless otherwise specified)

Unit

Max.

Typ.

Min.

35

6.0

--

Supply Current 1

I

DD1

CPU in HALT mode.

mA

1

(High-speed clock oscillation stop)

Decoder in HALT mode.

(Decoder oscillation stop)

80

35

--

Supply Current 2

I

DD2

CPU in HALT mode.

mA

(High-speed clock oscillation stop)

Decoder in carrier on state.

(76.8 kHz operation)

200

85

--

Supply Current 3

I

DD3

CPU in HALT mode.

mA

(High-speed clock oscillation stop)

Decoder in data receiving state.

(76.8 kHz operation)

40

22

--

Supply Current 4

I

DD4

CPU in operation at 32 kHz.

mA

(High-speed clock oscillation stop)

Decoder in HALT mode.

(Decoder oscillation stop)

800

600

--

Supply Current 5

I

DD5

CPU in operation at high speed.

mA

(RC oscillation, R

OS

= 51 kW)

Decoder in HALT mode.

(Decoder oscillation stop)

900

700

--

Supply Current 6

I

DD6

CPU in operation at high speed.

mA

(Ceramic oscillation, 1 MHz)

Decoder in HALT mode.

(Decoder oscillaiton stop)

° Semiconductor

MSM63238

19/32

DC Characteristics (continued)

∑ When backup is not used

Parameter

Symbol

Condition

Mea-

suring

Circuit

(V

DD

= V

DDI

= 3.0 V, V

SS

= 0 V, Ta = ≠20 to +70∞C unless otherwise specified)

Unit

Max.

Typ.

Min.

20

3.0

--

Supply Current 1

I

DD1

CPU in HALT mode.

mA

1

(High-speed clock oscillation stop)

Decoder in HALT mode.

(Decoder oscillation stop)

40

17

--

Supply Current 2

I

DD2

CPU in HALT mode.

mA

(High-speed clock oscillation stop)

Decoder in carrier on state.

(76.8 kHz operation)

100

42

--

Supply Current 3

I

DD3

CPU in HALT mode.

mA

(High-speed clock oscillation stop)

Decoder in data receiving state.

(76.8 kHz operation)

25

10

--

Supply Current 4

I

DD4

CPU in operation at 32 kHz.

mA

(High-speed clock oscillation stop)

Decoder in HALT mode.

(Decoder oscillation stop)

600

450

--

Supply Current 5

I

DD5

CPU in operation at high speed.

mA

(RC oscillation, R

OS

= 51 kW)

Decoder in HALT mode.

(Decoder oscillation stop)

1000

800

--

Supply Current 6

I

DD6

CPU in operation at high speed.

mA

(Ceramic oscillation, 2 MHz)

Decoder in HALT mode.

(Decoder oscillation stop)

° Semiconductor

MSM63238

20/32

DC Characteristics (continued)

Parameter

Symbol

Condition

Mea-

suring

Circuit

(V

DD

= V

DDI

= V

DDH

= V

DDR

= 3.0 V, V

SS

= 0 V, Ta = ≠20 to +70∞C unless otherwise specified)

Unit

Max.

Output Current 1

(P2.0 to P2.3)

(P3.0 to P3.3)

(P4.0 to P4.3)

(PC.0 to PC.3)

(PD.0 to PD.3)

≠0.4

mA

2

I

OH1

V

OH1

= V

DDI

≠ 0.5 V

≠1.0

mA

≠1.5

mA

Output Current 2

(MD)

Output Current 4

(OSC1)

I

OH4R

V

OH4R

= V

DDH

≠ 0.5 V

(RC oscillation)

≠0.25

mA

Output Leakage

(P2.0 to P2.3)

(P3.0 to P3.3)

(P4.0 to P4.3)

(PD.0 to PD.3)

I

OOH

V

OH

= V

DDI

1.0

mA

I

OOL

V

OL

= V

SS

--

mA

.

.

.

Typ.

≠1.4

≠3.5

≠5.0

≠1.3

--

--

Min.

≠2.5

≠6.0

≠8.5

≠2.5

--

≠1.0

V

DDI

= 1.5 V

V

DDI

= 3.0 V

V

DDI

= 5.0 V

2.5

mA

I

OL1

V

OL1

= 0.5 V

6.0

mA

8.5

mA

1.4

3.0

3.7

0.4

1.0

1.5

V

DDI

= 1.5 V

V

DDI

= 3.0 V

V

DDI

= 5.0 V

≠0.5

mA

I

OH2

V

OH2

= V

DD

≠ 0.7 V

≠2.0

mA

≠4.0

mA

≠2.0

≠6.0

≠9.0

≠4.0

≠11.0

≠14.0

V

DD

= 1.5 V

V

DD

= 3.0 V

V

DD

= V

DDH

= 5.0 V

4.0

mA

I

OL2

V

OL2

= 0.7 V

11.0

mA

14.0

mA

2.0

5.5

7.0

0.5

2.0

4.0

V

DD

= 1.5 V

V

DD

= 3.0 V

V

DD

= V

DDH

= 5.0 V

Output Current 3

(BS1, BS2)

≠1.0

mA

I

OH3

V

OH3

= V

DDR

≠ 0.5 V

≠2.0

mA

≠3.0

mA

≠4.5

≠10.0

≠14.0

≠7.0

≠16.0

≠24.0

V

DDR

= 1.5 V

V

DDR

= 3.0 V

V

DDR

= 5.0 V

7.0

mA

I

OL3

V

OL3

= 0.5 V

16.0

mA

24.0

mA

4.0

8.0

9.5

1.0

2.0

3.0

V

DDR

= 1.5 V

V

DDR

= 3.0 V

V

DDR

= 5.0 V

V

DD

= V

DDH

= 3.0 V

V

DD

= V

DDH

= 5.0 V

≠0.5

mA

≠1.7

≠3.5

I

OL4R

V

OL4R

= 0.5 V

(RC oscillation)

2.5

mA

1.5

0.25

V

DD

= V

DDH

= 3.0 V

V

DD

= V

DDH

= 5.0 V

3.5

mA

1.8

0.5

I

OH4C

V

OH4C

= V

DDH

≠ 0.5 V

(ceramic oscillation)

≠60

mA

≠160

≠300

V

DD

= V

DDH

= 3.0 V

V

DD

= V

DDH

= 5.0 V

≠100

mA

≠240

≠400

I

OL4C

V

OL4C

= 0.5 V

(ceramic oscillation)

300

mA

170

60

V

DD

= V

DDH

= 3.0 V

V

DD

= V

DDH

= 5.0 V

400

mA

210

100

.

.

.

° Semiconductor

MSM63238

21/32

DC Characteristics (continued)

Parameter

Symbol

Condition

Mea-

suring

Circuit

(V

DD

= V

DDI

= V

DDH

= V

DDR

= 3.0 V, V

SS

= 0 V, Ta = ≠20 to +70∞C unless otherwise specified)

Unit

Max.

Input Current 1

(P1.0 to P1.3)

(P8.0, P8.1)

(P9.0 to P9.3)

(PD.0 to PD.3)

45

mA

3

I

IH1

V

IH1

= V

DDI

(when pulled down)

260

mA

650

mA

Input Current 2

(SIGIN)

Input Current 4

(RESET)

I

IH4

V

IH4

= V

DD

350

mA

.

.

.

Typ.

20

120

350

180

Min.

2

30

70

10

V

DDI

= 1.5 V

V

DDI

= 3.0 V

V

DDI

= 5.0 V

≠2

mA

I

IL1

V

IL1

= V

SS

(when pulled up)

≠30

mA

≠70

mA

≠20

≠120

≠350

≠45

≠260

≠650

V

DDI

= 1.5 V

V

DDI

= 3.0 V

V

DDI

= 5.0 V

Input Current 3

(OSC0)

≠30

mA

I

IL3

V

IL3

= V

SS

(when pulled up)

≠200

mA

≠170

≠450

≠350

≠750

V

DD

= V

DDH

= 3.0 V

V

DD

= V

DDH

= 5.0 V

V

DD

= 1.5 V

V

DD

= 3.0 V

2400

mA

1100

150

I

IH1Z

V

IH1

= V

DDI

(in a high impedance state)

1.0

mA

--

0.0

I

IL1Z

V

IL1

= V

SS

(in a high impedance state)

0.0

mA

--

≠1.0

I

IH2Z

V

IH2

= V

DDR

1.0

mA

--

0.0

I

IL2Z

V

IL2

= V

SS

0.0

mA

--

≠1.0

I

IH3R

V

IH3

= V

DDH

(RC oscillation)

1.0

mA

--

0.0

I

IL3R

V

IL3

= V

SS

(RC oscillation)

0.0

mA

--

≠1.0

1.0

mA

I

IH3C

V

IH3

= V

DDH

(ceramic oscillation)

3.0

mA

0.5

1.5

0.1

0.75

V

DD

= V

DDH

= 3.0 V

V

DD

= V

DDH

= 5.0 V

≠0.1

mA

I

IL3C

V

IL3

= V

SS

(ceramic oscillation)

≠0.75

mA

≠0.5

≠1.5

≠1.0

≠3.0

V

DD

= V

DDH

= 3.0 V

V

DD

= V

DDH

= 5.0 V

V

DD

= V

DDH

= 5.0 V

5.0

mA

2.7

0.5

I

IL4

V

IL4

= V

SS

0.0

mA

--

≠1.0

Input Current 5

(TST1, TST2, TST3)

I

IH5

V

IH5

= V

DD

1500

mA

750

50

V

DD

= 1.5 V

V

DD

= 3.0 V

5.5

mA

3.0

0.5

V

DD

= V

DDH

= 5.0 V

11.0

mA

6.5

0.25

I

IL5

V

IL5

= V

SS

0.0

mA

--

≠1.0

I

IH6Z

V

IH6

= V

DD

1.0

mA

--

0.0

Input Current 6

(XTSEL0, XTSEL1)

I

IL6Z

V

IL6

= V

SS

0.0

mA

--

≠1.0

° Semiconductor

MSM63238

22/32

DC Characteristics (continued)

Parameter

Symbol

Condition

Mea-

suring

Circuit

(V

DD

= V

DDI

= V

DDH

= V

DDR

= 3.0 V, V

SS

= 0 V, Ta = ≠20 to +70∞C unless otherwise specified)

Unit

Max.

Typ.

Min.

Input Voltage 1

(P1.0 to P1.3)

(P8.0, P8.1)

(P9.0 to P9.3)

(PD.0 to PD.3)

V

DDI

= 1.5 V

1.2

--

1.5

V

4

V

IH1

V

DDI

= 3.0 V

2.4

--

3.0

V

V

DDI

= 5.0 V

4.0

--

5.0

V

Input Voltage 3

(OSC0)

.

.

.

DV

T2

Input Pin Capacitance

(P1.0 to P1.3)

(P8.0, P8.1)

(P9.0 to P9.3)

(PD.0 to PD.3)

C

IN

--

--

--

5

pF

Hysteresis Width 2

(RESET, TST1, TST2, TST3,

XTSEL0, XTSEL1)

.

.

.

1

V

DDI

= 1.5 V

0.0

--

0.3

V

V

IL1

V

DDI

= 3.0 V

0.0

--

0.6

V

V

DDI

= 5.0 V

0.0

--

1.0

V

Input Voltage 2

(SIGIN)

V

DDR

= 1.5 V

1.2

--

1.5

V

V

IH2

V

DDR

= 3.0 V

2.4

--

3.0

V

V

DDR

= 5.0 V

4.0

--

5.0

V

V

DDR

= 1.5 V

0.0

--

0.3

V

V

IL2

V

DDR

= 3.0 V

0.0

--

0.6

V

V

DDR

= 5.0 V

0.0

--

1.0

V

V

DD

= V

DDH

= 3.0 V

2.4

--

3.0

V

V

IH3

V

DD

= V

DDH

= 5.0 V

4.0

--

5.0

V

V

DD

= V

DDH

= 3.0 V

0.0

--

0.6

V

V

IL3

V

DD

= V

DDH

= 5.0 V

0.0

--

1.0

V

Input Voltage 4

(RESET, TST1, TST2, TST3,

XTSEL0, XTSEL1)

V

DD

= 1.5 V

1.35

--

1.5

V

V

IH4

V

DD

= 3.0 V

2.4

--

3.0

V

V

DD

= V

DDH

= 5.0 V

4.0

--

5.0

V

V

DD

= 1.5 V

0.0

--

0.15

V

V

IL4

V

DD

= 3.0 V

0.0

--

0.6

V

V

DD

= V

DDH

= 5.0 V

0.0

--

1.0

V

V

DDI

= 1.5 V

0.05

0.1

0.3

V

DV

T1

V

DDI

= 3.0 V

0.2

0.5

1.0

V

V

DDI

= 5.0 V

0.25

1.0

1.5

V

Hysteresis Width 1

(P1.0 to P1.3)

(P8.0, P8.1)

(PD.0 to PD.3)

.

.

.

V

DD

= 1.5 V

0.05

0.1

0.3

V

V

DD

= 3.0 V

0.2

0.5

1.0

V

V

DD

= V

DDH

= 5.0 V

0.25

1.0

1.5

V

° Semiconductor

MSM63238

23/32

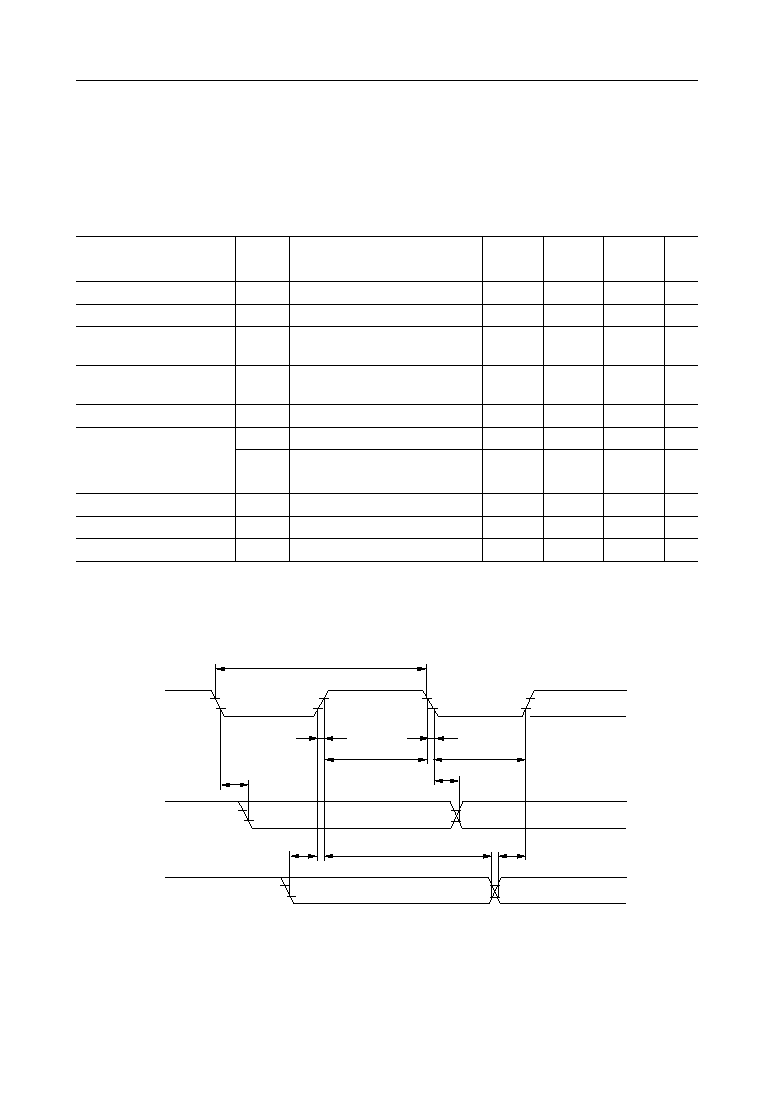

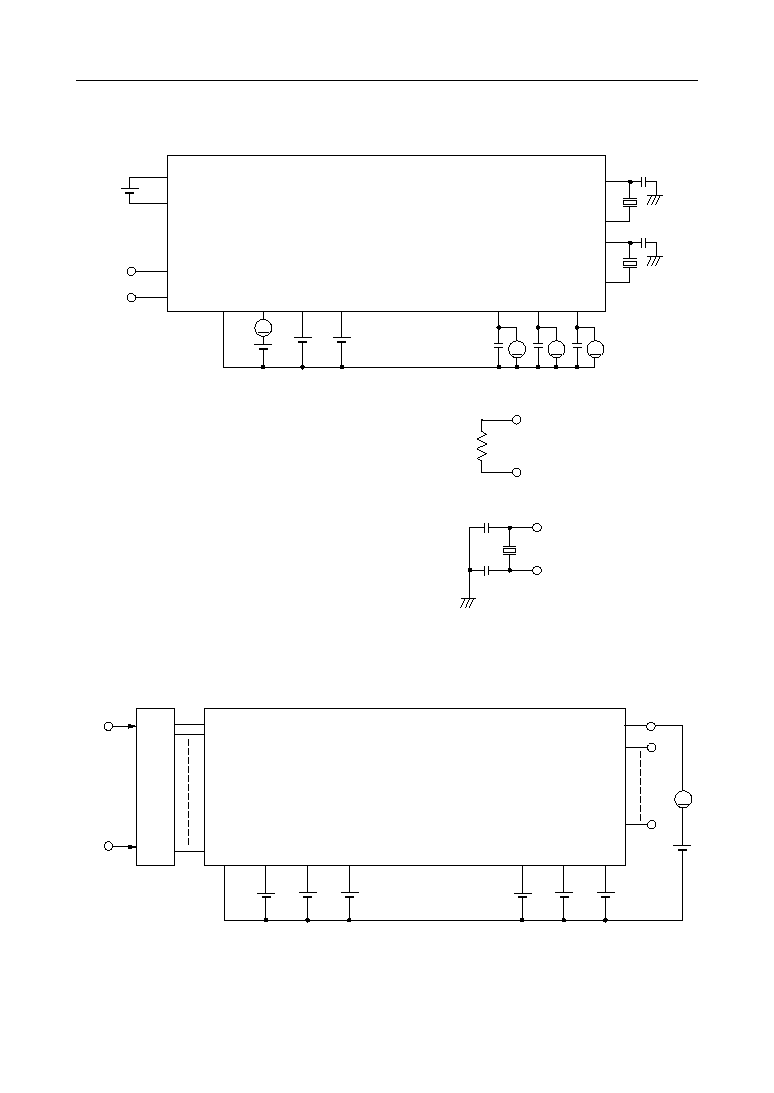

Measuring circuit 1

Measuring circuit 2

A

V

SS

V

DD

V

DDR

V

DDH

V

DDI

C

G

XT0

XT1

CB1

CB2

OSC0

OSC1

q

w

(*1)

C

L0

C

L1

q

w

q

w

R

OS

*1 RC Oscillator

Ceramic Oscillator

Ceramic Resonator

C

l

, C

2

C

h

, C

b12

C

G

, C

GM

C

L0

C

L1

Ceramic Resonator

: 0.1 mF

: 1 mF

: 15 pF

: 30 pF

: 30 pF

: CSB1000J (1 MHz)

CSA2.00MG (2 MHz)

(Murata MFG.-make)

V

V

C

2

V

DD2

C

GM

XTM0

XTM1

C

h

C

b12

V

DDL

V

C

l

76.8 kHz

Crystal

32.768 kHz

Crystal

A

(*3)

V

SS

V

DD

V

DDR

V

DDI

(*2)

V

IH

V

IL

*2 Input logic circuit to determine the specified measuring conditions.

*3 Measured at the specified output pins.

V

DDH

V

DD2

V

DDL

OUTPUT

INPUT

° Semiconductor

MSM63238

24/32

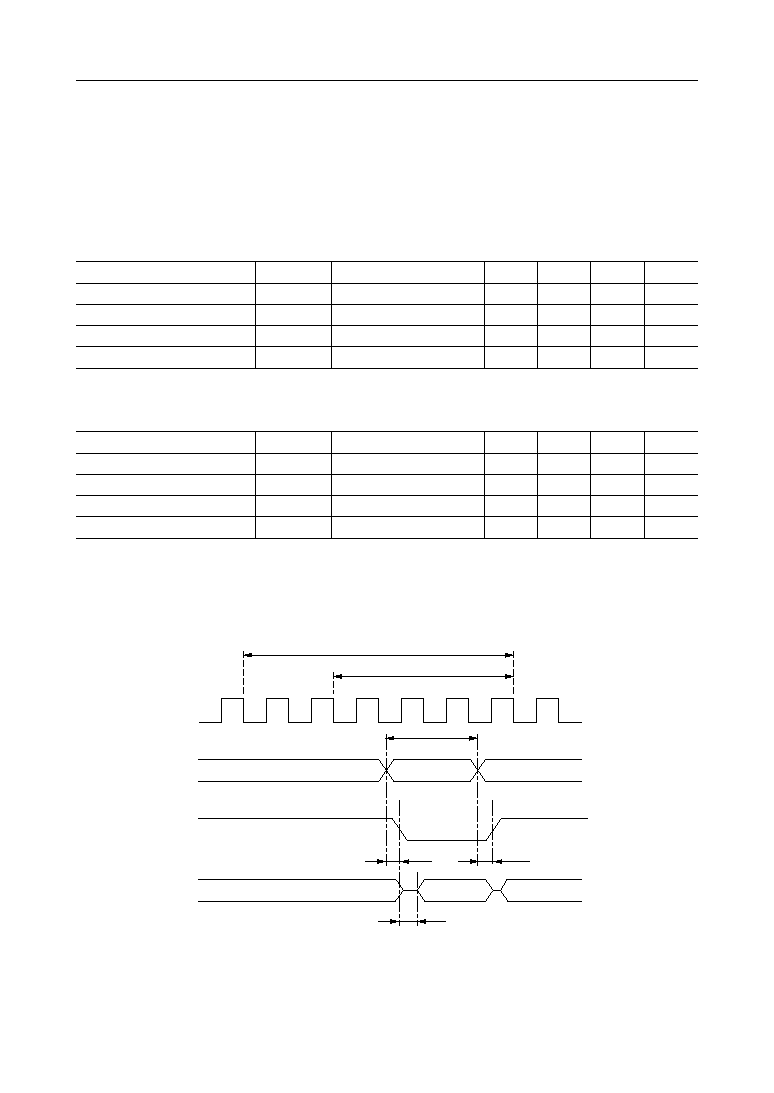

Measuring circuit 3

Measuring circuit 4

V

SS

V

DD

V

DDR

V

DDL

V

DDI

A

V

DD2

(*4)

V

DDH

INPUT

OUTPUT

V

SS

V

DD

V

DDR

V

DDL

V

DDI

(*4)

V

IH

V

IL

*4 Measured at the specified input pins.

V

DD2

V

DDH

INPUT

OUTPUT

Waveform

Monitoring

° Semiconductor

MSM63238

25/32

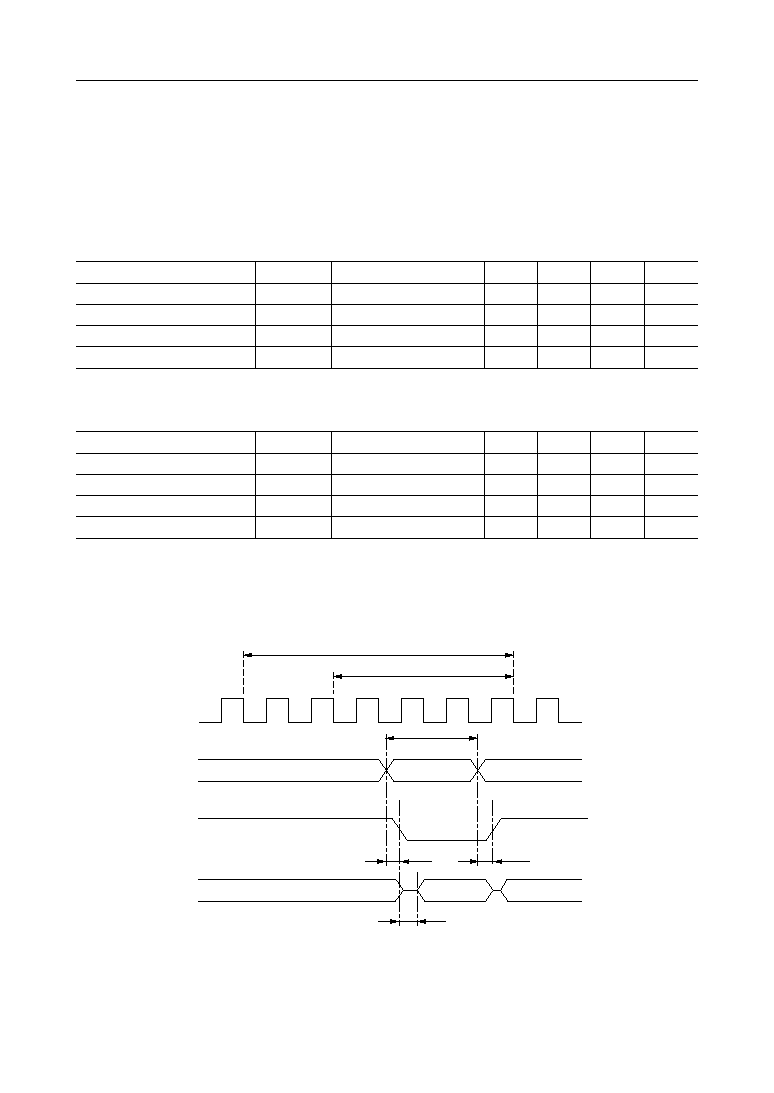

TXD (PC.3)

RXD (PC.0)

t

CYC

t

DDR

t

r

t

f

t

CWH

t

CWL

t

DDR

t

DS

t

DS

t

DH

5 V (V

DDI

)

0 V (V

SS

)

5 V (V

DDI

)

0 V (V

SS

)

5 V (V

DDI

)

0 V (V

SS

)

TXC (PC.1)/

RXC (PC.2)

AC Characteristics (Serial Interface, Serial Port)

(V

DD

= V

DDR

= 0.9 to 5.5 V, V

DDH

= 1.8 to 5.5 V, V

SS

= 0 V, V

DDI

= 5.0 V, Ta = ≠20 to +70

∞

C unless

otherwise specified)

(1) Synchronous Communication

Parameter

Symbol

Condition

Unit

--

TXC/RXC Input Fall Time

Max.

Typ.

Min.

t

f

--

ms

--

1.0

--

TXC/RXC Input Rise Time

t

r

--

ms

--

1.0

0.8

TXC/RXC Input "L" Level

Pulse Width

t

CWL

--

ms

--

--

0.8

TXC/RXC Input "H" Level

Pulse Width

t

CWH

--

ms

--

--

2.0

TXC/RXC Input Cycle Time

t

CYC

--

ms

--

--

--

TXC/RXC Output Cycle Time

t

CYC1(O)

CPU in operation state at 32 kHz

ms

30.5

--

--

t

CYC2(O)

CPU in operation at 2 MHz

V

DD

= V

DDH

= 2.7 V to 5.5 V

ms

0.5

--

--

TXD Output Delay Time

t

DDR

Output load capacitance 10 pF

ms

--

0.4

0.5

RXD Input Setup Time

t

DS

--

ms

--

--

0.8

RXD Input Hold Time

t

DH

--

ms

--

--

Synchronous communication timing

("H" level = 4.0 V, "L" level = 1.0 V)

° Semiconductor

MSM63238

26/32

TXD (PC.3)

T

BRT

5 V (V

DDI

)

0 V (V

SS

)

RXD (PC.0)

R

BRT

5 V (V

DDI

)

0 V (V

SS

)

(2) UART Communication

Parameter

Symbol

Condition

Unit

T

BRT

≠T

CR

Transmit Baud Rate

Max.

Typ.

Min.

T

BRT

T

BRT

= 1/f

BRT

T

CR

= 1/f

OSC

s

T

BRT

T

BRT

+T

CR

R

BRT

•0.97

Receive Baud Rate

R

BRT

s

R

BRT

R

BRT

•1.03

R

BRT

= 1/f

BRT

f

BRT

: Baud rates (1200, 2400, 4800, 9600 bps)

UART communication timing

("H" level = 4.0 V, "L" level = 1.0 V)

° Semiconductor

MSM63238

27/32

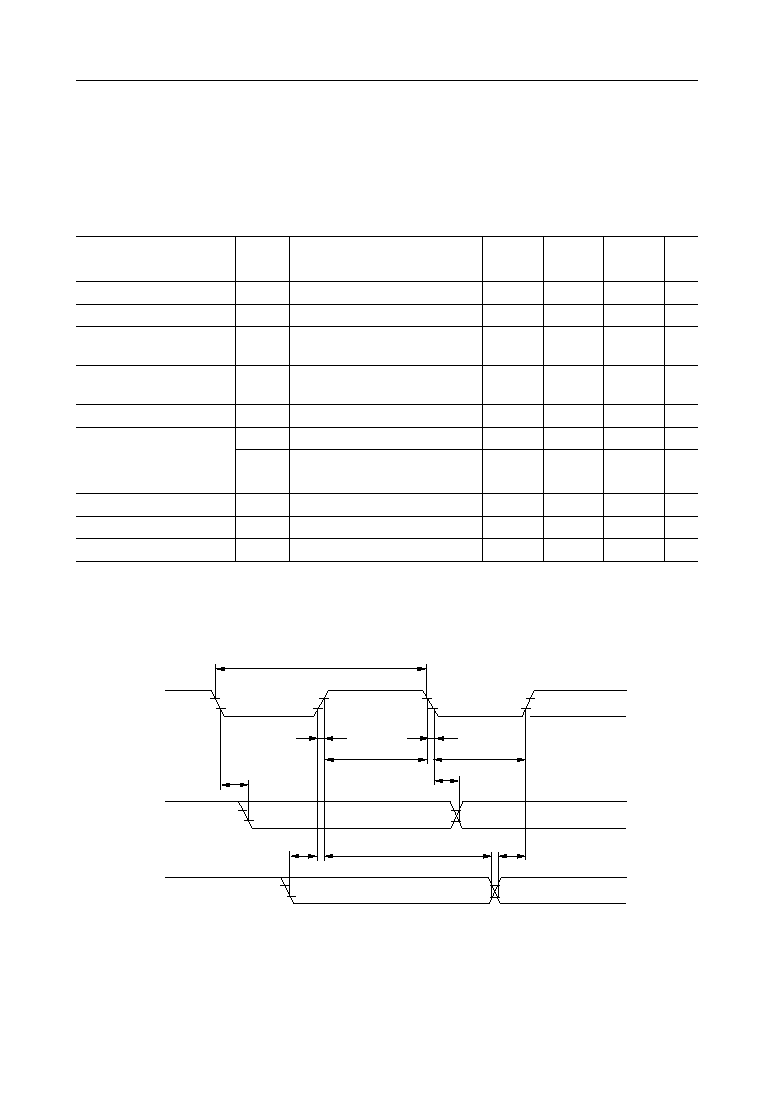

AC Characteristics (External Memory Interface)

(V

DD

= V

DDR

= 0.9 to 5.5 V, V

DDH

= 1.8 to 5.5 V, V

SS

= 0 V, V

DDI

= 5.0 V, Ta = ≠20 to +70

∞

C unless

otherwise specified)

(1) Reading from External Memory

Parameter

Read Cycle Time

RD Output Delay Time

Output Valid Time

External Memory Output Delay Time

Symbol

Condition

Min.

Typ.

Max.

Unit

t

RC

t

OE

t

OHA

t

DO

61.0

ms

ms

ms

ms

5.0

5.0

5.0

(a) When CPU operates at 32.768 kHz

Parameter

Read Cycle Time

RD Output Delay Time

Output Valid Time

External Memory Output Delay Time

Symbol

Condition

Min.

Typ.

Max.

Unit

t

RC

t

OE

t

OHA

t

DO

1.0

ms

ns

ns

ns

100

100

150

(b) When CPU operates at 2 MHz (V

DDH

= 2.7 to 5.5 V)

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

AC characteristics timing

("H" level = 4.0 V, "L" level = 1.0 V)

t

RC

t

OE

t

OHA

t

DO

Address output

Port setup value

Port setup value

Input data

Port setup value

Port setup value

P7 - P4

(A15 - A0)

P8.0

(RD)

PA, P9

(D7 - D0)

MOVXB obj, [RA]

MOVXB obj, xadr16

S2

S1

S2

S1

S2

S1

System clock

5 V (V

DDI

)

0 V (V

SS

)

5 V (V

DDI

)

0 V (V

SS

)

5 V (V

DDI

)

0 V (V

SS

)

° Semiconductor

MSM63238

28/32

(2) Writing to External Memory

Parameter

Write Cycle Time

Address Setup Time

Write Time

Write Recovery Time

Symbol

Condition

Min.

Typ.

Max.

Unit

t

WC

t

AS

t

W

t

WR

61.0

ms

ms

ms

ms

(a) When CPU operates at 32.768 kHz

Data Setup Time

t

DS

ms

Data Hold Time

t

DH

ms

30.5

15.3

15.3

45.8

15.3

Parameter

Write Cycle Time

Address Setup Time

Write Time

Write Recovery Time

Symbol

Condition

Min.

Typ.

Max.

Unit

t

WC

t

AS

t

W

t

WR

1.0

ms

ms

ms

ms

(b) When CPU operates at 2 MHz (V

DDH

= 2.7 to 5.5 V)

Data Setup Time

t

DS

ms

Data Hold Time

t

DH

ms

0.4

0.2

0.2

0.7

0.2

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

AC characteristics timing

("H" level = 4.0 V, "L" level = 1.0 V)

t

WC

t

DS

t

DH

t

AS

Address output

Port setup value

Port setup value

P7 - P4

(A15 - A0)

P8.1

(WR)

PA, P9

(D7 - D0)

MOVXB [RA], obj or MOVXB xadr16, obj

S2

S1

S2

S1

S2

S1

System clock

Output data

Port setup value

Port setup value

t

W

t

WR

5 V (V

DDI

)

0 V (V

SS

)

5 V (V

DDI

)

0 V (V

SS

)

5 V (V

DDI

)

0 V (V

SS

)

° Semiconductor

MSM63238

29/32

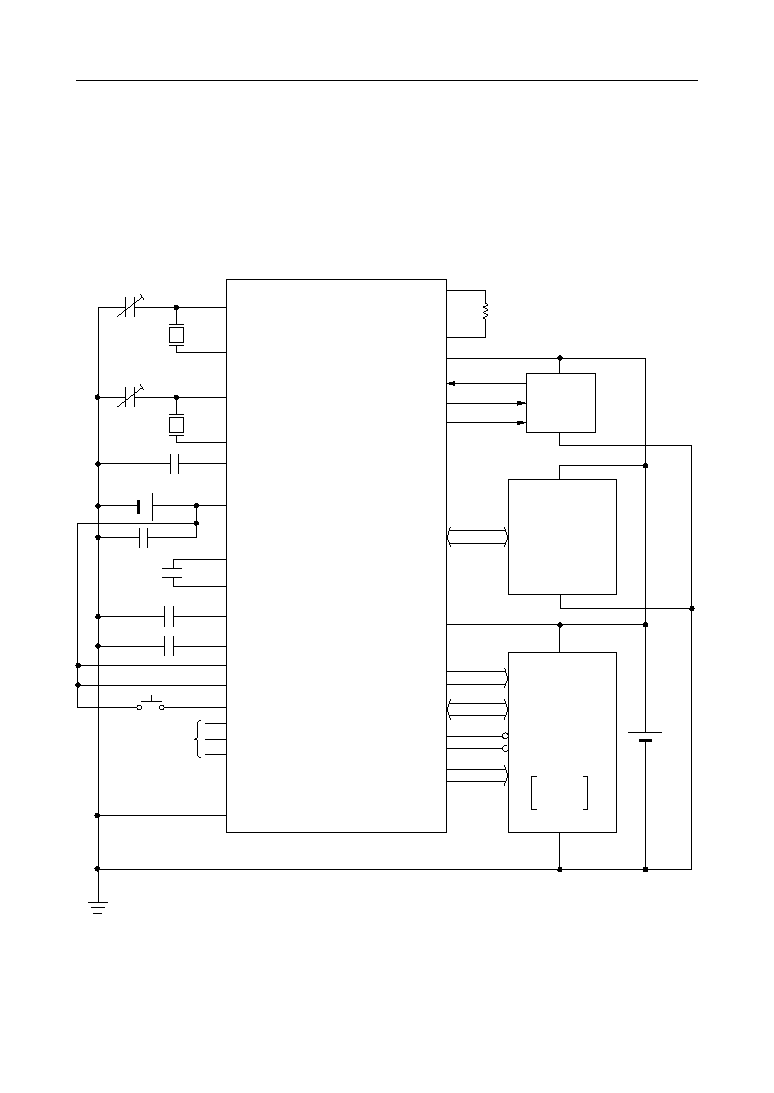

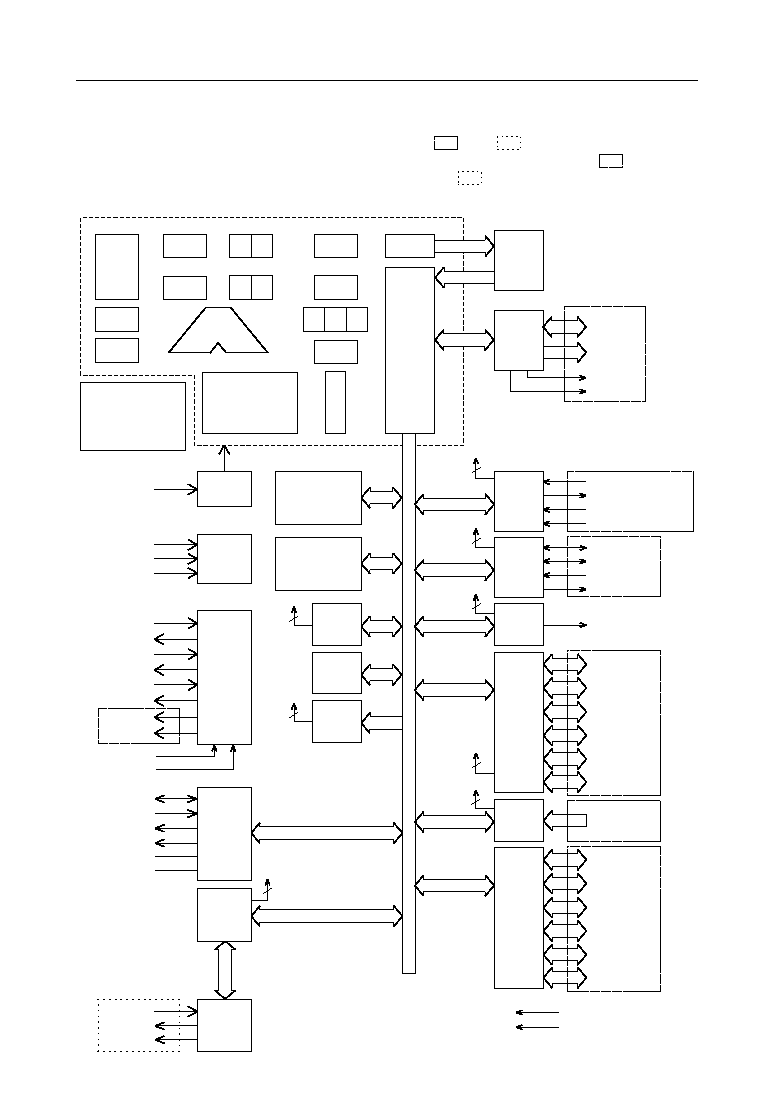

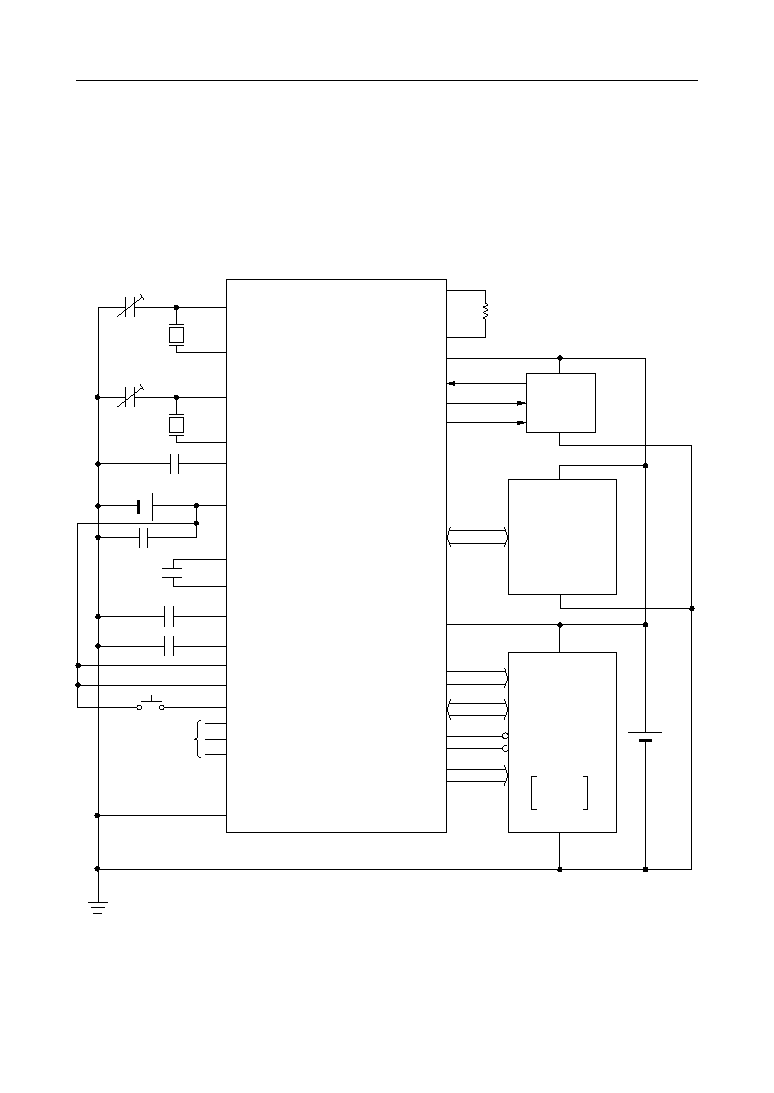

APPLICATION CIRCUITS

Note: V

DDI

is the power supply pin for the input, output, and input-output ports. V

DDR

is the

interface power supply pin for SIGIN, BS1, and BS2.

Be sure to connect the V

DDI

and V

DDR

pins either to the positive power supply pin (V

DD

)

of this device or to the positive power supply pin of the external memory.

Application Circuit Example with Power Supply Backup

XT0

XT1

XTM0

V

DD

CB1

CB2

V

DDL

RESET

TST1

TST2

V

SS

OSC0

OSC1

R

OS

C

b12

C

V

C

GM

5 to 25 pF

1.5 V

C

l

∑ RC oscillation is selected as high-speed oscillation.

∑ Ports and RF section are powered from

external memory power source.

∑ C

V

is an IC power supply bypass capacitor.

∑ Values of C

l

, C

2

, C

G

, C

GM

, C

h

, C

b12

, and C

V

are

for reference only.

V

DDI

P4-7

P9, PA

P8.0

P8.1

V

DD

A15-0

D7-0

RD

WR

V

SS

LCD Module

ROM

SRAM

EEPROM

5.0 V

76.8 kHz

Crystal

Push SW

MSM63238

P3

P2

PC

PD

Key Matrix

LED

Vibrator

UART

V

DD

V

SS

V

DD

V

SS

RF Section

TST3

XTSEL1

XTSEL0

XTM1

C

h

32.768 kHz

Crystal

C

G

5 to 25 pF

V

DDR

SIGIN

BS1

BS2

V

DD2

C

2

V

DDH

1.0 mF

0.1 mF

1.0 mF

0.1 mF

0.1 mF

Open

External

Memory

° Semiconductor

MSM63238

30/32

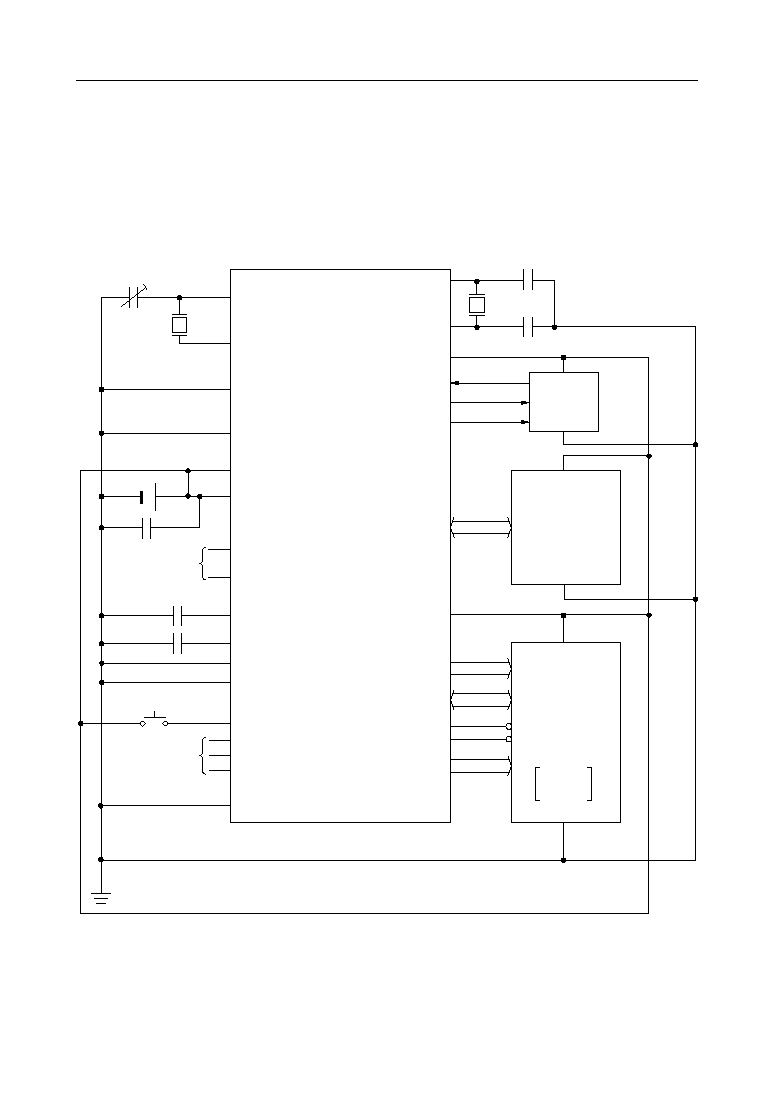

Note: V

DDI

is the power supply pin for the input, output, and input-output ports. V

DDR

is the

interface power supply pin for SIGIN, BS1, and BS2.

Be sure to connect the V

DDI

and V

DDR

pins either to the positive power supply pin (V

DD

)

of this device or to the positive power supply pin of the external memory.

Application Circuit Example with No Power Supply Backup

XT0

XT1

XTM0

V

DD

CB1

CB2

RESET

TST1

TST2

V

SS

C

V

3.0 V

∑ Ceramic oscillation is selected as high-speed oscillation.

∑ Ports and RF section are powered from

external memory power source.

∑ C

V

is an IC power supply bypass capacitor.

∑ Values of C

l

, C

2

, C

G

, C

V

, C

L0

, and C

L1

are for

reference only.

V

DDI

P4-7

P9, PA

P8.0

P8.1

V

DD

A15-0

D7-0

RD

WR

V

SS

LCD Module

ROM

SRAM

EEPROM

32.768 kHz

Crystal

Push SW

MSM63238

P3

P2

PC

PD

Key Matrix

LED

Vibrator

UART

V

DD

V

SS

V

DD

V

SS

RF Section

TST3

XTSEL1

XTSEL0

XTM1

C

2

C

G

5 to 25 pF

OSC0

OSC1

C

L0

C

L1

Ceramic

Resonator

V

DDR

SIGIN

BS1

BS2

V

DDH

C

l

V

DDL

V

DD2

30 pF

0.1 mF

0.1 mF

0.1 mF

Open

Open

30 pF

External

Memory

APPLICATION CIRCUITS (continued)

° Semiconductor

MSM63238

31/32

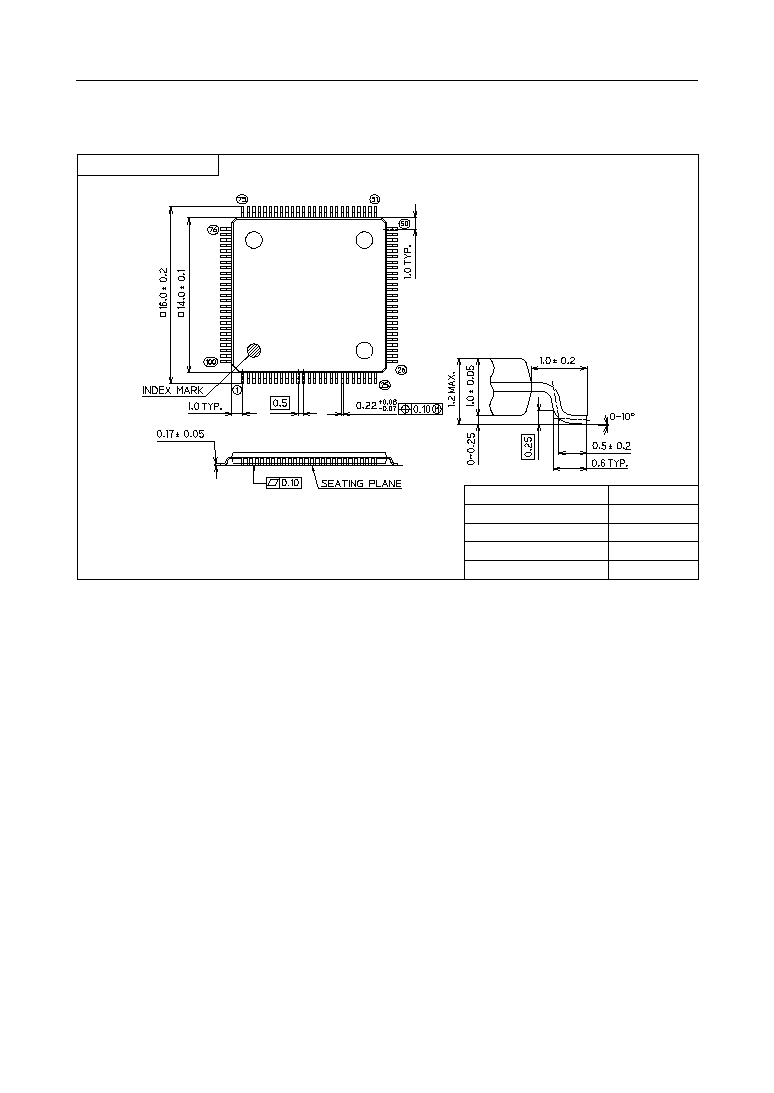

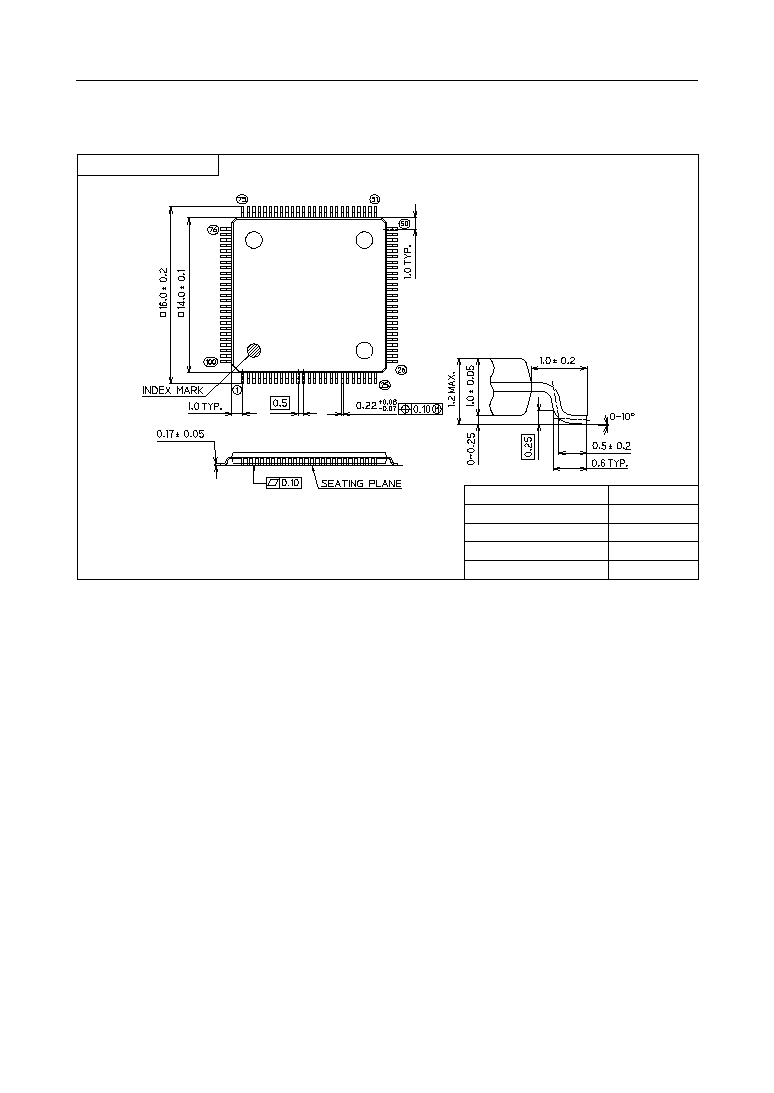

(Unit : mm)

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which

are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the

product name, package name, pin number, package code and desired mounting conditions

(reflow method, temperature and times).

QFP80-P-1420-0.80-BK

Package material

Lead frame material

Pin treatment

Solder plate thickness

Package weight (g)

Epoxy resin

42 alloy

Solder plating

5 mm or more

1.27 TYP.

Mirror finish

PACKAGE DIMENSIONS

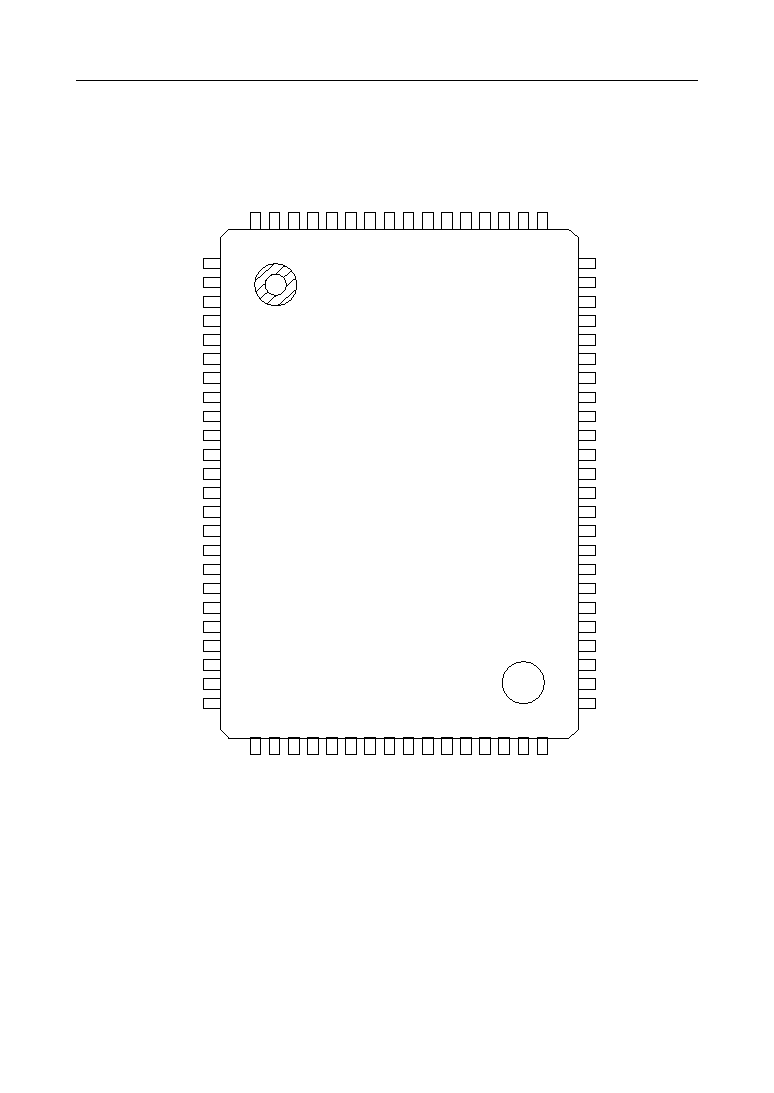

° Semiconductor

MSM63238

32/32

(Unit : mm)

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which

are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the

product name, package name, pin number, package code and desired mounting conditions

(reflow method, temperature and times).

PACKAGE DIMENSIONS

TQFP100-P-1414-0.50-K

Package material

Lead frame material

Pin treatment

Solder plate thickness

Package weight (g)

Epoxy resin

42 alloy

Solder plating

5 mm or more

0.55 TYP.

Mirror finish