° Semiconductor

MSM6895/6896

1/43

° Semiconductor

MSM6895/6896

Multi-Function PCM CODEC

GENERAL DESCRIPTION

The MSM6895/MSM6896, developed especially for low-power and multi-function applications

in ISDN telephone terminals, are single +5 V power supply CODEC LSI devices. The devices

consist of the analog speech paths directly connectable to a handset, the calling circuit directly

connectable to a piezosounder, the push-button key scanning interface between push buttons

and control processors, the dial tone generator, the B-channel interface, the CODEC, and the

processor interface. The functions can be controlled via the 8-bit data bus.

FEATURES

∑ Single +5 V Power Supply

∑ Low Power Dissipation

Power ON Mode

: 20 mW Typ. 53 mW Max.

CODEC Power Down Mode

: 10 mW Typ. 21 mW Max.

∑ In compliance with ITU-T's companding law

m-law

: MSM6895

A-law

: MSM6896

∑ Transmission clocks

Continuous CLK

: 64, 128, 256 kHz

Burst CLK

: 192, 384, 768, 1536, 2048 kHz

∑ Built-in PLL

∑ Built-in Reference Voltage Supply

∑ Ringing Tone

: Controlled by processor, 9 modes

∑ Ringing Tone Combination

: Controlled by processor, 6 modes

∑ Information Tone

: Controlled by processor, 9 modes

∑ Built-in PB Tone Generator

∑ B-Channel Selectable

∑ General Latch Output for Speech path Control

: 4 bits

∑ Watchdog Timer

: 500 ms

∑ Key Scanning I/O

Output

: 5 bits

Input

: 8 bits

∑ Direct Connection to Handset

∑ Built-in Preamplifier for Loudspeaker

∑ Handfree Interface

∑ Digital and Analog Interface for the phone-conference speech paths

∑ Package:

80-pin plastic QFP (QFP80-P-1420-0.80-BK)

(Product name : MSM6895GS-BK)

(Product name : MSM6896GS-BK)

E2U0022-28-81

This version: Aug. 1998

Previous version: Nov. 1996

° Semiconductor

MSM6895/6896

2/43

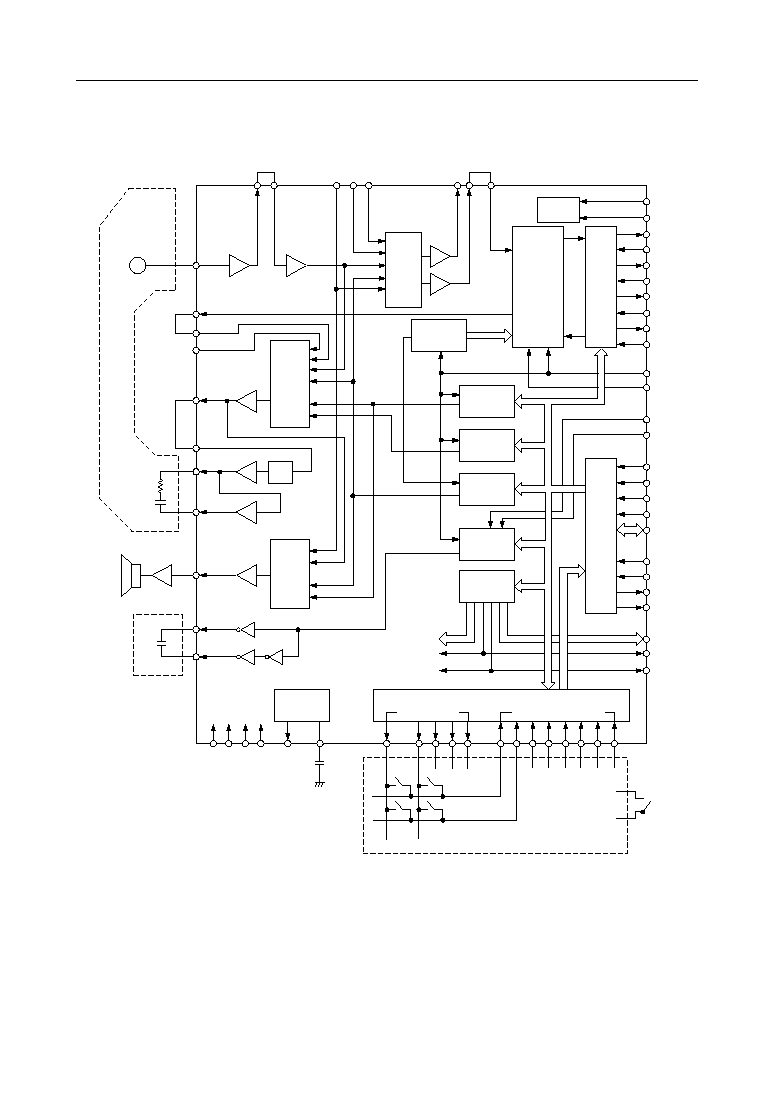

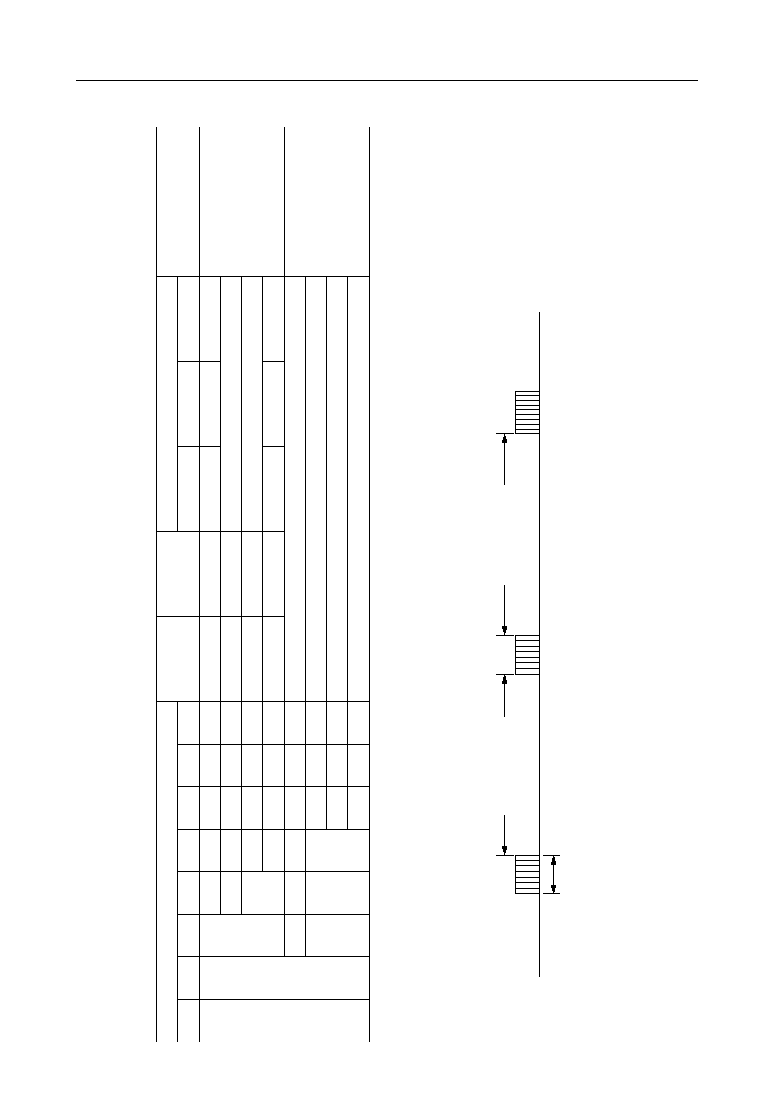

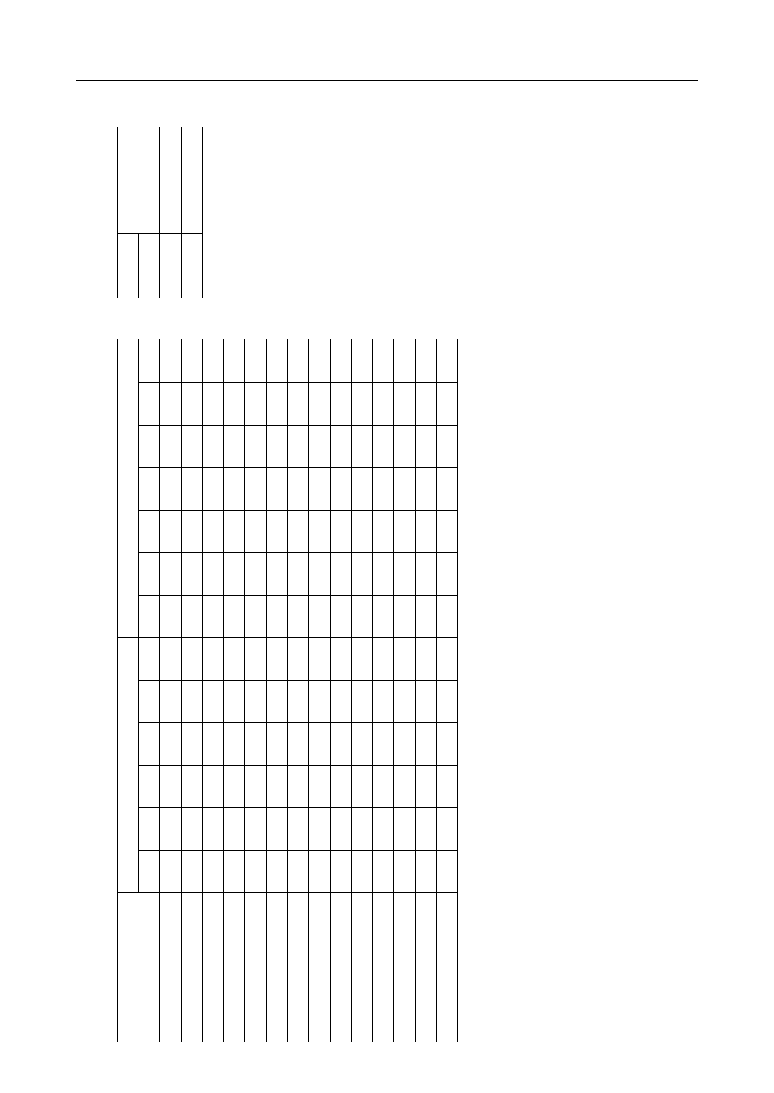

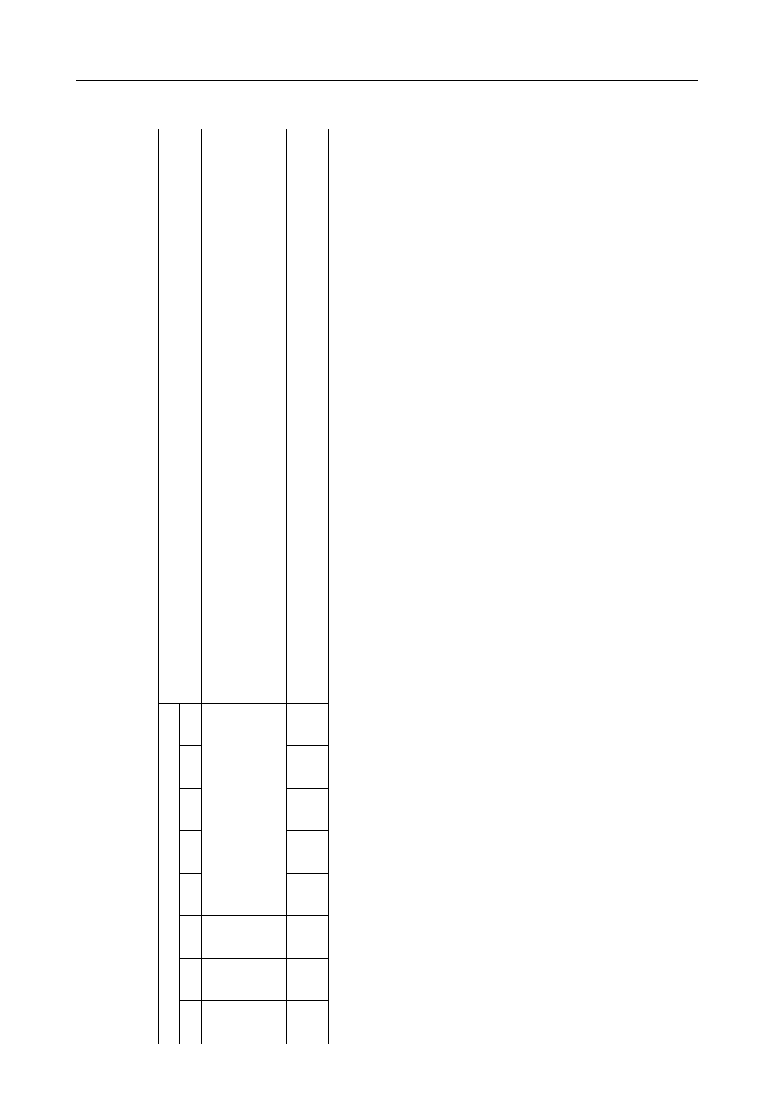

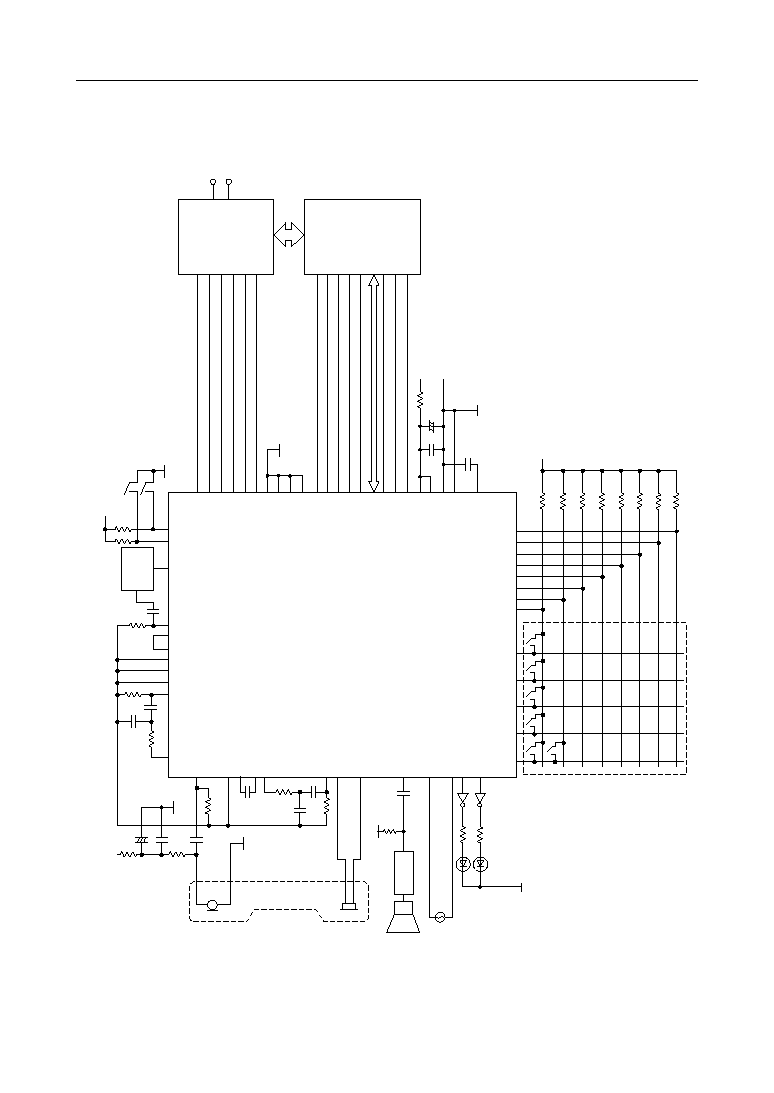

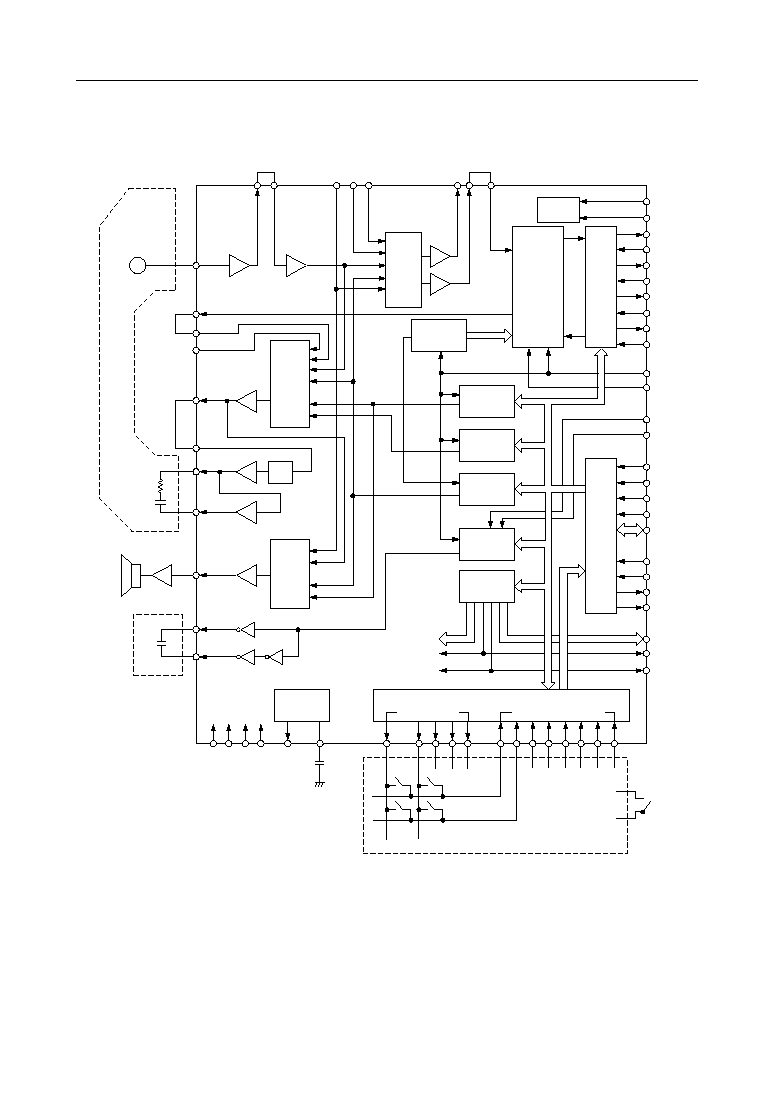

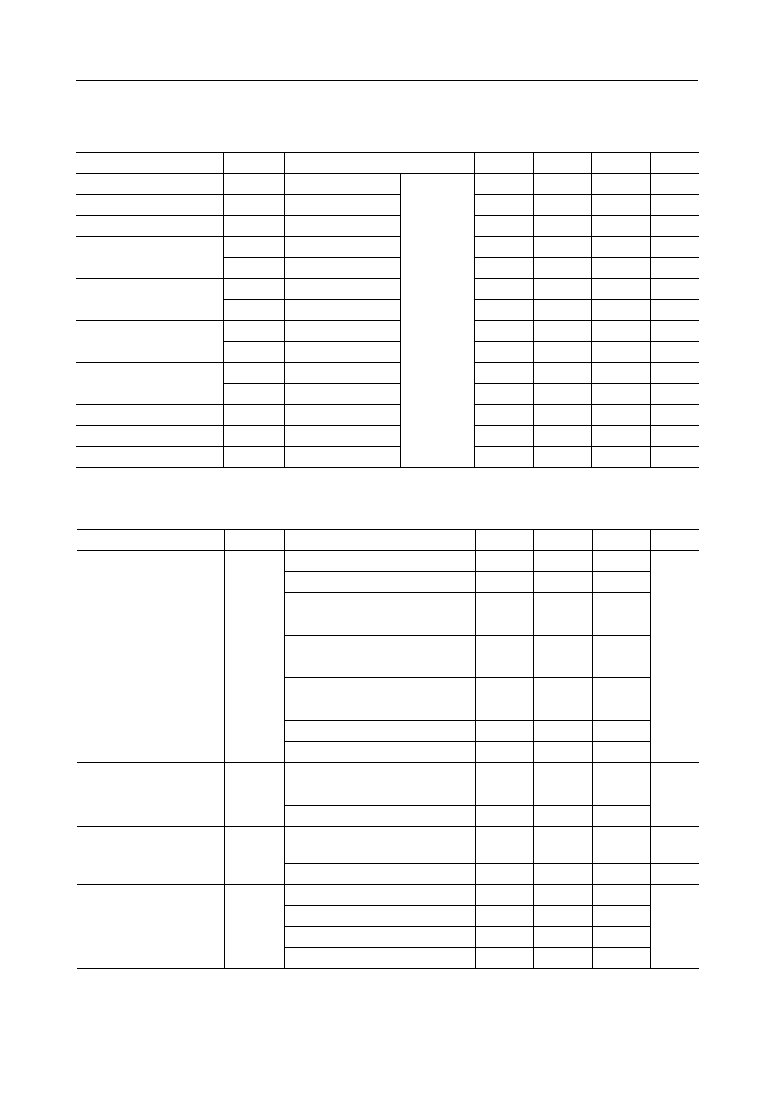

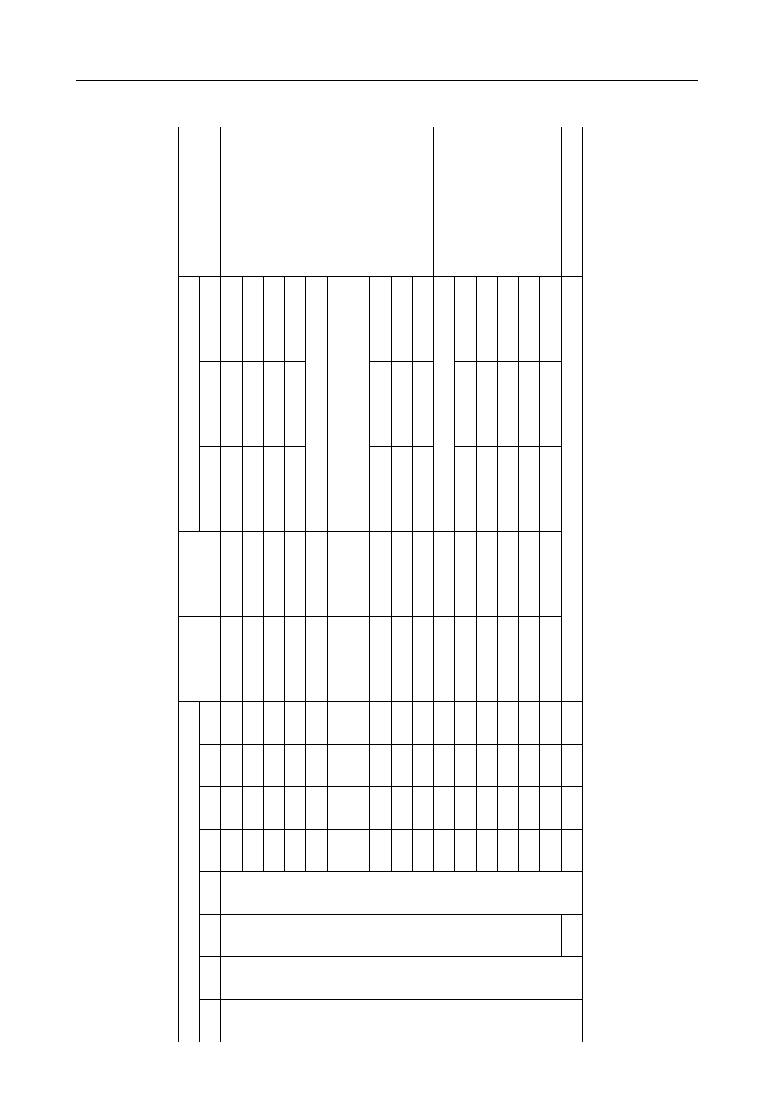

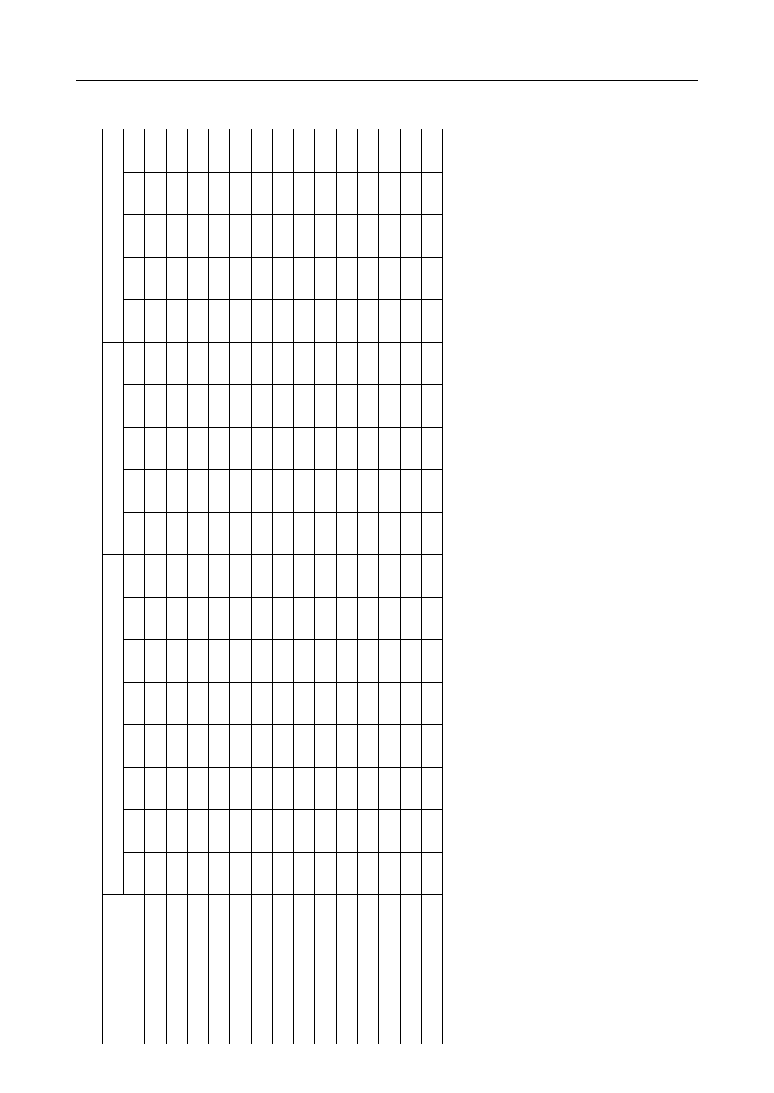

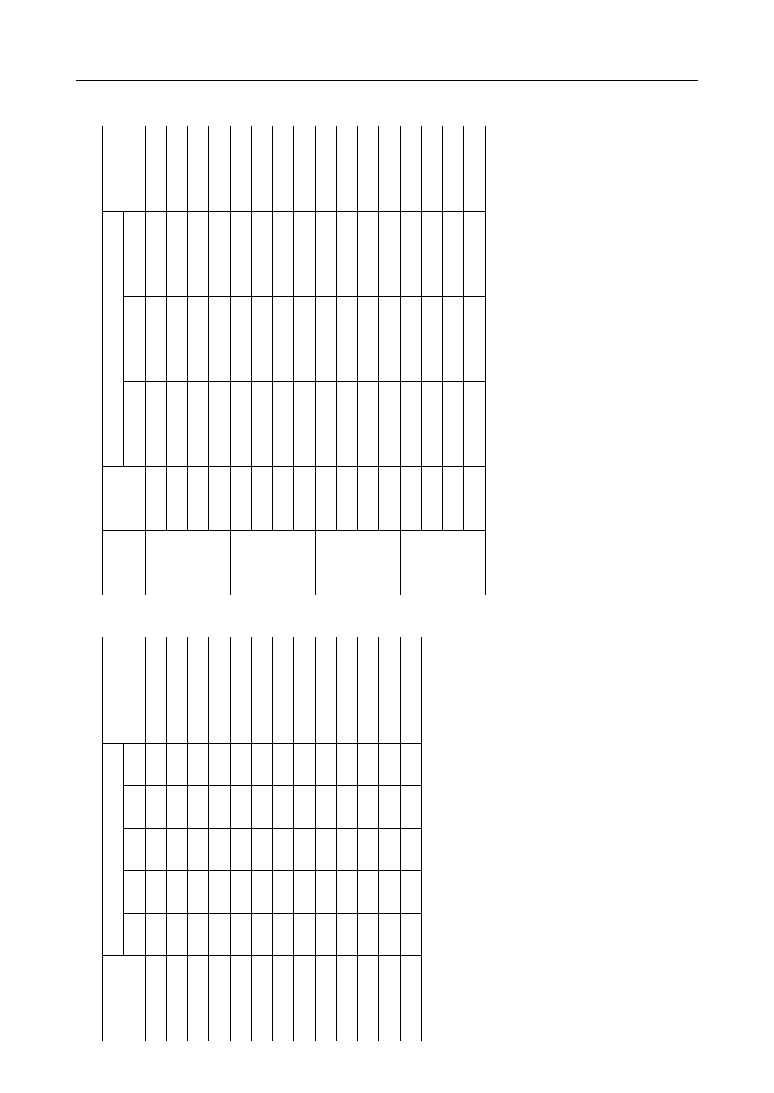

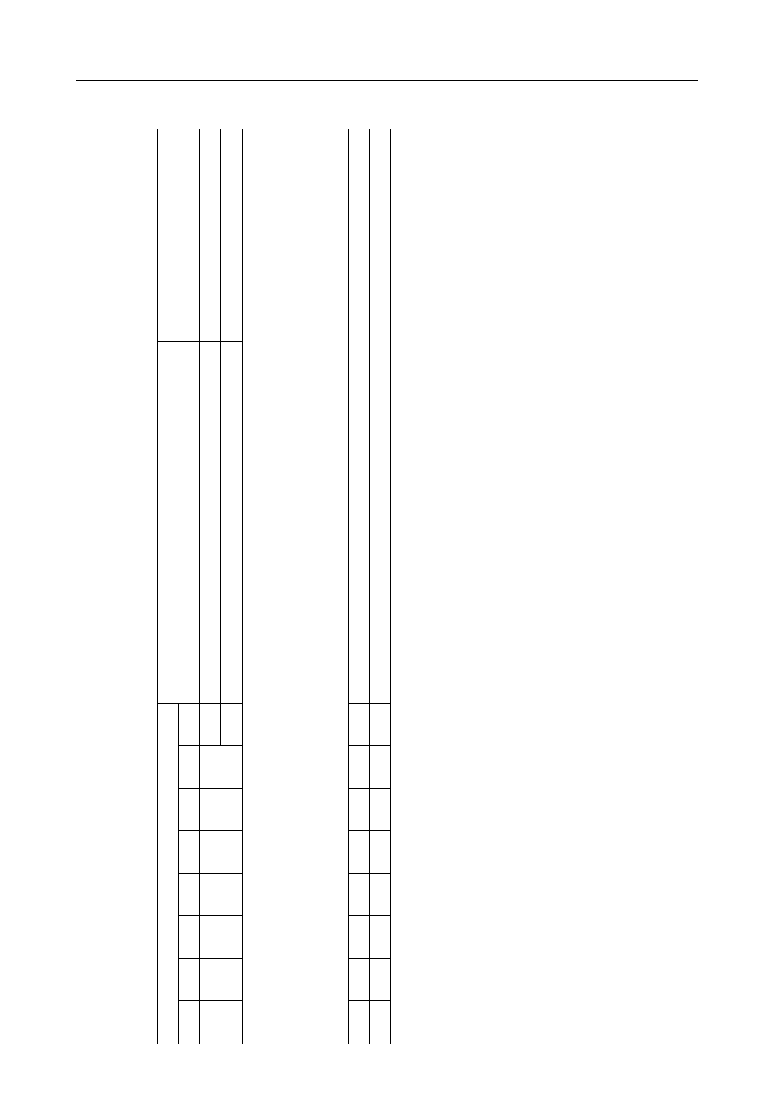

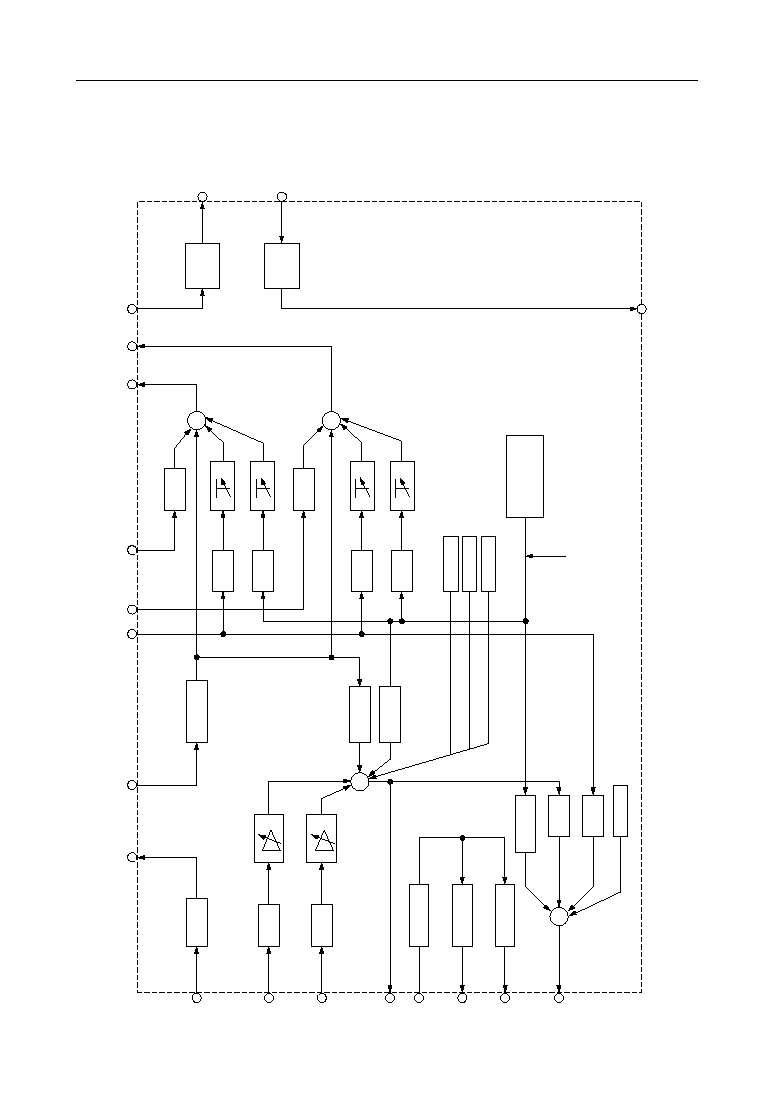

BLOCK DIAGRAM

M

TPAO

MLDY

TPBI

TMX1I

TMX2I

T2O

T1O

CAI

B1T

B1R

B2T

B2R

BR1

BT1

BR2

BT2

CK8

CK64

WR

SW0

SW1

8K

64K

RD

CE

RESET

8BIT

Data Bus

AD0

AD1

INTT

TIME

4BIT

LOSS

LML

B1

B2

PI0 to

PI7

7

6

5

4

3

2

1

0

4

3

2

1

0

PO0 ~

PO4

KEY INTF.

PUSH-BOTTON SWITCH

KEY DATA INPUT

SCANNING

OUTPUT

SGGEN

VSGC

VSG

VD VAG VDG

VA

SA0

HANDSET

SPO

RMO1

RMO0

RMI

RPO

R2I

R1I

SW

&

MIX

TPAI

SW

CONT.

SW

&

MIX

SW

LATCH

S-TONE

R-TONE

F-TONE

GEN

GEN

GEN

DTMF TONE

GEN

PLL

AIN

AOUT

CODEC

SW

&

MIX

CAO

SA1

+

≠

LA ~

LD

SP

BUZZER

SWITCH

HOOK

MPU INTF.

CHANNEL SELECTOR

TEST

CK1536

TEST

° Semiconductor

MSM6895/6896

3/43

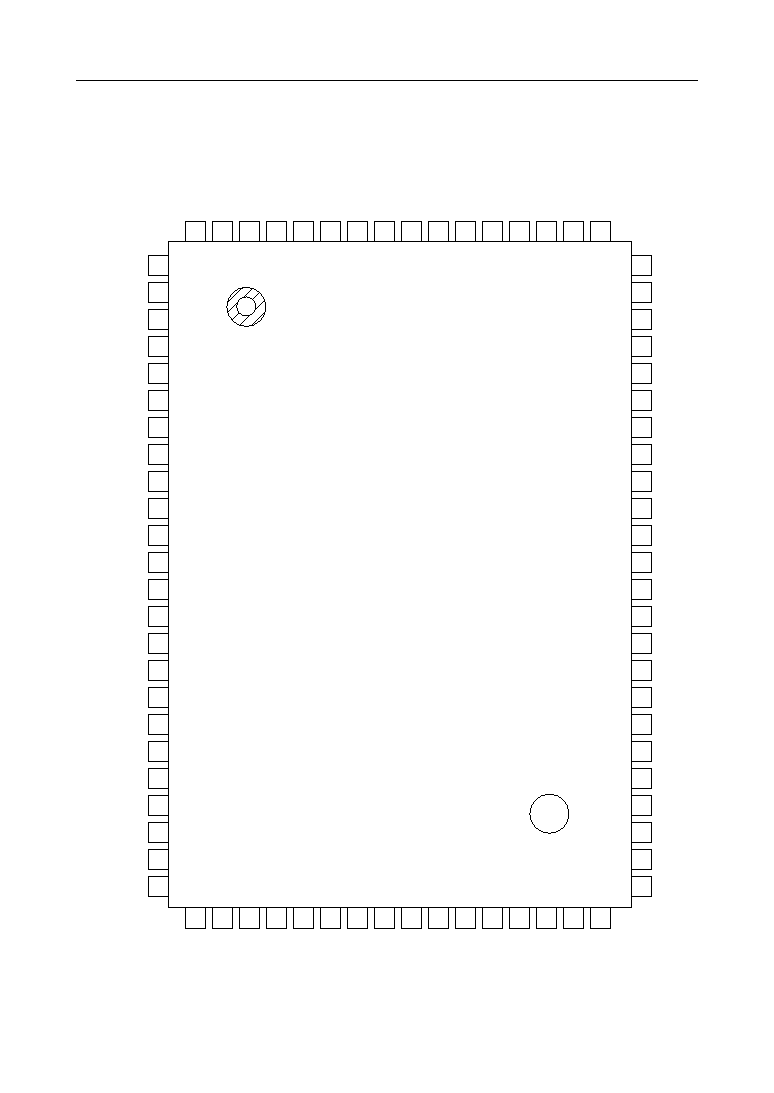

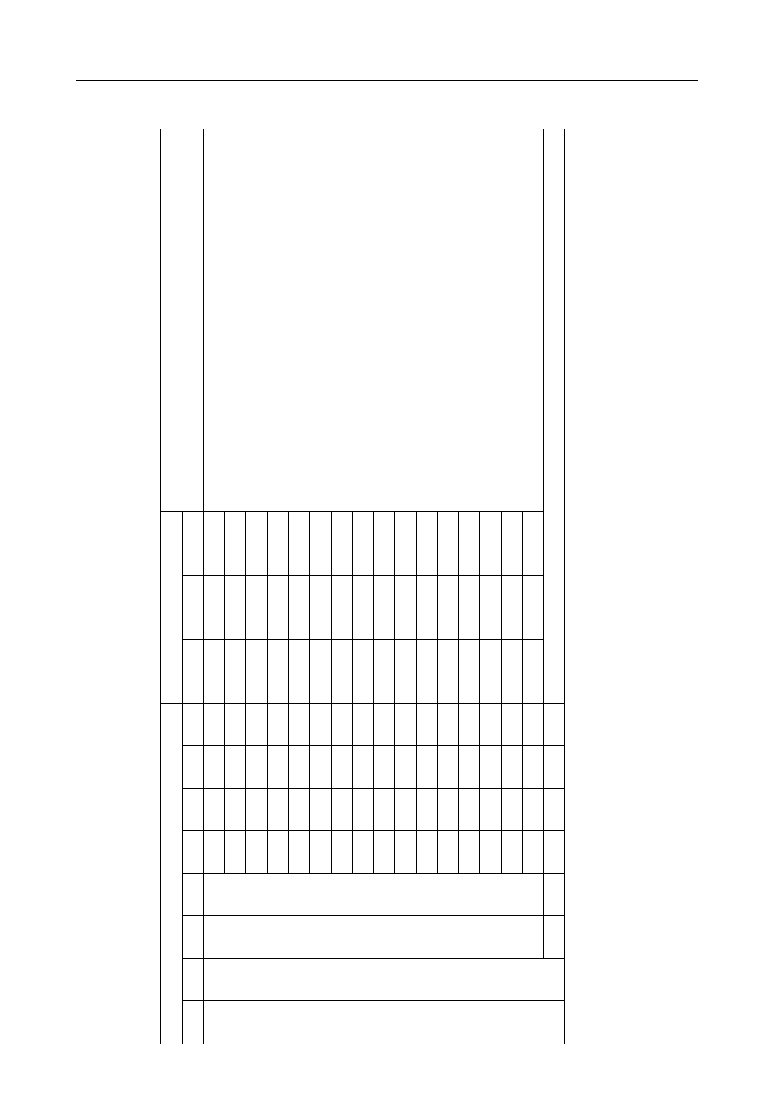

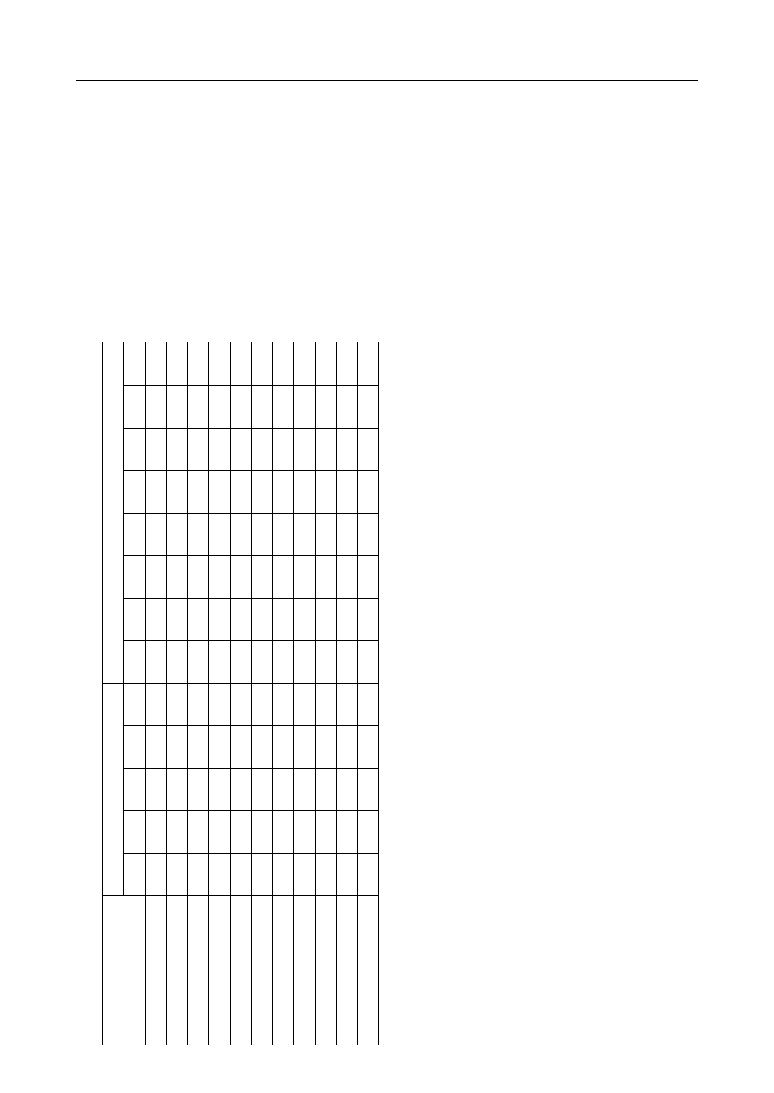

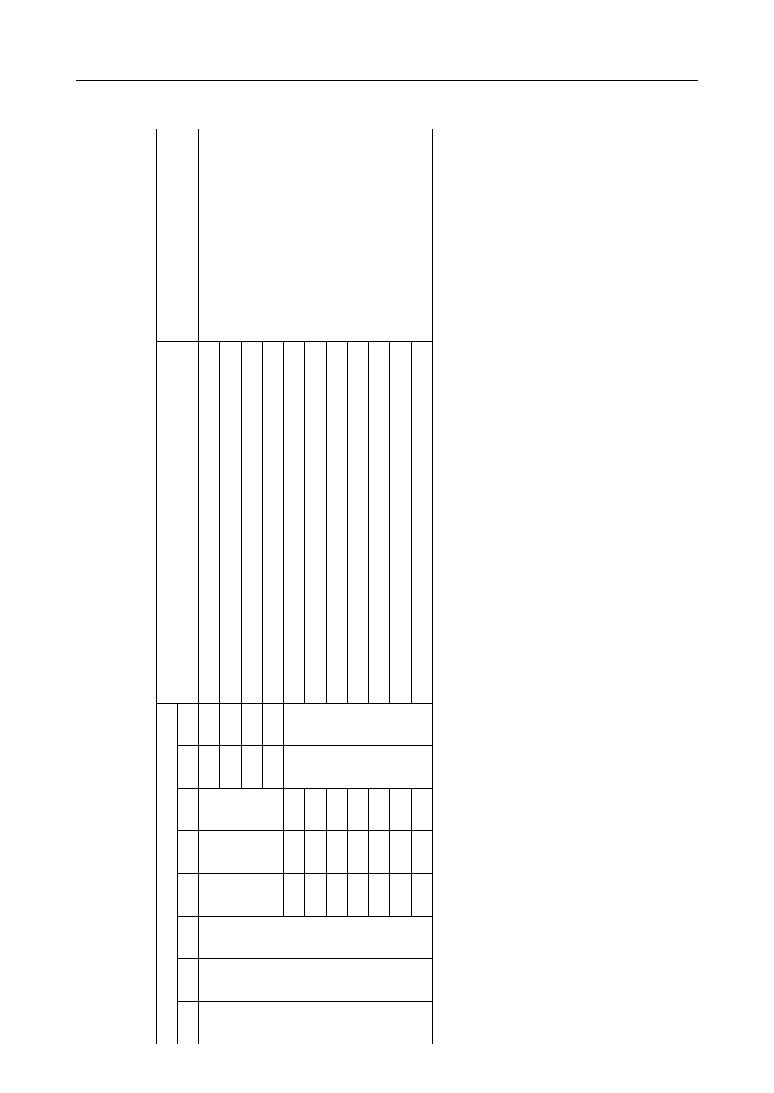

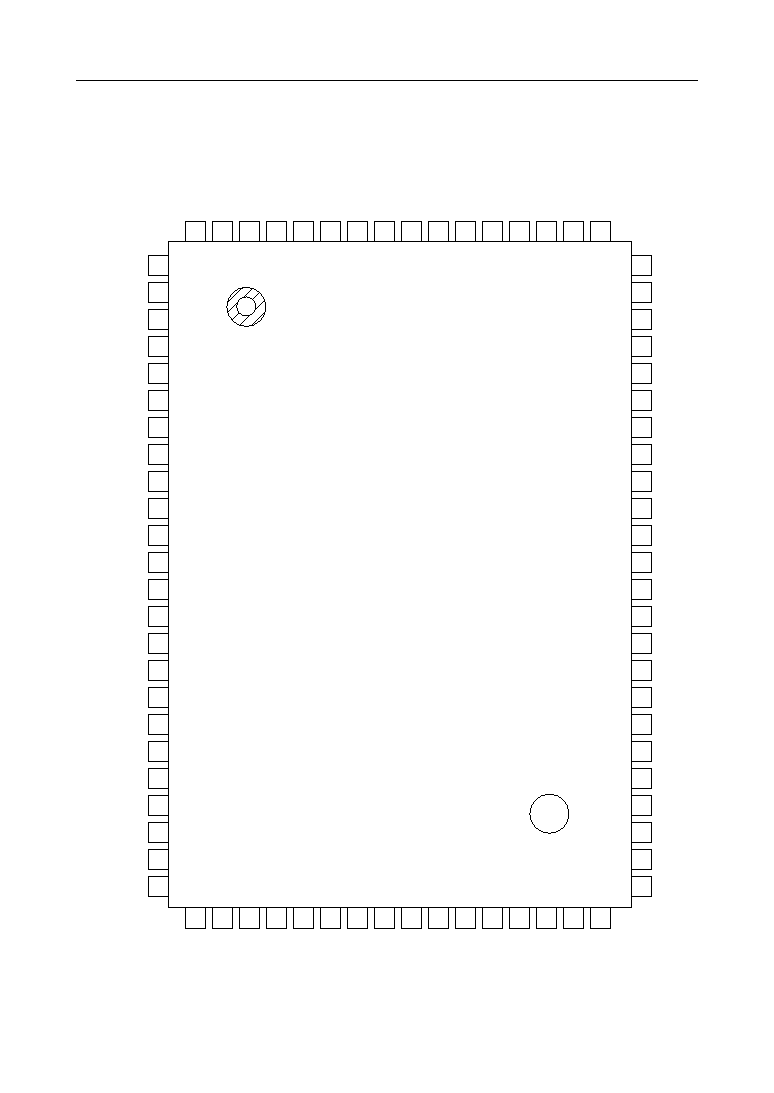

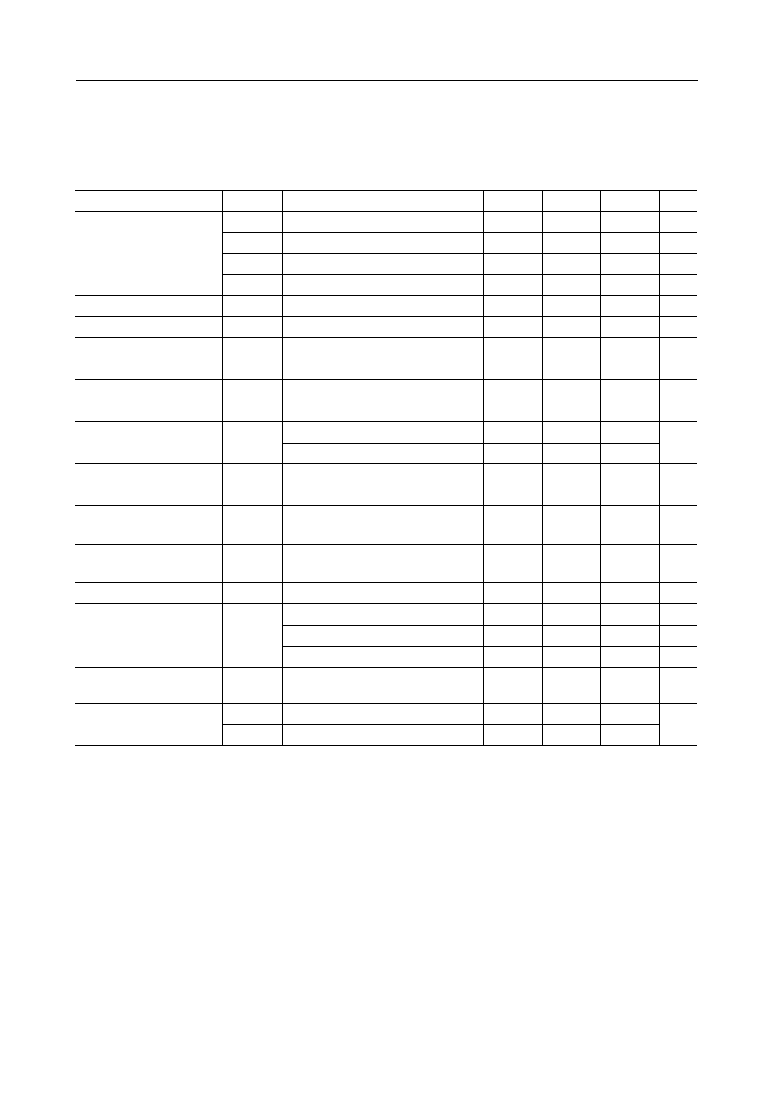

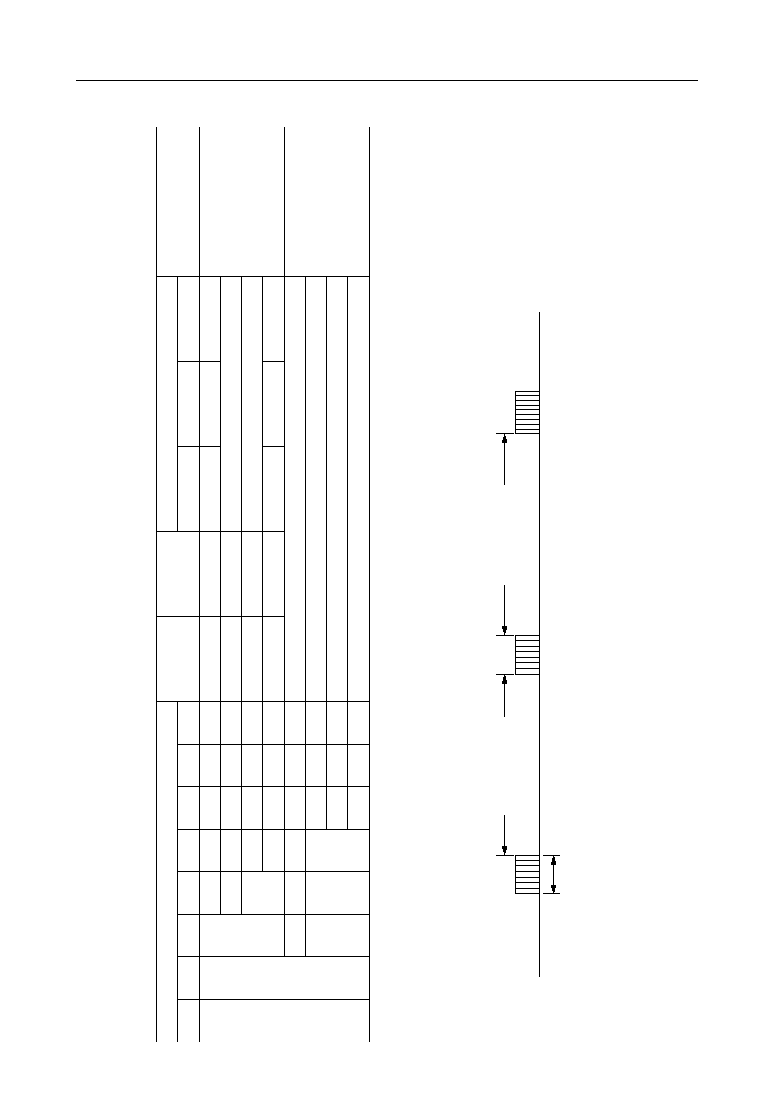

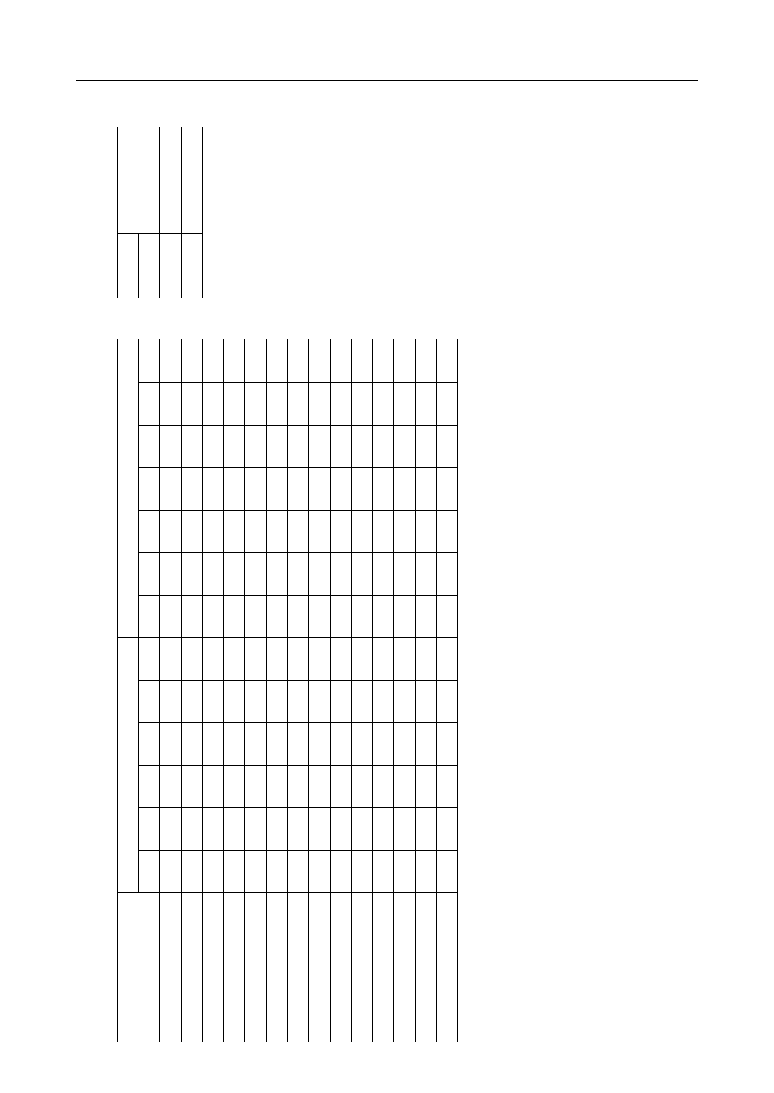

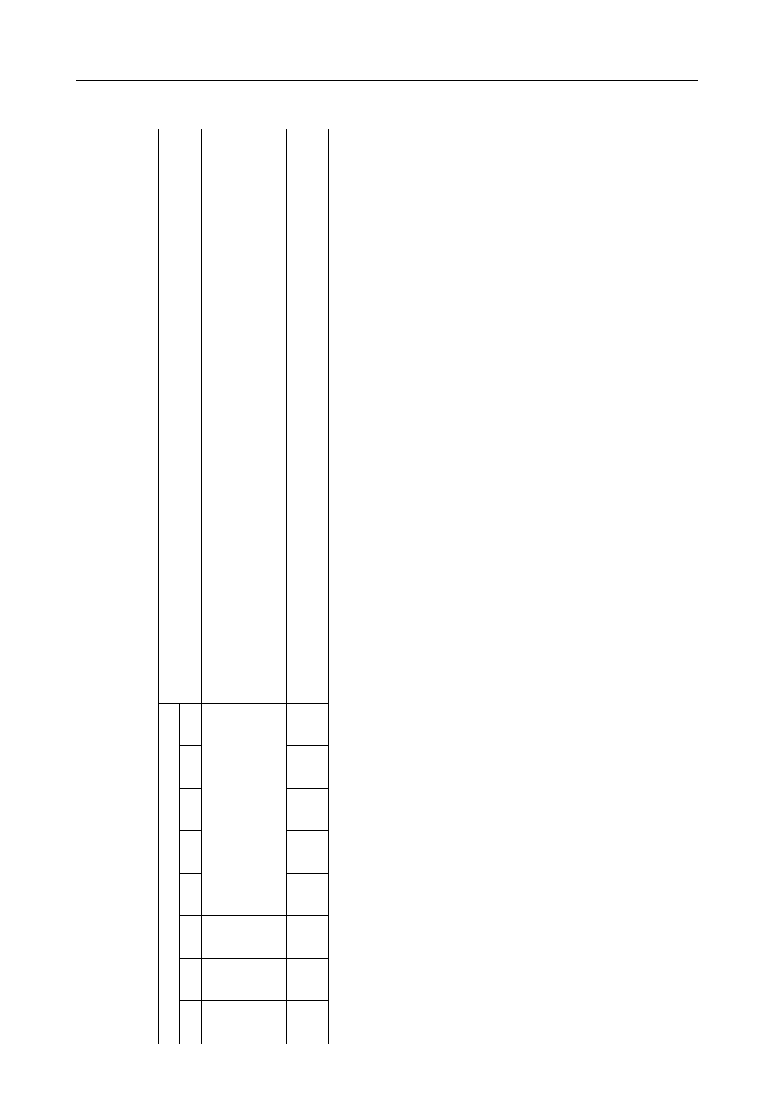

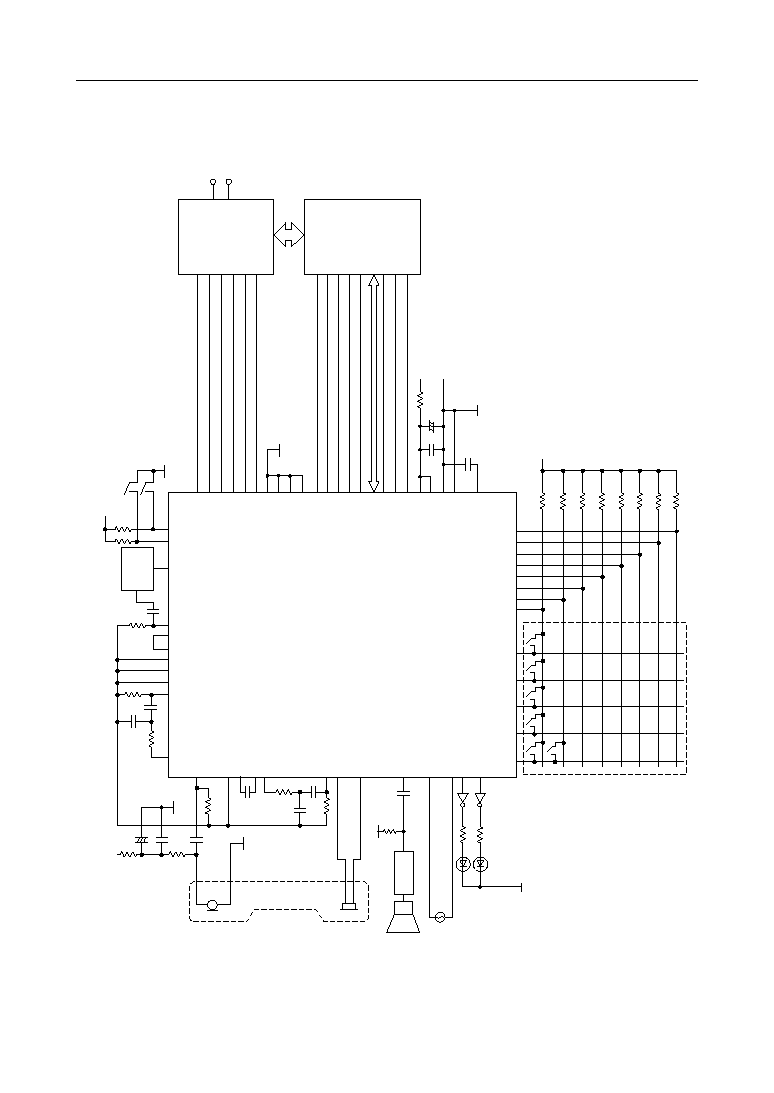

PIN CONFIGURATION (TOP VIEW)

1

24

64

41

LB

LC

LD

SW0

SW1

VDG

VAG

SA0

SA1

NC

RM1

NC

RMO1

SPO

RPO

R2I

R1I

NC

NC

TMX2I

TPBI

VD

AD0

DB7

DB6

DB5

DB4

DB3

DB2

DB1

INTT

PI7

PI5

PI4

PI3

PI2

PI1

PI0

PO4

PO3

PO1

PI6

PO2

VSG

TPAO

T2O

NC

NC

VA

VSGC

TEST

CK8

LML

TIME

BR2

BR1

BT2

BT1

B1R

B1T

WR

LA

RESET

B2R

B2T

CE

RD

AD1

NC : No connect pin

RMO0

MLDY

TMX1I

TPAI

T1O

CAI

CA0

CK1536

CK64

LOSS

PO0

DB0

2

3

4

5

6

7

8

9

10

11

12

14

15

16

17

18

19

20

21

23

13

22

63

62

61

60

59

58

57

56

55

54

53

51

50

49

48

47

46

45

44

42

52

43

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

80-Pin Plastic QFP

° Semiconductor

MSM6895/6896

4/43

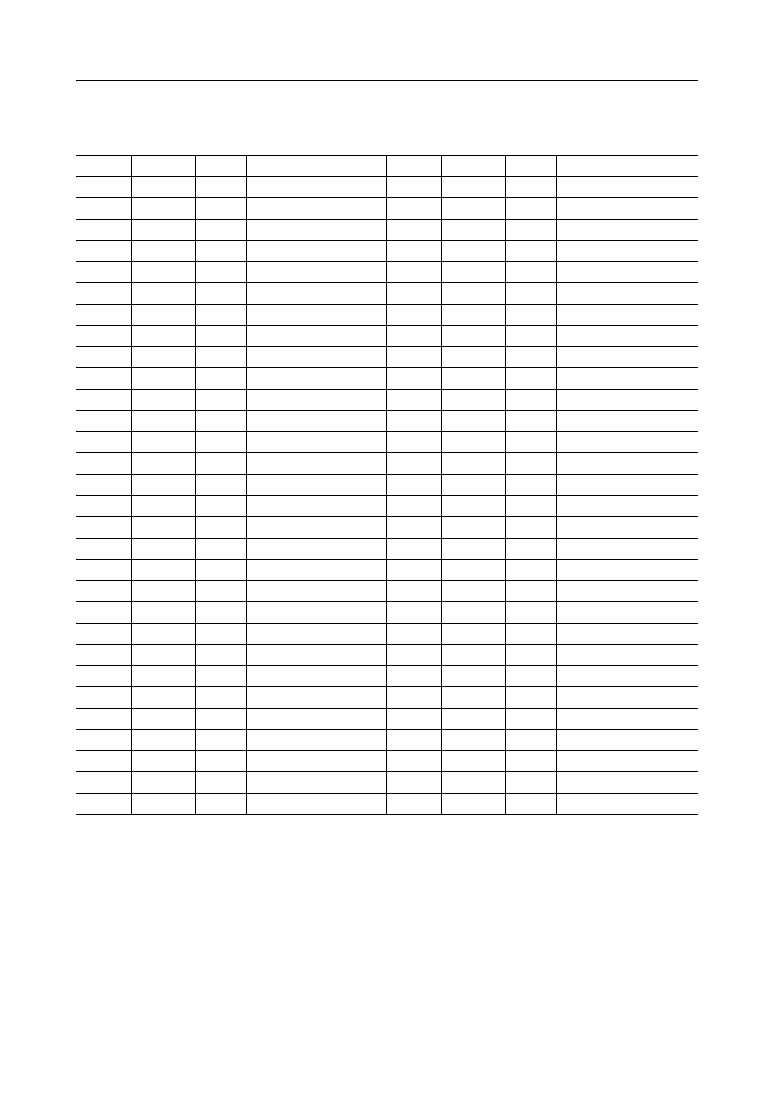

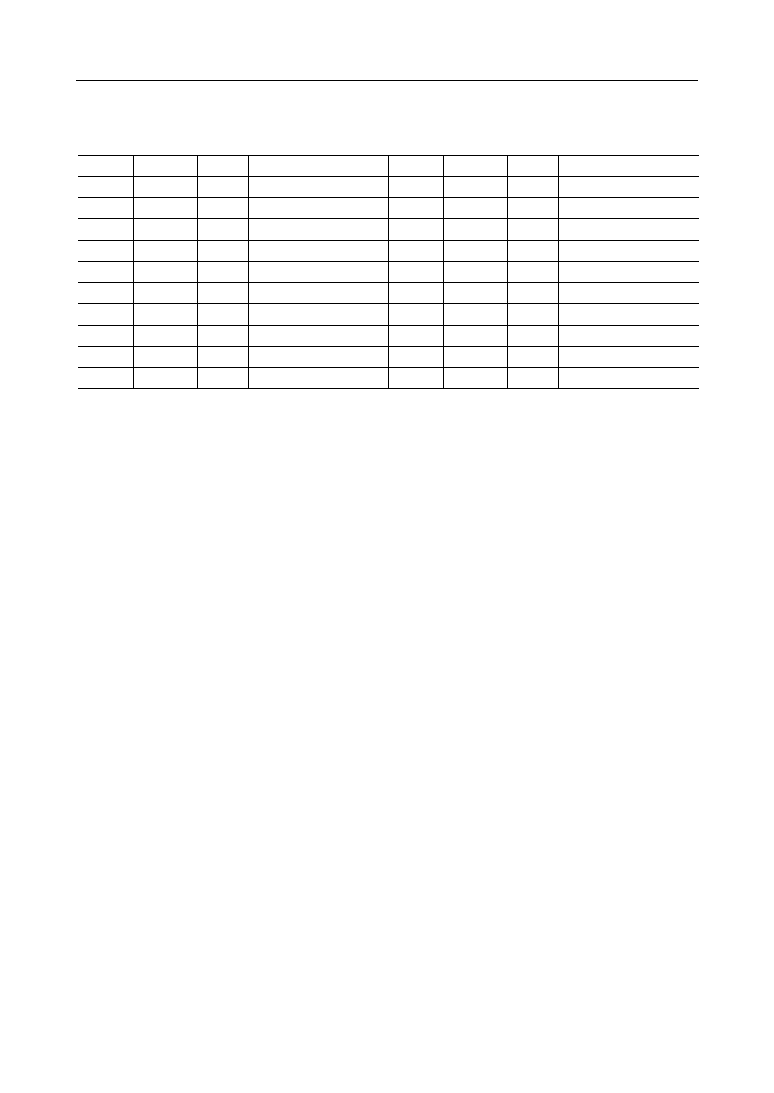

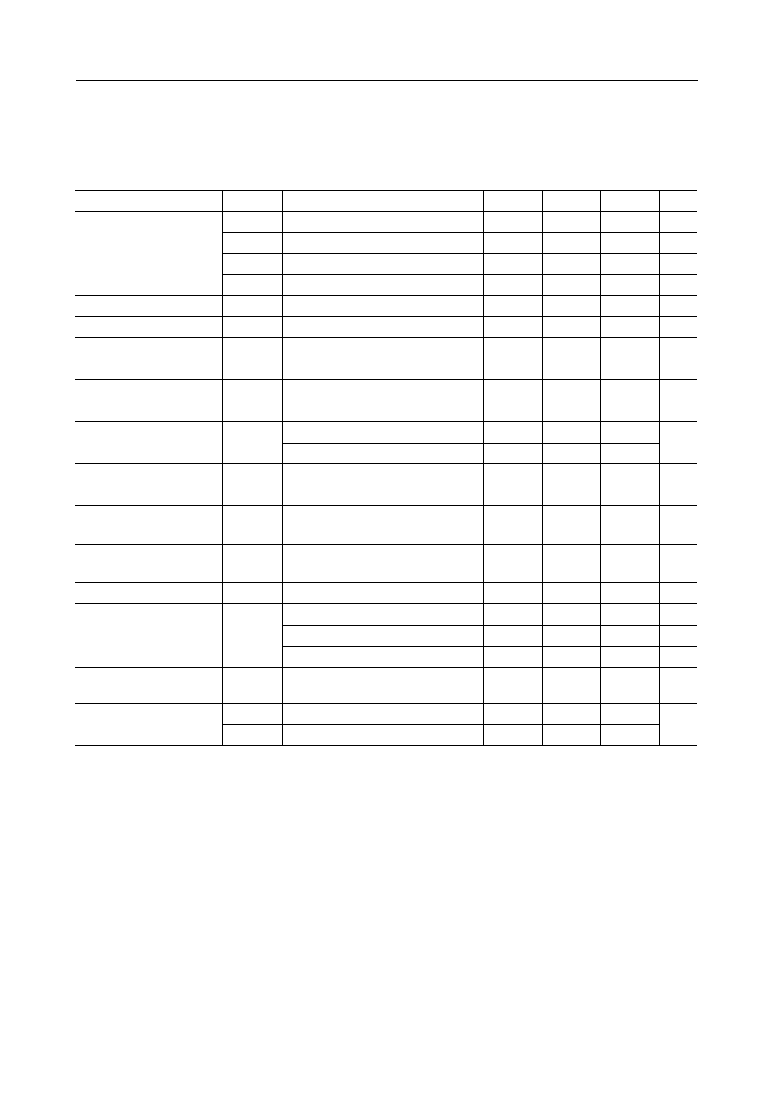

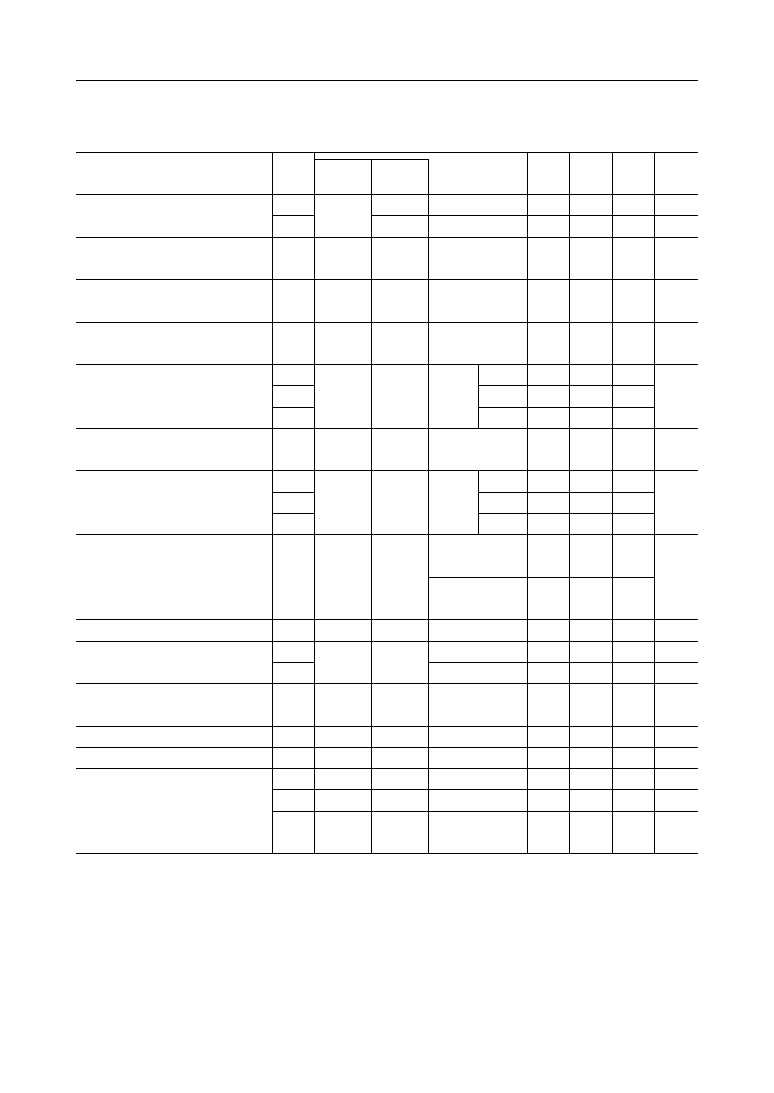

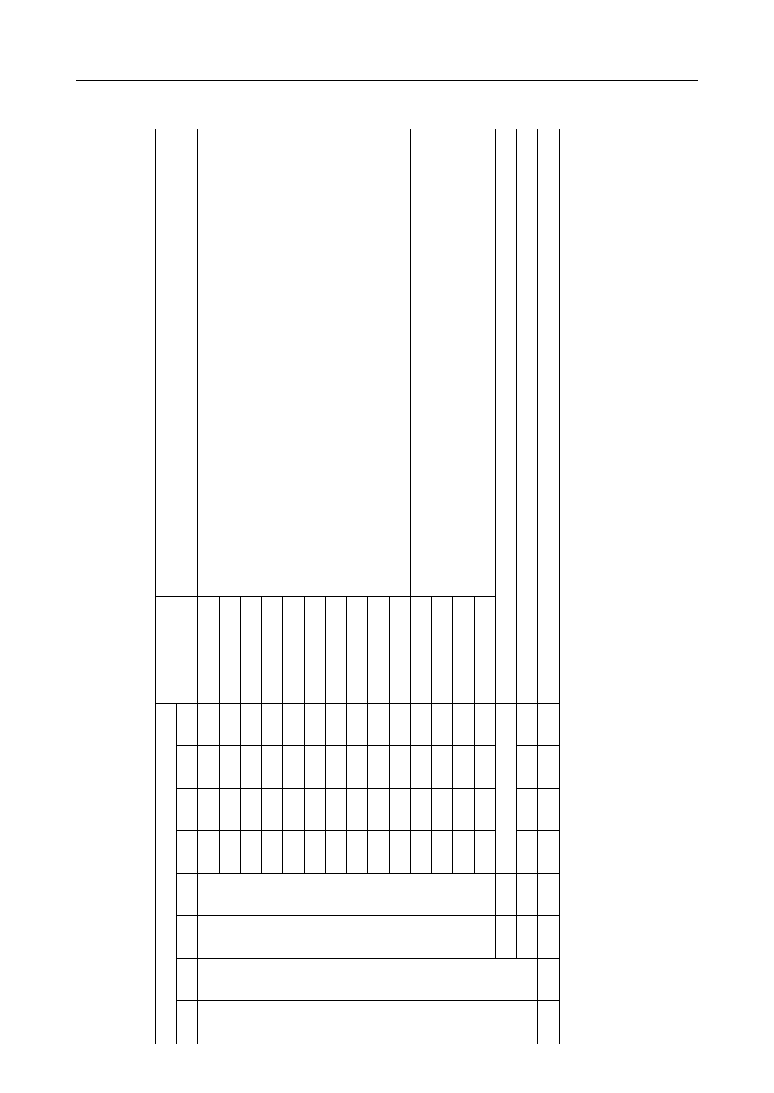

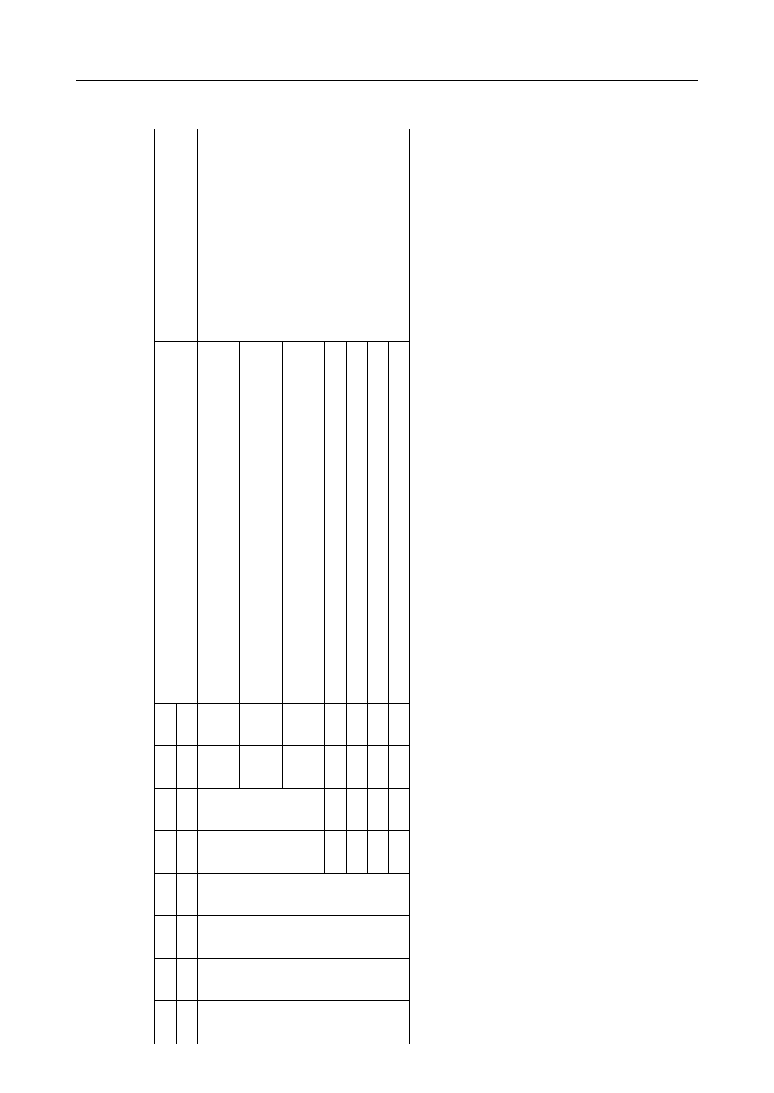

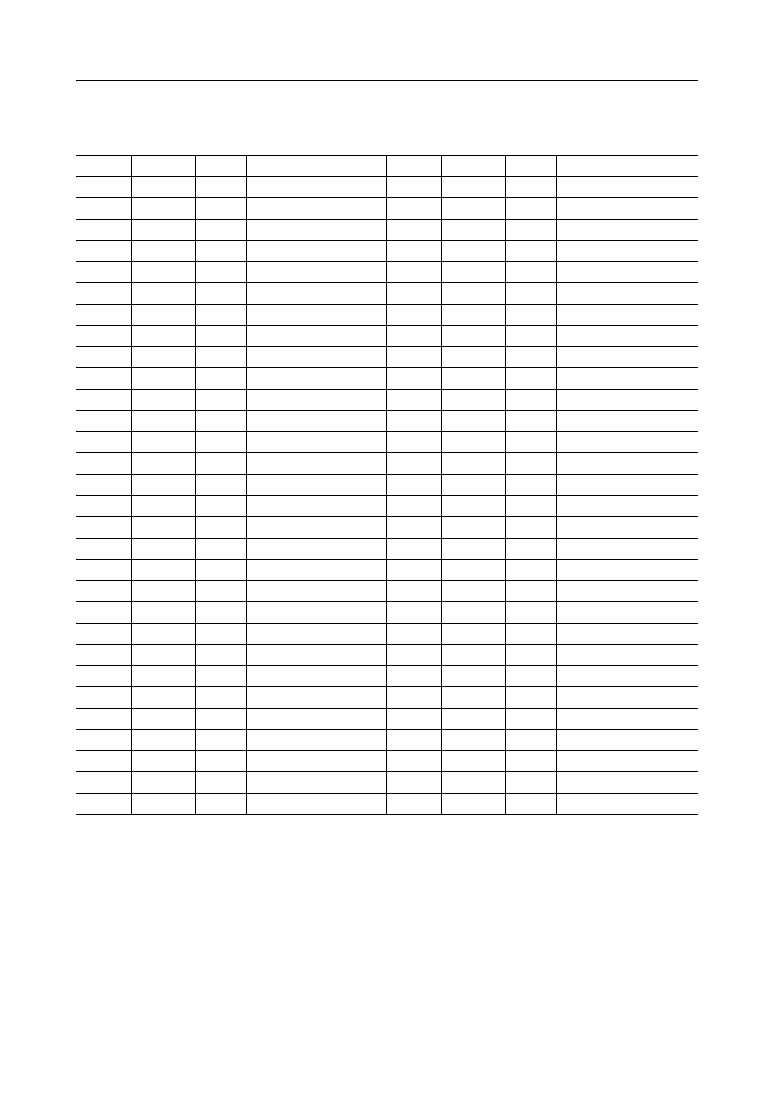

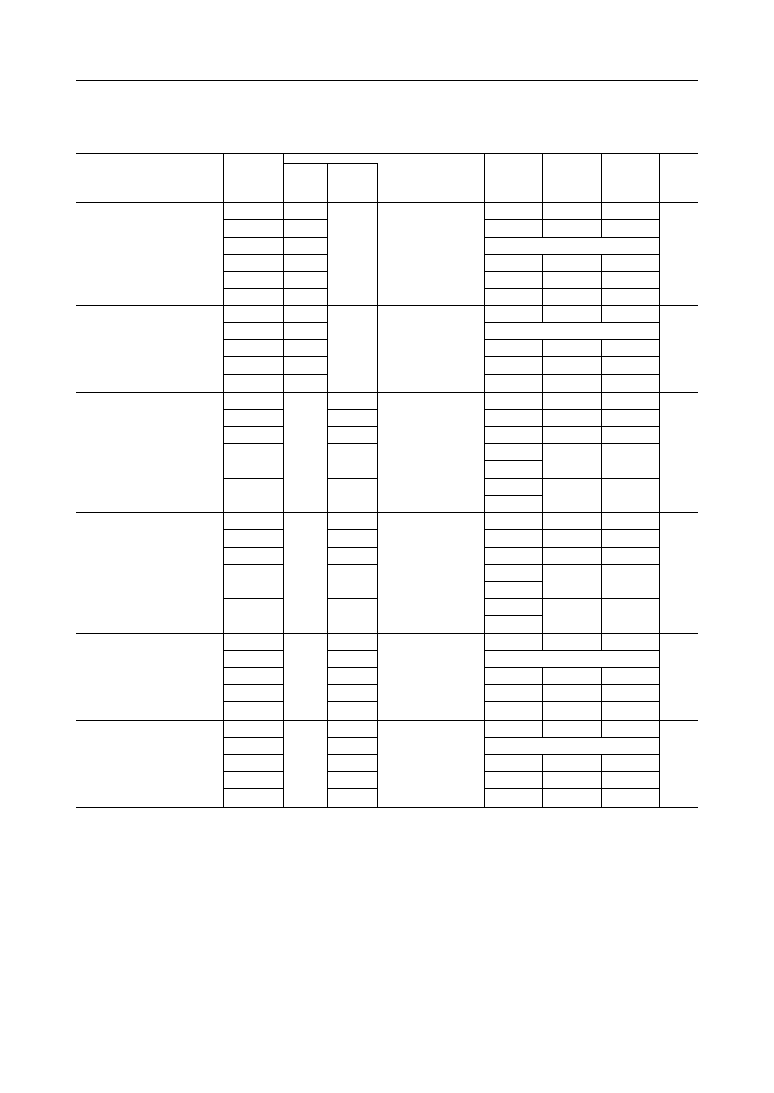

PIN DESCRIPTION

Pin

Symbol

Type

Description

1

LB

DO

Data Latch Output B

2

LC

DO

Data Latch Output C

3

LD

DO

Data Latch Output D

4

SW0

DI

Sounder Tone Select (1)

5

SW1

DI

Sounder Tone Select (2)

6

VDG

--

Digital Ground

7

VAG

--

Analog Ground

8

SA0

DO

Sounder Output (+)

9

SA1

DO

Sounder Output (≠)

10

--

--

NC

11

RMI

AI

Receive Main Amp Input

12

--

--

NC

13

RMO0

AO

Receive MainAmp Output (+)

14

RMO1

AO

Receive MainAmp Output (≠)

15

SPO

AO

Speaker Pre-Amp Output

16

RPO

AO

Receive Pre-Amp Output

17

R2I

AI

Receive Addition Signal Input

18

R1I

AI

Receive Signal Input

19

--

--

NC

20

--

--

NC

21

TMX2I

AI

Transmit Addtion Signal Input (2)

22

MLDY

AI

Hold Tone Input

23

TPBI

AI

Transmit Pre-Amp (B) Input

24

TMX1I

AI

Transmit Addtion Signal Input (1)

25

TPAI

AI

Transmit Pre-Amp (A) Input

26

VSG

AO

Signal Ground

27

TPAO

AO

Transmit Pre-Amp (A) Output

28

T1O

AO

Transmit Signal Output (1)

29

T2O

AO

Transmit Signal Output (2)

30

--

--

NC

Pin

Symbol

Type

Description

31

--

--

NC

32

VA

--

+5 V Analog Power Supply

33

CAI

AI

Analog Signal Input to CODEC

34

VSGC

AO

Bypass Capacitor for Signal Ground

35

CAO

AO

Analog Signal Output from CODEC

36

TEST

DI

Control Input for Test

37

CK1536

DI

Clock Input for Test

38

CK64

DI

Transmission Colck Input

39

CK8

DI

Frame Synchronous Clock Input

40

LOSS

DO

Howler Tone Control Signal

41

PO0

DO

Key Scanning Signal Output (0)

42

PO1

DO

Key Scanning Signal Output (1)

43

PO2

DO

Key Scanning Signal Output (2)

44

PO3

DO

Key Scanning Signal Output (3)

45

PO4

DO

Key Scanning Signal Output (4)

46

PI0

DI

Key Scanned Data Input (0)

47

PI1

DI

Key Scanned Data Input (1)

48

PI2

DI

Key Scanned Data Input (2)

49

PI3

DI

Key Scanned Data Input (3)

50

PI4

DI

Key Scanned Data Input (4)

51

PI5

DI

Key Scanned Data Input (5)

52

PI6

DI

Key Scanned Data Input (6)

53

PI7

DI

Key Scanned Data Input (7)

54

INTT

DO

Interrupt Output

55

DB0

I/O

Data Bus (0)

56

DB1

I/O

Data Bus (1)

57

DB2

I/O

Data Bus (2)

58

DB3

I/O

Data Bus (3)

59

DB4

I/O

Data Bus (4)

60

DB5

I/O

Data Bus (5)

° Semiconductor

MSM6895/6896

5/43

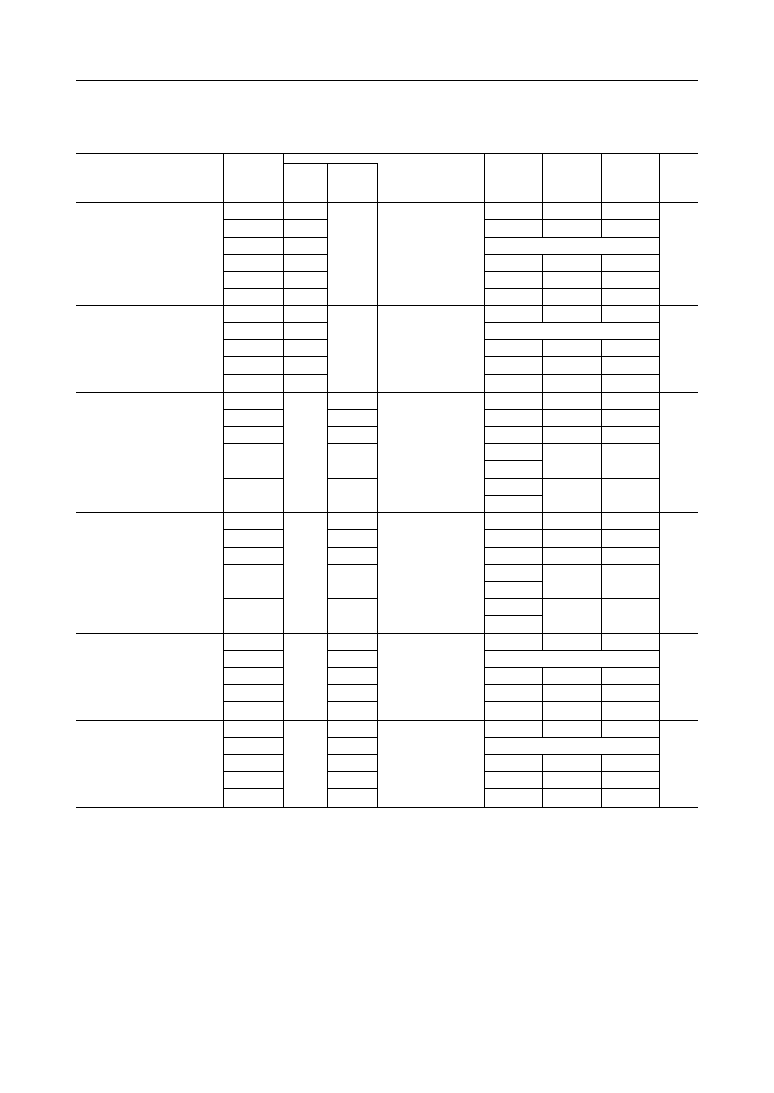

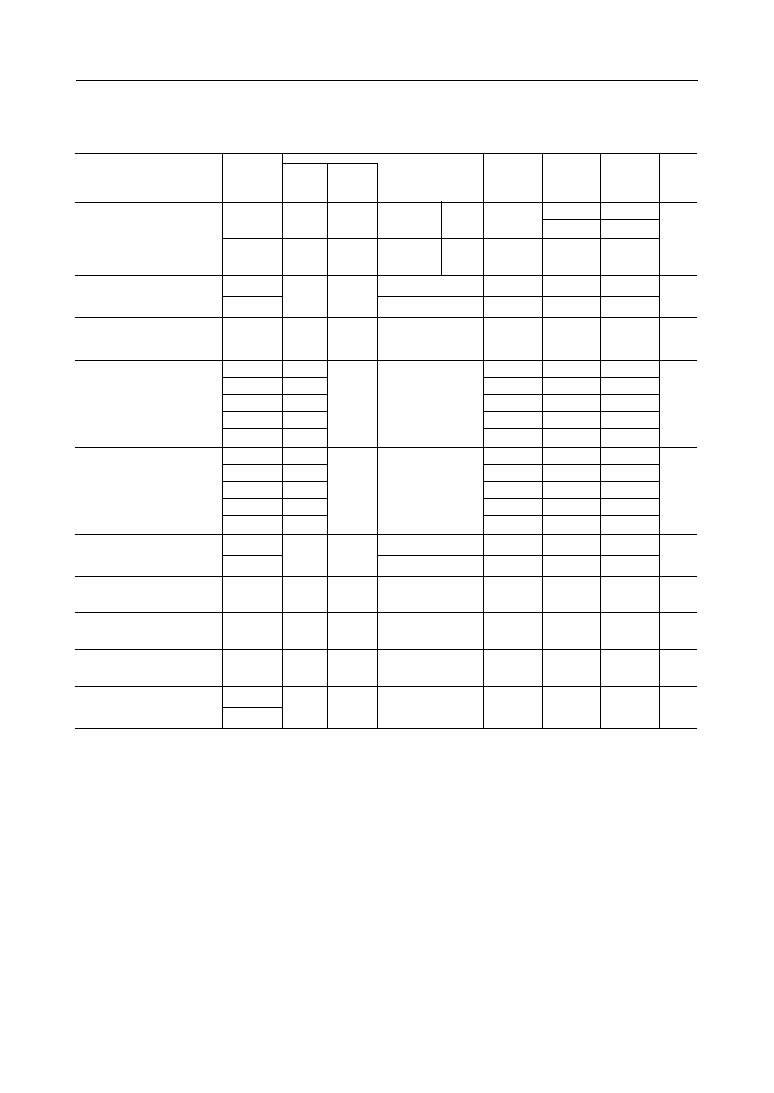

PIN DESCRIPTION (Continued)

Pin

Symbol

Type

Description

61

DB6

I/O

Data Bus (6)

62

DB7

I/O

Data Bus (7)

63

AD0

DI

Address Data (0)

64

VD

--

+5 V Digital Power Supply

65

AD1

DI

Address Data Input (1)

66

WR

DI

Write Signal Input

67

RD

DI

Read Signal Input

68

CE

DI

Chip Enable

69

B1T

DO

B1 Channel Transmit Output

70

B2T

DO

B2 Channel Transmit Output

Pin

Symbol

Type

Description

71

B1R

B1 Channel Recive Input

72

B2R

B2 Channel Recive Input

73

BT1

B Channel Selector Transmit Data (1)

74

BT2

B Channel Selector Transmit Data (2)

75

BR1

B Channel Selector Receive Data (1)

76

BR2

B Channel Selector Receive Data (2)

77

RESET

Reset Input

78

TIME

Timer Output

79

LML

Hold Tone Control Output

80

LA

Data Latch Output (A)

DI

DI

DI

DI

DO

DO

DI

DO

DO

DO

° Semiconductor

MSM6895/6896

6/43

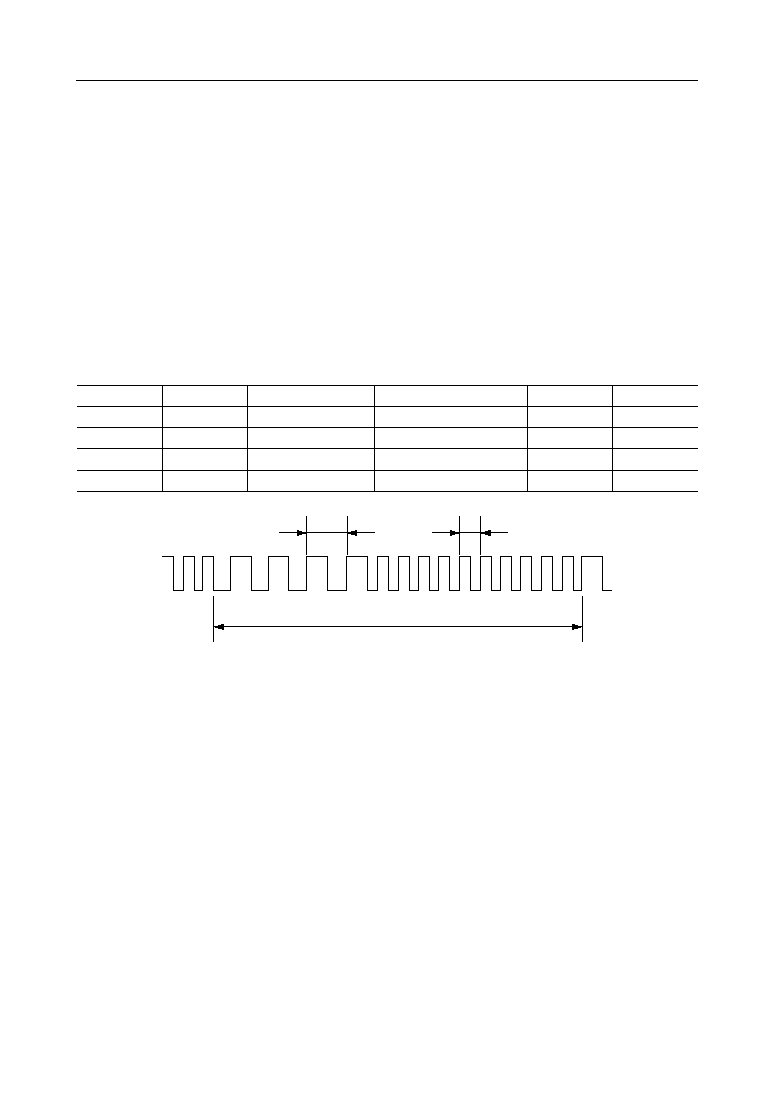

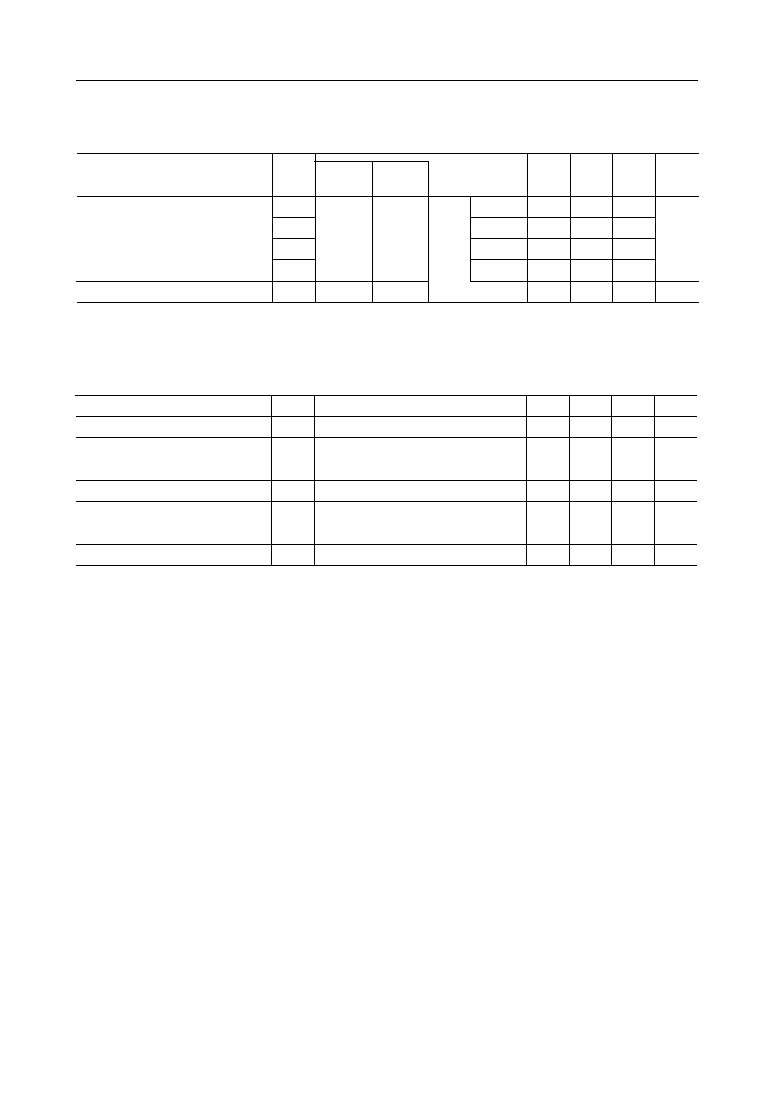

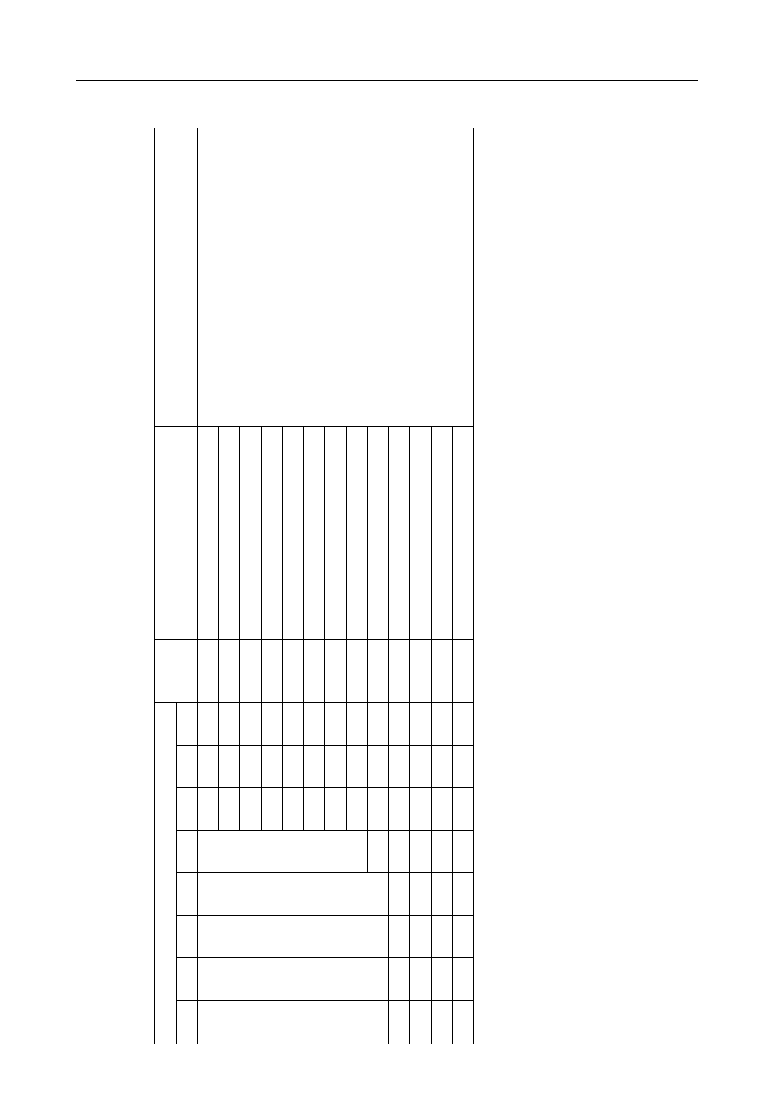

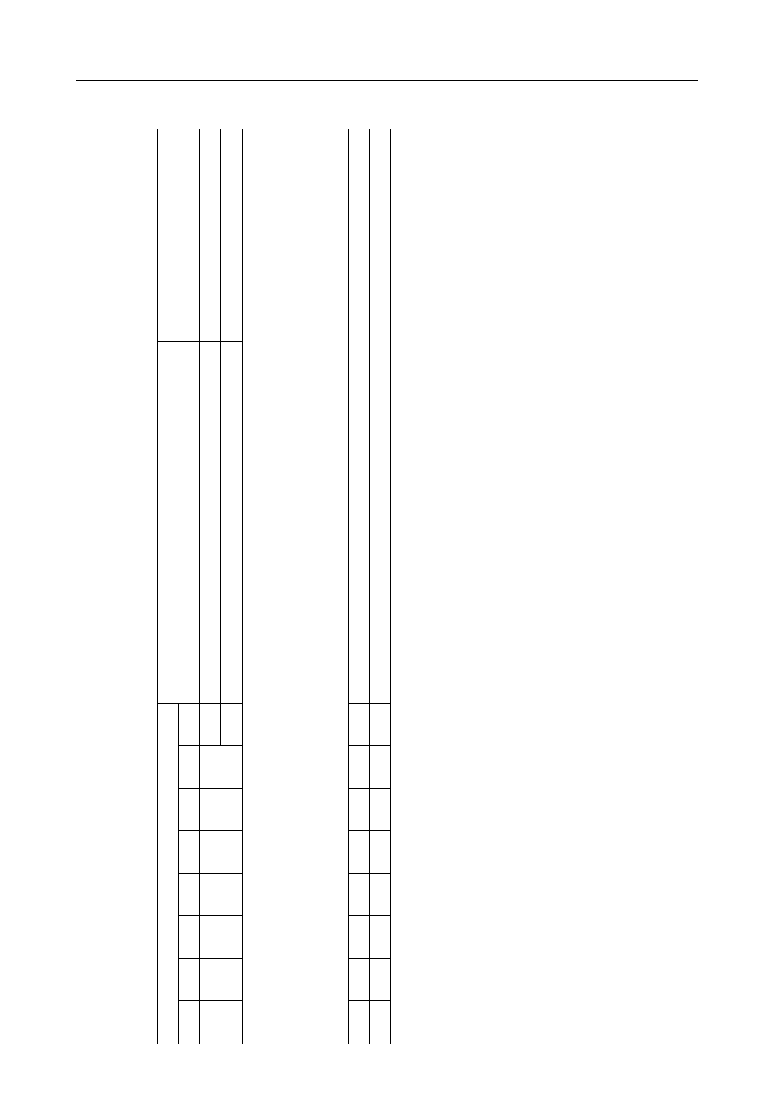

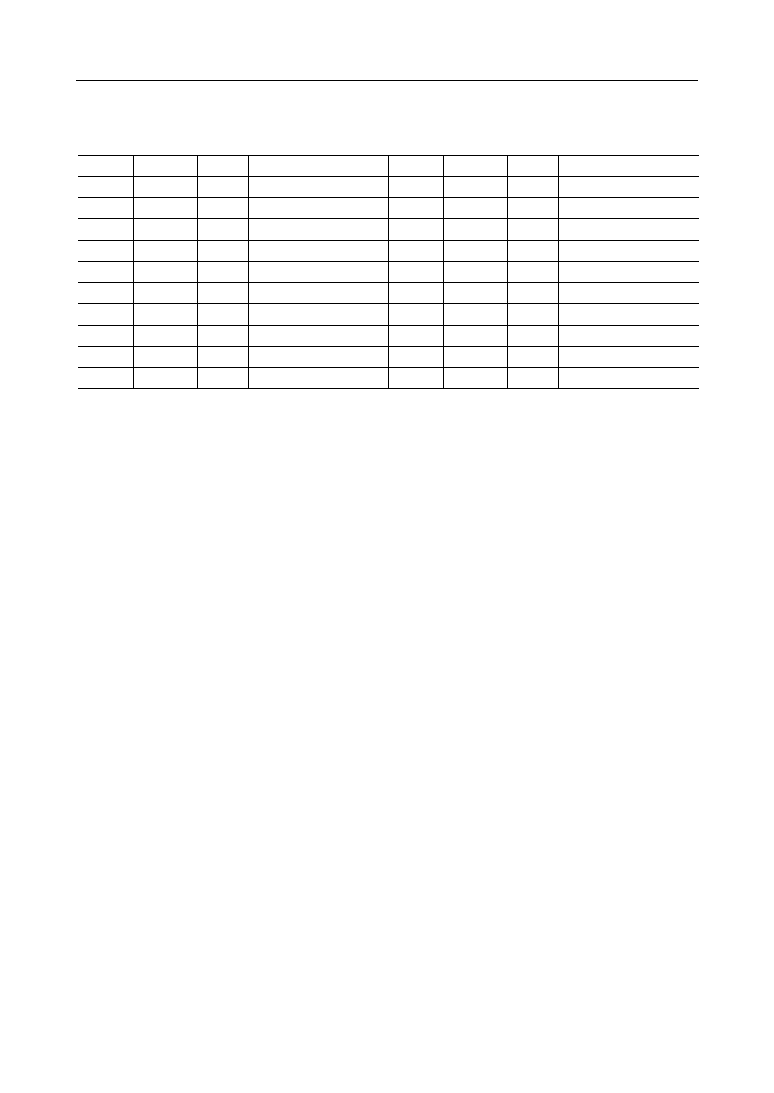

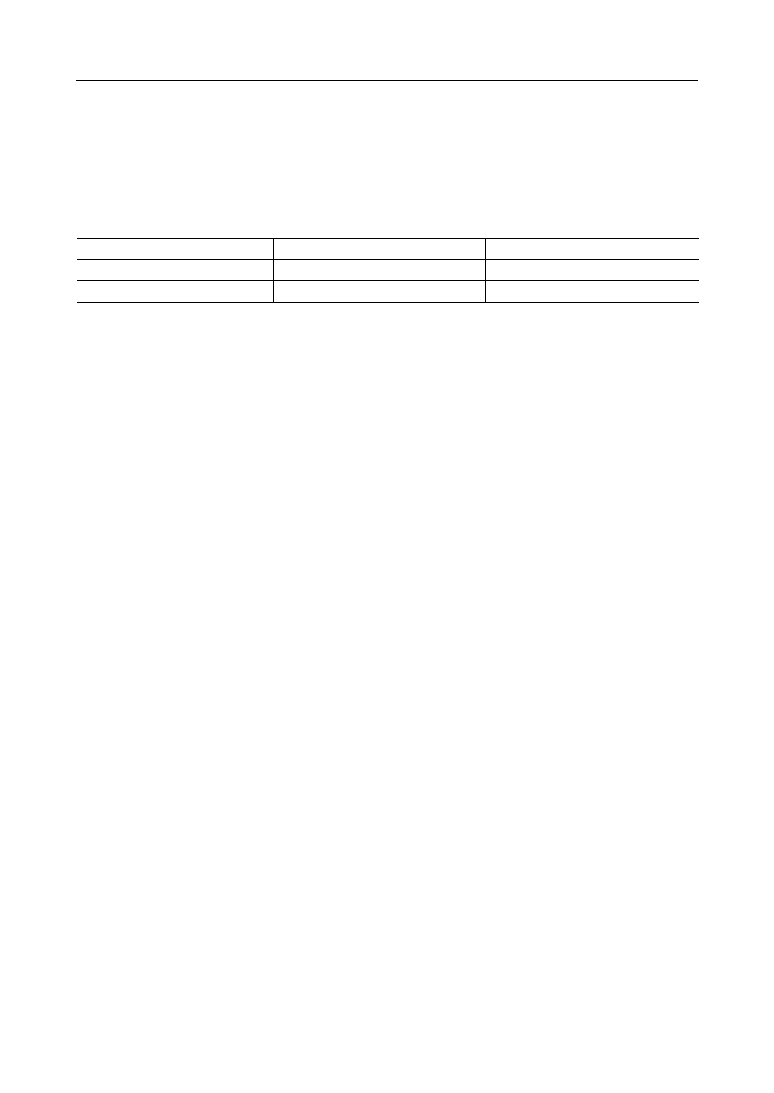

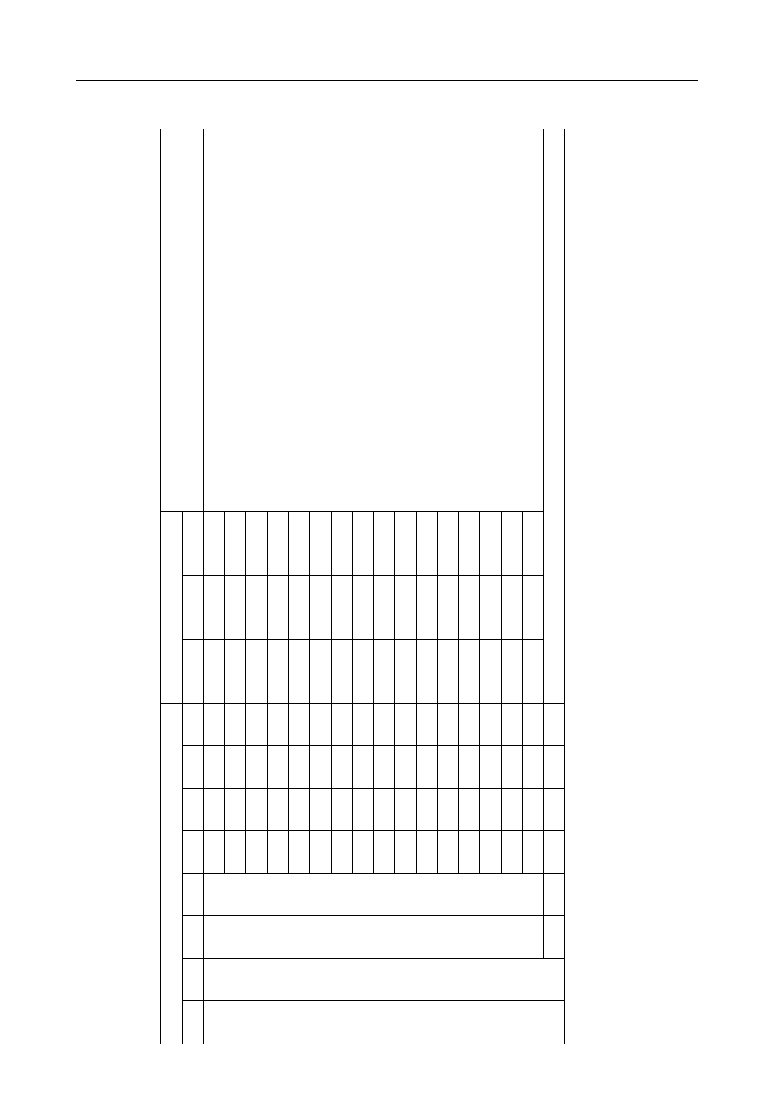

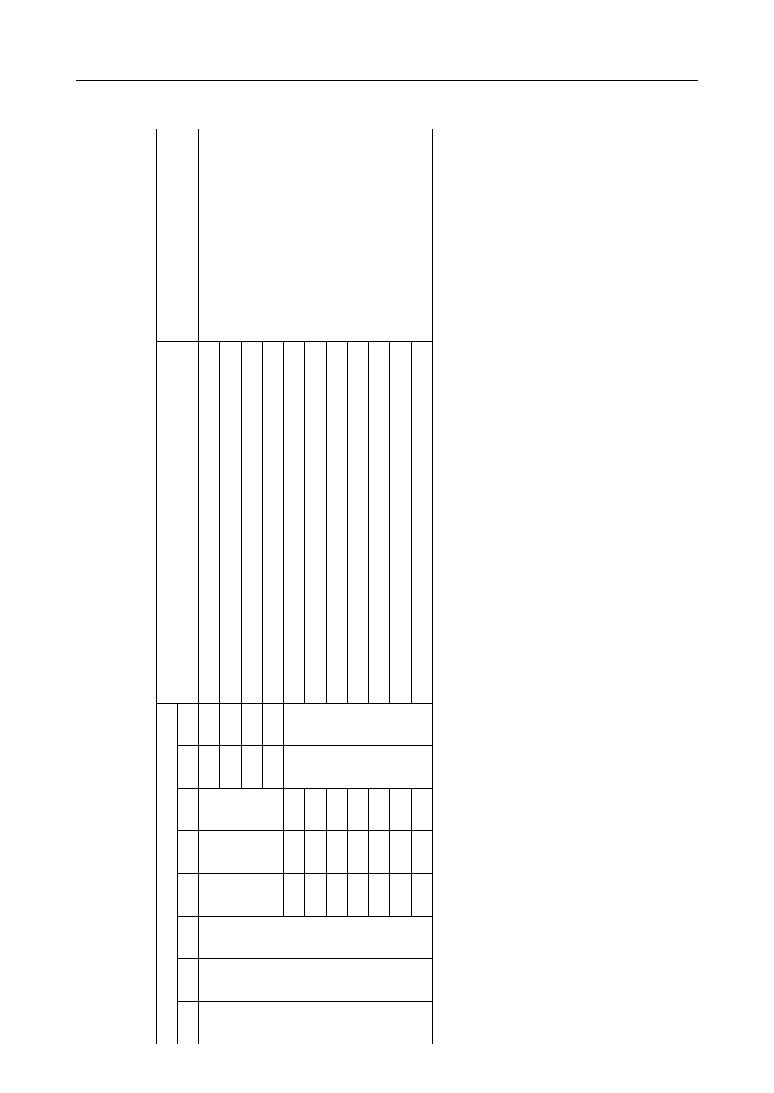

SW0

0

0

1

1

SW1

0

1

0

1

Tone combination 1

Tone combination 2

Tone combination 3

Tone combination 1

f1

1000 Hz

800 Hz

800 Hz

1000 Hz

f2

1333 Hz

1000 Hz

1000 Hz

1333 Hz

Wambling Cycle

16 Hz

16 Hz

8 Hz

16 Hz

1 / f1

Wambling Cycle Time

1 / f2

PIN AND FUNCTIONAL DESCRIPTIONS

LA, LB, LC, LD

General latch outputs for external control.

Statuses of these outputs are controlled via the processor interface. Refer to the description of the

control data for details.

SW0, SW1

External control signal inputs for setting the tone combination of the ringing tone.

When the external control for setting the tone combination is selected, the tone combination is

set by these pins.

VDG

Digital Ground.

VAG

Analog Ground.

° Semiconductor

MSM6895/6896

7/43

SA0, SA1

Sounder (ringing tone) driving outputs.

The output signal on SA1 is inverted against the signal on SA0. The sounder circuit can be easily

configured by connecting a piezo-sounder between SA0 and SA1. Through processor control, the

ringing tone volume is selectable from four levels and one of six tone combinations is selectable.

Initially, the ringing tone volume is set at a maximum and the tone combination is set externally.

If these pins are used with no-load, tone volume cannot be controlled.

When tone volume control is required, a load resistor must be connected between SA0 and SA1.

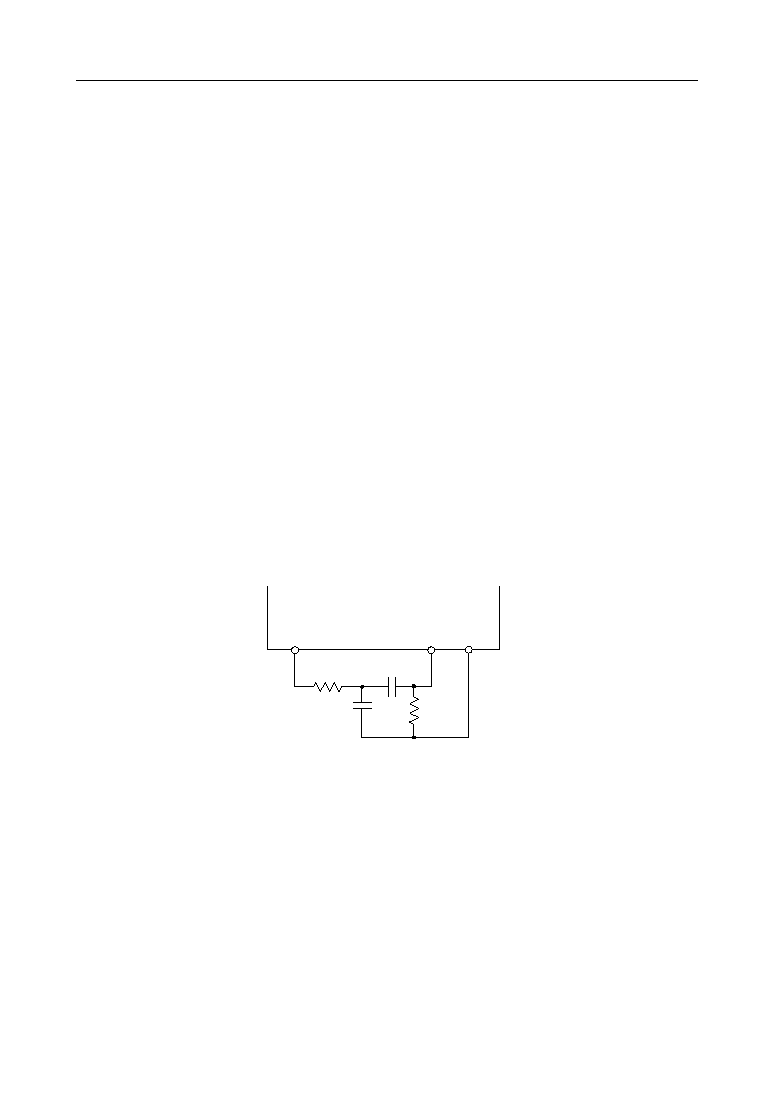

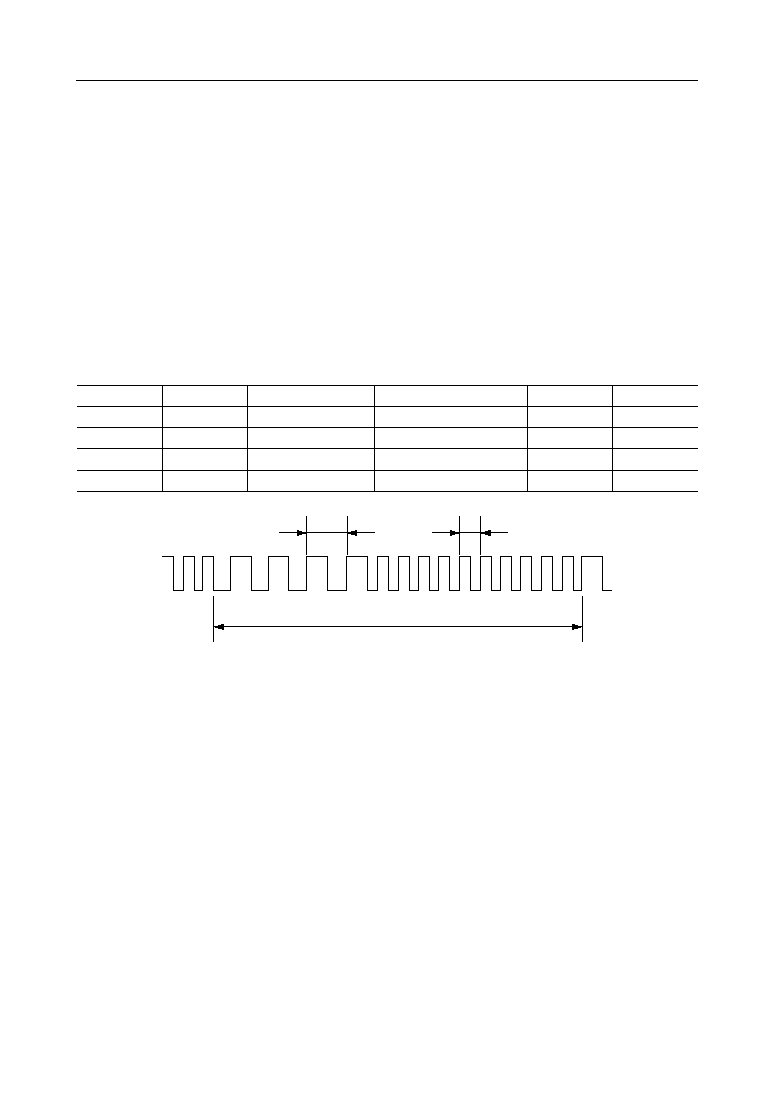

RMI, RMO0, RMO1

Receive main amplifier input and outputs.

RMI is the main amplifier input and RMO0 and RMO1 are the main amplifier outputs. The

output signal on RMO1 is inverted against RMO0, so the earphone of a piezo electric-type

handset is directly connected between RMO0 and RMO1. The RMI input pin is connected to the

receive preamplifier output pin (RPO).

If the adjusting of receive path frequency characteristics is required, insert the following circuit

for adjustment. During initial setting, the speech path from RMI to RMO0 and RMO1 is

disconnected and the output of RMO0 and RMO1 is at the VSG level (VA/2). The speech path

is provided by processor control.

A circuit example for adjustment of frequency characteristics

RPO

R1

C2

R2

C1

RMI

VSG

SPO

Output of preamplifier for speaker.

Since the driving capability is 2.4 V

PP

for the load of 20 kW, SPO can not directly drive a speaker.

During initial setting, SPO is in a non-signal state (VSG level), and a speech signal, RTONE0,

RTONE1, FTONE, hold acknowledge tone, and PB signal acknowledge tone are output through

processor control.

° Semiconductor

MSM6895/6896

8/43

R1I, R2I, RPO

Receive preamplifier inputs and output.

R1I and R2I are for the inputs and RPO is for the output of the receive preamplifier. Normally,

R1I is connected via an AC-coupling capacitor to the CODEC analog output (CAO), and R2I is

used as the mixing signal input pin.

During initial setting, the RPO output is in non-signal state (VSG level), and speech signal,

RTONE1, RTONE2, FTONE, PB acknowledge tone, and side tone signal are output through

processor control. And if the three-party speech function is required, the R2I pin is connected to

the analog output of the other CODEC.

MLDY

Hold tone signal input.

This pin is connected to the output of external melody IC. Through processor control, the signal

applied to MLDYI is output from the TO output pin as a hold tone on the transmit path, and from

the SPO output pin as a hold acknowledge tone on the receive path.

TPBI

Transmit signal input.

When the handset is used, TPBI is connected to the transmit preamplifier output pin (TPAO). If

adjustment of frequency characteristics on the transmit path is required, insert a circuit for

adjustment of characteristic between TPAO and TPBI. Through processor control, the signal

applied to this pin is output via the T1O and T2O pins on the transmit path output and its side

tone via the RPO pin.

TPAO

TPBI

VSG

C3

R3

C4

R4

A circuit example for adjustment of frequency characteristics

TMX1I, TMX2I

Transmit addition signal inputs.

Through processor control, the input signals to TMX1I and TMX2I are added to the transmit

signal and are output to T1O and T2O respectively.

° Semiconductor

MSM6895/6896

9/43

TPAI, TPAO

The transmit preamplifier input and output.

TPAI is the input and TPAO is the output. Connect TPAI to the microphone of handset via an AC-

coupling capacitor if the DC offset appears at a transmit signal (offset from SGT). The transmit

path from TPAI to TPAO is always established regardless of processor control.

VSG

Signal ground level output.

The output level is equal to a half of the power supply voltage.

VSGC

Bypass capacitor connecting pin for signal ground level.

Insert a 0.1 mF capacitor with good higher frequency characteristic, between VSGC and VAG.

VA, VD

+5 V power supply.

VA is for an analog circuit and VD is for digital supply. Connect both VA and VD to the +5 V

analog path of the system.

CAI

CODEC analog output.

Connect CAI to T1O.

CAO

CODEC analog output.

Connect CAO to R1I via an AC-Coupling capacitor.

° Semiconductor

MSM6895/6896

10/43

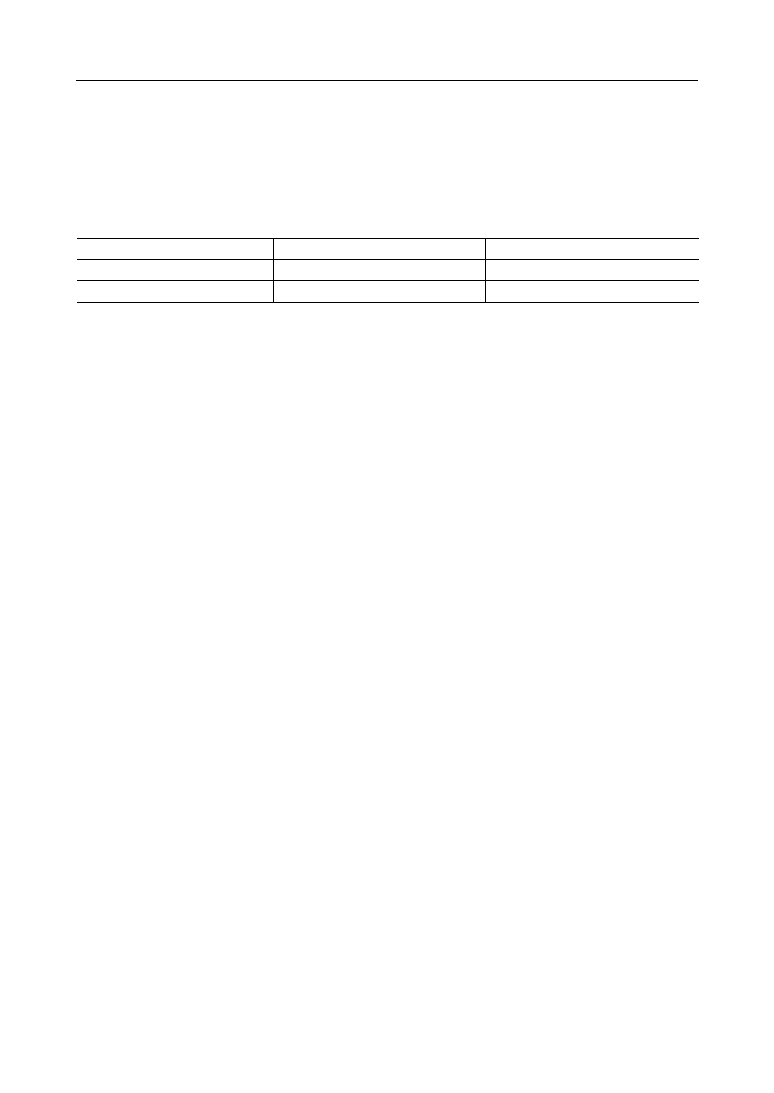

TEST, CK1536

External master clock inputs.

Since the MSM6895 and MSM6896 contain PLL internally, the external clock signal is eliminated.

But the device can operate with the external clock through these pins.

When these pins are not used, leave these pins open or at 0 V.

Mode

Internal PLL

External master clock

TEST pin

0 V

Digital "1"

CK1536 pin

open or 0 V

Input the signal of 1536 kHz

When the external clock is used, the CK1536 signal is required to be synchronized in phase with

the CK8 signal.

CK64

CODEC PCM data input and output shift clock input.

When the continuous clock is set, the frequency is one of 64 kHz, 128 kHz, and 256 kHz. When

the burst clock is used, one of 192, 384, 768, 1536, and 2048 kHz is available. If the BCLOCK signal

is not applied, PLL is out of synchronization and goes into the self-running mode.

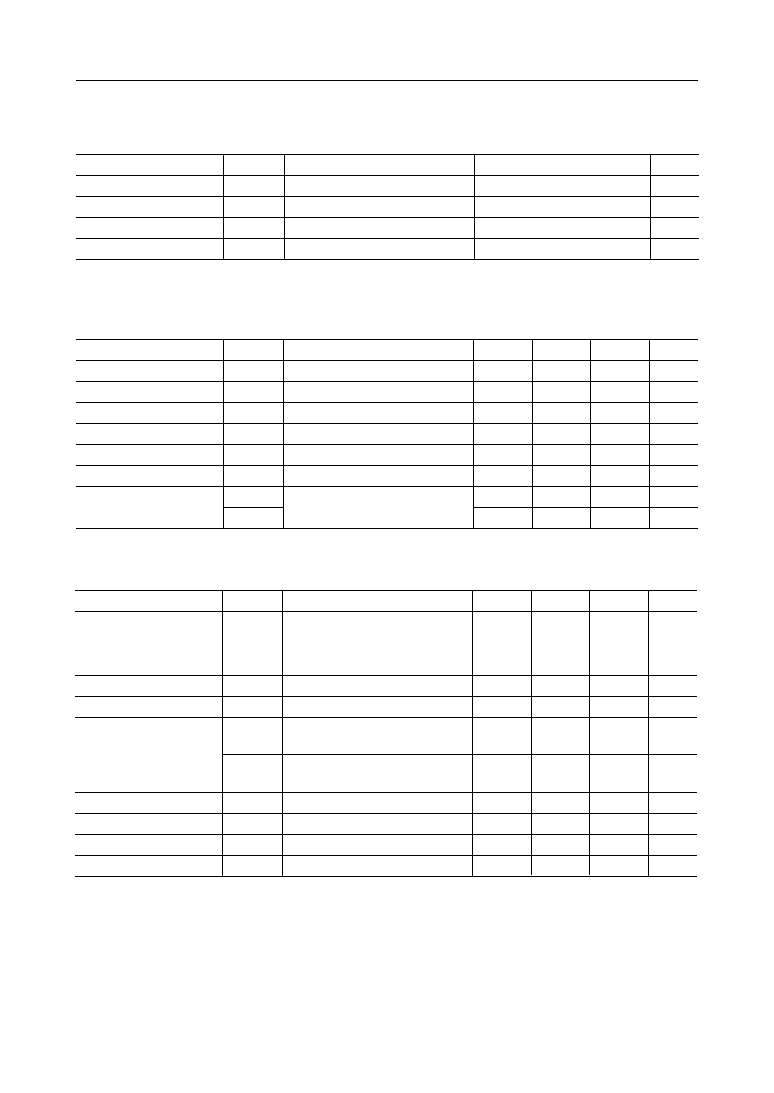

CK8

Synchronous signal input.

CODEC PCM data is sent out sequencially from MSB at the rising edge of the CK64 signal in

synchronization with the rise of the synchronous signal. PCM data should be entered from MSB

in synchronization with the rise of the synchronous signal. PCM data is shifted in at the falling

edge of the CK64 signal.

Since the CK8 signal is used for a trigger signal for PLL and for a clock signal to the tone generator,

if this signal is not applied, not only any tone can not be output, but also PLL goes out of

synchronization and goes into self-running mode. This signal has to be synchronous with the

CK64 signal and its frequency must be within 8 kHz

±

50 ppm to ensure the CODEC AC

characteristics (mainly frequency characteristics).

LOSS

Signal output for controlling the external circuits.

When the howler tone of sounder is selected through processor control, the output is in a digital

"1".

Initially, this output is set to a digital "0".

° Semiconductor

MSM6895/6896

11/43

PO0, PO1, PO2, PO3, PO4, PO5, PO6, PO7

Key scanning outputs.

These output pins need external pull-up resistors because of their open- drain circuits. Through

processor control, these outputs can be set open or to digital "0". Initially, these outputs are set

at an opened state.

PI0, PI1, PI2, PI3, PI4, PI5, PI6, PI7

Key scanning inputs.

In the READ mode, data on PI0 to PI7 can be read out of the processor via data bus (DB0 to DB7).

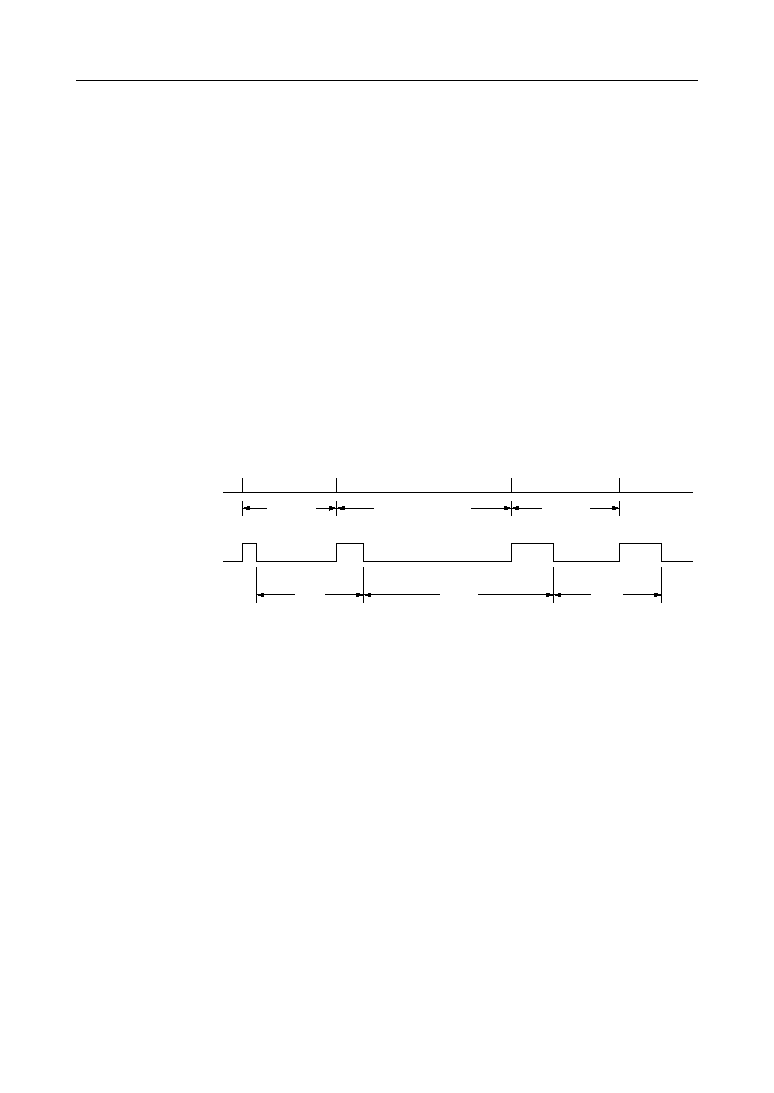

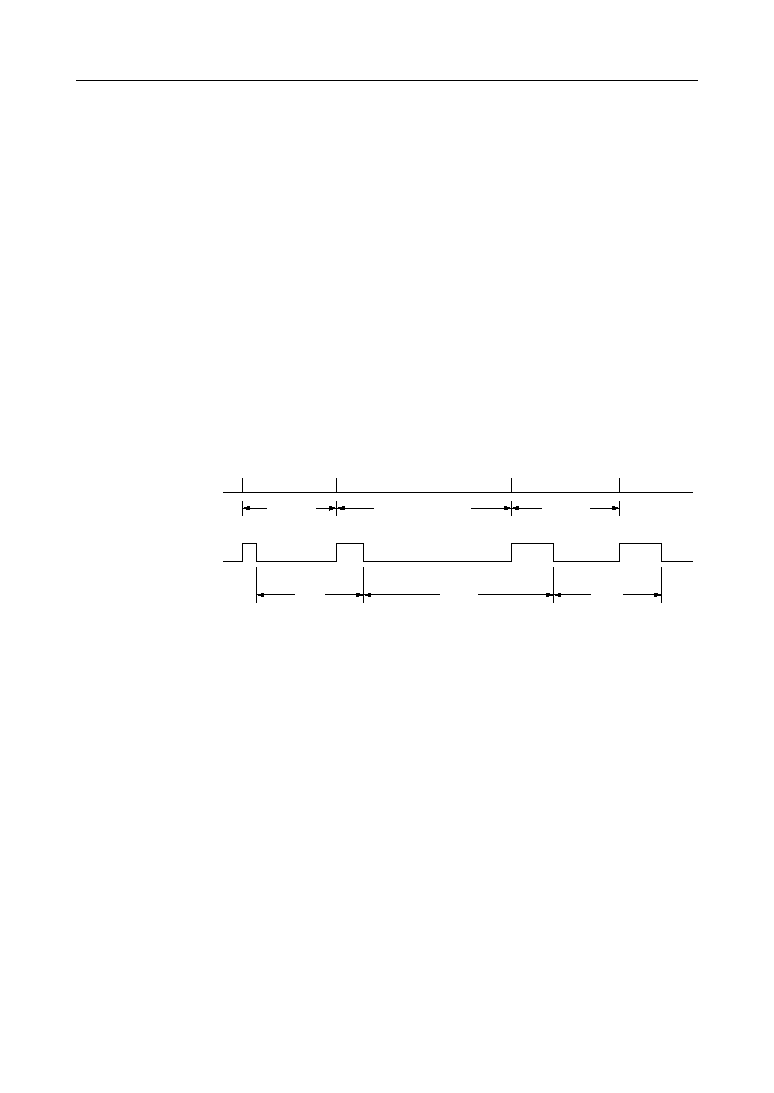

INTT

Interrupt signal output to the processor.

INTT outputs interrupt signals (digital "0") at intervals of 8 ms by the interrupt release control

signal from the processor. INTT does not output any signal while no CK8 signal is input.

Interrupt release signal

from processor

INTT output

t < 8 ms

8 ms < t < 16 ms

t < 8 ms

8 ms

16 ms

8 ms

DB0, DB1, DB2, DB3, DB4, DB5, DB6, DB7

Data bus inputs and outputs.

° Semiconductor

MSM6895/6896

12/43

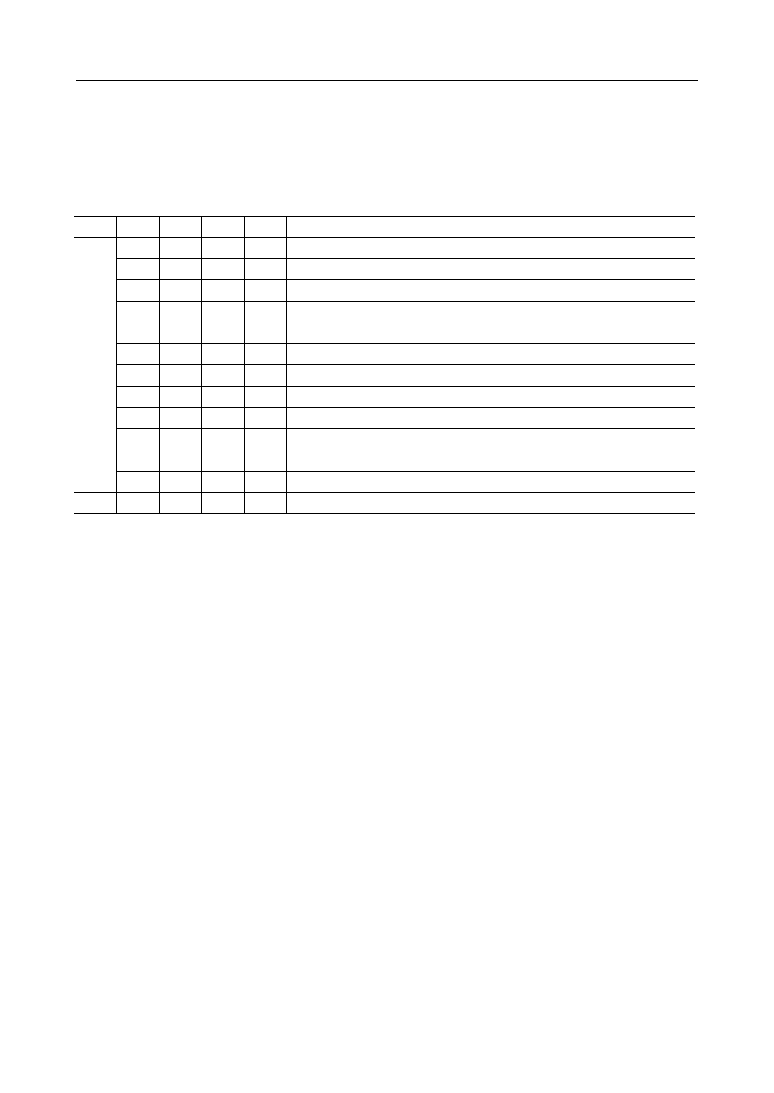

AD0, AD1

Address data inputs for the internal control registers.

Addressing of the internal control registers is executed by AD0 and AD1 and sub address data,

DB7 and DB6.

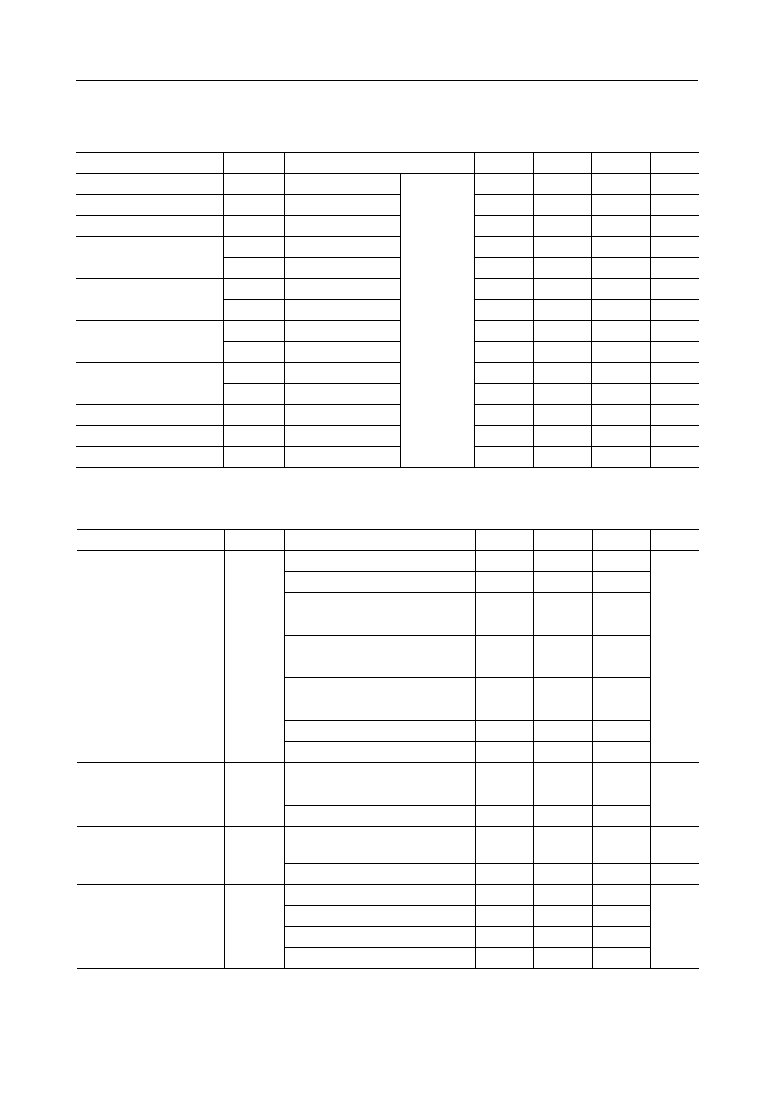

WR

Write signal for internal control registers.

Data on the data bus is written into the registers at the rising edge of WR under the condition of

digital "0" of CE (Chip Enable). While CE is in digital "1" state, WR becomes invalid. The Write

cycle is a minimum of 2 ms, but if the CK64 and CK8 signals are silent, the write cycle requires

a minimum of 50 ms.

A minimum of 2 ms specified as the write cycle is valid 10 ms after CK64 and CK8 signals are input.

RD

Read signal input to read PI0 to PI7 out of the processor.

When CE and RD are in digital "0" state, the digital values on PI0 to PI7 are output onto the data

buses DB0 to DB7. While CE is in digital "1" state, the RD signal becomes invalid.

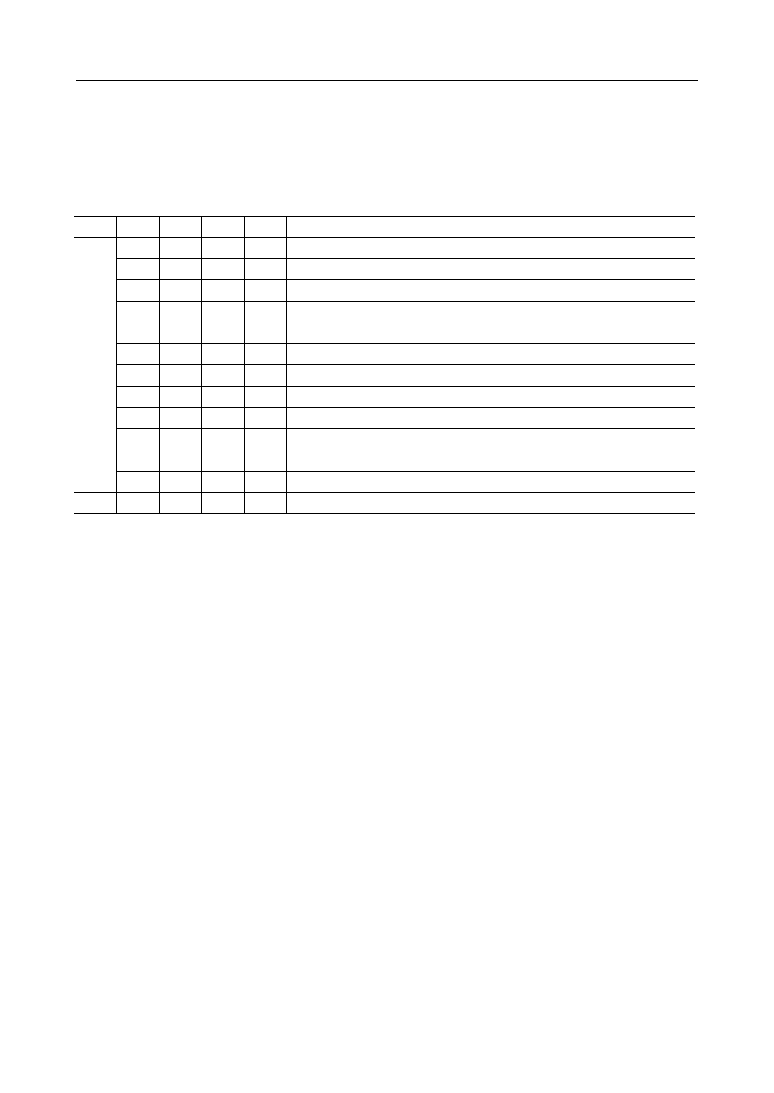

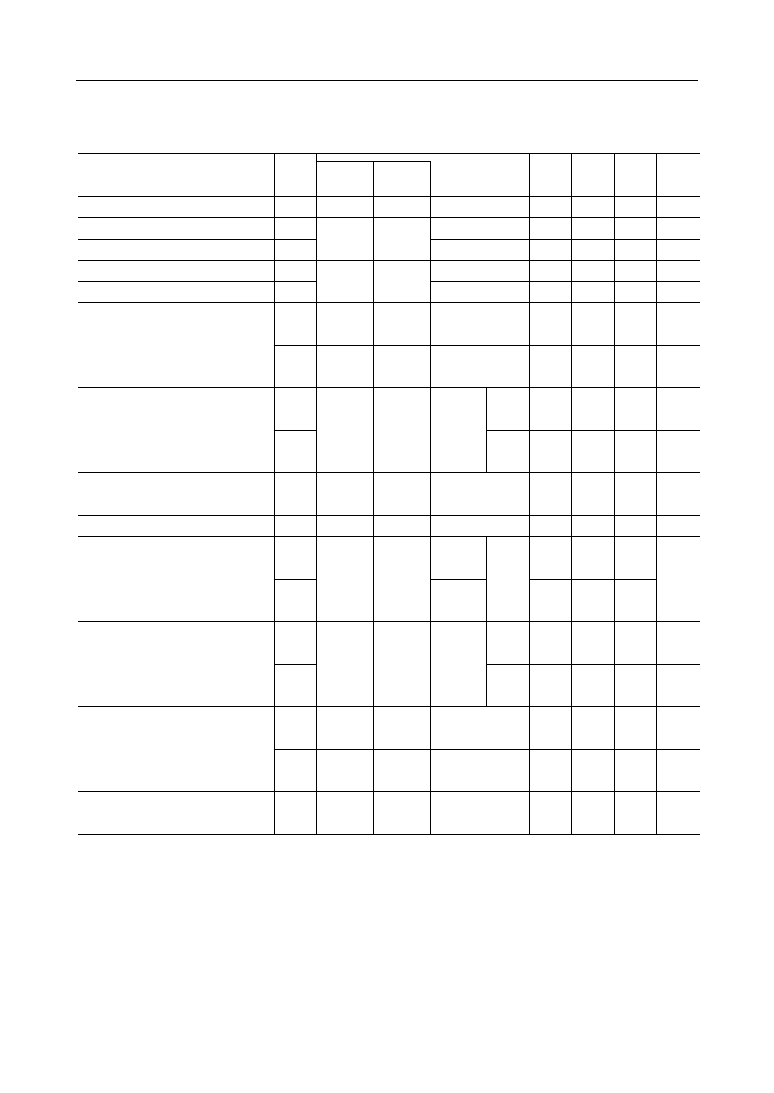

Write

Read

AD1

AD0

DB7

DB6

0

0

0

0

0

0

0

1

0

0

1

0

0

0

1

1

0

1

--

--

1

0

--

--

1

1

0

0

1

1

0

1

1

1

1

0

1

1

1

1

1

0

--

--

Function

Sounder Control

Control of function key acknowledge tone

PB tone control

Control of the internal control latch and the general-purpose latch,

Reset control of the watch dog timer.

Control of channel selector

Key scanning output control, interrupt release control

Volume control and tone combination control of sounder

CODEC power down control

Level control of transmit path, PB tone, and Hold tone, Gain control of

receive path

Frequency control of howler tone

Read of the key scanning data

° Semiconductor

MSM6895/6896

13/43

CE

Chip Enable signal input.

When CE is in digital "0" state, WR and RD are valid.

B1T, B2T, B1R, B2R

B channel interface inputs and outputs.

B1T and B2T are outputs, and B1R and B2R are inputs. Through channel control by the processor,

various data paths are set. The CODEC input and output signals are input and output via these

pins.

Initially the B1T and B2T outputs are fixed in a digital "1", and the B1R and B2R inputs are

neglected.

BR1, BR2, BT1, BT2

External digital inputs and outputs to the B-channel.

BR1 and BR2 are outputs, and BT1 and BT2 are inputs. Through channel control by processor,

the digital paths are set between these input and output pins and the B channel.

These signals are applied to another CODEC interface of three-party the speech path and to the

interface of 64 kbps at the rate adaptor circuit.

Initially the BR1 and BR2 outputs are fixed in a digital "1", and the BT1 and BT2 inputs are

neglected.

RESET

Reset signal input.

Digital "0" input to RESET makes all of internal control registers to be initialized. When powered

on, this RESET signal should be input for initializing the system.

TIME

Watchdog timer output.

When the processor does not reset the timer, the 500 ms period (Digital "0" : 4 ms) digital signal

is continuously output. When RESET is at digital "0", this timer is reset. And, in about 500 ms after

RESET goes to digital "1", the first timer output signal is issued and then the timer signal is output

at intervals of a 500 ms. If the CK8 signal is not input, the TIME signal is not output.

LML

Control signal output for external hold tone generator.

LML goes to digital "1" state when the hold tone transmit mode on transmit path or the hold

acknowledge tone mode on receive path is selected. During initialized state, LML is in digital "0"

state.

° Semiconductor

MSM6895/6896

14/43

ABSOLUTE MAXIMUM RATINGS

Parameter

Symbol

Condition

Rating

Unit

Power Supply Voltage

V

DD

0 to 7

V

Analog Input Voltage

V

AIN

≠0.3 to V

DD

+ 0.3

Digital Input Voltage

V

DIN

≠0.3 to V

DD

+ 0.3

Storage Temperature

T

STG

≠55 to +150

VAG, VDG = 0 V

--

VAG, VDG = 0 V

VAG, VDG = 0 V

V

∞C

V

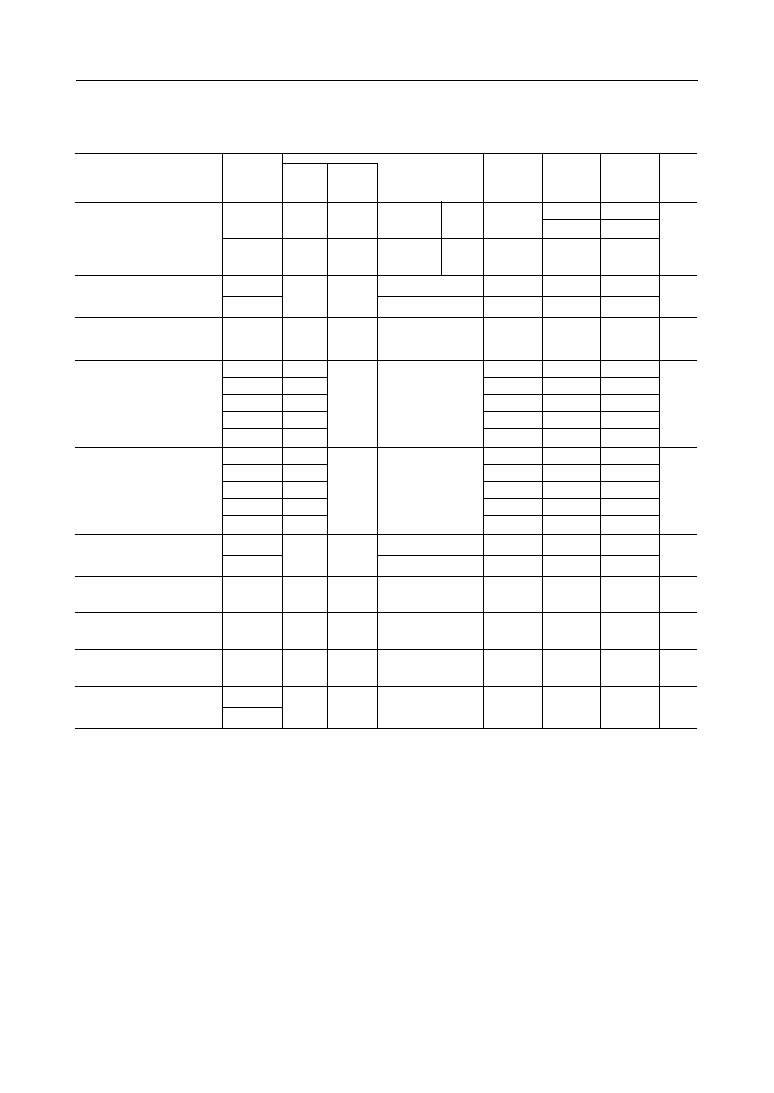

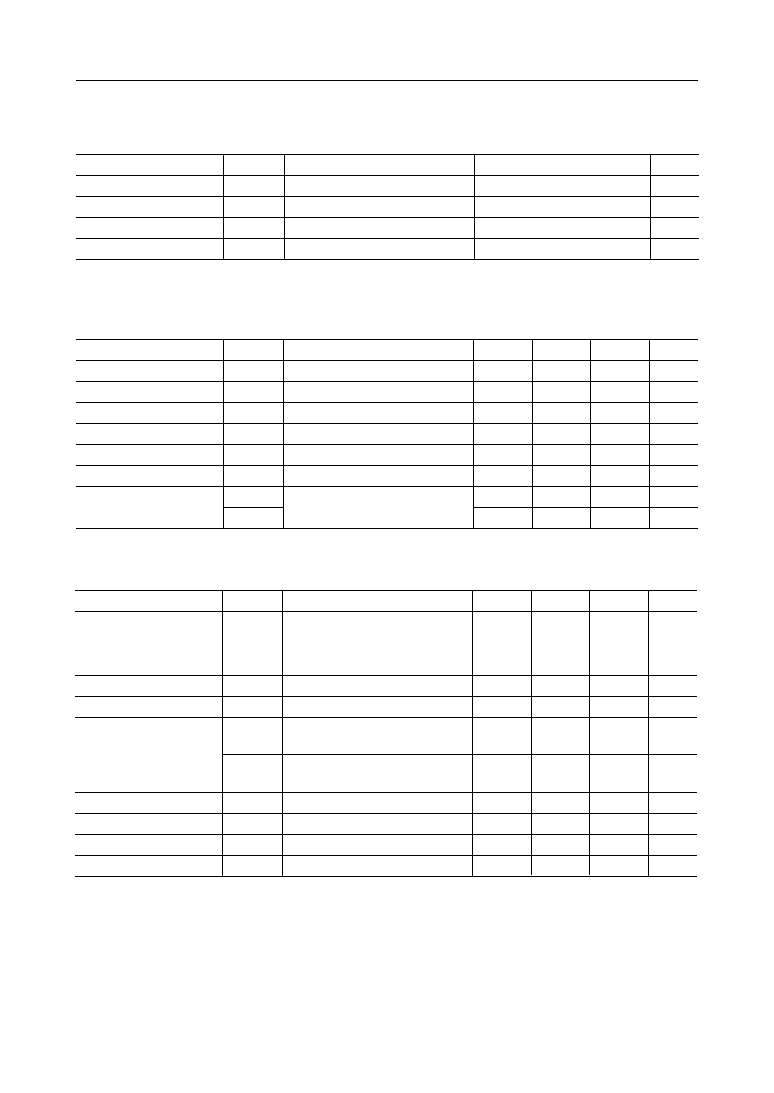

RECOMMENDED OPERATING CONDITIONS

Recommended Operating Conditions (CODEC Digital Interface)

F

C

8.0

--

--

Clock Frequency

kHz

Sync Pulse Frequency

Clock Duty Ratio

F

S

D

C

CK64

CK8

CK64

kHz

50

40

60

%

CK64∆CK8

See Fig.1

Sync Pulse Setting Time

t

XS

--

--

100

ns

CK8∆CK64

See Fig.1

t

SX

--

--

100

ns

Sync Pulse Width

t

WS

--

--

1 CK64

100

ms

Data Setup Time

t

DS

B1R, B2R

--

100

--

ns

Data Hold Time

t

DH

B1R, B2R

--

100

--

ns

Allowable Jitter Width

--

CK8

--

--

500

ns

Min.

Max.

Parameter

Symbol

Condition

Typ.

Unit

256

128

--

--

64

Input High Voltage

V

D

VA, VD (Voltage must be fixed)

5.0

4.75

5.25

Ta

--

+25

≠10

+70

Power Supply Voltage

V

V

IH

All Digital Input Pins

--

2.2

V

DD

V

Input Low Voltage

V

IL

All Digital Input Pins

--

0

0.8

V

Operating Temperature

∞C

Digital Input Rise Time

t

Ir

All Digital Input Pins

--

--

50

ns

Digital Input Fall Time

t

If

All Digital Input Pins

--

--

50

ns

PO0 to PO4 Output

--

10

--

Digital Output Load

R

DL

kW

--

--

100

C

DL

pF

Min.

Max.

Parameter

Symbol

Condition

Typ.

Unit

° Semiconductor

MSM6895/6896

15/43

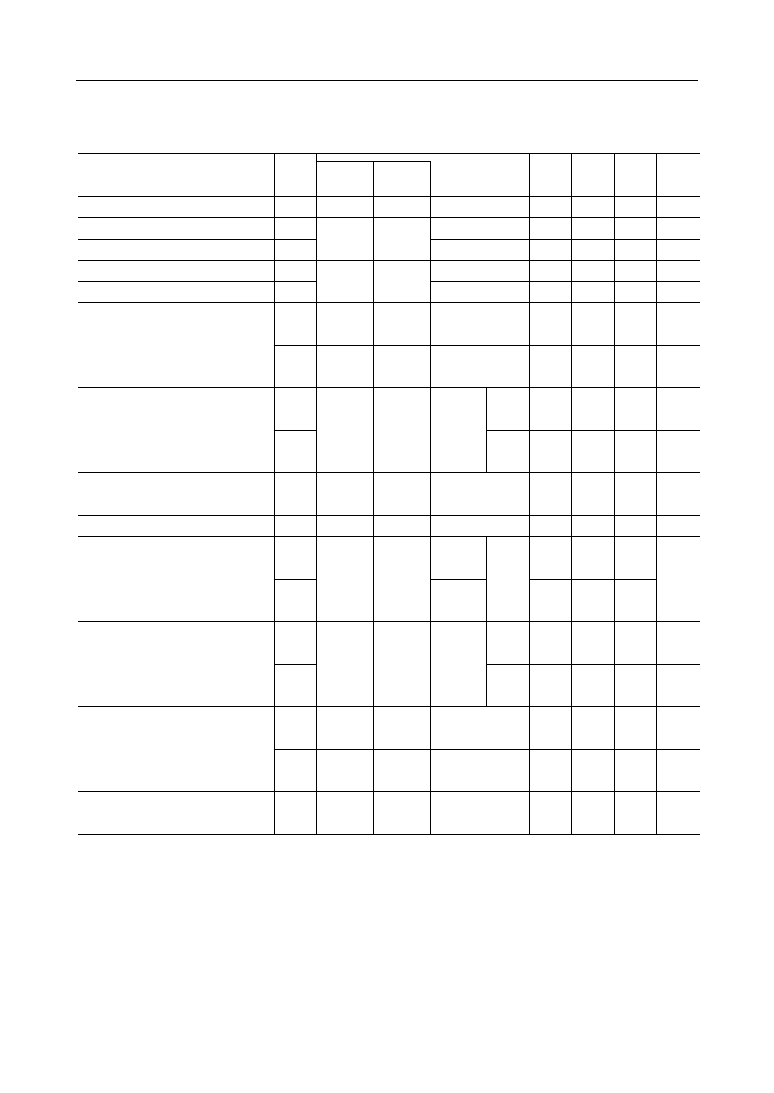

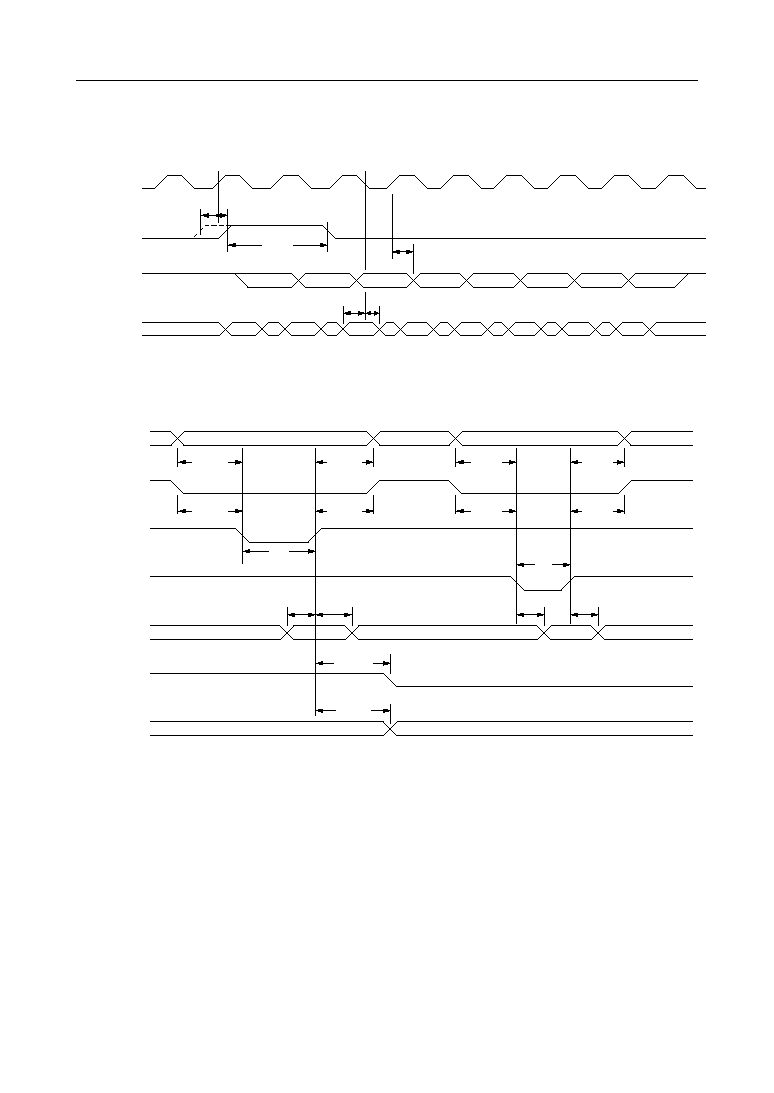

Recommended Operating Conditions (Processor Digital Interface)

P

W

Write Pulse Period

ns

WR

--

2000

--

T

W

Write Pulse Width

ns

WR

--

100

--

T

R

Read Pulse Width

ns

RD

--

200

--

AD0, AD1∆WR

ns

--

10

--

t

AW1

AD0, AD1∆RD

ns

--

80

--

t

AR1

Address Data

Setup Time

WR∆AD0, AD1

ns

--

50

--

t

AW2

RD∆AD0, AD1

ns

--

10

--

t

AR2

Address Data

Hold Time

CE∆WR

ns

--

10

--

t

CW1

CE∆RD

ns

--

80

--

t

CR1

CE Setup Time

WR∆CE

ns

--

50

--

t

CW2

RD∆CE

ns

--

10

--

t

CR2

CE Hold Time

DB0 to 7∆WR

Data Setup Time

ns

--

110

--

t

DW1

WR∆DB0 to 7

Data Hold Time

ns

--

20

--

t

DW2

RESET

Reset Pulse Width

ns

--

100

--

t

WRES

See Fig.2

Min.

Max.

Parameter

Symbol

Condition

Typ.

Unit

Recommend Operating Conditions (Analog Interface)

R

AL

TPAO, T1O, T2O,

--

20

--

Analog Load Resistance

kW

RMO0, RMO1

--

3

--

C

AL

TPAO, T1O, T2O,

RPO, SPO, CAO

--

--

100

Analog Load Capacitance

RMO0, RMO1

--

--

55

pF

nF

TPAI, TPBI, RMI

--

≠10

+10

MLDYI, TMX1I, TMX2I

--

≠50

+50

R1I, R2I

--

≠25

+25

CAI

--

≠100

+100

Allowable Analog

Input Offset Voltage

V

off

mV

Min.

Max.

Parameter

Symbol

Condition

Typ.

Unit

RPO, SPO, CAO

--

0.24

TPAI

--

--

--

--

--

--

--

--

--

--

--

--

--

0.31

TPBI

2.40

TMX1I, TMX2I

(Transmit Gain: Typ.)

1.90

Analog Input Voltage

V

AIN

MLDYI

V

PP

(Transmit Gain: Typ.)

1.20

R1I, R2I

(Transmit Gain: Typ.)

0.51

RMI

2.40

CAI

° Semiconductor

MSM6895/6896

16/43

ELECTRICAL CHARACTERISTICS

DC and Digital Interface Characteristics

I

DD1

Operating Mode (No Signal, Sounder OFF)

3.9

--

10.0

Power Supply Current

mA

(V

DD

= 5 V ±5%, Ta = ≠10∞C to +70∞C)

I

DD2

CODEC Receive Power Down

3.3

--

8.0

mA

I

DD3

CODEC Transmit Power Down

2.8

--

7.0

mA

Input High Voltage

V

IH

--

--

2.2

V

DD

V

Input Low Voltage

V

IL

--

--

0.0

0.8

V

--

--

--

2.0

mA

I

IH

High Input Leakage

Current

--

--

--

0.5

mA

I

IL

Low Input Leakage

Current

I

OH

= 0.4 mA

I

OH

= 1 mA

2.4

3.8

Digital Output High

Voltage

V

OH

--

V

I

OL

= ≠1.6 mA

0.0

Digital Output Low

Voltage

V

OL

--

0.4

V

--

Digital Output Leakage

Current

I

O

--

--

10

mA

TPAO, T1O, T2O,

CAO, RPO, RMO1, RMO2, SPO

Analog Output Offset

Voltage

V

off

--

≠100

+100

mV

Input Capacitance

C

IN

--

5

--

--

pF

TPAI, TPBI, MLDYI, RMI

10

--

--

MW

TMX1I, TMX2I, R1I, R2I

--

10

--

kW

CAI (fin : < 4 kHz)

1

--

--

MW

Analog Input Resistance

R

IN

VA/2

≠0.05

VA/2

+0.05

VSG Voltage

--

--

VA/2

V

I

SGF

FORCE Current

1.5

1.0

--

I

SGS

SINK Current

0.5

0.3

--

VSG Drive Current

mA

V

DD

V

DD

--

Min.

Max.

Parameter

Symbol

Condition

Typ.

Unit

I

DD4

CODEC Transmit/Receive Power Down

2.2

--

4.0

mA

° Semiconductor

MSM6895/6896

17/43

AC Characteristics 1 (CODEC)

Loss T1

Loss T2

Loss T3

Loss T4

Loss T5

Loss T6

Transmit Frequency

Response

dB

Parameter

Symbol

Condition

Typ.

Unit

Min.

Max.

Freq.

(Hz)

Level

(dBm0)

60

300

1020

2020

3000

3400

27

+0.07

≠0.03

+0.06

0.38

20

≠0.15

≠0.15

≠0.15

0.0

--

+0.20

+0.20

+0.20

0.80

0

Reference

Loss R1

Loss R2

Loss R3

Loss R4

Loss R5

300

1020

2020

3000

3400

≠0.03

≠0.02

+0.15

0.56

≠0.15

≠0.15

≠0.15

0.0

+0.20

+0.20

+0.20

0.80

Reference

Receive Frequency

Response

dB

0

SD T1

SD T2

SD T3

SD T4

SD T5

43.0

41.0

38.0

31.0

26.5

35

35

35

29

28

24

23

--

--

--

--

--

dB

1020

3

0

≠30

≠40

≠45

Transmit Signal to

Distortion Ratio

*1

SD R1

SD R2

SD R3

SD R4

SD R5

43.0

41.0

40.0

34.0

31.0

37

37

37

31

30

26

25

--

--

--

--

--

dB

1020

3

0

≠30

≠40

≠45

Receive Signal to

Distortion Ratio

*1

GT T1

GT T2

GT T3

GT T4

GT T5

+0.01

+0.13

+0.32

+0.64

≠0.3

≠0.3

≠0.6

≠1.5

+0.3

+0.3

+0.6

+1.5

Reference

Transmit Gain

Tracking

dB

1020

3

≠10

≠40

≠50

≠55

GT R1

GT R2

GT R3

GT R4

GT R5

0.0

≠0.06

≠0.20

≠0.27

≠0.2

≠0.2

≠0.4

≠0.8

+0.2

+0.2

+0.4

+0.8

Reference

Receive Gain

Tracking

dB

1020

3

≠10

≠40

≠50

≠55

(V

DD

= 5 V ±5%, Ta = ≠10∞C to +70∞C)

*2

*2

*2

*2

Notes:

*1 Psophometric filter is used

*2 Upper is specified for the MSM6895, lower for the MSM6896

° Semiconductor

MSM6895/6896

18/43

AC Characteristics 1 (CODEC) (Continued)

tgd T1

tgd T2

tgd T3

tgd T4

tgd T5

Transmit Group Delay

ms

500

600

1000

2600

2800

0.19

0.12

0.02

0.05

0.08

--

--

--

--

--

0.75

0.35

0.125

0.125

0.75

0

*4

tgd R1

tgd R2

tgd R3

tgd R4

tgd R5

Receive Group Delay

ms

500

600

1000

2600

2800

0.0

0.0

0.0

0.09

0.12

--

--

--

--

--

0.75

0.35

0.125

0.125

0.75

0

*4

CR T

Transmit ∆ Receive

86

66

--

CR R

Receive ∆ Transmit

78

70

--

1020

0

Crosstalk Attenuation

dB

4.6 kHz to

72 kHz

Discrimination

DIS

0 to 4000 Hz

≠25

32.0

30

--

dB

300 to

3400

Out-of-band Signal

Spurious

S

4.6 kHz to 100 kHz

0

≠37.5

--

≠35

dBmO

fa = 470

fb = 320

Intermodulation Distortion

IMD

2fa≠fb

≠4

≠52

--

≠35

dBmO

PSR T

*5

30

--

--

PSR R

0 to 50

kHz

100

mV

pp

Power Supply Noise

Rejection Ratio

dB

Parameter

Symbol

Condition

Typ.

Unit

Min.

Max.

Freq.

(Hz)

Level

(dBm0)

(V

DD

= 5 V ±5%, Ta = ≠10∞C to +70∞C)

AIN = SG

*1

Nidle T

--

--

--

*2

≠73.5

≠71

≠70

≠69

*1

*3

Nidle R

--

--

--

≠77.8

≠74

Idle Channel Noise

dBmOp

AV T

0.5671

0.6007

0.6363

AV R

0.5671

0.6007

0.6363

1020

0

Vrms

Absolute Amplitude

A to A

CK64 = 64 kHz

Absolute Delay Time

Td

1020

0

--

0.58

0.60

ms

Transmit CODEC

Receive CODEC

Notes:

*1 Psophometric filter is used

*2 Upper is specified for the MSM6895, lower for the MSM6896

*3 PCM data for MSM6895: All "1"

PCM data for MSM6896: "11010101"

*4 Minimum value of the group delay distortion

*5 The measurement under idle channel noise

° Semiconductor

MSM6895/6896

19/43

AC Characteristics 2 (Transmit Path)

Parameter

Symbol

Level

(dBV)

Max.

Unit

(V

DD

= 5 V ±5%, Ta = ≠10∞C to +70∞C)

Freq.

(Hz)

Condition

GTPA

1020

22.0

dB

GTPB1

19.7

dB

In-Channel PB Signal Output Level

VPBT1

≠13.4

dBV

--

VPBT2

≠13.4

--

GPBT1

≠1.0

dBV

In-Channel PB Signal

≠4.0

+0.9

%

--

≠30

Pre-Amp Gain

≠24.4

--

--

GPBT2

DfPBT

THDPBT

--

--

Transmit Path 2 Gain

1020

≠22.1

--

GPAT1

0.0

GPAT2

0.0

dB

Hold Tone Path Gain

1020

≠22.4

Hold Tone Path Gain Setting

RG1 PAT

≠1.0

dB

≠22.4

1020

RG2 PAT

≠4.0

dB

Idle Channel Noise

Ni TPA

--

dBV

--

--

Ni TPB

--

dBV

--

--

Maximum Output Voltage Swing

VOT

--

V

PP

--

--

GTPB2

19.7

Transmit Path 1 Gain

dB

GTMX1

+2.0

dB

Transmit Addition Signal 2 Gain

1020

≠4.4

GTMX2

+2.0

Transmit Addition Signal 1 Gain

dB

T1O

T2O

Typ.

20.0

17.7

≠15.4

≠15.4

≠3.0

≠6.0

--

≠35

≠2.0

≠2.0

≠3.0

≠6.0

≠93

≠91

--

17.7

0.0

0.0

Min.

18.0

15.7

≠17.4

≠17.4

≠5.0

≠8.0

≠0.9

--

≠4.0

≠4.0

≠5.0

≠8.0

--

--

2.4

15.7

≠2.0

≠2.0

--

Frequency Deviation

In-Channel PB Signal Distortion

--

dB

TPAO, T1O,

T2O, R

L

= 20 kW

T1O, T2O

Meature at TPAO

TPAI: 510 W at termination

In-Channel PB Signal Output

Level Setting

*6

*6

≠3 dB

≠

6 dB

For

typical

setting

MLDYI-T1O

MLDYI-T2O

Set at

typical

gain

In-Band Distortion

T1O, T2O

≠ 3 dB

≠

6 dB

For

typical

setting

Set at

typical gain

Set at

typical gain

TMX1I-T2O

TPBI-T2O

TMX1I-T1O

TPBI-T1O

TPAI-TPAO

dB

dB

Note:

*6 Noise band width: 0.3 kHz to 3.4 kHz, non-weighted

° Semiconductor

MSM6895/6896

20/43

AC Characteristics 3 (Receive Path)

GRMO0

1020

17.3

dB

GRMO1

17.3

dB

Receive Signal Path Gain Setting

RG RPA1

5.0

RG RPA3

11.0

≠1.0

dB

≠26.2

Receive Main Amp. Gain

≠19.4

VPBRP

--

Receive Main Amp.

1020

≠19.4

DGRMO

--

dB

deg

Receive Main Amp.

1020

≠19.4

DPRMO

--

Output Gain Difference

15.3

15.3

3.0

9.0

≠3.0

≠28.2

≠0.01

≠179.6

13.2

13.2

1.0

7.0

≠5.0

≠30.2

--

--

PB Acknowledge Tone Output Level

--

dBV

SPO

MLDYI-SPO

+3 dB

+6 dB

+9 dB

RMO0/RMO1

RMO0/RMO1

RMI-RMO1

RMI-RMO0

≠19.4

RG RPA2

8.0

≠23.4

dB

1020

6.0

4.0

Receive Addition Signal Path Gain

≠4.0

dB

≠14.4

GRPB

1020

≠6.0

≠8.0

R2I-RPO

Receive Addition Signal Path

RG RPB1

5.0

RG RPB3

11.0

For

typical

setting

3.0

9.0

1.0

7.0

+3 dB

+6 dB

+9 dB

RG RPB2

8.0

≠14.4

dB

1020

6.0

4.0

GPAS

1020

Hold Acknowledge Tone Path Gain

≠7.4

≠28.1

≠30.1

≠32.1

dBV

RPO

VPBRP

+0.9

%

--

≠0.9

RPO, SPO

DfPBR

--

PB Acknowledge Tone Frequency

--

≠30

dB

≠35

--

RPO, SPO

THD PBR

--

PB Acknowledge Tone Distortion

--

12.9

dB

10.9

8.9

TPBI-RPO

GSIDE

1020

Side Tone Path Gain

≠21.4

--

dBV

≠86

--

RPO

Ni RPO

--

--

--

dBV

≠86

--

SPO

Ni SPO

--

--

--

dBV

≠95

--

RMI, VSG

Ni RMO

--

Idle Channel Noise

--

RMO0, RMO1

Output Phase Difference

dB

Receive Signal Path Gain

1020

≠14.4

GRPA

≠4.0

≠6.0

≠8.0

R1I-RPO

Gain Setting

dB

Speaker Preamp. Gain

1020

≠4.4

GSP

≠4.0

≠6.0

≠8.0

R1I-SPO

≠4.0

≠6.0

≠8.0

R2I-SPO

Set at

typical

*6

*6

*6

Parameter

Symbol

Level

(dBV)

Max.

Unit

(V

DD

= 5 V ±5%, Ta = ≠10∞C to +70∞C)

Freq.

(Hz)

Condition

Typ.

Min.

Difference

Set at

typical

Set at

typical

Set at

typical

For

typical

setting

Note:

*6 Noise band width: 0.3 kHz to 3.4 kHz, non-weighted

° Semiconductor

MSM6895/6896

21/43

AC Characteristics 3 (Receive Path) (Continued)

V

PP

187.0 mV

PP

224.6

VFTRP

--

--

VOR

--

V

PP

--

--

VOM

--

Maximum Output Amplitude

157.0

189.0

--

--

132.0

159.0

2.4

3.0

FTONE Output Amplitude

--

SPO

RPO

RMO0, RMO1

RPO, SPO

--

VRT1

--

RTONE1 Output Amplitude

--

191.5

161.0

135.5

mV

PP

RPO

VFTSP

R

L

= 3 kW +55 nF

R

L

= 20 kW

109.0 mV

PP

91.7

77.2

RPO

VRT0

--

RTONE0 Output Amplitude

--

*8

*7

Parameter

Symbol

Level

(dBV)

Max.

Unit

(V

DD

= 5 V ±5%, Ta = ≠10∞C to +70∞C)

Freq.

(Hz)

Condition

Typ.

Min.

Notes:

*7 DT, PDT, SDT, CRBT, IIT

*8 RBT, DT, T250

° Semiconductor

MSM6895/6896

22/43

AC Characteristics 4 (Ringing Tone Output Circuit)

0.45

VHOW

--

0.28

0.13

Howler Tone Output Amplitude

--

VST4

--

4.0

3.25

V

PP

0.65

0.47

0.25

VST3

1.98

V

PP

1.28

0.73

VST2

--

Calling Tone Output Amplitude

--

--

4.0

3.25

SA0-

SA1

730 W

to

VDG

VST1

*9

Volume 4

Volume 3

Volume 2

Volume 1

Parameter

Symbol

Level

(dBV)

Max.

Unit

(V

DD

= 5 V ±5%, Ta = ≠10∞C to +70∞C)

Freq.

(Hz)

Condition

Typ.

Min.

Note:

*9. IR-1, IR-2, SIR-1, SIR-2, CR, T1K, HR, SPT

Digital Interface Characteristics

Parameter

Symbol

Max.

Unit

(V

DD

= 5 V ±5%, Ta = ≠10∞C to +70∞C)

Condition

t

PDPATH

Typ.

Min.

Digital Path Delay Time

150

52

20

ns

BT1∆BR1, BR2

t

PDDATA

Digital Output (Data) Delay Time

150

52

20

ns

RD∆DB0 to DB7

Pull-up resistor : 10 kW

t

PDSCN

key Scanning Output Delay Time

1.9

--

0.5

ms

WR∆PO0, PO1, PO2, PO3, PO4

t

PDLA

Digital Output (Latch) Delay Time

1.9

--

0.5

ms

WR∆LA, LB, LC, LD, LML, LOSS

BT2∆BR1, BR2

t

PDCOD

CODEC Data Output Delay Time

100

50

20

ns

CK64∆B1T, B2T

° Semiconductor

MSM6895/6896

23/43

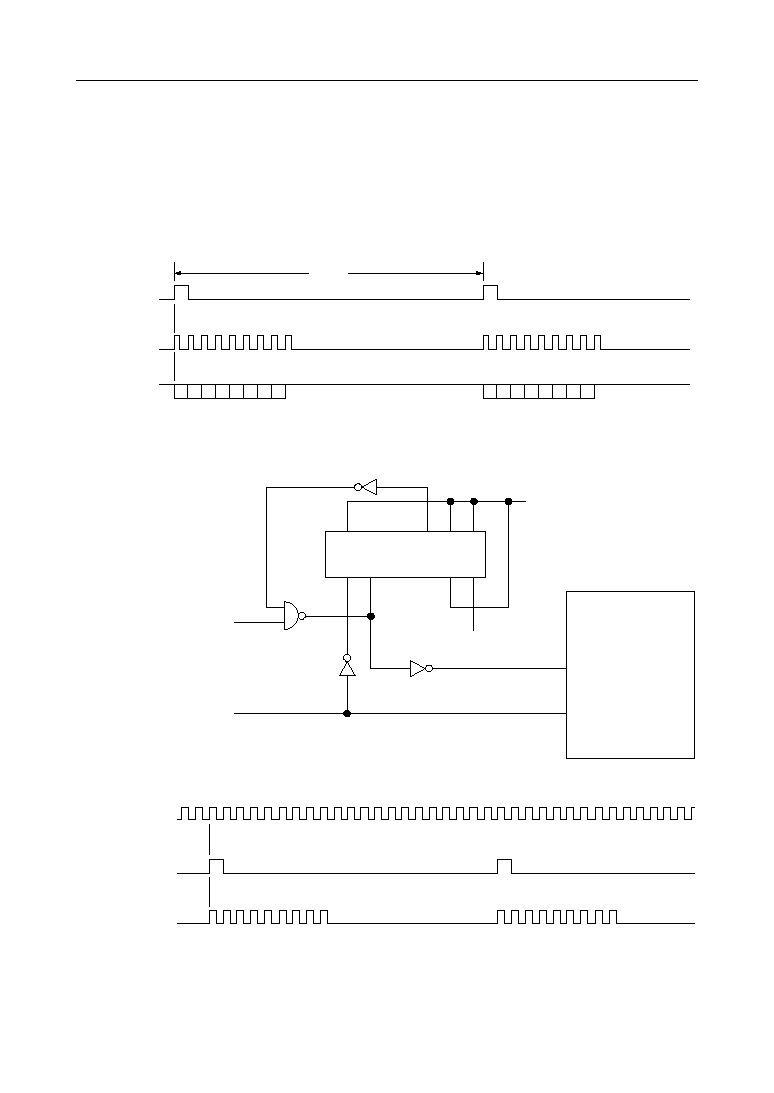

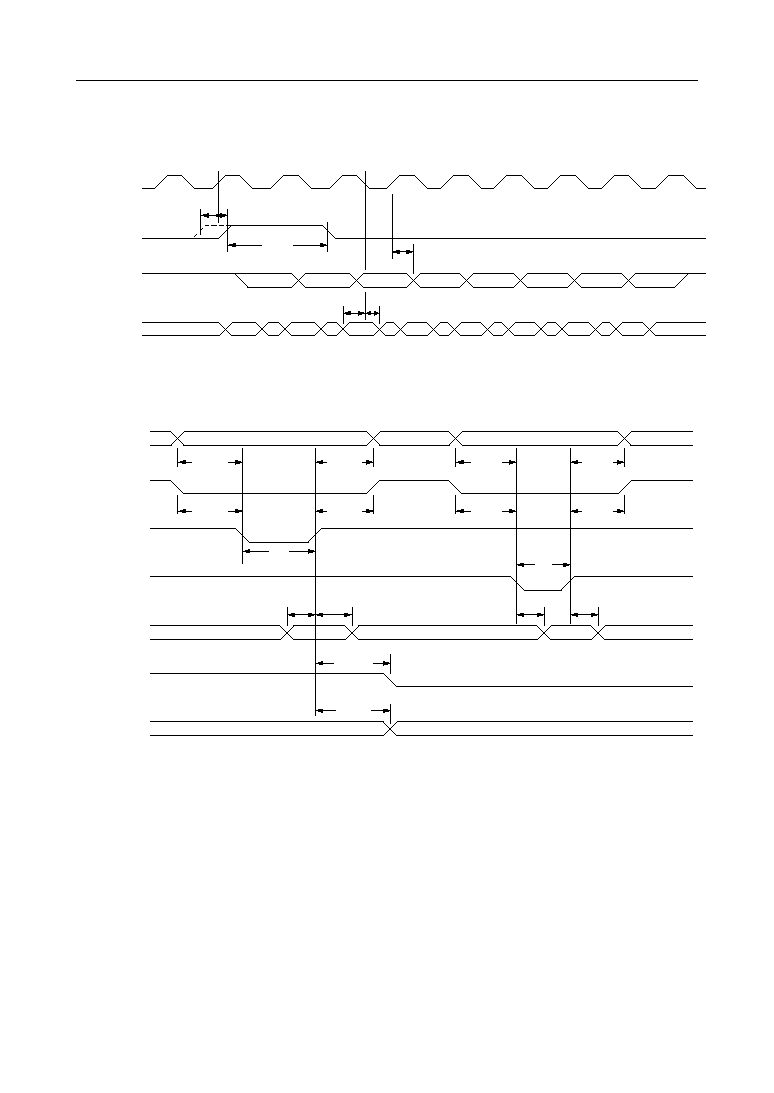

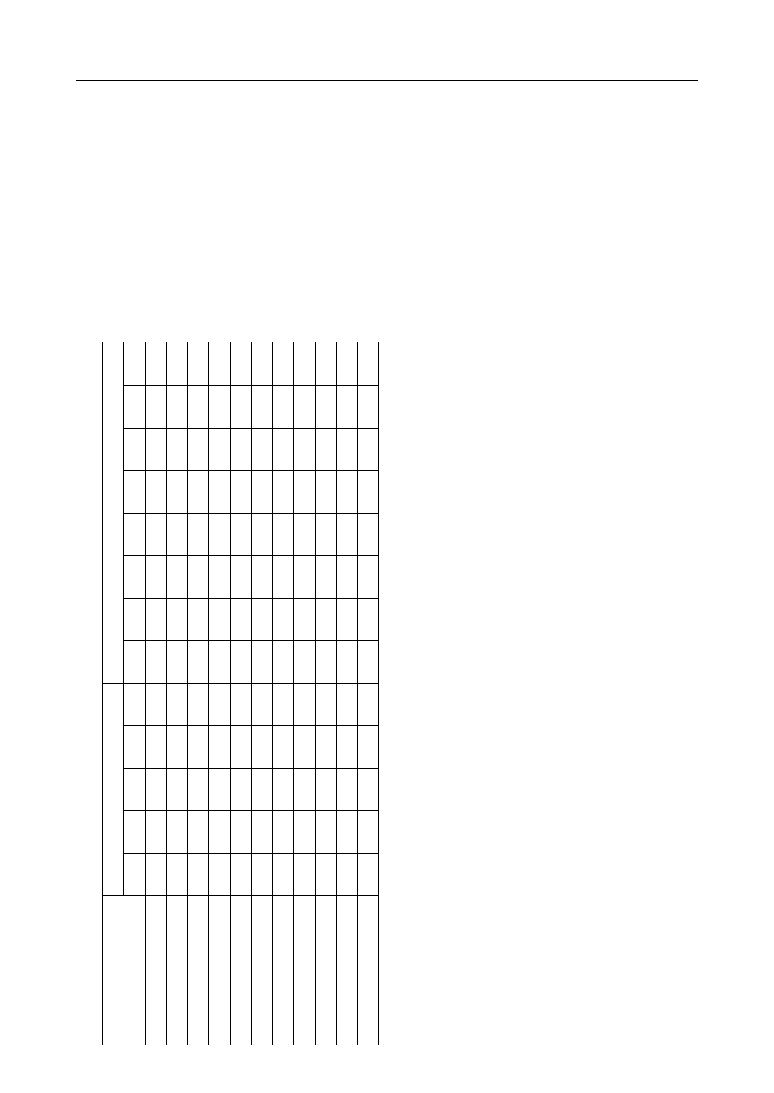

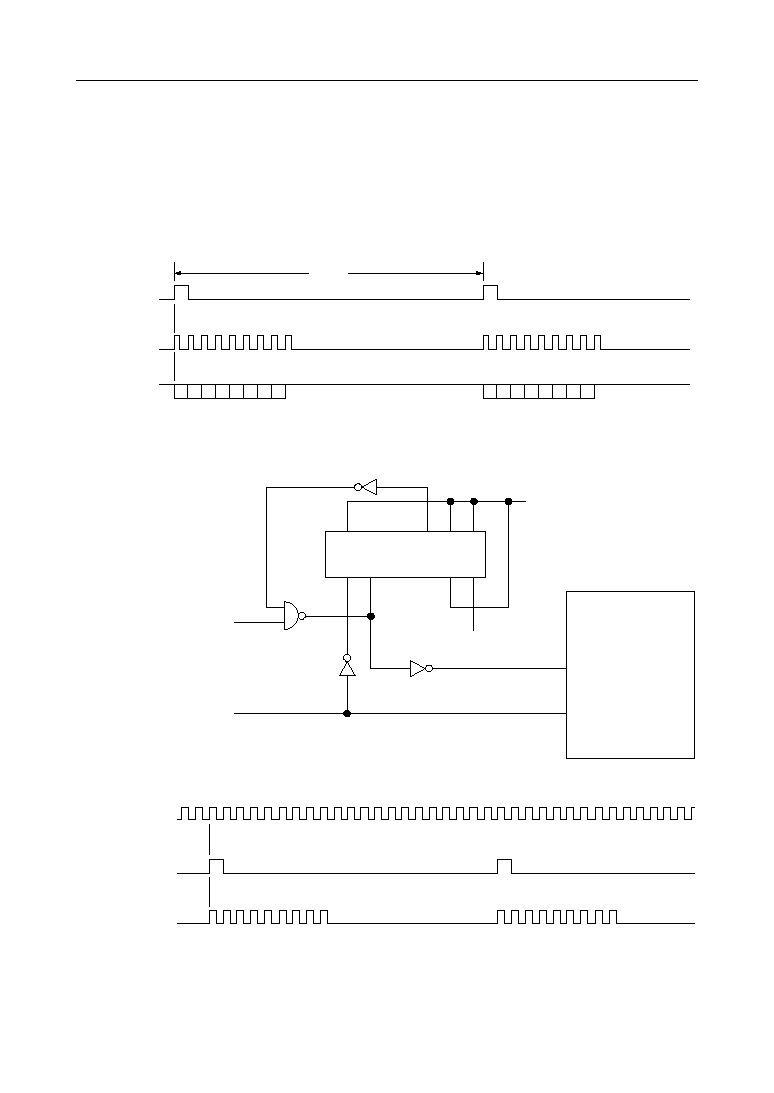

TIMING DIAGRAM

CK64

CK8

B1T or

B2T

B1R or

B2R

1

2

3

4

5

6

7

8

t

SX

t

XS

t

WS

tpd cod

MSB

B2

B3

B4

B5

B6

B7

B8

MSB

t

DS

t

DH

B2

B3

B4

B5

B6

B8

B7

Figure 1 CODEC Timing

Latch Output

DB0 to DB7

PO0 to PO4

WR

RD

CE

A0, A1

t

AW1

t

AW2

t

AR1

t

AR2

t

CW1

t

CW2

t

CR1

t

CR2

T

W

T

R

t

DW1

t

DW2

t

PDDATA

t

PDDATA

t

PDSCN

t

PDLA

Figure 2 Processor Interface Timing

° Semiconductor

MSM6895/6896

24/43

FUNCTIONAL DESCRIPTION

Control Data Description

Sounder control

WRITE Mode

Address Data

AD1 = 0, AD0 = 0

*1.

PDC: This bit is used for the CODEC power-down control. For making this bit valid, "0"s must be written to the control data bits

described in the later section.

PDC = 1: CODEC is in power-down mode. PDC = 0: CODEC is in operation mode.

*2.

When the HOW is indicated, the LOSS output is "1". Otherwise it is "0".

*3.

In the above specification, the data contents written later are valid. The signal of sounder path (SA0, SA1) and the signal of receive path

(RPO) can not be output simultaneously.

Control Data

Make/Break Timing *6

DB7

DB6

DB5

DB4

DB3

DB2

DB1

DB0

0

0

1

PDC

0

0

0

0

*1

0

0

0

0

1

0

0

1

0

0

0

1

1

0

1

0

0

0

1

0

1

0

1

1

0

0

1

1

1

1

0

0

0

1

0

0

0

1

0

1

0

1

0

1

1

1

1

0

0

1

1

0

1

1

1

1

0

X

X

X

X

Output Tone

(Hz)

Frequency

SPT

IR-1

IR-2

SIR-1

CR

HOW

SIR-2

T1K

HR

DT

SDT

RBT

BT

PDT

CRBT

*2

1

Wamble Tone

Wamble Tone

Wamble Tone

Wamble Tone

800 or

Wamble Tone

1

1

400

400

400/16

400

400

400/16

Wamble Tone

Make (Sec) Break1 (Sec) Break2 (Sec)

0.125

1

0.5

0.25

0.125

2

0.5

0.25

∑

--

--

2.25

Continuous

Continuous

0.5

0.25

0.125

Continuous

0.125

1

0.5

0.25

0.5

1

0.25

0.125

0.125

2

0.5

0.25

∑

--

--

--

--

--

--

--

--

Remarks

Tone Output:

SA0, SA1

Tone Output:

RPO, Refer to Table 2

and 4.

Suspends the tones above.

° Semiconductor

MSM6895/6896

25/43

Make

Break1

Break2

Control of function key acknowledge tone

WRITE Mode

Address Data

AD1 = 0, AD0 = 0

*4.

NTTC = 1 when the initial state is set. NTTC can be set as PBTC when the PB tone is set, but the data written into NTTC in later is valid.

When NTTC = 1, the FTONE (1) and FTONE (2) signals are output from SPO. When NTTC = 0, these signals are output from RPO.

NTTC = 1 when FTONE and PB tone is stopped.

*5.

When two or more signals are specified out of IIT, T250 and FTONE, the output signals are compounded by two or three tones.

*6.

The definition of Make/Break Timing is as follows;

Make/Break Timing *6

Control Data

DB7

DB6

DB5

DB4

DB3

DB2

DB1

DB0

0

1

1

X

X

0

0

1

X

X

0

1

0

X

0

1

1

X

1

0

0

0

0

0

0

0

0

0

1

0

1

1

Output Tone

(Hz)

Frequency

IIT

T250

FTONE (1)

FTONE (2)

400

250

1 k

1 k

Make (Sec) Break1 (Sec) Break2 (Sec)

0.25

Continuous

Continuous

0.1

0.25

∑

2.25

--

Suspends the all above tones

Suspends the IIT tone

Suspends the FTONE

Remarks

Tone output:

RPO, SPO

NTTC

*4

0

0

0

0

0

1

0

Suspends the T250 tone

° Semiconductor

MSM6895/6896

26/43

PB tone control

WRITE Mode

Address Data

AD1 = 0, AD0 = 0

Control Data

Output PB Frequency

DB7

DB6

DB5

DB4

DB3

DB2

DB1

DB0

PB

Low

High

Remarks

1

0

1

PBTC

0

0

0

0

0

0

0

1

0

0

1

0

0

0

1

1

0

1

0

0

0

1

0

1

0

1

1

0

0

1

1

1

1

0

0

0

1

0

0

1

1

0

1

0

1

0

1

1

1

1

0

0

1

1

0

1

1

1

1

0

1

1

1

1

X

X

X

X

0

0

1

2

3

A

4

5

6

B

7

8

9

C

*

0

#

D

697 Hz

697 Hz

697 Hz

697 Hz

770 Hz

770 Hz

770 Hz

770 Hz

852 Hz

852 Hz

852 Hz

852 Hz

941 Hz

941 Hz

941 Hz

941 Hz

1209 Hz

1336 Hz

1477 Hz

1633 Hz

1209 Hz

1336 Hz

1477 Hz

1633 Hz

1209 Hz

1336 Hz

1477 Hz

1633 Hz

1209 Hz

1336 Hz

1477 Hz

1633 Hz

Suspends the PB tone

When PBTC = 0, the PB tone is output from the transmit path and the

receive path RPO.

The conditions of internal control signals are MUTN = 0 and NTTC = 0.

When PBTC = 1, the PB tone is output only from the receive path

SPO.

The PB signal is not output from the transmit path.

The conditions of internal control signals are MUTN = 1 and NTTC = 1.

When the initial state is set and the PB tone is suspended,

the conditions of internal control signals are MUTN = 1 and NTTC = 1.

° Semiconductor

MSM6895/6896

27/43

Latch control and timer reset

WRITE Mode

Address Data

AD1 = 0, AD0 = 0

Control data

Latch output

DB7

DB6

DB5

DB4

DB3

DB2

DB1

DB0

1

1

1

0

0

0

0

1

0

0

1

0

0

0

1

1

0

1

0

1

0

1

1

0

0

1

1

1

1

0

0

0

1

0

0

1

1

0

1

0

1

0

1

1

1

1

0

0

1

1

0

1

1

1

1

0

1

1

1

1

0

0

0

0

0

0

0

0

0

0

1

1

1

1

0

0

Latch codes described above

LT1 = 1

LML1 = 1

LMX1 = 1

LT2 = 1

LML2 = 1

LMX2 = 1

LR = 1

LS = 1

LMN = 1

LMR = 1

LA = 1

LB = 1

LC = 1

LD = 1

Remarks

These latch are for internal control and used for control of speech path.

Initially all latch are set to "0". For details of speech path control, refer to Table 1 to 4.

Each latch can be specified independently.

The output at the LML pin is in "1" when either LML1, LML2, or LMR is in "1".

These general latches are for external control. LA, LB, LC, and LD correspond to

the external pin symbols and are set independently. Initially, all latches are set to "0".

Sets the corresponding latches listed above to "0".

Sets all latches listed above to "0".

Resets the watch dog timer.

° Semiconductor

MSM6895/6896

28/43

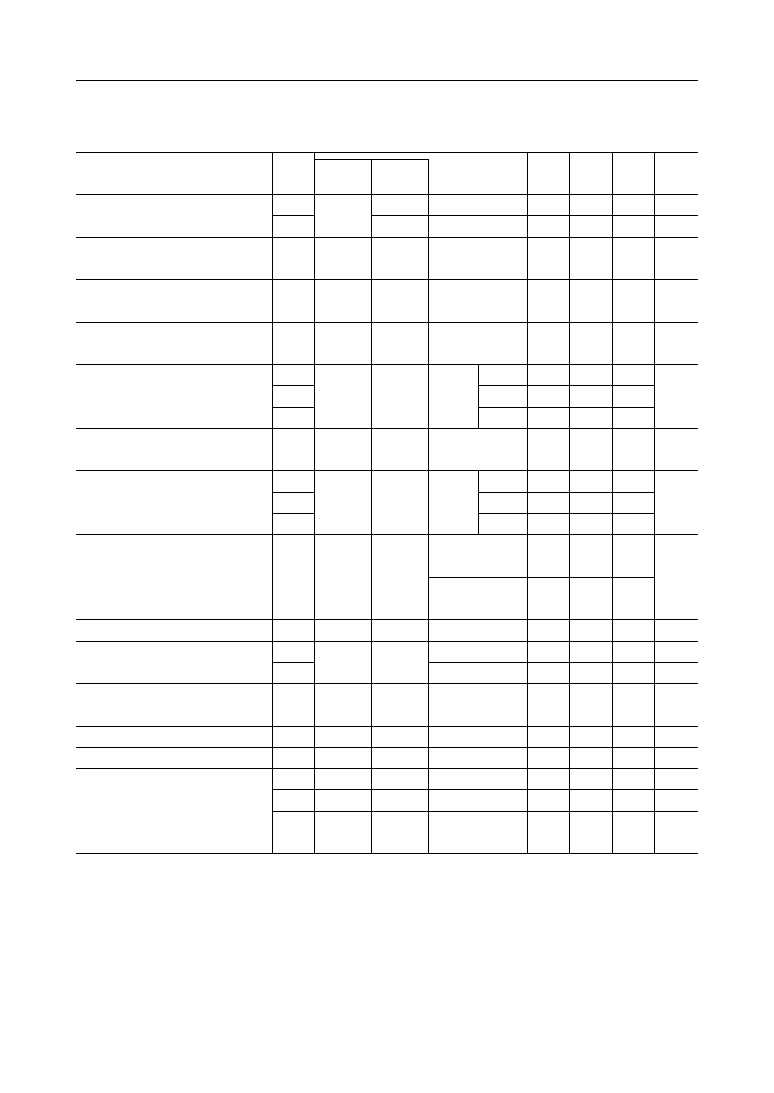

Table 1. Transmit speech path setting list

Status Symbol

TA-1

TA-2

TA-3

TA-4

TA-5

TA-6

TA-7

TB-1

TB-2

TB-3

TB-4

TB-5

TB-6

TB-7

Control Symbol

LML1

LT1 LMX1 LML2

LT2 LMX2 LMN MUTN

0

0

X

--

--

--

X

X

0

1

0

--

--

--

0

1

0

1

0

--

--

--

1

1

0

1

1

--

--

--

0

1

0

1

1

--

--

--

1

1

0

1

X

--

--

--

X

0

1

X

X

--

--

--

X

X

--

--

--

0

0

X

X

X

--

--

--

0

1

0

0

1

--

--

--

0

1

0

1

1

--

--

--

0

1

1

0

1

--

--

--

0

1

1

1

1

--

--

--

0

1

X

X

0

--

--

--

1

X

X

X

X

SG

T

TMX1

PBt

Ht

Output Signal at T1O

1

--

--

--

--

--

1

--

--

--

1

--

--

--

--

--

1

1

--

--

--

--

1

--

--

--

--

--

1

--

--

--

--

--

1

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

SG

T

TMX2

PBt

Ht

Output Signal at T2O

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

1

--

--

--

--

--

1

--

--

--

1

--

--

--

--

--

1

1

--

--

--

--

1

--

--

--

--

--

1

--

--

--

--

--

1

Notes:

1. MUTN of Control Signal is set by PBTC (DB4).

MUTN = 1 when the initial state is set. MUTN = 0 when PBTC = 0. MUTN = 1 when PBTC= 1.

2. SG: Signal ground, T: Transmit signal, TMX1: Transmit addition signal 1, TMX2: Transmit addition signal 2, PBt: PB signal, Ht: Hold

tone signal

3. The output signals of T1O and T2O are the signals added by the signals indicated in "1"s in each column.

° Semiconductor

MSM6895/6896

29/43

Table 2. Receive speech path setting list (RPO output)

Table 3. Control of receive

main amplifier

Notes:

4. R1: Receive signal 1, R2: Receive signal 2, Ts: Side tone signal, RT0: DT, PDT, SDT, CRBT, and IIT, RT1: RBT, BT, and T250, FT:

FTONE and PBr: PB acknowledge signal.

5. Output Signal RPO is the signal added by the signal indicated in "1"s in each column.

6. "0"s of Control Signal NTTC are equivalent to "1"s of the Output Signals FT and PBr, and "1"s are equivalent to "0"s of Output Signals.

7. Control Signals MUTN and NTTC are the internal control signals. Initially, both signals are in "1"s. MUTN is controlled by PBTC

of controlling the PB tone.

MUTN = 0 when PBTC = 0. MUTN = 1 when PBTC = 1.

NTTC is controlled by PBTC of controlling the PB tone or NTTC of controlling the function key acknowledge tone, but the NTTC

data written later is valid.

NTTC = 0 when PBTC = 0. NTTC = 1 when PBTC = 1.

Control Signal

LR

0

1

RMO0 and RMO1

SG

Input signal to RMI

Output signal of

Status Symbol

RP-1

RP-2

RP-3

RP-4

RP-5

RP-6

RP-7

RP-8

RP-9

RP-10

RP-11

RP-12

RP-13

RP-14

Control Signal

LS

LT1

LT2

LMN MUTN NTTC

0

0

0

0

0

0

0

0

0

0

1

1

1

1

0

1

1

1

0

0

0

1

1

1

0

1

0

1

0

0

0

0

1

1

1

1

1

1

0

0

1

1

X

0

0

1

0

0

1

0

0

1

X

X

X

X

X

1

0

X

1

0

X

1

0

X

X

X

X

X

0/1

0/1

0/1

0/1

0/1

0/1

0/1

0/1

0/1

0/1

X

X

X

X

Output Signal at RPO

R2

Ts

RT0

RT1

FT

PBr

R1

--

1

1

1

--

--

--

1

1

1

--

1

--

1

--

--

--

--

1

1

1

1

1

1

--

--

1

1

--

1

--

--

1

--

--

1

--

--

--

--

--

--

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1/0

1/0

1/0

1/0

1/0

1/0

1/0

1/0

1/0

1/0

--

--

--

--

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1/0

1/0

1/0

1/0

1/0

1/0

1/0

1/0

1/0

1/0

--

--

--

--

° Semiconductor

MSM6895/6896

30/43

Table 4. Receive speech path setting list (SPO)

Status Symbol

RS-1

RS-2

RS-3

RS-4

RS-5

RS-6

RS-7

RS-8

RS-9

RS-10

RS-11

Control Signal

LS

LT1

LT2 NTTC

LMR

0

0

0

1

1

1

1

1

1

1

1

0

0

1

0

0

0

0

1

1

1

1

X

X

X

0

1

0

1

0

1

0

1

X

X

X

0

0

1

1

0

0

1

1

0

1

0/1

X

X

X

X

X

X

X

X

Output Signal at SPO

SG

1

--

--

--

--

--

--

--

--

--

--

R1

--

--

--

--

1

--

1

--

1

--

1

R2

--

--

--

--

--

1

1

--

--

1

1

RT0

--

--

--

1

1

1

1

1

1

1

1

RT1

--

--

--

1

1

1

1

1

1

1

1

FT

--

1

0/1

1

1

1

1

1

1

1

1

PBr

--

1

0/1

1

1

1

1

1

1

1

1

Hr

--

--

1

--

--

--

--

1

1

1

1

Notes:

8. SG: Signal ground, R1: Receive signal 1, R2: Receive signal 2, Hr: Hold acknowledge tone, PBr: PB acknowledge tone, FT: FTONE,

RT0: DT, PDT, SDT, CRBT, and IIT and RT1: RBT, BT, and T250.

9. An Output Signal at SPO is the signal added by the signal indicated in "1"s in each column.

10. The Control Signal NTTC is defined equally to Notes : 7.

° Semiconductor

MSM6895/6896

31/43

Channel selector control

WRITE Mode

Address Data

AD1 = 0, AD0 = 1

Control Data

DB7

DB6

DB5

DB4

DB3

DB2

DB1

DB0

0

0

0

0

0

0

0

0

0

0

1

0

1

0

0

1

1

1

0

0

1

0

1

1

1

0

1

1

1

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

1

X

X

X

X

X

X

1

X

1

X

1

X

X

X

X

X

X

X

X

1

A1

A2

A3

A4

B1

B2

B3

B4

C

D1

D2

D3

D4

Symbol

Status

Main Connection Status

B1T®"1"

B1T®DOUT

B1T®BT1

B1T®BT2

B2T®"1"

B2T®DOUT

B2T®BT1

B2T®BT2

B1T®B2R

B1T®B1R

B2T®B2R

BT1∆BR1

BT2∆BR2

B1R∆No connection

B1R∆DIN

B1R∆BR1

B1R∆BR2

B2R∆No connection

B2R∆DIN

B2R∆BR1

B2R∆BR2

B2T®B1R

Remarks

Different groups (A, B, C, and D) are set

independently.

For setting the same group, the data written later is

valid.

Refer to Table 5 and 6 for details.

The initial statuses are A1 and B2.

° Semiconductor

MSM6895/6896

32/43

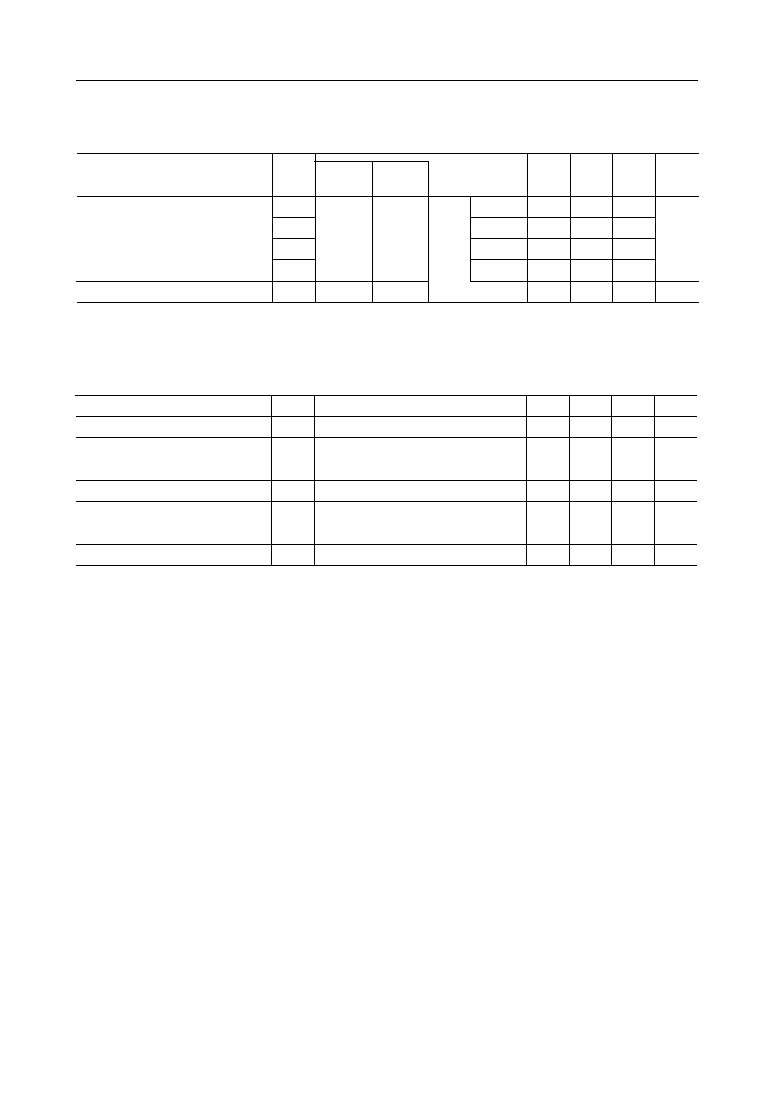

Table 6. Output pin status by the combination of A and B

Table 5. Output pin connection status by channel selector control

Notes: 11. *1. According to the combination of A and B (Table 6).

*2. One of statuses A1 to A4 is held.

*3. One of statuses B1 to B4 is held.

*4. One of statuses A1 to A4 or one of statuses B1 to B4,

whichever is written later, is held.

When the setting of C is performed before the setting

of D group, the setting of D must be performed after

the setting of the group A and B.

12. The statuses of the pins indicated by "--" is not

affected.

13. DIN is connected to the digital input of CODEC and

DOUT is connected to the digital output of CODEC.

*5.

When writing is performed in the sequence of setting of A and

setting of B, the output status becomes B2R, and when writing

is performed in the sequence of setting of B and setting of A, the

output status becomes B1R.

Status

Symbol

A1

A2

A3

A4

B1

B2

B3

B4

C

D1

D2

D3

D4

1

DOUT

BT1

BT2

--

--

--

--

B2R

B1R

*2

*2

*2

--

--

--

--

1

DOUT

BT1

BT2

B1R

*3

B2R

*3

*3

*1

B1R

*1

*1

*1

B2R

*1

*1

--

--

--

--

--

*1

*1

B1R

*1

*1

*1

B2R

*1

--

*4

*4

BT1

*4

A1

A2

A3

BIT

B2T

DIN

BR1

Setting of A

Output Pin Connection Status

Initial Setting

Initial Setting

Remarks

A4

Setting of B

B1

B2

B3

B4

B1

B2

B3

B4

B1

B2

B3

B4

B1

B2

B3

B4

1

B2R

1

1

B1R

B1R or B2R

B1R

B1R

1

B2R

1

1

1

B2R

1

1

1

1

B2R

1

1

1

B2R

1

B1R

B1R

B1R or B2R

B1R

1

1

B2R

1

1

1

1

B2R

1

1

1

B2R

1

1

1

B2R

B1R

B1R

B1R

B1R or B2R

DIN

BR1

BR2

Output Pin Connection Status

Initial Setting

DIN *5

BR1 *5

BR2 *5

Remarks

*1

*1

*1

B1R

*1

*1

*1

B2R

--

*4

*4

*4

BT2

BR2

° Semiconductor

MSM6895/6896

33/43

key scanning output control and interrupt

WRITE Mode

Address Data

AD1 = 1, AD0 = 0

Control Data

DB7

DB6

DB5

DB4

DB3

DB2

DB1

DB0

0

0

0

Output Data

1

X

X

X

X

X

X

X

Remarks

Resets the INTT output and sets to "1".

This control data is valid only when written, it is not held.

Initially, PO4 to PO0 are left open.

When the data is "0", the output goes to "0", when the data is "1", the output is left open.

The output statuses are held until the data is rewritten.

The data set in DB4 to DB0 is output from output pins PO4 to PO0, respectively.

° Semiconductor

MSM6895/6896

34/43

Sounder, volume, and tone combination

WRITE Mode

Address Data

AD1 = 1, AD0 = 1

Control Data

DB7

DB6

DB5

DB4

DB3

DB2

DB1

DB0

0

0

X

X

X

X

0

0

0

1

1

0

1

1

0

0

0

0

0

1

0

1

0

0

1

1

1

0

1

1

1

0

1

1

1

X

X

Remarks

The setting of volume and tone

combination is performed

simultaneously, not

independently.

Initially the high volume is set,

and tone combination is set

externally.

Control

Volume 1 (High)

Volume 2 (Medium)

Volume 3 (Low1)

Volume 4 (Low2)

Tone combination setting (Initial setting) by external control (SW0, SW1)

Tone combination 1 (1.0 kHz and 1.3 kHz, 16 Hz Wamble period)

Tone combination 2 (0.8 kHz and 1.0 kHz, 16 Hz Wamble period)

Tone combination 3 (0.8 kHz and 1.0 kHz, 8 Hz Wamble period)

Tone combination 4 (0.5 kHz and 0.65 kHz, 16 Hz Wamble period)

Tone combination 5 (0.4 kHz and 0.5 kHz, 16 Hz Wamble period)

Tone combination 6 (0.4 kHz and 0.5 kHz, 8 Hz Wamble period)

° Semiconductor

MSM6895/6896

35/43

CODEC power down control

WRITE Mode

Address Data

AD1 = 1, AD0 = 1

Contorol Data

DB7

DB6

DB5

DB4

DB3

DB2

DB1

DB0

0

1

X

X

X

0

0

0

1

0

1

1

1

0

1

1

1

1

0

0

Remarks

CODEC power-down is controlled by PDC (DB4) during sounder

Control

control. (Initial setting)

PDC = 0 CODEC power-on

PDC = 1 CODEC power-down

CODEC Transmit power-down

CODEC Receive power-down

CODEC Transmit and Receive power-down

CODEC power-down release

Data written later is valid.

° Semiconductor

MSM6895/6896

36/43

Gain control

WRITE Mode

Address Data

AD1 = 1, AD0 = 1

DB7

DB6

DB5

DB4

DB3

DB2

DB1

DB0

DB7

1

0

X

X

X

X

0

0

0

1

1

X

1

1

X

X

1

0

X

X

0

1

X

X

0

0

X

X

Remarks

The gain setting of the transmit path

and the receive path can be performed

simultaneously, not independently.

Control

Sets the transmit PB tone and hold tone level at the typical

value.(Initial setting)

Sets the transmit PB tone and hold tone level by 3 dB below the

typical value.

Sets the transmit PB tone and hold tone level by 6 dB below the

typical value.

Sets the receive gain at the typical value. (Initial setting)

Sets the receive gain by 3 dB above the typical value.

Sets the receive gain by 6 dB above the typical value.

Sets the receive gain by 9 dB above the typical value.

° Semiconductor

MSM6895/6896

37/43

Howler tone color combination

WRITE Mode

Address Data

AD1 = 1, AD0 = 0

Key scanning data read out

READ Mode

Address Data

AD1 = 1, AD0 = 0

Control Data

DB7

DB6

DB5

DB4

DB3

DB2

DB1

DB0

1

1

X

X

X

X

X

0

1

Control

Howler tone frequency: 0.8 kHz

Howler tone frequency: 1.0 kHz and 1.3 kHz, 16 Hz Wamble period

Remarks

Initial setting

DB7

DB6

DB5

DB4

DB3

DB2

DB1

DB0

PI7

PI6

PI5

PI4

PI3

PI2

PI1

PI0

Control

The data input to the pins PI7 to PI0 is output from DB7 to DB0, respectively.

° Semiconductor

MSM6895/6896

38/43

APPLICATION CIRCUIT

Handset

Speaker

AG

100 k

W •

2

0.47

m

F

DG

1

m

F

+5 V

Line

Line Interface

Controller

DG

AG

100 k

W

LED

AG

0.47

m

F

Driver

+5 V analog

+5 V

1

m

F

10

m

F

100 k

W

100 k

W •

8

AG

+5 V analog

0.1

m

F

1

m

F

10

m

F

+

Melody Tone

Generation

+

DG

Swith the sounder

tone combination

TPAO

TPBI

TMX1I

TMX2I

R2I

T1O

CAI

MLDY

LML

SW0

SW1

B1T

B1R

B2T

B2R

CK8

CK64

BT1

BT2

TEST

CK1536

WR RD

AD0

DB7 to DB0

INTT

TIME

RESET

VA

VD

VAG

VDG

AD1

VSGC

PO0

PO1

PO2

PO3

PO4

PI0

PI1

PI2

PI3

PI4

PI5

PI6

PI7

TPAI

VSG

CAO

R1I RPO

RMI

RMO0

RMO1

SPO

SAO

SA1

LA

LB

MSM6895

Sounder

SW Matrix

0 V analog

CE

0-20

W

° Semiconductor

MSM6895/6896

39/43

Application circuit at the PCM Signal Data Rate of 192, 384, 768, 1536 and 2048

kbps.

BCLOCK signal

When the PCM signal data rate is one of 192, 384, 768, 1536, and 2048 kbps, input the 9-bit burst

clock corresponding to the frequency equivalent to each of the data rates, as CK64 signal.

PCMIN/OUT

CK64

CK8

125 mS

1 2 3 4 5 6 7 8

1 2 3 4 5 6 7 8 9

Burst clock generator

Burst Clock

CK64

CK8

MSM6895/6896

Equivalent to the 74LS161

+5 V

16

11 10

9

1

2

7

8

0 V

Continuous Clock

8 kHz

Syncronous Signal

Syncronous Signal

Continuous Clock

° Semiconductor

MSM6895/6896

40/43

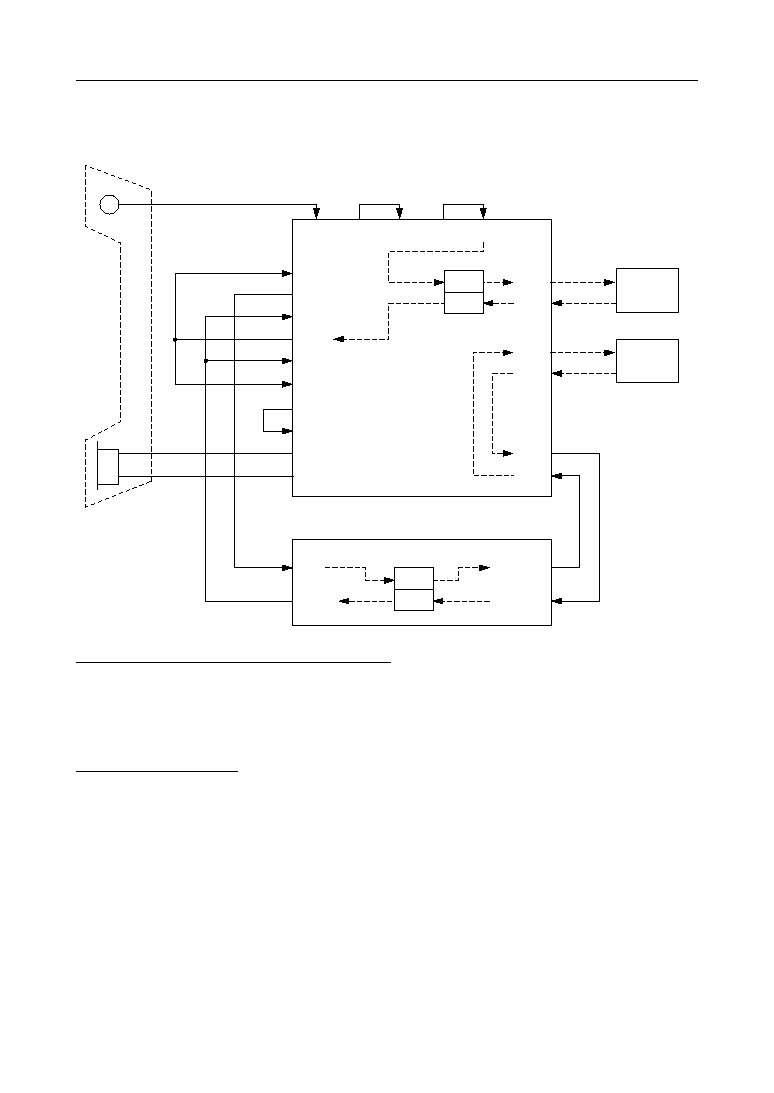

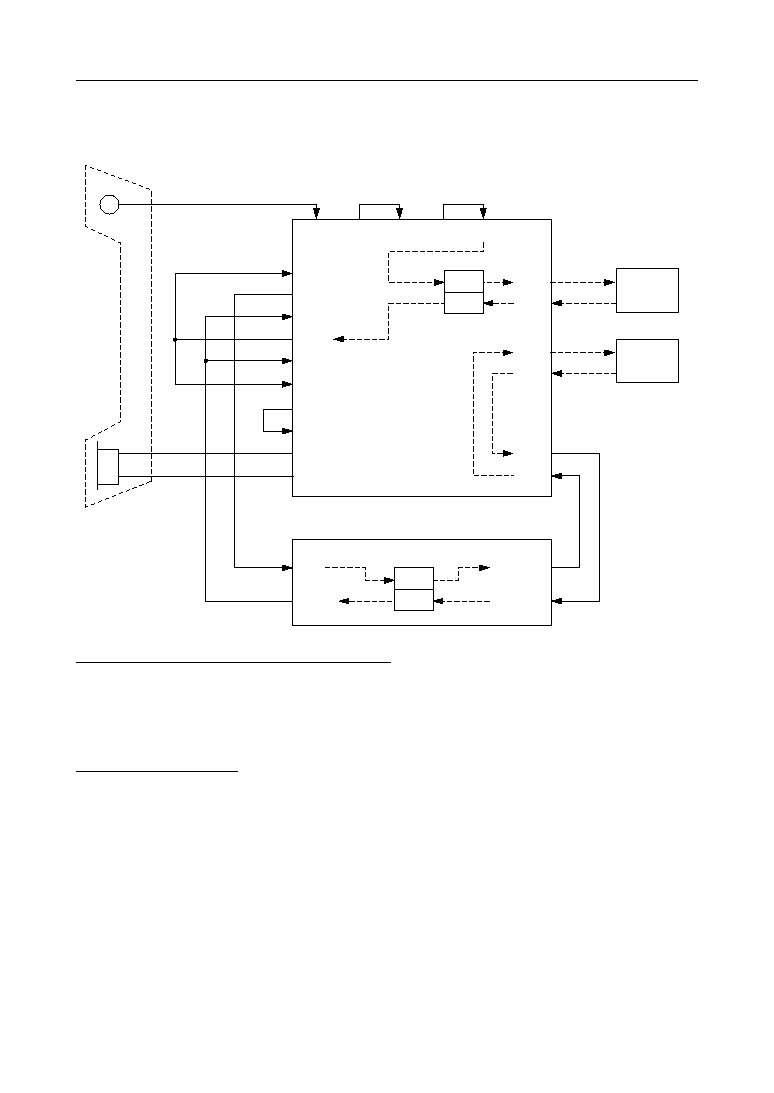

Application Circuit of Three-party Speech Path

TPAI

CAO

T2O

TMX1I

R2I

RMO0

(A)

RMO1

RPO

M

Note:

(A) indicates

the voice signal of

the A speaker

Speaker A

Handset

Speaker B

(B)

TPAO

(A + C)

(B)

B1T

B1R

TPBI

T1O

CAI

TMX2I

AD

R1I

RMI

(B + C)

(A + B)

(C)

(B)

(C)

(B)

DA

(A + B)

(C)

Speaker C

B2T

B2R

BR2

BT2

AD

DA

PCMOUT

PCMIN

AIN

AOUT

(A + B)

(C)

MSM6895

MSM7508

(A)

(A + C)

Speech path setting (Speech through a handset)

Transmit:

TA-4 (LT1 = 1, LMX1 = 1, LMN = 0, MUTN = 1)

TB-4 (LT2 = 1, LMX2 = 1, LMN = 0, MUTN = 1)

Receive:

RP-8 (LT1 = 1, LT2 = 1, LMN = 0, MUTN = 1, LR = 1)

Channel selector control

A2, B4

° Semiconductor

MSM6895/6896

41/43

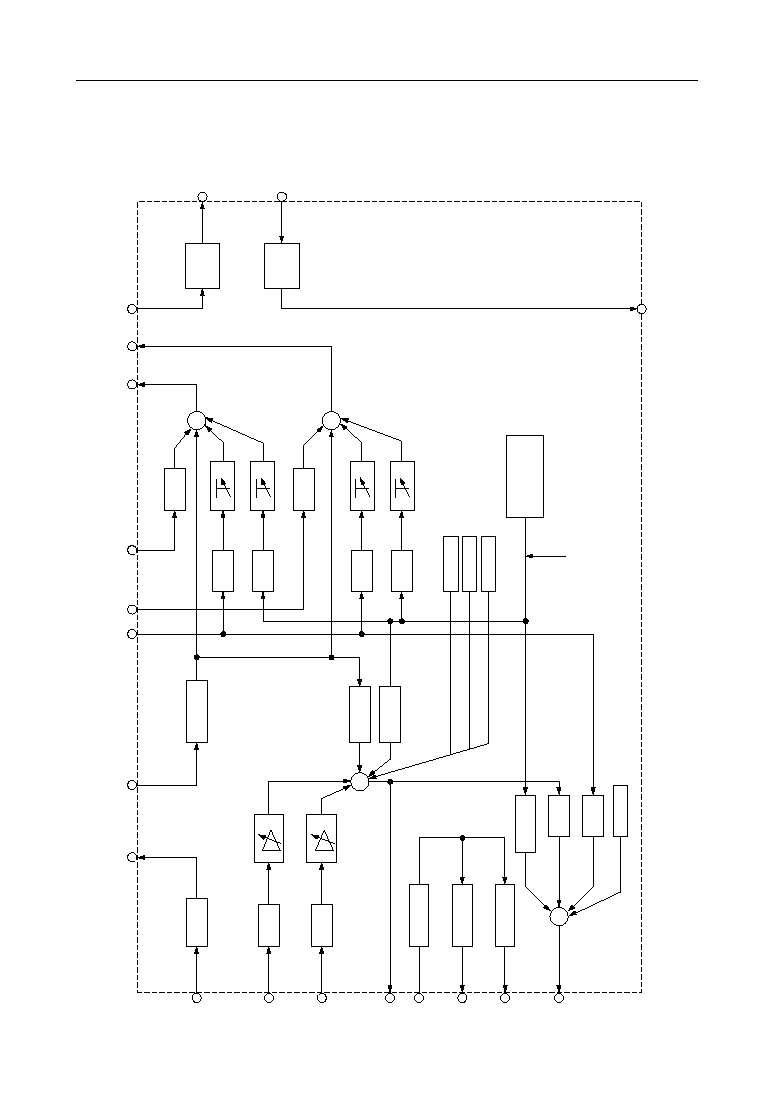

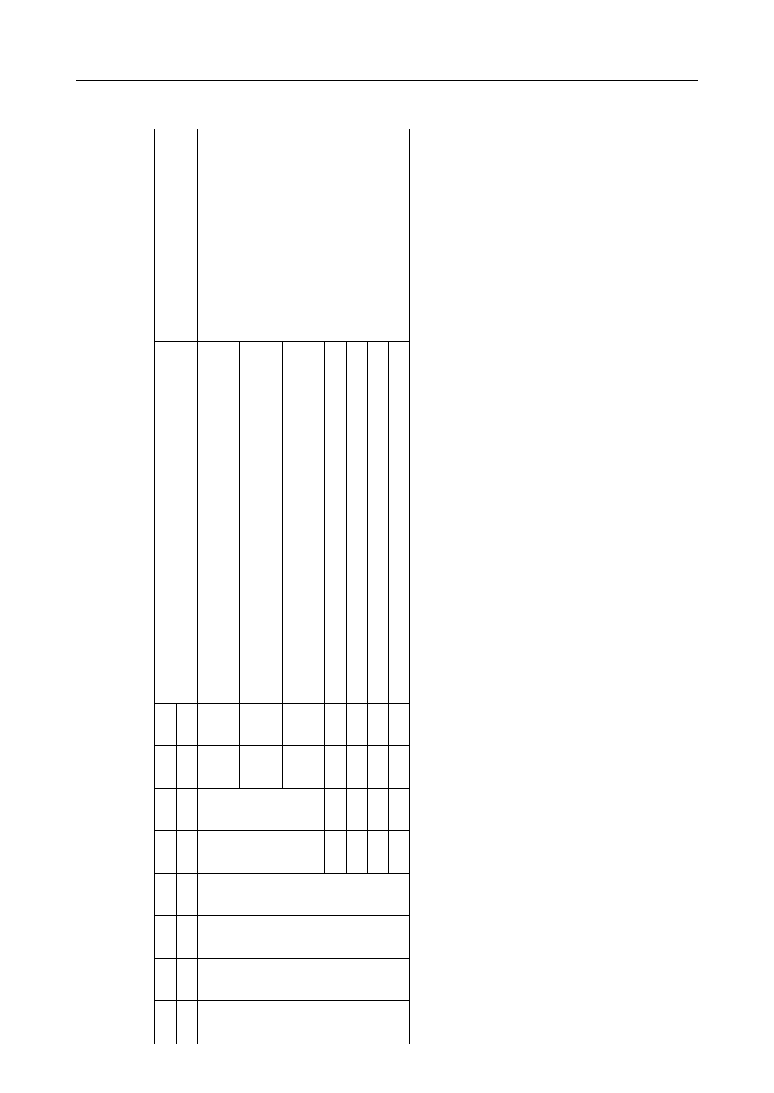

SPEECH PATH GAIN

TPAI

R1I

R2I

RPO

RMI

RMO0

RMO1

SPO

+20 dB

≠6 dB

≠6 dB

+15.3 dB

X 1

X≠1

≠6.8 dB

0 dB

≠3 dB

+

+

+

≠

0, 3, 6, 9 dB

0, 3, 6, 9 dB

+17.7 dB

≠2 dB

≠8.8 dB

+6 dB

0 dB

0 dB

≠2 dB

+6 dB

≠6.8 dB

0, ≠3, ≠6dB

0, ≠3, ≠6dB

0, ≠3, ≠6 dB

0, ≠3, ≠6 dB

AD

0 dB

DA

0 dB

TPAO

TPBI

MLDY

TMX2I

TMX1I

T1O

T2O

CAI

(Maximum input of

1.2 V

op

)

CAO

(Maximum input of

1.2 V

op

)

RTONE1

RTONE2

FTONE

91.7 mV

PP

(DT, PDT, SDT, CRBT)

157 mV

PP

(RBT, BT, T250)

161 mV

PP

189 mV

PP

≠21.4 dBV (240 mV

PP

per signal)

PB

tone

Generator

FTONE

° Semiconductor

MSM6895/6896

42/43

RECOMMENDATIONS FOR ACTUAL DESIGN

∑ To assure proper electrical characteristics, use bypass capacitors with excellent high frequency

characteristics for the power supply and keep them as close as possible to the device pins.

∑ Connect the AG pin and the DG pin each other as close as possible. Connect to the system

ground with low impedance.

∑ Mount the device directly on the board when mounted on PCBs. Do not use IC sockets. If an

IC socket is unavoidable, use the short lead type socket.

∑ When mounted on a frame, use electro-magnetic shielding, if any electro-magnetic wave

source such as power supply transformers surround the device.

∑ Keep the voltage on the V

DD

pin not lower than ≠0.3 V even instantaneously to avoid latch-

up phenomenon when turning the power on.

∑ Use a low noise (particularly, low level type of high frequency spike noise or pulse noise)

power supply to avoid erroneous operation and the degradation of the characteristics of these

devices.

∑ Unused analog input pins must be connected to the VSG pin and unused digital pins must

be connected to the GND pin.

° Semiconductor

MSM6895/6896

43/43

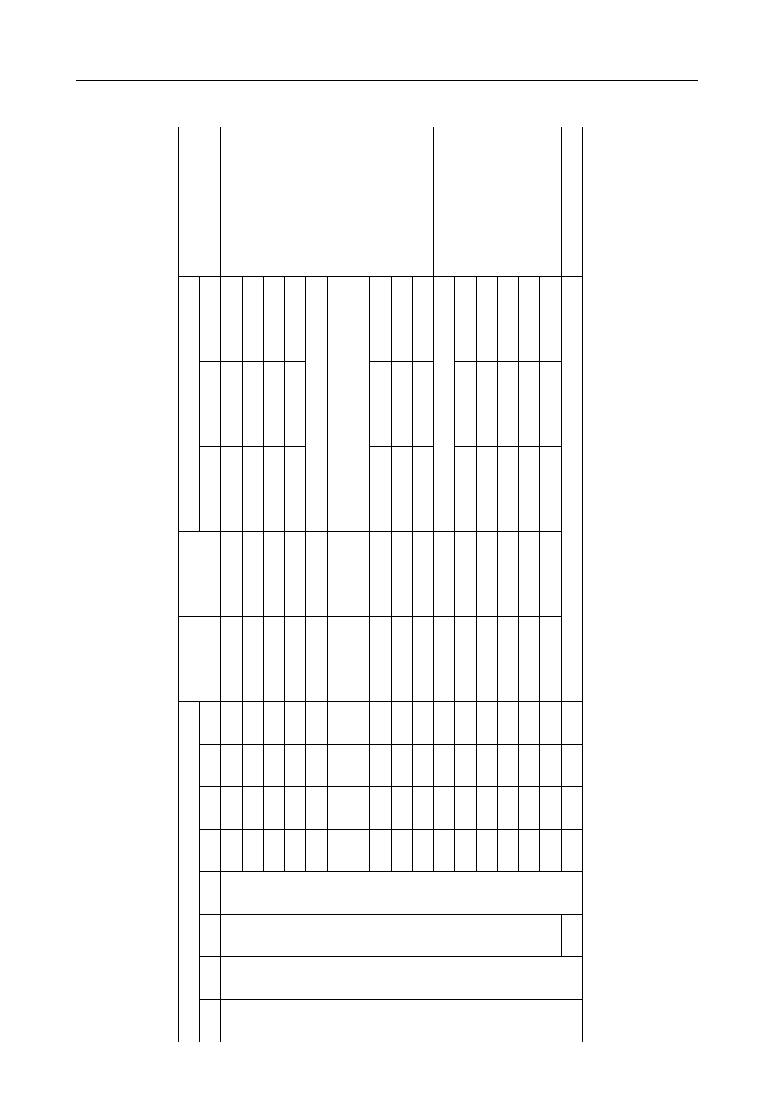

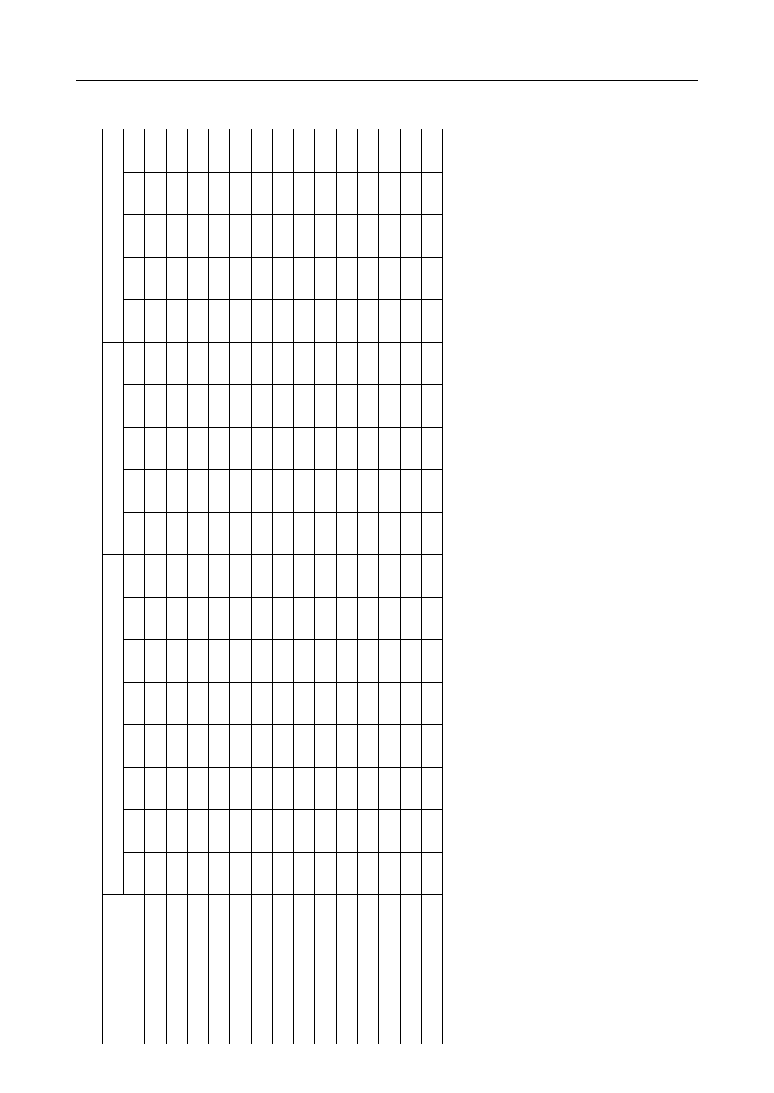

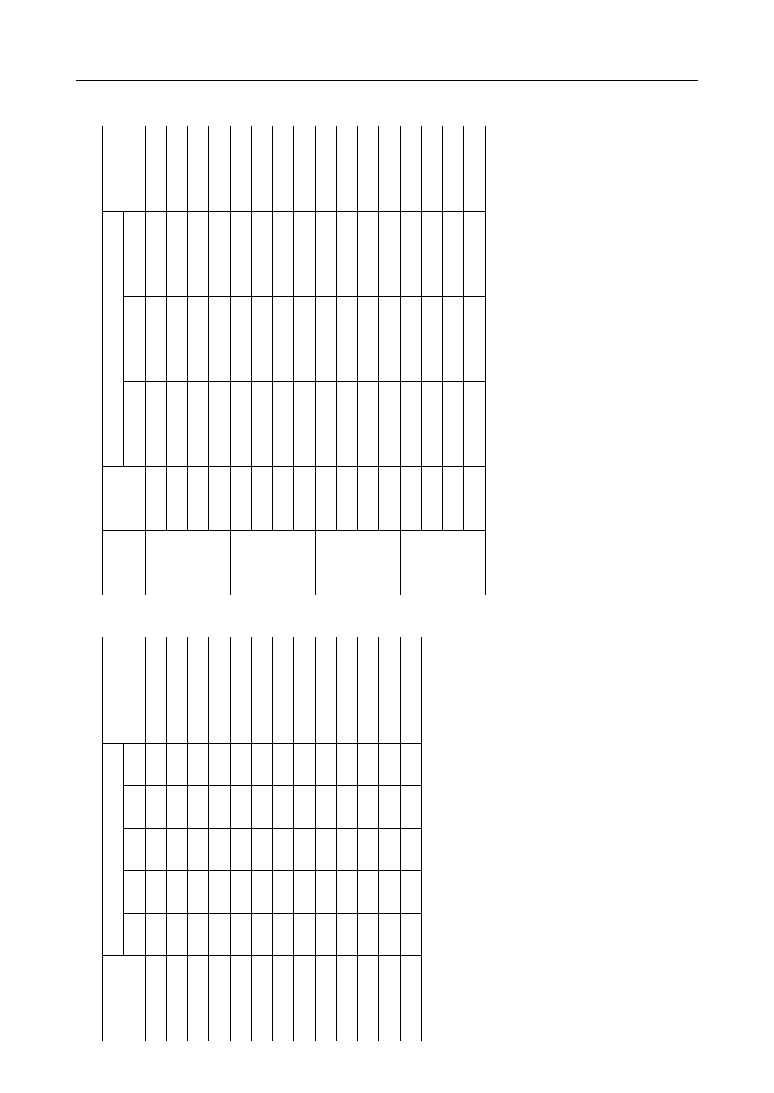

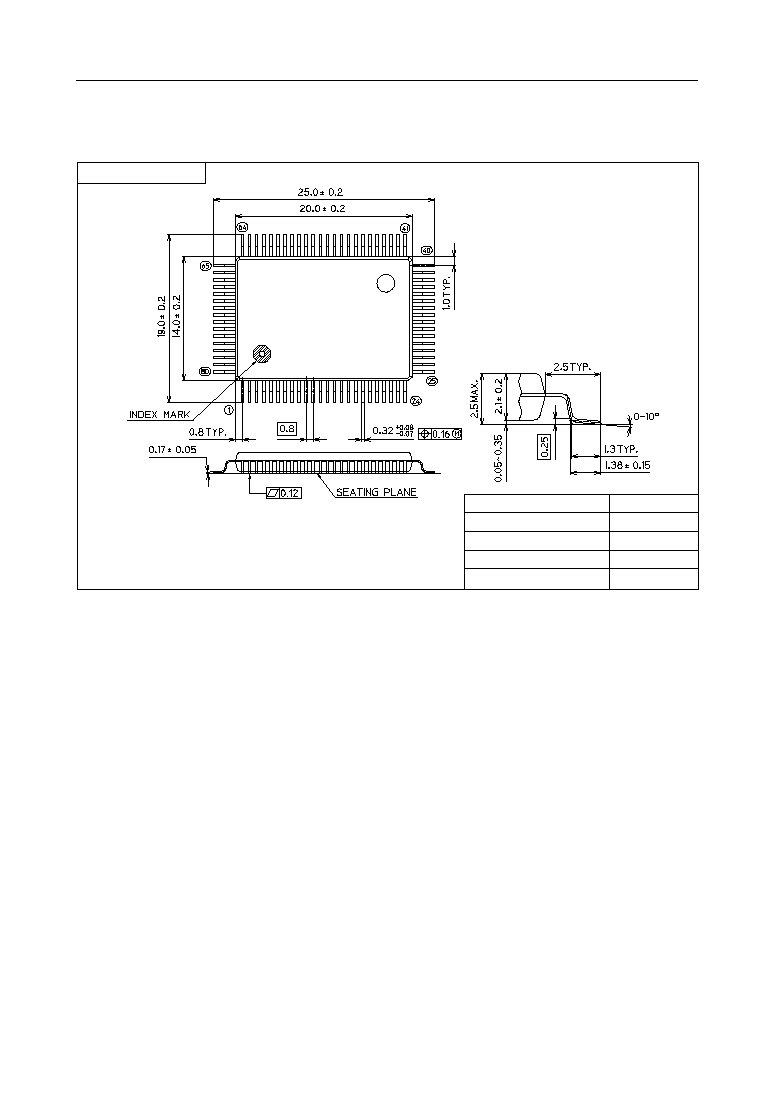

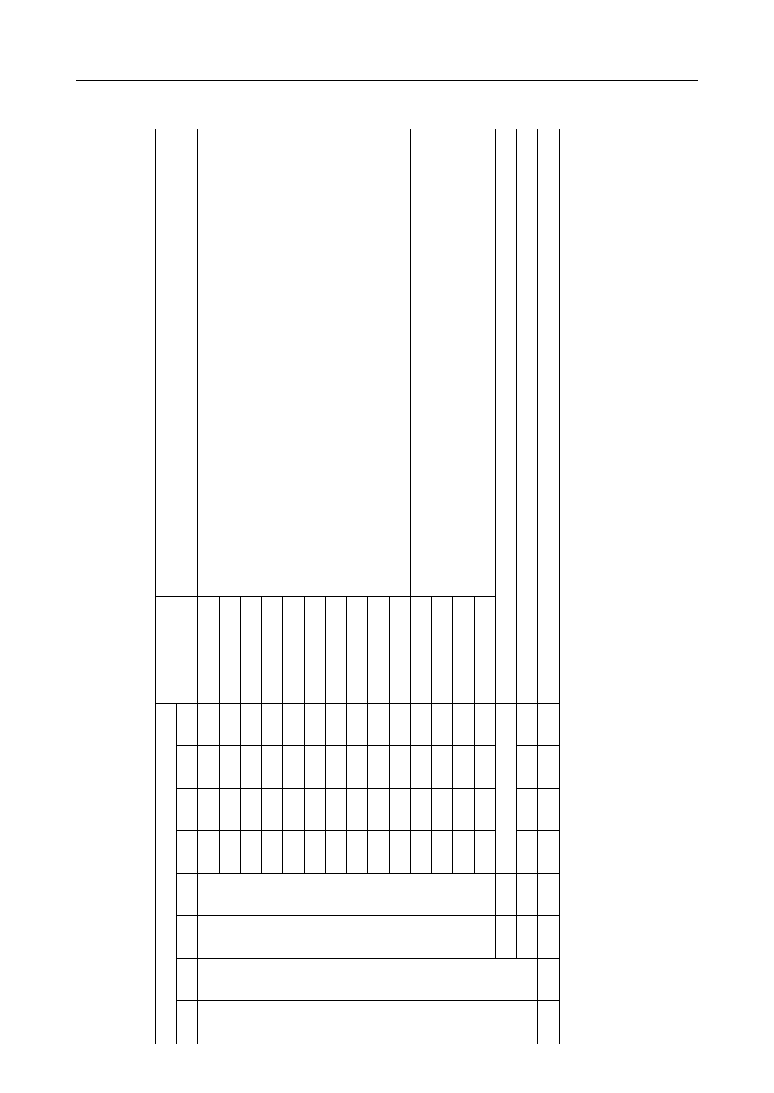

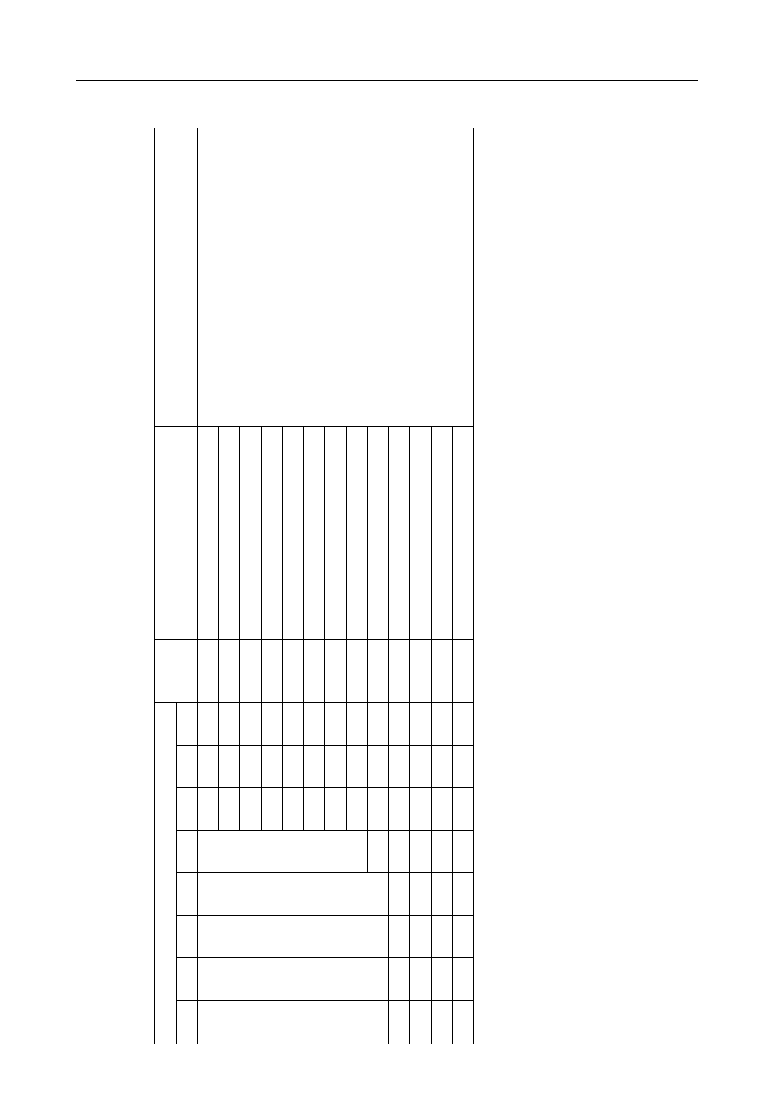

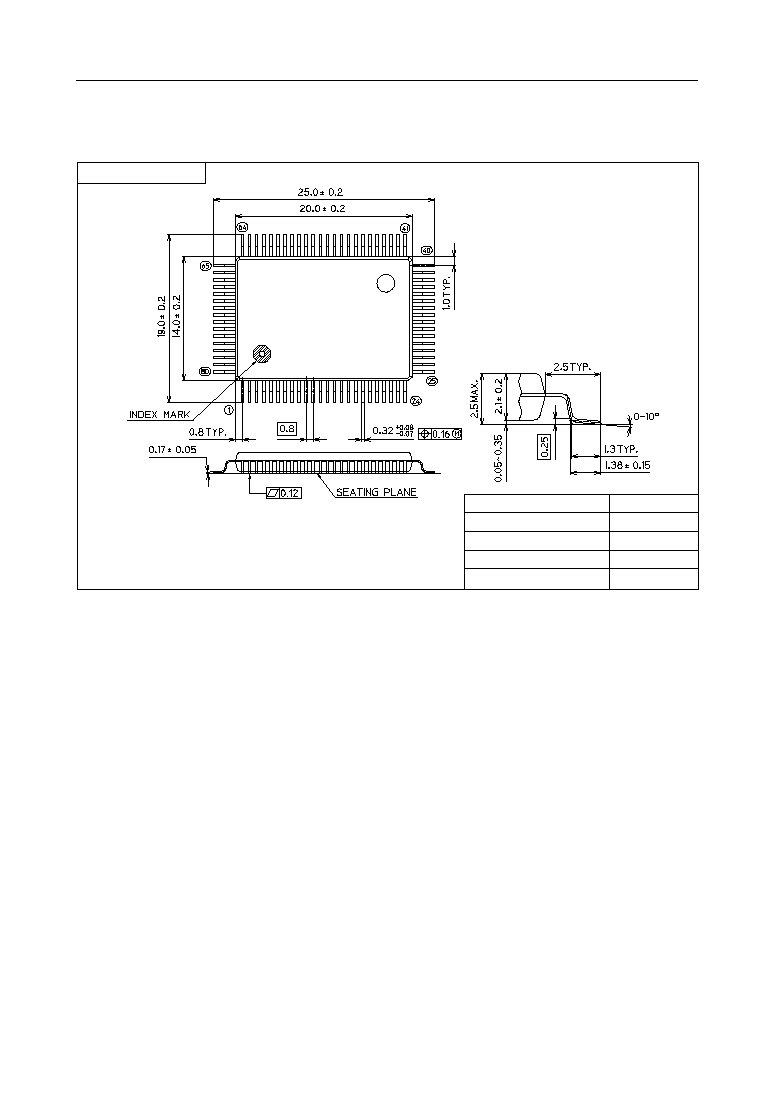

(Unit : mm)

PACKAGE DIMENSIONS

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which

are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the

product name, package name, pin number, package code and desired mounting conditions

(reflow method, temperature and times).

QFP80-P-1420-0.80-BK

Package material

Lead frame material

Pin treatment

Solder plate thickness

Package weight (g)

Epoxy resin

42 alloy

Solder plating

5 mm or more

1.27 TYP.

Mirror finish