| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: 4239-52 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Page 1 of 8

Document No. 70-0068-01

www.psemi.com

©2005 Peregrine Semiconductor Corp. All rights reserved.

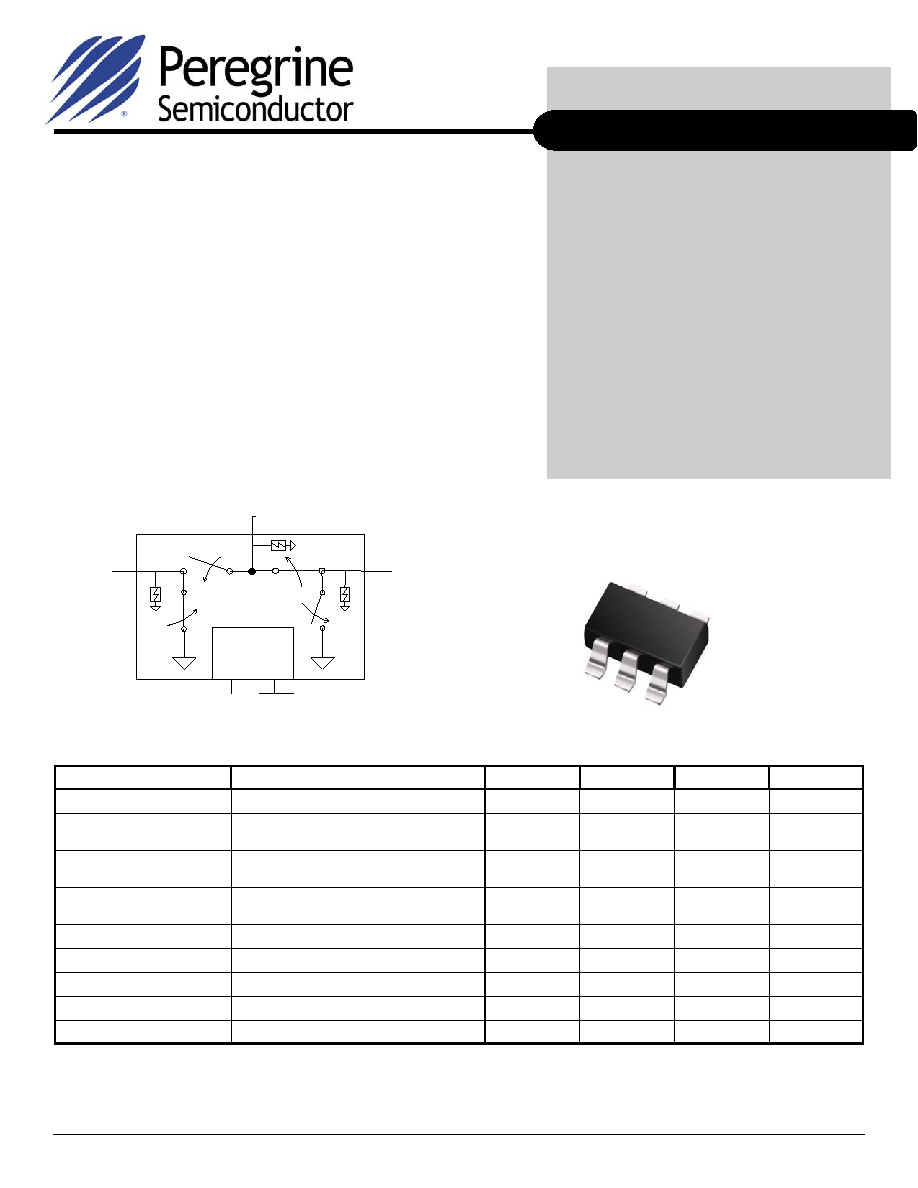

RFCommon

RF1

RF2

CMOS

Control

Driver

CTRL CTRL or V

DD

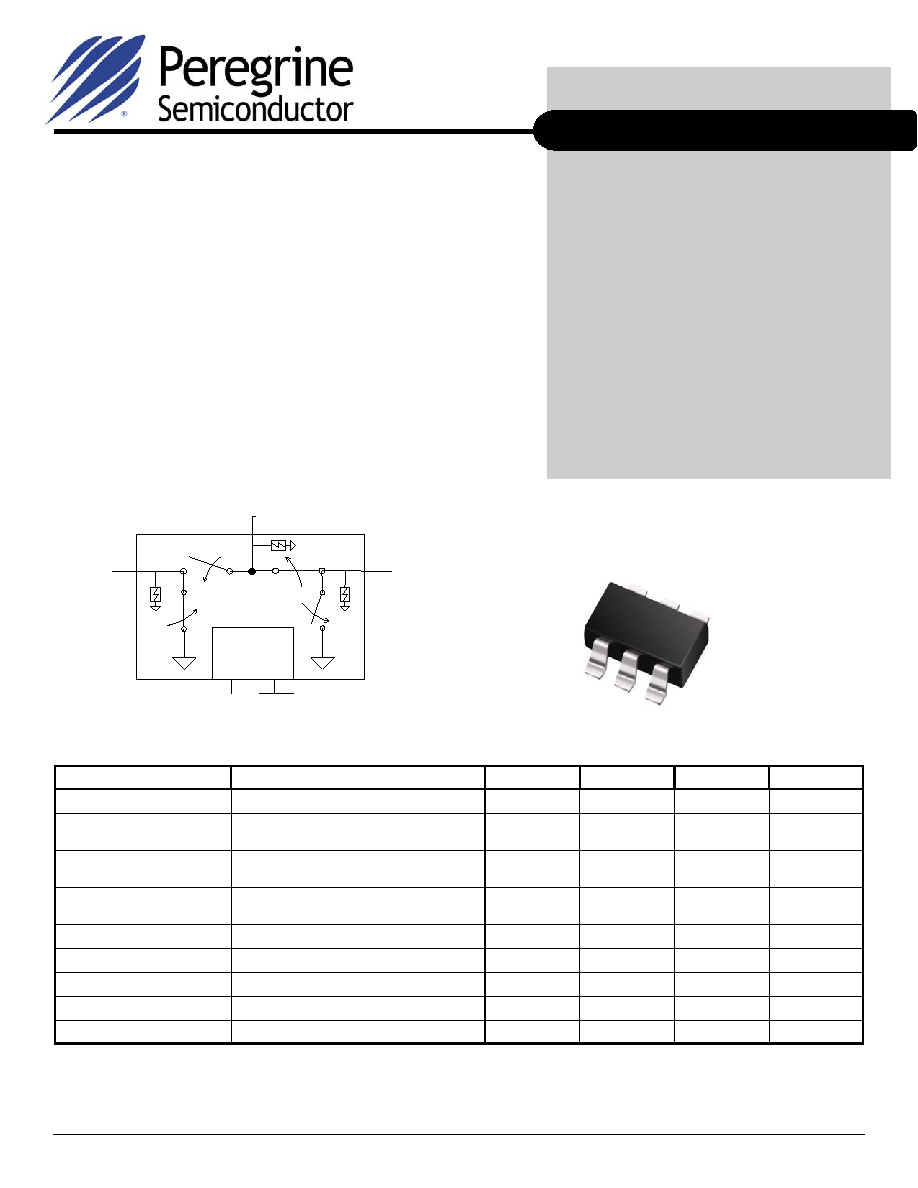

The PE4239 UltraCMOSTM RF Switch is designed to cover a

broad range of applications from DC through 3.0 GHz. This

reflective switch integrates on-board CMOS control logic with a

low voltage CMOS-compatible control interface, and can be

controlled using either single-pin or complementary control

inputs. Using a nominal +3-volt power supply voltage, a typical

input 1 dB compression point of +27 dBm can be achieved.

The PE4239 UltraCMOSTM RF Switch is manufactured in

Peregrine's patented Ultra Thin Silicon (UTSiÆ) CMOS

process, offering the performance of GaAs with the economy

and integration of conventional CMOS.

Product Specification

SPDT UltraCMOSTM RF Switch

Product Description

Figure 1. Functional Diagram

Figure 2. Package Type SC-70

PE4239

Features

∑

Single-pin or complementary CMOS

logic control inputs

∑

+3.0-volt power supply needed for

single-pin control mode

∑

Low insertion loss: 0.7 dB at 1.0 GHz,

0.9 dB at 2.0 GHz

∑

Isolation of 32 dB at 1.0 GHz, 23 dB at

2.0 GHz

∑

Typical input 1 dB compression point of

+27 dBm

∑

Ultra-small SC-70 package

Parameter Conditions

Minimum

Typical

Maximum

Units

Operation Frequency

1

DC

3000

MHz

Insertion Loss

1000 MHz

2000 MHz

0.7

0.9

0.85

1.05

dB

dB

Isolation

1000 MHz

2000 MHz

30

21

32

23

dB

dB

Return Loss

1000 MHz

2000 MHz

18

16

20

18

dB

dB

`ON' Switching Time

50% CTRL to 0.1 dB of final value, 1 GHz

300

ns

`OFF' Switching Time

50% CTRL to 25 dB isolation, 1 GHz

200

ns

Video Feedthrough

2

15

mV

pp

Input 1 dB Compression

2000 MHz

26

27

dBm

Input IP3

2000 MHz, 14 dBm input power

43

45

dBm

Notes: 1. Device linearity will begin to degrade below 10 MHz.

2. The DC transient at the output of any port of the switch when the control voltage is switched from Low to High or High to Low in a 50

test

set-up, measured with 1ns risetime pulses and 500 MHz bandwidth.

Table 1. Electrical Specifications @ +25 ∞C, V

DD

= 3 V (Z

S

= Z

L

= 50

)

6-lead SC-70

Product Specification

PE4239

Page 2 of 8

©2005 Peregrine Semiconductor Corp. All rights reserved.

Document No. 70-0068-01

UltraCMOSTM RFIC Solutions

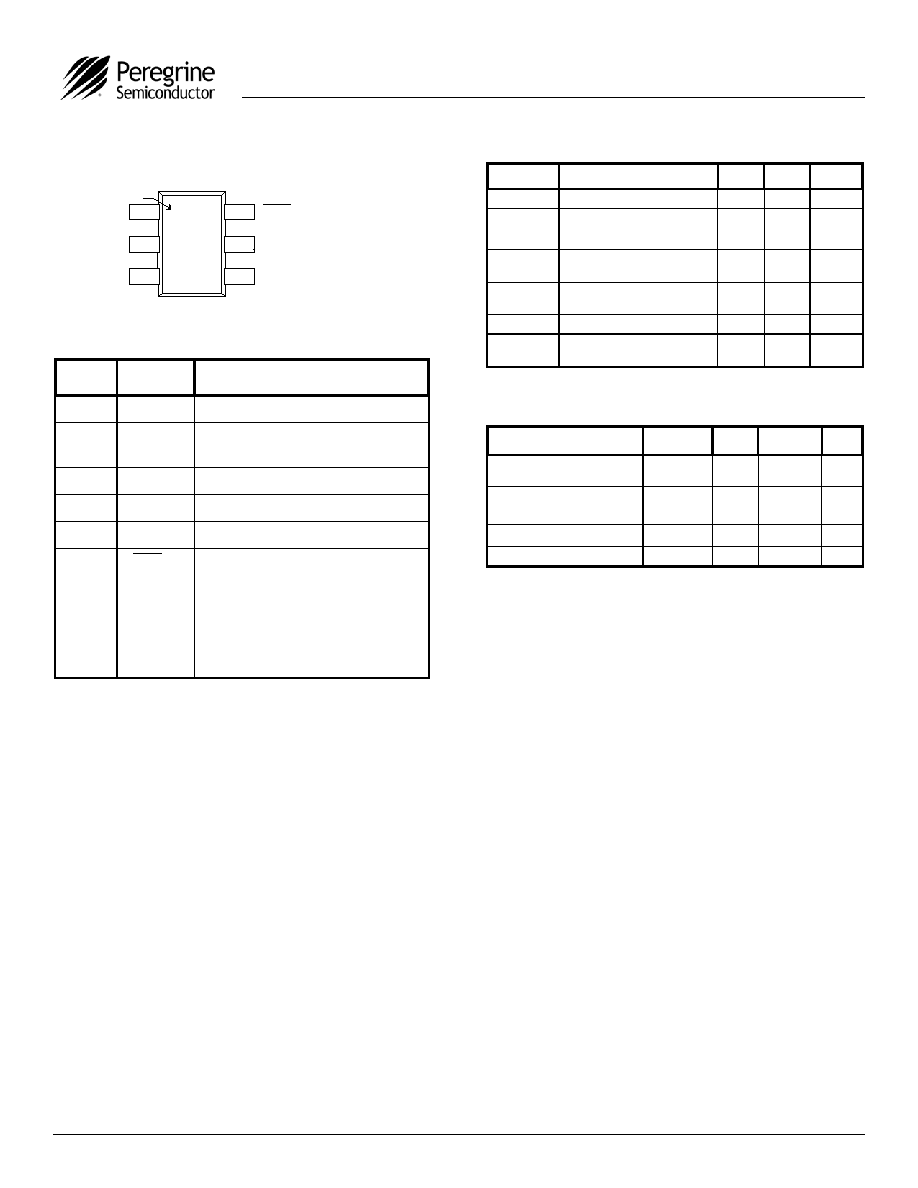

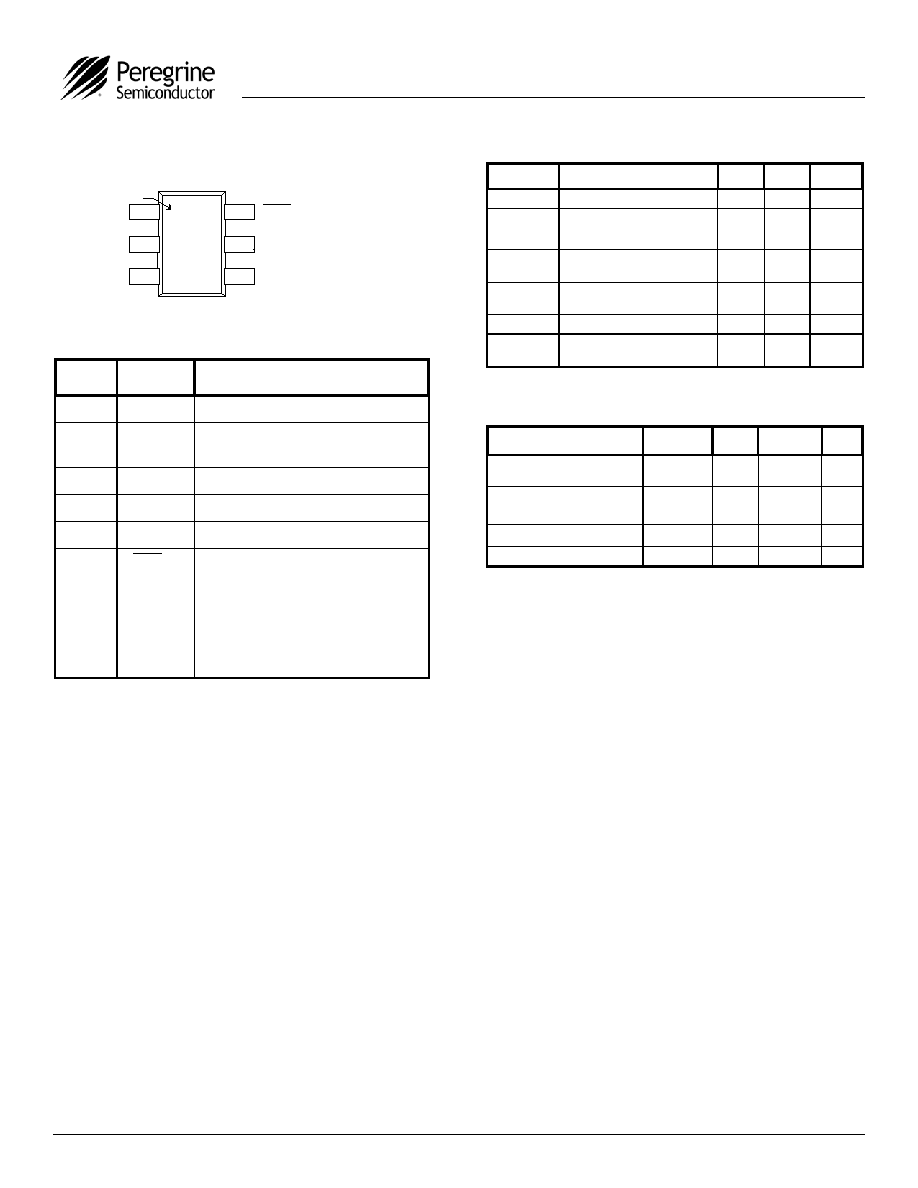

Table 2. Pin Descriptions

Note 1: All RF pins must be DC blocked with an external series

capacitor or held at 0 V

DC

.

Figure 3. Pin Configuration (Top View)

Table 3. Absolute Maximum Ratings

Electrostatic Discharge (ESD) Precautions

When handling this UltraCMOSTM device, observe

the same precautions that you would use with

other ESD-sensitive devices. Although this device

contains circuitry to protect it from damage due to

ESD, precautions should be taken to avoid

exceeding the specified rating.

Latch-Up Avoidance

Unlike conventional CMOS devices, UltraCMOSTM

devices are immune to latch-up.

Table 4. DC Electrical Specifications

Pin

No.

Pin

Name

Description

1

RF1

RF1 port (Note 1)

2

GND

Ground connection. Traces should be

physically short and connected to

ground plane for best performance.

3

RF2

RF2 port (Note 1)

4

CTRL

Switch control input, CMOS logic level.

5

RFC

Common RF port for switch (Note 1)

6 CTRL

or

V

DD

This pin supports two interface options:

Single-pin control mode. A nominal 3-

volt supply connection is required.

Complementary-pin control mode. A

complementary CMOS control signal

to CTRL is supplied to this pin. By-

passing on this pin is not required in

this mode.

Symbol Parameter/Conditions Min Max Units

V

DD

Power supply voltage

-0.3

4.0

V

V

I

Voltage on any input

-0.3

V

DD

+

0.3

V

T

ST

Storage temperature

range

-65 150 ∞C

T

OP

Operating temperature

range

-40 85 ∞C

P

IN

Input power (50

)

30

dBm

V

ESD

ESD voltage (Human

Body Model)

1500

V

Parameter Min

Typ

Max

Units

V

DD

Power Supply

Voltage

2.7 3.0 3.3 V

I

DD

Power Supply Current

(V

DD

= 3V, V

CTRL

= 3V)

250

500

nA

Control Voltage High

0.7x V

DD

V

Control Voltage Low

0.3x V

DD

V

1

2

3

4

5

6

CTRL or V

DD

RFC

CTRL

RF1

GND

RF2

.

239

pin 1

Product Specification

PE4239

Page 3 of 8

©2005 Peregrine Semiconductor Corp. All rights reserved.

Document No. 70-0068-01

www.psemi.com

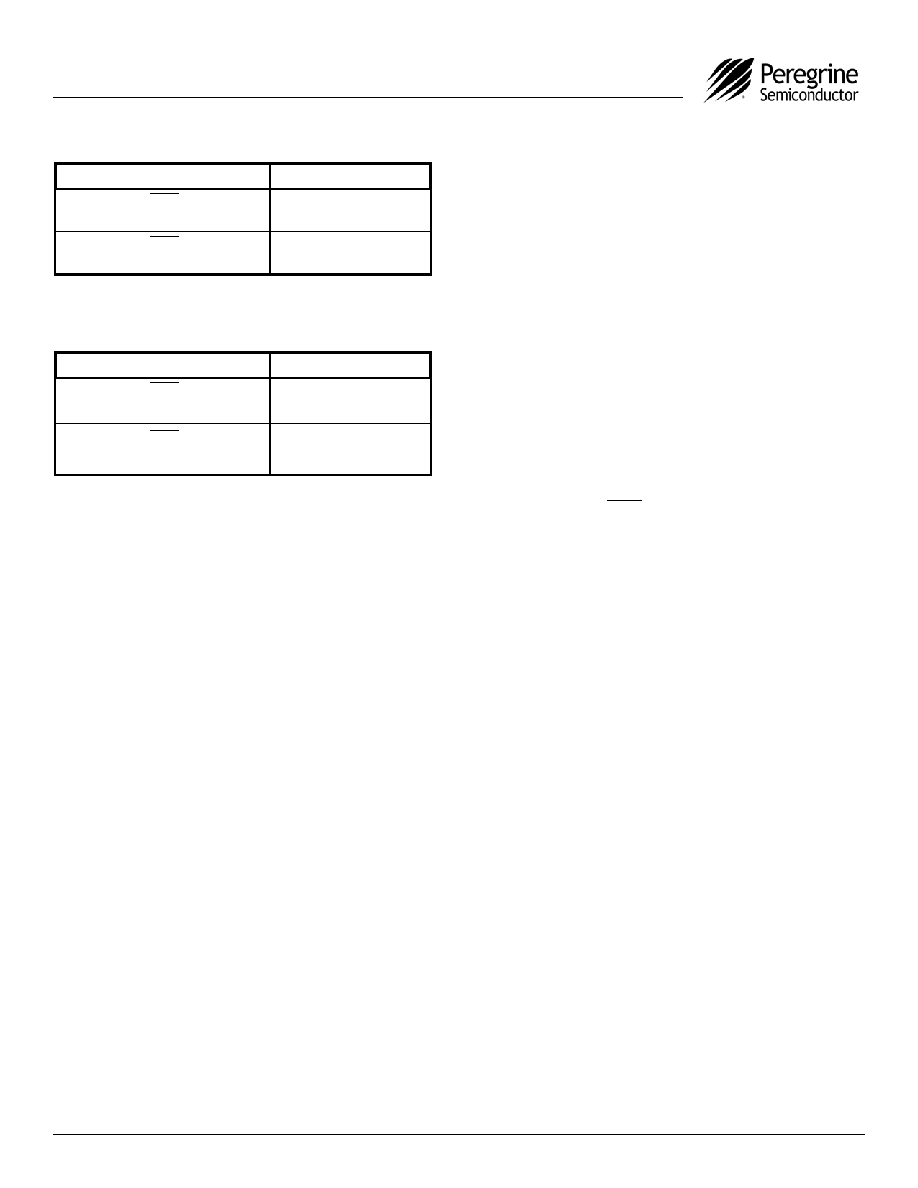

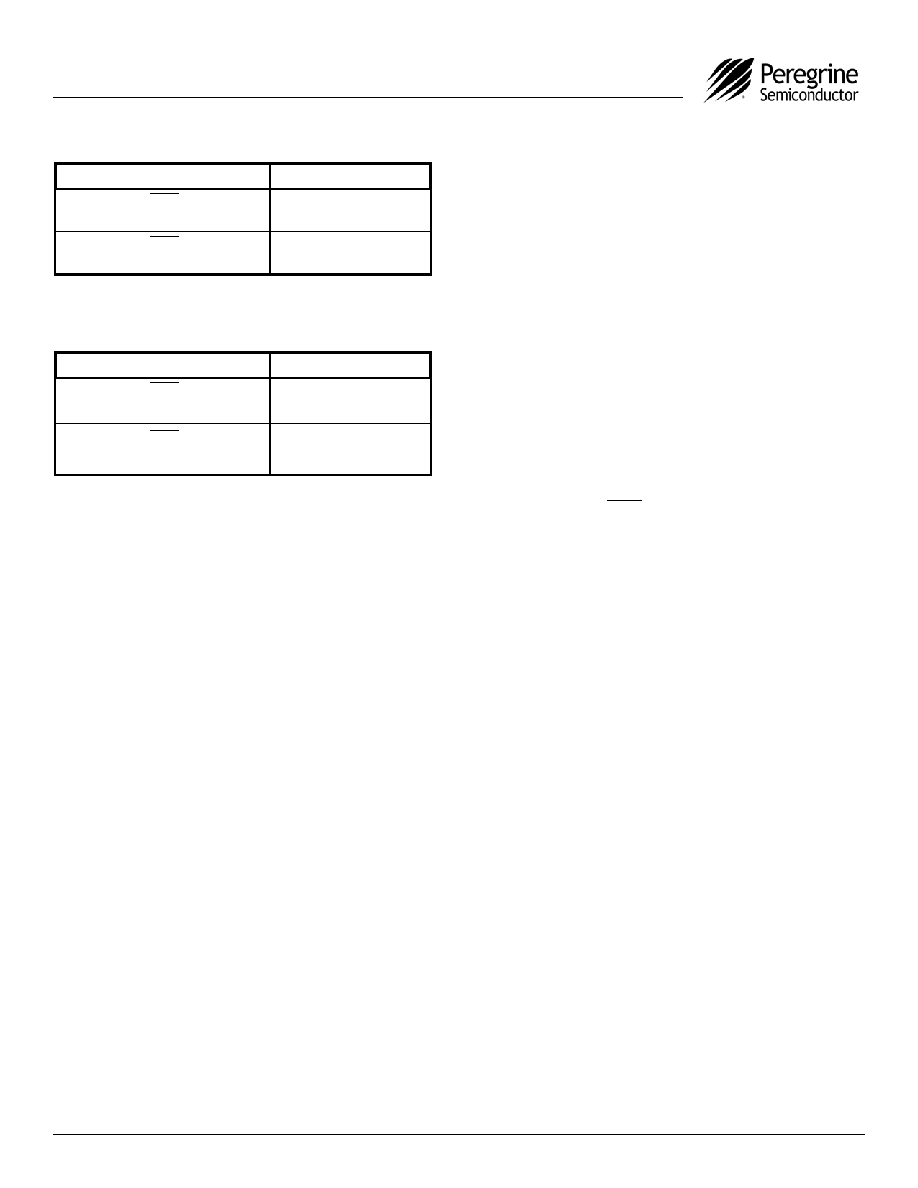

Control Voltages

Signal Path

Pin 6 (CTRL or V

DD

) = V

DD

Pin 4 (CTRL) = High

RFC to RF1

Pin 6 (CTRL or V

DD

) = V

DD

Pin 4 (CTRL) = Low

RFC to RF2

Table 5. Single-pin Control Logic Truth Table

Table 6. Complementary-pin Control Logic

Truth Table

Control Voltages

Signal Path

Pin 6 (CTRL or V

DD

) = Low

Pin 4 (CTRL) = High

RFC to RF1

Pin 6 (CTRL or V

DD

) = High

Pin 4 (CTRL) = Low

RFC to RF2

Control Logic Input

The PE4239 is a very versatile RF CMOS switch

that supports two operating control modes; single-

pin control mode and complementary-pin control

mode.

Single-pin control mode enables the switch to

operate with a single control pin (pin 4) supporting

a +3-volt CMOS logic input, and requires a

dedicated +3-volt power supply connection on pin

6 (V

DD

). This mode of operation reduces the

number of control lines required and simplifies the

switch control interface typically derived from a

CMOS

µ

Processor

I/O port

.

Complementary-pin control mode allows the

switch to operate using complementary control

pins CTRL and

CTRL

(pins 4 & 6), that can be

directly driven by +3-volt CMOS logic or a suitable

µ

Processor

I/O port. This enables the PE4239 to

be used as a potential alternate source for SPDT

RF switch products used in positive control

voltage mode and operating within the PE4239

operating limits.

Product Specification

PE4239

Page 4 of 8

©2005 Peregrine Semiconductor Corp. All rights reserved.

Document No. 70-0068-01

UltraCMOSTM RFIC Solutions

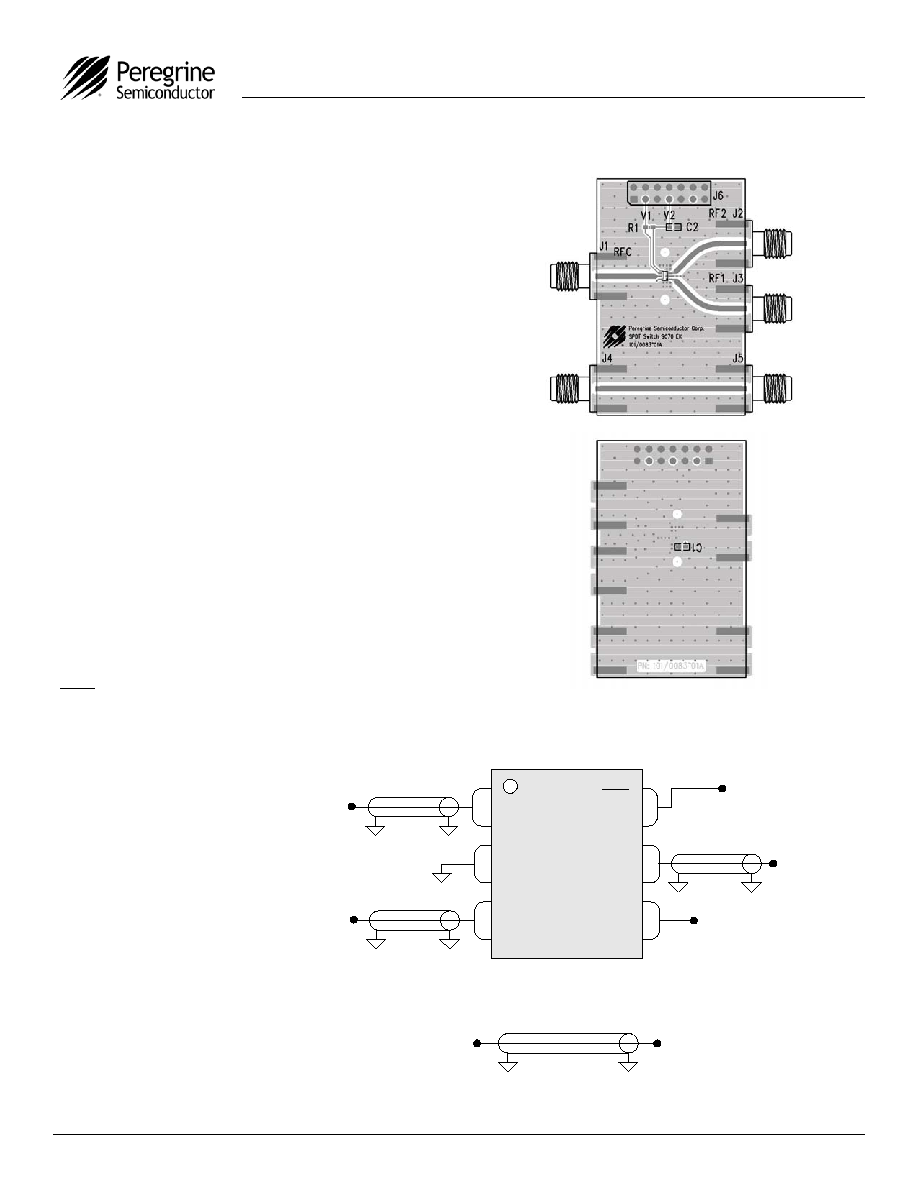

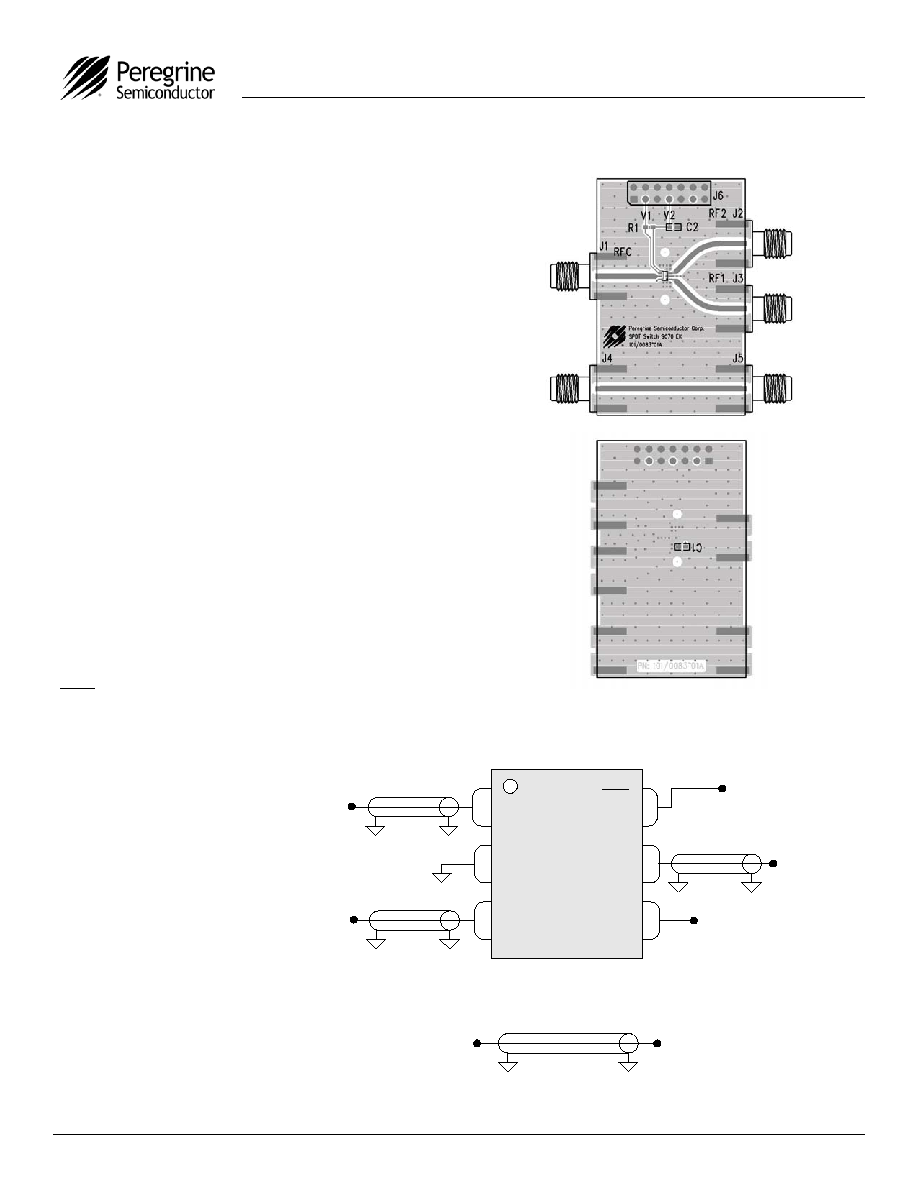

Evaluation Kit

The SPDT Switch Evaluation Kit board was

designed to ease customer evaluation of the

PE4239 SPDT switch. The RF common port is

connected through a 50

transmission line to the

top left SMA connector, J1. Port 1 and Port 2 are

connected through 50

transmission lines to the

top two SMA connectors on the right side of the

board, J3 and J2, respectively. A through

transmission line connects SMA connectors J4

and J5. This transmission line can be used to

estimate the loss of the PCB over the

environmental conditions being evaluated.

The board is constructed of a two metal layer FR4

material with a total thickness of 0.031". The

bottom layer provides ground for the RF

transmission lines. The transmission lines were

designed using a coplanar waveguide with ground

plane model using a trace width of 0.0476", trace

gaps of 0.030", dielectric thickness of 0.028",

metal thickness of 0.0021" and

r

of 4.4.

J6 provides a means for controlling DC and digital

inputs to the device. Starting from the lower left

pin, the second pin to the right (J6-3) is connected

to the device V1 or CTRL input. The fourth pin to

the right (J6-7) is connected to the device V2 or

CTRL/V

DD

input.

Figure 4. Evaluation Board Layout

Figure 5. Evaluation Board Schematic

CTRL

or V

DD

CTRL

RF2

RFC

GND

RF1

J6-3

J2

J1

J3

J4

J5

J6-7

Product Specification

PE4239

Page 5 of 8

©2005 Peregrine Semiconductor Corp. All rights reserved.

Document No. 70-0068-01

www.psemi.com

20

30

40

50

60

20

30

40

50

60

0

500

1000

1500

2000

2500

3000

I

I

P3 (

d

Bm

)

1

d

B C

o

m

p

r

e

s

s

i

on

P

o

i

n

t

(

d

Bm

)

Frequency (MHz)

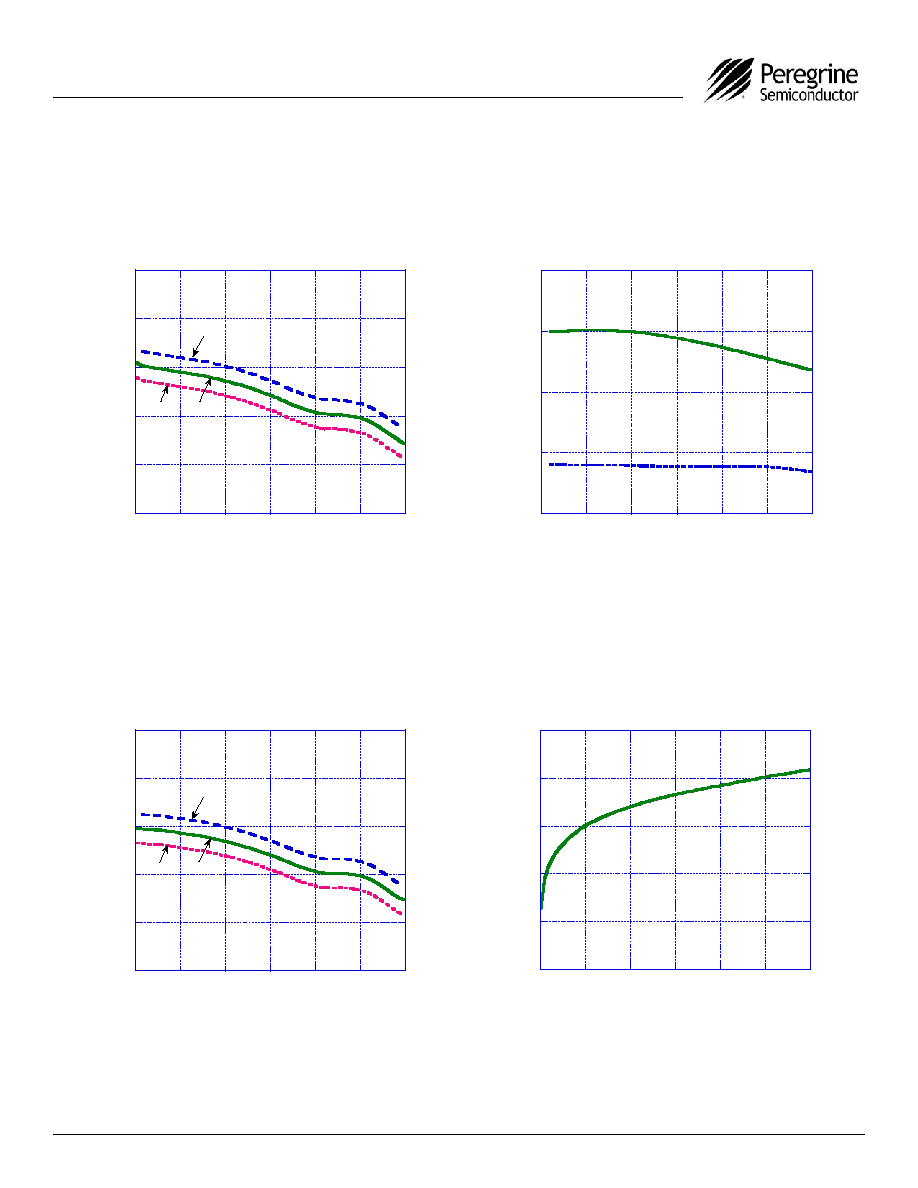

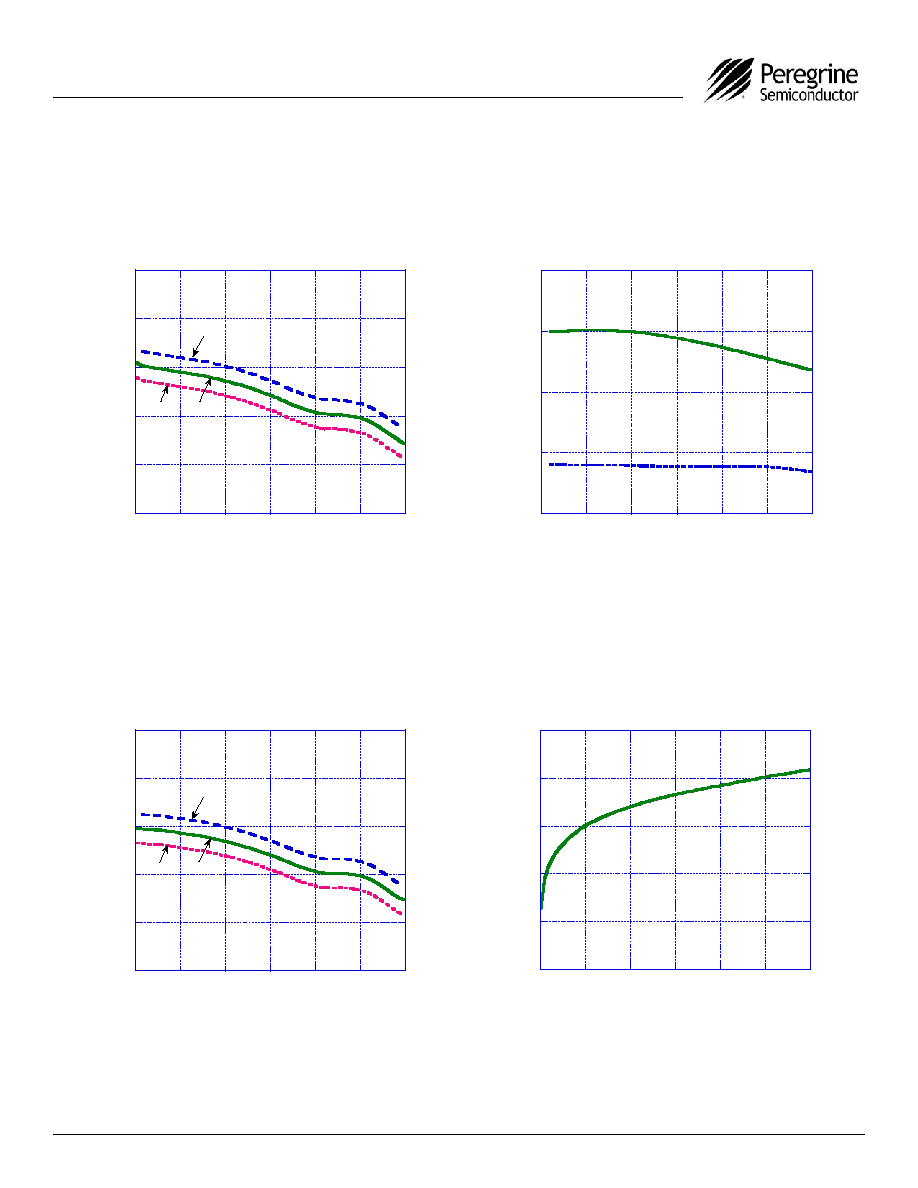

Typical Performance Data @ -40 ∞C to 85 ∞C (Unless otherwise noted)

Figure 7. Input 1 dB Compression Point & IIP3

(Typical performance @ 25 ∞C)

Figure 9. Isolation ≠ RFC to RF1

Figure 8. Insertion Loss ≠ RFC to RF2

Figure 6. Insertion Loss ≠ RFC to RF1

-1.5

-1.2

-0.9

-0.6

-0.3

0

0

500

1000

1500

2000

2500

3000

I

n

se

r

t

i

o

n

L

o

ss

(

d

B

)

Frequency (MHz)

I

n

se

r

t

i

o

n

L

o

ss

(

d

B

)

-40∞C

25∞C

85∞C

-100

-80

-60

-40

-20

0

0

500

1000

1500

2000

2500

3000

Is

ol

ati

o

n

(

d

B

)

Frequency (MHz)

-1.5

-1.2

-0.9

-0.6

-0.3

0

0

500

1000

1500

2000

2500

3000

I

n

s

e

rt

i

o

n

L

o

s

s

(d

B

)

Frequency (MHz)

I

n

s

e

rt

i

o

n

L

o

s

s

(d

B

)

-40∞C

25∞C

85∞C