| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: 83336-00 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

PEREGRINE SEMICONDUCTOR CORP.

|

http://www.peregrine-semi.com

Copyright

Peregrine Semiconductor Corp. 2003

Page 1 of 14

Product Description

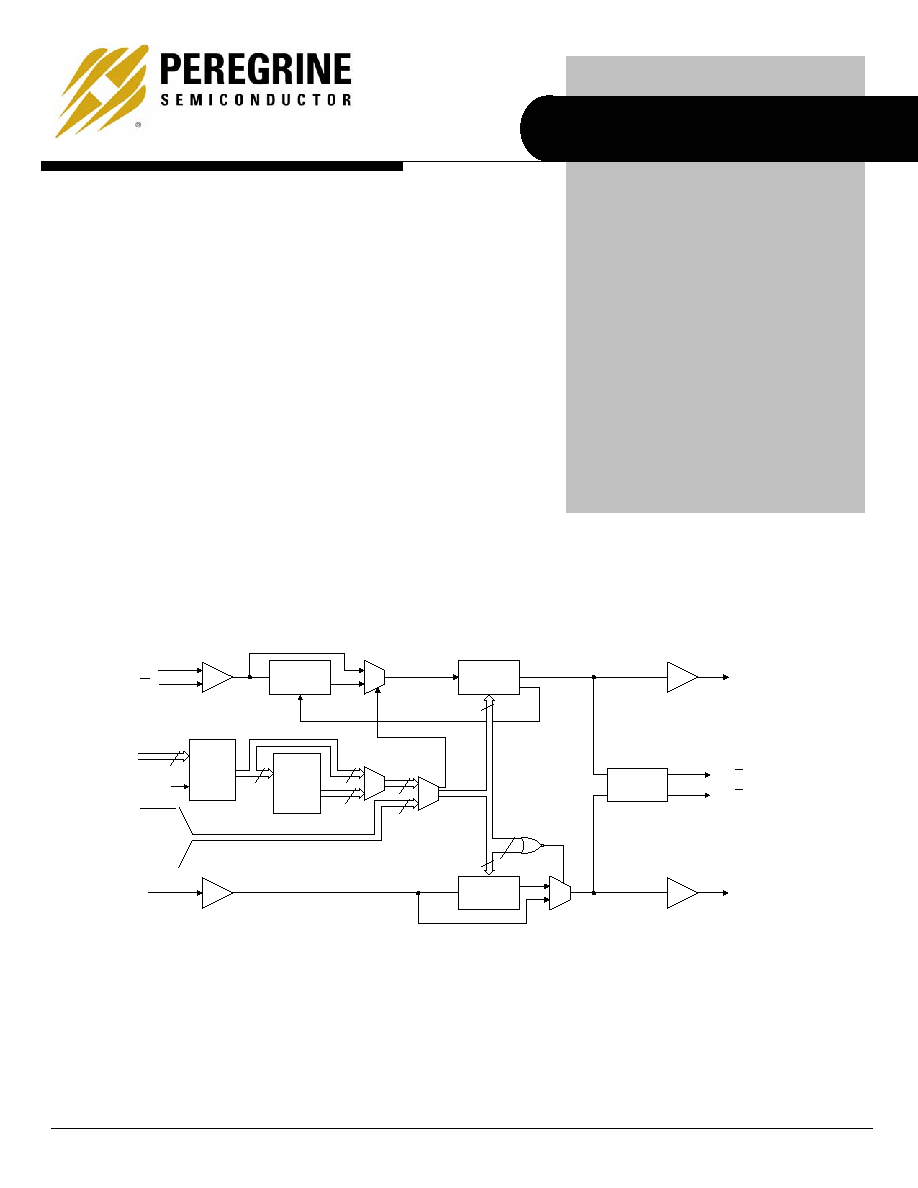

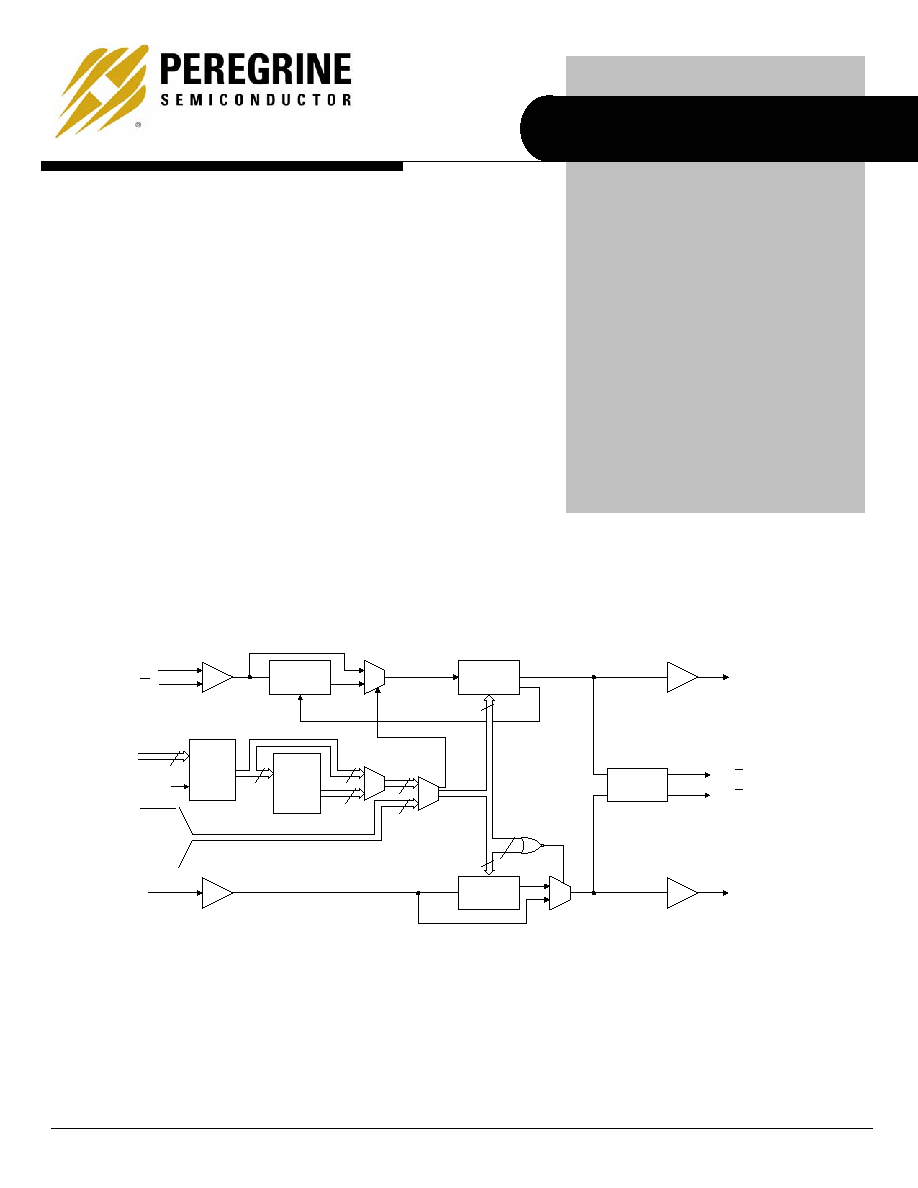

Figure 1. Block Diagram

PRODUCT SPECIFICATION

PE83336

Military Operating Temperature Range

3.0 GHz Integer-N PLL for Low

Phase Noise Applications

Features

∑ 3.0 GHz operation

∑ ˜10/11 dual modulus prescaler

∑ Internal phase detector

∑ Serial, parallel or hardwired

programmable

∑ Ultra-low phase noise

∑ Available in 44-lead CQFJ

Peregrine's PE83336 is a high performance integer-N PLL

capable of frequency synthesis up to 3.0 GHz. The

superior phase noise performance of the PE83336 makes

it ideal for rugged military environments including: radio

handsets, radar, avionics, missiles, etc.

The PE83336 features a 10/11 dual modulus prescaler,

counters and a phase comparator as shown in Figure 1.

Counter values are programmable through either a serial

or parallel interface and can also be directly hard wired.

Fabricated in Peregrine's patented UTSi

Æ

(Ultra Thin

Silicon) CMOS technology, the PE83336, while optimized

for stringent military environments, offers excellent RF

performance together with the economy and integration of

conventional CMOS.

F

in

F

in

Prescaler

10 / 11

20

Main

Counter

20

Secon-

dary

20-bit

Latch

20

Primary

20-bit

Latch

Pre_en

M(6:0)

A(3:0)

R(3:0)

16

20

R Counter

f

r

Phase

Detector

6

6

f

c

f

p

8

D(7:0)

13

Sdata

PD_U

PD_D

PE83336

Product Specification

Copyright

Peregrine Semiconductor Corp. 2003

File No. 70/0137~01A

|

UTSi

CMOS RFIC SOLUTIONS

Page 2 of 14

11

12

13

14

15

16

17

10

9

8

7

6

5

4

3

2

1 44 43 42 41 40

35

34

33

32

31

30

29

36

37

38

39

18 19 20 21 22 23 24 25 26 27 28

D

0

, M

0

D

1

, M

1

D

2

, M

2

D

3

, M

3

V

DD

V

DD

S_WR, D

4

, M

4

Sdata, D

5

, M

5

Sclk, D

6

, M

6

FSELS, D

7

, Pre_en

GND

GND

f

p

V

DD

_f

p

D

out

V

DD

C

ext

V

DD

PD_D

PD_U

V

DD

_f

c

f

c

F

in

F

in

Ho

p_

W

R

A_W

R

M1

_

W

R

V

DD

Bmo

d

e

S

m

od

e, A

3

M2

_

W

R

,

A

2

E_W

R

, A

1

F

S

EL

P,

A

0

GN

D

R

3

R

2

R

1

R

0

V

DD

En

h

LD

fr

GN

D

GN

D

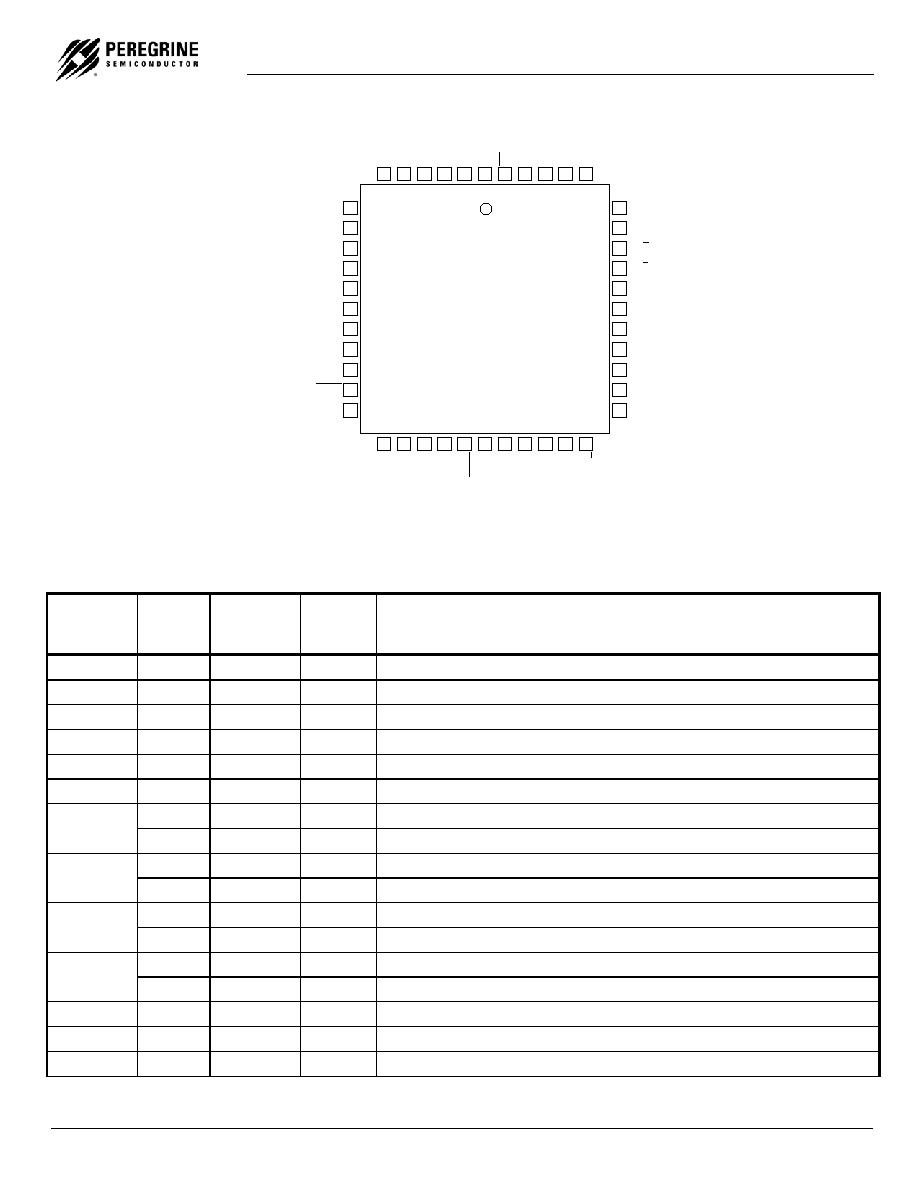

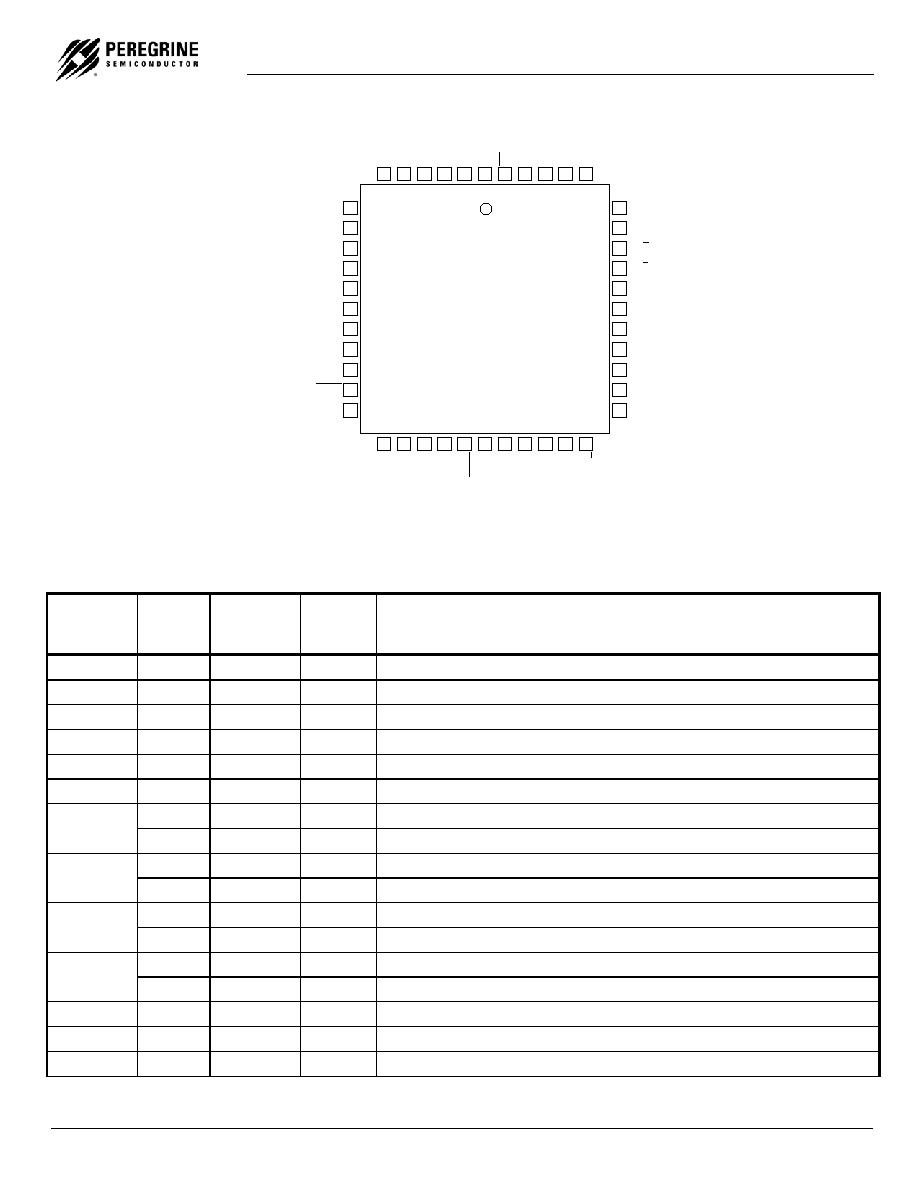

Figure 2. Pin Configuration

44-lead CQFJ

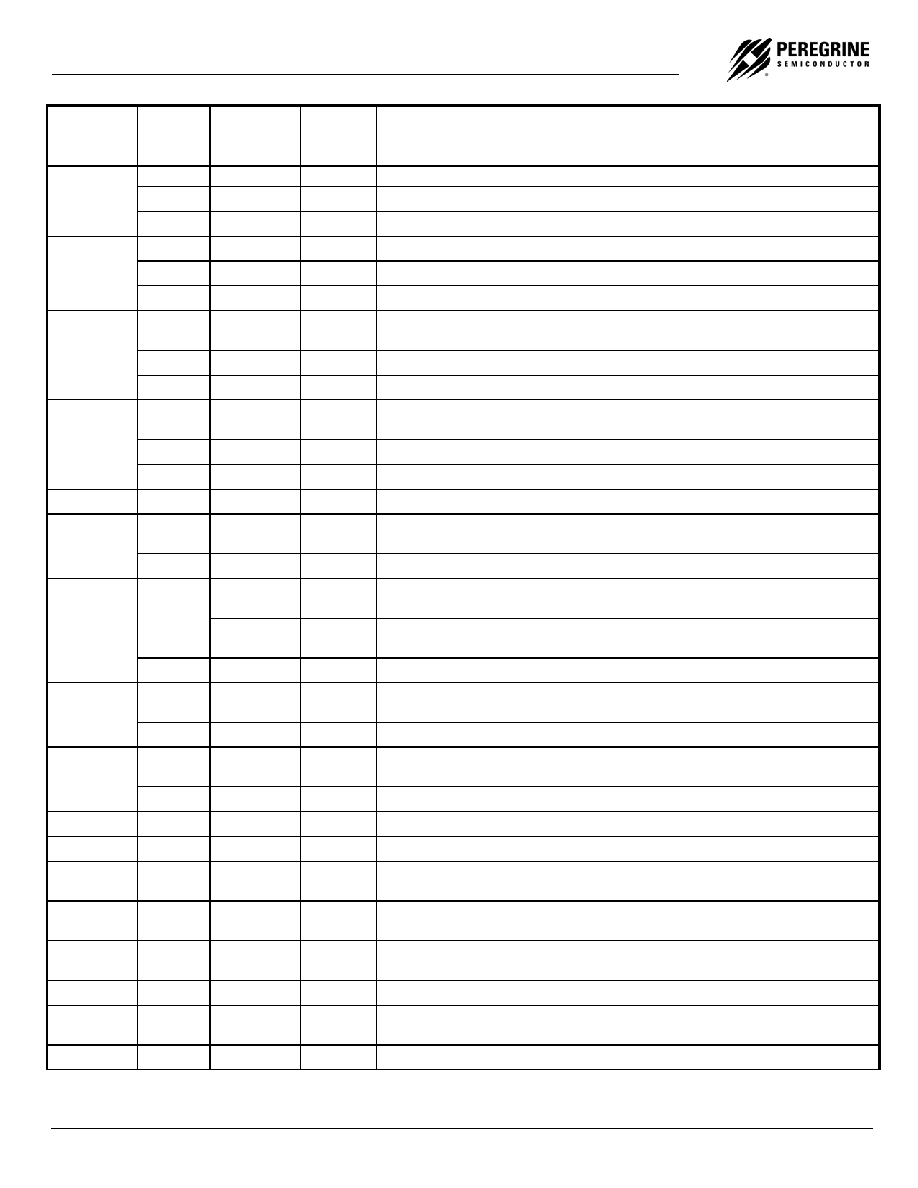

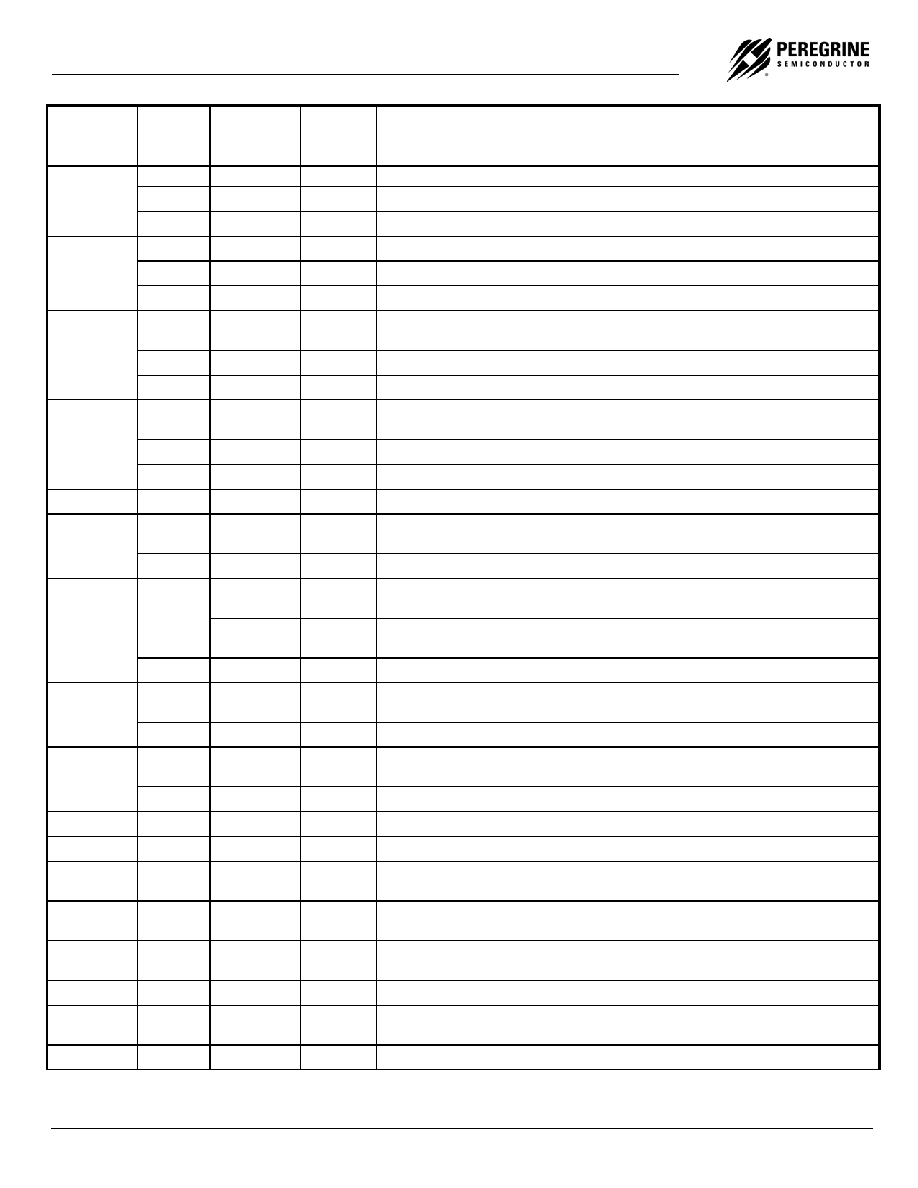

Table 1. Pin Descriptions

Pin No.

(44-lead

CQFJ)

Pin

Name

Interface

Mode

Type Description

1 V

DD

ALL

(Note 1)

Power supply input. Input may range from 2.85 V to 3.15 V. Bypassing recommended.

2 R

0

Direct

Input

R Counter bit0 (LSB).

3 R

1

Direct

Input

R Counter bit1.

4 R

2

Direct

Input

R Counter bit2.

5 R

3

Direct

Input

R Counter bit3.

6 GND ALL

(Note

1)

Ground.

D

0

Parallel

Input

Parallel data bus bit0 (LSB).

7

M

0

Direct

Input

M Counter bit0 (LSB).

D

1

Parallel

Input

Parallel data bus bit1.

8

M

1

Direct Input

M

Counter

bit1.

D

2

Parallel

Input

Parallel data bus bit2.

9

M

2

Direct Input

M

Counter

bit2.

D

3

Parallel

Input

Parallel data bus bit3.

10

M

3

Direct Input

M

Counter

bit3.

11 V

DD

ALL

(Note 1)

Same as pin 1.

12 V

DD

ALL

(Note 1)

Same as pin 1.

13

S_WR

Serial

Input

Serial load enable input. While S_WR is "low", Sdata can be serially clocked. Primary

PE83336

Product Specification

PEREGRINE SEMICONDUCTOR CORP.

|

http://www.peregrine-semi.com

Copyright

Peregrine Semiconductor Corp. 2003

Page 3 of 14

Pin No.

(44-lead

CQFJ)

Pin

Name

Interface

Mode

Type Description

register data are transferred to the secondary register on S_WR or Hop_WR rising edge.

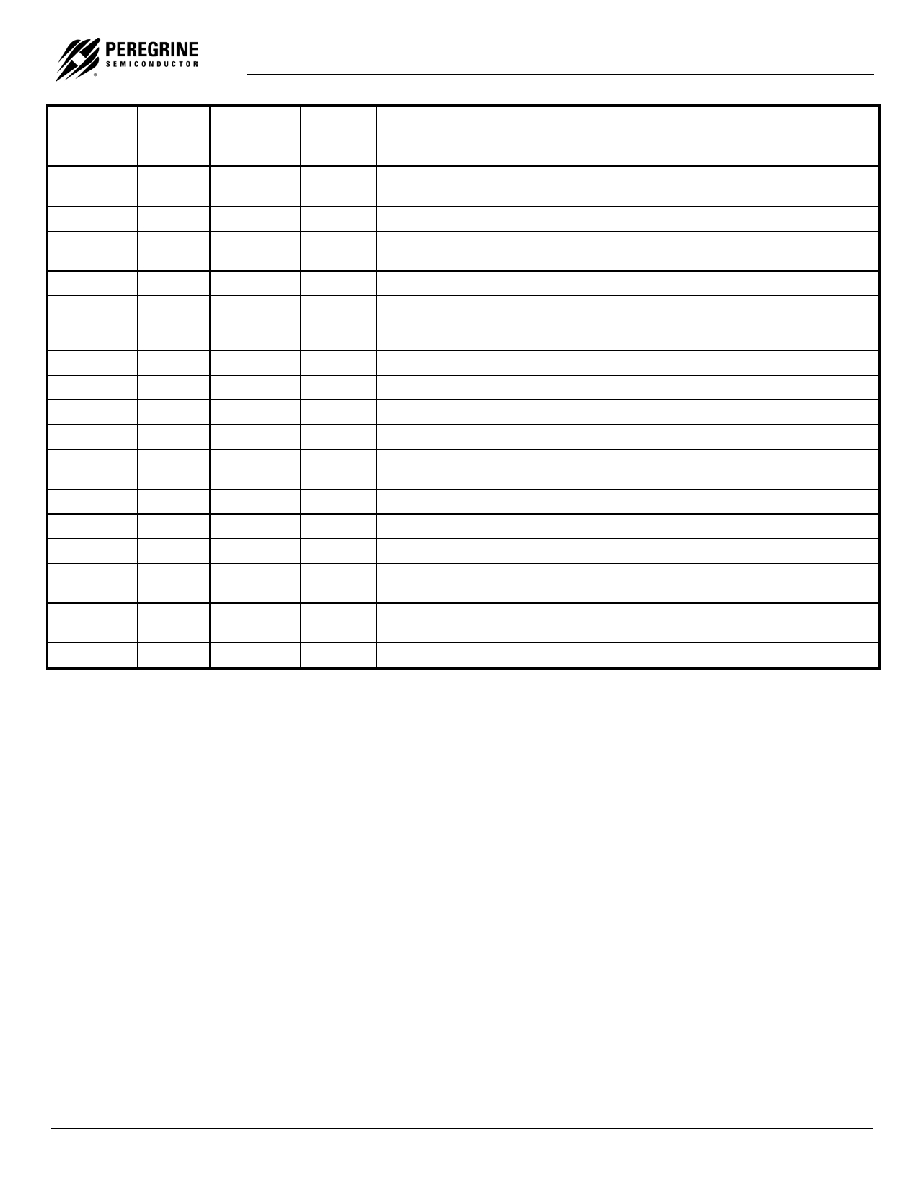

D

4

Parallel

Input

Parallel data bus bit4

M

4

Direct Input

M

Counter

bit4

Sdata

Serial

Input

Binary serial data input. Input data entered MSB first.

D

5

Parallel

Input

Parallel data bus bit5.

14

M

5

Direct Input

M

Counter

bit5.

Sclk Serial Input

Serial clock input. Sdata is clocked serially into the 20-bit primary register (E_WR "low") or

the 8-bit enhancement register (E_WR "high") on the rising edge of Sclk.

D

6

Parallel

Input

Parallel data bus bit6.

15

M

6

Direct Input

M

Counter

bit6.

FSELS Serial

Input

Selects contents of primary register (FSELS=1) or secondary register (FSELS=0) for

programming of internal counters while in Serial Interface Mode.

D

7

Parallel

Input

Parallel data bus bit7 (MSB).

16

Pre_en

Direct

Input

Prescaler enable, active "low". When "high", F

in

bypasses the prescaler.

17 GND ALL

Ground.

FSELP Parallel

Input

Selects contents of primary register (FSELP=1) or secondary register (FSELP=0) for

programming of internal counters while in Parallel Interface Mode.

18

A

0

Direct

Input

A Counter bit0 (LSB).

Serial Input

Enhancement register write enable. While E_WR is "high", Sdata can be serially clocked

into the enhancement register on the rising edge of Sclk.

E_WR

Parallel Input

Enhancement register write. D[7:0] are latched into the enhancement register on the rising

edge of E_WR.

19

A

1

Direct

Input

A Counter bit1.

M2_WR Parallel

Input

M2 write. D[3:0] are latched into the primary register (R[5:4], M[8:7]) on the rising edge of

M2_WR.

20

A

2

Direct

Input

A Counter bit2.

Smode

Serial,

Parallel

Input

Selects serial bus interface mode (Bmode=0, Smode=1) or Parallel Interface Mode

(Bmode=0, Smode=0).

21

A

3

Direct

Input

A Counter bit3 (MSB).

22

Bmode

ALL

Input

Selects direct interface mode (Bmode=1).

23 V

DD

ALL

(Note 1)

Same as pin 1.

24 M1_WR

Parallel Input

M1 write. D[7:0] are latched into the primary register (Pre_en, M[6:0]) on the rising edge of

M1_WR.

25 A_WR

Parallel Input

A write. D[7:0] are latched into the primary register (R[3:0], A[3:0]) on the rising edge of

A_WR.

26 Hop_WR

Serial,

Parallel

Input

Hop write. The contents of the primary register are latched into the secondary register on

the rising edge of Hop_WR.

27 F

in

ALL

Input

Prescaler input from the VCO. 3.0 GHz max frequency.

28 F

in

ALL Input

Prescaler complementary input. A bypass capacitor should be placed as close as possible

to this pin and be connected in series with a 50

resistor directly to the ground plane.

29 GND ALL

Ground.

PE83336

Product Specification

Copyright

Peregrine Semiconductor Corp. 2003

File No. 70/0137~01A

|

UTSi

CMOS RFIC SOLUTIONS

Page 4 of 14

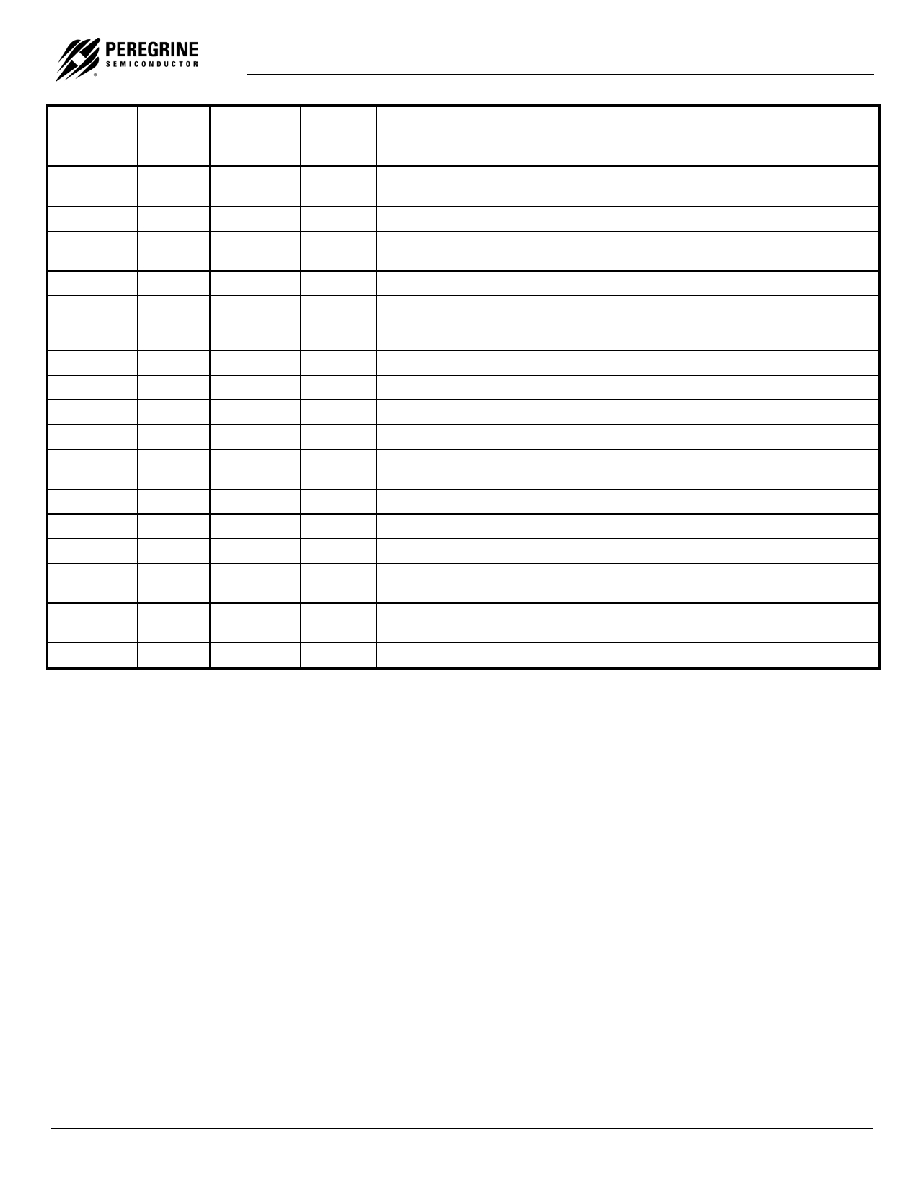

Pin No.

(44-lead

CQFJ)

Pin

Name

Interface

Mode

Type Description

30 f

p

ALL Output

Monitor pin for main divider output. Switching activity can be disabled through

enhancement register programming or by floating or grounding V

DD

pin 31.

31 V

DD

-f

p

ALL

(Note

1)

V

DD

for f

p

. Can be left floating or connected to GND to disable the f

p

output.

32 Dout

Serial,

Parallel

Output

Data Out. The MSEL signal and the raw prescaler output are available on Dout through

enhancement register programming.

33 V

DD

ALL

(Note 1)

Same as pin 1.

34 Cext ALL

Output

Logical "NAND" of PD_U and PD_D terminated through an on chip, 2 k

series resistor.

Connecting Cext to an external capacitor will low pass filter the input to the inverting

amplifier used for driving LD.

35 V

DD

ALL

(Note 1)

Same as pin 1.

36

PD_D

ALL

Output

PD_D is pulse down when f

p

leads f

c

.

37

PD_U

ALL

PD_U is pulse down when f

c

leads f

p

.

38 V

DD

-f

c

ALL

(Note

1)

V

DD

for f

c

can be left floating or connected to GND to disable the f

c

output.

39 f

c

ALL Output

Monitor pin for reference divider output. Switching activity can be disabled through

enhancement register programming or by floating or grounding V

DD

pin 38.

40 GND ALL

Ground.

41 GND ALL

Ground.

42 f

r

ALL

Input

Reference frequency input.

43 LD ALL

Output

Lock detect and open drain logical inversion of CEXT. When the loop is in lock, LD is high

impedance, otherwise LD is a logic low ("0").

44 Enh

Serial,

Parallel

Input

Enhancement mode. When asserted low ("0"), enhancement register bits are functional.

N/A NC ALL

No

connection.

Note 1:

All V

DD

pins are connected by diodes and must be supplied with the same positive voltage level.

V

DD

-f

p

and V

DD

-f

p

are used to power the f

p

and f

c

outputs and can alternatively be left floating or connected to GND to disable the f

p

and f

c

outputs.

Note 2:

All digital input pins have 70 k

pull-down resistors to ground.

PE83336

Product Specification

PEREGRINE SEMICONDUCTOR CORP.

|

http://www.peregrine-semi.com

Copyright

Peregrine Semiconductor Corp. 2003

Page 5 of 14

Table 2. Absolute Maximum Ratings

Symbol Parameter/Conditions Min Max Units

V

DD

Supply

voltage

-0.3

4.0 V

V

I

Voltage on any input

-0.3

V

DD

+ 0.3

V

I

I

DC into any input

-10

+10

mA

I

O

DC into any output

-10

+10

mA

T

stg

Storage

temperature

range

-65 150

∞

C

Table 3. Operating Ratings

Symbol Parameter/Conditions Min Max Units

V

DD

Supply

voltage

2.85

3.15 V

T

A

Operating

ambient

temperature range

-55 125

∞

C

Table 4. ESD Ratings

Symbol Parameter/Conditions Level

Units

V

ESD

ESD voltage (Human Body

Model)

1000 V

Note 1:

Periodically sampled, not 100% tested. Tested per MIL-

STD-883, M3015 C2

Electrostatic Discharge (ESD) Precautions

When handling this UTSi

Æ

device, observe the

same precautions that you would use with other

ESD-sensitive devices. Although this device

contains circuitry to protect it from damage due to

ESD, precautions should be taken to avoid

exceeding the rating specified in Table 4.

Latch-Up Avoidance

Unlike conventional CMOS devices, UTSi

Æ

CMOS

devices are immune to latch-up.