| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: PE4126-21 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

PEREGRINE SEMICONDUCTOR CORP.

|

http://www.peregrine-semi.com

Copyright

Peregrine Semiconductor Corp. 2003

Page 1 of 8

Product Description

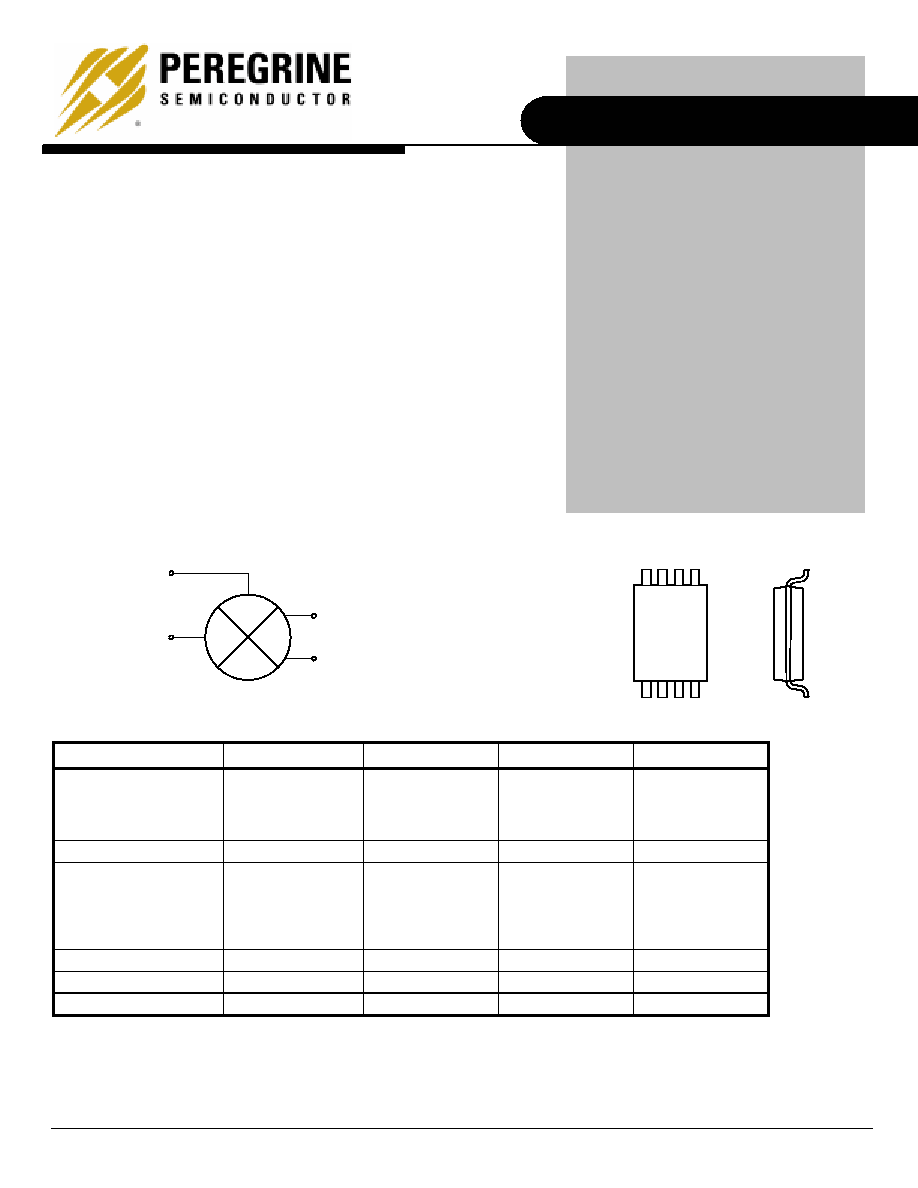

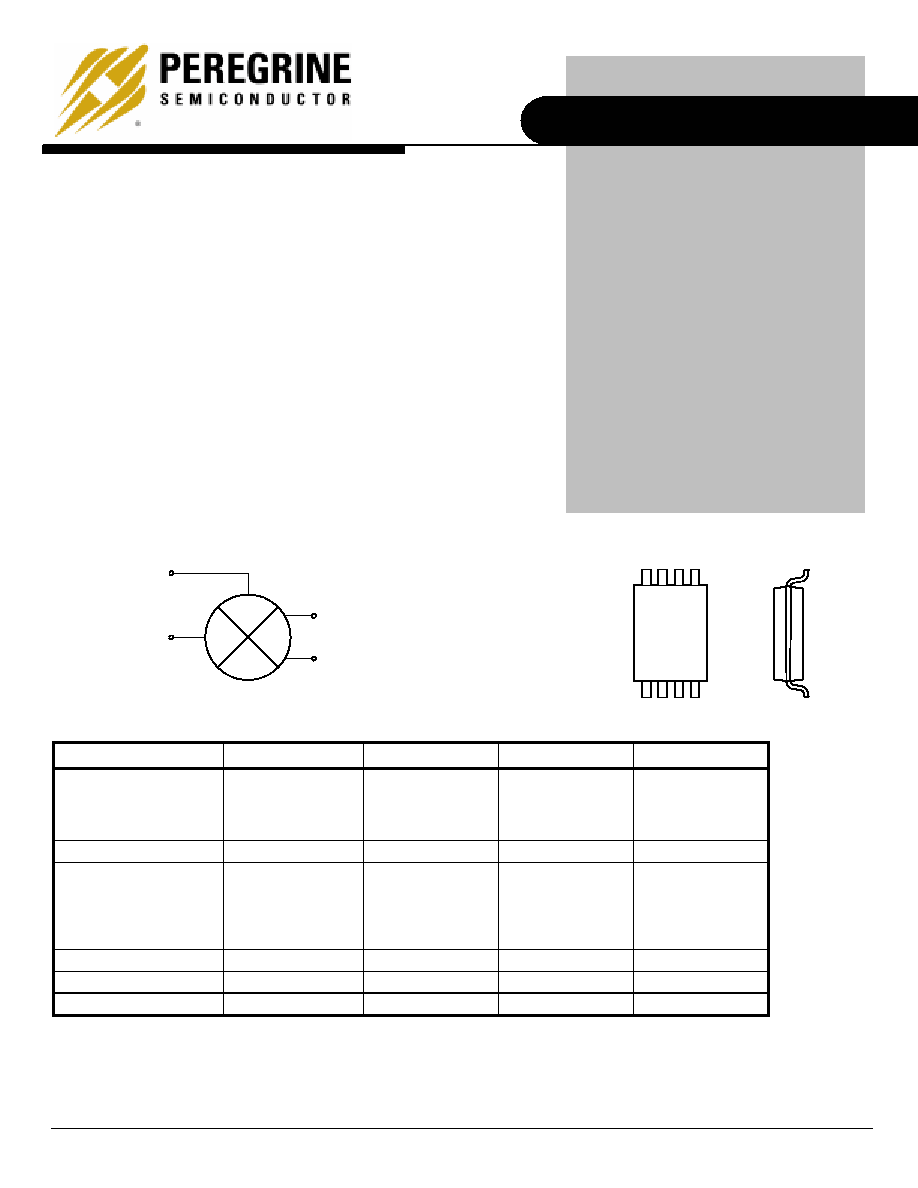

Figure 1. Functional Schematic Diagram

PE4126

RF

LO

IF

Figure 2. Package Type

Table 1. Electrical Specifications @ +25 ∞C

(Z

S

= Z

L

= 50

)

Parameter Minimum

Typical Maximum Units

Frequency Range:

LO

RF

IF*

1450

1700

--

--

--

250

1550

1800

--

MHz

MHz

MHz

Conversion Loss**

7.9

8.3

dB

Isolation:

LO-RF

1.7 GHz

1.75 GHz

1.8 GHz

30

32

34

34

36

38

dB

dB

dB

LO-IF 33

37

dB

Input IP3

30

32

dBm

Input 1 dB Compression

21

dBm

*An IF frequency of 250MHz is a nominal frequency. The IF frequency can be specified by the user as long as the RF and LO frequencies are within

the specified maximum and minimum.

**Conversion Loss includes loss of IF transformer (M/ACom ETK4-2T - nominal loss 0.7 dB at 250MHz.)

Test conditions unless otherwise noted: LO = 250MHz, LO input drive = 17dBm, RF input drive = 3dBm.

PRODUCT SPECIFICATION

PE4126

High Linearity Quad MOSFET

Mixer for DCS 1800 BTS

Features

∑ Integrated, single-ended RF & LO

interfaces

∑ High linearity: IIP3 of +32 dBm,

1700

- 1800 MHz (+17 dBm LO)

∑ Low conversion loss: 7.9 dB

(+17 dBm LO)

∑ High Isolation: typical LO-IF at

37 dB, LO-RF at 38 dB (1.8 GHz)

∑ Designed for low-side LO

injection

The PE4126 is a high linearity, passive Quad MOSFET

Mixer for DCS1800 Base Station Receivers exhibiting

high dynamic range performance over a broad LO drive

range up to 20 dBm. This mixer integrates passive

matching networks to provide single-ended interfaces for

the RF and LO ports, eliminating the need for external

RF baluns or matching networks. The PE4126 is

optimized for frequency down-conversion using low-side

LO injection for DCS1800 Base Station applications, and

is also suitable for use in up-conversion applications.

The PE4126 is manufactured in Peregrine's patented

Ultra Thin Silicon (UTSi

) CMOS process, offering the

performance of GaAs with the economy and integration

of conventional CMOS.

8-lead

TSSOP

PE4126

Product Specification

Copyright

Peregrine Semiconductor Corp. 2003

File No. 70/0045~03A

|

UTSi CMOS RFIC SOLUTIONS

Page 2 of 8

Figure 3. Pin Configuration

PE4126

5

6

7

8

4

3

2

1

GND

RF

GND

LO

GND

IF2

IF1

GND

Table 2. Pin Descriptions

Pin

No.

Pin

Name

Description

1 LO

LO

Input

2

GND

Ground connection for Mixer. Traces

should be physically short and connect

immediately to ground plane for best

performance.

3 RF

RF

Input

4 GND

Ground.

5 GND

Ground.

6

IF2

IF differential output

7

IF1

IF differential output

8 GND

Ground.

Table 3. Absolute Maximum Ratings

Symbol Parameter/Conditions Min Max Units

T

ST

Storage temperature

range

-65 150

∞C

T

OP

Operating temperature

range

-40 85

∞C

P

LO

LO input power

20

dBm

P

RF

RF input power

16

dBm

V

ESD

ESD Sensitive Device

250

V

Electrostatic Discharge (ESD) Precautions

When handling this UTSi device, observe the same

precautions that you would use with other ESD-

sensitive devices. Although this device contains

circuitry to protect it from damage due to ESD,

precautions should be taken to avoid exceeding the

rating specified in Table 3.

Latch-Up Avoidance

Unlike conventional CMOS devices, UTSi CMOS

devices are immune to latch-up.

PE4126

Product Specification

PEREGRINE SEMICONDUCTOR CORP.

|

http://www.peregrine-semi.com

Copyright

Peregrine Semiconductor Corp. 2003

Page 3 of 8

IF

PE4126

GND

IF2

IF1

GND

GND

RF

GND

LO

LO

IF

RF

4126

Eval

Board

Sig

Gen

Sig

Gen

Hybrid

Tee

3 dB

PA

Sig

Gen

3 dB

Spectrum

Analyzer

3 dB

6 dB

6 dB

Figure 4. Evaluation Board Schematic Diagram

T2 M/A-Com E-Series RF 4:1 Transformer 2.0 ≠ 1000 MHz ETK4-2T

Figure 5. Evaluation Board

Table 4. Bill of Materials

Reference

Value / Description

T2

M/A Com ETK4-2T

U1 (Not Labeled)

PE4126 Mixer

R1 0

J1, J2, J3

SMA Connector

Figure 6. Evaluation Board Testing Block Diagram, 2-Tone Setup

Pin 1

T2

PE4126

Product Specification

Copyright

Peregrine Semiconductor Corp. 2003

File No. 70/0045~03A

|

UTSi CMOS RFIC SOLUTIONS

Page 4 of 8

0

5

10

15

20

25

30

1700

1720

1740

1760

1780

1800

1d

B

Com

p

r

e

s

s

i

on (

d

B

m

)

Frequency (MHz)

85!C

-40!C 25!C

-10

-8

-6

-4

-2

0

1700

1720

1740

1760

1780

1800

Con

v

ers

i

on Lo

s

s

(

d

B

)

Frequency (MHz)

85!C

25!C

-40!C

0

10

20

30

40

1700

1720

1740

1760

1780

1800

II

P

3

(

d

B

m

)

Frequency (MHz)

-40!C 25!C 85!C

0

5

10

15

20

25

30

35

1700

1720

1740

1760

1780

1800

OI

P

3

(d

B

m

)

Frequency (MHz)

-40!C 25!C 85!C

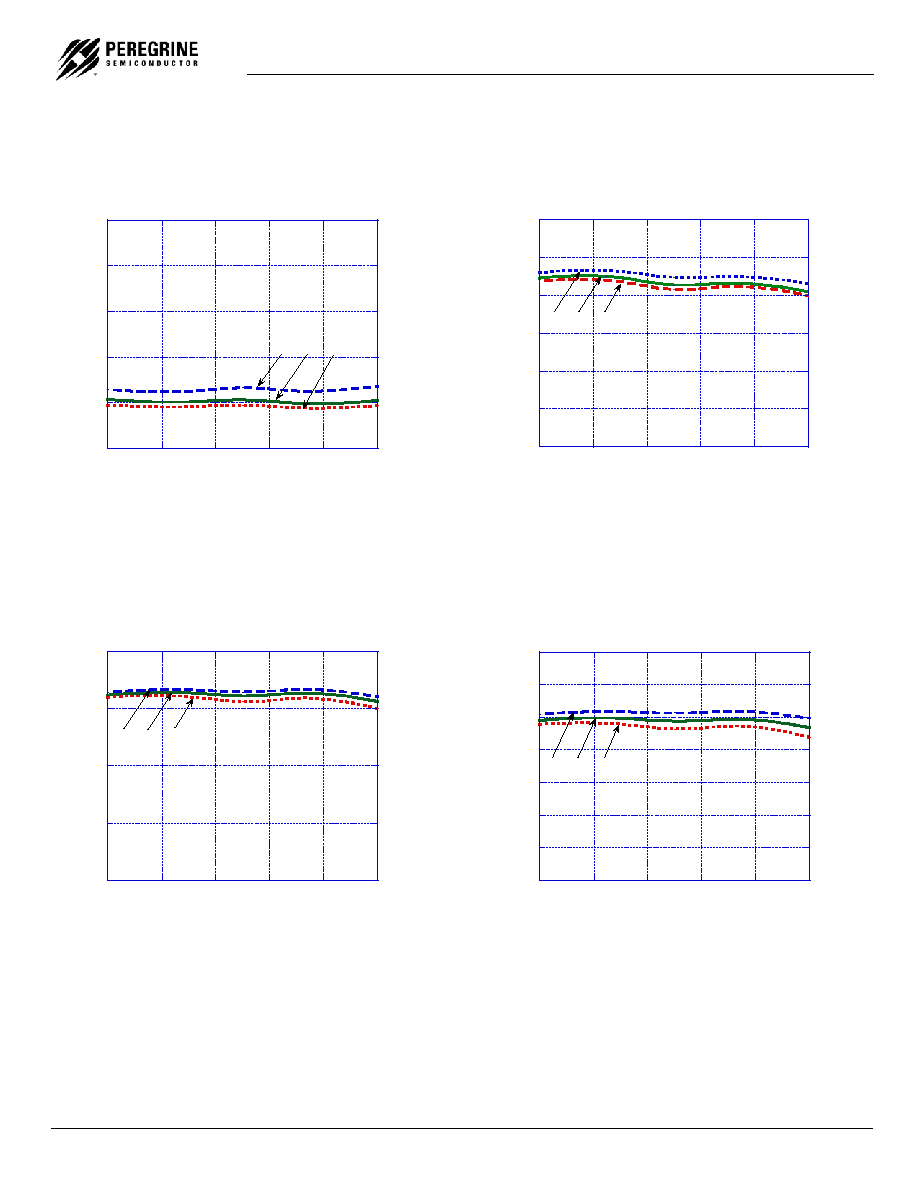

Typical Performance Data (LO=17dBm, RF=3dBm, IF=250MHz)

Figure 7. Conversion Loss vs. Frequency

Figure 8. Input 1dB Compression vs. Frequency

Figure 9. Input IP3 vs. Frequency

Figure 10. Output IP3 vs. Frequency

PE4126

Product Specification

PEREGRINE SEMICONDUCTOR CORP.

|

http://www.peregrine-semi.com

Copyright

Peregrine Semiconductor Corp. 2003

Page 5 of 8

-50

-40

-30

-20

-10

0

1700

1720

1740

1760

1780

1800

LO

-

I

F

I

s

ol

a

t

ion

(

d

B

)

Frequency (MHz)

25!C

85!C

-40!C

-25

-20

-15

-10

-5

0

1.3

1.35

1.4

1.45

1.5

1.55

1.6

R

e

t

u

rn

L

o

s

s

(d

B

)

Frequency (GHz)

-20

-15

-10

-5

0

1.6

1.65

1.7

1.75

1.8

1.85

1.9

Re

t

u

r

n

L

o

ss

(

d

B

)

Frequency (GHz)

-50

-40

-30

-20

-10

0

1700

1720

1740

1760

1780

1800

LO

-

R

F I

s

ol

at

i

o

n

(

d

B

)

Frequency (MHz)

-40!C

25!C

85!C

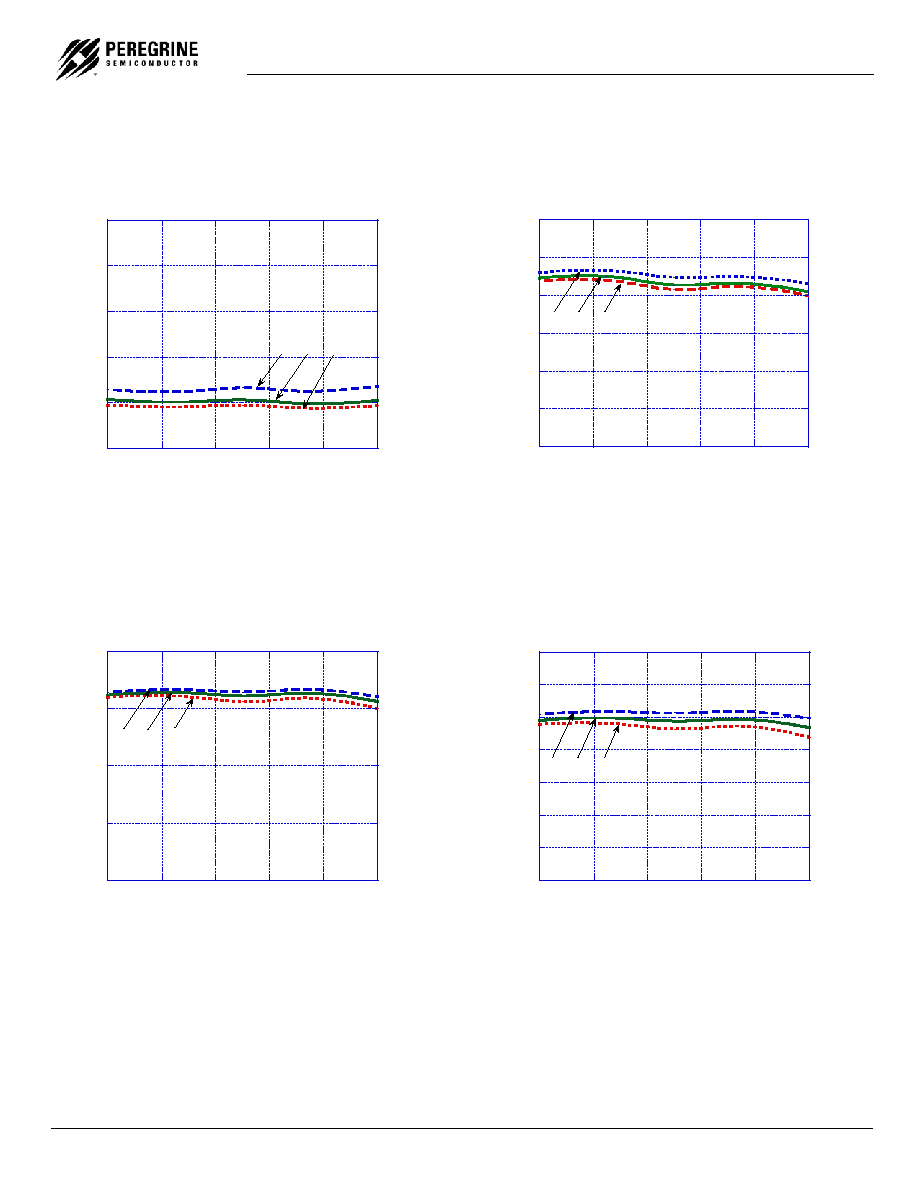

Typical Performance Data (LO=17dBm, RF=3dBm, IF=250MHz)

Figure 11. LO-IF Isolation vs. Frequency

Figure 12. LO-RF Isolation vs. Frequency

Figure 13. LO Port Return Loss @ 25∞C

Figure 14. RF Port Return Loss @ 25∞C