DATA SHEET

Product specification

File under Integrated Circuits, IC04

January 1995

INTEGRATED CIRCUITS

HEF4030B

gates

Quadruple exclusive-OR gate

For a complete data sheet, please also download:

∑

The IC04 LOCMOS HE4000B Logic

Family Specifications HEF, HEC

∑

The IC04 LOCMOS HE4000B Logic

Package Outlines/Information HEF, HEC

January 1995

2

Philips Semiconductors

Product specification

Quadruple exclusive-OR gate

HEF4030B

gates

DESCRIPTION

The HEF4030B provides the positive quadruple

exclusive-OR function. The outputs are fully buffered for

highest noise immunity and pattern insensitivity of output

impedance.

Fig.1 Functional diagram.

HEF4030BP(N):

14-lead DIL; plastic

(SOT27-1)

HEF4030BD(F):

14-lead DIL; ceramic (cerdip)

(SOT73)

HEF4030BT(D):

14-lead SO; plastic

(SOT108-1)

( ): Package Designator North America

Fig.2 Pinning diagram.

Fig.2 Logic diagram (one gate).

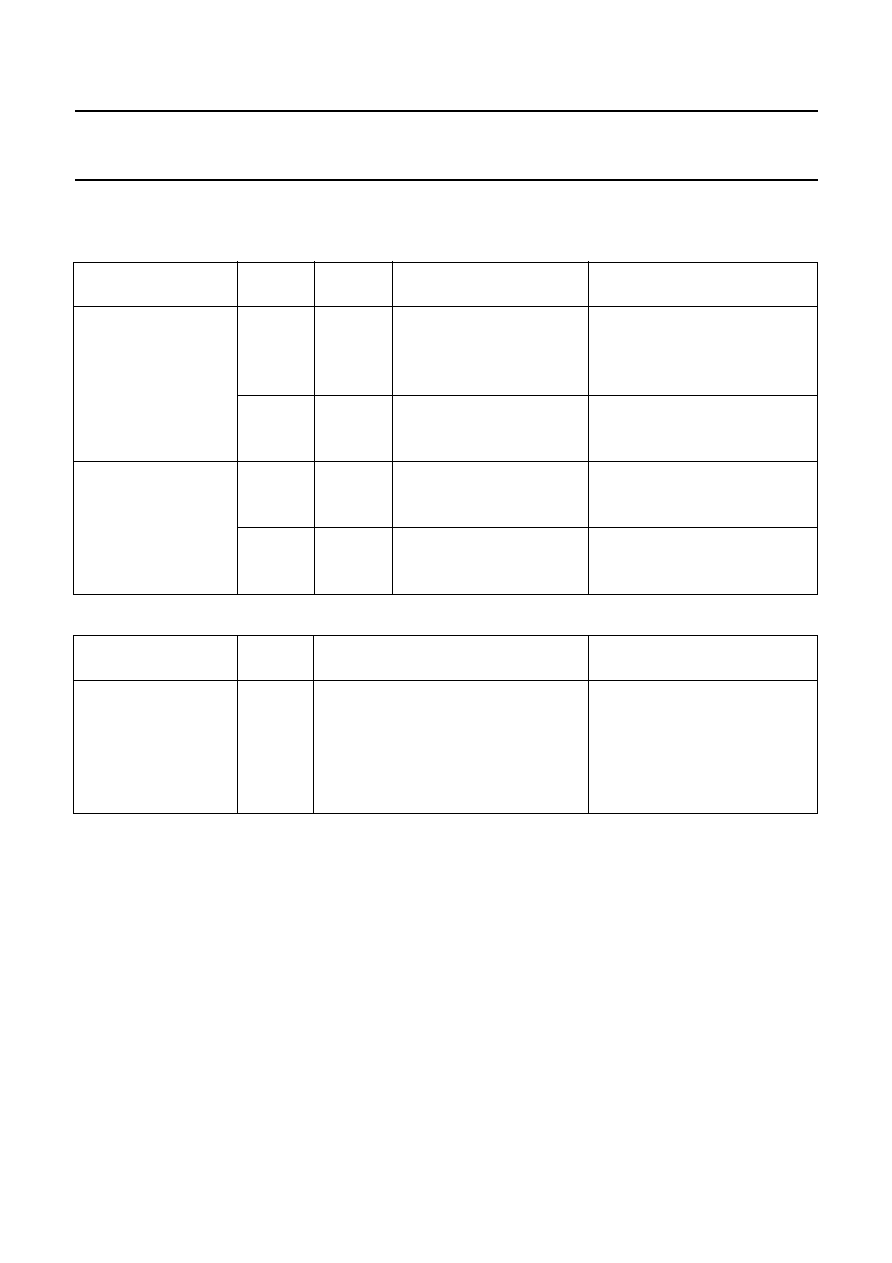

TRUTH TABLE

Notes

1. H = HIGH state (the more positive voltage)

L = LOW state (the less positive voltage)

I

1

I

2

O

1

L

L

L

H

L

H

L

H

H

H

H

L

FAMILY DATA, I

DD

LIMITS category GATES

See Family Specifications