DATA SHEET

Product specification

File under Integrated Circuits, IC04

January 1995

INTEGRATED CIRCUITS

HEF4049B

buffers

HEX inverting buffers

For a complete data sheet, please also download:

∑

The IC04 LOCMOS HE4000B Logic

Family Specifications HEF, HEC

∑

The IC04 LOCMOS HE4000B Logic

Package Outlines/Information HEF, HEC

January 1995

2

Philips Semiconductors

Product specification

HEX inverting buffers

HEF4049B

buffers

DESCRIPTION

The HEF4049B provides six inverting buffers with high

current output capability suitable for driving TTL or high

capacitive loads. Since input voltages in excess of the

buffers' supply voltage are permitted, the buffers may also

be used to convert logic levels of up to 15 V to standard

TTL levels. Their guaranteed fan-out into common bipolar

logic elements is shown in the table below.

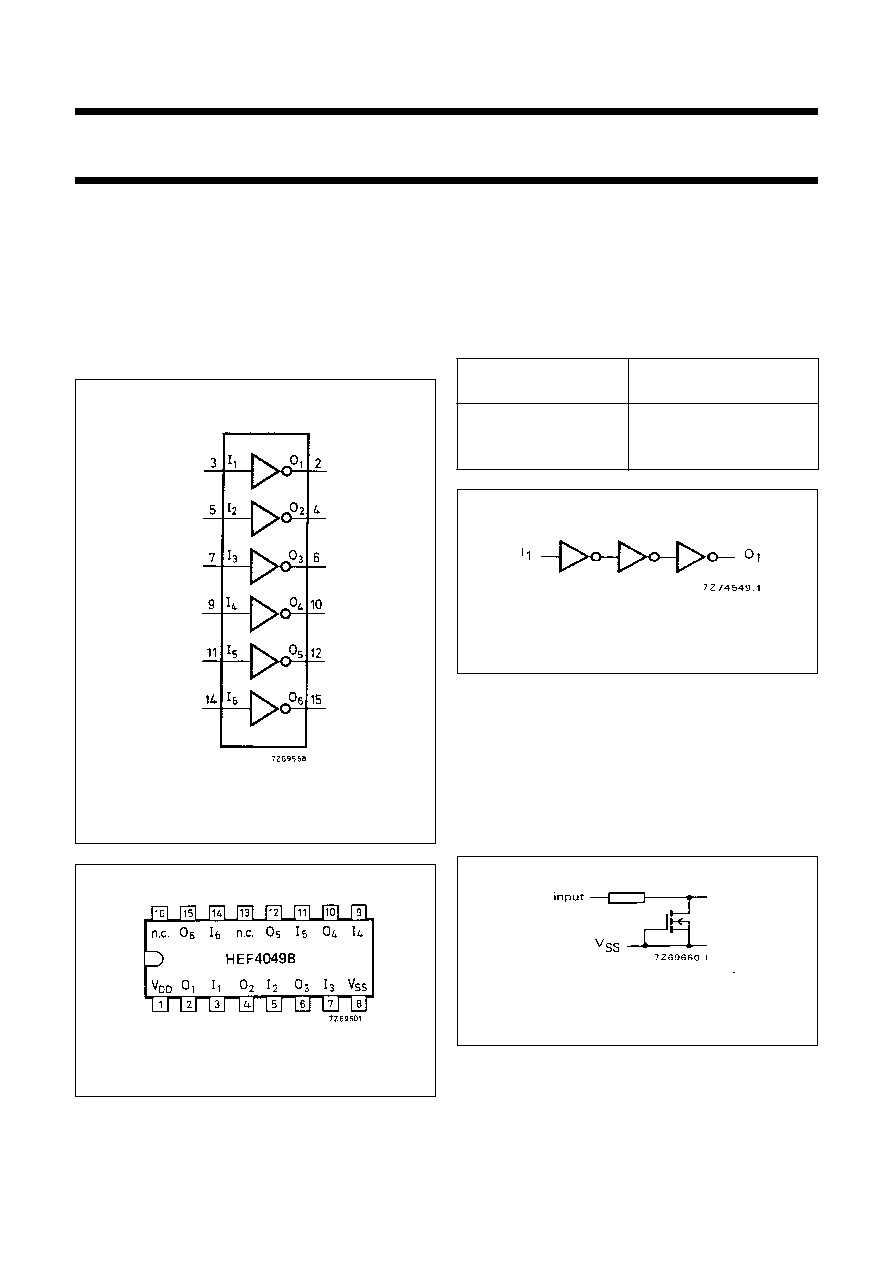

Fig.1 Functional diagram.

Fig.2 Pinning diagram.

Guaranteed fan-out in common logic families

APPLICATION INFORMATION

Some examples of applications for the HEF4049B are:

∑

LOCMOS to DTL/TTL converter

∑

HIGH sink current for driving 2 TTL loads

∑

HIGH-to-LOW level logic conversion

Input protection

FAMILY DATA, I

DD

LIMITS category BUFFERS

See Family Specifications

HEF4049BP(N): 16-lead DIL; plastic (SOT38-1)

HEF4049BD(F): 16-lead DIL; ceramic (cerdip) (SOT74)

HEF4049BT(D): 16-lead SO; plastic (SOT109-1)

( ): Package Designator North America

DRIVEN ELEMENT

GUARANTEED

FAN-OUT

standard TTL

2

74 LS

9

74 L

16

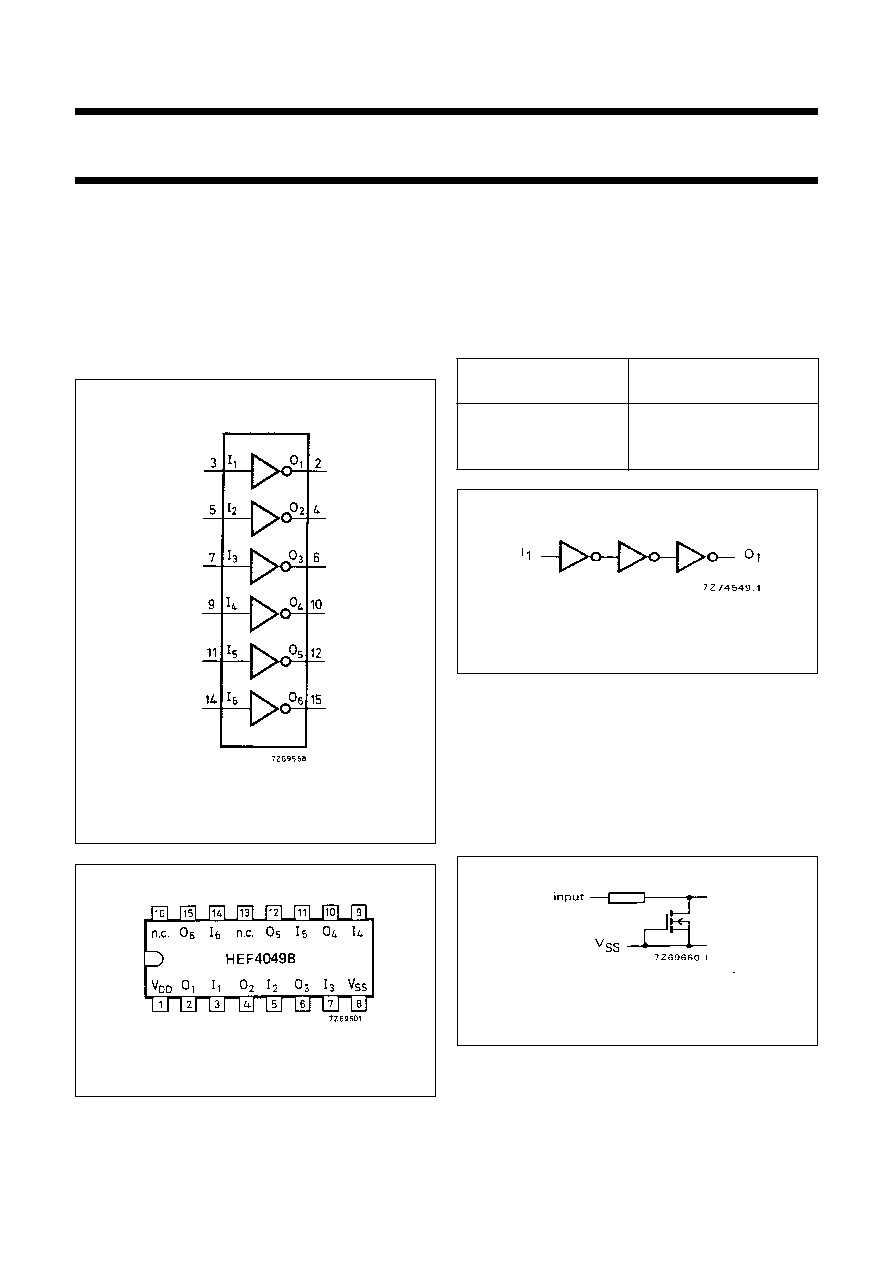

Fig.3 Logic diagram (one gate).

Fig.4

Input protection circuit that allows input

voltages in excess of V

DD

.