2002 Nov 12

2

Philips Semiconductors

Preliminary specification

Single 2-input NAND gate

74AUC1G00

FEATURES

∑

Wide supply voltage range from 0.8 to 2.7 V

∑

Performance optimised for V

CC

= 1.8 V

∑

High noise immunity

∑

Complies with JEDEC standard:

≠ JESD76 (1.65 to 1.95 V)

∑

8 mA output drive (V

CC

= 1.65 V)

∑

CMOS low power consumption

∑

Latch-up performance exceeds 250 mA

∑

ESD protection:

2000 V Human Body Model (A 114-A)

200 V Machine Model (A 115-A)

∑

3.3 V tolerant inputs/outputs

∑

SC-88A and SC-74A package.

DESCRIPTION

The 74AUC1G00 is a high-performance, low-power,

low-voltage, Si-gate CMOS device.

Schmitt-trigger action at all inputs makes the circuit

tolerant for slower input rise and fall time.

This device is fully specified for partial power-down

applications using I

off

. The I

off

circuitry disables the output,

preventing the damaging current backflow through the

device when it is powered down.

The 74AUC1G00 provides the single 2-input NAND

function.

QUICK REFERENCE DATA

GND = 0 V; T

amb

= 25

∞

C; input slewrate

1 V/ns.

Notes

1. C

PD

is used to determine the dynamic power dissipation (P

D

in

µ

W).

P

D

= C

PD

◊

V

CC

2

◊

f

i

+ (C

L

◊

V

CC

2

◊

f

o

) where:

f

i

= input frequency in MHz;

f

o

= output frequency in MHz;

C

L

= output load capacitance in pF;

V

CC

= supply voltage in Volts.

2. The condition is V

I

= GND to V

CC

.

SYMBOL

PARAMETER

CONDITIONS

TYPICAL

UNIT

t

PHL

/t

PLH

propagation delay inputs A and B to

output Y

V

CC

= 0.8 V; C

L

= 15 pF; R

L

= 2 k

4.7

ns

V

CC

= 1.2 V; C

L

= 15 pF; R

L

= 2 k

1.8

ns

V

CC

= 1.5 V; C

L

= 15 pF; R

L

= 2 k

1.4

ns

V

CC

= 1.8 V; C

L

= 30 pF; R

L

= 1 k

1.4

ns

V

CC

= 2.5 V; C

L

= 30 pF; R

L

= 500

1.2

ns

C

I

input capacitance

4

pF

C

PD

power dissipation capacitance per buffer

V

CC

= 1.8 V; notes 1 and 2

14

pF

2002 Nov 12

4

Philips Semiconductors

Preliminary specification

Single 2-input NAND gate

74AUC1G00

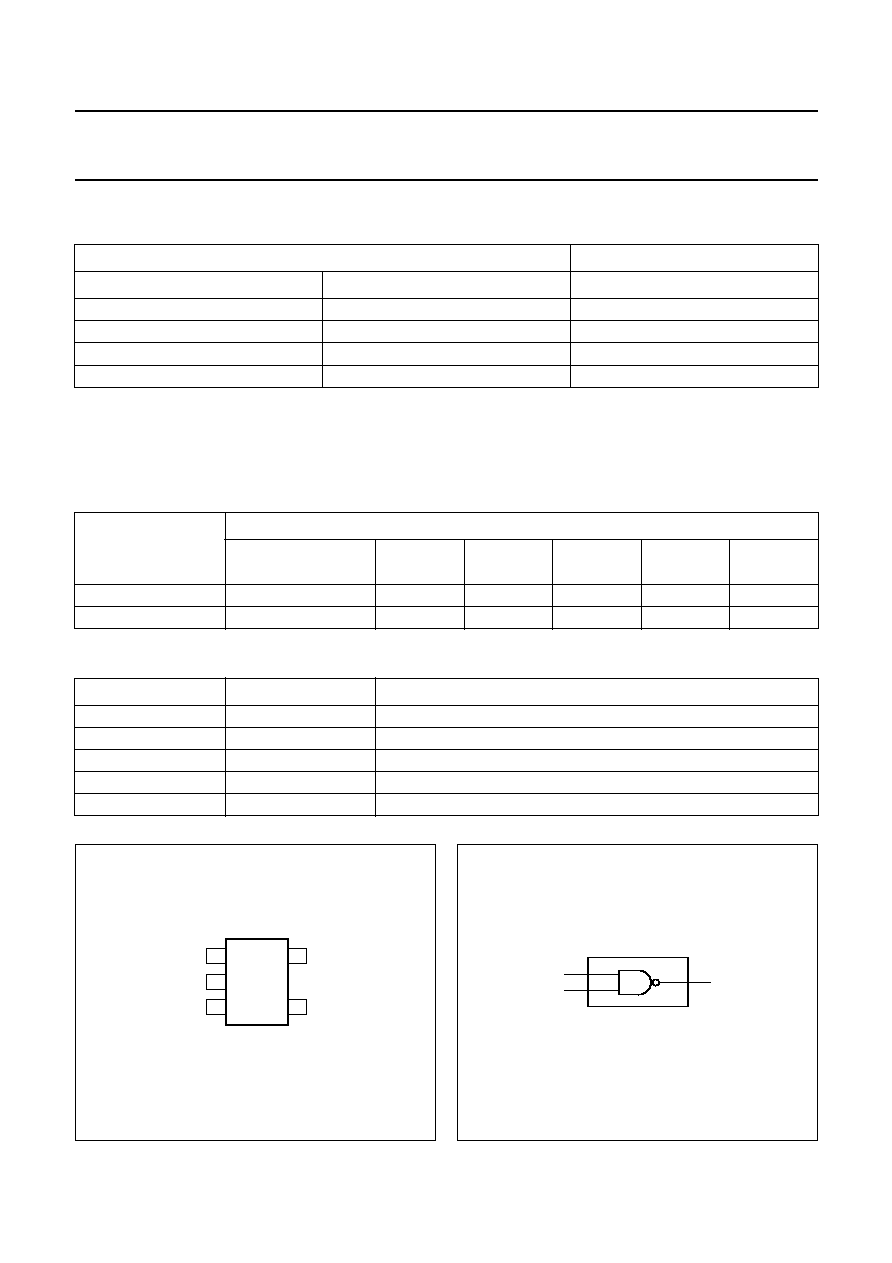

handbook, halfpage

MNA098

2

4

&

1

Fig.3 IEE/IEC logic symbol.

handbook, halfpage

MNA099

B

A

Y

Fig.4 Logic diagram.

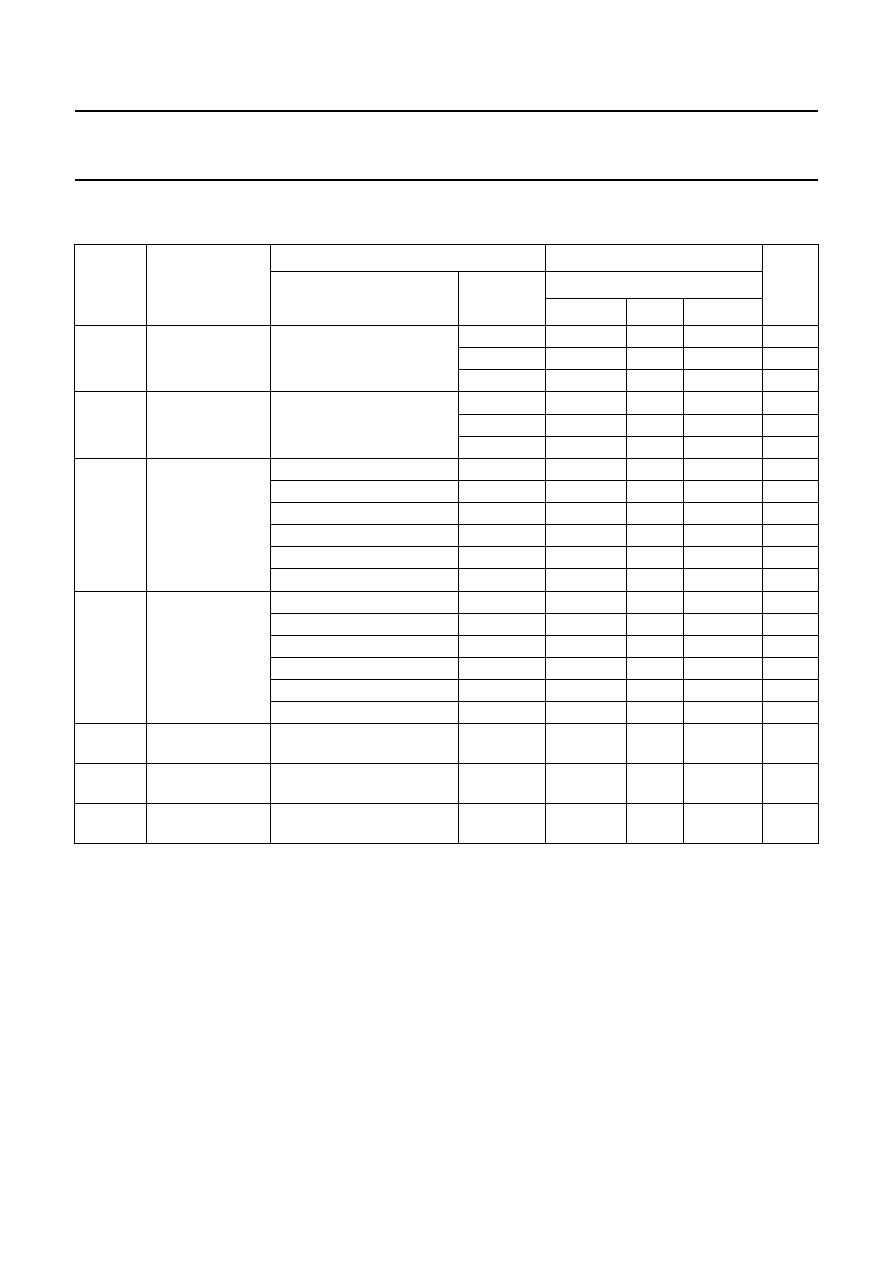

RECOMMENDED OPERATING CONDITIONS

LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 60134); voltages are referenced to GND (ground = 0 V).

Notes

1. The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

2. When V

CC

=0 (Powered-down mode), the output voltage can be 2.7 V in normal operation.

SYMBOL

PARAMETER

CONDITIONS

MIN.

MAX.

UNIT

V

CC

supply voltage

0.8

2.7

V

V

I

input voltage

0

2.7

V

V

O

output voltage

active mode

0

V

CC

V

V

CC

= 0 V; Power-down mode

0

2.7

V

T

amb

operating ambient temperature

-

40

+85

∞

C

t

r

,t

f

(

t/

f)

input rise and fall times

0

20

ns/V

SYMBOL

PARAMETER

CONDITIONS

MIN.

MAX.

UNIT

V

CC

supply voltage

-

0.5

+3.6

V

I

IK

input diode current

V

I

< 0

-

-

50

mA

V

I

input voltage

note 1

-

0.5

+3.6

V

I

OK

output diode current

V

O

> V

CC

or V

O

< 0

-

±

50

mA

V

O

output voltage

active mode; notes 1 and 2

-

0.5

V

CC

+ 0.5

V

Power-down mode; notes 1 and 2

-

0.5

+3.6

V

I

O

output source or sink current

V

O

= 0 to V

CC

-

±

60

mA

I

CC

, I

GND

V

CC

or GND current

-

±

100

mA

T

stg

storage temperature

-

65

+150

∞

C

P

D

power dissipation per package

for temperature range from

-

40 to +85

∞

C

-

250

mW