| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: 74HC157D | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

DATA SHEET

Product specification

File under Integrated Circuits, IC06

December 1990

INTEGRATED CIRCUITS

74HC/HCT157

Quad 2-input multiplexer

For a complete data sheet, please also download:

∑

The IC06 74HC/HCT/HCU/HCMOS Logic Family Specifications

∑

The IC06 74HC/HCT/HCU/HCMOS Logic Package Information

∑

The IC06 74HC/HCT/HCU/HCMOS Logic Package Outlines

December 1990

2

Philips Semiconductors

Product specification

Quad 2-input multiplexer

74HC/HCT157

FEATURES

∑

Non-inverting data path

∑

Output capability: standard

∑

I

CC

category: MSI

GENERAL DESCRIPTION

The 74HC/HCT157 are high-speed Si-gate CMOS devices

and are pin compatible with low power Schottky TTL

(LSTTL). They are specified in compliance with JEDEC

standard no. 7A.

The 74HC/HCT157 are quad 2-input multiplexers which

select 4 bits of data from two sources under the control of

a common data select input (S). The four outputs present

the selected data in the true (non-inverted) form. The

enable input (E) is active LOW. When E is HIGH, all of the

outputs (1Y to 4Y) are forced LOW regardless of all other

input conditions.

Moving the data from two groups of registers to four

common output buses is a common use of the "157". The

state of the common data select input (S) determines the

particular register from which the data comes. It can also

be used as function generator.

The device is useful for implementing highly irregular logic

by generating any four of the 16 different functions of two

variables with one variable common.

The "157" is the logic implementation of a 4-pole,

2-position switch, where the position of the switch is

determined by the logic levels applied to S.

The logic equations are:

1Y = E.(1l

1

.S + 1l

0

.S)

2Y = E.(2l

1

.S + 2l

0

.S)

3Y = E.(3l

1

.S + 3l

0

.S)

4Y = E.(4l

1

.S + 4l

0

.S)

The "157" is identical to the "158" but has non-inverting

(true) outputs.

QUICK REFERENCE DATA

GND = 0 V; T

amb

= 25

∞

C; t

r

= t

f

= 6 ns

Notes

1. C

PD

is used to determine the dynamic power dissipation (P

D

in

µ

W):

P

D

= C

PD

◊

V

CC

2

◊

f

i

+

(C

L

◊

V

CC

2

◊

f

o

) where:

f

i

= input frequency in MHz

f

o

= output frequency in MHz

(C

L

◊

V

CC

2

◊

f

o

) = sum of outputs

C

L

= output load capacitance in pF

V

CC

= supply voltage in V

2. For HC the condition is V

I

= GND to V

CC

For HCT the condition is V

I

= GND to V

CC

-

1.5 V

ORDERING INFORMATION

See

"74HC/HCT/HCU/HCMOS Logic Package Information"

.

SYMBOL

PARAMETER

CONDITIONS

TYPICAL

UNIT

HC

HCT

t

PHL

/ t

PLH

propagation delay

C

L

= 15 pF; V

CC

= 5 V

nI

0

, nI

1

to nY

11

13

ns

E to nY

11

12

ns

S to nY

12

19

ns

C

I

input capacitance

3.5

3.5

pF

C

PD

power dissipation capacitance per multiplexer notes 1 and 2

70

70

pF

December 1990

3

Philips Semiconductors

Product specification

Quad 2-input multiplexer

74HC/HCT157

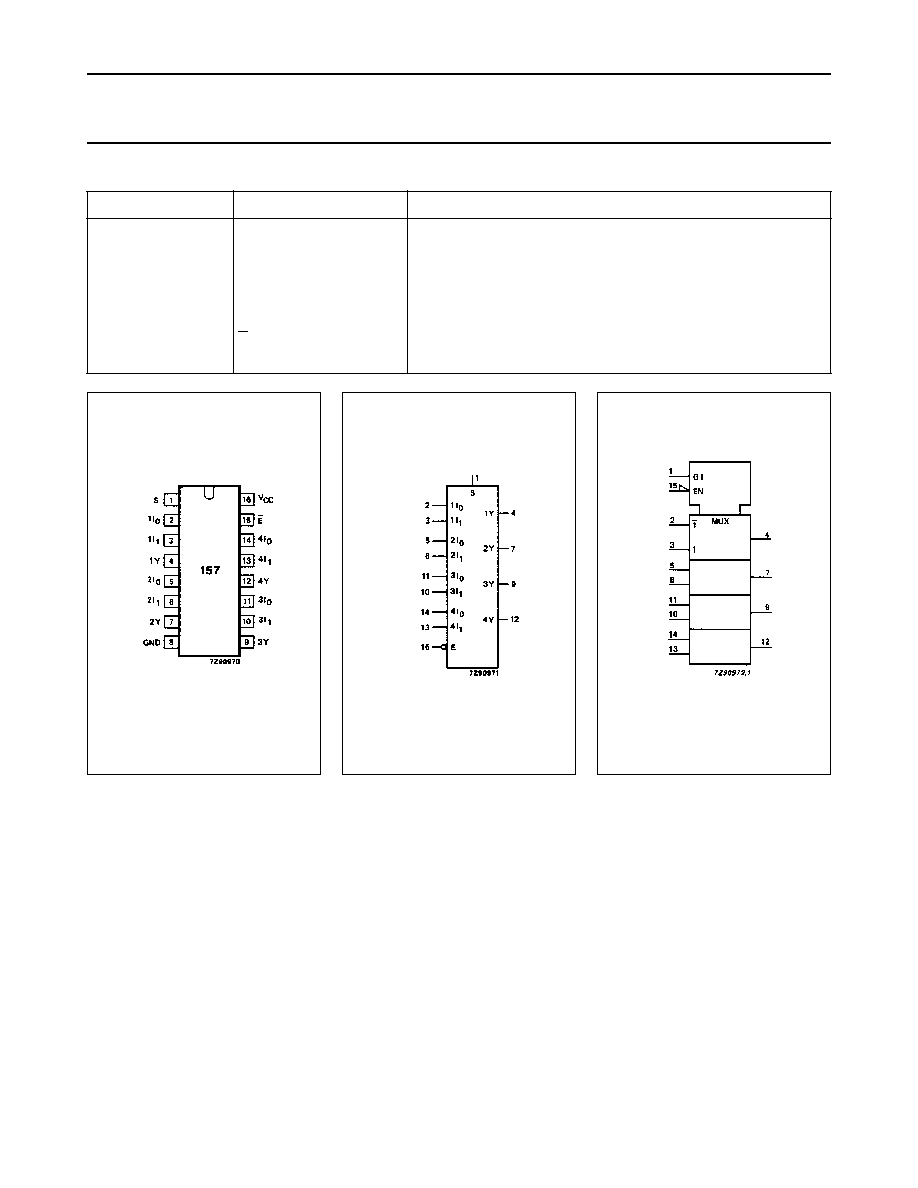

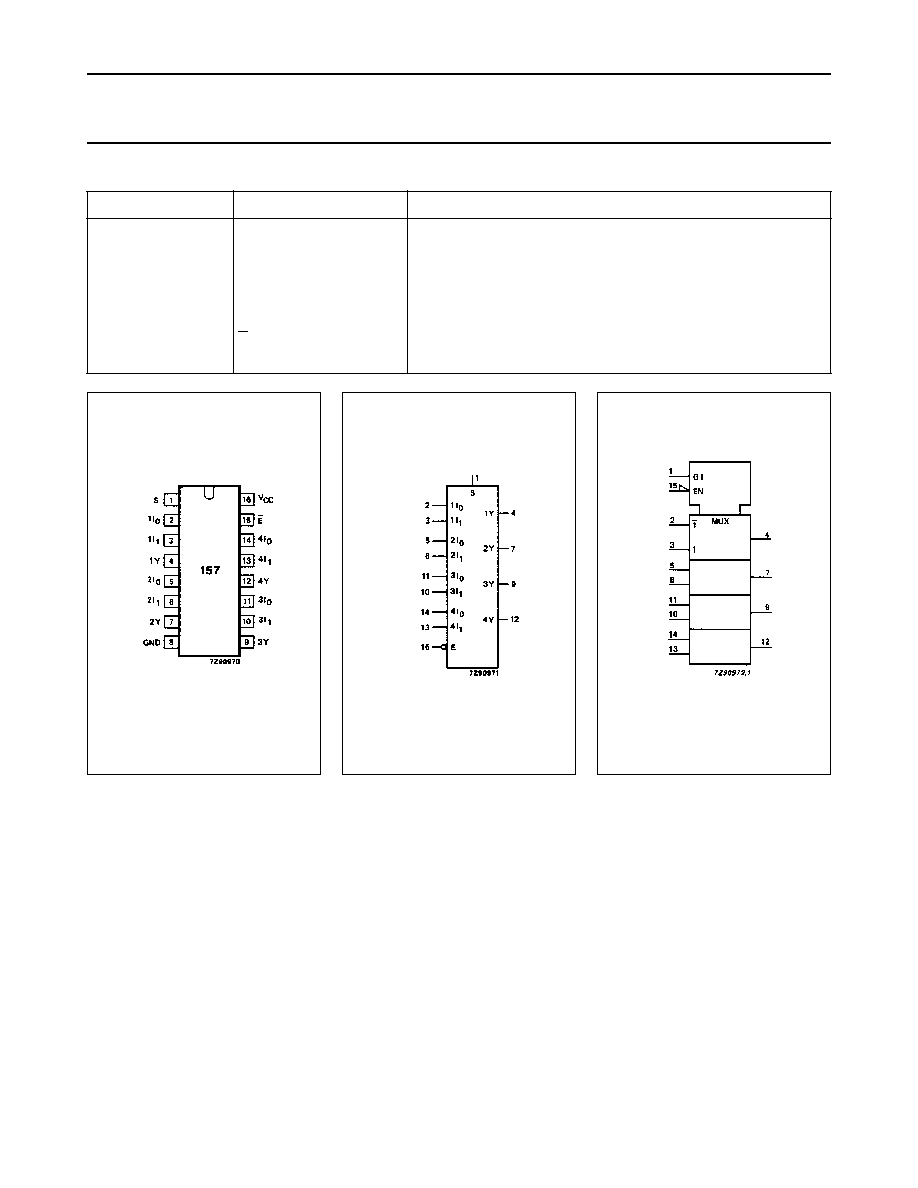

PIN DESCRIPTION

PIN NO.

SYMBOL

NAME AND FUNCTION

1

S

common data select input

2, 5, 11, 14

1I

0

to 4I

0

data inputs from source 0

3, 6, 10, 13

1I

1

to 4I

1

data inputs from source 1

4, 7, 9, 12

1Y to 4Y

multiplexer outputs

8

GND

ground (0 V)

15

E

enable input (active LOW)

16

V

CC

positive supply voltage

Fig.1 Pin configuration.

Fig.2 Logic symbol.

Fig.3 IEC logic symbol.

December 1990

4

Philips Semiconductors

Product specification

Quad 2-input multiplexer

74HC/HCT157

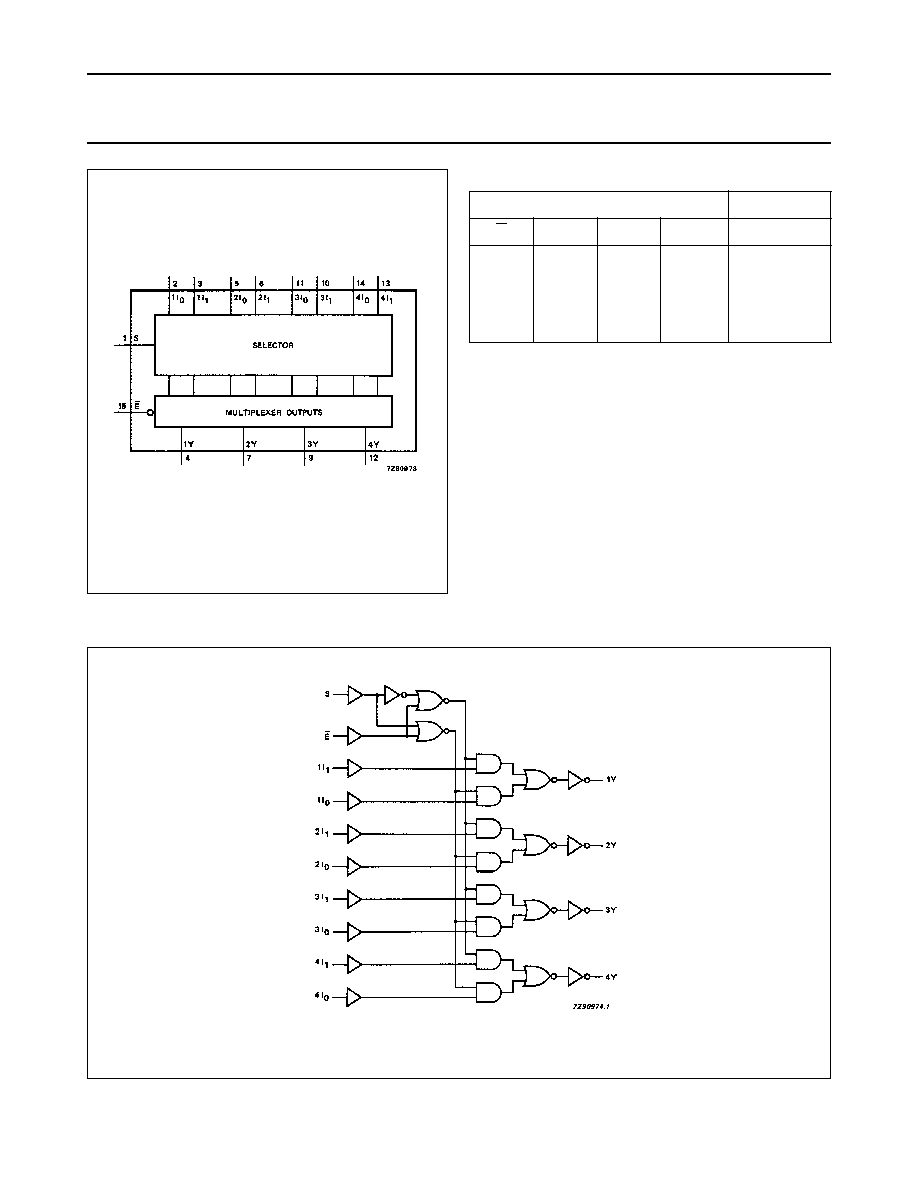

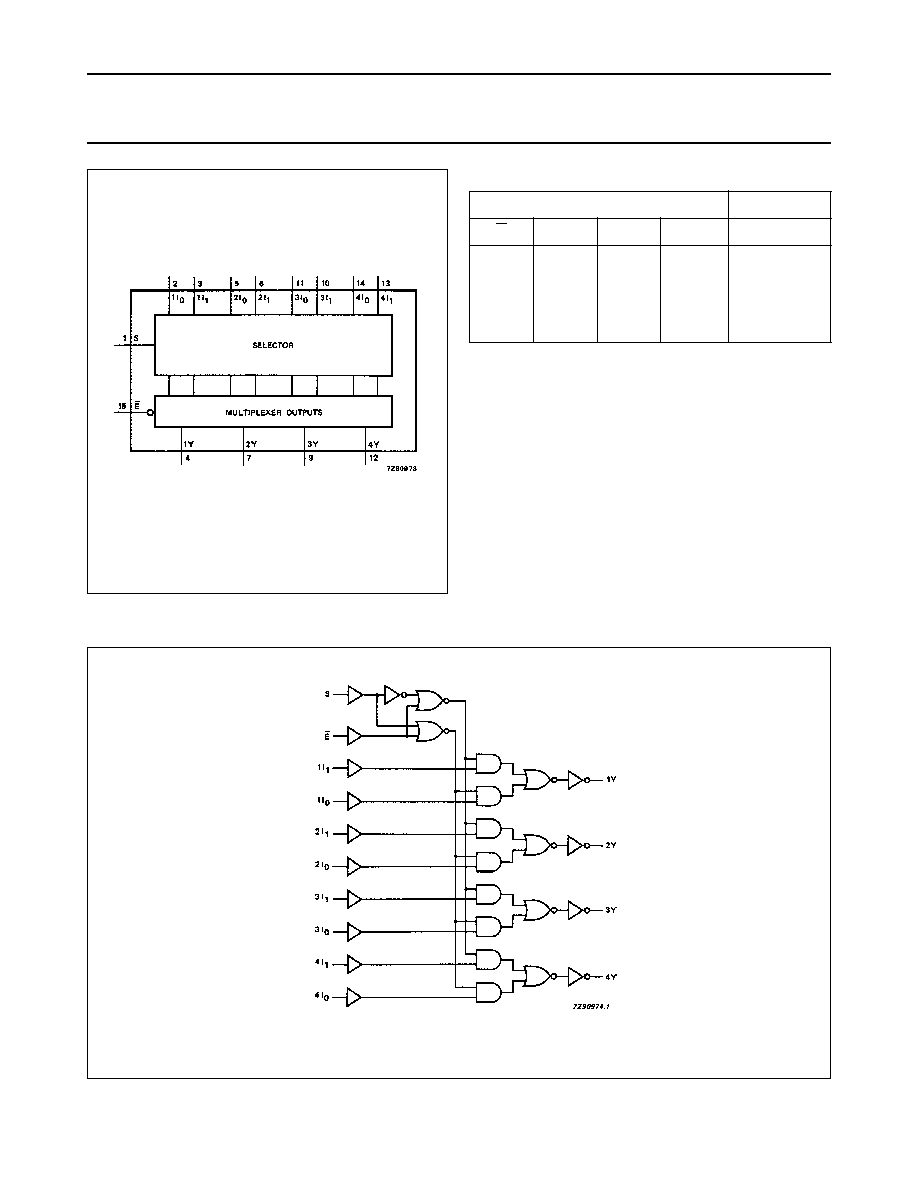

Fig.4 Functional diagram.

FUNCTION TABLE

Notes

1. H = HIGH voltage level

L = LOW voltage level

X = don't care

INPUTS

OUTPUT

E

S

nI

0

nI

1

nY

H

X

X

X

L

L

L

L

L

L

L

H

H

L

H

X

X

X

X

L

H

L

H

L

H

Fig.5 Logic diagram.

December 1990

5

Philips Semiconductors

Product specification

Quad 2-input multiplexer

74HC/HCT157

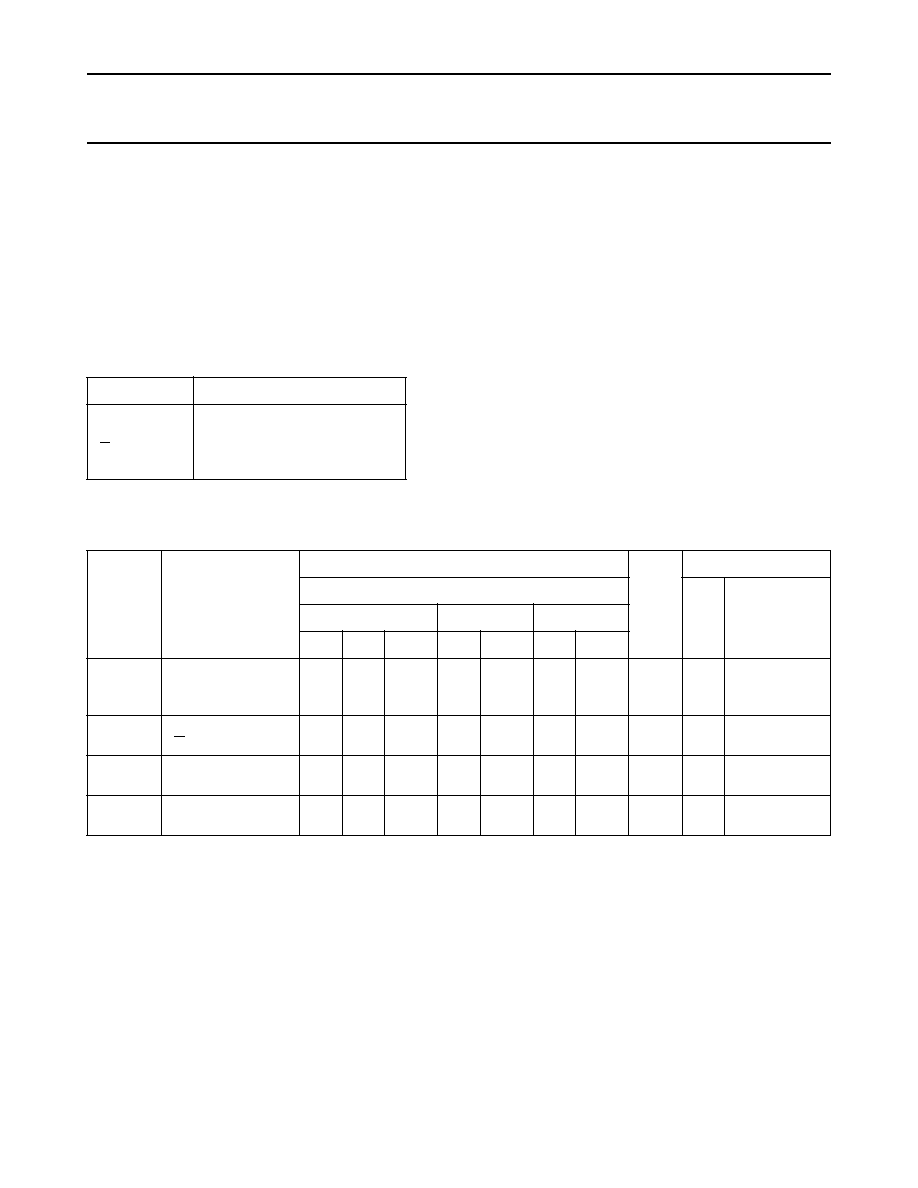

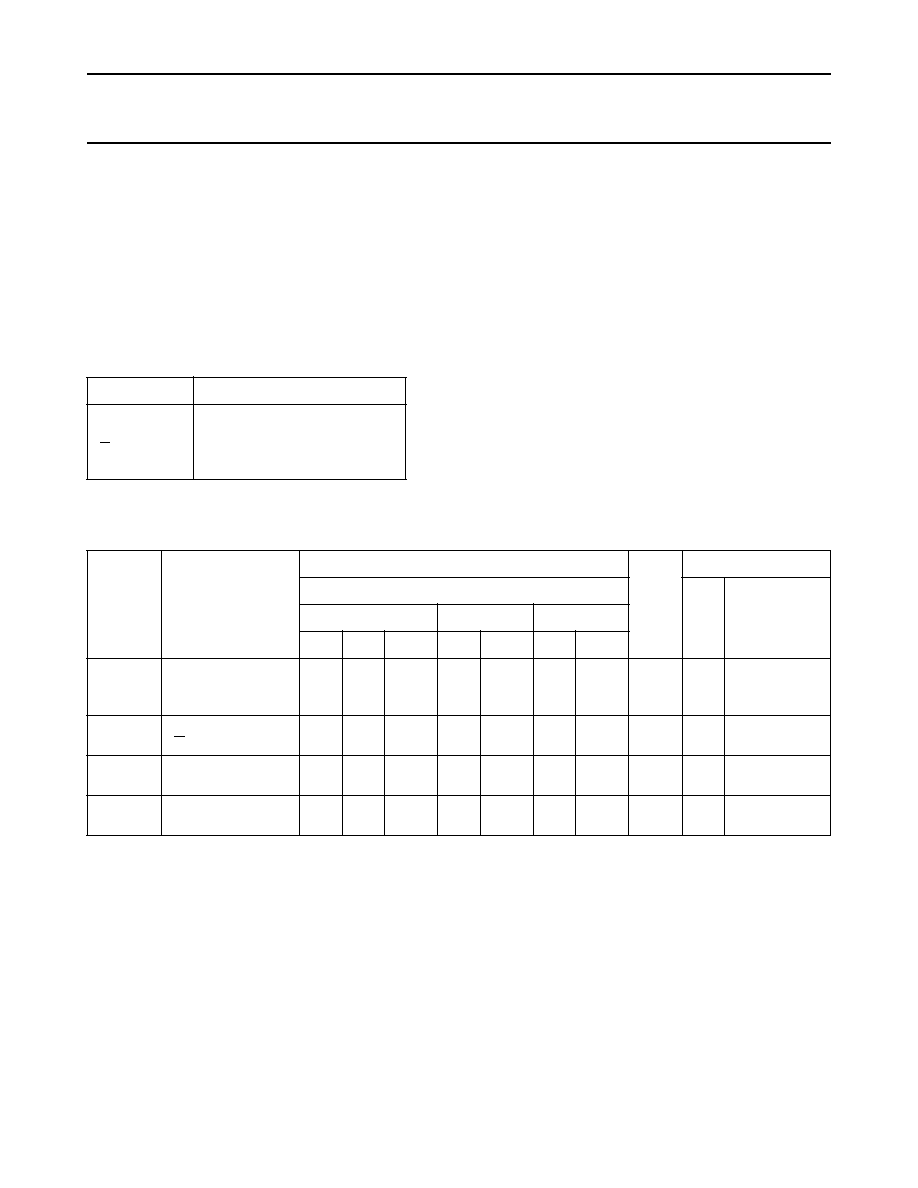

DC CHARACTERISTICS FOR 74HC

For the DC characteristics see

"74HC/HCT/HCU/HCMOS Logic Family Specifications"

.

Output capability: standard

I

CC

category: MSI

AC CHARACTERISTICS FOR 74HC

GND = 0 V; t

r

= t

f

= 6 ns; C

L

= 50 pF

SYMBOL

PARAMETER

T

amb

(

∞

C)

UNIT

TEST CONDITIONS

74HC

V

CC

(V)

WAVEFORMS

+25

-

40 to +85

-

40 to +125

min.

typ.

max.

min.

max.

min.

max.

t

PHL

/ t

PLH

propagation delay

nI

0

to nY;

nI

1

to nY

36

13

10

125

25

21

155

31

26

190

38

32

ns

2.0

4.5

6.0

Fig.7

t

PHL

/ t

PLH

propagation delay

E to nY

39

14

11

115

23

20

145

29

25

175

35

30

ns

2.0

4.5

6.0

Fig.6

t

PHL

/ t

PLH

propagation delay

S to nY

41

15

12

125

25

21

155

31

26

190

38

32

ns

2.0

4.5

6.0

Fig.7

t

THL

/ t

TLH

output transition

time

19

7

6

75

15

13

95

19

16

110

22

19

ns

2.0

4.5

6.0

Fig.6 and Fig.7

December 1990

6

Philips Semiconductors

Product specification

Quad 2-input multiplexer

74HC/HCT157

DC CHARACTERISTICS FOR 74HCT

For the DC characteristics see

"74HC/HCT/HCU/HCMOS Logic Family Specifications"

.

Output capability: standard

I

CC

category: MSI

Note to HCT types

The value of additional quiescent supply current (

I

CC

) for a unit load of 1 is given in the family specifications.

To determine

I

CC

per input, multiply this value by the unit load coefficient shown in the table below.

AC CHARACTERISTICS FOR 74HCT

GND = 0 V; t

r

= t

f

= 6 ns; C

L

= 50 pF

INPUT

UNIT LOAD COEFFICIENT

nI

0

nI

1

E

S

1.00

1.00

0.60

1.00

SYMBOL

PARAMETER

T

amb

(

∞

C)

UNIT

TEST CONDITIONS

74HCT

V

CC

(V)

WAVEFORMS

+25

-

40 to +85

-

40 to +125

min.

typ.

max.

min.

max.

min.

max.

t

PHL

/ t

PLH

propagation delay

nI

0

to nY;

nI

1

to nY

16

27

34

41

ns

4.5

Fig.7

t

PHL

/ t

PLH

propagation delay

E to nY

15

26

33

39

ns

4.5

Fig.6

t

PHL

/ t

PLH

propagation delay

S to nY

22

37

46

56

ns

4.5

Fig.7

t

THL

/ t

TLH

output transition

time

7

15

19

22

ns

4.5

Fig.6 and Fig.7

December 1990

7

Philips Semiconductors

Product specification

Quad 2-input multiplexer

74HC/HCT157

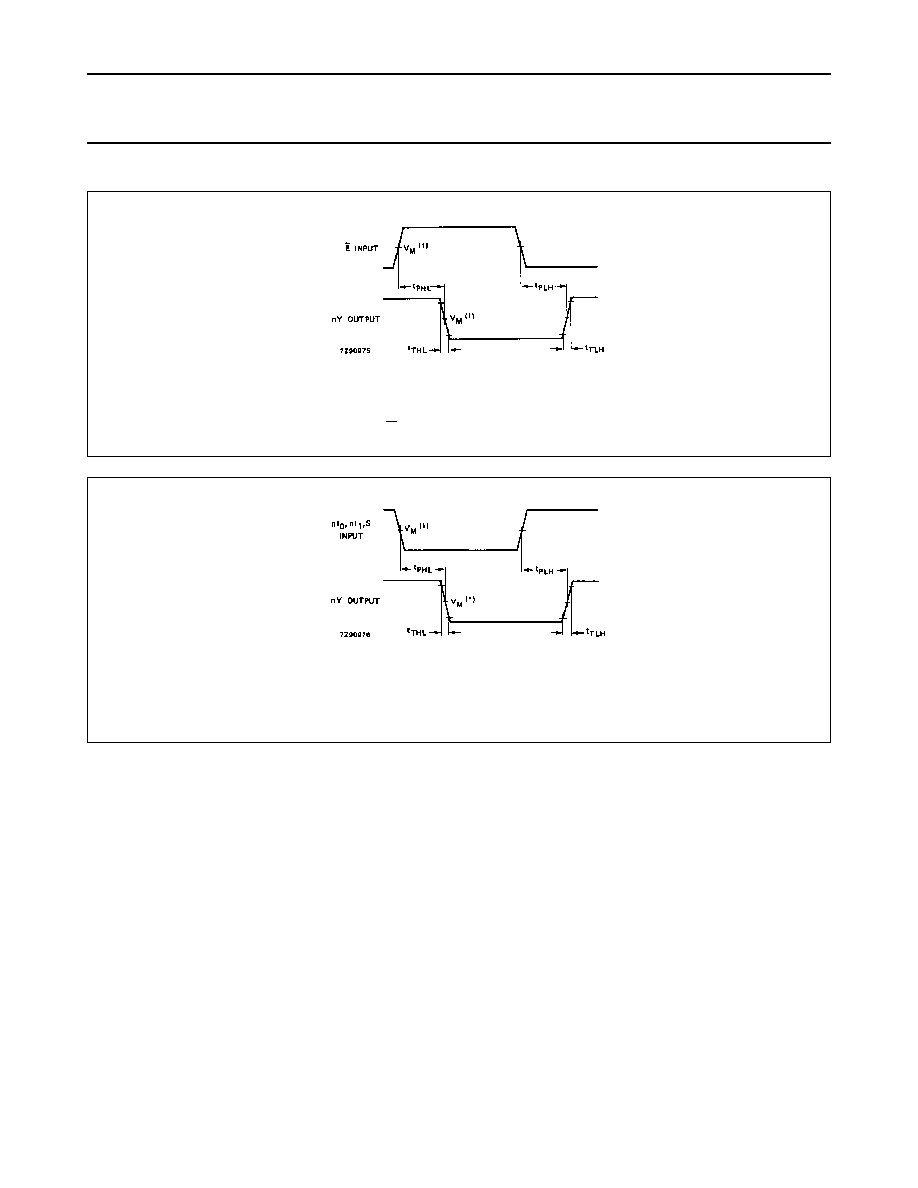

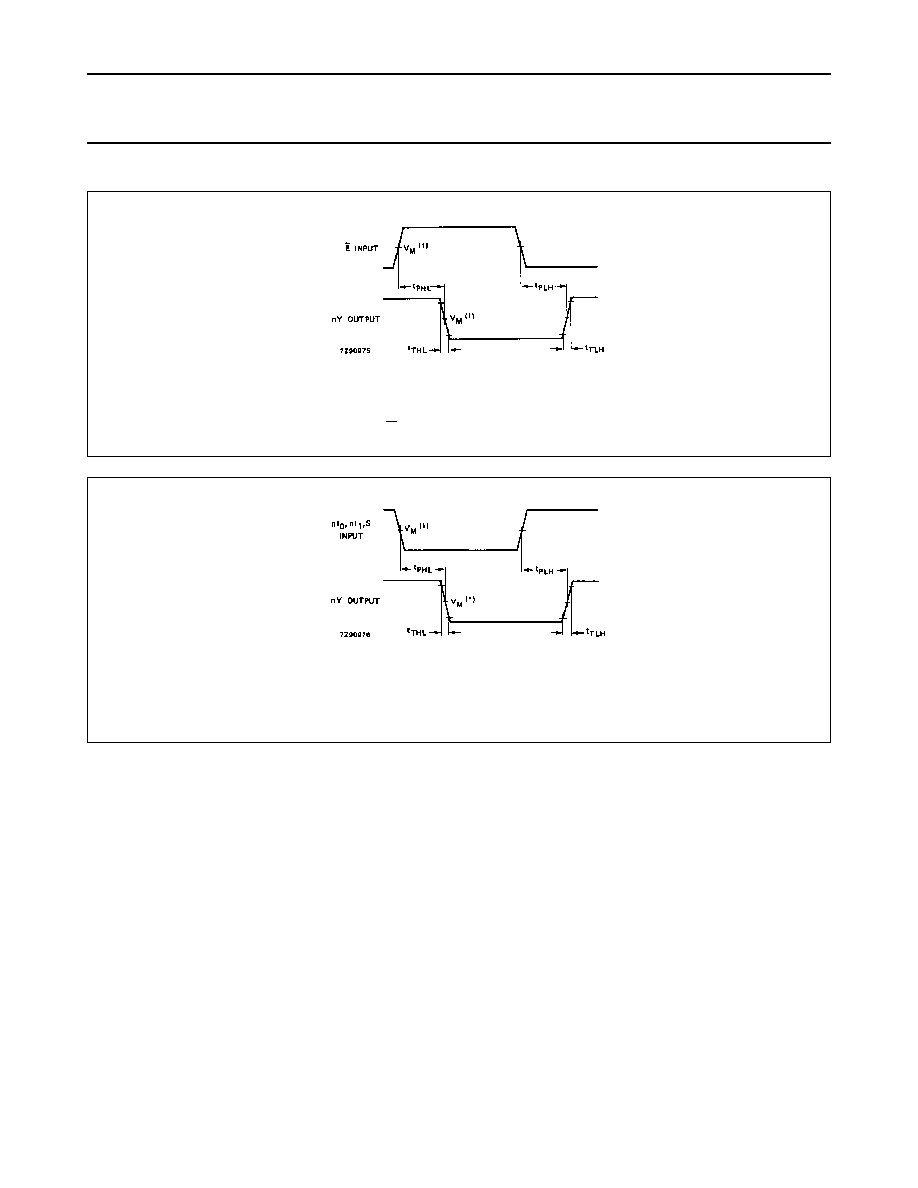

AC WAVEFORMS

PACKAGE OUTLINES

See

"74HC/HCT/HCU/HCMOS Logic Package Outlines"

.

Fig.6 Waveforms showing the enable input (E) to output (nY) propagation delays and the output transition times.

(1) HC : V

M

= 50%; V

I

= GND to V

CC

.

HCT: V

M

= 1.3 V; V

I

= GND to 3 V.

Fig.7

Waveforms showing the data inputs (nI

n

) and common data select input (S) to output (nY) propagation

delays.

(1) HC : V

M

= 50%; V

I

= GND to V

CC

.

HCT: V

M

= 1.3 V; V

I

= GND to 3 V.