| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: 74HC377D | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

DATA SHEET

Product specification

File under Integrated Circuits, IC06

December 1990

INTEGRATED CIRCUITS

74HC/HCT377

Octal D-type flip-flop with data

enable; positive-edge trigger

For a complete data sheet, please also download:

∑

The IC06 74HC/HCT/HCU/HCMOS Logic Family Specifications

∑

The IC06 74HC/HCT/HCU/HCMOS Logic Package Information

∑

The IC06 74HC/HCT/HCU/HCMOS Logic Package Outlines

December 1990

2

Philips Semiconductors

Product specification

Octal D-type flip-flop with data enable;

positive-edge trigger

74HC/HCT377

FEATURES

∑

Ideal for addressable register applications

∑

Data enable for address and data synchronization

applications

∑

Eight positive-edge triggered D-type flip-flops

∑

See "273" for master reset version

∑

See "373" for transparent latch version

∑

See "374" for 3-state version

∑

Output capability: standard

∑

I

CC

category: MSI

GENERAL DESCRIPTION

The 74HC/HCT377 are high-speed Si-gate CMOS devices

and are pin compatible with low power Schottky TTL

(LSTTL). They are specified in compliance with JEDEC

standard no. 7A.

The 74HC/HCT377 have eight edge-triggered, D-type

flip-flops with individual D inputs and Q outputs. A common

clock (CP) input loads all flip-flops simultaneously when

the data enable (E) is LOW. The state of each D input, one

set-up time before the LOW-to-HIGH clock transition, is

transferred to the corresponding output (Q

n

) of the flip-flop.

The E input must be stable only one set-up time prior to the

LOW-to-HIGH transition for predictable operation.

QUICK REFERENCE DATA

GND = 0 V; T

amb

= 25

∞

C; t

r

= t

f

= 6 ns

Notes

1. C

PD

is used to determine the dynamic power dissipation (P

D

in

µ

W):

P

D

= C

PD

◊

V

CC

2

◊

f

i

+

(C

L

◊

V

CC

2

◊

f

o

) where:

f

i

= input frequency in MHz

f

o

= output frequency in MHz

(C

L

◊

V

CC

2

◊

f

o

) = sum of outputs

C

L

= output load capacitance in pF

V

CC

= supply voltage in V

2. For HC the condition is V

I

= GND to V

CC

For HCT the condition is V

I

= GND to V

CC

-

1.5 V

ORDERING INFORMATION

See

"74HC/HCT/HCU/HCMOS Logic Package Information"

.

SYMBOL

PARAMETER

CONDITIONS

TYPICAL

UNIT

HC

HCT

t

PHL

/ t

PLH

propagation delay CP to Q

n

C

L

= 15 pF; V

CC

= 5 V

13

14

ns

f

max

maximum clock frequency

77

53

MHz

C

I

input capacitance

3.5

3.5

pF

C

PD

power dissipation capacitance per flip-flop

notes 1 and 2

20

20

pF

December 1990

3

Philips Semiconductors

Product specification

Octal D-type flip-flop with data enable;

positive-edge trigger

74HC/HCT377

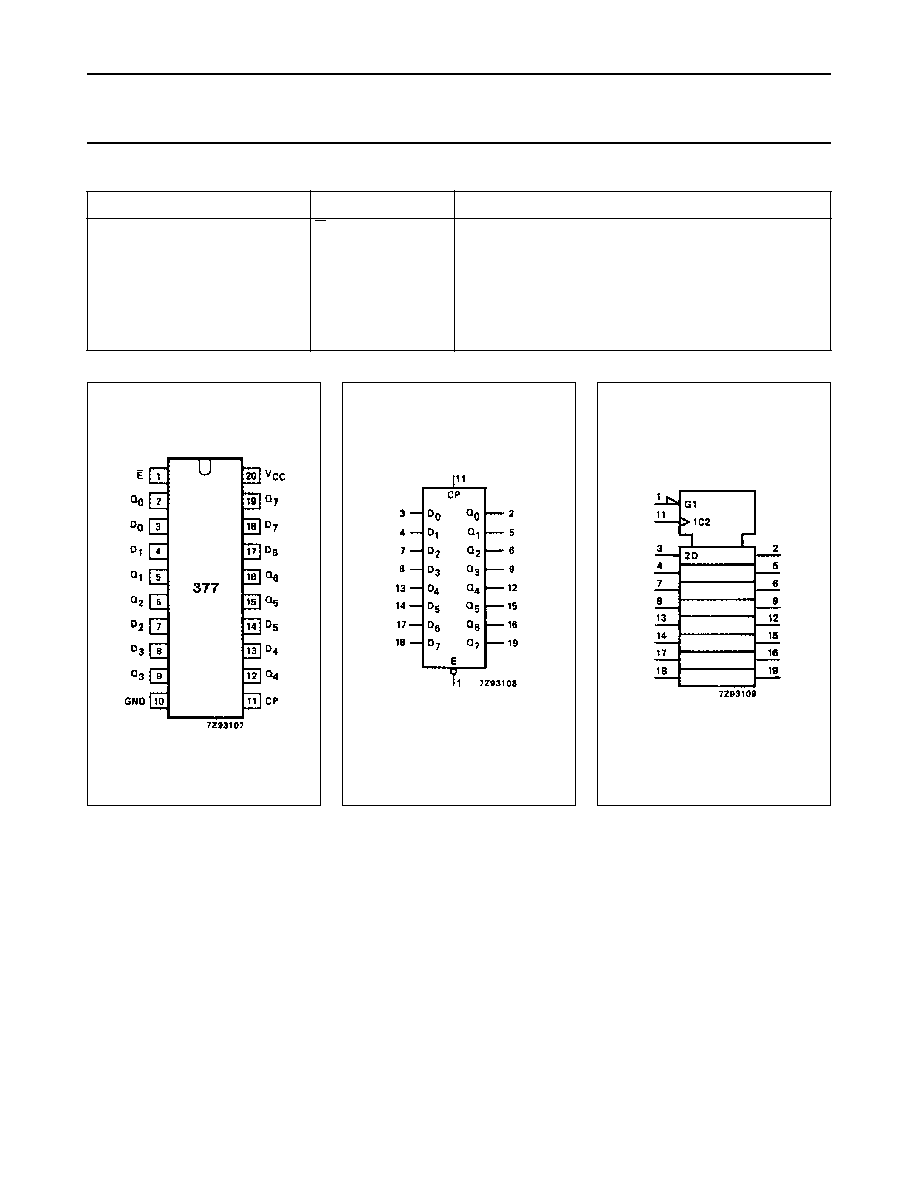

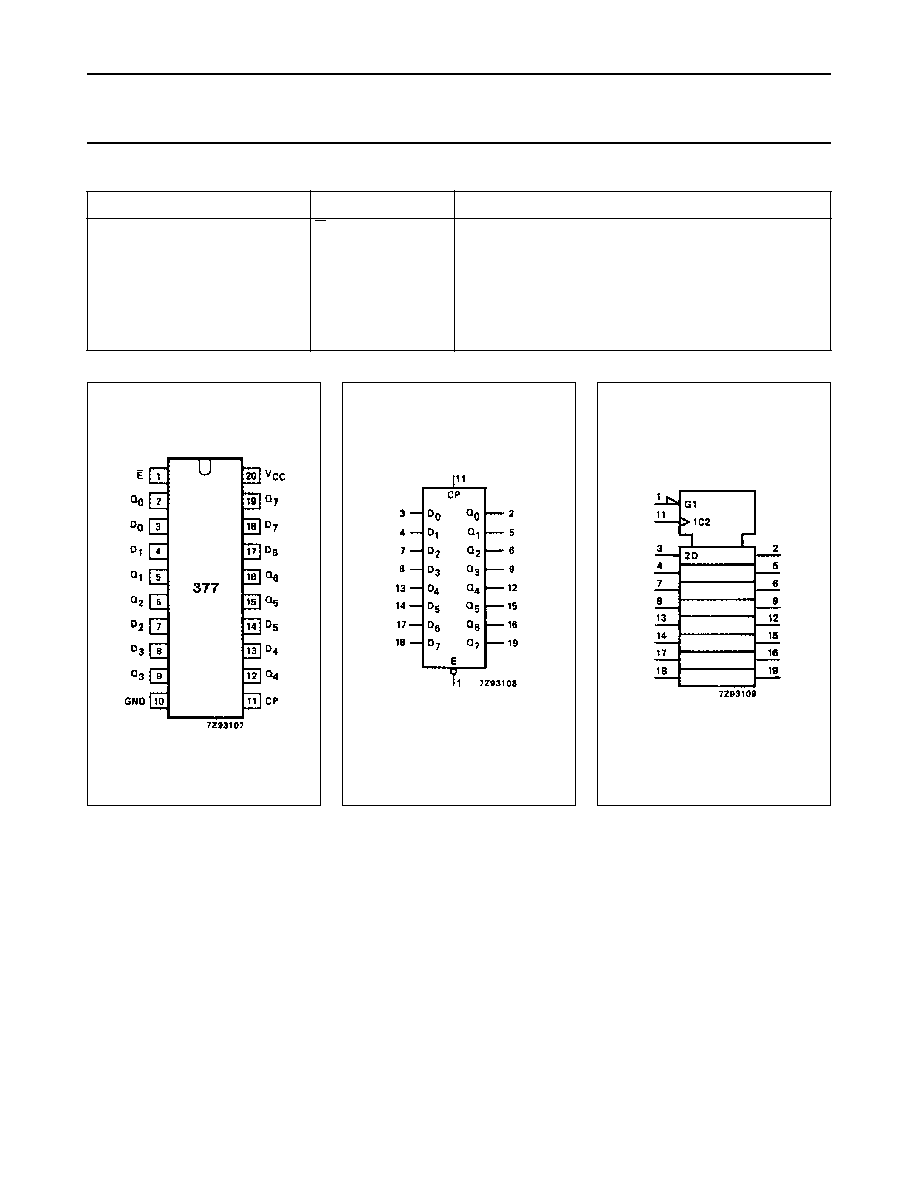

PIN DESCRIPTION

PIN NO.

SYMBOL

NAME AND FUNCTION

1

E

data enable input (active LOW)

2, 5, 6, 9, 12, 15, 16, 19

Q

0

to Q

7

flip-flop outputs

3, 4, 7, 8, 13, 14, 17, 18

D

0

to D

7

data inputs

10

GND

ground (0 V)

11

CP

clock input (LOW-to-HIGH, edge-triggered)

20

V

CC

positive supply voltage

Fig.1 Pin configuration.

Fig.2 Logic symbol.

Fig.3 IEC logic symbol.

December 1990

4

Philips Semiconductors

Product specification

Octal D-type flip-flop with data enable;

positive-edge trigger

74HC/HCT377

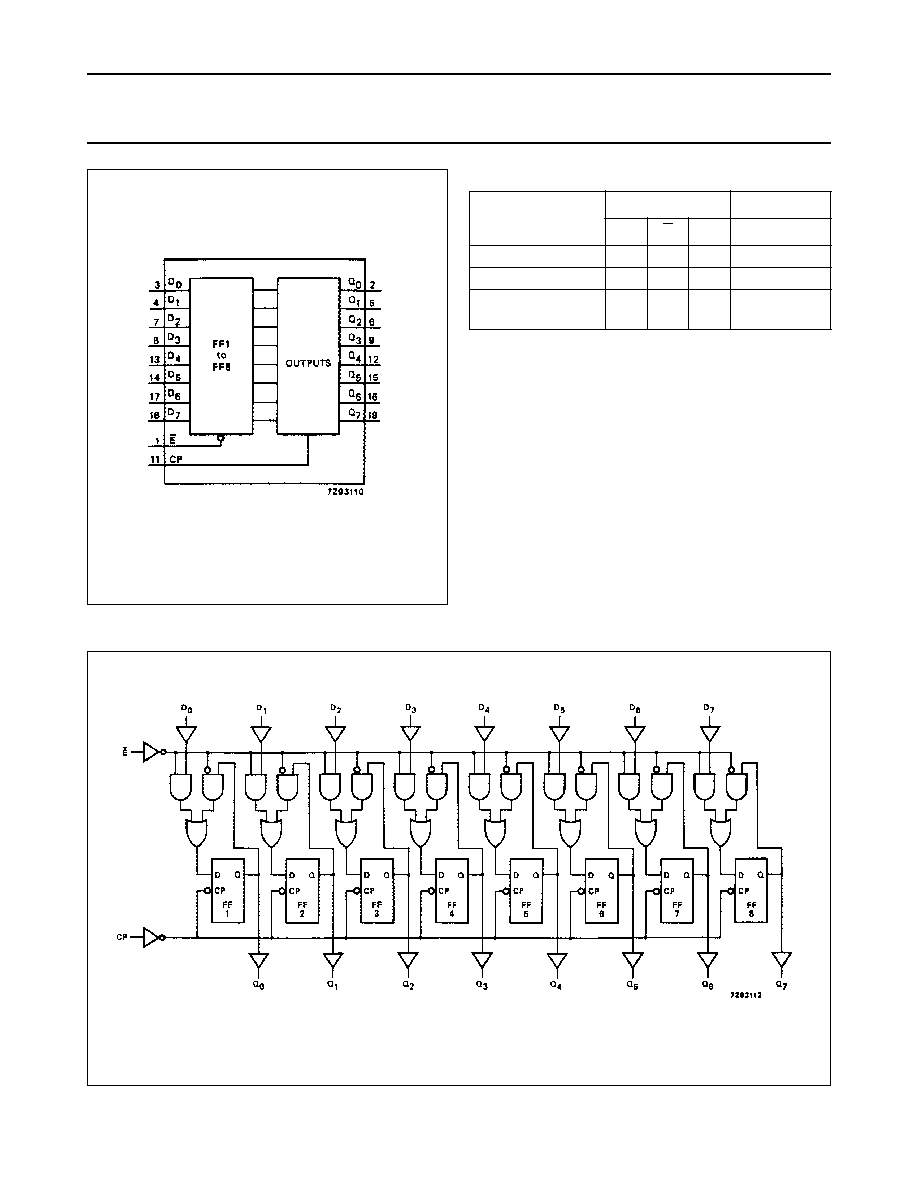

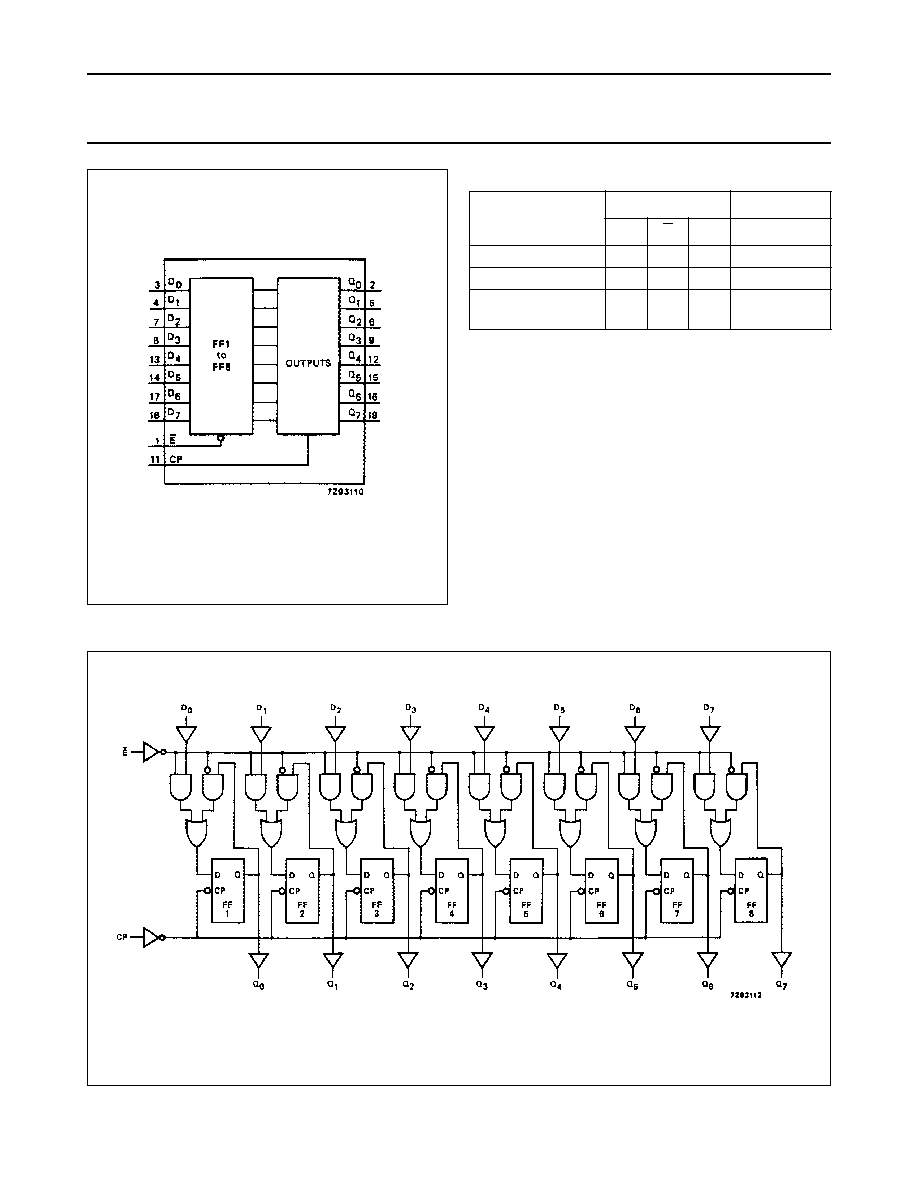

Fig.4 Functional diagram.

FUNCTION TABLE

Notes

1. H = HIGH voltage level

h = HIGH voltage level one set-up time

prior to the LOW-to-HIGH CP transition

L = LOW voltage level

I

= LOW voltage level one set-up time

prior to the LOW-to-HIGH CP transition

= LOW-to-HIGH CP transition

X = don't care

OPERATING

MODES

INPUTS

OUTPUTS

CP

E

D

n

Q

n

load "1"

l

h

H

load "0"

l

l

L

hold (do nothing)

X

h

H

X

X

no change

no change

Fig.5 Logic diagram.

December 1990

5

Philips Semiconductors

Product specification

Octal D-type flip-flop with data enable;

positive-edge trigger

74HC/HCT377

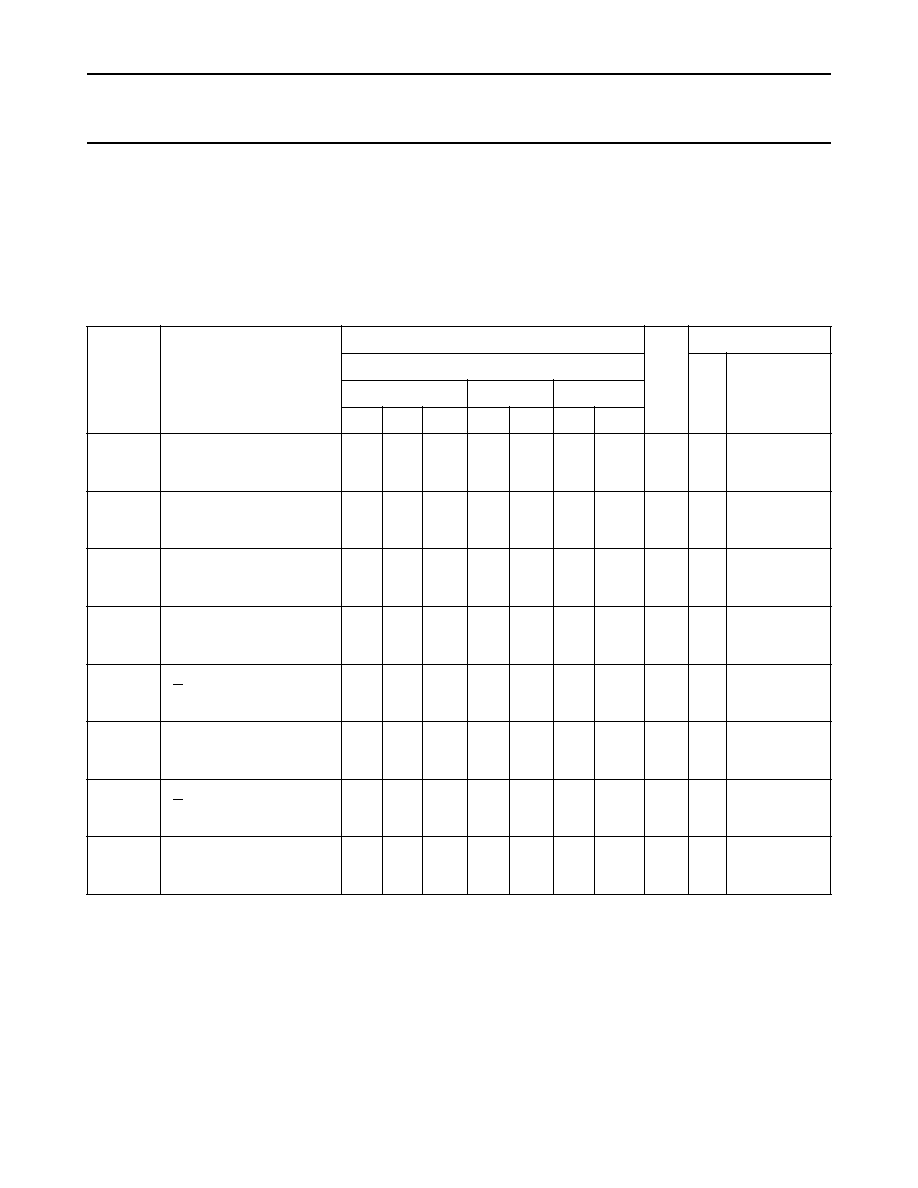

DC CHARACTERISTICS FOR 74HC

For the DC characteristics see

"74HC/HCT/HCU/HCMOS Logic Family Specifications"

.

Output capability: standard

I

CC

category: MSI

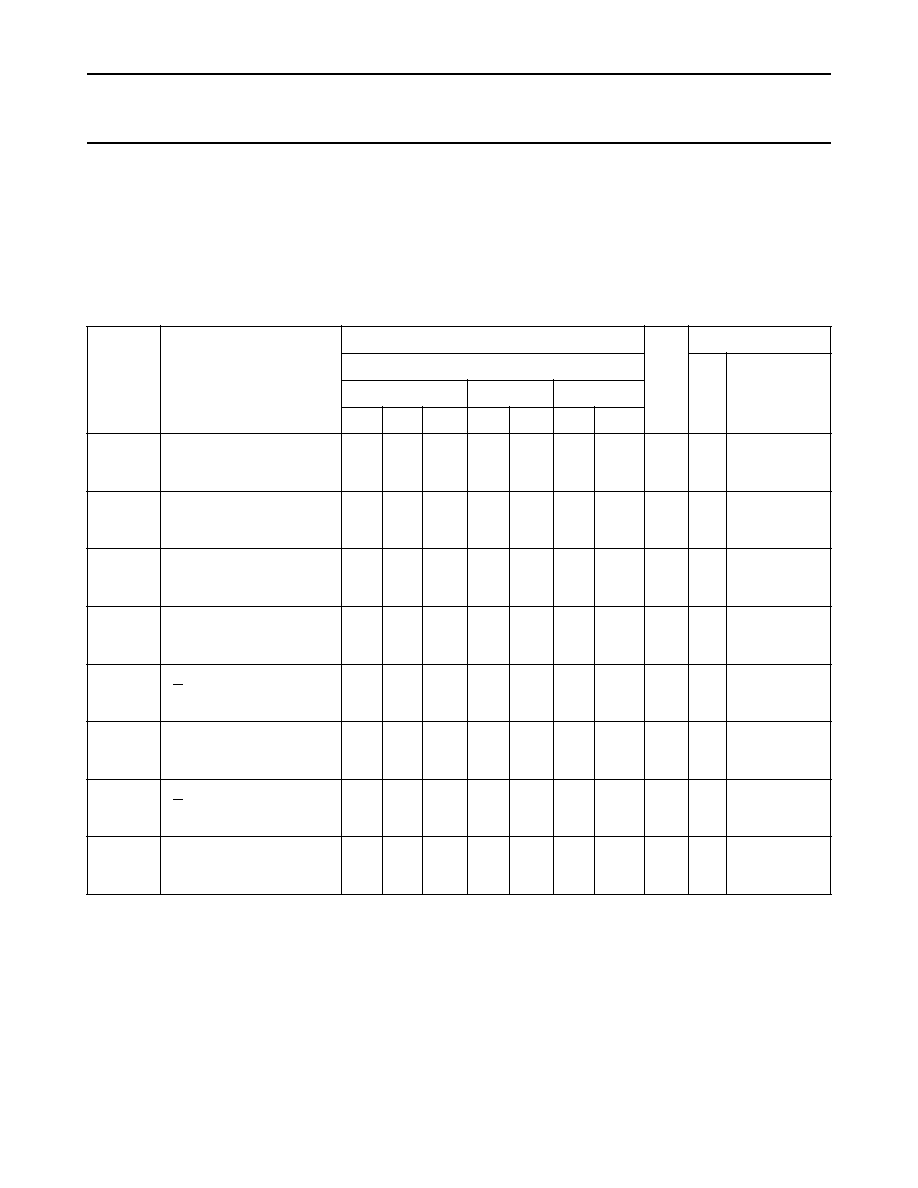

AC CHARACTERISTICS FOR 74HC

GND = 0 V; t

r

= t

f

= 6 ns; C

L

= 50 pF

SYMBOL

PARAMETER

T

amb

(

∞

C)

UNIT

TEST CONDITIONS

74HC

V

CC

(V)

WAVEFORMS

+

25

-

40 to

+

85

-

40 to

+

125

min.

typ.

max. min. max. min.

max.

t

PHL

/ t

PLH

propagation delay

CP to Q

n

44

16

13

160

32

27

200

40

34

240

48

41

ns

2.0

4.5

6.0

Fig.6

t

THL

/ t

TLH

output transition time

19

7

6

75

15

13

95

19

16

110

22

19

ns

2.0

4.5

6.0

Fig.6

t

W

clock pulse width

HIGH or LOW

80

16

14

14

5

4

100

20

17

120

24

20

ns

2.0

4.5

6.0

Fig.6

t

su

set-up time

D

n

to CP

60

12

10

14

5

4

75

15

13

90

18

15

ns

2.0

4.5

6.0

Fig.7

t

su

set-up time

E to CP

60

12

10

6

2

2

75

15

13

90

18

15

ns

2.0

4.5

6.0

Fig.7

t

h

hold time

D

n

to CP

3

3

3

-

8

-

3

-

2

3

3

3

3

3

3

ns

2.0

4.5

6.0

Fig.7

t

h

hold time

E to CP

4

4

4

-

3

-

1

-

1

4

4

4

4

4

4

ns

2.0

4.5

6.0

Fig.7

f

max

maximum clock pulse

frequency

6

30

35

23

70

83

5

24

28

4

20

24

MHz

2.0

4.5

6.0

Fig.6