DATA SHEET

Product specification

File under Integrated Circuits, IC04

January 1995

INTEGRATED CIRCUITS

HEF40192B

MSI

4-bit up/down decade counter

For a complete data sheet, please also download:

·

The IC04 LOCMOS HE4000B Logic

Family Specifications HEF, HEC

·

The IC04 LOCMOS HE4000B Logic

Package Outlines/Information HEF, HEC

January 1995

2

Philips Semiconductors

Product specification

4-bit up/down decade counter

HEF40192B

MSI

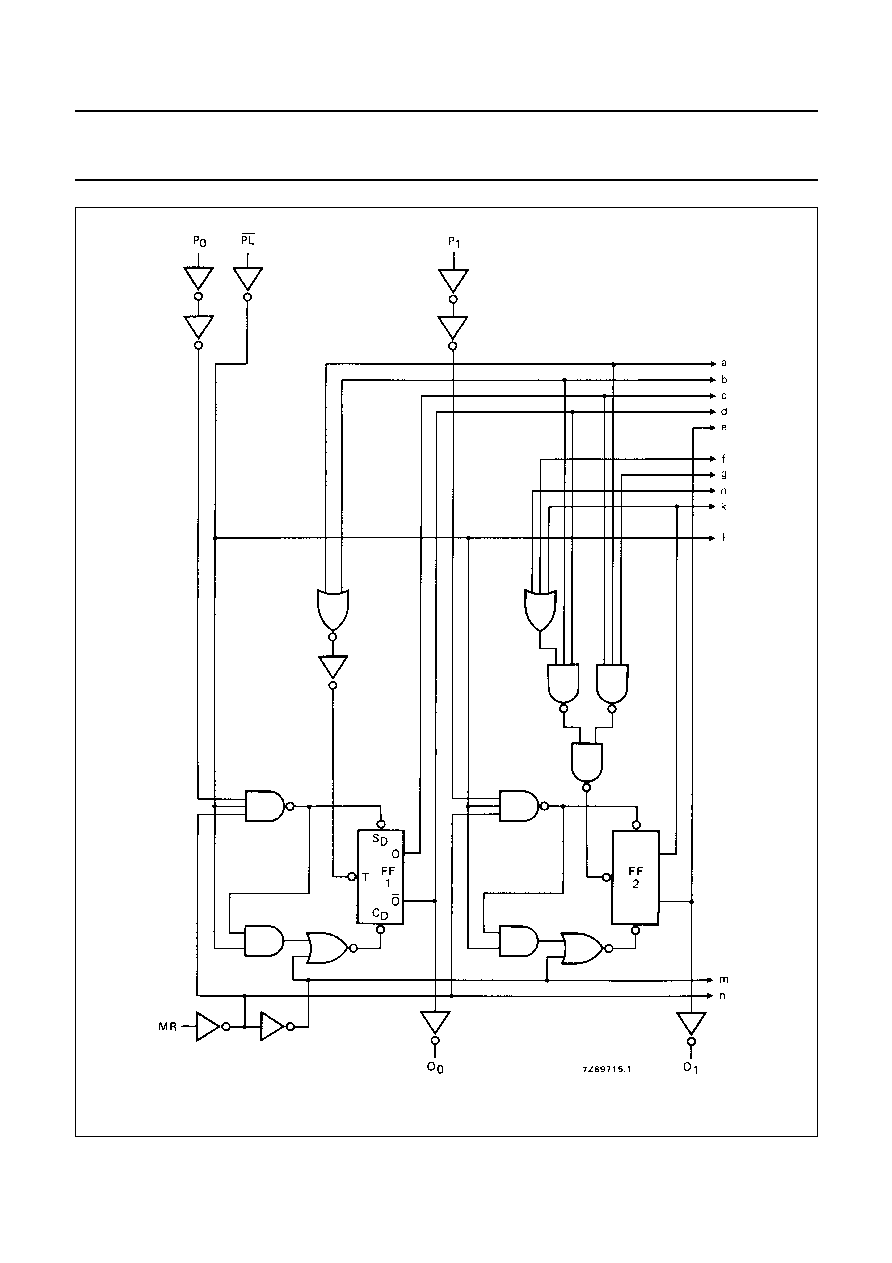

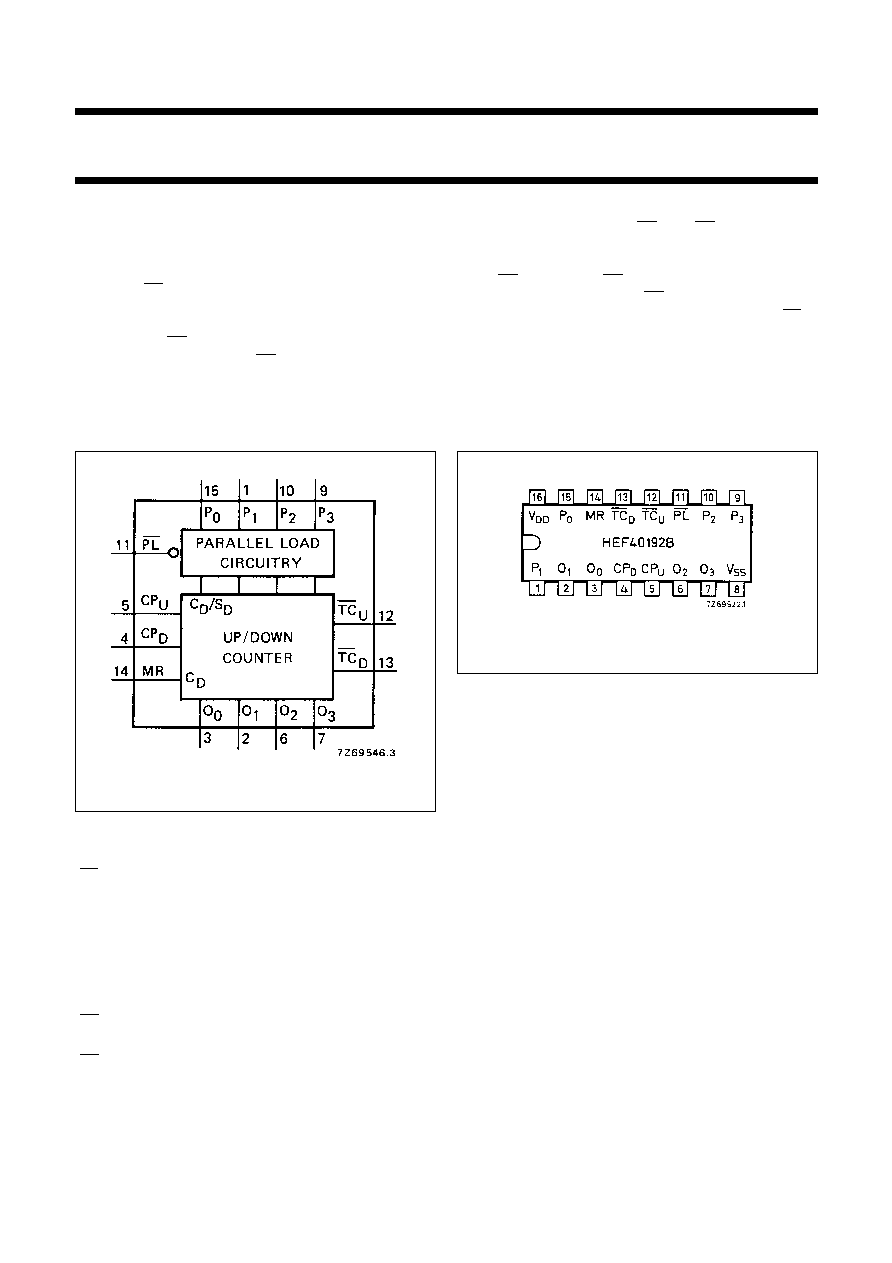

DESCRIPTION

The HEF40192B is a 4-bit synchronous up/down decade

counter. The counter has a count-up clock input (CP

U

), a

count-down clock input (CP

D

), an asynchronous parallel

load input (PL), four parallel data inputs (P

0

to P

3

), an

asynchronous master reset input (MR), four counter

outputs (O

0

to O

3

), an active LOW terminal count-up

(carry) output (TC

U

) and an active LOW terminal

count-down (borrow) output (TC

D

).

The counter outputs change state on the LOW to HIGH

transition of either clock input. However, for correct

counting, both clock inputs cannot be LOW

simultaneously. The outputs TC

U

and TC

D

are normally

HIGH. When the circuit has reached the maximum count

state of `9', the next HIGH to LOW transition of CP

U

will

cause TC

U

to go LOW. TC

U

will stay LOW until CP

U

goes

HIGH again. Likewise, output TC

D

will go LOW when the

circuit is in the zero state and CP

D

goes LOW. When PL is

LOW, the information on P

0

to P

3

is asynchronously

loaded into the counter. A HIGH on MR resets the counter

independent of all other input conditions. The counter

stages are of a static toggle type flip-flop.

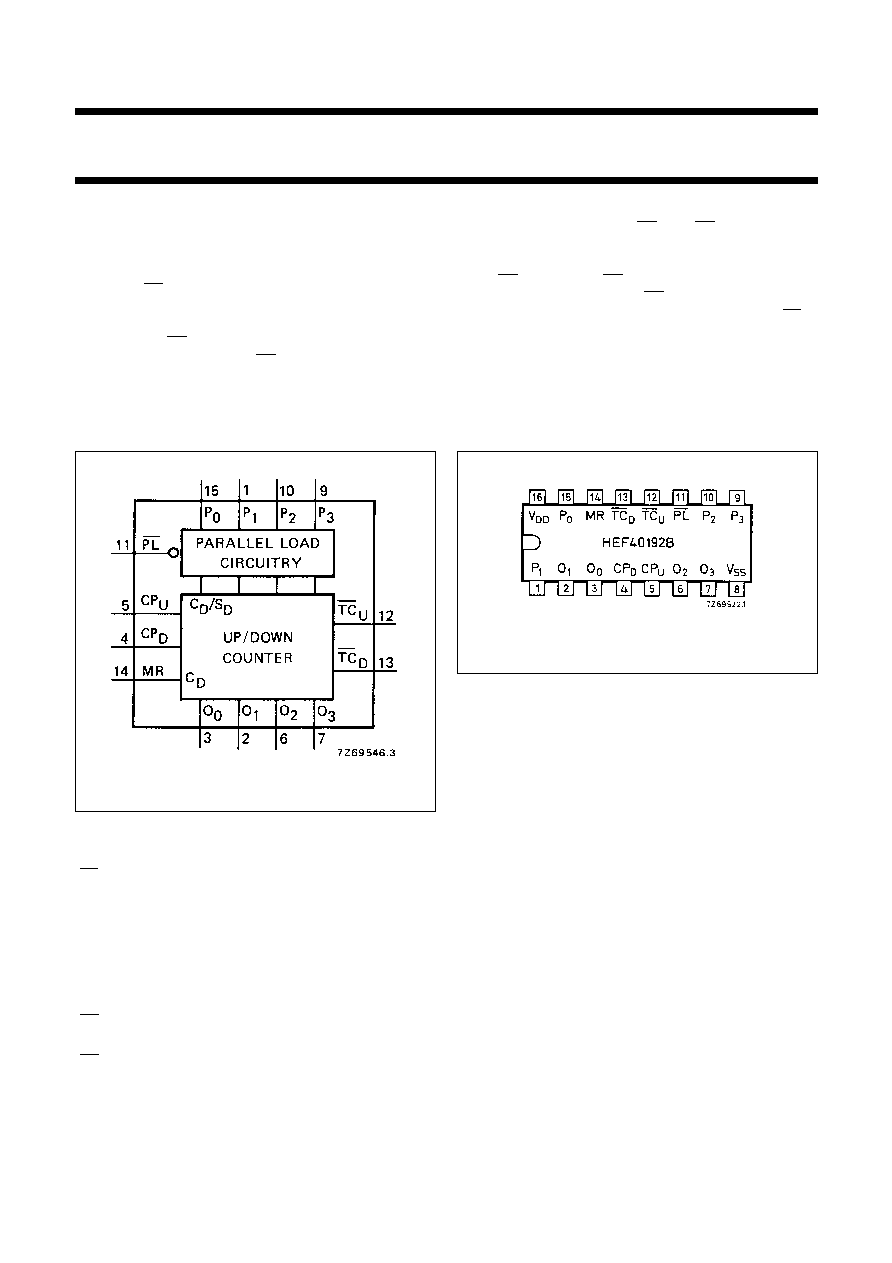

Fig.1 Functional diagram.

HEF40192BP(N): 16-lead DIL; plastic

(SOT38-1)

HEF40192BD(F):

16-lead DIL; ceramic (cerdip)

(SOT74)

HEF40192BT(D):

16-lead SO; plastic

(SOT109-1)

( ): Package Designator North America

Fig.2 Pinning diagram.

PINNING

PL

parallel load input (active LOW)

P

0

to P

3

parallel data inputs

CP

U

count-up clock pulse input (LOW to HIGH,

edge-triggered)

CP

D

count-down clock pulse input (LOW to

HIGH, edge-triggered)

MR

master reset input (asynchronous)

TC

U

buffered terminal count-up (carry) output

(active LOW)

TC

D

buffered terminal count-down

(borrow) output (active LOW)

O

0

to O

3

buffered counter outputs

FAMILY DATA, I

DD

LIMITS category MSI

See Family Specifications

January 1995

5

Philips Semiconductors

Product specification

4-bit up/down decade counter

HEF40192B

MSI

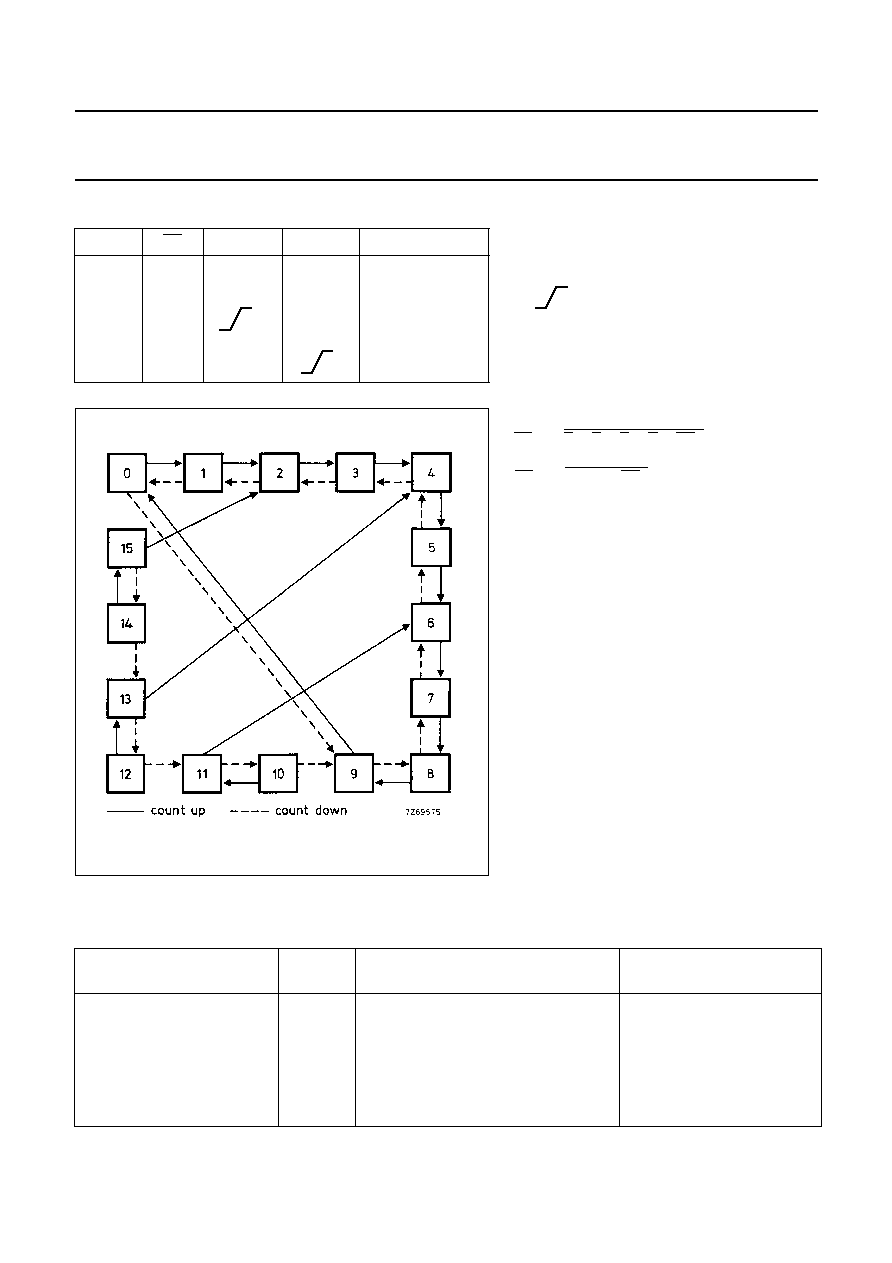

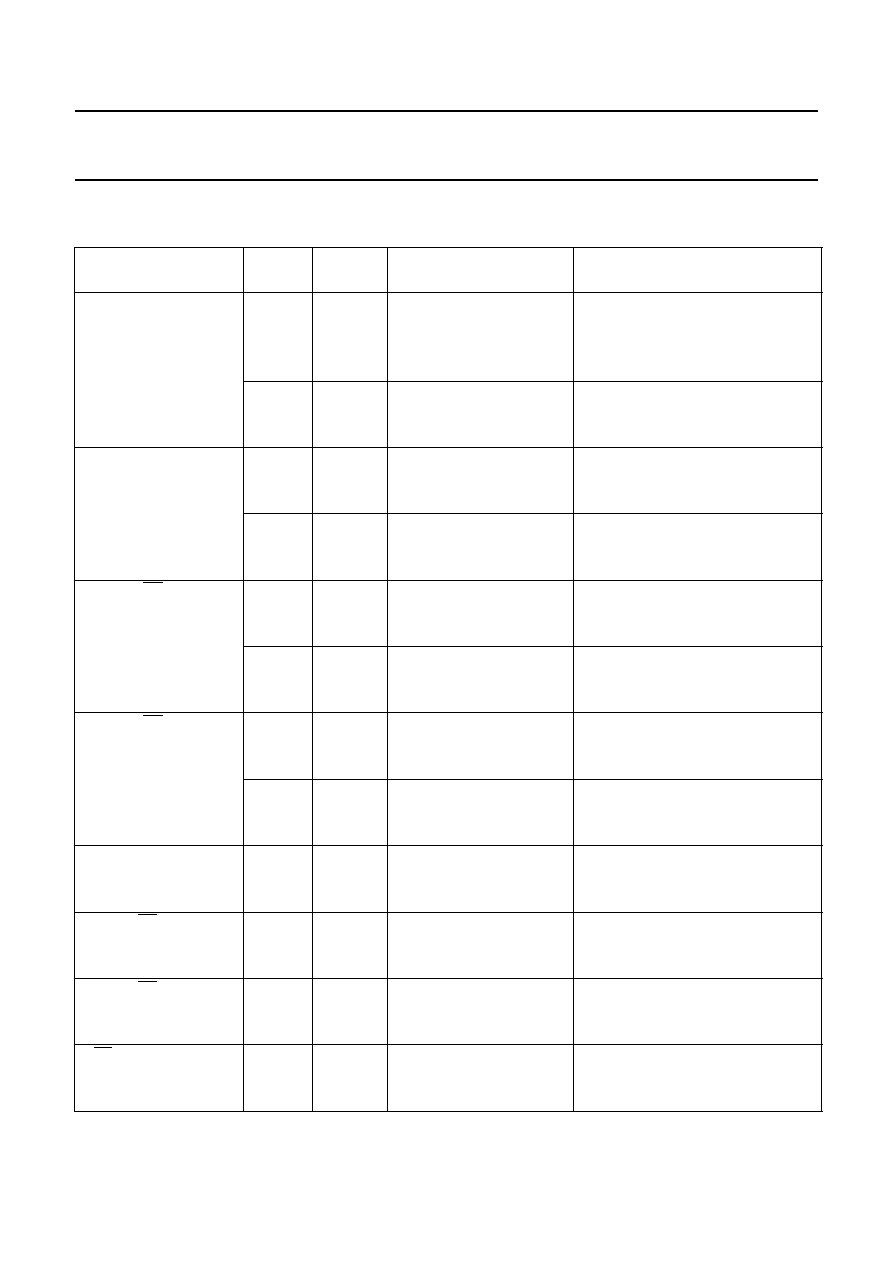

FUNCTION TABLE

MR

PL

CP

U

CP

D

MODE

H

X

X

X

reset (asyn.)

L

L

X

X

parallel load

L

H

H

count-up

L

H

H

count-down

Notes

1. H = HIGH state (the more positive voltage)

L = LOW state (the less positive voltage)

X = state is immaterial

= positive-going transition

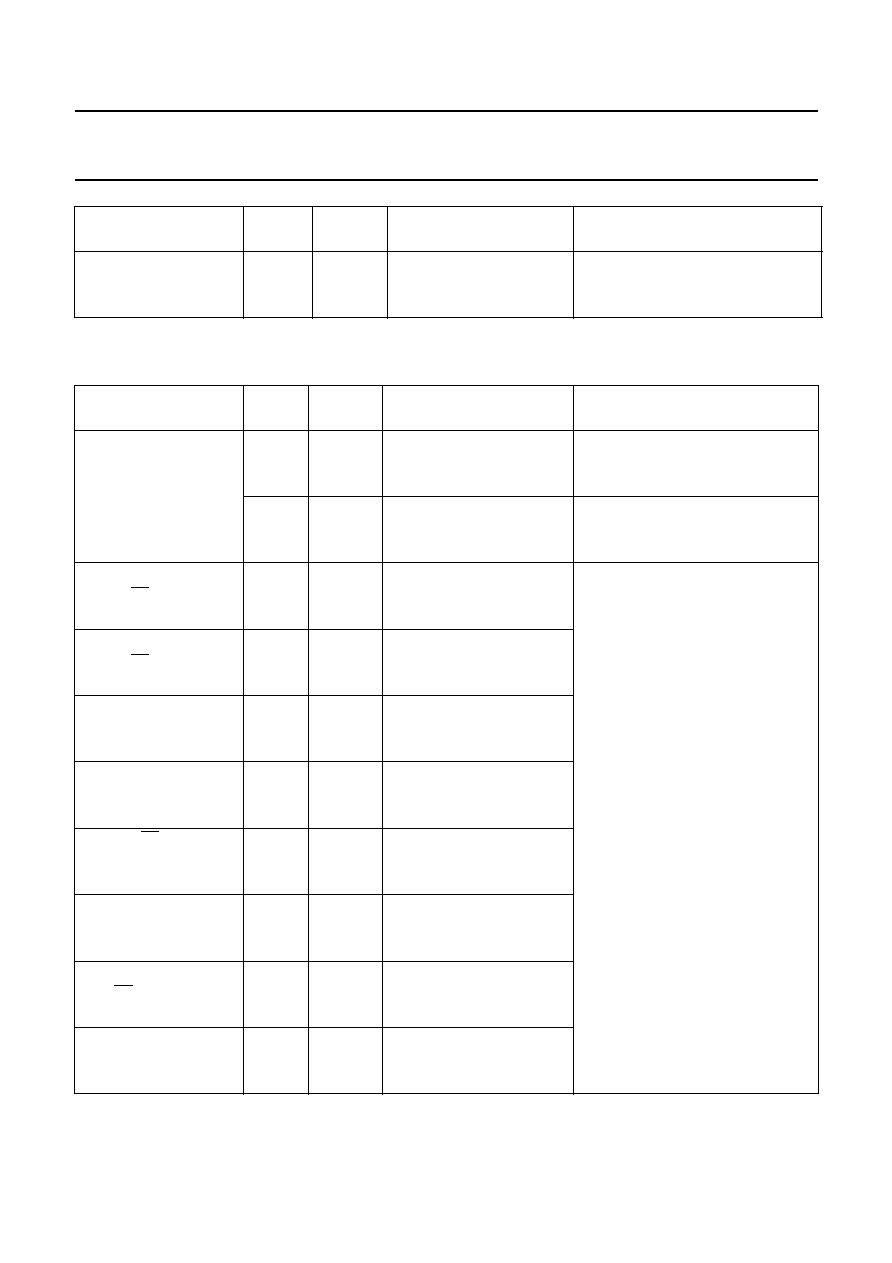

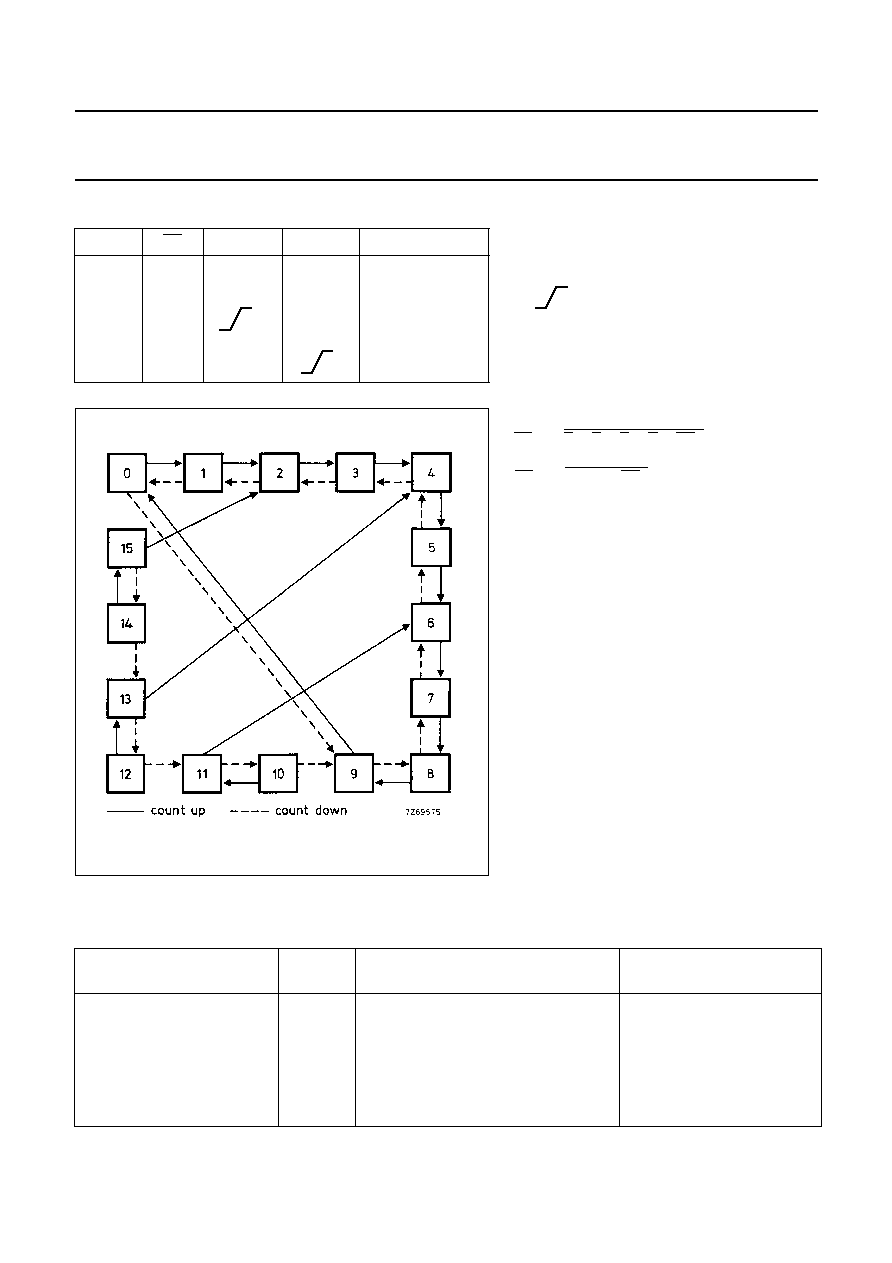

Fig.5 State diagram.

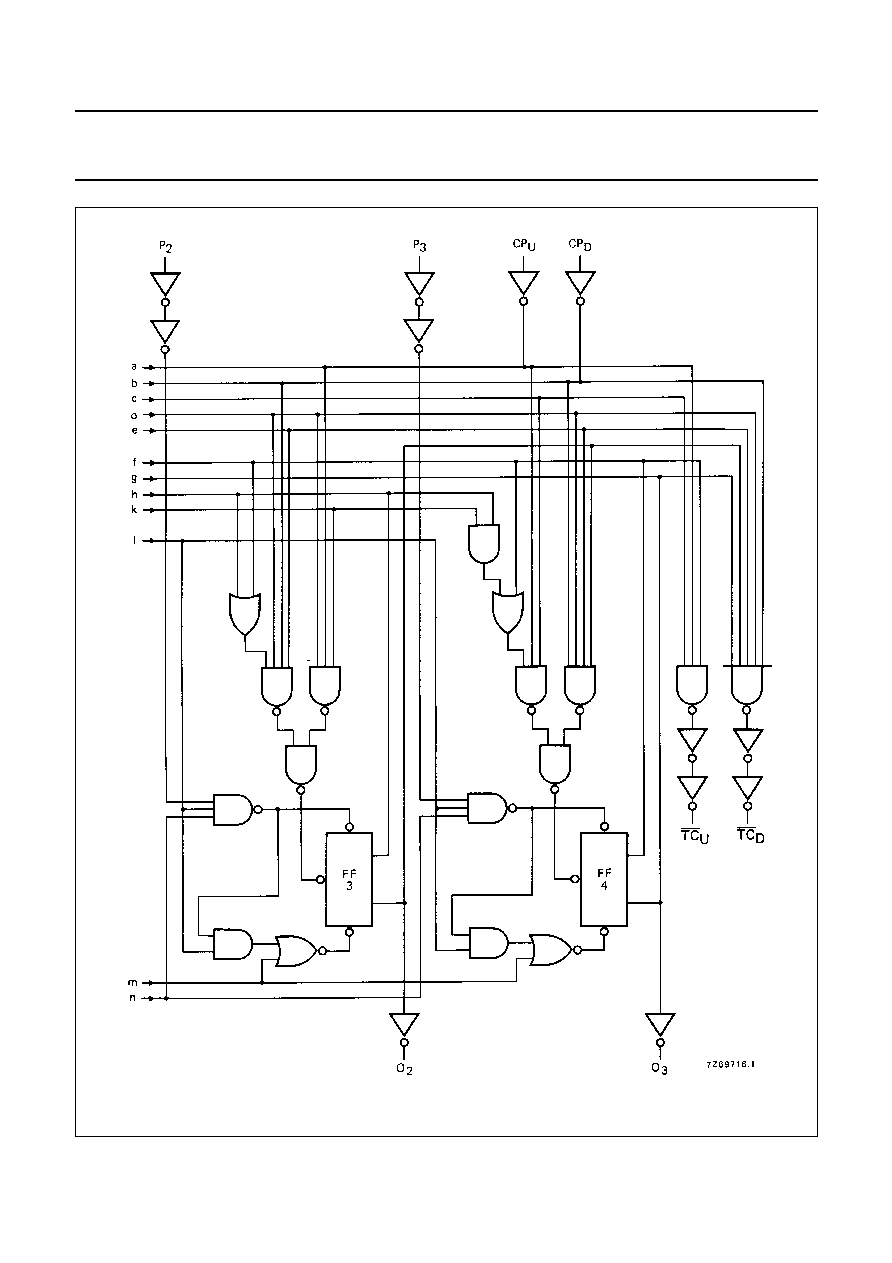

Logic equations for terminal count:

TC

U

O

0

O

3

CP

U

=

TC

D

O

0

O

1

O

2

O

3

CP

D

=

AC CHARACTERISTICS

V

SS

= 0 V; T

amb

= 25

°

C; input transition times

20 ns

V

DD

V

TYPICAL FORMULA FOR P (

µ

W)

Dynamic power

5

550 f

i

+

(f

o

C

L

)

×

V

DD

2

where

dissipation per

10

2400 f

i

+

(f

o

C

L

)

×

V

DD

2

f

i

= input freq. (MHz)

package (P)

15

6500 f

i

+

(f

o

C

L

)

×

V

DD

2

f

o

= output freq. (MHz)

C

L

= load capacitance (pF)

(f

o

C

L

) = sum of outputs

V

DD

= supply voltage (V)

January 1995

9

Philips Semiconductors

Product specification

4-bit up/down decade counter

HEF40192B

MSI

APPLICATION INFORMATION

Some examples of applications for the HEF40192B are:

·

Up/down difference counting

·

Multistage ripple counting

·

Multistage synchronous counting.

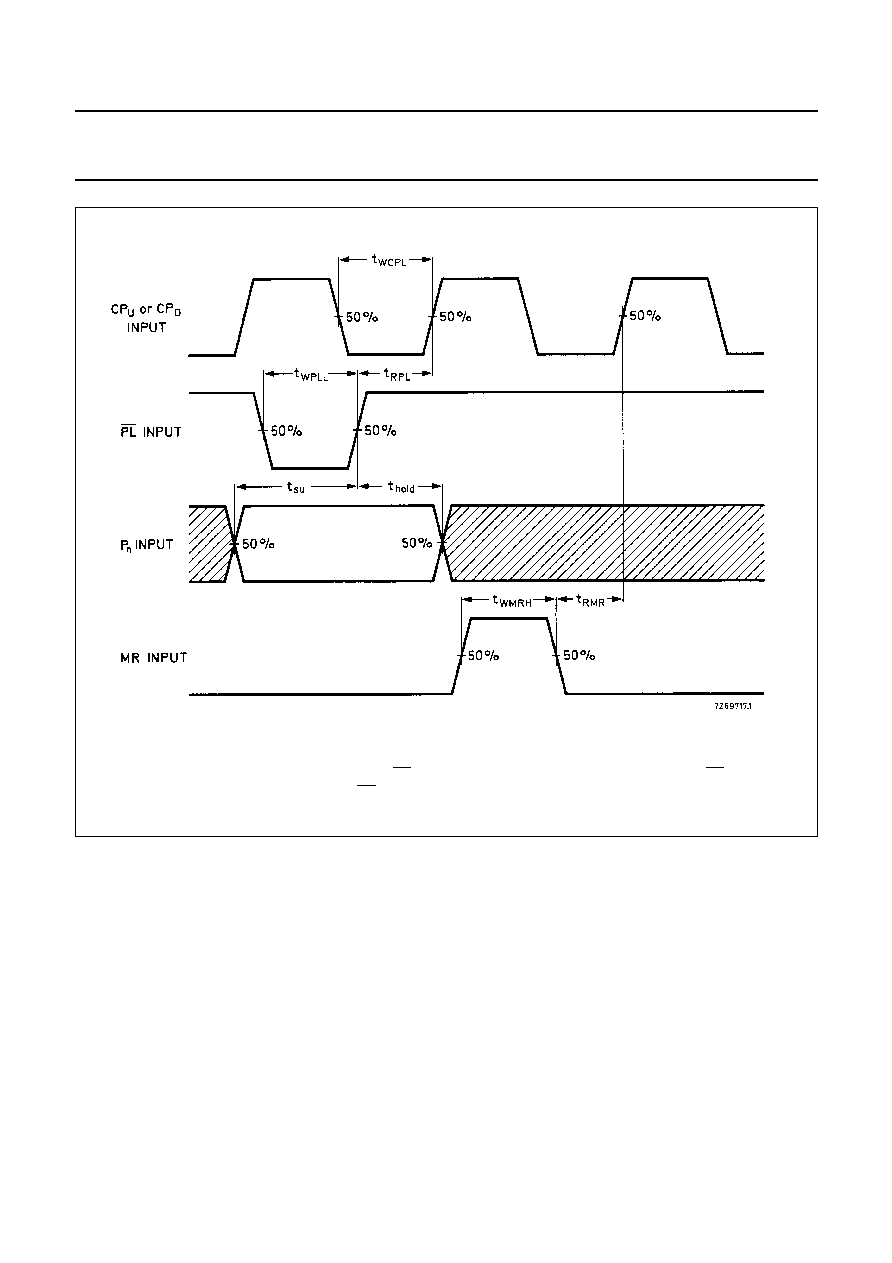

Fig.7 Timing diagram.

Fig.8 Example of cascaded HEF40192B ICs.