DATA SHEET

Product specification

File under Integrated Circuits, IC04

January 1995

INTEGRATED CIRCUITS

HEF4028B

MSI

1-of-10 decoder

For a complete data sheet, please also download:

∑

The IC04 LOCMOS HE4000B Logic

Family Specifications HEF, HEC

∑

The IC04 LOCMOS HE4000B Logic

Package Outlines/Information HEF, HEC

January 1995

2

Philips Semiconductors

Product specification

1-of-10 decoder

HEF4028B

MSI

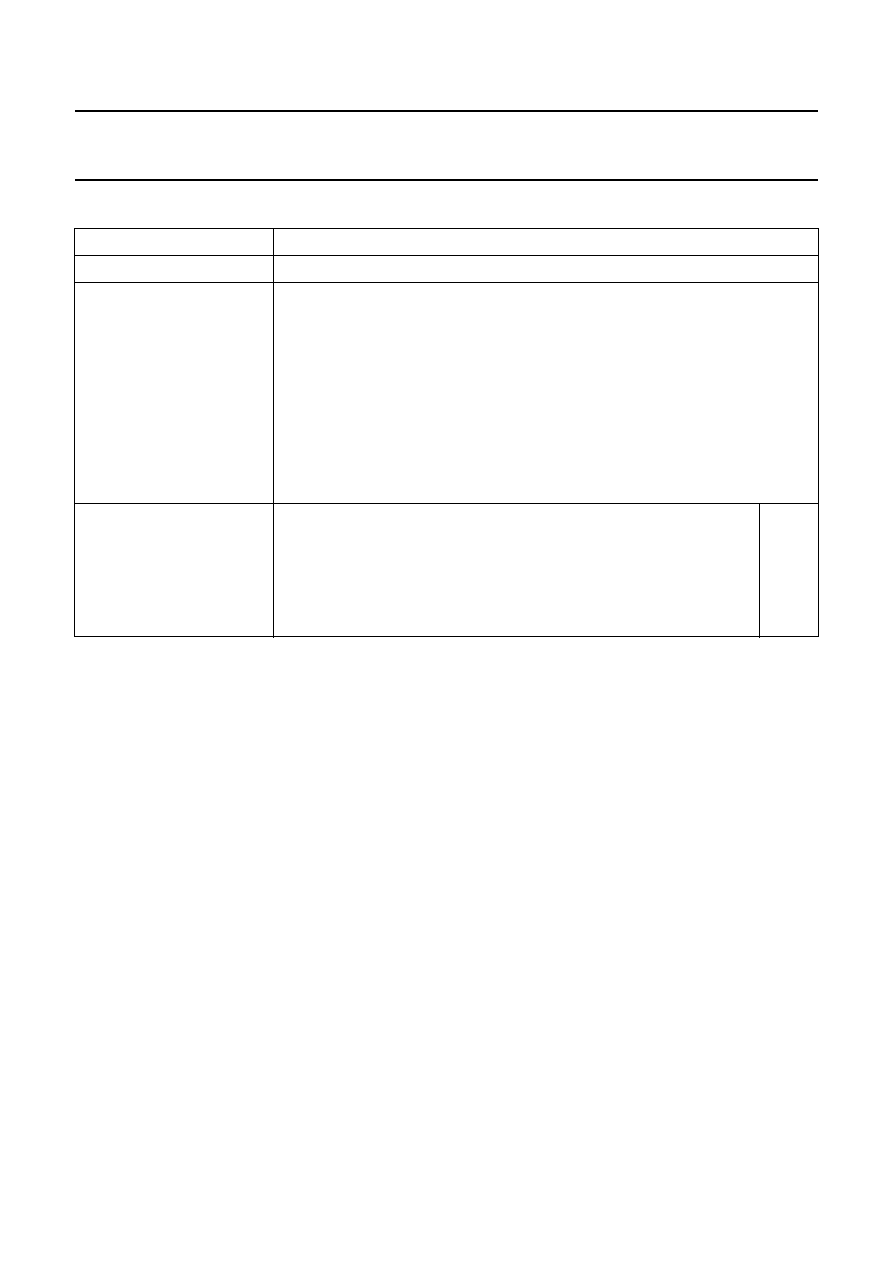

DESCRIPTION

The HEF4028B is a 4-bit BCD to 1-of-10 active HIGH

decoder. A 1-2-4-8 BCD code applied to inputs A

0

to A

3

causes the selected output to be HIGH, the other nine will

be LOW. If desired, the device may be used as a 1-of-8

decoder with enable; 3-bit octal inputs are applied to inputs

A

0

, A

1

and A

2

selecting an output O

0

to O

7

. Input A

3

then

becomes an active LOW enable, forcing the selected

output LOW when A

3

is HIGH. The HEF4028B may also

be used as an 8-output (O

0

to O

7

) demultiplexer with A

0

to

A

2

as address inputs and A

3

as an active LOW data input.

The outputs are fully buffered for best performance.

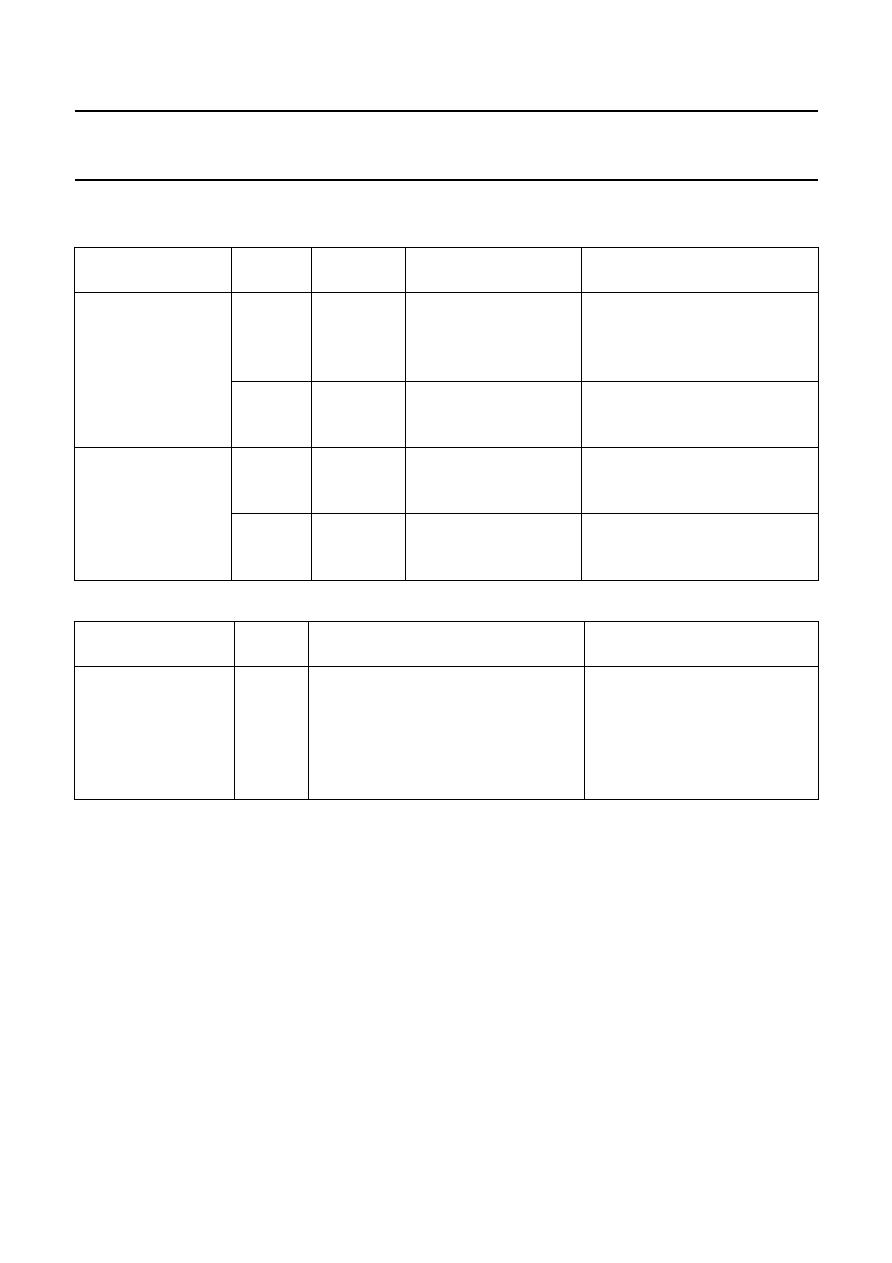

Fig.1 Functional diagram.

Fig.2 Pinning diagram.

PINNING

FAMILY DATA, I

DD

LIMITS category MSI

See Family Specifications

HEF4028BP(N):

16-lead DIL; plastic

(SOT38-1)

HEF4028BD(F):

16-lead DIL; ceramic (cerdip)

(SOT74)

HEF4028BT(D):

16-lead SO; plastic

(SOT109-1)

( ): Package Designator North America

A

0

to A

3

address inputs, 1-2-4-8 BCD

O

0

to O

9

outputs (active HIGH)