DATA SHEET

Product specification

File under Integrated Circuits, IC04

January 1995

INTEGRATED CIRCUITS

HEF4041B

buffers

Quadruple true/complement buffer

For a complete data sheet, please also download:

∑

The IC04 LOCMOS HE4000B Logic

Family Specifications HEF, HEC

∑

The IC04 LOCMOS HE4000B Logic

Package Outlines/Information HEF, HEC

January 1995

2

Philips Semiconductors

Product specification

Quadruple true/complement buffer

HEF4041B

buffers

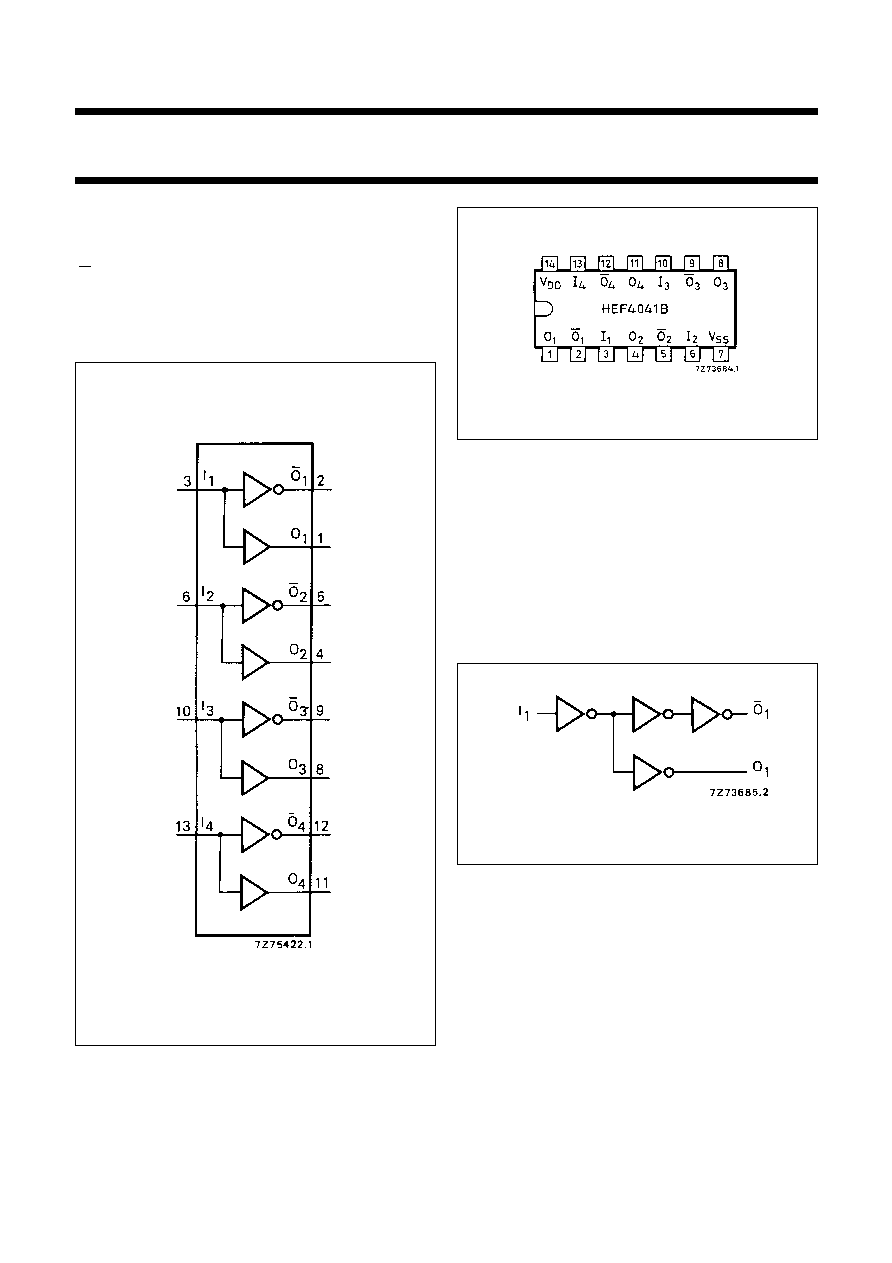

DESCRIPTION

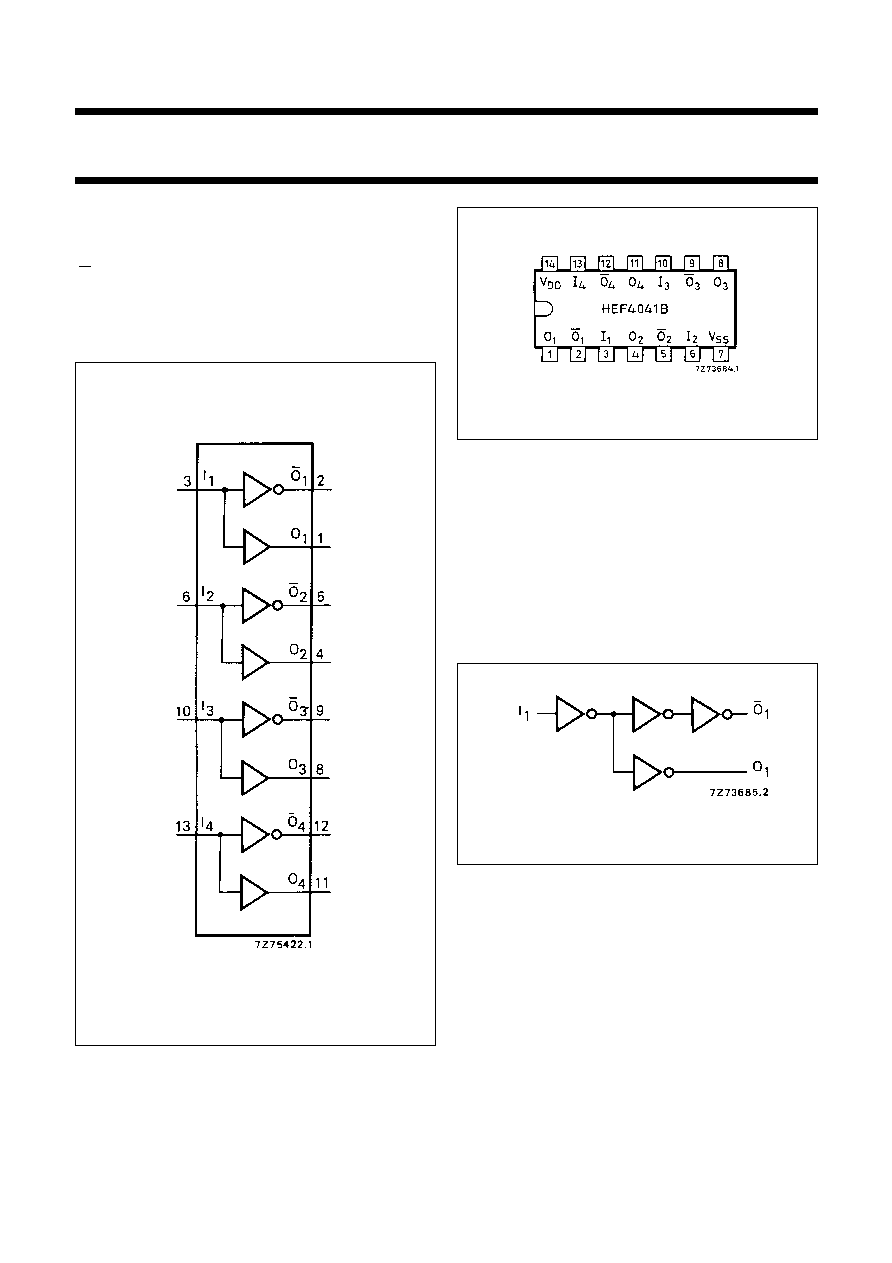

The HEF4041B is a quadruple true/complement buffer

which provides both an inverted active LOW output

(O) and a non-inverted active HIGH output (O) for each

input (I).

The buffers exhibit high current output capability suitable

for driving TTL or high capacitive loads.

Fig.1 Functional diagram.

APPLICATION INFORMATION

Some examples of applications for the HEF4041B are:

∑

LOCMOS to DTL/TTL converter

∑

High current sink and source driver

FAMILY DATA, I

DD

LIMITS category BUFFERS

See Family Specifications

HEF4041BP(N):

14-lead DIL; plastic

(SOT27-1)

HEF4041BD(F):

14-lead DIL; ceramic (cerdip)

(SOT73)

HEF4041BT(D):

14-lead SO; plastic

(SOT108-1)

( ): Package Designator North America

Fig.2 Pinning diagram.

Fig.3 Logic diagram (one buffer).