DATA SHEET

Product specification

File under Integrated Circuits, IC04

January 1995

INTEGRATED CIRCUITS

HEF4515B

MSI

1-of-16 decoder/demultiplexer with

input latches

For a complete data sheet, please also download:

·

The IC04 LOCMOS HE4000B Logic

Family Specifications HEF, HEC

·

The IC04 LOCMOS HE4000B Logic

Package Outlines/Information HEF, HEC

January 1995

2

Philips Semiconductors

Product specification

1-of-16 decoder/demultiplexer with input latches

HEF4515B

MSI

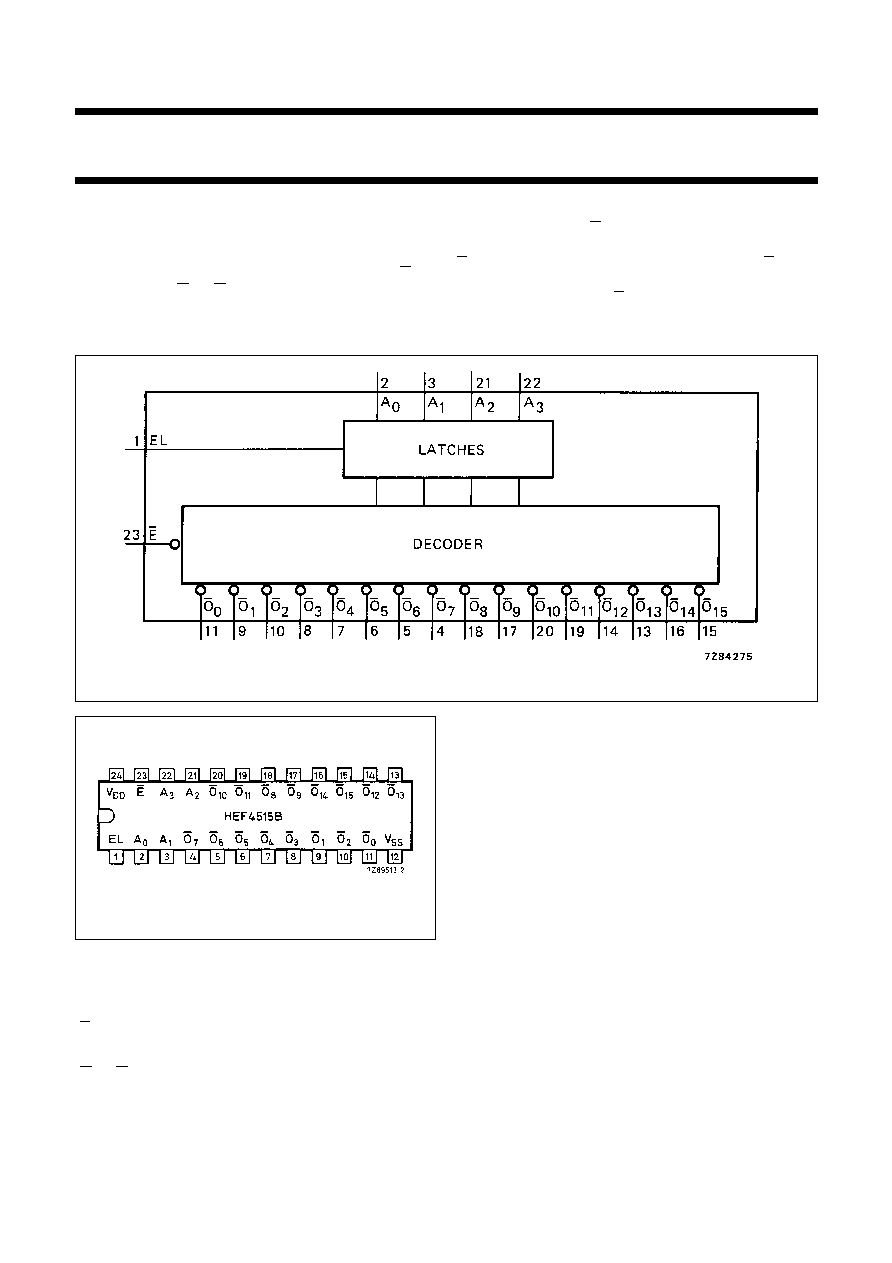

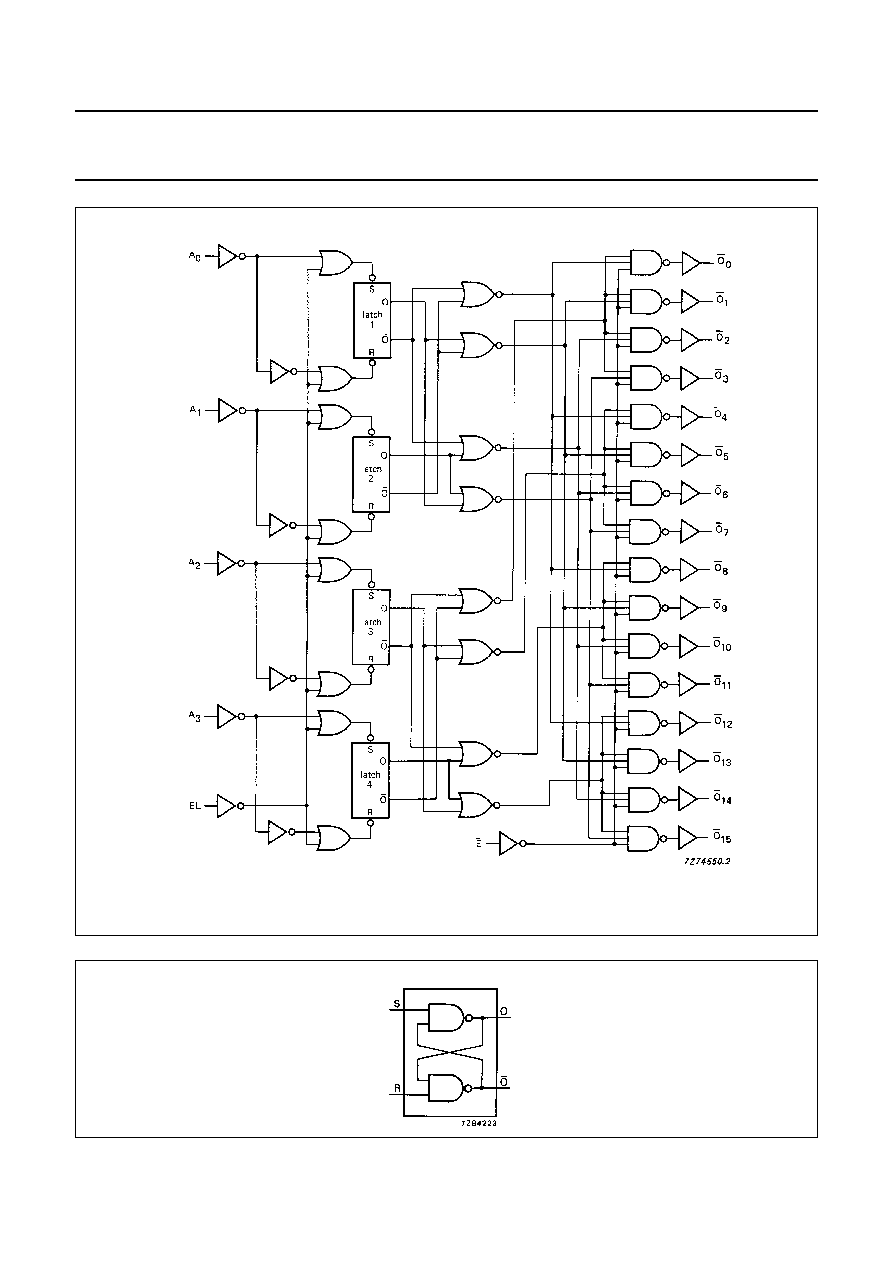

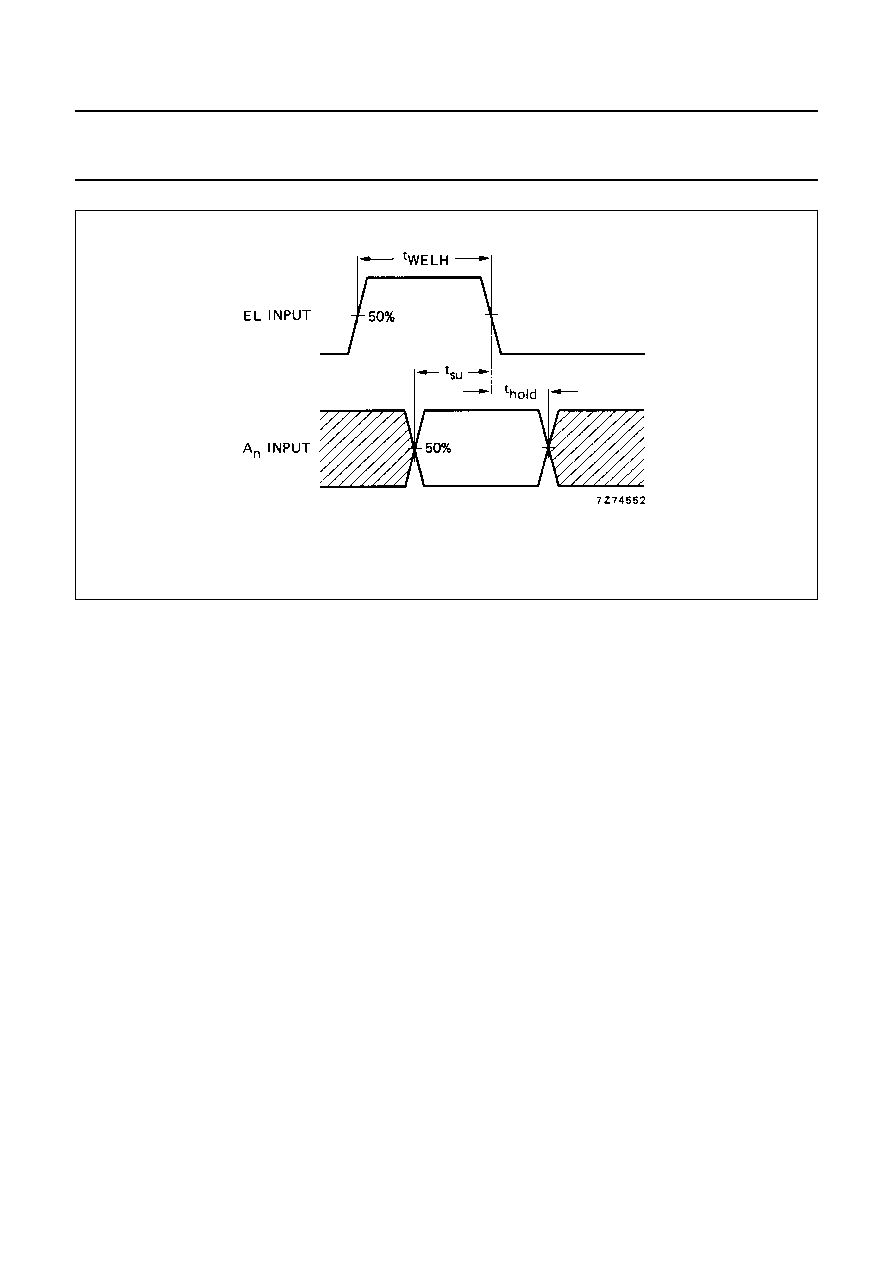

DESCRIPTION

The HEF4515B is a 1-of-16 decoder/demultiplexer, having

four binary weighted address inputs (A

0

to A

3

), a latch

enable input (EL), and an active LOW enable input (E).

The 16 outputs (O

0

to O

15

) are mutually exclusive active

LOW. When EL is HIGH, the selected output is determined

by the data on A

n

. When EL goes LOW, the last data

present at A

n

are stored in the latches and the outputs

remain stable. When E is LOW, the selected output,

determined by the contents of the latch, is LOW. At

E HIGH, all outputs are HIGH. The enable input (E) does

not affect the state of the latch. When the HEF4515B is

used as a demultiplexer, E is the data input and A

0

to

A

3

are the address inputs.

Fig.1 Functional diagram.

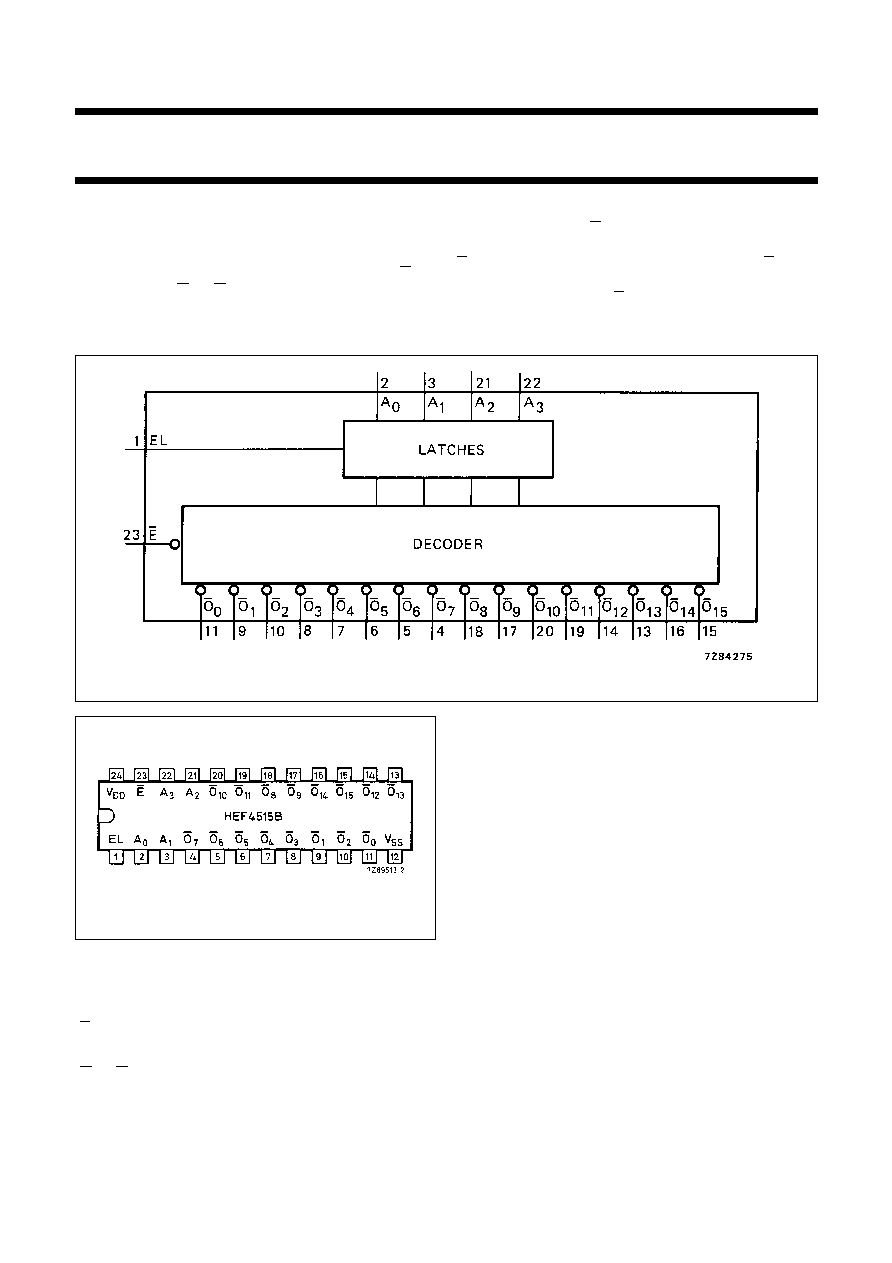

PINNING

A

0

to A

3

address inputs

E

enable input (active LOW)

EL

latch enable input

O

0

to O

15

outputs (active LOW)

Fig.2 Pinning diagram.

APPLICATION INFORMATION

Some examples of applications for the HEF4515B are:

·

Digital multiplexing.

·

Address decoding.

·

Hexadecimal/BCD decoding.

FAMILY DATA, I

DD

LIMITS category MSI

See Family Specifications

HEF4515BP(N):

24-lead DIL; plastic

(SOT101-1)

HEF4515BD(F):

24-lead DIL; ceramic (cerdip)

(SOT94)

HEF4515BT(D):

24-lead SO; plastic

(SOT137-1)

( ): Package Designator North America

January 1995

4

Philips Semiconductors

Product specification

1-of-16 decoder/demultiplexer with input latches

HEF4515B

MSI

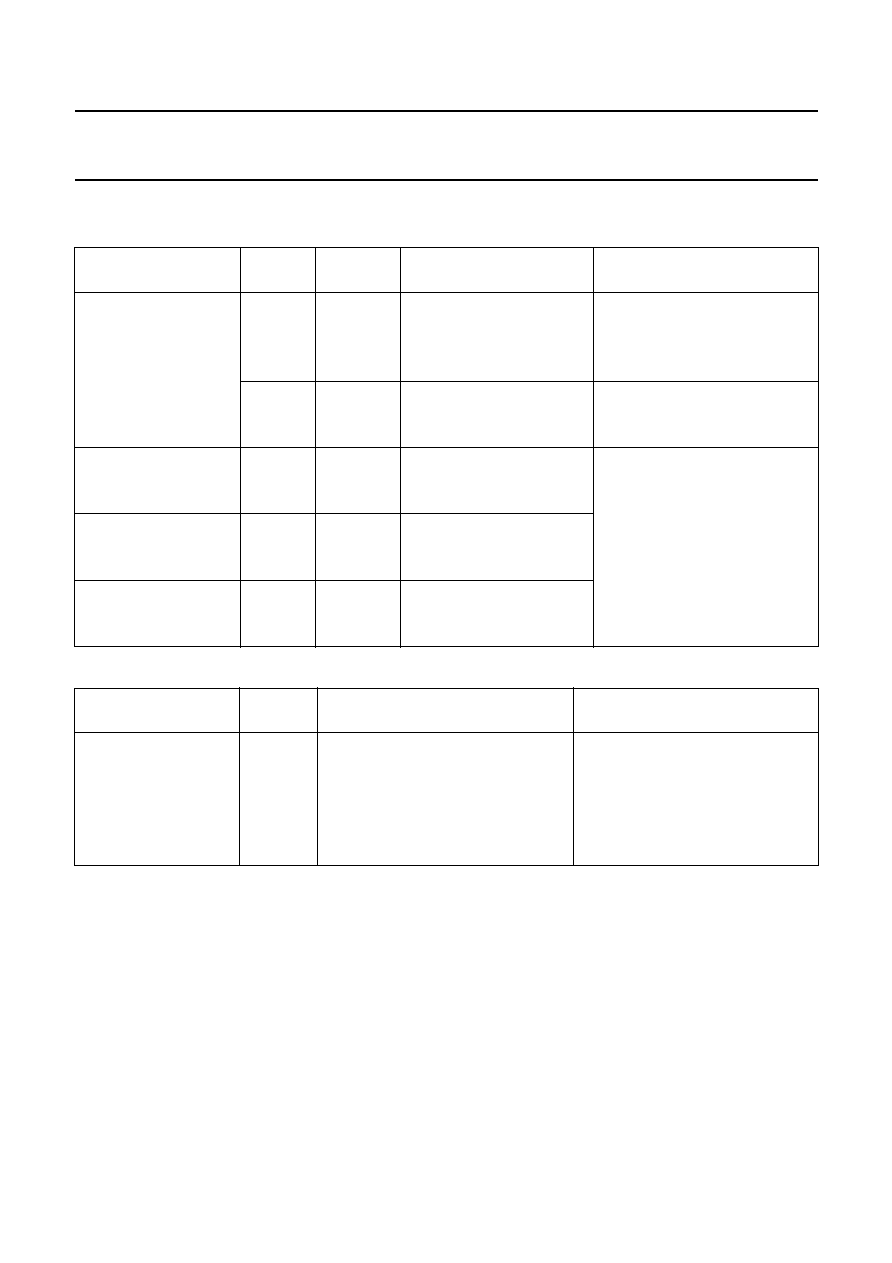

TRUTH TABLE

Notes

1. EL = HIGH; H = HIGH state (the more positive voltage)

L = LOW state (the less positive voltage); X = state is immaterial

AC CHARACTERISTICS

V

SS

= 0 V; T

amb

= 25

°

C; C

L

= 50 pF; input transition times

20 ns

INPUTS

OUTPUTS

E

A

0

A

1

A

2

A

3

O

0

O

1

O

2

O

3

O

4

O

5

O

6

O

7

O

8

O

9

O

10

O

11

O

12

O

13

O

14

O

15

H

X

X

X

X

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

L

L

L

L

L

L

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

L

H

L

L

L

H

L

H

H

H

H

H

H

H

H

H

H

H

H

H

H

L

L

H

L

L

H

H

L

H

H

H

H

H

H

H

H

H

H

H

H

H

L

H

H

L

L

H

H

H

L

H

H

H

H

H

H

H

H

H

H

H

H

L

L

L

H

L

H

H

H

H

L

H

H

H

H

H

H

H

H

H

H

H

L

H

L

H

L

H

H

H

H

H

L

H

H

H

H

H

H

H

H

H

H

L

L

H

H

L

H

H

H

H

H

H

L

H

H

H

H

H

H

H

H

H

L

H

H

H

L

H

H

H

H

H

H

H

L

H

H

H

H

H

H

H

H

L

L

L

L

H

H

H

H

H

H

H

H

H

L

H

H

H

H

H

H

H

L

H

L

L

H

H

H

H

H

H

H

H

H

H

L

H

H

H

H

H

H

L

L

H

L

H

H

H

H

H

H

H

H

H

H

H

L

H

H

H

H

H

L

H

H

L

H

H

H

H

H

H

H

H

H

H

H

H

L

H

H

H

H

L

L

L

H

H

H

H

H

H

H

H

H

H

H

H

H

H

L

H

H

H

L

H

L

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

L

H

H

L

L

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

L

H

L

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

L

V

DD

V

SYMBOL

TYP.

MAX.

TYPICAL EXTRAPOLATION

FORMULA

Propagation delays

A

n

, EL

O

n

5

260

520

ns

233 ns

+

(0,55 ns/pF) C

L

HIGH to LOW

10

t

PHL

95

190

ns

84 ns

+

(0,23 ns/pF) C

L

15

65

130

ns

57 ns

+

(0,16 ns/pF) C

L

5

270

550

ns

243 ns

+

(0,55 ns/pF) C

L

LOW to HIGH

10

t

PLH

95

190

ns

84 ns

+

(0,23 ns/pF) C

L

15

65

130

ns

57 ns

+

(0,16 ns/pF) C

L

E

O

n

5

175

350

ns

148 ns

+

(0,55 ns/pF) C

L

HIGH to LOW

10

t

PHL

65

130

ns

54 ns

+

(0,23 ns/pF) C

L

15

45

90

ns

37 ns

+

(0,16 ns/pF) C

L

5

200

400

ns

173 ns

+

(0,55 ns/pF) C

L

LOW to HIGH

10

t

PLH

70

140

ns

59 ns

+

(0,23 ns/pF) C

L

15

50

100

ns

42 ns

+

(0,16 ns/pF) C

L

January 1995

6

Philips Semiconductors

Product specification

1-of-16 decoder/demultiplexer with input latches

HEF4515B

MSI

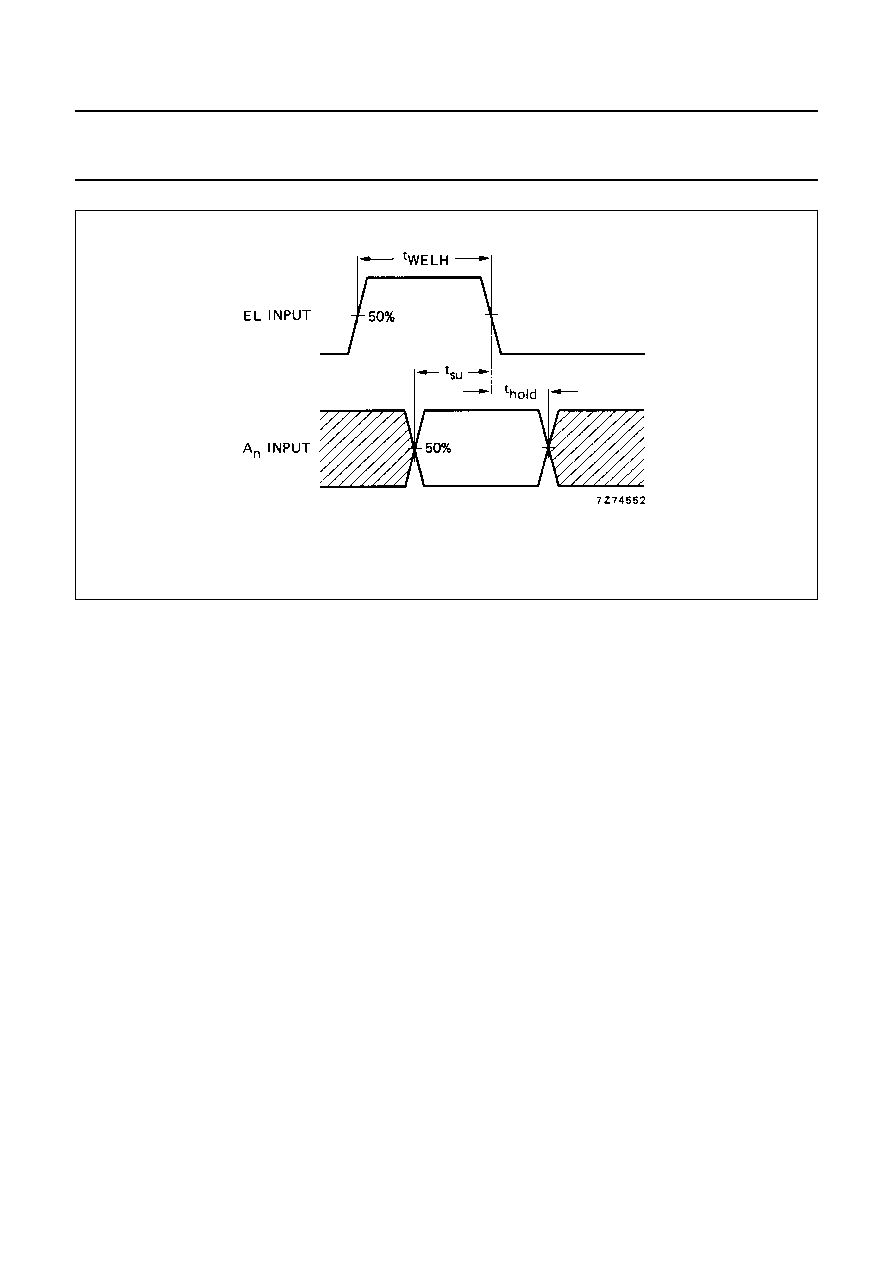

Fig.5

Waveforms showing minimum pulse width for EL, set-up and hold times for A

n

to EL. Set-up and hold

times are shown as positive values but may be specified as negative values.