| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: N74F323N | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Document Outline

- FEATURES

- DESCRIPTION

- PIN CONFIGURATION

- ORDERING INFORMATION

- INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

- LOGIC SYMBOL

- LOGIC SYMBOL (IEEE/IEC)

- FUNCTION TABLE

- LOGIC DIAGRAM

- ABSOLUTE MAXIMUM RATINGS

- RECOMMENDED OPERATING CONDITIONS

- DC ELECTRICAL CHARACTERISTICS

- AC ELECTRICAL CHARACTERISTICS

- AC SETUP REQUIREMENTS

- AC WAVEFORMS

- TEST CIRCUIT AND WAVEFORM

Philips Semiconductors

Product specification

74F323

8-bit universal shift/storage register with synchronous

reset and common I/O pins (3-State)

1

1990 Mar 01

853-0367 98987

FEATURES

∑

Common parallel I/O for reduced pin count

∑

Additional serial inputs and outputs for expansion

∑

Four operating modes: Shift left, shift right, load, and store

∑

3-State outputs for bus-oriented applications

DESCRIPTION

The 74F323 is an 8-bit universal shift/storage register with 3-State

outputs. Its function is similar to the 74F299 with the exception of

synchronous Reset. Parallel load inputs and flip-flop outputs are

multiplexed to minimize pin counts. Separate serial inputs and

outputs are provided for flip-flops Q0 and Q7 to allow easy serial

cascading. Four modes of operation are possible: Hold (store), shift

left, shift right, and parallel load.

The 74F323 contains eight edge-triggered D-type flip-flops and the

interstage logic necessary to perform synchronous reset, shift left,

shift right, parallel load, and hold operations. The type of operation is

determined by S0 and S1, as shown in the Function Table. All

flip-flop outputs are brought out through 3-State buffers to separate

I/O pins that also serve as data inputs in the parallel load mode.

Q0 and Q7 are also brought out on other pins for expansion in serial

shifting of longer words.

A Low signal on SR overrides the Select and inputs and allows the

flip-flops to be reset by the next rising edge of clock. All other state

changes are initiated by the rising edge of the clock. Inputs can

change when the clock is in either state provided only that the

recommended setup and hold times, relative to the rising edge of

clock are observed.

A High signal on either OE0 or OE1 disables the 3-State buffers and

puts the I/O pins in the high impedance state. In this condition the

shift, hold, load and reset operations can still occur. The 3-State

buffers are also disabled by High signals on both S0 and S1 in

preparation for a parallel load operation.

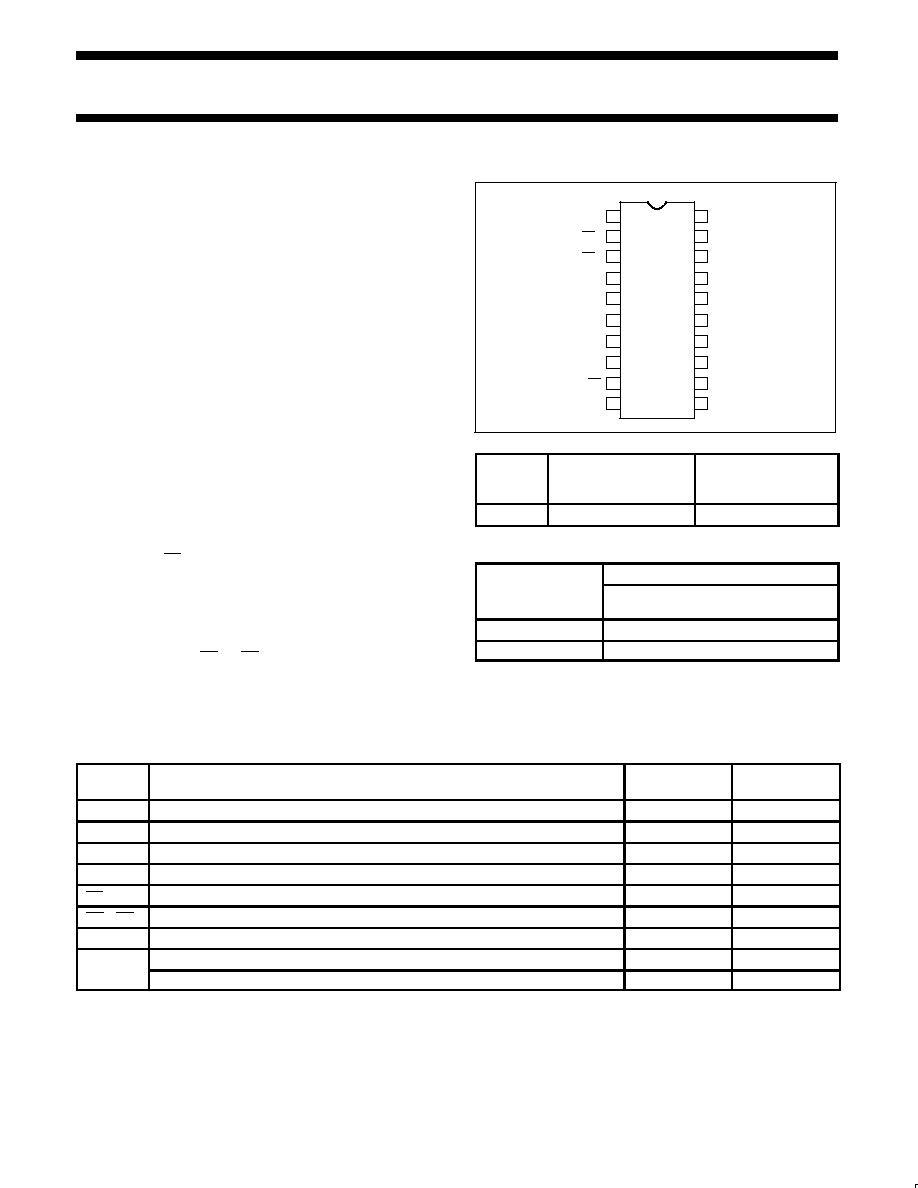

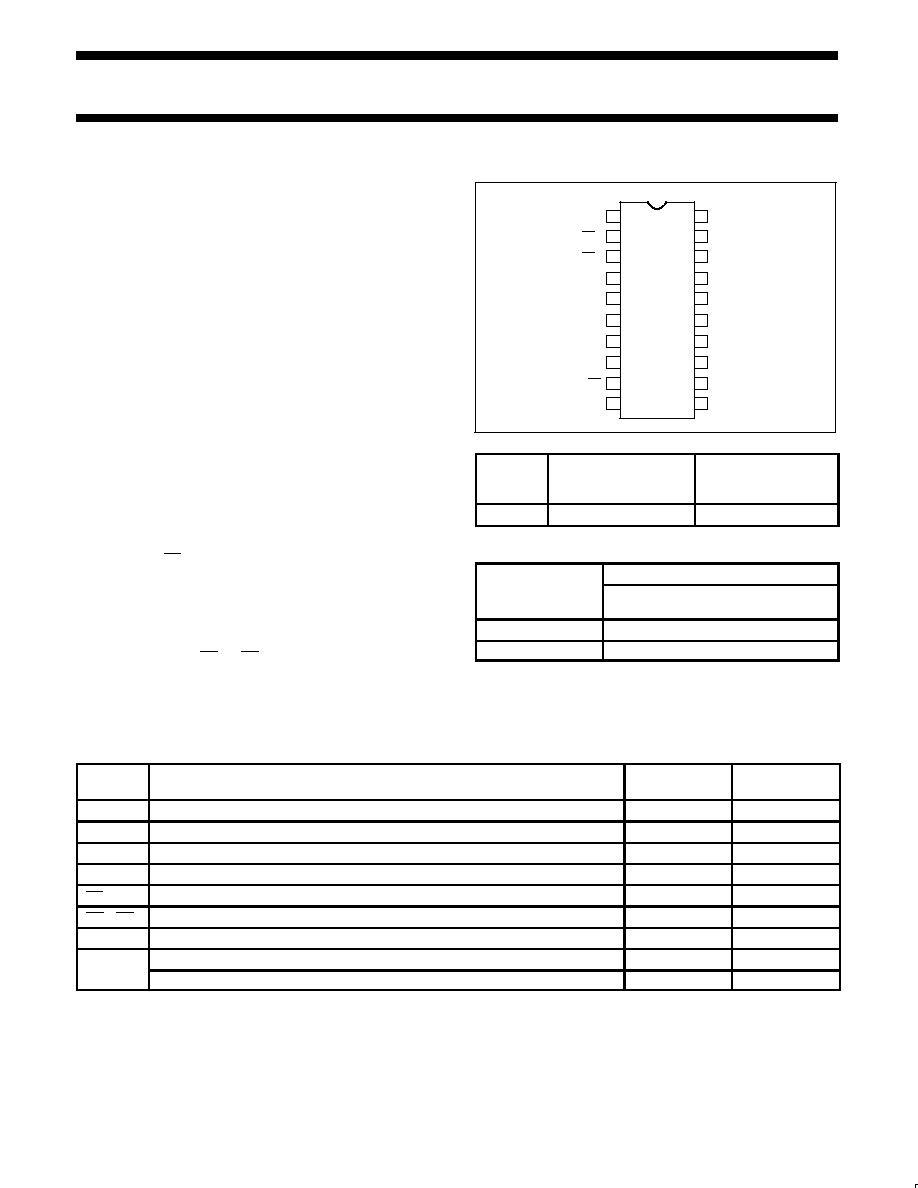

PIN CONFIGURATION

20

19

18

17

16

15

14

13

12

10

11

9

8

7

6

5

4

3

2

1

VCC

S1

DS7

Q7

I/O7

I/O5

I/O3

I/O1

DS0

S0

I/O6

I/O4

I/O2

I/O0

Q0

OE0

OE1

SR

GND

CP

SF00888

TYPE

TYPICAL f

MAX

TYPICAL

SUPPLY CURRENT

(TOTAL)

74F323

115MHz

55mA

ORDERING INFORMATION

DESCRIPTION

ORDER CODE

DESCRIPTION

COMMERCIAL RANGE

V

CC

= 5V

±

10%, T

amb

= 0

∞

C to +70

∞

C

20-pin plastic DIP

N74F323N

20-pin plastic SOL

N74F323D

INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

PINS

DESCRIPTION

74F(U.L.)

HIGH/LOW

LOAD VALUE

HIGH/LOW

DS0

Serial data input for right shift

1.0/1.0

20

µ

A/0.6mA

DS7

Serial data input for left shift

1.0/1.0

20

µ

A/0.6mA

S0, S1

Mode select inputs

1.0/2.0

20

µ

A/1.2mA

CP

Clock pulse input (Active rising edge)

1.0/1.0

20

µ

A/0.6mA

SR

Synchronous Reset input (Active Low)

1.0/1.0

20

µ

A/0.6mA

OE0, OE1

Output Enable input (Active Low)

1.0/1.0

20

µ

A/0.6mA

Q0, Q7

Serial outputs

50/33

20

µ

A/20mA

I/On

Multiplexed parallel data inputs or

3.5/1.0

70

µ

A/0.6mA

I/On

3-State parallel outputs

150/40

3.0mA/24mA

NOTE: One (1.0) FAST Unit Load (U.L.) is defined as: 20

µ

A in the High State and 0.6mA in the Low state.

Philips Semiconductors

Product specification

74F323

8-bit universal shift/storage register with synchronous

reset and common I/O pins (3-State)

1990 Mar 01

2

LOGIC SYMBOL

11

18

7

13

6

14

5

15

4

16

1

19

12

9

2

3

Q0

Q7

DS0

DS7

I/O0

I/O2

I/O4

I/O6

I/O1

I/O3

I/O5

I/O7

S0

S1

CP

OE0

OE1

SR

VCC = Pin 20

GND = Pin 10

8

17

SF00889

LOGIC SYMBOL (IEEE/IEC)

SF00890

&

3EN13

C4/1

/2

9

4R

11

7

6

14

5

15

4

3

12

19

17

8

SRG8

1, 4D

2

1

0

3

M

0

1

3, 4D

5, 13

13

3, 4D

6, 13

3, 4D

12, 13

2, 4D

16

18

Z5

Z6

Z6

Z12

FUNCTION TABLE

INPUTS

OPERATING MODE

OEn

SR

S1

S0

CP

OPERATING MODE

L

L

X

X

Synchronous Reset; Q0 - Q7 = Low

L

H

H

H

Parallel load; I/On

Qn

L

H

L

H

Shift right; DS0

Q0, Q0

Q1, etc.

L

H

H

L

Shift left; DS7

Q7, Q7

Q6, etc.

L

H

L

L

X

Hold

H

X

X

X

X

Outputs disabled (3-state)

H = High voltage level

L = Low voltage level

X = Don't care

= Low-to-High clock transition

Philips Semiconductors

Product specification

74F323

8-bit universal shift/storage register with synchronous

reset and common I/O pins (3-State)

1990 Mar 01

3

LOGIC DIAGRAM

Q

Q7

I/O7

S0

D

CP

Q

I/O6

D

CP

Q

I/O5

D

CP

Q

I/O4

D

CP

Q

I/O3

D

CP

Q

I/O2

D

CP

Q

I/O1

D

CP

Q

I/O0

D

CP

Q0

CP

DS0

S1

OE1

OE0

DS7

SF00883

18

2

3

19

1

11

12

VCC = Pin 20

GND = Pin 10

17

16

4

15

5

14

6

13

7

8

SR

9

Philips Semiconductors

Product specification

74F323

8-bit universal shift/storage register with synchronous

reset and common I/O pins (3-State)

1990 Mar 01

4

ABSOLUTE MAXIMUM RATINGS

(Operation beyond the limits set forth in this table may impair the useful life of the device. Unless otherwise noted these limits are over the

operating free-air temperature range.)

SYMBOL

PARAMETER

RATING

UNIT

V

CC

Supply voltage

≠0.5 to +7.0

V

V

IN

Input voltage

≠0.5 to +7.0

V

I

IN

Input current

≠30 to +5

mA

V

OUT

Voltage applied to output in High output state

≠0.5 to +5.5

V

I

OUT

Current applied to output in Low output state

Q0, Q7

40

mA

I

OUT

Current applied to output in Low output state

I/On

48

mA

T

amb

Operating free-air temperature range

0 to +70

∞

C

T

stg

Storage temperature

≠65 to +150

∞

C

RECOMMENDED OPERATING CONDITIONS

SYMBOL

PARAMETER

LIMITS

UNIT

MIN

NOM

MAX

V

CC

Supply voltage

4.5

5.0

5.5

V

V

IH

High-level input voltage

2.0

V

V

IL

Low-level input voltage

0.8

V

I

IK

Input clamp current

≠18

mA

I

OH

High-level output current

Q0, Q7

≠1

mA

I

OH

High-level output current

I/On

≠3

mA

I

OL

Low-level output current

Q0, Q7

20

mA

I

OL

Low-level output current

I/On

24

mA

T

amb

Operating free-air temperature range

0

70

∞

C

Philips Semiconductors

Product specification

74F323

8-bit universal shift/storage register with synchronous

reset and common I/O pins (3-State)

1990 Mar 01

5

DC ELECTRICAL CHARACTERISTICS

(Over recommended operating free-air temperature range unless otherwise noted.)

SYMBOL

PARAMETER

TEST CONDITIONS

1

LIMITS

UNIT

SYMBOL

PARAMETER

TEST CONDITIONS

1

MIN

TYP

2

MAX

UNIT

V

OH

High-level output voltage

Q0, Q7

V

CC

= MIN,

V

IL

= MAX,

V

IH

= MIN

I

OH

= ≠1mA

±

10%V

CC

2.5

V

V

OH

High-level output voltage

Q0, Q7

V

CC

= MIN,

V

IL

= MAX,

V

IH

= MIN

I

OH

= ≠1mA

±

5%V

CC

2.7

3.4

V

V

OH

High-level output voltage

I/On

V

IL

= MAX,

V

IH

= MIN

I

OH

= ≠3mA

±

10%V

CC

2.5

V

I/On

V

IH

= MIN

I

OH

= ≠3mA

±

5%V

CC

2.7

3.4

V

V

OL

Low-level output voltage

V

CC

= MIN,

V

IL

= MAX,

V

IH

= MIN

I

OL

= MAX

±

10%V

CC

0.35

0.50

V

V

OL

Low-level output voltage

V

IL

= MAX,

V

IH

= MIN

I

OL

= MAX

±

5%V

CC

0.35

0.50

V

V

IK

Input clamp voltage

V

CC

= MIN, I

I

= I

IK

≠0.73

≠1.2

V

I

I

Input current at

maximum input voltage

others

V

CC

= MAX, V

I

= 7.0V

100

µ

A

I

I

Input current at

maximum input voltage

I/On

V

CC

= 5.5V, V

I

= 5.5V

1

mA

I

IH

High-level input current

except

I/On

V

CC

= MAX, V

I

= 2.7V

20

µ

A

I

IL

Low-level input current

S0, S1

V

CC

= MAX, V

I

= 0.5V

≠1.2

mA

I

IL

Low-level input current

others

V

CC

= MAX, V

I

= 0.5V

≠0.6

mA

I

IH +

I

OZH

Off-state output current,

High-level voltage

applied

I/On

only

V

CC

= MAX, V

O

= 2.7V

70

µ

A

I

IL +

I

OZL

Off-state output current

Low-level voltage applied

only

V

CC

= MAX, V

O

= 0.5V

≠0.6

mA

I

OS

Short-circuit output current

3

V

CC

= MAX

≠60

≠150

mA

I

CCH

V

CC

= MAX

55

75

mA

I

CC

Supply current (total)

I

CCL

V

CC

= MAX

65

90

mA

I

CCZ

CC

= MAX

55

85

mA

NOTES:

1. For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable type.

2. All typical values are at V

CC

= 5V, T

amb

=+ 25

∞

C.

3. Not more than one output should be shorted at a time. For testing I

OS

, the use of high-speed test apparatus and/or sample-and-hold

techniques are preferable in order to minimize internal heating and more accurately reflect operational values. Otherwise, prolonged shorting

of a High output may raise the chip temperature well above normal and thereby cause invalid readings in other parameter tests. In any

sequence of parameter tests, I

OS

tests should be performed last.

Philips Semiconductors

Product specification

74F323

8-bit universal shift/storage register with synchronous

reset and common I/O pins (3-State)

1990 Mar 01

6

AC ELECTRICAL CHARACTERISTICS

SYMBOL

PARAMETER

TEST CONDITIONS

LIMITS

UNIT

SYMBOL

PARAMETER

TEST CONDITIONS

T

amb

= +25

∞

C

T

amb

= 0

∞

C to +70

∞

C

UNIT

SYMBOL

PARAMETER

TEST CONDITIONS

V

CC

= +5.0V

V

CC

= +5.0V

±

10%

UNIT

C

L

= 50pF, R

L

= 500

C

L

= 50pF, R

L

= 500

MIN

TYP

MAX

MIN

MAX

f

MAX

Maximum clock frequency

I/O

Waveform 1

70

100

70

MHz

f

MAX

Maximum clock frequency

Qn

Waveform 1

85

115

85

MHz

t

PLH

t

PHL

Propagation delay

CP to Q0 or Q7

Waveform 1

4.0

3.5

6.0

6.0

8.5

8.5

3.5

4.5

9.5

9.5

ns

ns

t

PLH

t

PHL

Propagation delay

CP to I/On

Waveform 1

4.0

5.0

6.0

6.5

9.0

9.5

4.0

4.0

10.0

10.0

ns

ns

t

PZH

t

PZL

Output Enable time

Sn, OE to I/On

Waveform 3

Waveform 4

3.5

4.0

6.0

8.0

9.0

11.0

3.5

4.0

10.0

11.5

ns

ns

t

PHZ

t

PLZ

Output Disable time

Sn, OE to I/On

Waveform 3

Waveform 4

2.5

1.5

5.0

3.0

7.5

5.5

2.5

1.5

8.0

6.5

ns

ns

AC SETUP REQUIREMENTS

SYMBOL

PARAMETER

TEST CONDITIONS

LIMITS

UNIT

SYMBOL

PARAMETER

TEST CONDITIONS

T

amb

= +25

∞

C

T

amb

= 0

∞

C to +70

∞

C

UNIT

SYMBOL

PARAMETER

TEST CONDITIONS

V

CC

= +5.0V

V

CC

= +5.0V

±

10%

UNIT

C

L

= 50pF, R

L

= 500

C

L

= 50pF, R

L

= 500

MIN

TYP

MAX

MIN

MAX

t

s

(H)

t

s

(L)

Setup time, High or Low

S0 or S1 to CP

Waveform 2

6.5

6.5

7.5

7.5

ns

t

h

(H)

t

h

(L)

Hold time, High or Low

S0 or S1 to CP

Waveform 2

0

0

0

0

ns

t

s

(H)

t

s

(L)

Setup time, High or Low

I/O0, DS0 or DS7 to CP

Waveform 2

3.5

3.5

4.0

4.0

ns

t

h

(H)

t

h

(L)

Hold time, High or Low

I/O0, DS0 or DS7 to CP

Waveform 2

0

0

0

0

ns

t

s

(H)

t

s

(L)

Setup time, High or Low

SR to CP

Waveform 2

7.0

7.0

8.5

8.5

ns

t

h

(H)

t

h

(L)

Hold time, High or Low

SR to CP

Waveform 2

0

0

0

0

ns

t

w

(H)

t

w

(L)

CP Pulse width, High or Low

Waveform 1

3.5

3.5

4.0

4.0

ns

Philips Semiconductors

Product specification

74F323

8-bit universal shift/storage register with synchronous

reset and common I/O pins (3-State)

1990 Mar 01

7

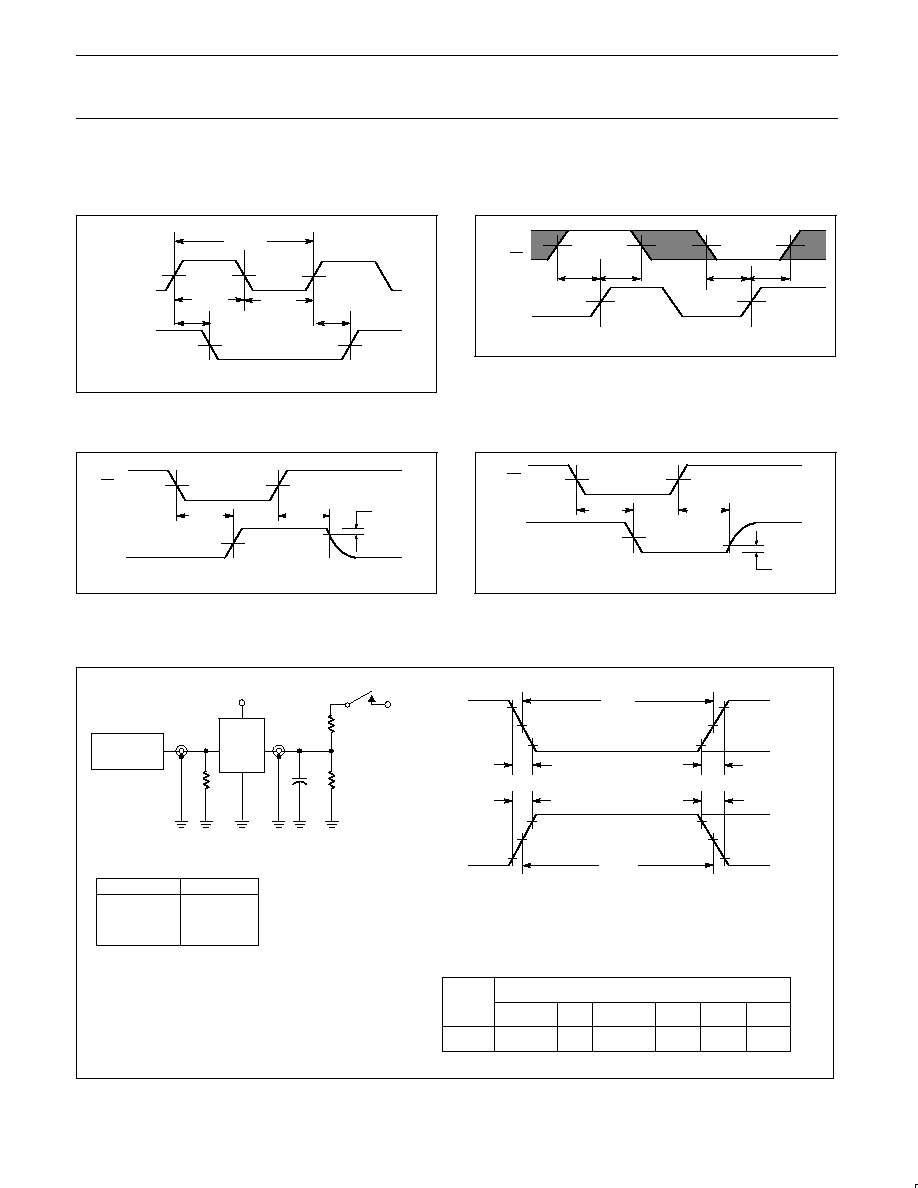

AC WAVEFORMS

For all waveforms, V

M

= 1.5V

The shaded areas indicate when the input is permitted to change for predictable output performance.

tPLH

tPHL

VM

VM

VM

VM

1/fMAX

tW(L)

CP

Q0, Q7, I/On

tW(H)

SF00884

Waveform 1. Propagation Delay, Clock Input to Output,

Clock Pulse Width, and Maximum Clock Frequency

VM

VM

VM

VM

VM

VM

S0, S1,

DS

L

, DS

R

,

I/On, SR

CP

SF00885

ts(H)

th(H)

th(L)

ts(L)

Waveform 2. Data, Select and Reset Setup and Hold Times

VM

VM

VM

tPHZ

tPZH

Sn, OEn

I/On

VOH -0.3V

0V

SF00886

Waveform 3. 3-State Output Enable Time to High Level

and Output Disable Time from High Level

VM

VM

VM

tPLZ

tPZL

Sn, OEn

I/On

VOL +0.3V

SF00887

Waveform 4. 3-State Output Enable Time to Low Level and

Output Disable Time from Low Level

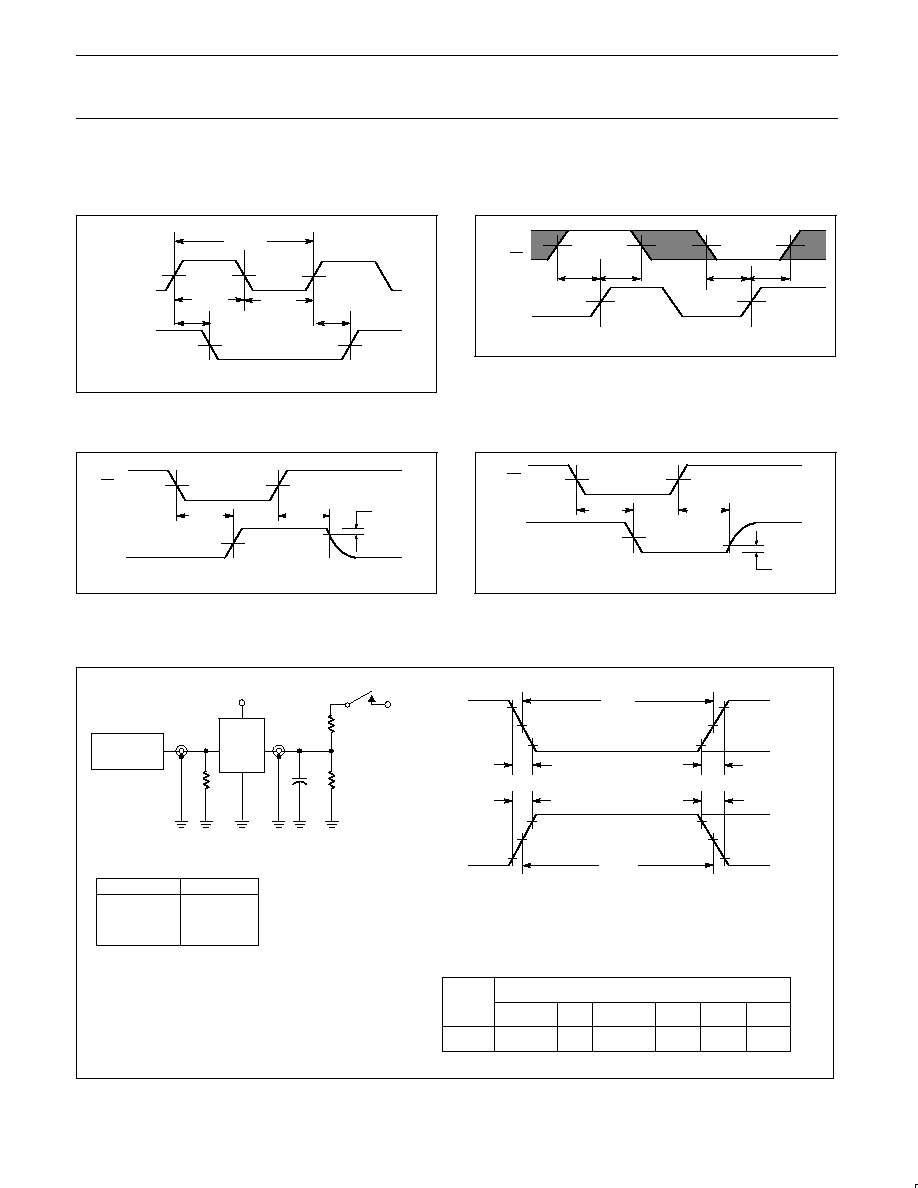

TEST CIRCUIT AND WAVEFORM

tw

90%

VM

10%

90%

VM

10%

90%

VM

10%

90%

VM

10%

NEGATIVE

PULSE

POSITIVE

PULSE

tw

AMP (V)

0V

0V

tTHL (tf

)

INPUT PULSE REQUIREMENTS

rep. rate

t

w

t

TLH

t

THL

1MHz

500ns

2.5ns

2.5ns

Input Pulse Definition

VCC

family

74F

D.U.T.

PULSE

GENERATOR

RL

CL

RT

VIN

VOUT

Test Circuit for 3-State Outputs

DEFINITIONS:

R

L

= Load resistor;

see AC electrical characteristics for value.

C

L

= Load capacitance includes jig and probe capacitance;

see AC electrical characteristics for value.

R

T

= Termination resistance should be equal to Z

OUT

of

pulse generators.

tTHL (tf

)

tTLH (tr

)

tTLH (tr

)

AMP (V)

amplitude

3.0V

1.5V

V

M

RL

7.0V

SF00777

TEST

SWITCH

t

PLZ

closed

t

PZL

closed

All other

open

SWITCH POSITION