| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: P83C654X2 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Document Outline

- DESCRIPTION

- FEATURES

- ORDERING INFORMATION

- BLOCK DIAGRAM 1

- BLOCK DIAGRAM (CPU ORIENTED)

- LOGIC SYMBOL

- PINNING

- PIN DESCRIPTIONS

- SPECIAL FUNCTION REGISTERS

- CLOCK CONTROL REGISTER (CKCON)

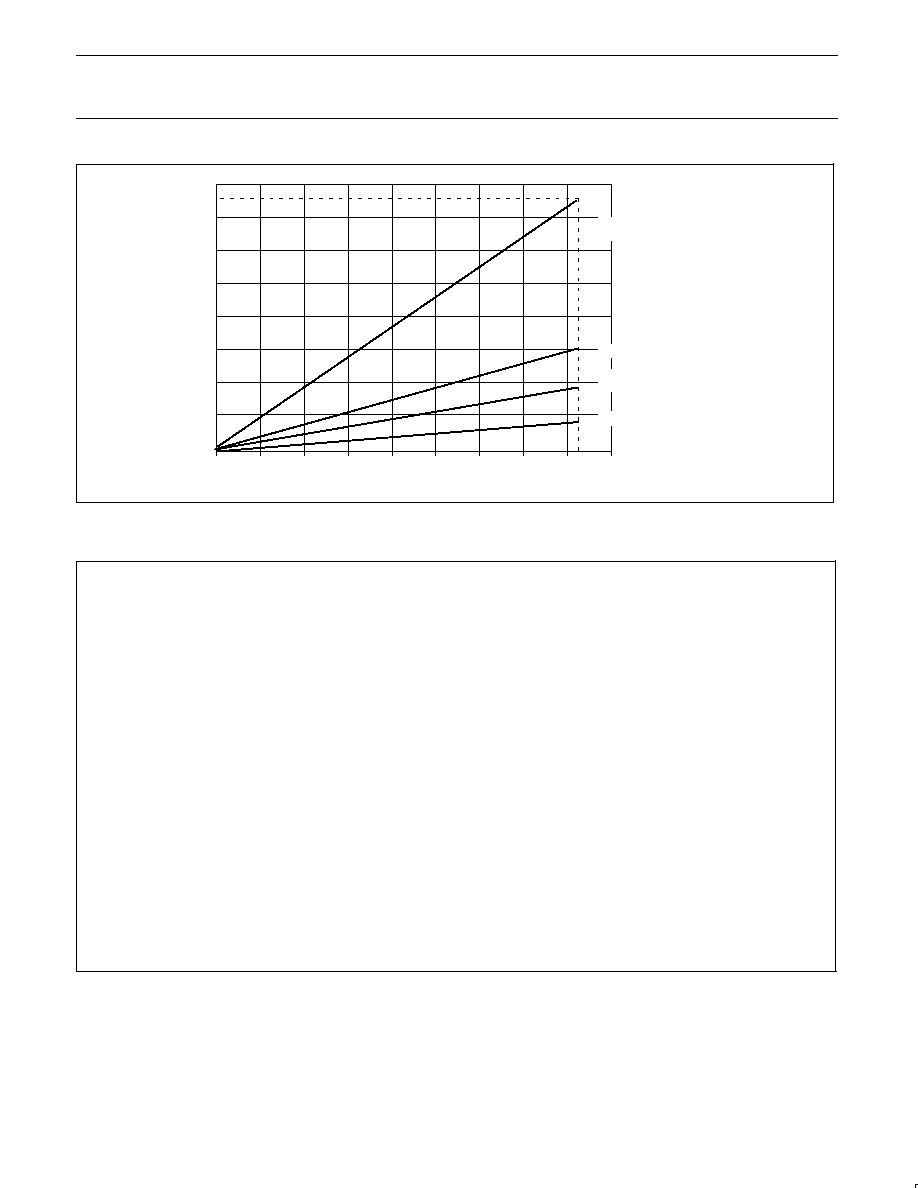

- OSCILLATOR CHARACTERISTICS

- RESET

- LOW POWER MODES

- POWER-OFF FLAG

- ONCEE Mode

- TIMER 0 AND TIMER 1 OPERATION

- TIMER 2 OPERATION

- FULL-DUPLEX ENHANCED UART

- HARDWARE WATCHDOG TIMER (ONE-TIME ENABLED WITH RESET-OUT FOR P8XC654X2)

- ABSOLUTE MAXIMUM RATINGS 1, 2, 3

- AC ELECTRICAL CHARACTERISTICS

- DC ELECTRICAL CHARACTERISTICS

- AC ELECTRICAL CHARACTERISTICS (12-CLOCK MODE, 5 V ±10 % OPERATION)

- AC ELECTRICAL CHARACTERISTICS (12-CLOCK MODE, 2.7 V TO 5.5 V OPERATION)

- AC ELECTRICAL CHARACTERISTICS (6-CLOCK MODE, 5 V ±10 % OPERATION)

- AC ELECTRICAL CHARACTERISTICS (6-CLOCK MODE, 2.7 V TO 5.5 V OPERATION)

- EXPLANATION OF THE AC SYMBOLS

- EPROM CHARACTERISTICS

- EPROM PROGRAMMING AND VERIFICATION CHARACTERISTICS

- MASK ROM DEVICES

- ROM CODE SUBMISSION FOR 16K ROM DEVICES

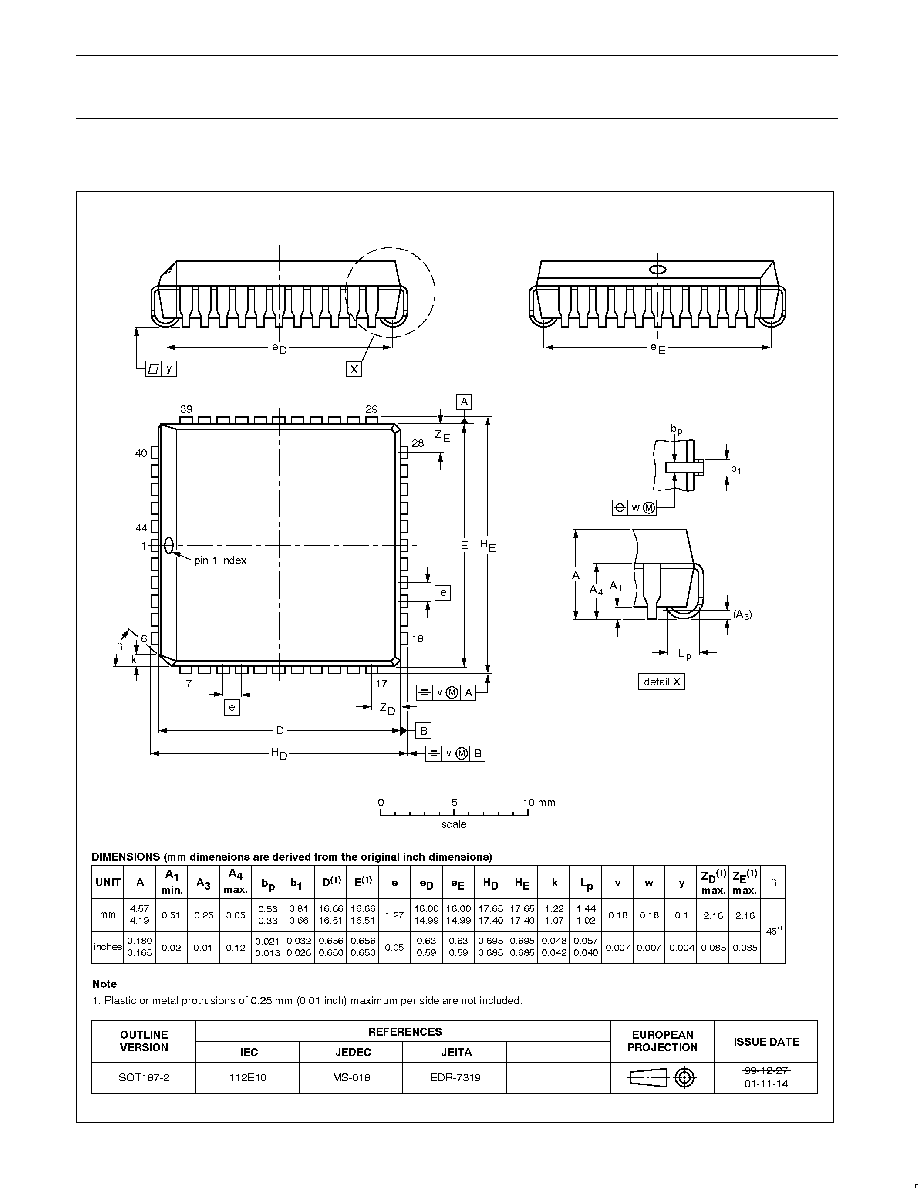

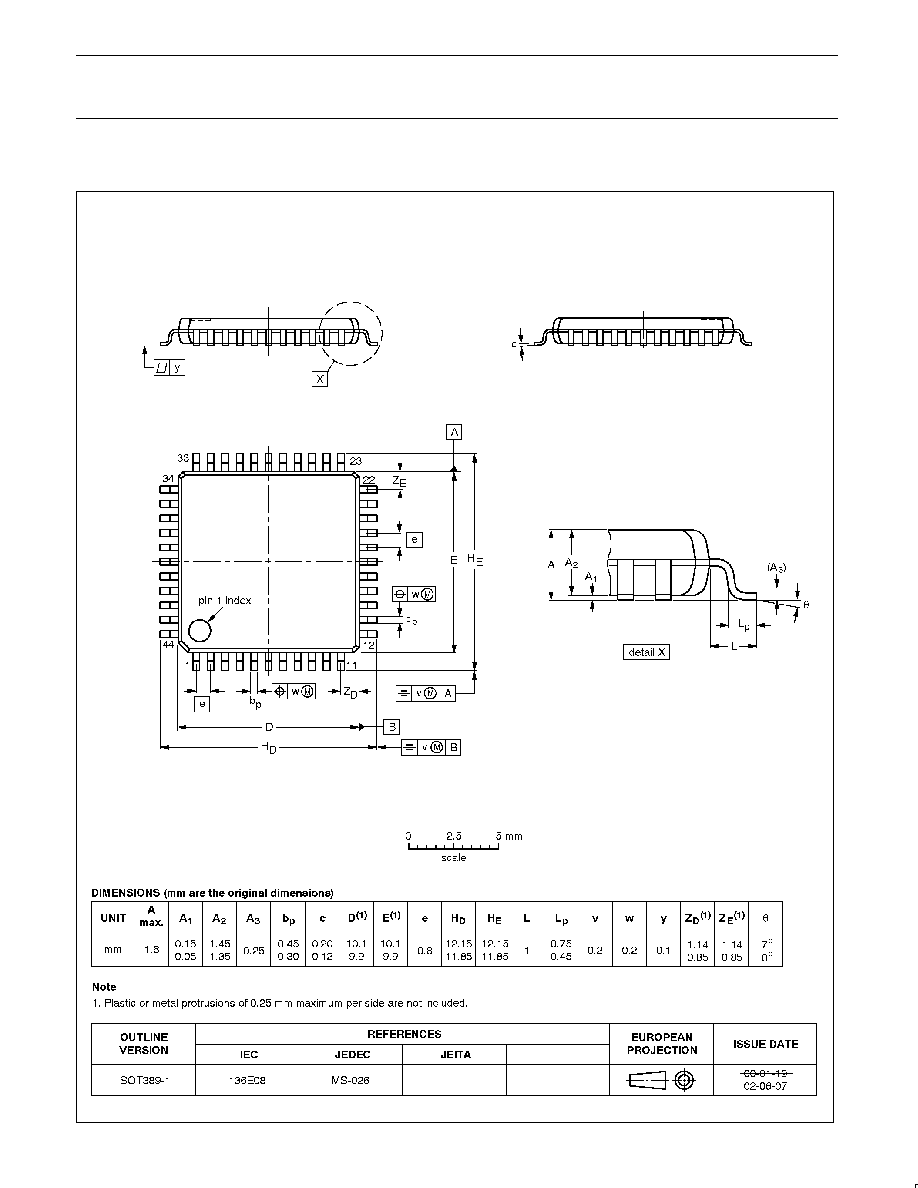

- PACKAGE OUTLINE

- REVISION HISTORY

- Data sheet status

- Definitions

- Disclaimers

Philips

Semiconductors

P83C654X2/P87C654X2

80C51 8-bit microcontroller family

16 kB OTP/ROM, 256B RAM, low voltage (2.7 to 5.5 V),

low power, high speed (30/33 MHz)

Product data

Supersedes data of 2003 Feb 13

2004 Apr 20

INTEGRATED CIRCUITS

Philips Semiconductors

Product data

P83C654X2/P87C654X2

80C51 8-bit microcontroller family

16 kB OTP/ROM,

256B RAM, low voltage (2.7 to 5.5 V), low power, high speed

(30/33 MHz)

2

2004 Apr 20

DESCRIPTION

The devices are Single-Chip 8-Bit Microcontrollers manufactured in

an advanced CMOS process and are derivatives of the 80C51

microcontroller family. The instruction set is 100 % compatible with

the 80C51 instruction set.

The devices support 6-clock/12-clock mode selection by

programming an OTP bit (OX2) using parallel programming. In

addition, an SFR bit (X2) in the clock control register (CKCON)

also selects between 6-clock/12-clock mode.

The devices also have four 8-bit I/O ports, three 16-bit timer/event

counters, a multi-source, four-priority-level, nested interrupt structure,

an enhanced UART and on-chip oscillator and timing circuits.

The added features of the P8xC654X2 make it a powerful

microcontroller for applications that require pulse width modulation,

high-speed I/O and up/down counting capabilities such as motor

control.

FEATURES

∑

80C51 Central Processing Unit

≠ 16 kbytes OTP

≠ 256 byte RAM

≠ Boolean processor

≠ Fully static operation

≠ Low voltage (2.7 V to 5.5 V at 16 MHz) operation

∑

12-clock operation with selectable 6-clock operation (via software

or via parallel programmer)

∑

Memory addressing capability

≠ Up to 64 kbytes ROM and 64 kbytes RAM

∑

Power control modes:

≠ Clock can be stopped and resumed

≠ Idle mode

≠ Power-down mode

∑

CMOS and TTL compatible

∑

Two speed ranges at V

CC

= 5 V

≠ 0 to 30 MHz with 6-clock operation

≠ 0 to 33 MHz with 12-clock operation

∑

Parallel programming with 87C51 compatible hardware interface

to programmer

∑

RAM expandable externally to 64 kbytes

∑

PLCC and LQFP packages

∑

Extended temperature ranges

∑

Dual Data Pointers

∑

Security bits (3 bits)

∑

Encryption array - 64 bytes

∑

Seven interrupt sources

∑

Four interrupt priority levels

∑

Four 8-bit I/O ports

∑

Full-duplex enhanced UART

≠ Framing error detection

≠ Automatic address recognition

∑

Three 16-bit timers/counters T0, T1 (standard 80C51) and

additional T2 (capture and compare)

∑

Programmable clock-out pin

∑

Asynchronous port reset

∑

Low EMI (inhibit ALE, slew rate controlled outputs, and 6-clock

mode)

∑

Wake-up from power-down by an external interrupt

∑

Watchdog timer

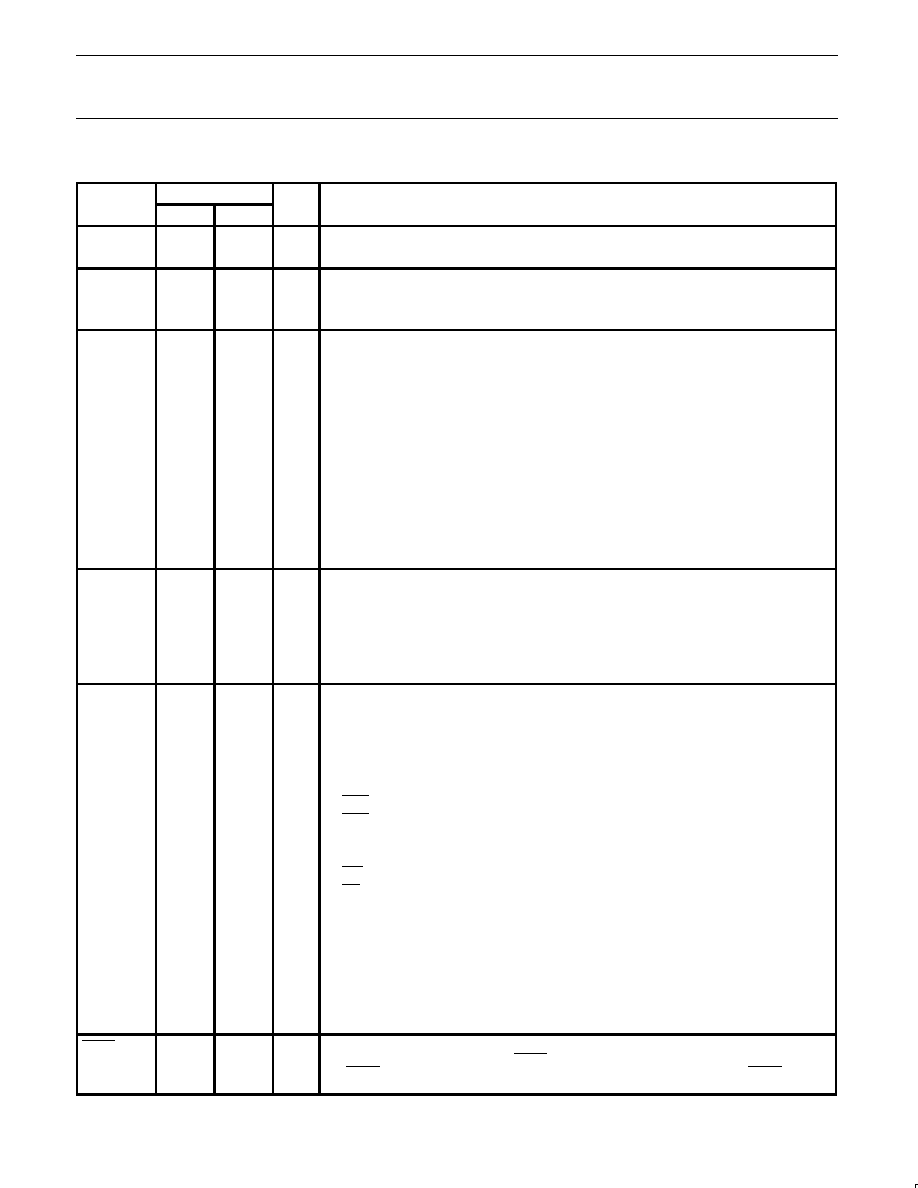

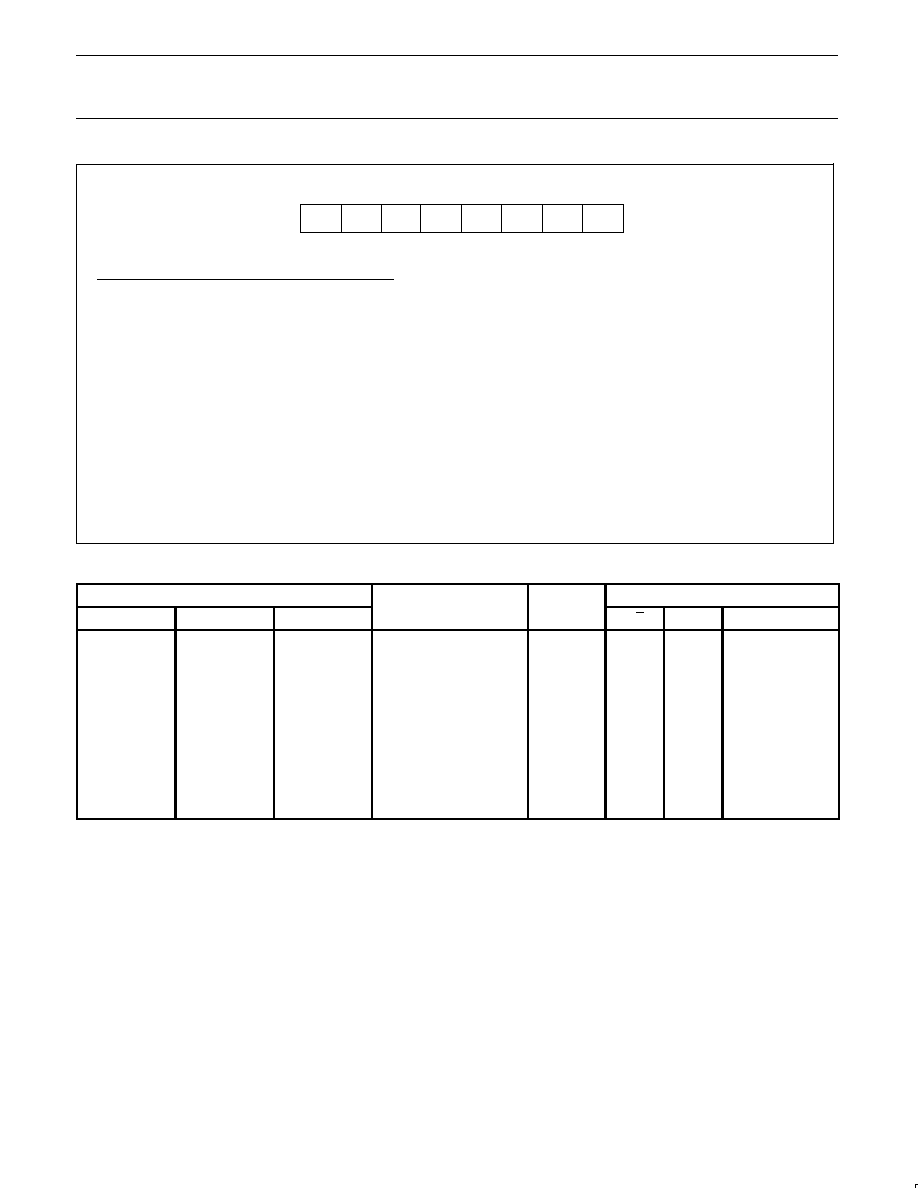

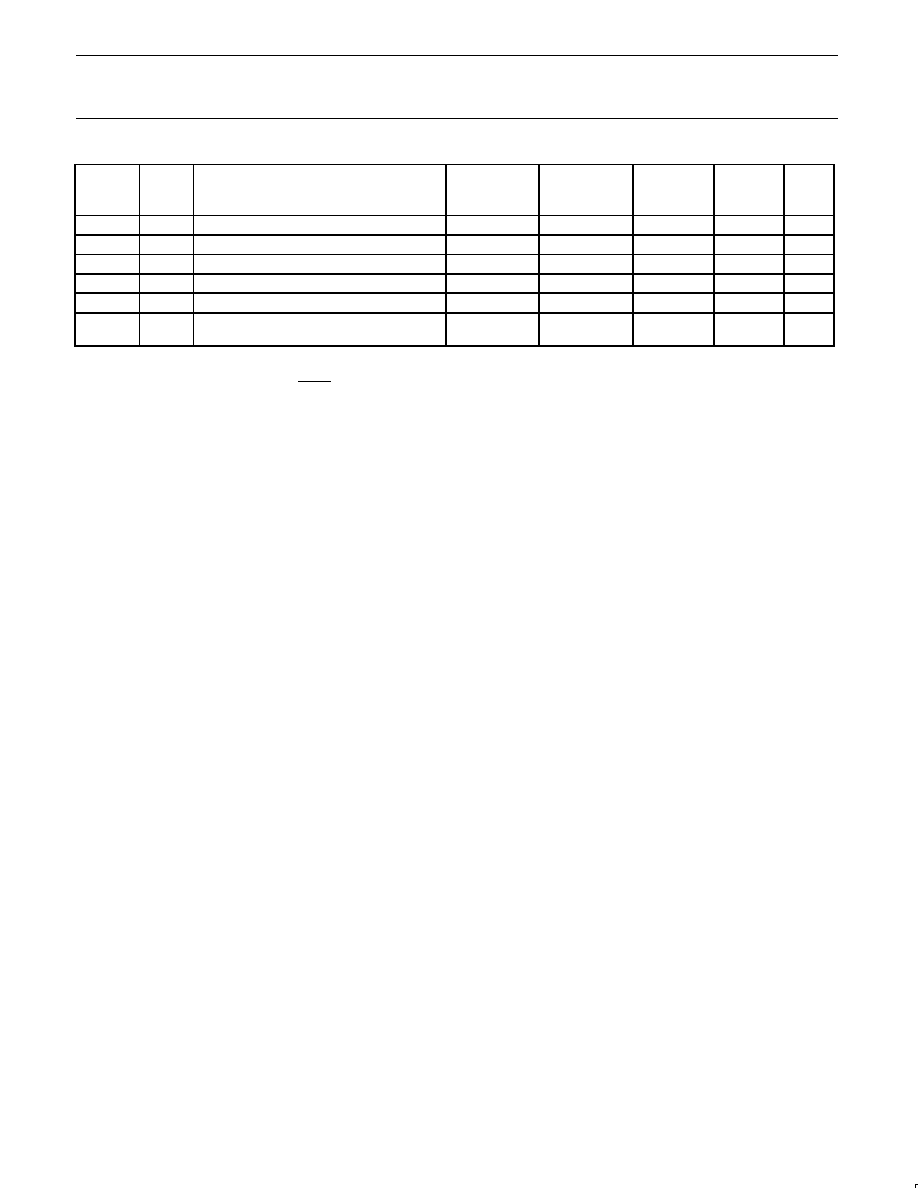

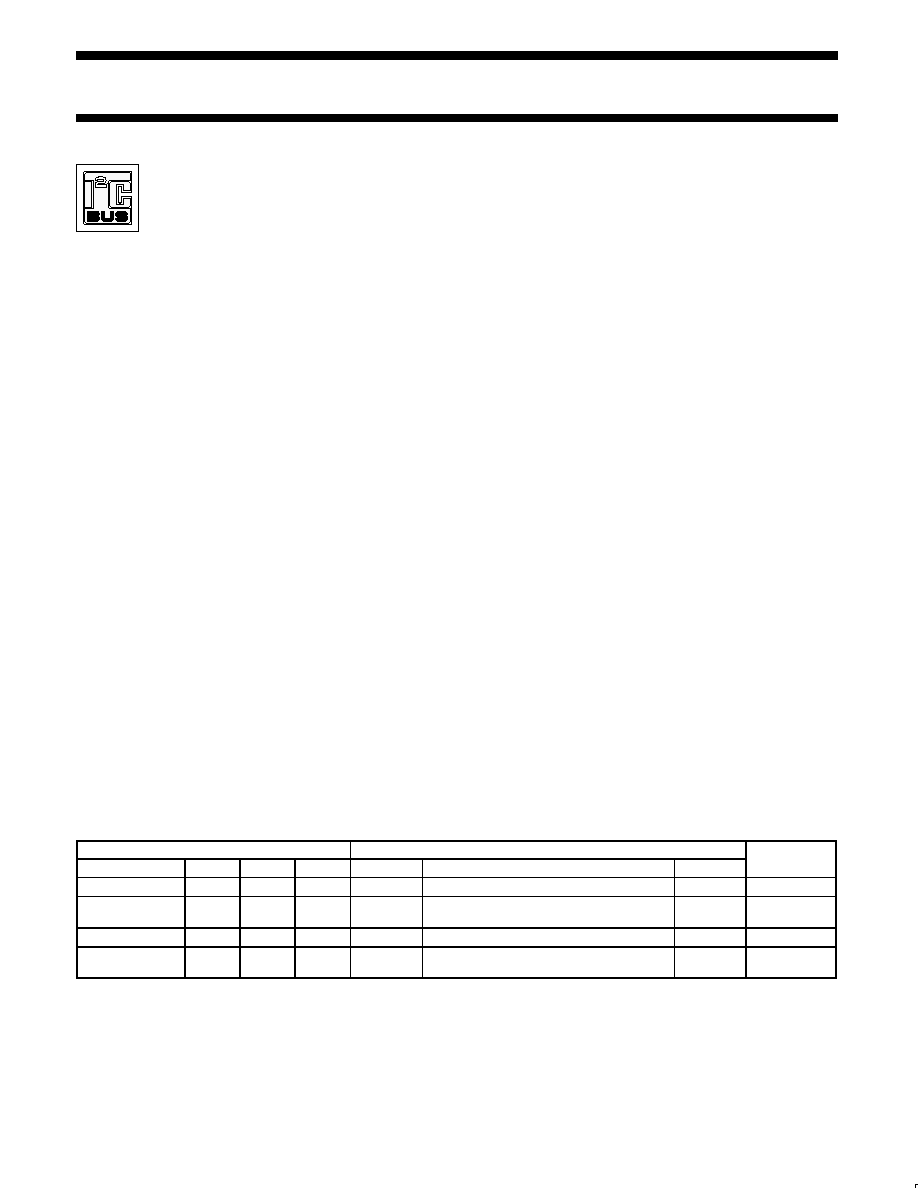

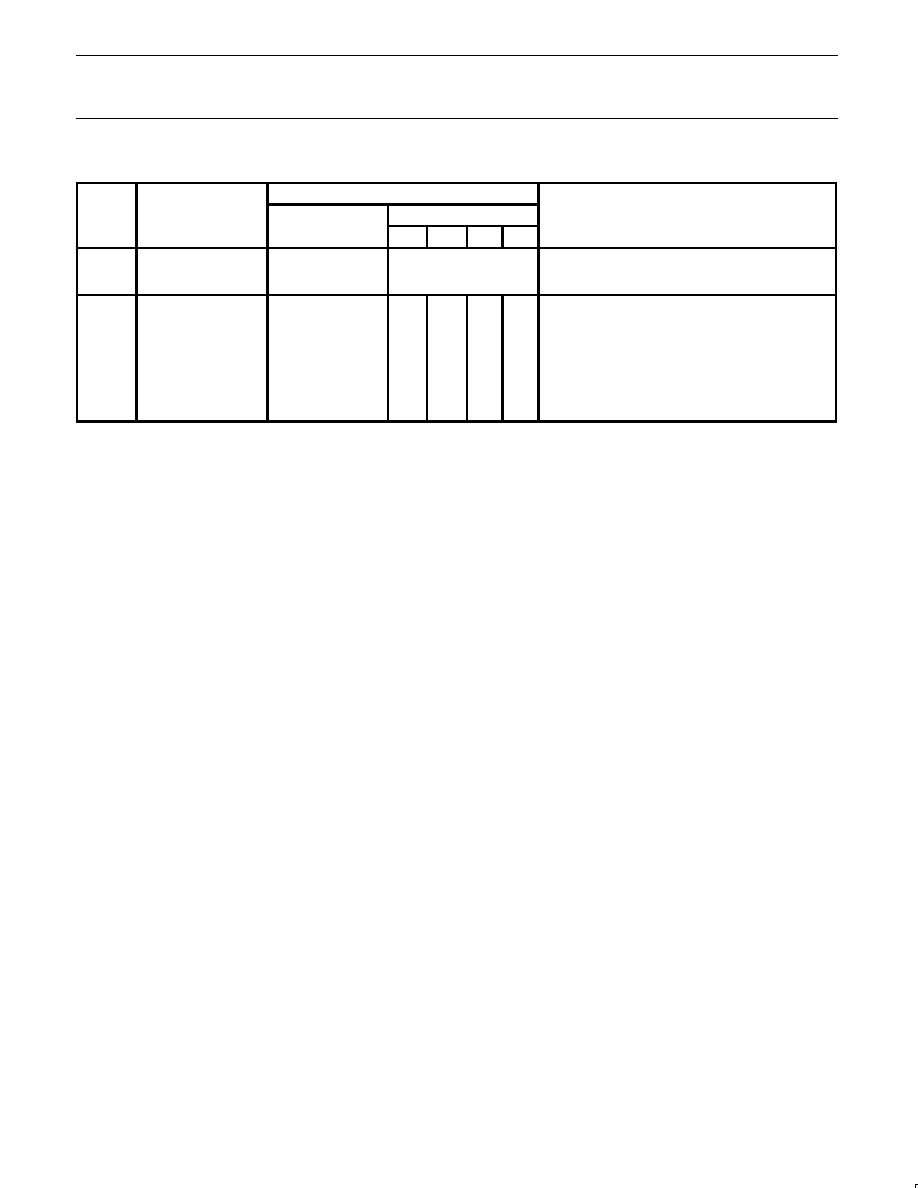

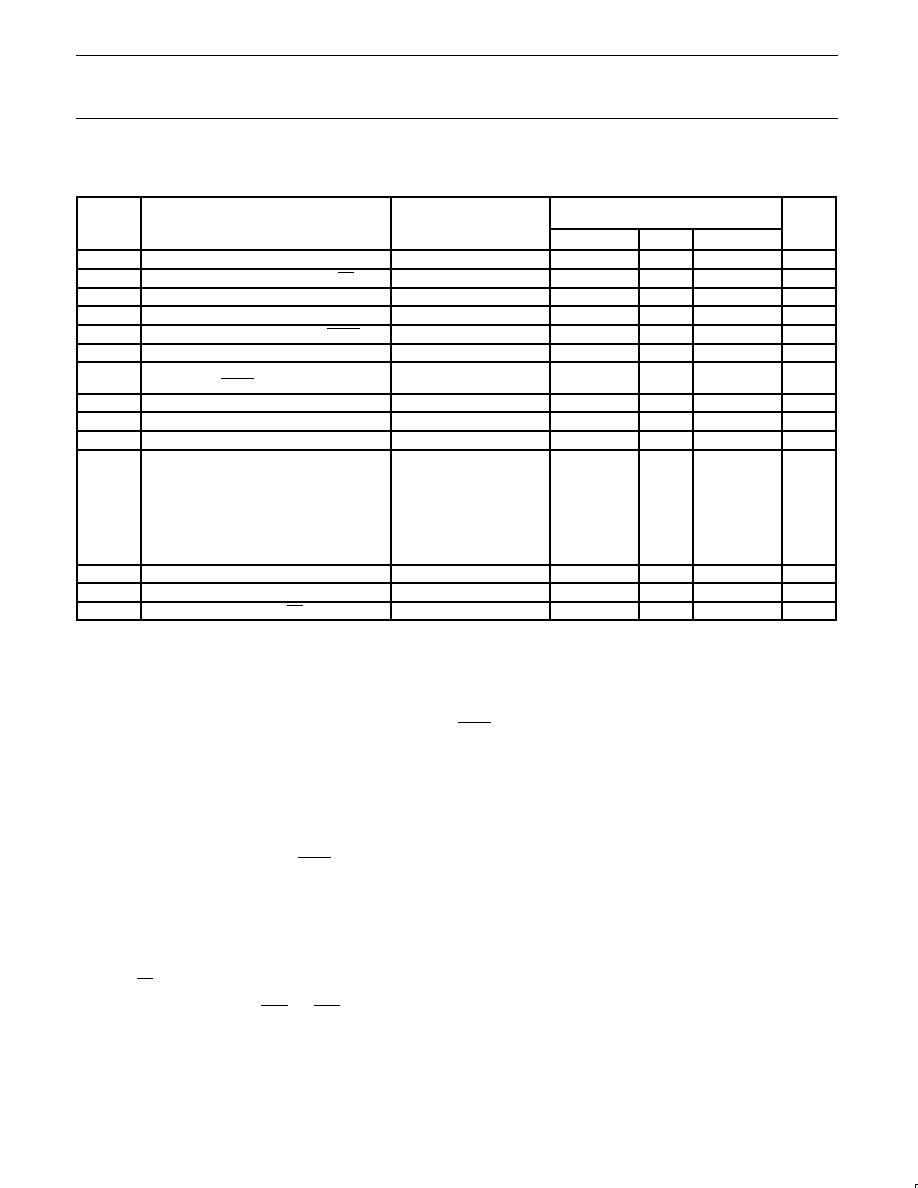

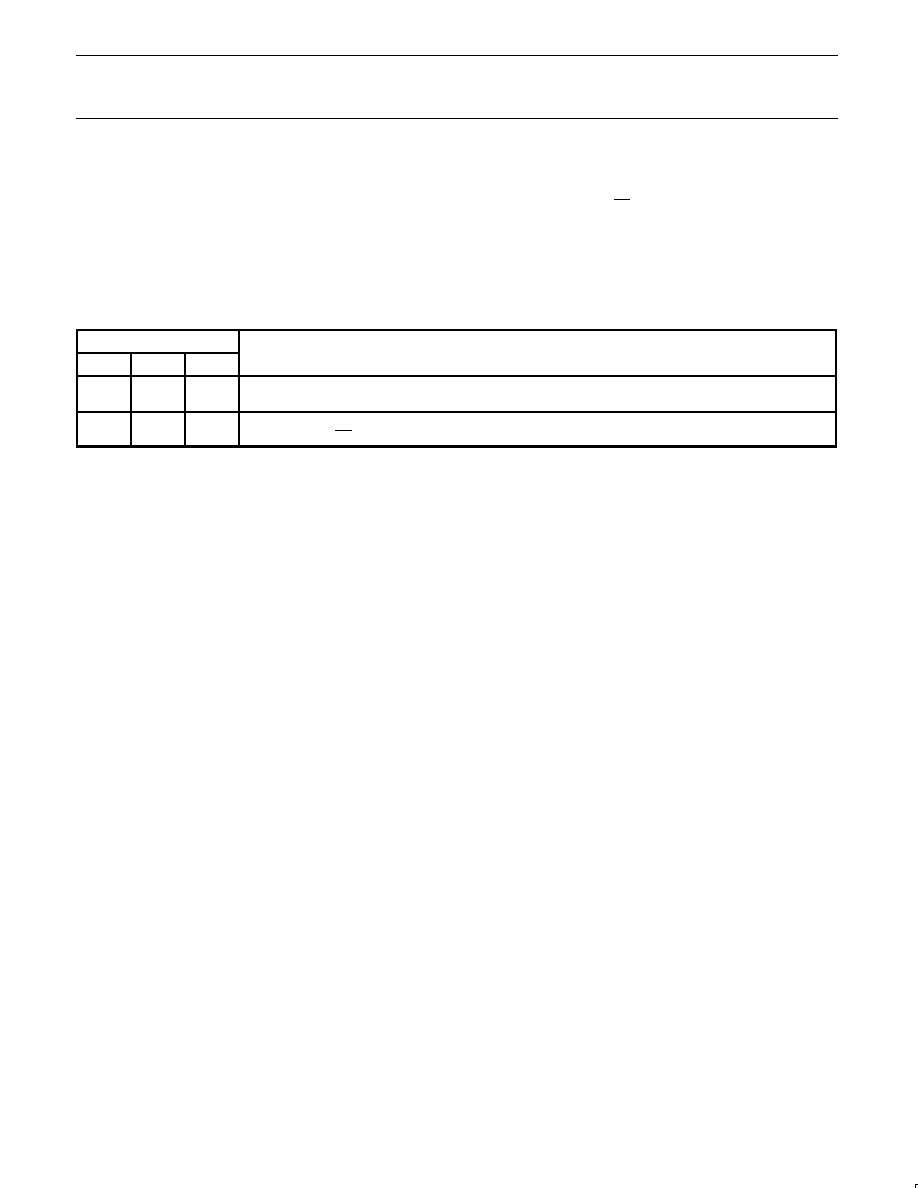

ORDERING INFORMATION

Type number

Package

Temp Range

(

∞

C)

OTP

ROM

RAM

Name

Description

Version

(

∞

C)

P83C654X2FA

≠

16 KB

256B

PLCC44

plastic leaded chip carrier; 44 leads

SOT187≠2

≠40 to +85

P83C654X2BBD

≠

16 KB

256B

LQFP44

plastic low profile quad flat package; 44 leads;

body 10

10

1.4 mm

SOT389≠1

0 to +70

P87C654X2FA

16 KB

≠

256B

PLCC44

plastic leaded chip carrier; 44 leads

SOT187≠2

≠40 to +85

P87C654X2BBD

16 KB

≠

256B

LQFP44

plastic low profile quad flat package; 44 leads;

body 10

10

1.4 mm

SOT389≠1

0 to +70

Philips Semiconductors

Product data

P83C654X2/P87C654X2

80C51 8-bit microcontroller family

16 kB OTP/ROM,

256B RAM, low voltage (2.7 to 5.5 V), low power, high speed

(30/33 MHz)

2004 Apr 20

3

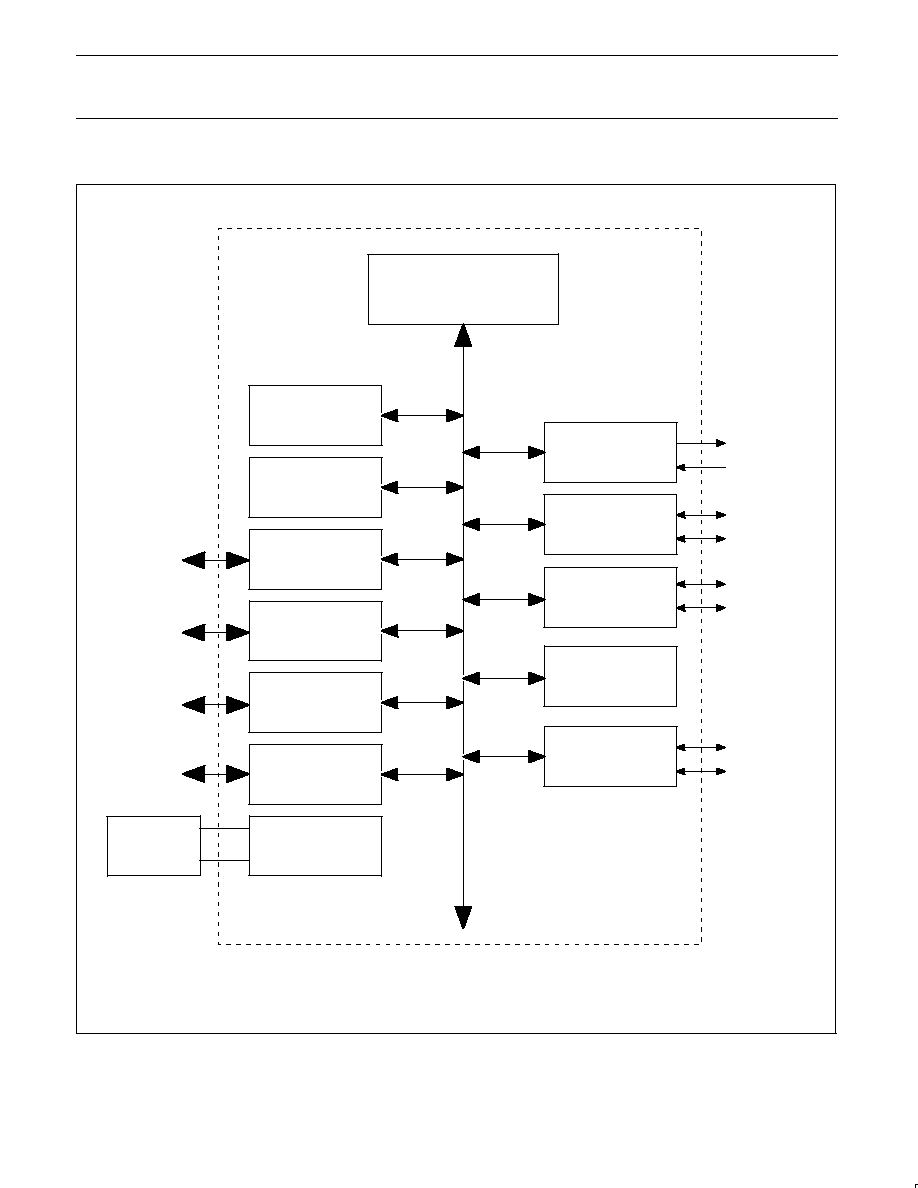

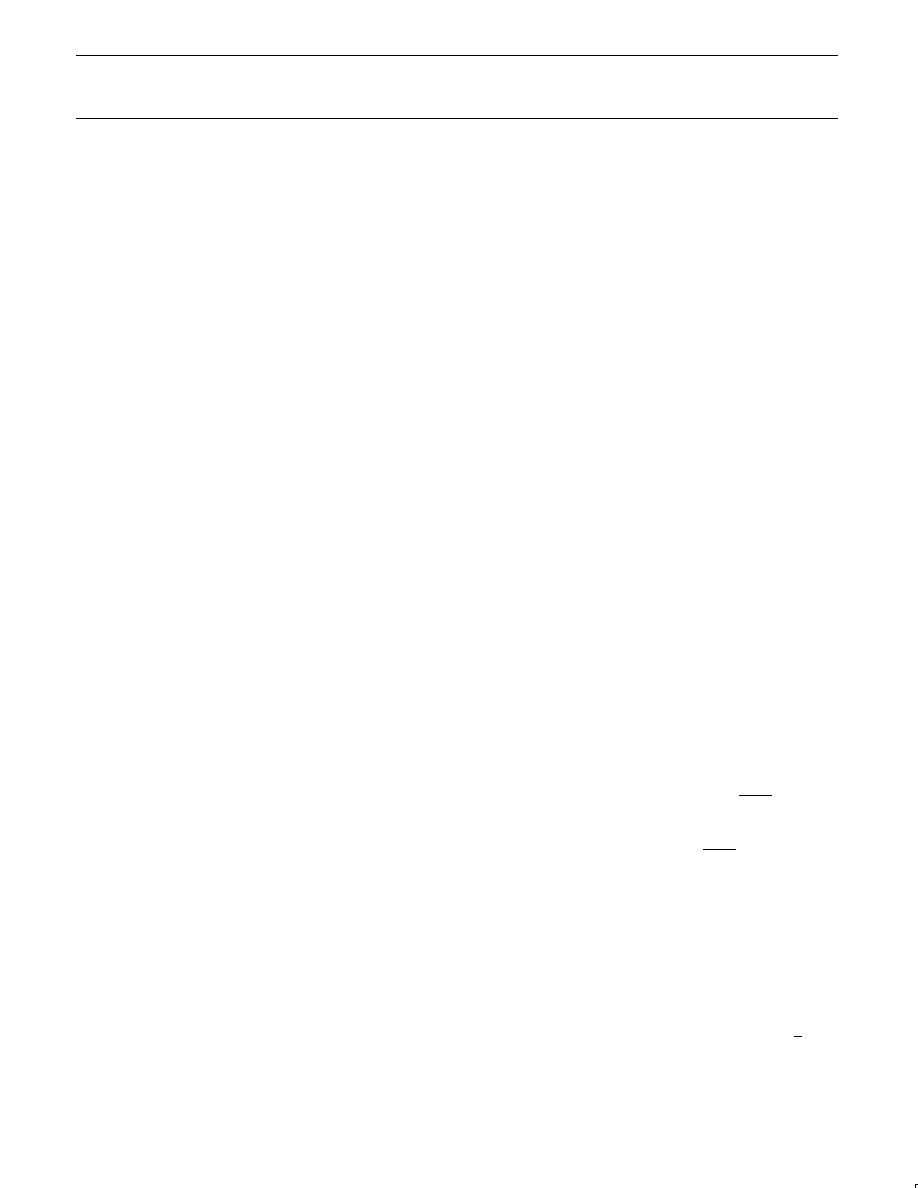

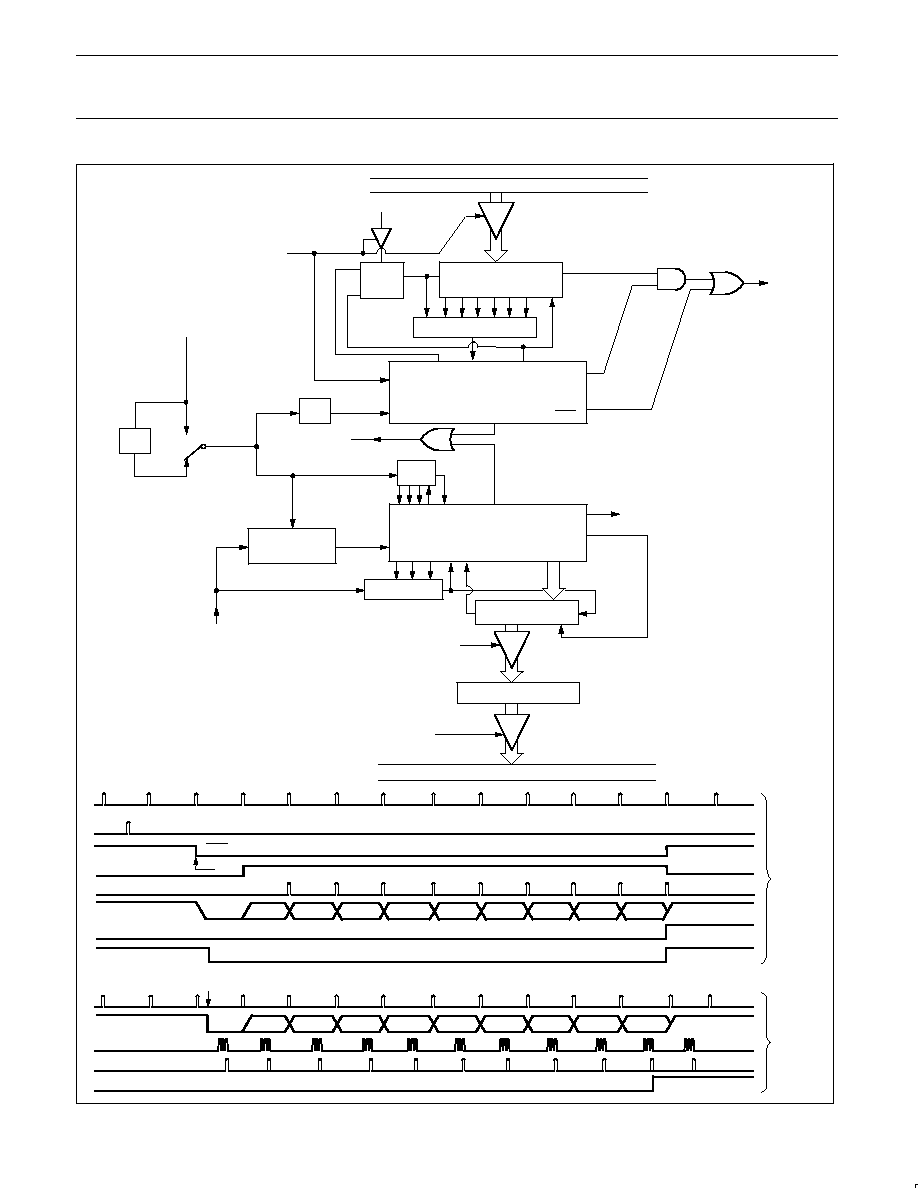

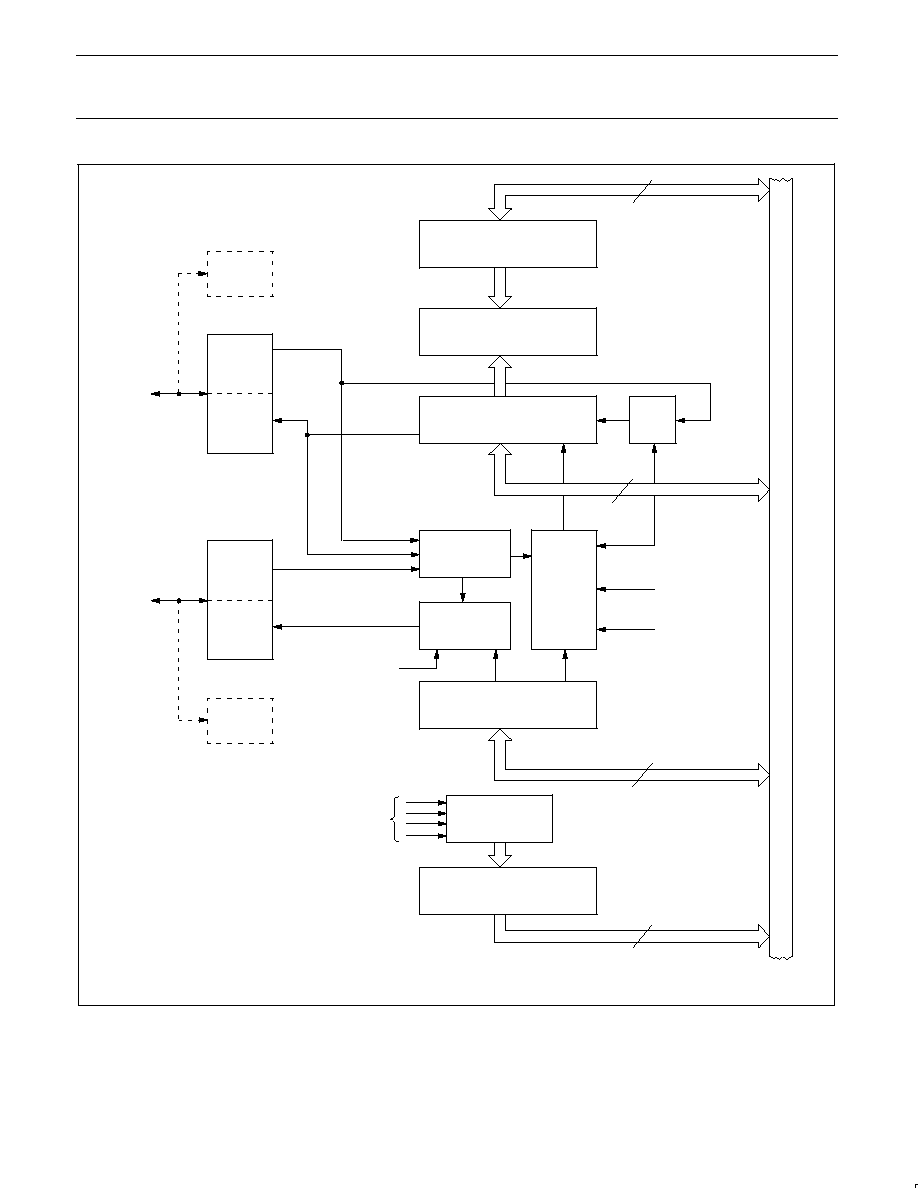

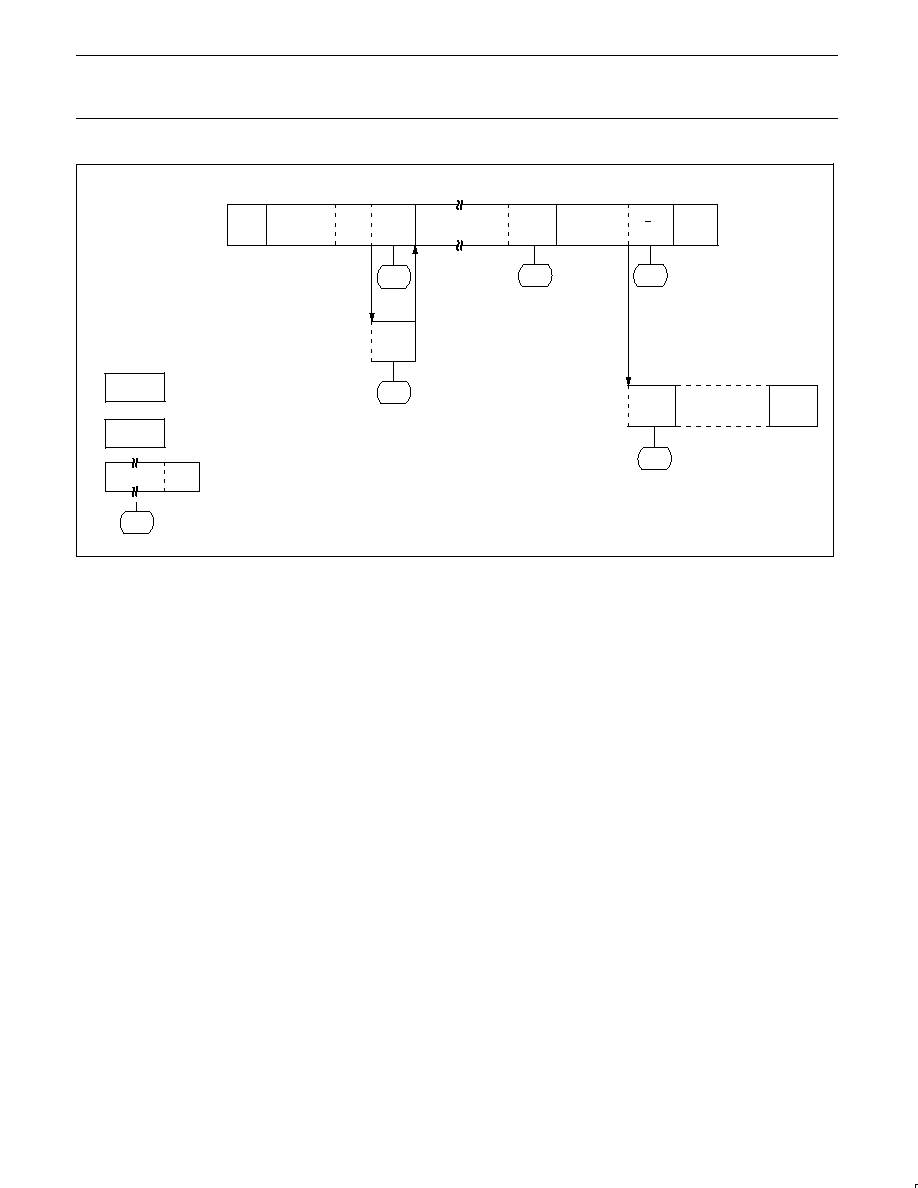

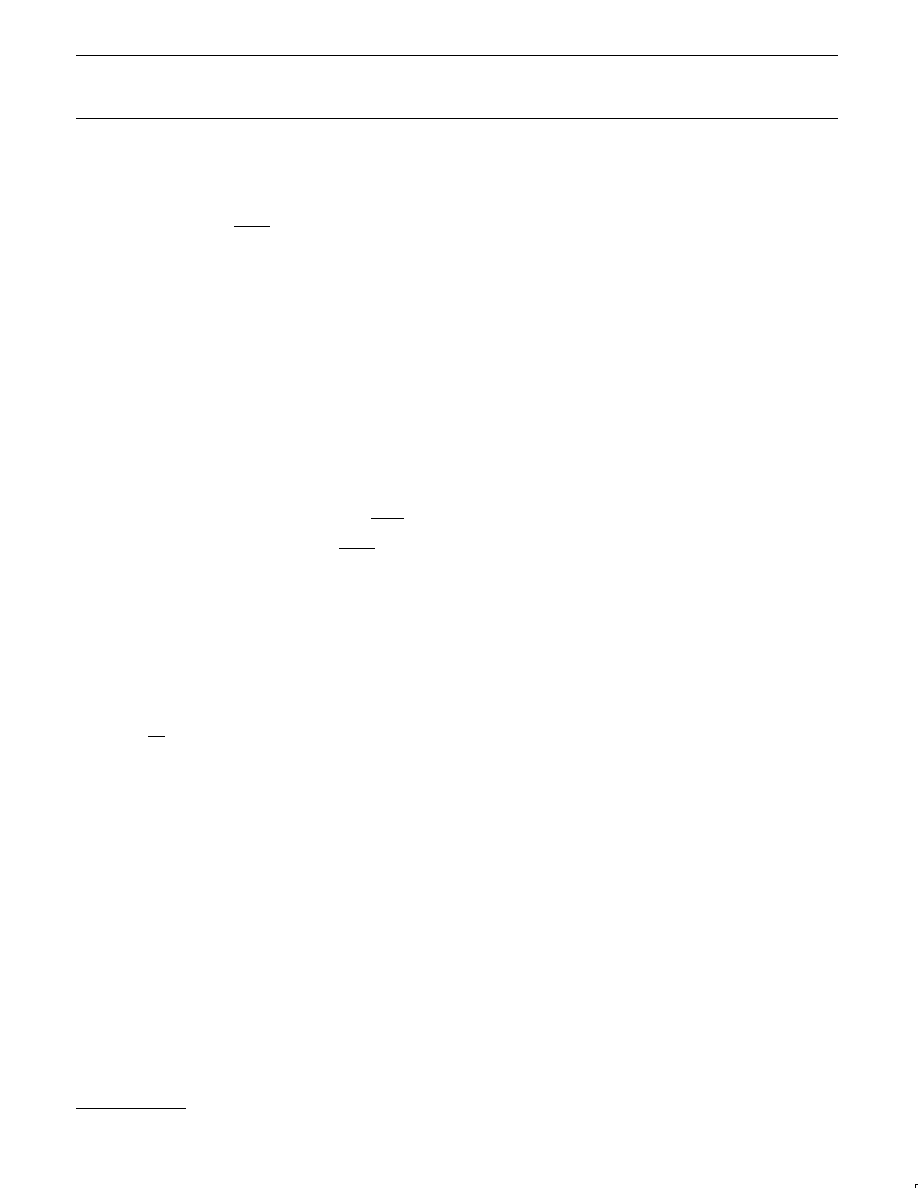

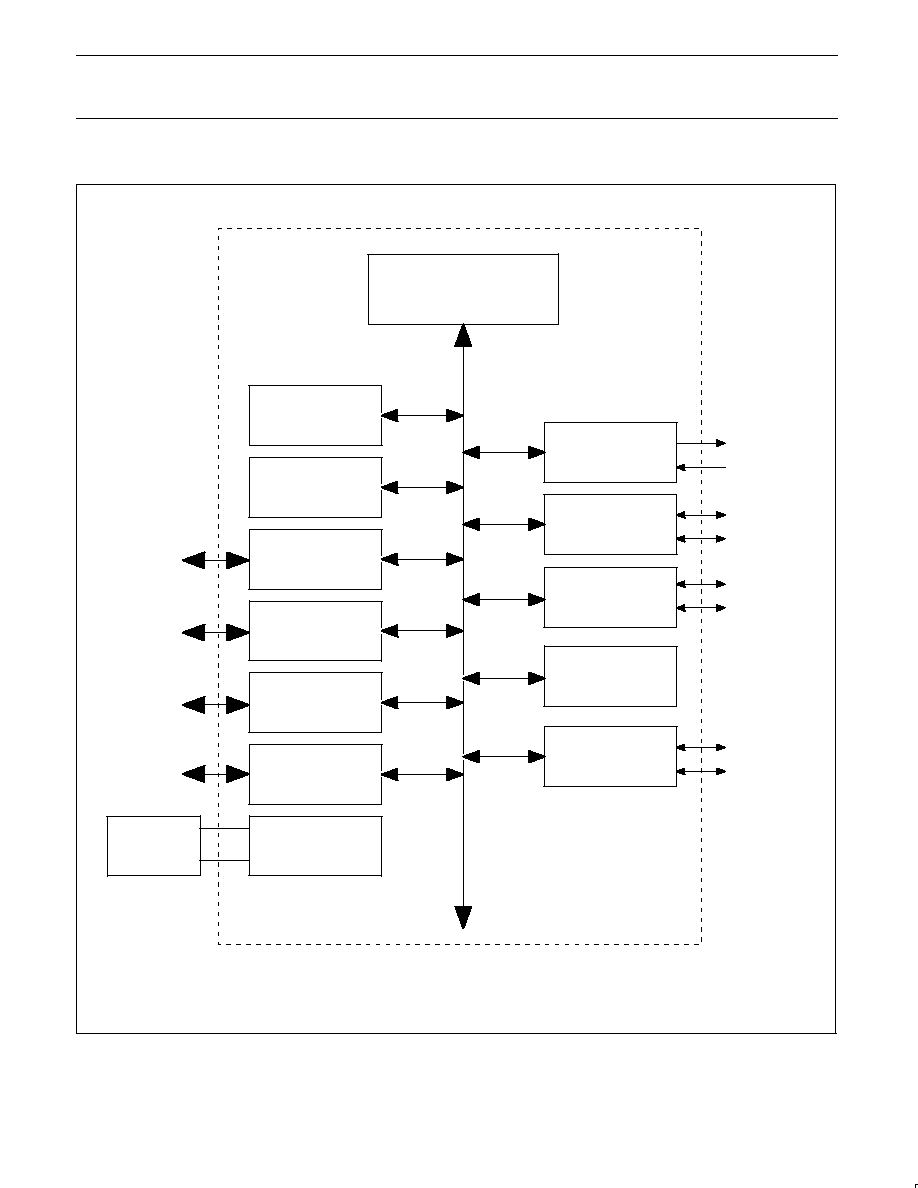

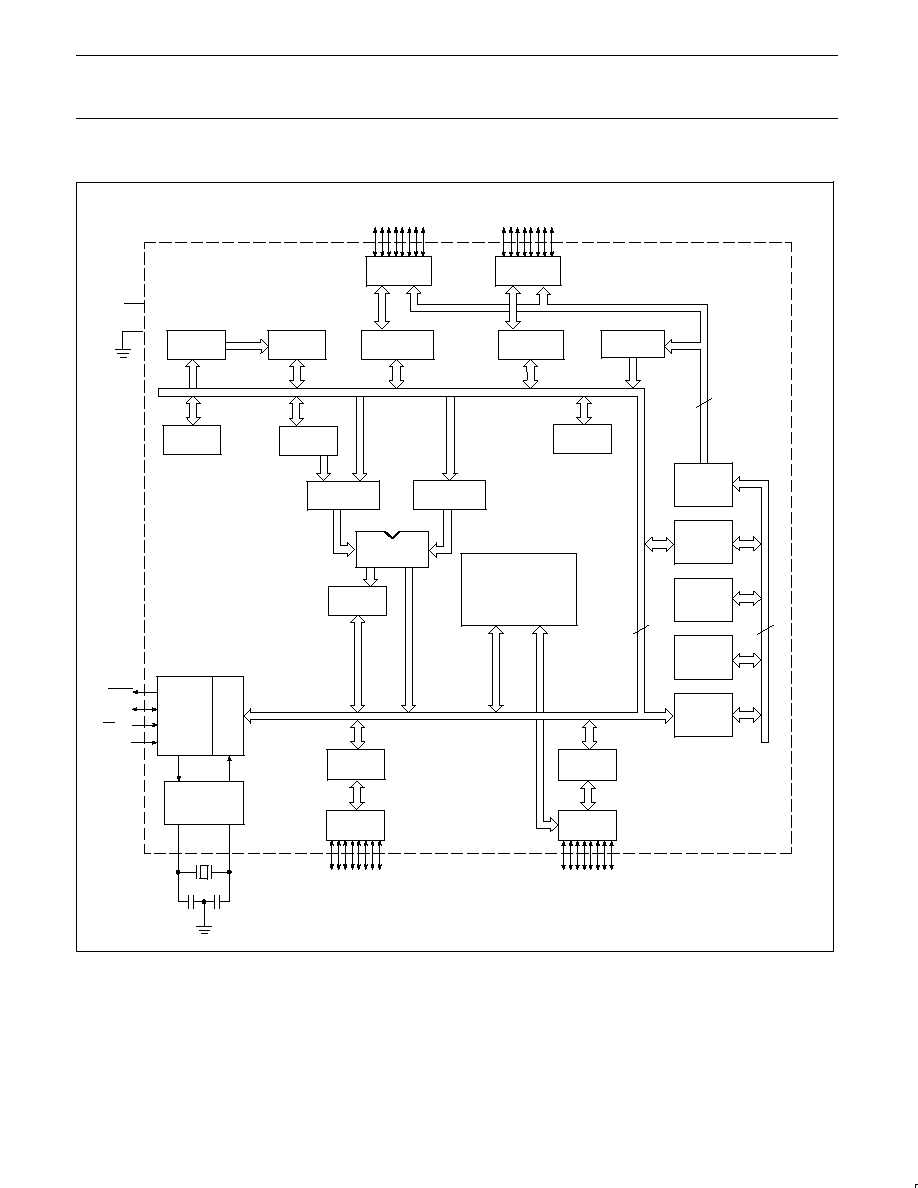

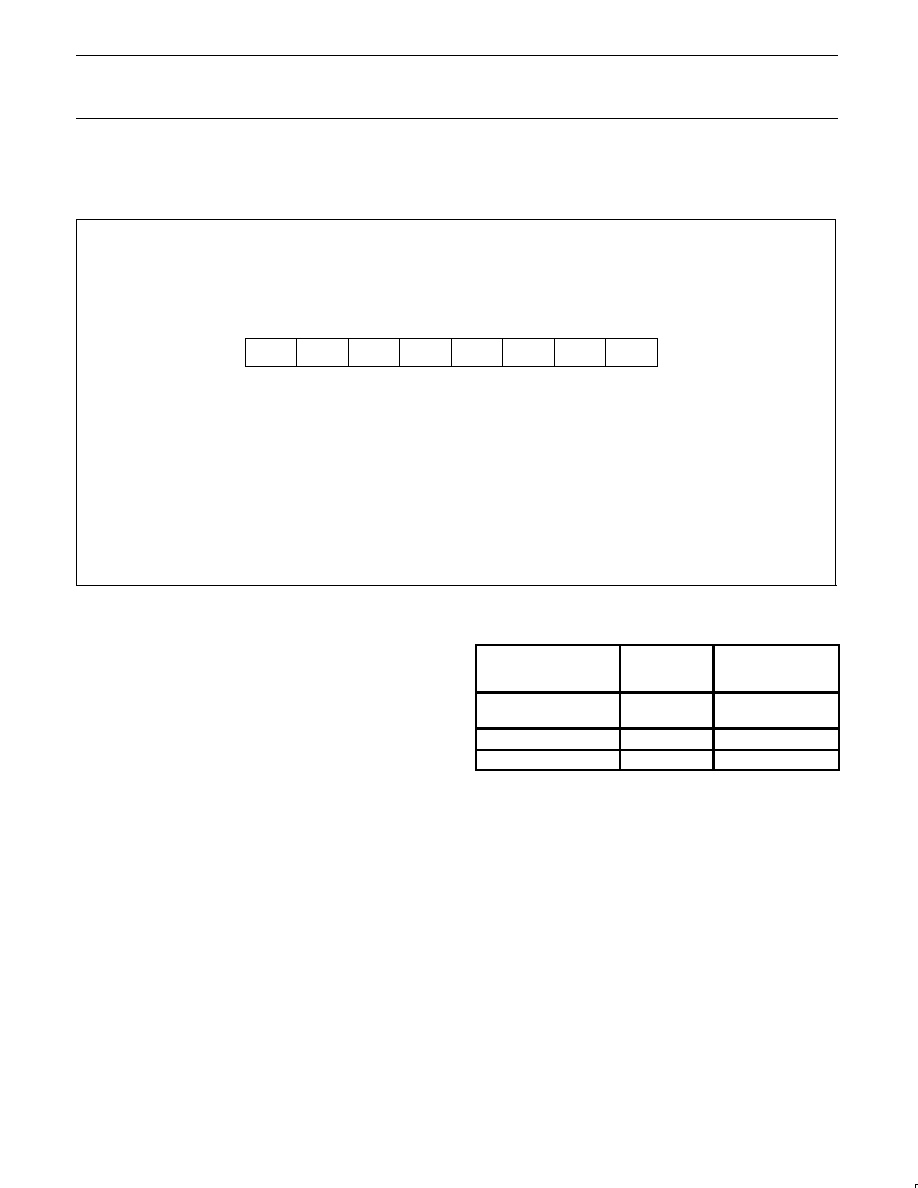

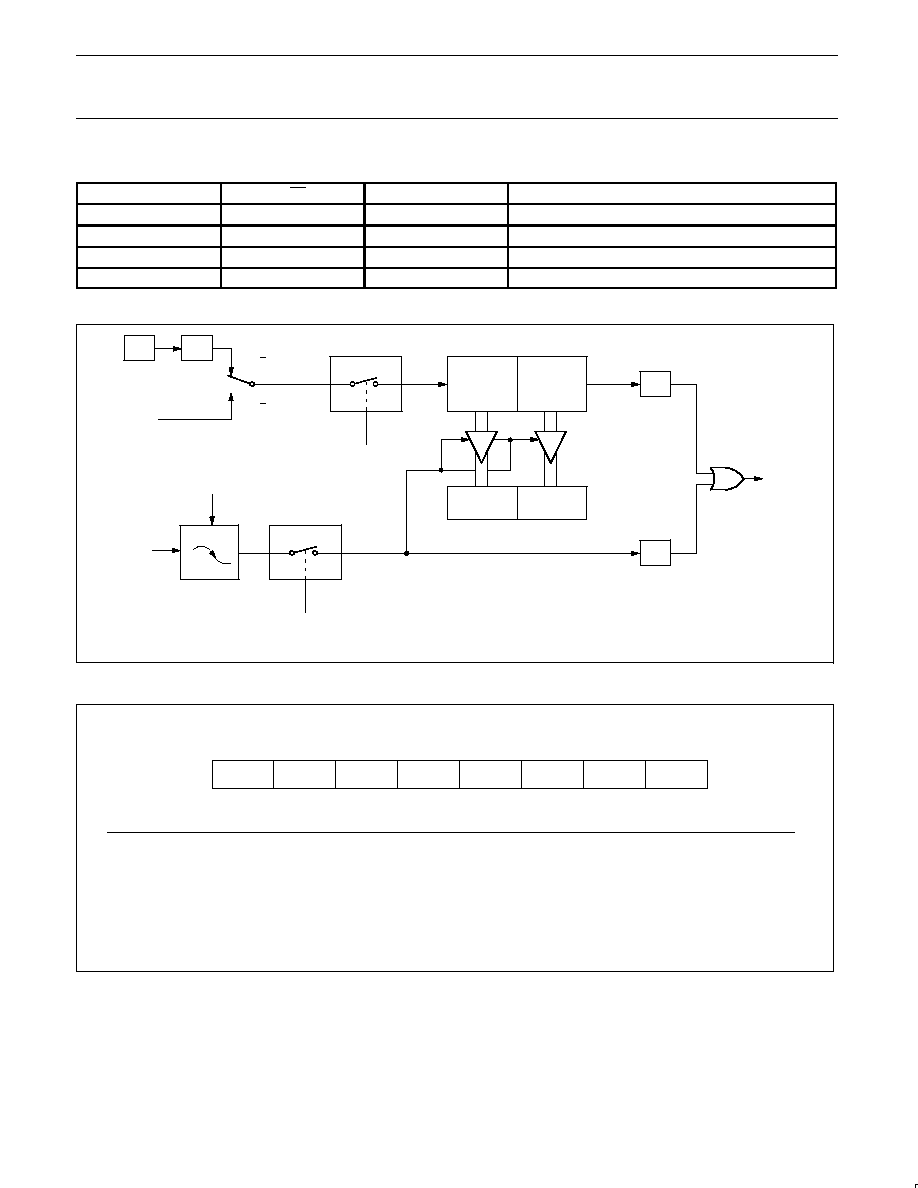

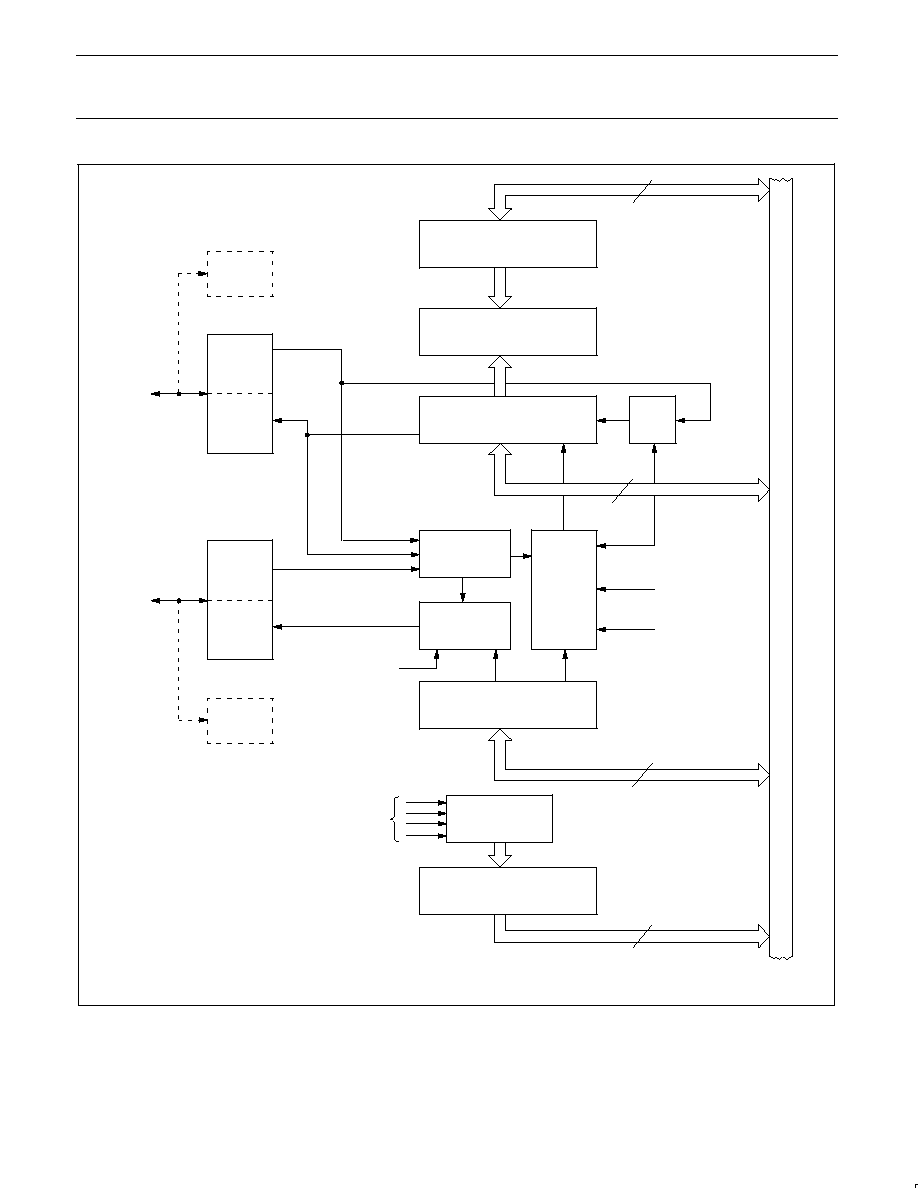

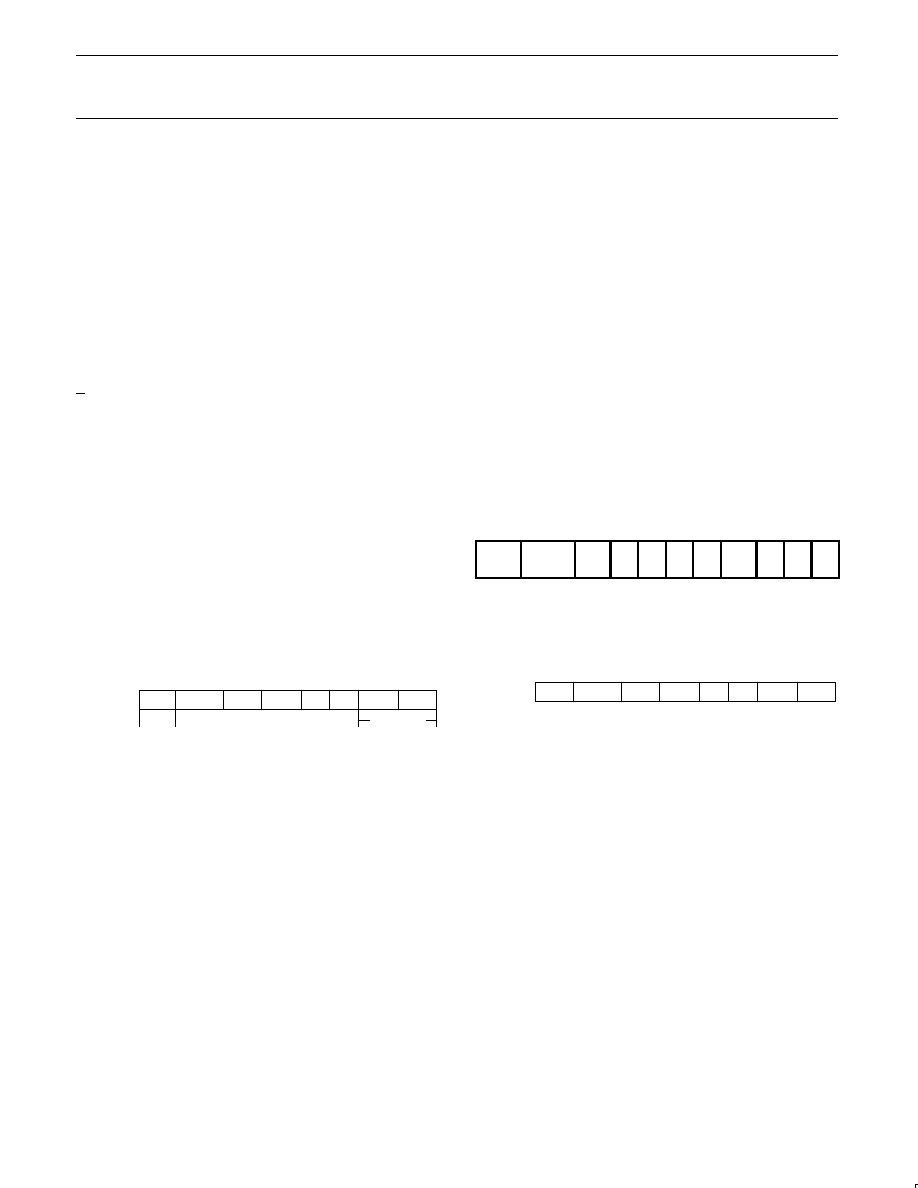

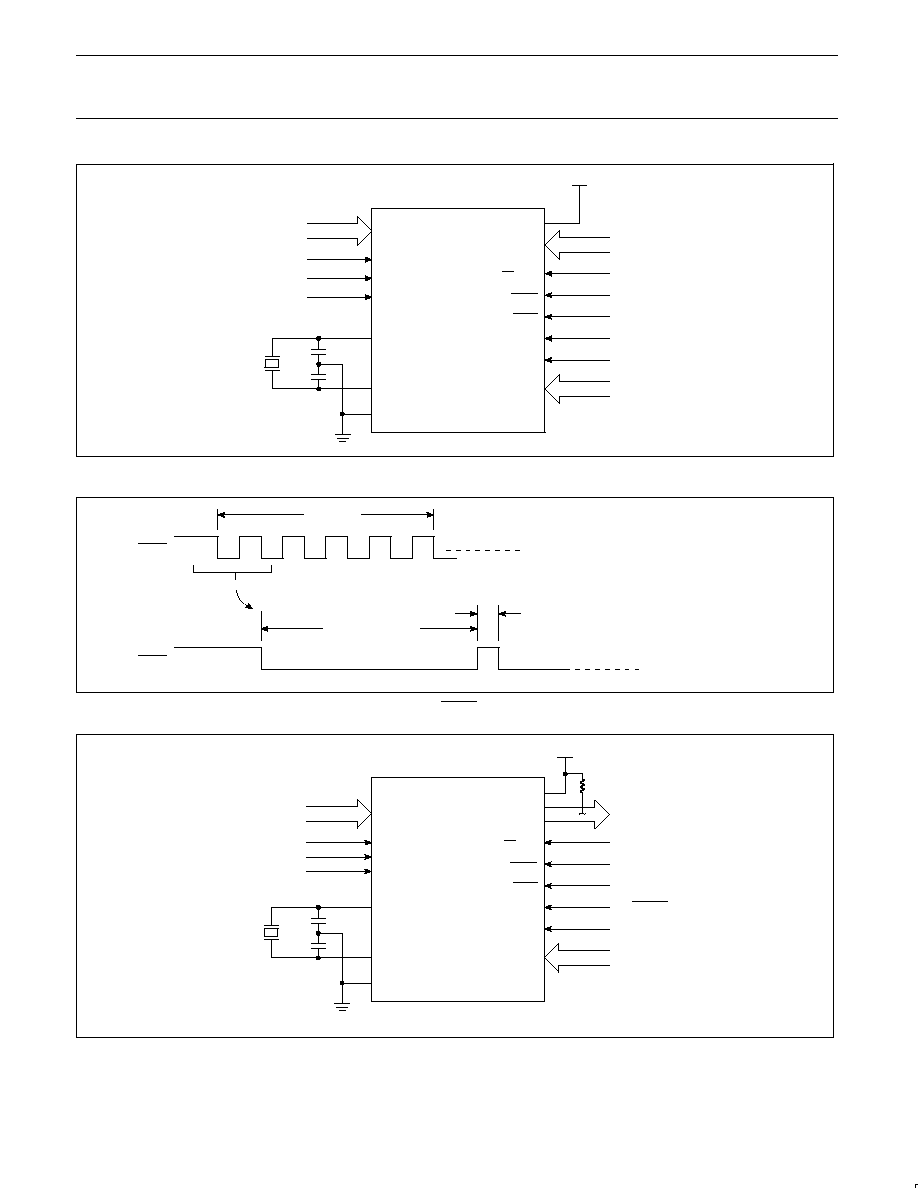

BLOCK DIAGRAM 1

su01728

ACCELERATED 80C51 CPU

(12-CLK MODE, 6-CLK MODE)

16 KB

CODE OTP/ROM

256 BYTE

DATA RAM

PORT 3

CONFIGURABLE I/Os

PORT 2

CONFIGURABLE I/Os

PORT 1

CONFIGURABLE I/Os

PORT 0

CONFIGURABLE I/Os

OSCILLATOR

CRYSTAL OR

RESONATOR

FULL-DUPLEX

ENHANCED UART

TIMER 0

TIMER 1

TIMER 2

WATCHDOG TIMER

FAST I

2

C

Philips Semiconductors

Product data

P83C654X2/P87C654X2

80C51 8-bit microcontroller family

16 kB OTP/ROM,

256B RAM, low voltage (2.7 to 5.5 V), low power, high speed

(30/33 MHz)

2004 Apr 20

4

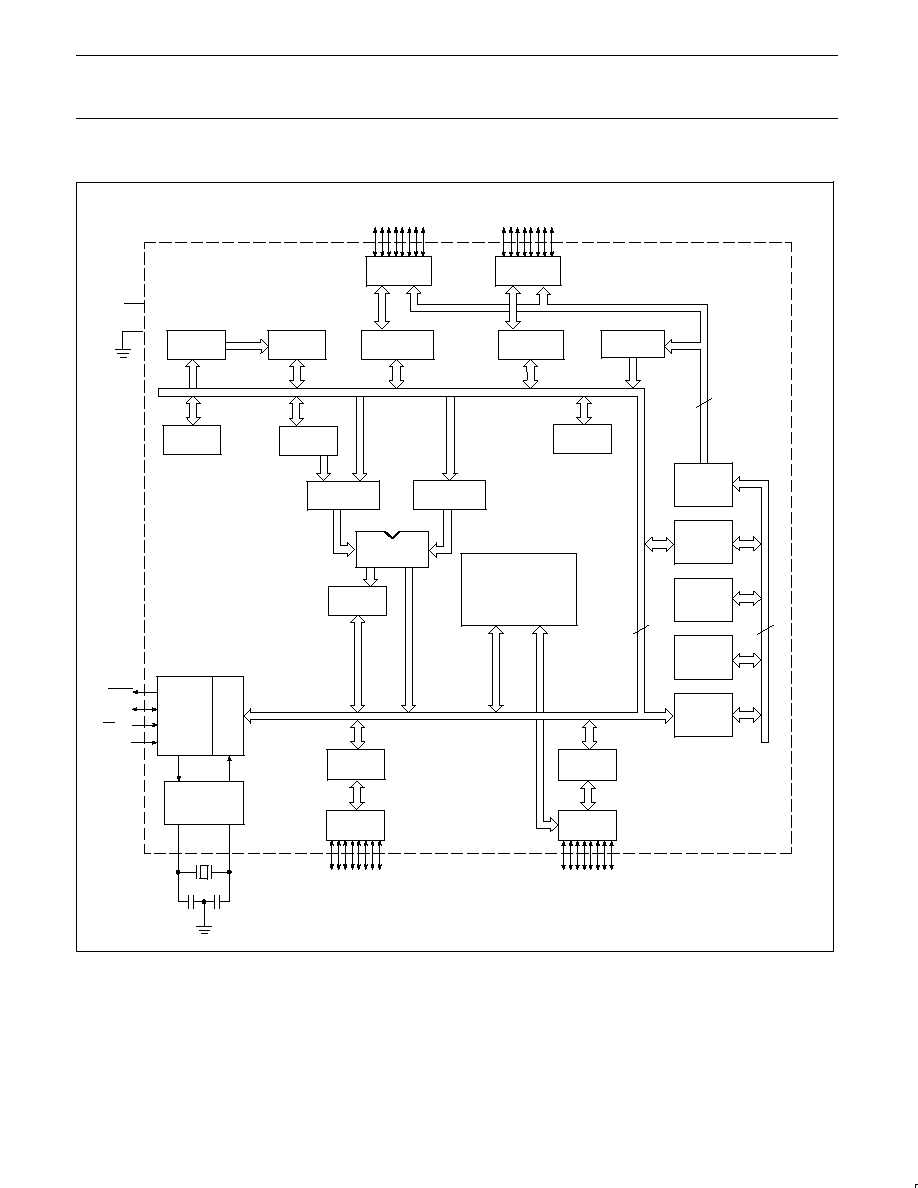

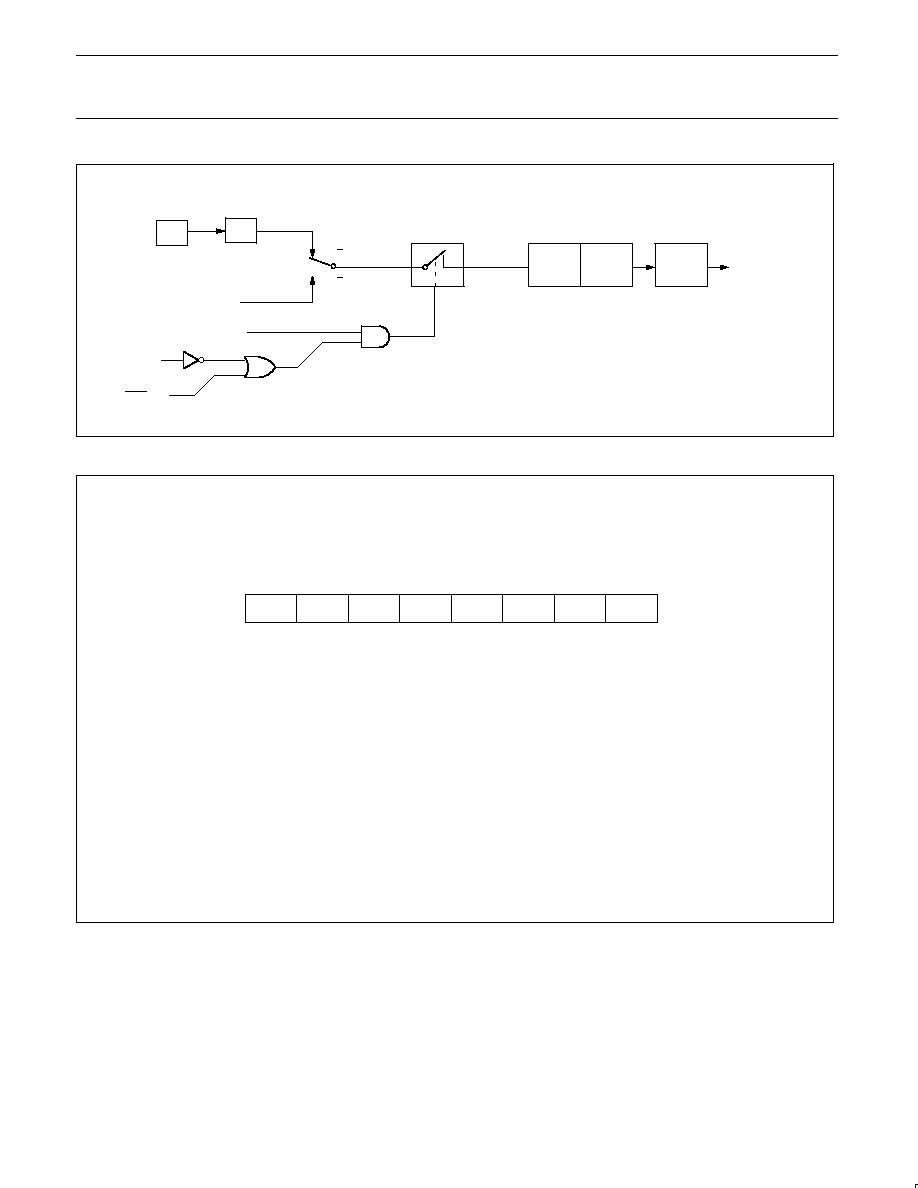

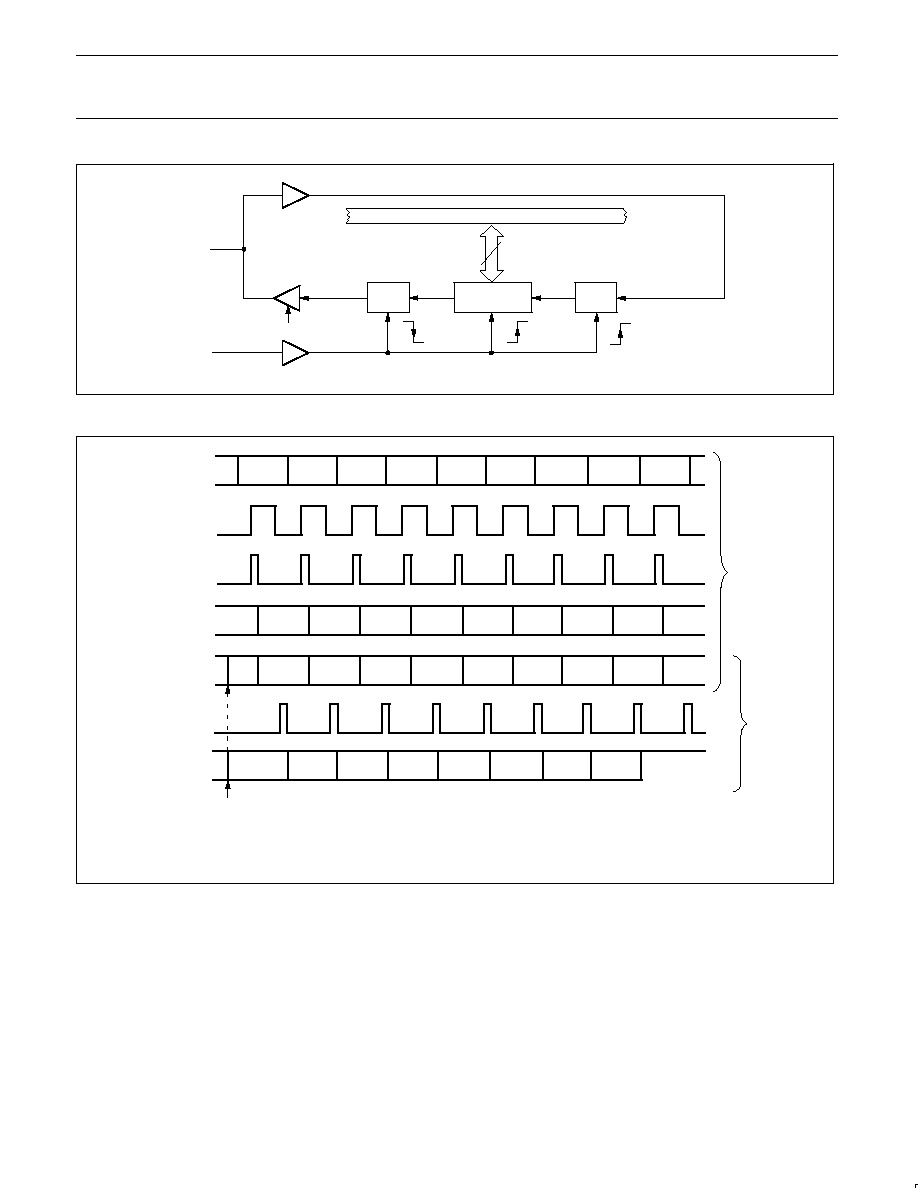

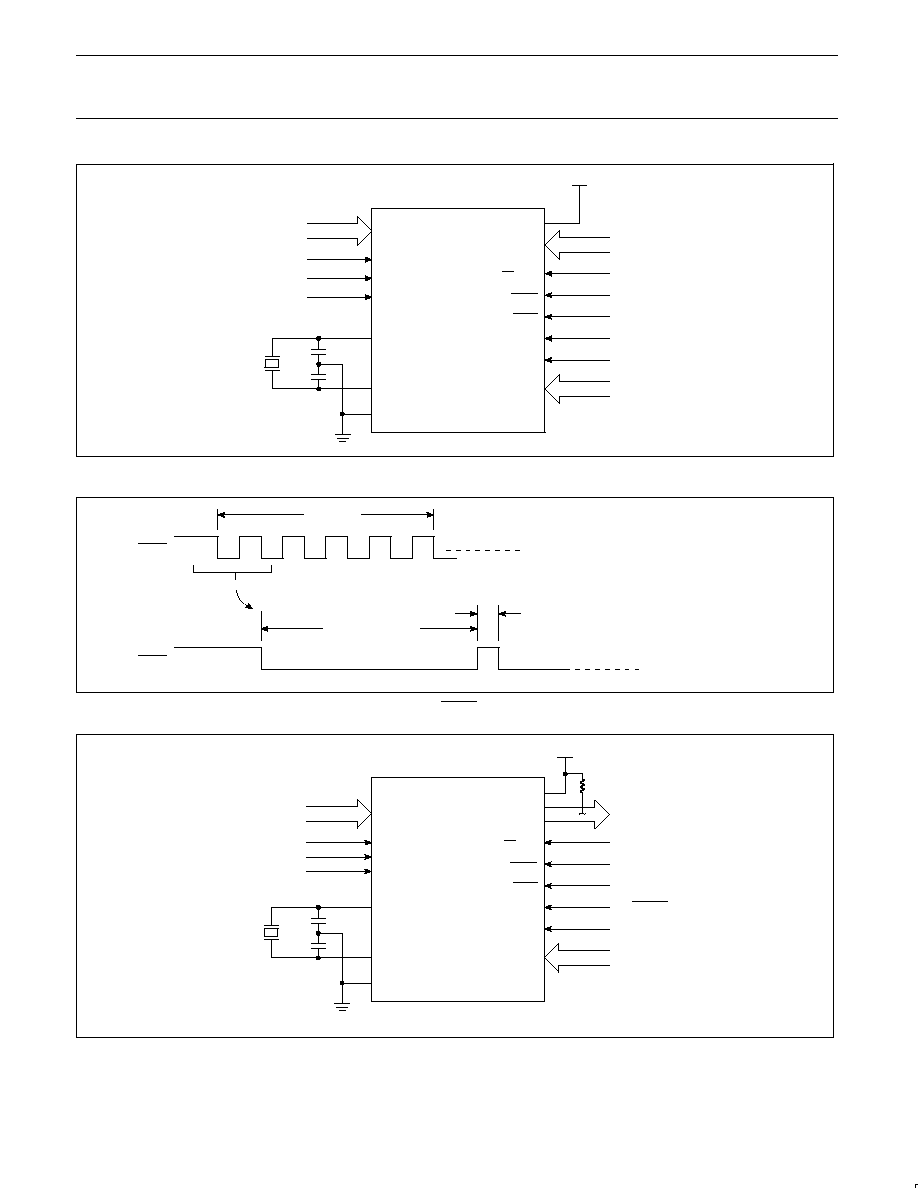

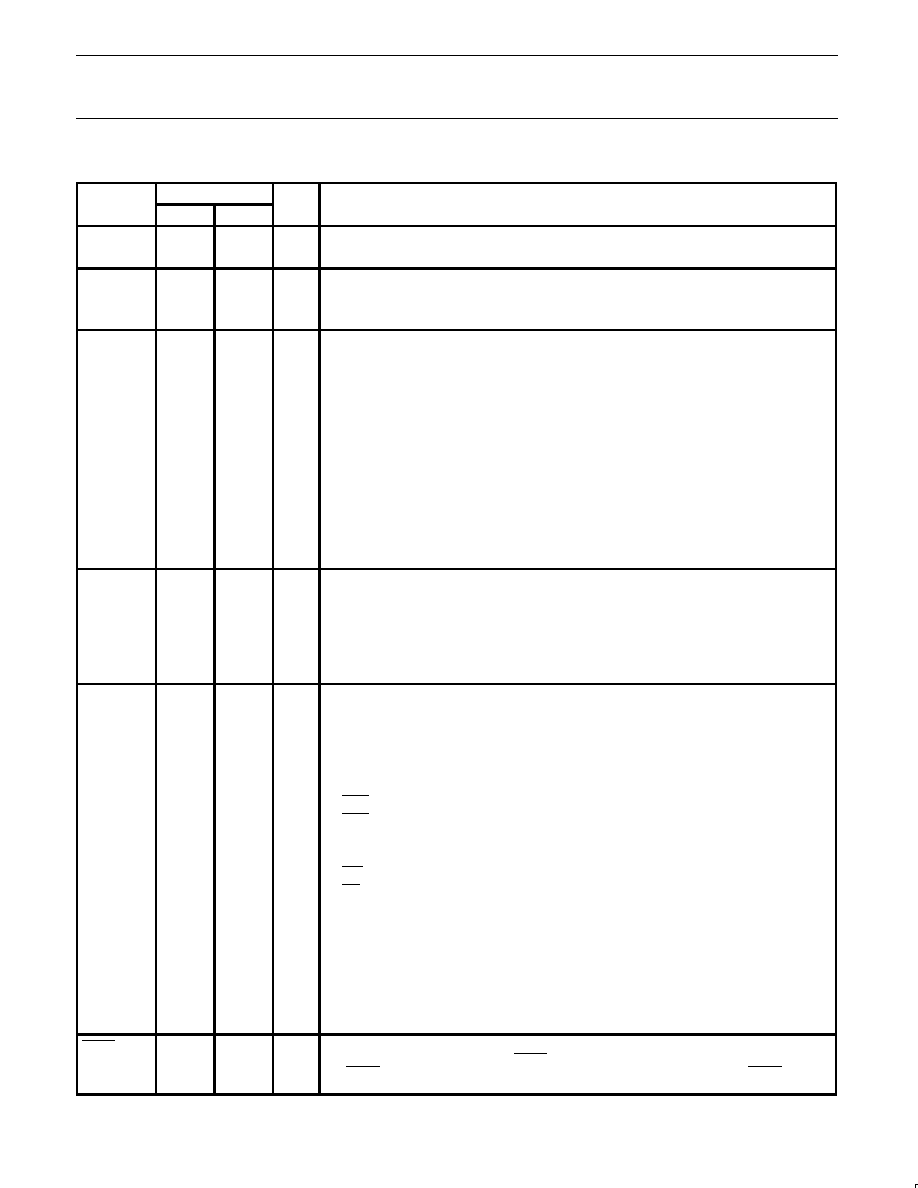

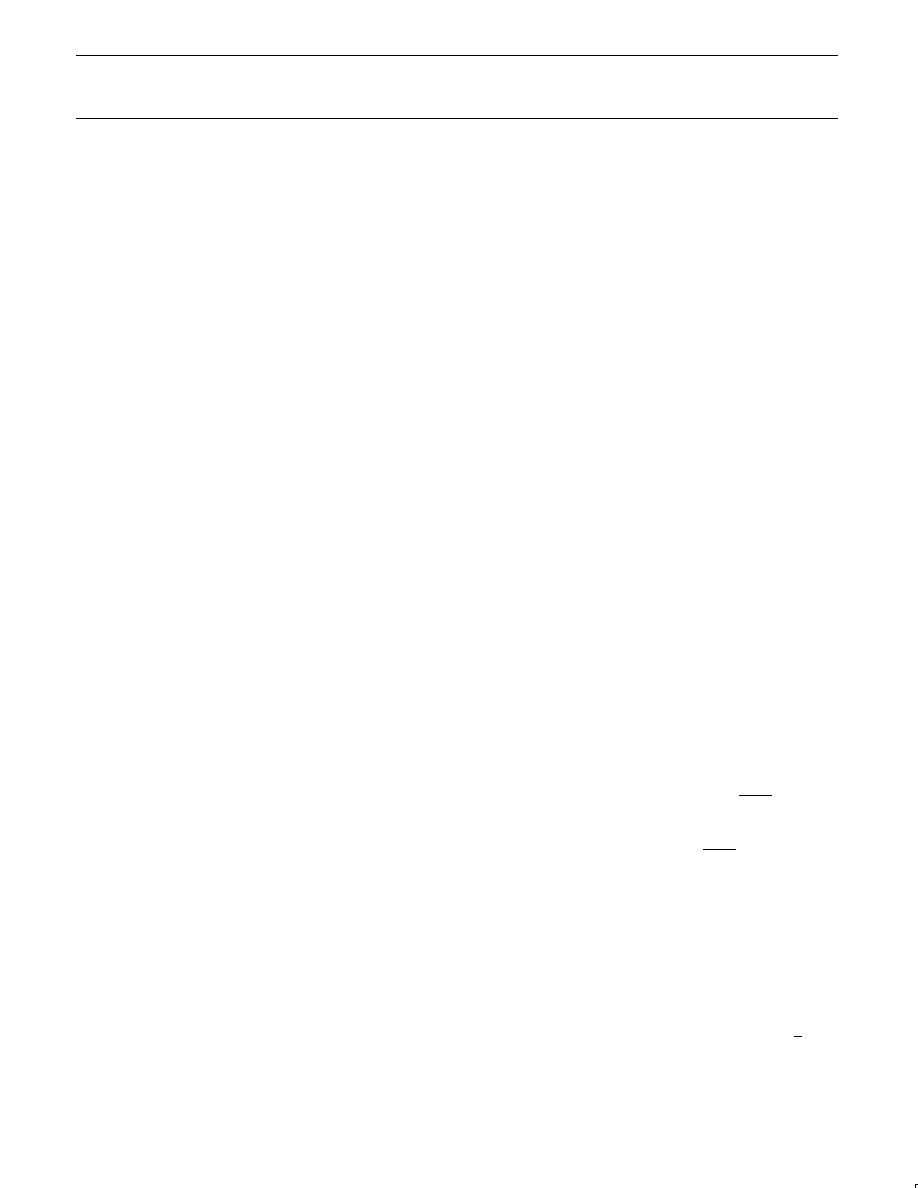

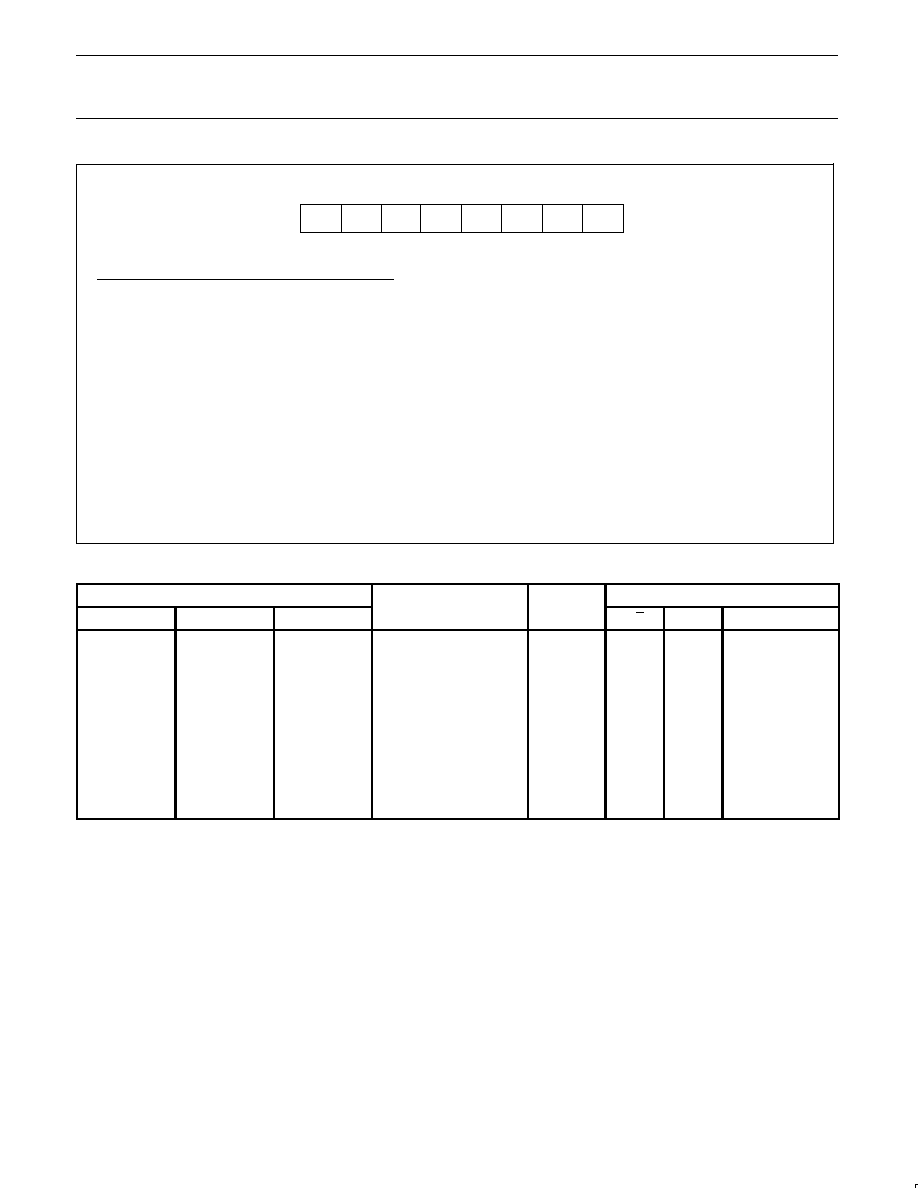

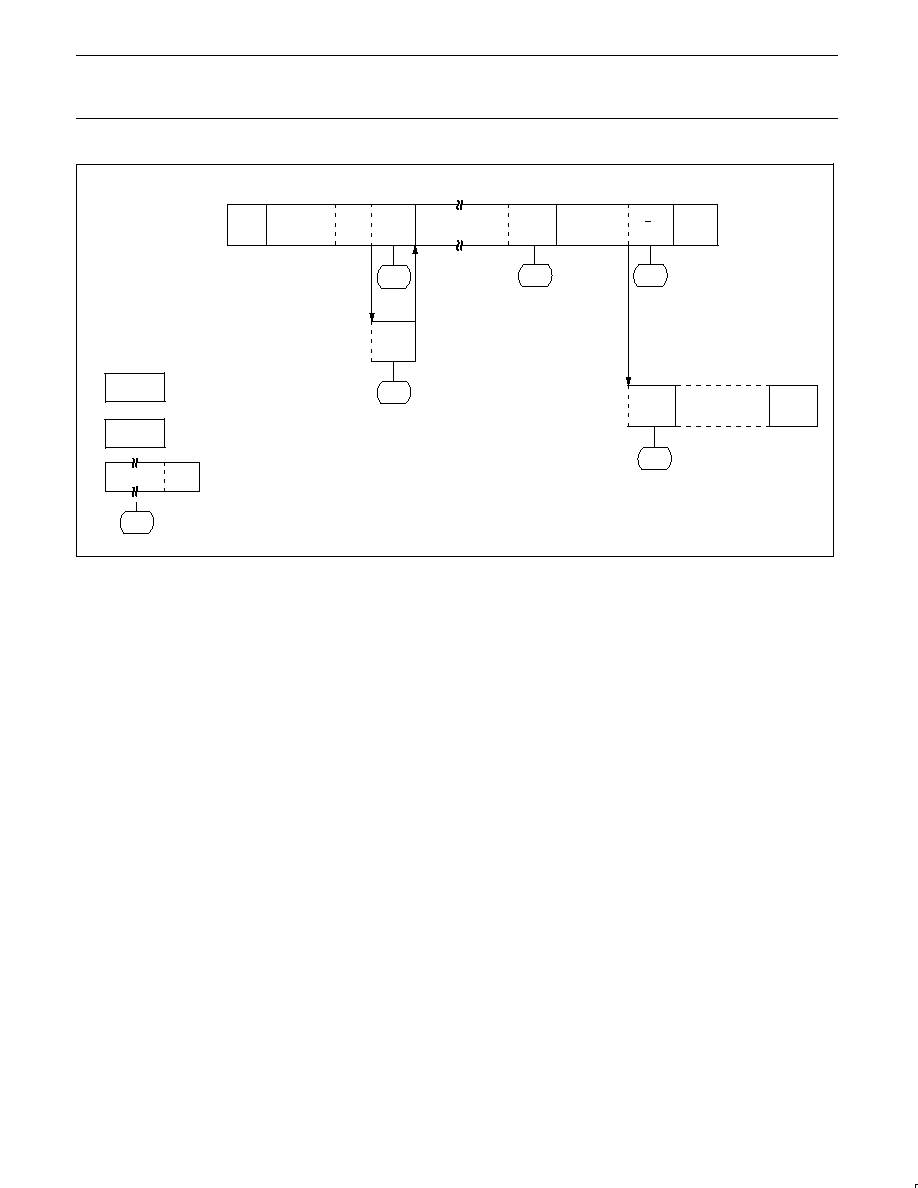

BLOCK DIAGRAM (CPU ORIENTED)

SU01751

PSEN

EAV

PP

ALE

RST

XTAL1

XTAL2

V

CC

V

SS

PORT 0

DRIVERS

PORT 2

DRIVERS

RAM ADDR

REGISTER

RAM

PORT 0

LATCH

PORT 2

LATCH

OTP/ROM

MEMORY

REGISTER

B

ACC

STACK

POINTER

TMP2

TMP1

ALU

TIMING

AND

CONTROL

INSTRUCTION

REGISTER

PD

OSCILLATOR

PSW

PORT 1

LATCH

PORT 3

LATCH

PORT 1

DRIVERS

PORT 3

DRIVERS

PROGRAM

ADDRESS

REGISTER

BUFFER

PC

INCRE-

MENTER

PROGRAM

COUNTER

DPTR'S

MULTIPLE

P1.0≠P1.7

P3.0≠P3.7

P0.0≠P0.7

P2.0≠P2.7

SFRs

TIMERS

P.C.A.

8

8

16

Philips Semiconductors

Product data

P83C654X2/P87C654X2

80C51 8-bit microcontroller family

16 kB OTP/ROM,

256B RAM, low voltage (2.7 to 5.5 V), low power, high speed

(30/33 MHz)

2004 Apr 20

5

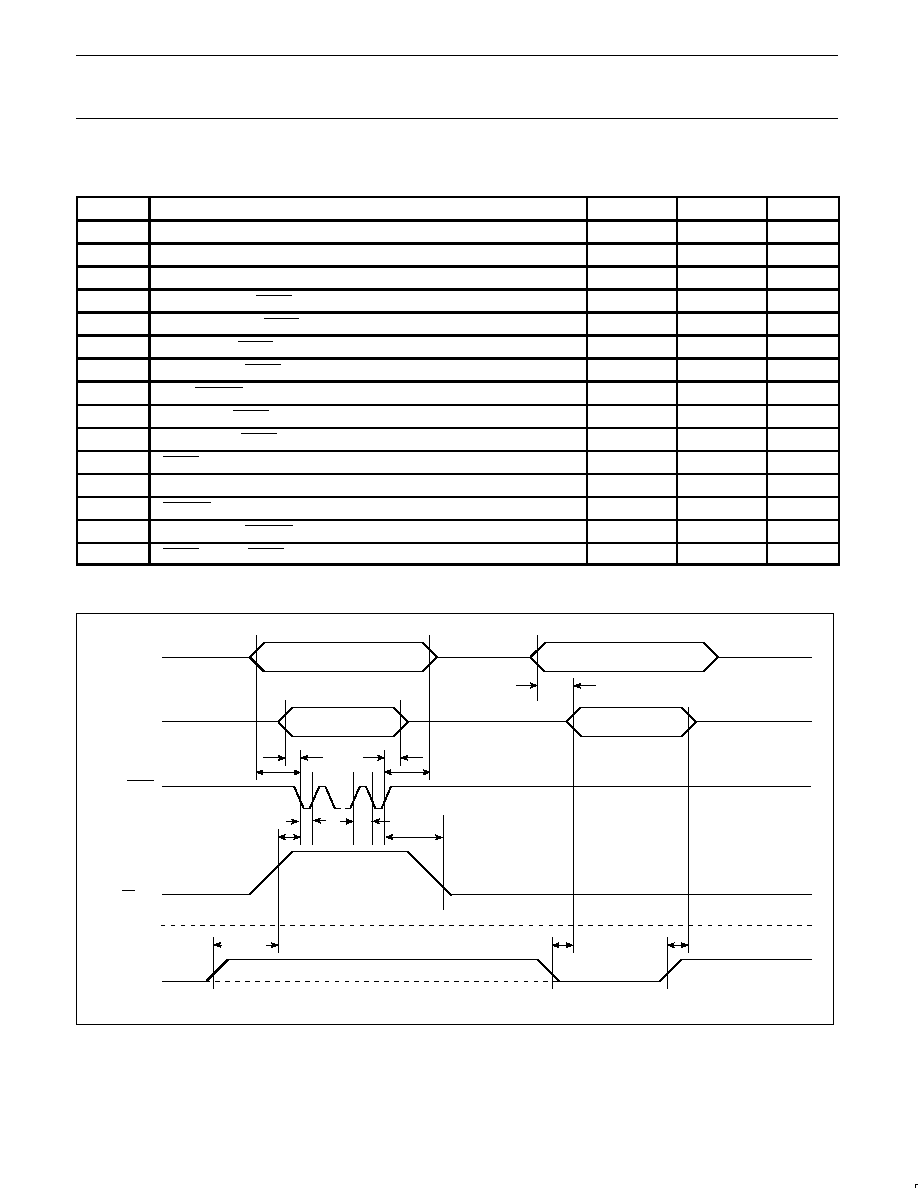

LOGIC SYMBOL

POR

T

0

POR

T

1

POR

T

2

POR

T

3

ADDRESS AND

DATA BUS

ADDRESS BUS

T2

T2EX

RxD

TxD

INT0

INT1

T0

T1

WR

RD

SECONDAR

Y

FUNCTIONS

RST

EA/V

PP

PSEN

ALE/PROG

V

SS

V

CC

XTAL1

XTAL2

SU01730

SCL0

SDA0

SCL1

SDA1

PINNING

Plastic Leaded Chip Carrier

LCC

6

1

40

7

17

39

29

18

28

Pin

Function

1

NIC

1

2

P1.0/T2

3

P1.1/T2EX

4

P1.2/ECI

5

P1.3

6

P1.4

7

P1.5

8

P1.6/SCL0

9

P1.7/SDA0

10

RST

11

P3.0/RxD

12

V

SS3

2

13

P3.1/TxD

14

P3.2/INT0

15

P3.3/INT1

Pin

Function

16

P3.4/T0

17

P3.5/T1

18

P3.6/WR

19

P3.7/RD

20

XTAL2

21

XTAL1

22

V

SS1

23

NIC

1

24

P2.0/A8

25

P2.1/A9

26

P2.2/A10

27

P2.3/A11

28

P2.4/A12

29

P2.5/A13

30

P2.6/A14

Pin

Function

31

P2.7/A15

32

PSEN

33

ALE

34

V

SS2

2

35

EA/V

PP

36

P0.7/AD7

37

P0.6/AD6

38

P0.5/AD5

39

P0.4/AD4

40

P0.3/AD3

41

P0.2/AD2

42

P0.1/AD1

43

P0.0/AD0

44

V

CC

SU01729

1. No internal connection

2. May be left open, but it is recommended that V

SS2

and V

SS3

be

connected to GND to improve EMC performance

Plastic Quad Flat Pack

LQFP

44

34

1

11

33

23

12

22

Pin

Function

1

P1.5

2

P1.6/SCL0

3

P1.7/SDA0

4

RST

5

P3.0/RxD

6

V

SS3

2

7

P3.1/TxD

8

P3.2/INT0

9

P3.3/INT1

10

P3.4/T0

11

P3.5/T1

12

P3.6/WR

13

P3.7/RD

14

XTAL2

15

XTAL1

Pin

Function

16

V

SS1

17

NIC

1

18

P2.0/A8

19

P2.1/A9

20

P2.2/A10

21

P2.3/A11

22

P2.4/A12

23

P2.5/A13

24

P2.6/A14

25

P2.7/A15

26

PSEN

27

ALE

28

V

SS2

2

29

EA/V

PP

30

P0.7/AD7

Pin

Function

31

P0.6/AD6

32

P0.5/AD5

33

P0.4/AD4

34

P0.3/AD3

35

P0.2/AD2

36

P0.1/AD1

37

P0.0/AD0

38

V

CC

39

NIC

1

40

P1.0/T2

41

P1.1/T2EX

42

P1.2/ECI

43

P1.3

44

P1.4

SU01731

1. No internal connection

2. May be left open, but it is recommended that V

SS2

and V

SS3

be

connected to GND to improve EMC performance

Philips Semiconductors

Product data

P83C654X2/P87C654X2

80C51 8-bit microcontroller family

16 kB OTP/ROM,

256B RAM, low voltage (2.7 to 5.5 V), low power, high speed

(30/33 MHz)

2004 Apr 20

6

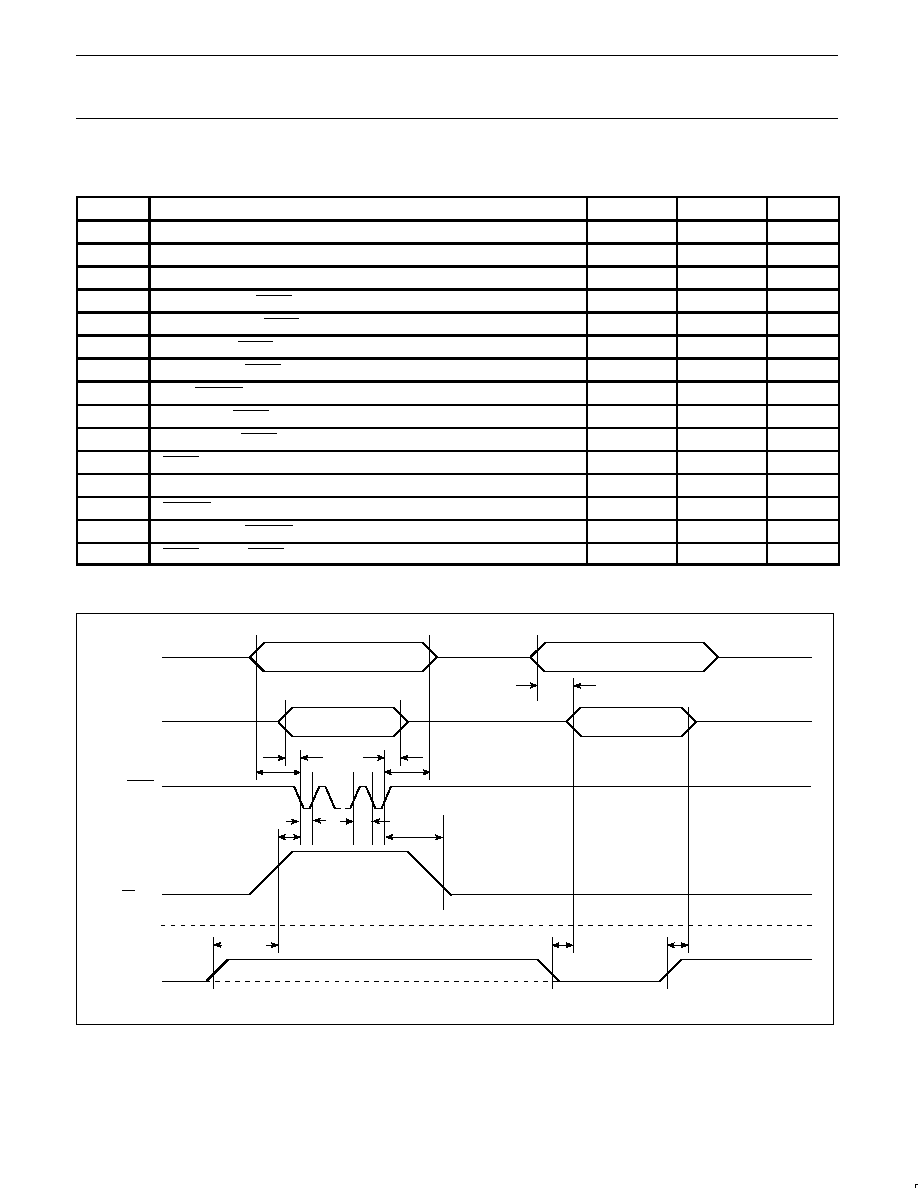

PIN DESCRIPTIONS

MNEMONIC

PIN NUMBER

TYPE

NAME AND FUNCTION

MNEMONIC

PLCC

LQFP

TYPE

NAME AND FUNCTION

V

SS

22

16

I

Ground: 0 V reference.

V

CC

44

38

I

Power Supply: This is the power supply voltage for normal, idle, and power-down operation.

P0.0≠0.7

2

43≠36

37≠30

I/O

Port 0: Port 0 is an open-drain, bidirectional I/O port. Port 0 pins that have 1s written to them

float and can be used as high-impedance inputs. Port 0 is also the multiplexed low-order

address and data bus during accesses to external program and data memory. In this

application, it uses strong internal pull-ups when emitting 1s.

P1.0≠P1.7

2

2≠9

40≠44,

1≠3

I/O

Port 1: Port 1 is an 8-bit bidirectional I/O port with internal pull-ups on all pins. Port 1 pins that

have 1s written to them are pulled HIGH by the internal pull-ups and can be used as inputs. As

inputs, port 1 pins that are externally pulled LOW will source current because of the internal

pull-ups. (See DC Electrical Characteristics: I

IL

).

Alternate functions for P8xC654X2 Port 1 include:

2

40

I/O

T2 (P1.0): Timer/Counter 2 external count input/Clockout (see Programmable Clock-Out)

3

41

I

T2EX (P1.1): Timer/Counter 2 Reload/Capture/Direction Control

3

41

I

4

42

I

5

43

I/O

6

44

I/O

7

1

I/O

8

2

I/O

SCL (P1.6): I

2

C-bus clock line (open drain)

9

3

I/O

SDA (P1.7): I

2

C-bus data line (open drain)

P2.0≠P2.7

2

24≠31

18≠25

I/O

Port 2: Port 2 is an 8-bit bidirectional I/O port with internal pull-ups. Port 2 pins that have 1s

written to them are pulled HIGH by the internal pull-ups and can be used as inputs. As inputs,

port 2 pins that are externally being pulled LOW will source current because of the internal

pull-ups. (See DC Electrical Characteristics: I

IL

). Port 2 emits the high-order address byte

during fetches from external program memory and during accesses to external data memory

that use 16-bit addresses (MOVX @DPTR). In this application, it uses strong internal pull-ups

when emitting 1s. During accesses to external data memory that use 8-bit addresses (MOV

@Ri), port 2 emits the contents of the P2 special function register.

P3.0≠P3.7

2

11,

13≠19

5, 7≠13

I/O

Port 3: Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins that have 1s

written to them are pulled HIGH by the internal pull-ups and can be used as inputs. As inputs,

port 3 pins that are externally being pulled LOW will source current because of the pull-ups.

(See DC Electrical Characteristics: I

IL

). Port 3 also serves the special features of the

P8xC654X2, as listed below:

11

5

I

RxD (P3.0): Serial input port

13

7

O

TxD (P3.1): Serial output port

14

8

I

INT0 (P3.2): External interrupt 0

15

9

I

INT1 (P3.3): External interrupt 1

16

10

I

T0 (P3.4): Timer 0 external input

17

11

I

T1 (P3.5): Timer 1 external input

18

12

O

WR (P3.6): External data memory write strobe

19

13

O

RD (P3.7): External data memory read strobe

RST

2

10

4

I

Reset: A HIGH on this pin for two machine cycles while the oscillator is running, resets the

device. An internal diffused resistor to V

SS

permits a power-on reset using only an external

capacitor to V

CC

.

ALE

2

33

27

O

Address Latch Enable: Output pulse for latching the LOW byte of the address during an

access to external memory. In normal operation, ALE is emitted at constant rate of 1/6 the

oscillator frequency in 12x clock mode, 1/3 the oscillator frequency in 6x clock mode, and can

be used for external timing or clocking. Note that one ALE pulse is skipped during each access

to external data memory. ALE can be disabled by setting SFR auxiliary.0. With this bit set, ALE

will be active only during a MOVX instruction.

PSEN

2

32

26

O

Program Store Enable: The read strobe to external program memory. When executing code

from the external program memory, PSEN is activated twice each machine cycle, except that

two PSEN activations are skipped during each access to external data memory. PSEN is not

activated during fetches from internal program memory.

Philips Semiconductors

Product data

P83C654X2/P87C654X2

80C51 8-bit microcontroller family

16 kB OTP/ROM,

256B RAM, low voltage (2.7 to 5.5 V), low power, high speed

(30/33 MHz)

2004 Apr 20

7

MNEMONIC

NAME AND FUNCTION

TYPE

PIN NUMBER

MNEMONIC

NAME AND FUNCTION

TYPE

LQFP

PLCC

EA

2

35

29

I

External Access Enable/Programming Supply Voltage: EA must be externally held LOW to

enable the device to fetch code from external program memory. The value on the EA pin is

latched when RST is released and any subsequent changes have no effect.

XTAL1

21

15

I

Crystal 1: Input to the inverting oscillator amplifier and input to the internal clock generator

circuits.

XTAL2

20

14

O

Crystal 2: Output from the inverting oscillator amplifier.

NOTES:

1. To avoid "latch-up" effect at power-on, the voltage on any pin (other than EA) at any time must not be higher than V

CC

+ 0.5 V or less than

V

SS

≠ 0.5 V, respectively.

2. The pins are designed for test mode also.

Philips Semiconductors

Product data

P83C654X2/P87C654X2

80C51 8-bit microcontroller family

16 kB OTP/ROM,

256B RAM, low voltage (2.7 to 5.5 V), low power, high speed

(30/33 MHz)

2004 Apr 20

8

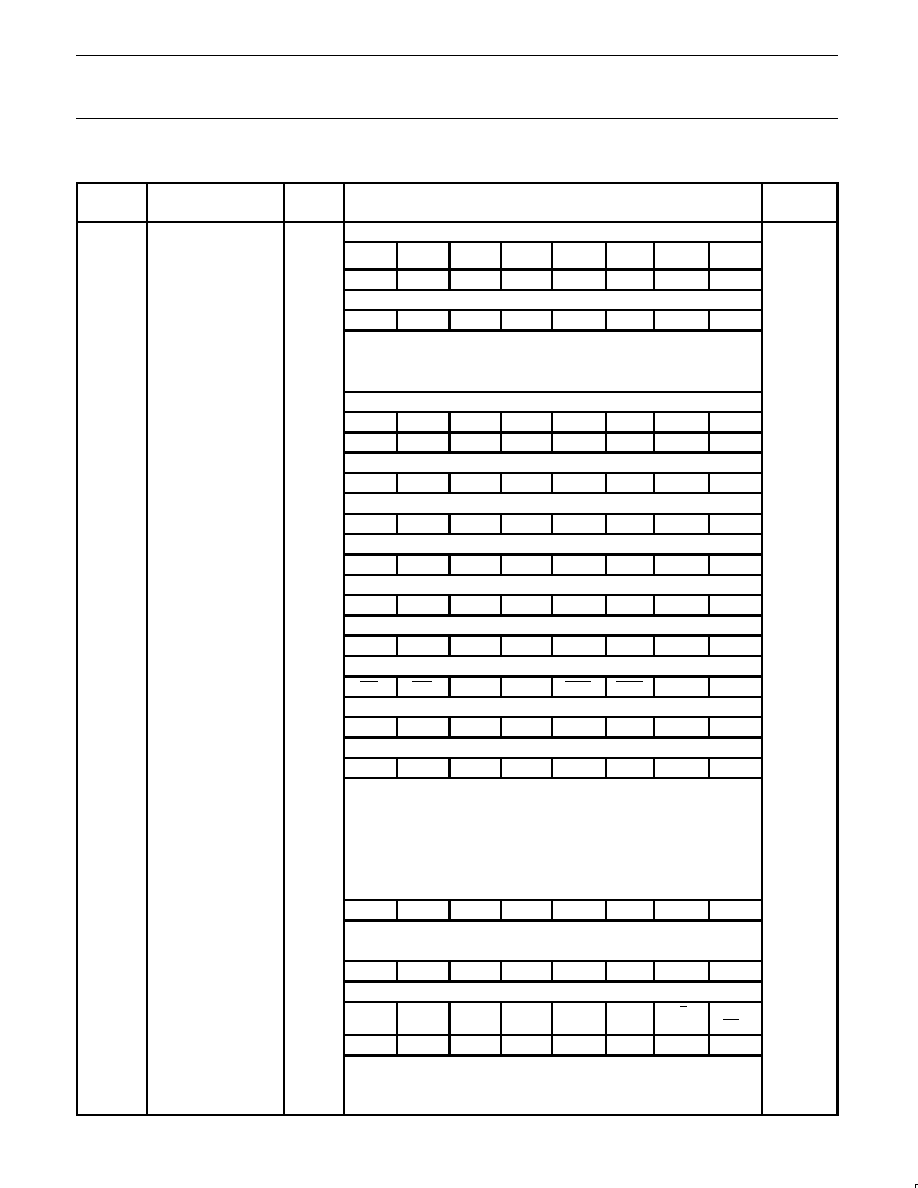

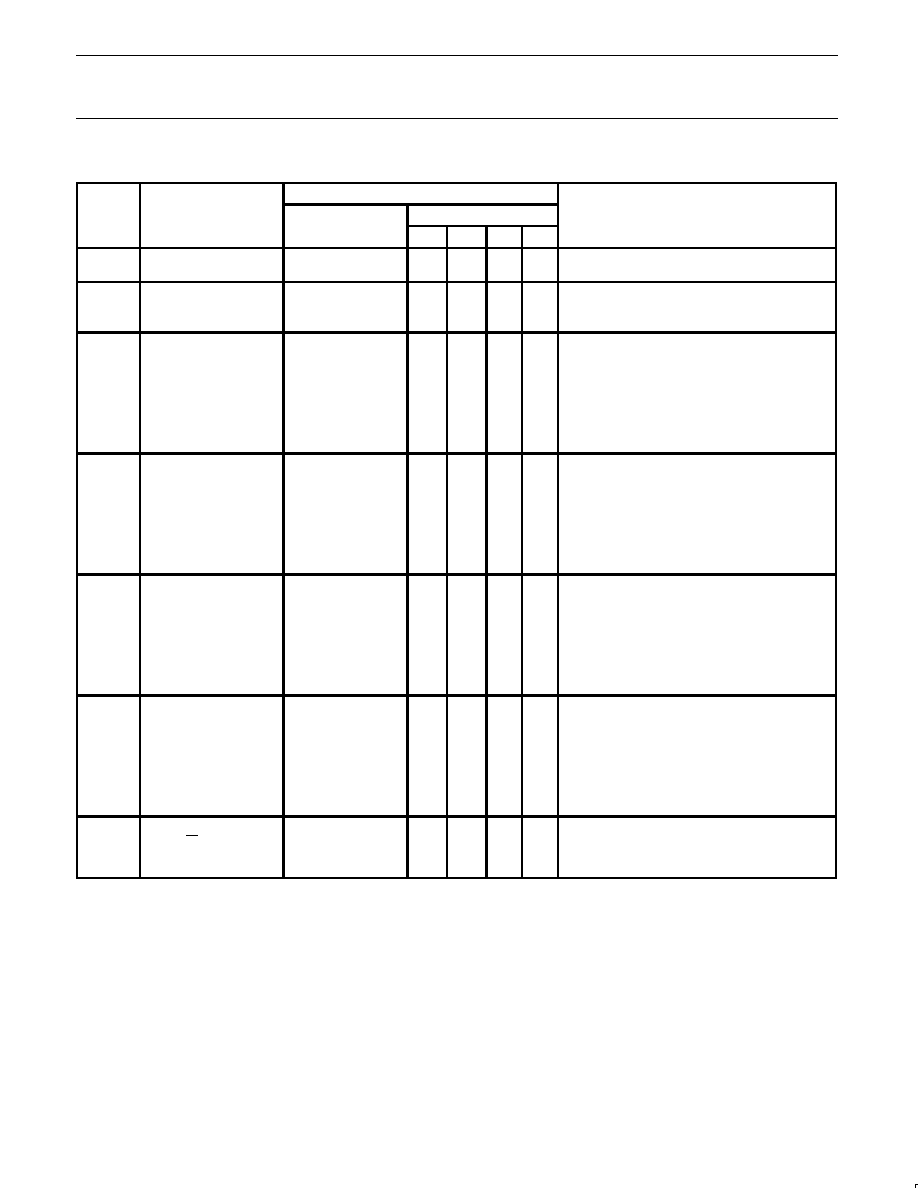

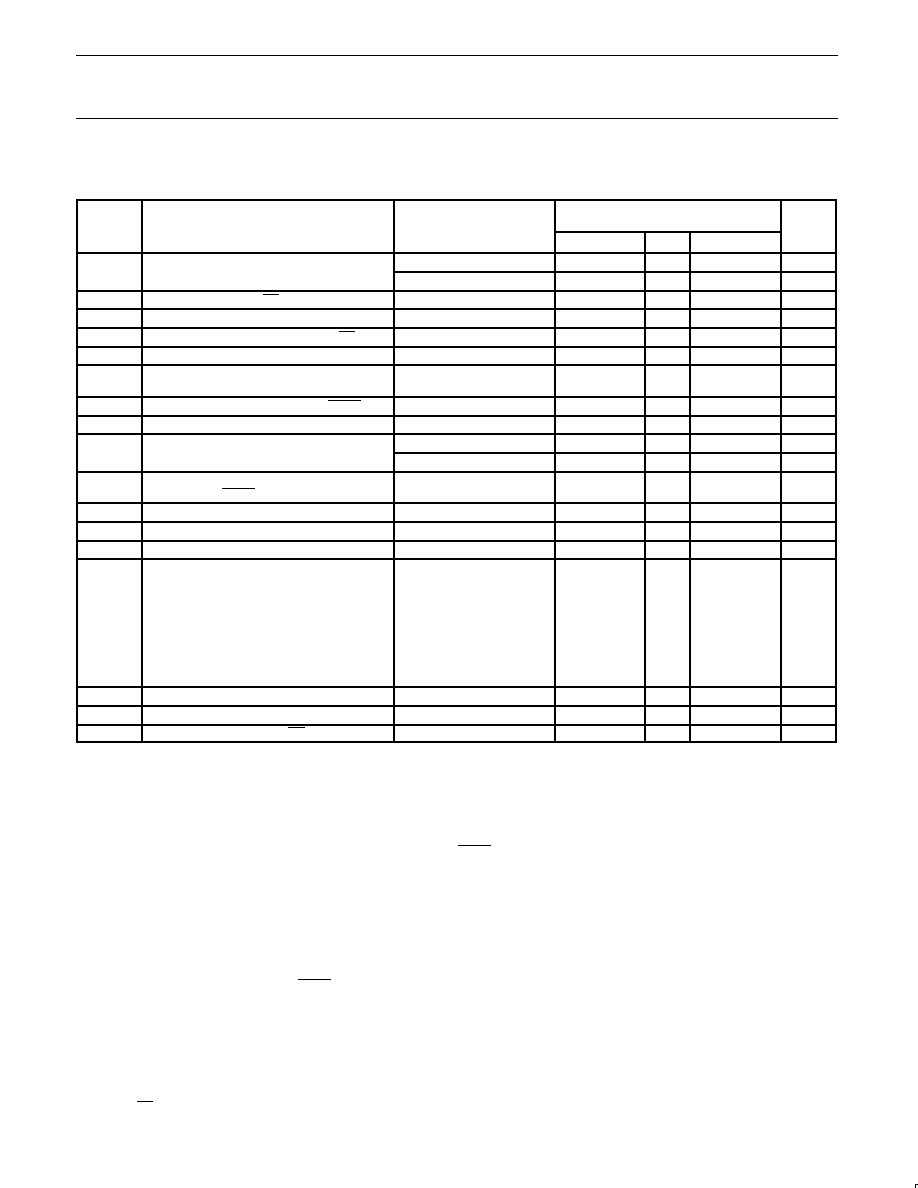

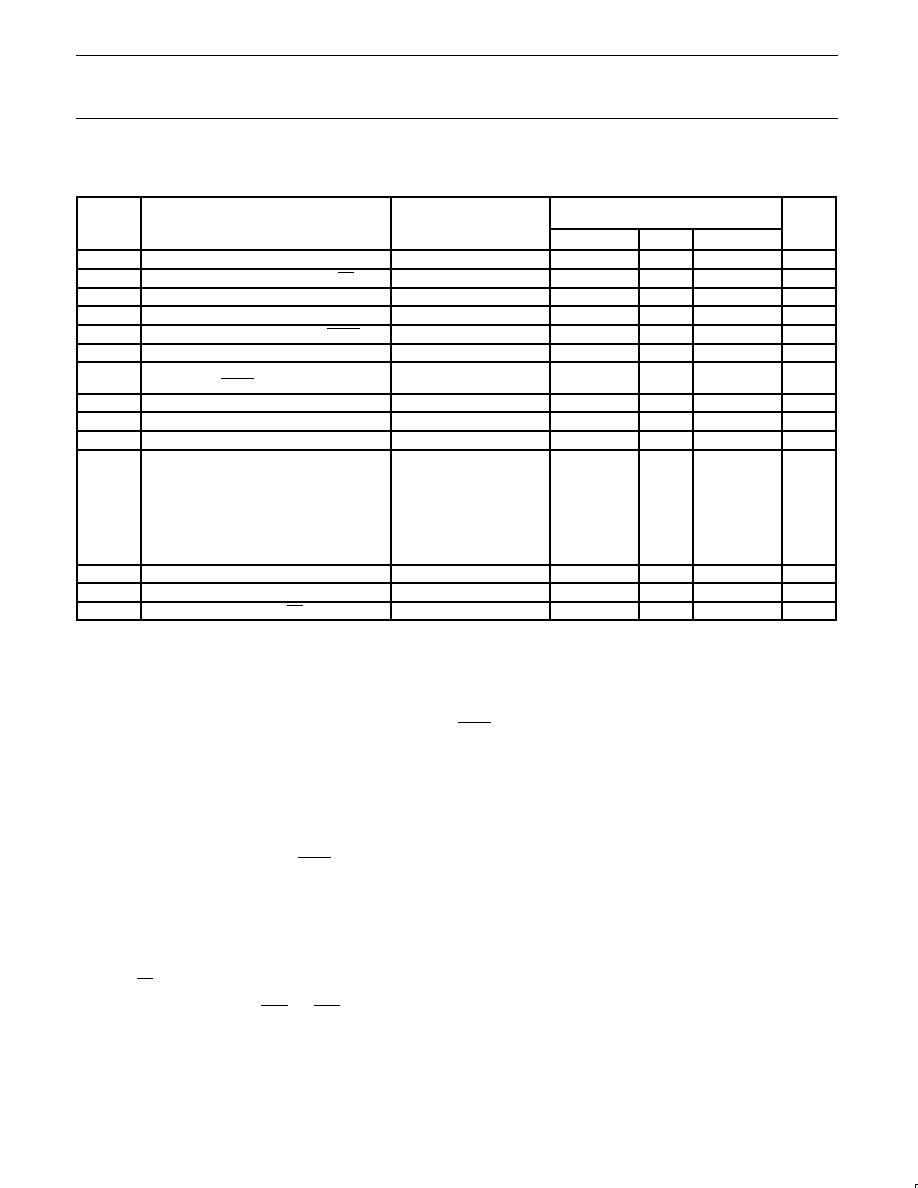

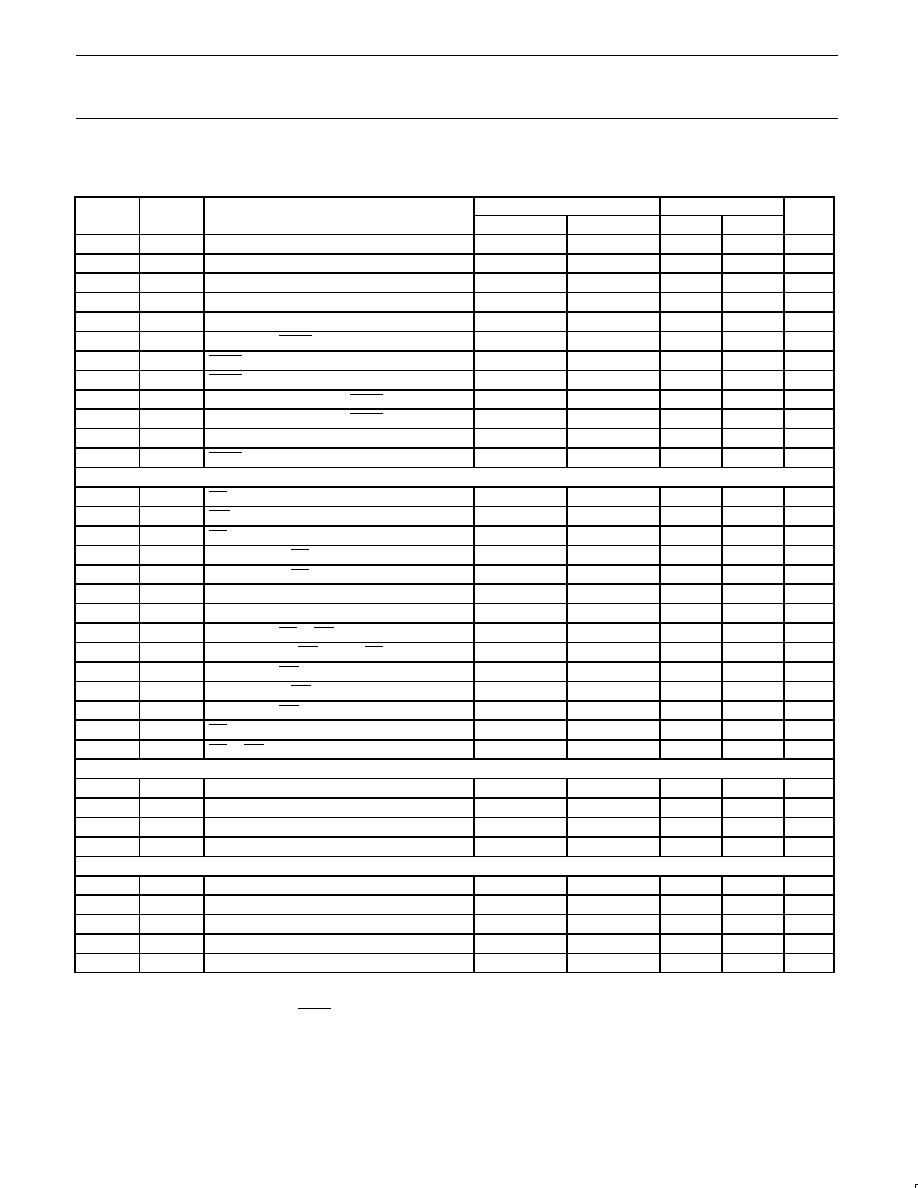

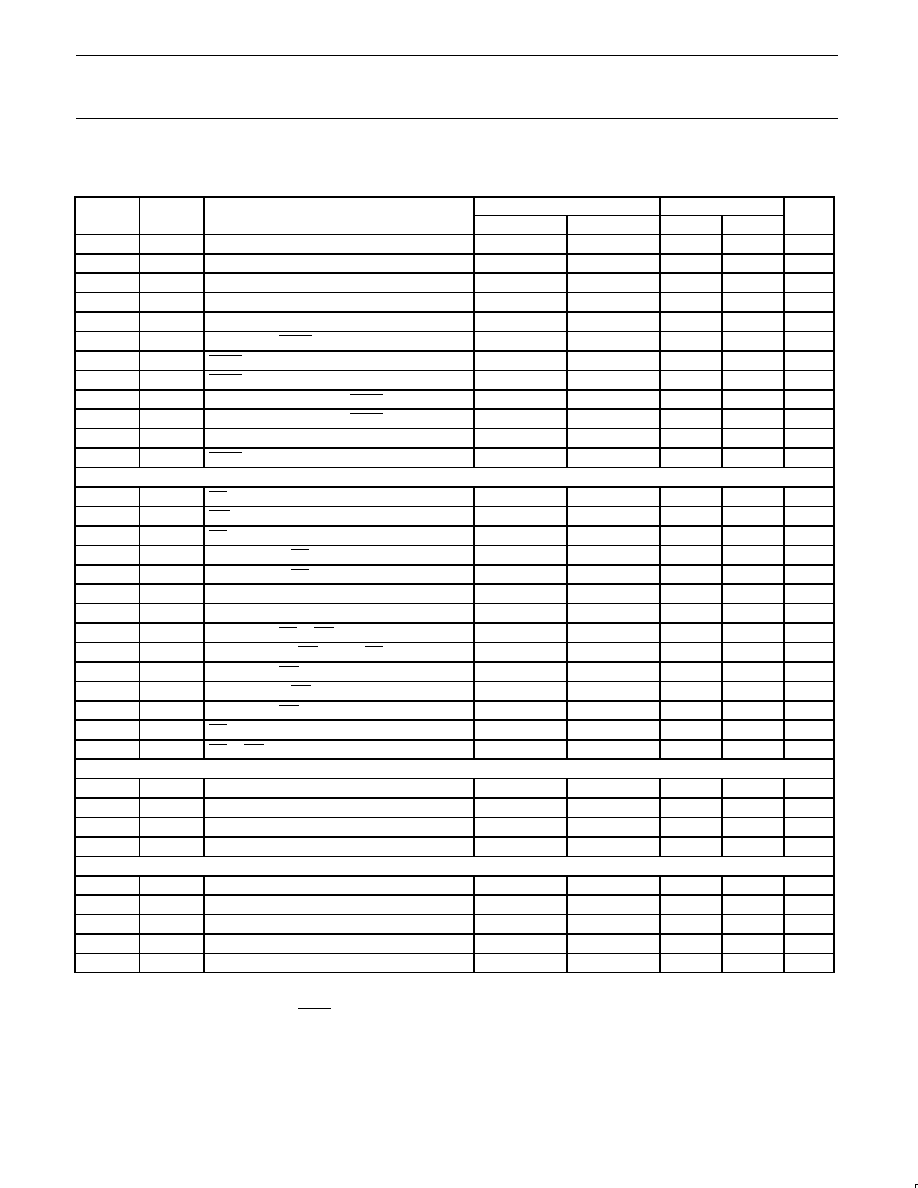

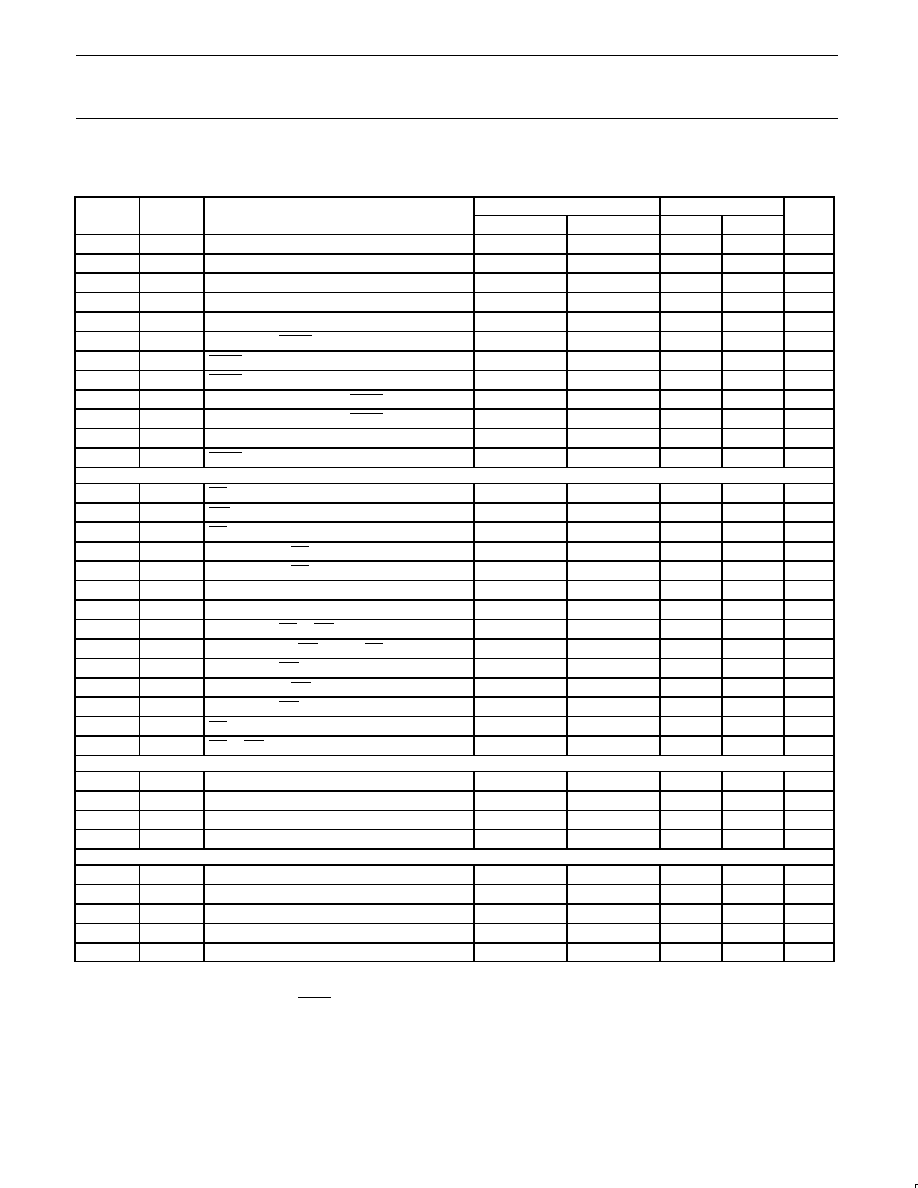

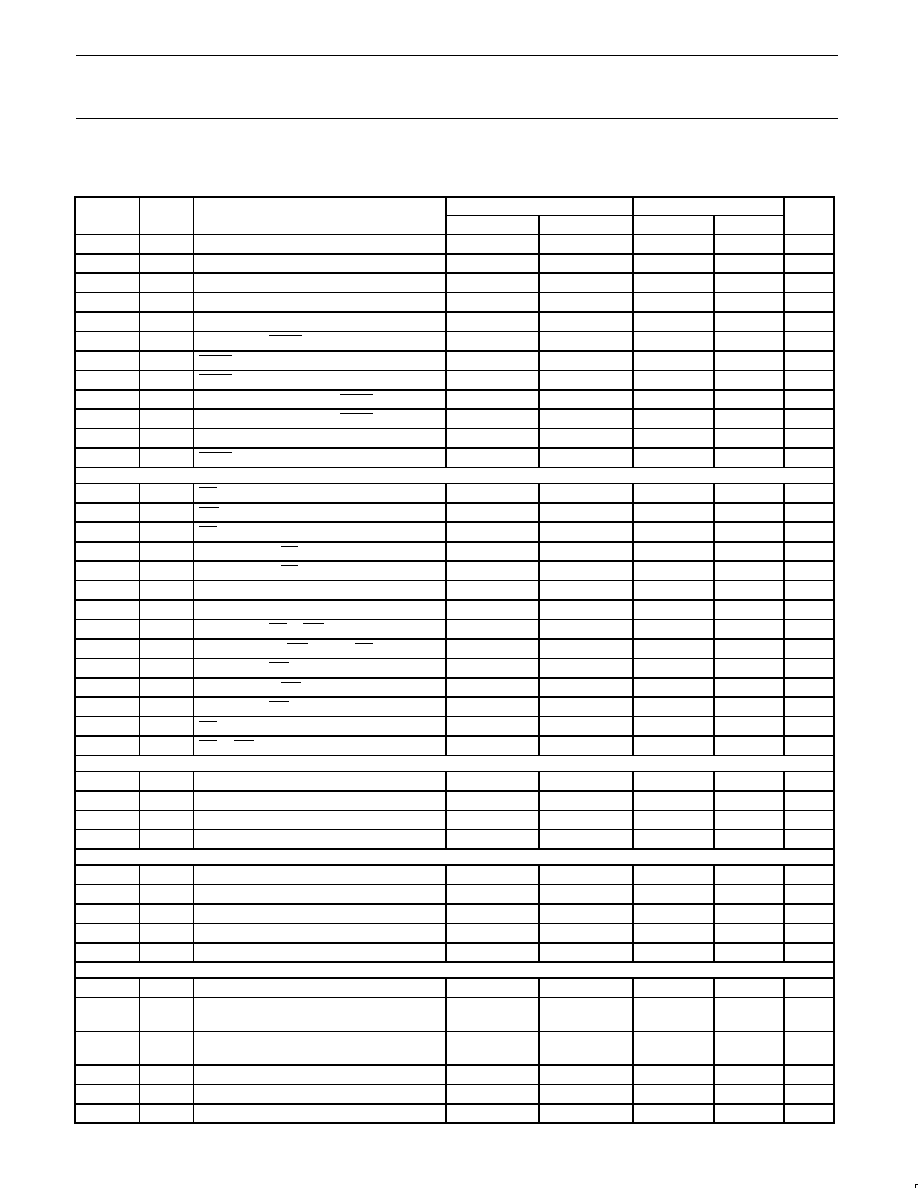

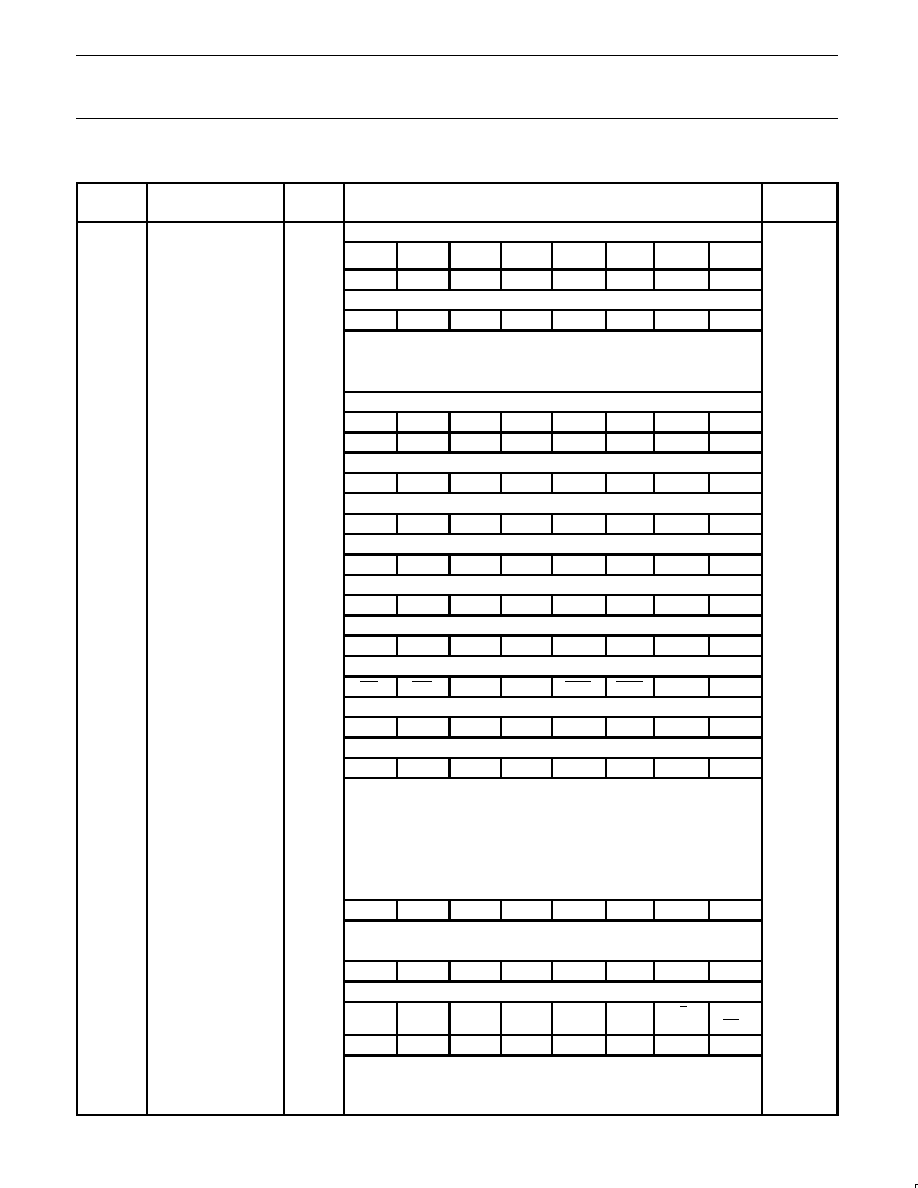

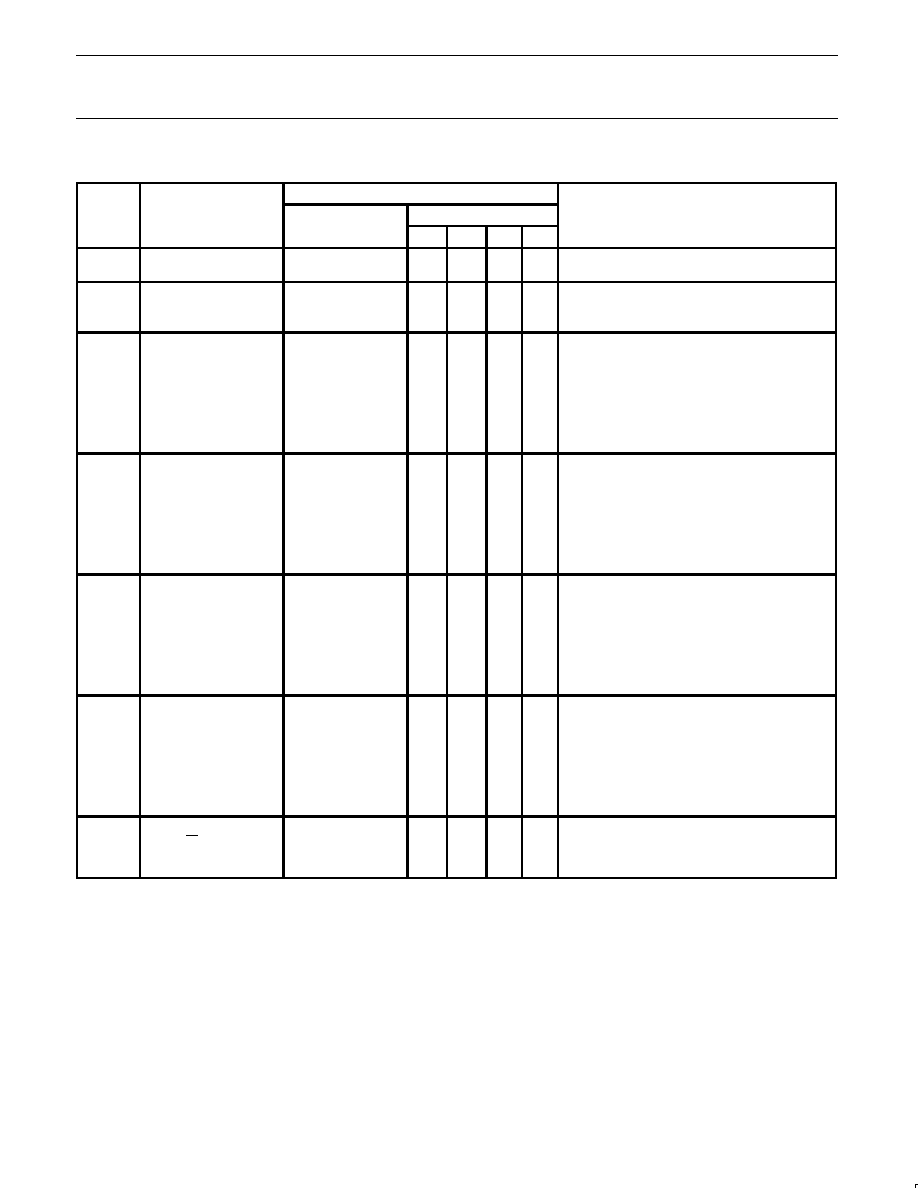

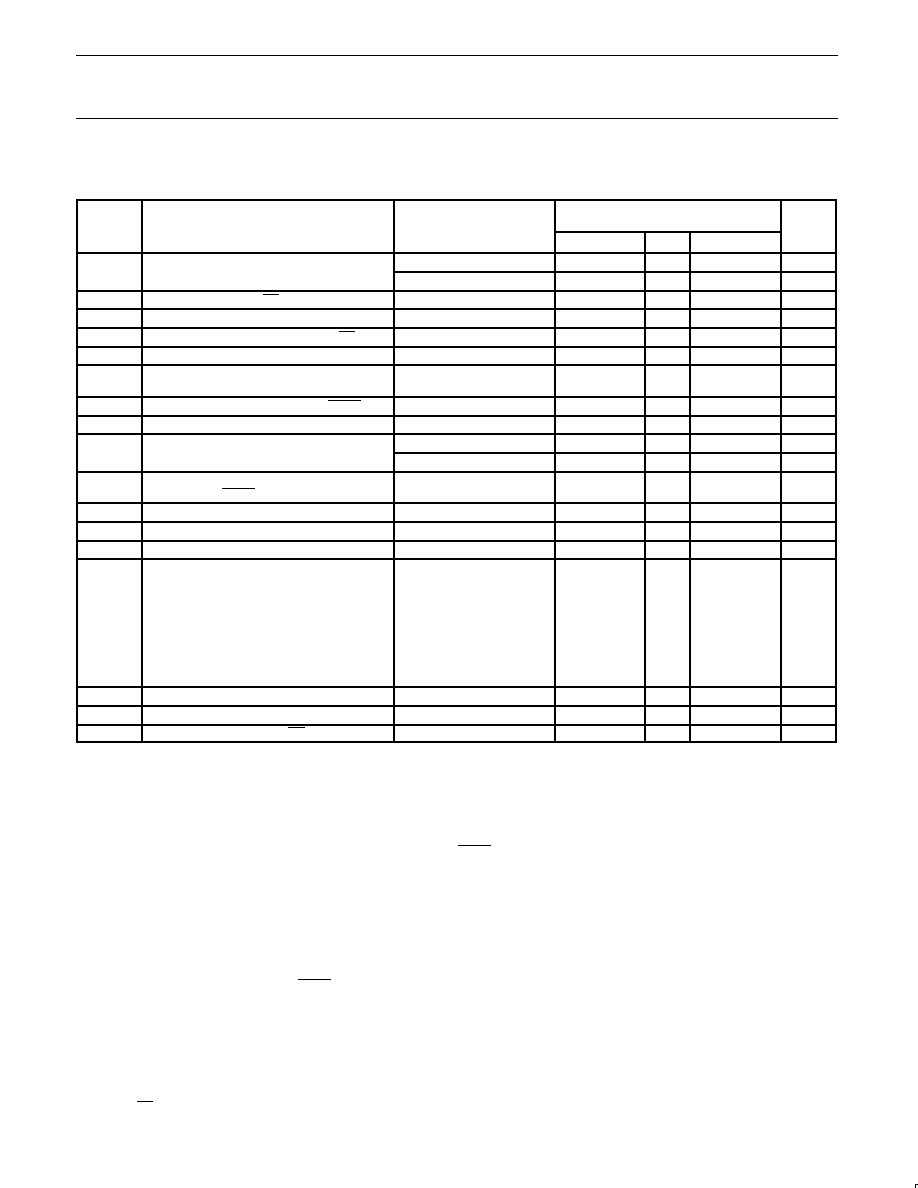

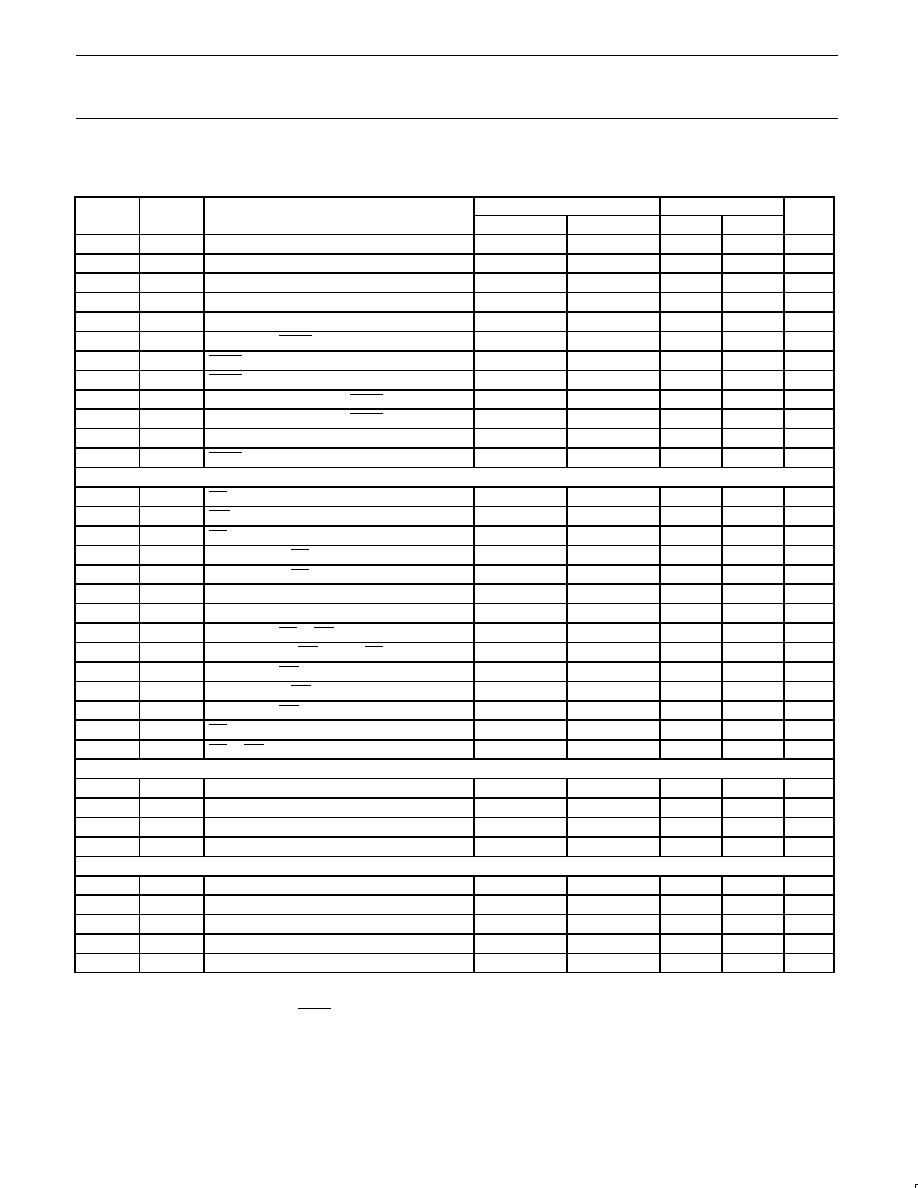

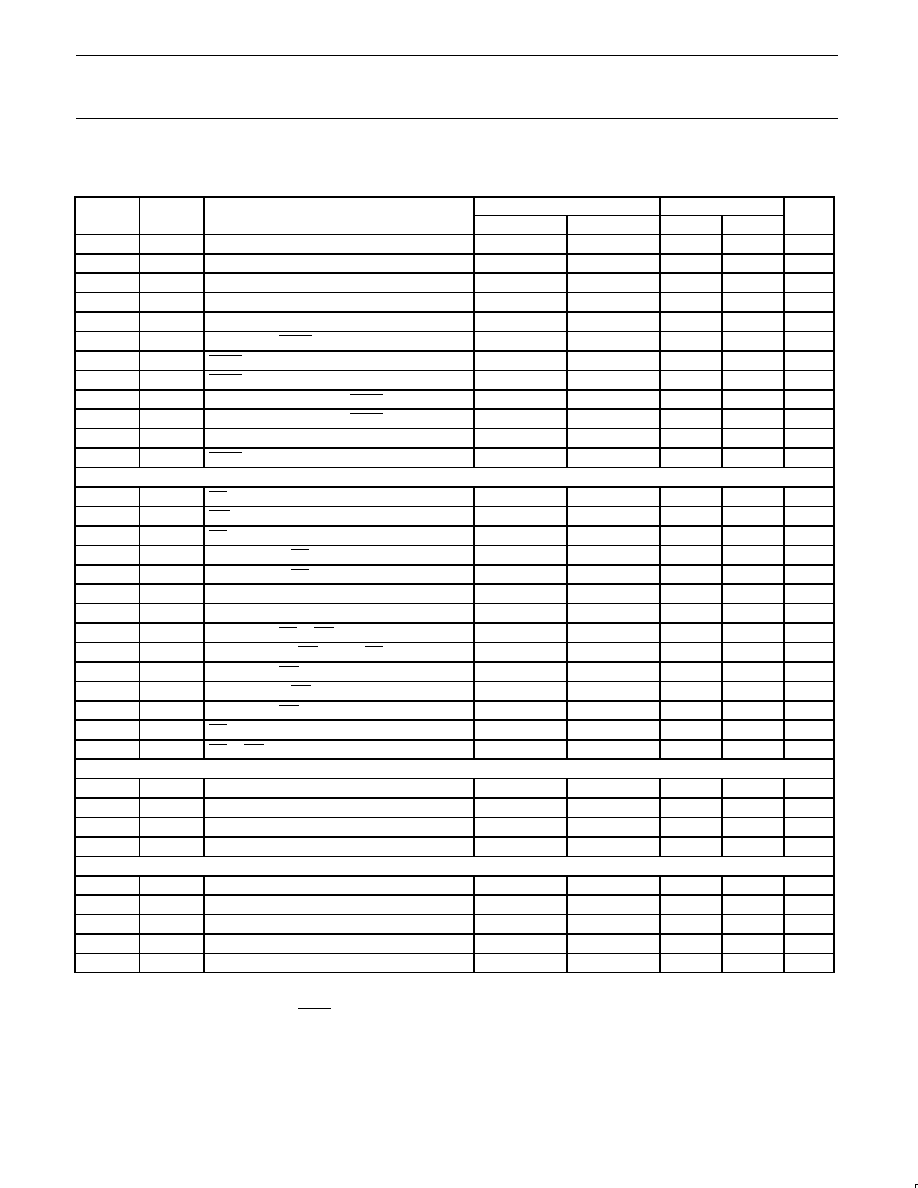

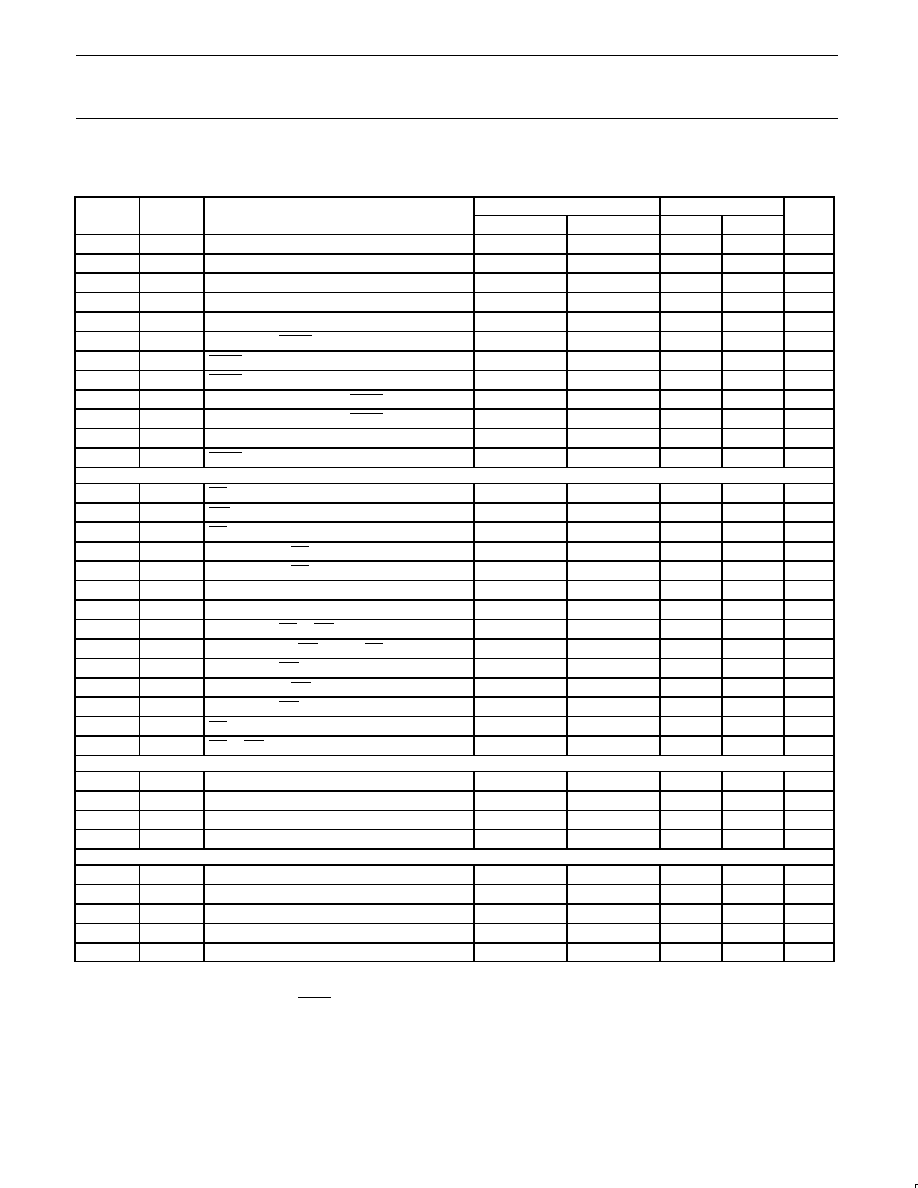

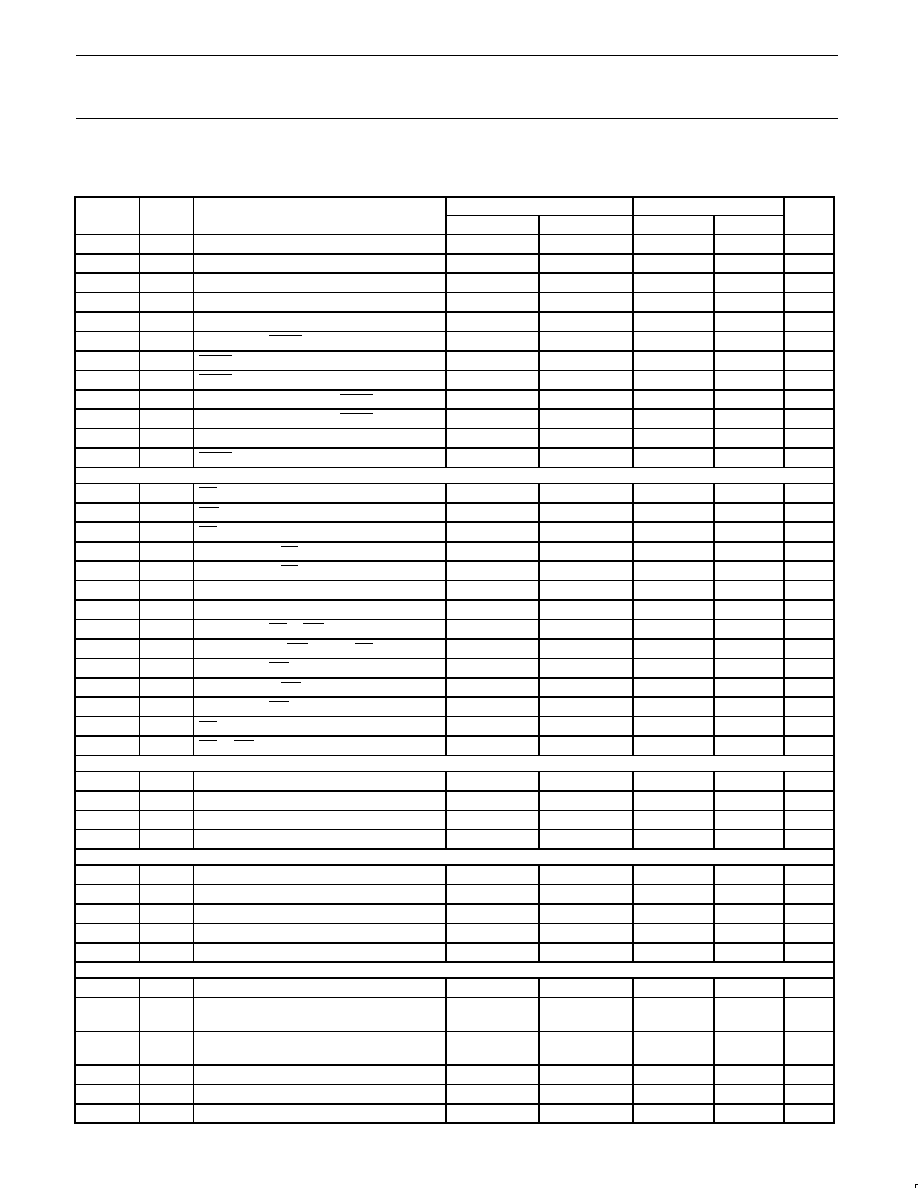

SPECIAL FUNCTION REGISTERS

SYMBOL

DESCRIPTION

DIRECT

ADDRESS

BIT ADDRESS, SYMBOL, OR ALTERNATIVE PORT FUNCTION

MSB

LSB

RESET

VALUE

ACC*

Accumulator

E0H

E7

E6

E5

E4

E3

E2

E1

E0

00H

AUXR#

Auxiliary

8EH

≠

≠

≠

≠

Fast/STD

I

2

C

≠

≠

AO

xxxx1xx0B

AUXR1#

Auxiliary 1

A2H

≠

≠

≠

LPEP

GPS

0

≠

DPS

xxxx00x0B

B*

B register

F0H

F7

F6

F5

F4

F3

F2

F1

F0

00H

CKCON

Clock control

8FH

≠

≠

≠

≠

≠

≠

≠

X2

xxxxxxx0B

DPTR:

Data Pointer (2 bytes)

DPH

Data Pointer High

83H

00H

DPL

Data Pointer Low

82H

00H

AF

AE

AD

AC

AB

AA

A9

A8

IEN0*

Interrupt Enable 0

A8H

EA

EC

ES1

ES0

ET1

EX1

ET0

EX0

00000000B

IEN1*

Interrupt Enable 1

E8H

≠

≠

≠

≠

≠

≠

ES2

ET2

xxxxxx00B

BF

BE

BD

BC

BB

BA

B9

B8

IP*#

Interrupt Priority

B8H

PT2

≠

PS1

PS0

PT1

PX1

PT0

PX0

00000000B

B7

B6

B5

B4

B3

B2

B1

B0

IPH#

Interrupt Priority High

B7H

PT2H

PPCH

PS1H

PS0H

PT1H

PX1H

PT0H

PX0H

00000000B

87

86

85

84

83

82

81

80

P0*

Port 0

80H

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AD0

FFH

97

96

95

94

93

92

91

90

P1*#

Port 1

90H

SDA

SCL

≠

≠

≠

≠

T2EX

T2

FFH

A7

A6

A5

A4

A3

A2

A1

A0

P2*

Port 2

A0H

AD15

AD14

AD13

AD12

AD11

AD10

AD9

AD8

FFH

B7

B6

B5

B4

B3

B2

B1

B0

P3*

Port 3

B0H

RD

WR

T1

T0

INT1

INT0

TxD

RxD

FFH

PCON#

1

Power Control

87H

SMOD1

SMOD0

≠

POF

GF1

GF0

PD

IDL

00xx0000B

D7

D6

D5

D4

D3

D2

D1

D0

PSW*

Program Status Word

D0H

CY

AC

F0

RS1

RS0

OV

F1

P

00000000B

RCAP2H

#

Timer 2 Capture High

CBH

00H

RCAP2L

#

Timer 2 Capture Low

CAH

00H

SADDR#

Slave Address

A9H

00H

SADEN#

Slave Address Mask

B9H

00H

SBUF

Serial Data Buffer

99H

xxxxxxxxB

9F

9E

9D

9C

9B

9A

99

98

SCON*

Serial Control

98H

SM0/FE

SM1

SM2

REN

TB8

RB8

TI

RI

00H

SP

Stack Pointer

81H

07H

8F

8E

8D

8C

8B

8A

89

88

TCON*

Timer Control

88H

TF1

TR1

TF0

TR0

IE1

IT1

IE0

IT0

00H

CF

CE

CD

CC

CB

CA

C9

C8

T2CON*

Timer 2 Control

C8H

TF2

EXF2

RCLK

TCLK

EXEN2

TR2

C/T2

CP/

RL2

00H

T2MOD#

Timer 2 Mode Control

C9H

≠

≠

≠

≠

≠

≠

T2OE

DCEN

xxxxxx00B

TH0

Timer High 0

8CH

00H

TH1

Timer High 1

8DH

00H

TH2#

Timer High 2

CDH

00H

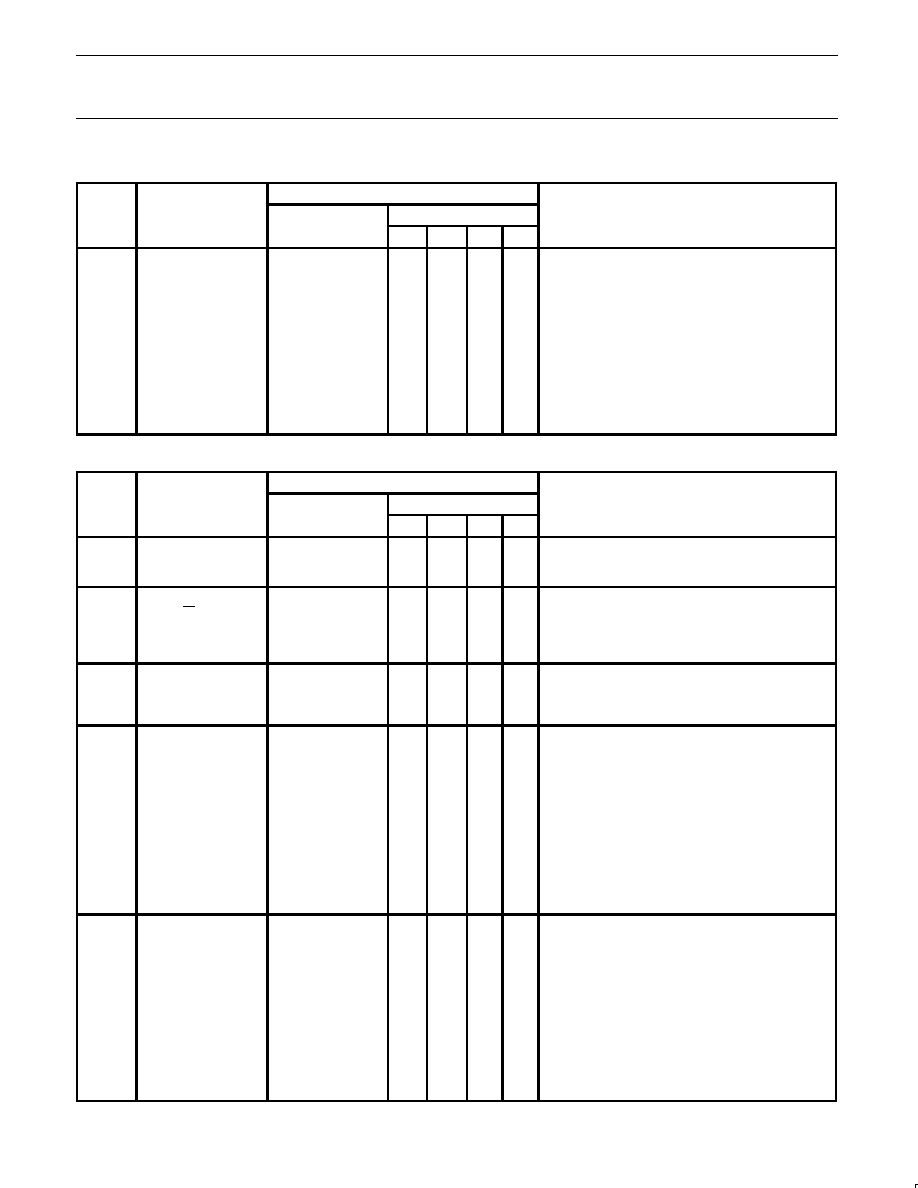

Philips Semiconductors

Product data

P83C654X2/P87C654X2

80C51 8-bit microcontroller family

16 kB OTP/ROM,

256B RAM, low voltage (2.7 to 5.5 V), low power, high speed

(30/33 MHz)

2004 Apr 20

9

SYMBOL

RESET

VALUE

BIT ADDRESS, SYMBOL, OR ALTERNATIVE PORT FUNCTION

MSB

LSB

DIRECT

ADDRESS

DESCRIPTION

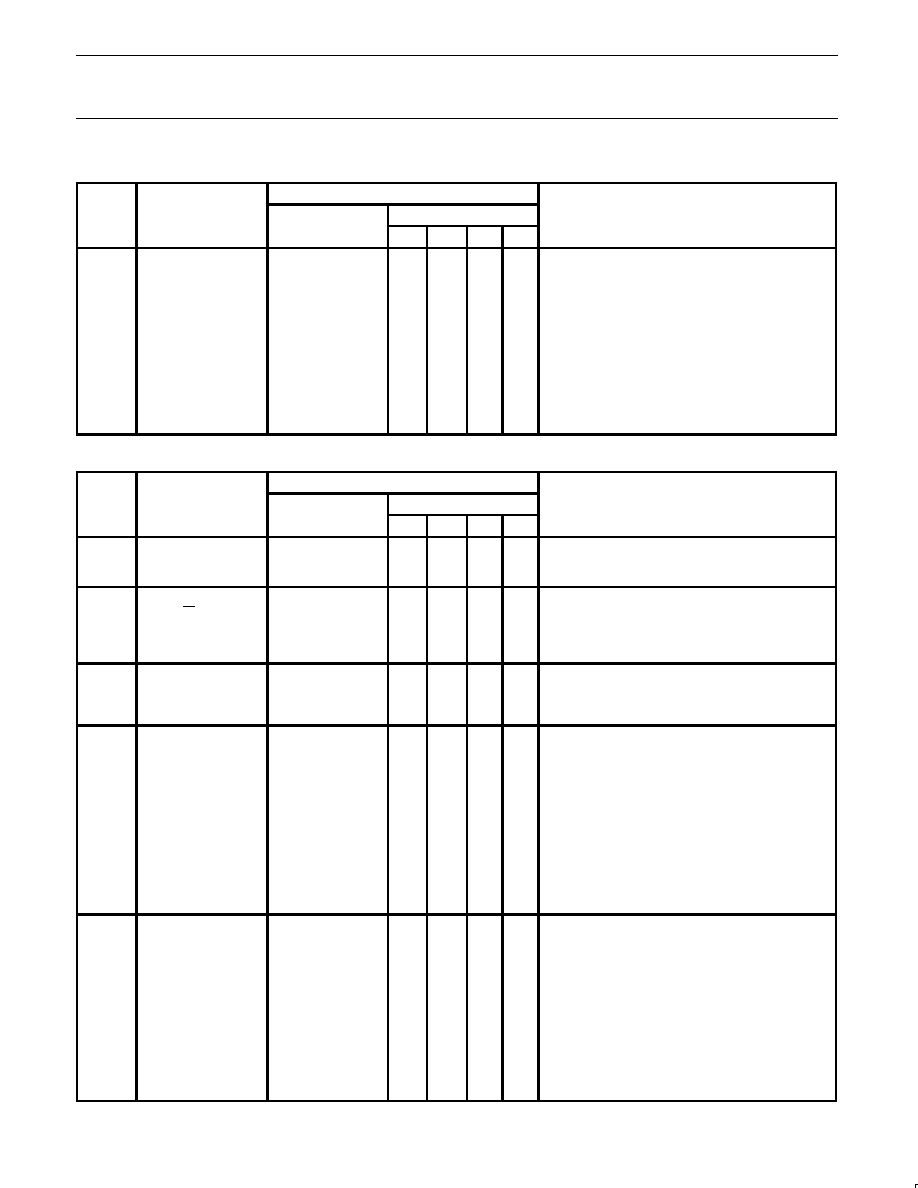

TL0

Timer Low 0

8AH

00H

TL1

Timer Low 1

8BH

00H

TL2#

Timer Low 2

CCH

00H

TMOD

Timer Mode

89H

GATE

C/T

M1

M0

GATE

C/T

M1

M0

00H

S1CON

I2C Control

D8H

CR2

ENA1

STA

STO

SI

AA

CR1

CR0

00H

S1STA

I2C STATUS

D9H

SC4

SC3

SC2

SC1

SC0

0

0

0

F8H

S1DAT

I2C DATA

DAH

00H

S1ADR

I2C ADDRESS

DBH

GC

00H

WDTRST

Watchdog Reset Timer

A6H

*

SFRs are bit addressable.

#

SFRs are modified from or added to the 80C51 SFRs.

≠

Reserved bits.

1. Reset value depends on reset source.

Philips Semiconductors

Product data

P83C654X2/P87C654X2

80C51 8-bit microcontroller family

16 kB OTP/ROM,

256B RAM, low voltage (2.7 to 5.5 V), low power, high speed

(30/33 MHz)

2004 Apr 20

10

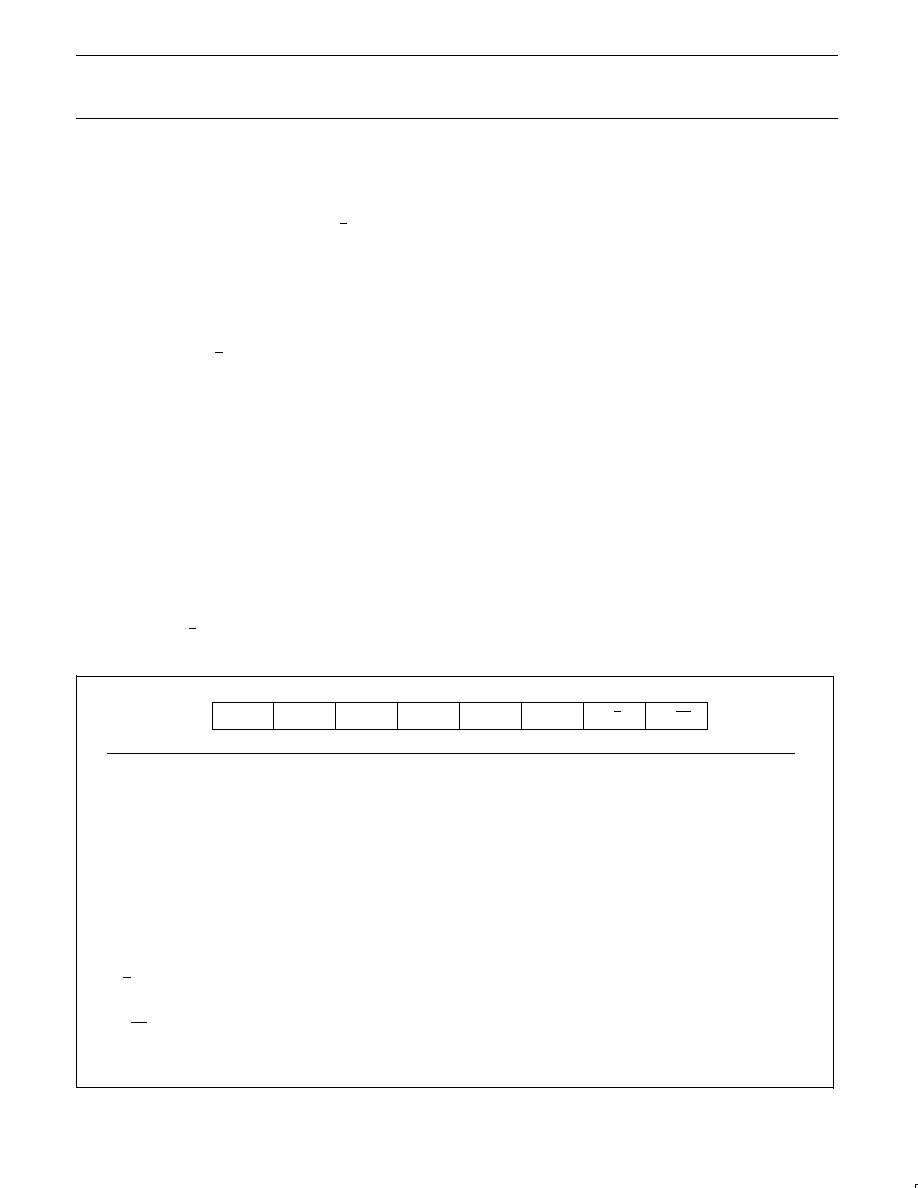

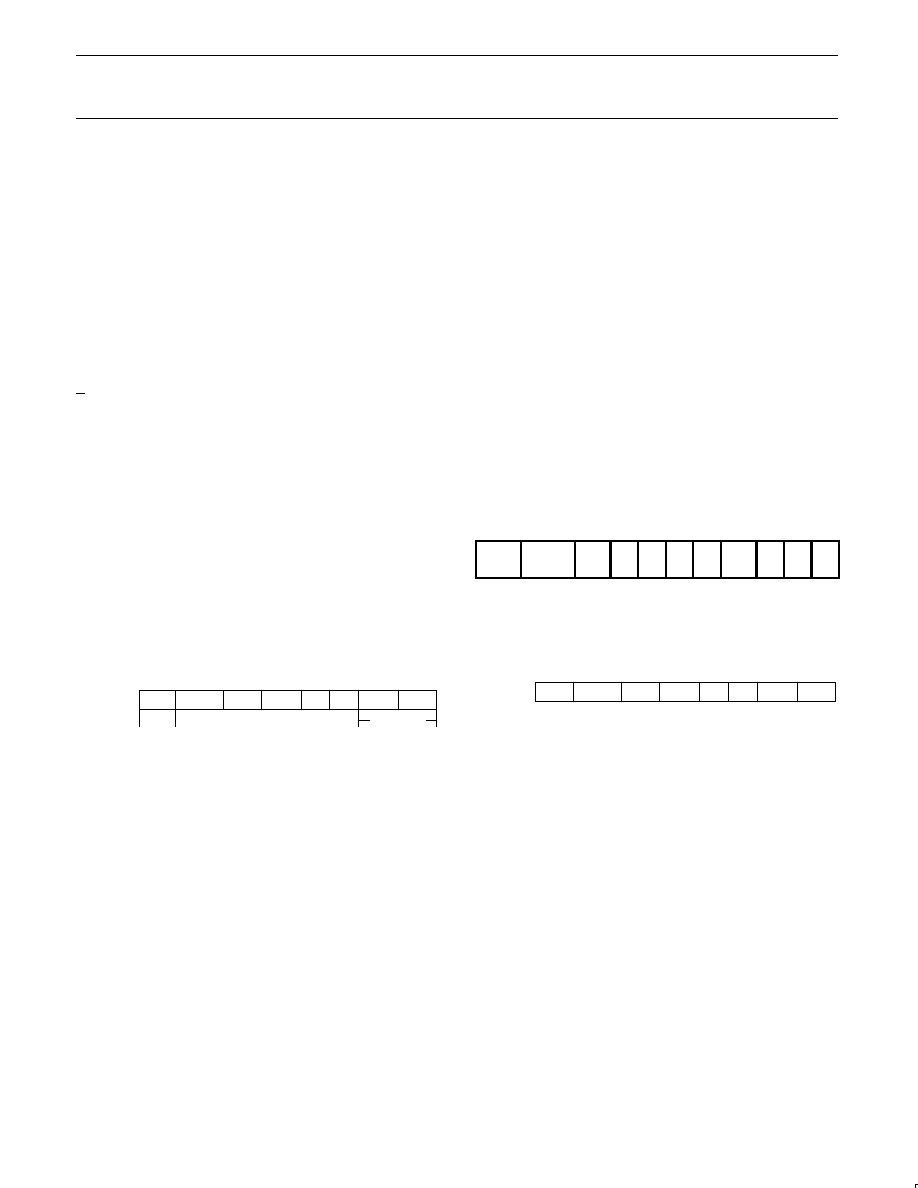

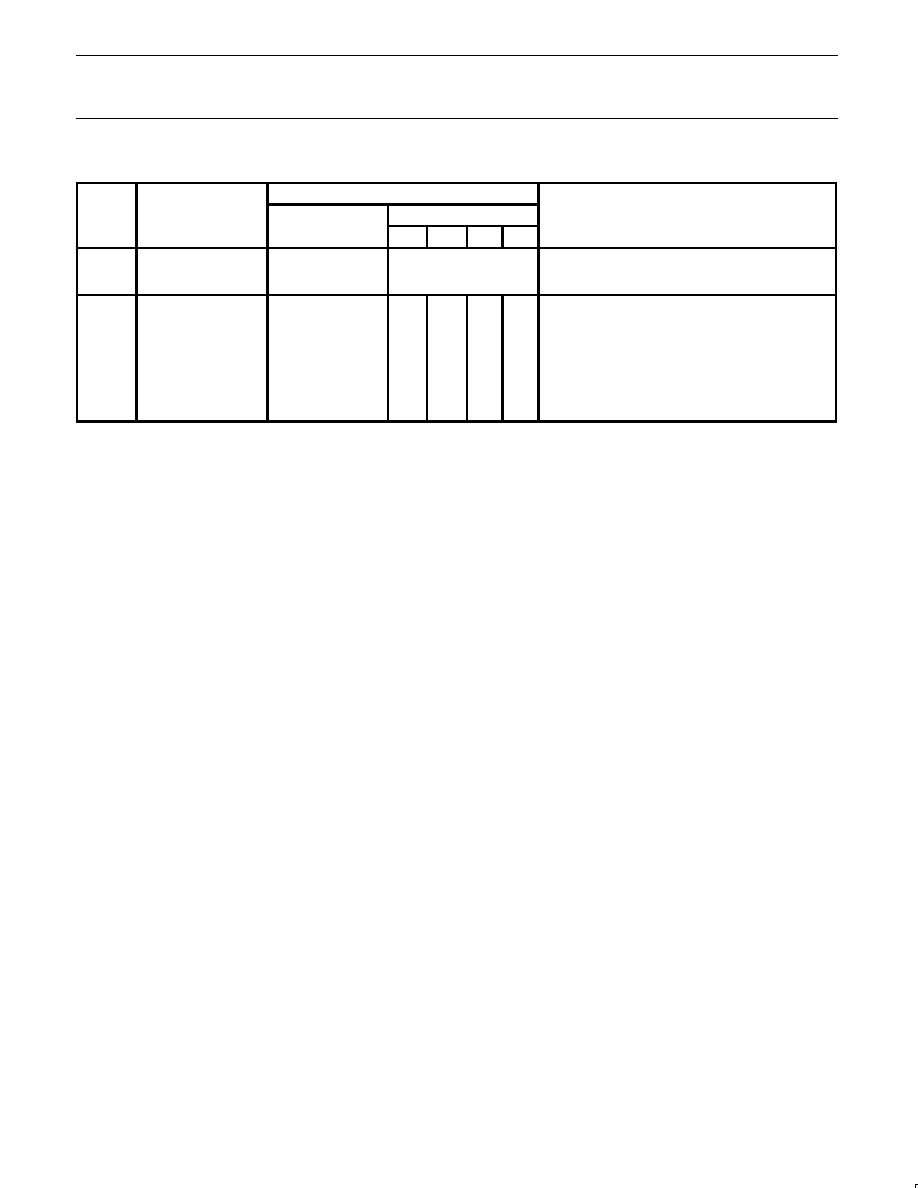

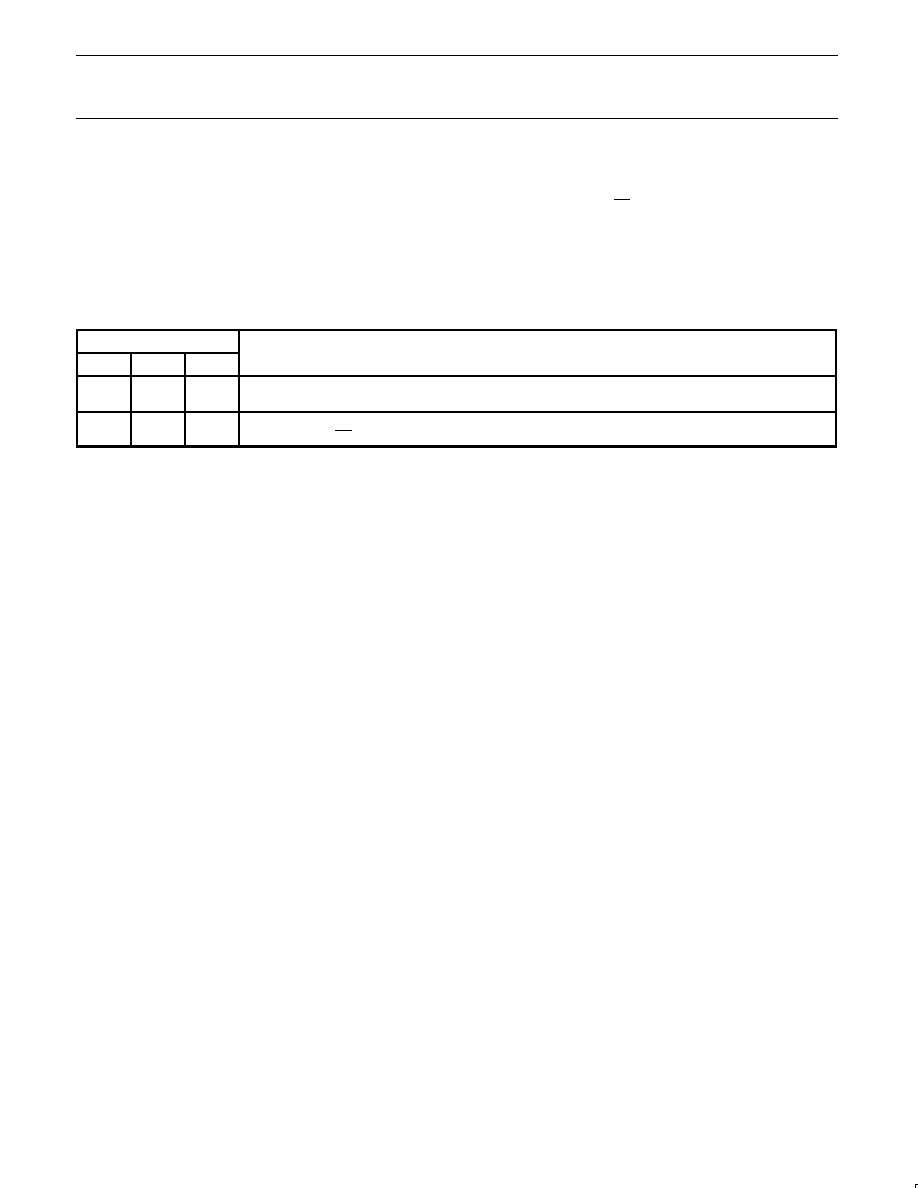

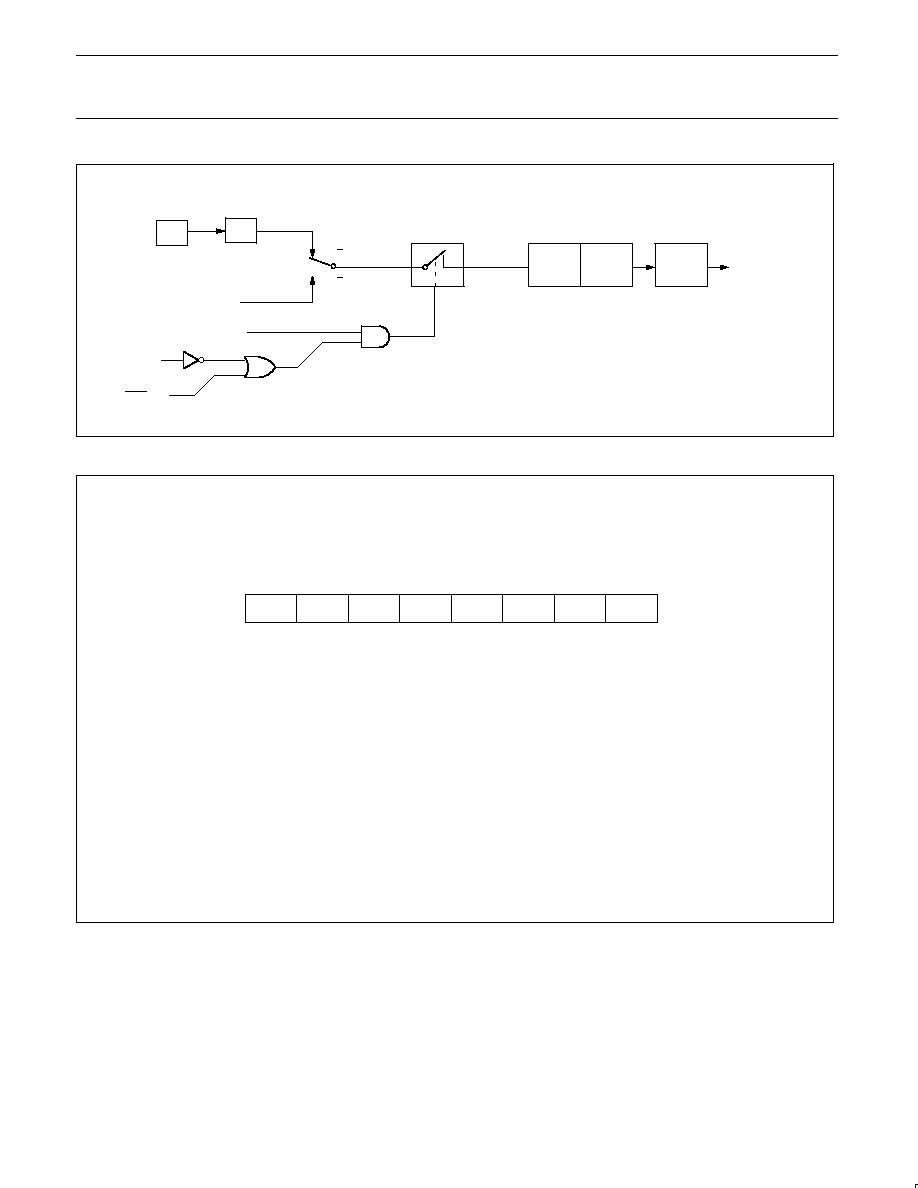

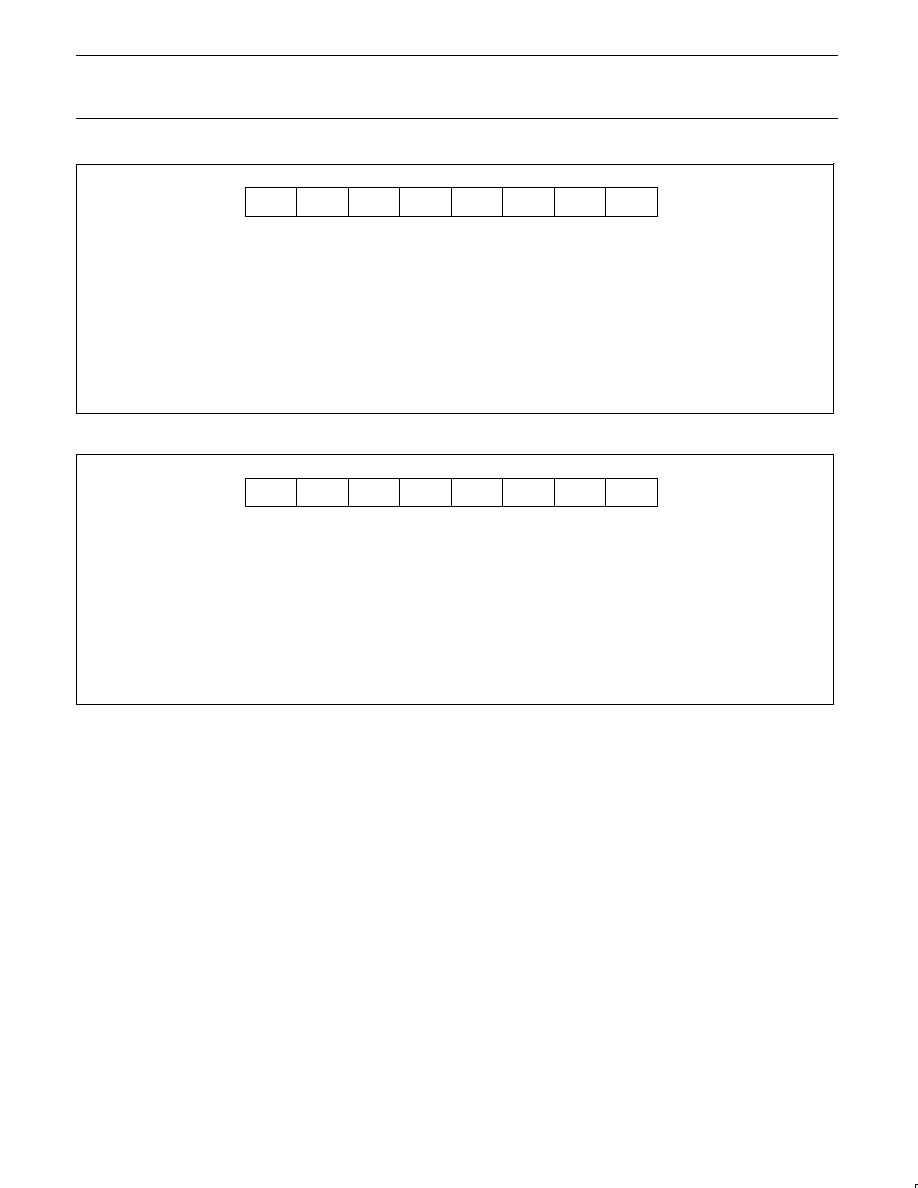

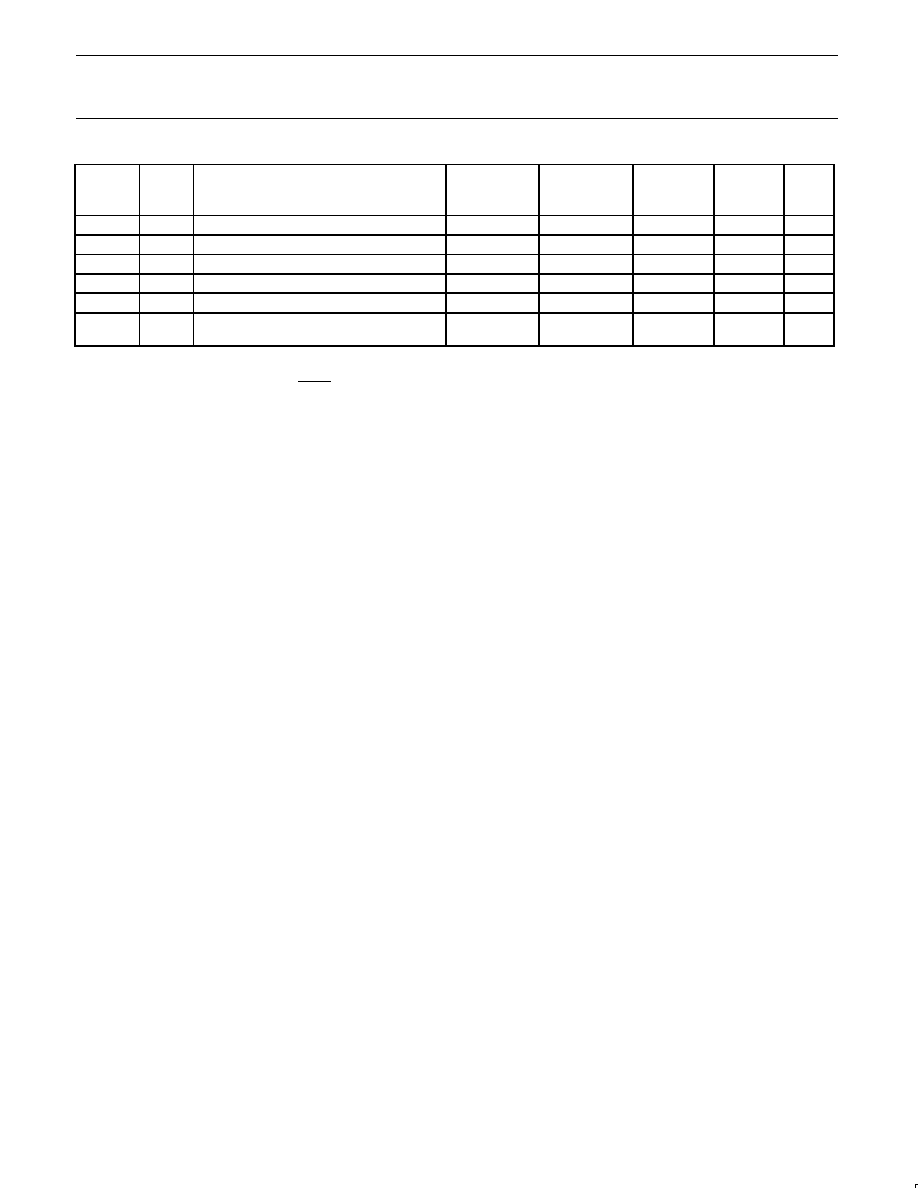

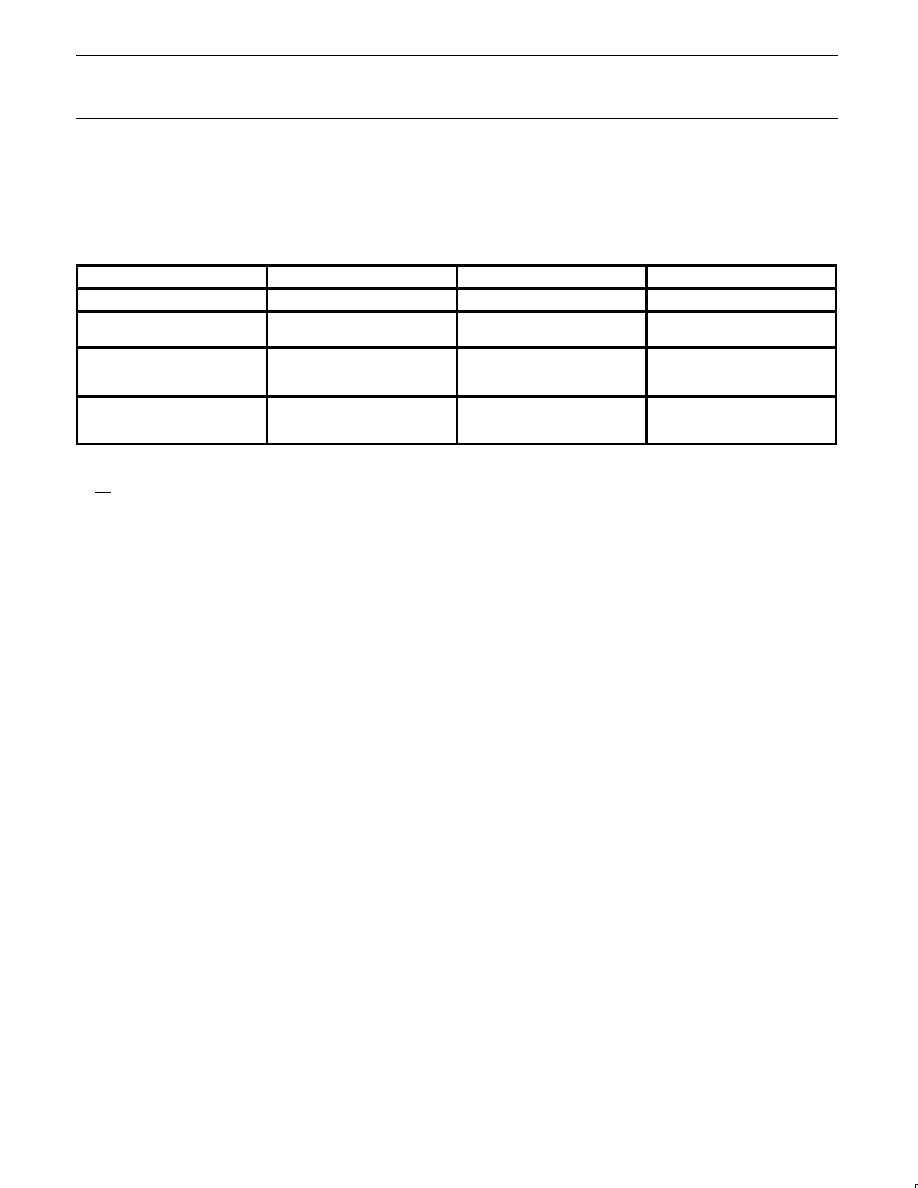

CLOCK CONTROL REGISTER (CKCON)

This device allows control of the 6-clock/12-clock mode by means of

both an SFR bit (X2) and an OTP bit. The OTP clock control bit

OX2, when programmed (6-clock mode), supersedes the X2 bit

(CKCON.0). The CKCON register is shown below in Figure 1.

X2

BIT

SYMBOL

FUNCTION

CKCON.7

≠

Reserved.

CKCON.6

Reserved.

CKCON.5

Reserved.

CKCON.4

Reserved.

CKCON.3

Reserved.

CKCON.2

Reserved.

CKCON.1

Reserved.

CKCON.0

X2

CPU clock; 1 = 6 clocks for each machine cycle, 0 = 12 clocks for each machine cycle

SU01689

≠

≠

Not Bit Addressable

CKCON

Address = 8Fh

Reset Value =

x0000000B

7

6

5

4

3

2

1

0

≠

≠

≠

≠

≠

Figure 1. Clock control (CKCON) register

Also please note that the clock divider applies to the serial port for

modes 0 and 2 (fixed baud rate modes). This is because modes 1

and 3 (variable baud rate modes) use either Timer 1 or Timer 2.

Below is the truth table for the CPU clock mode.

Table 1.

OX2 clock mode bit

(can only be set by

parallel programmer)

X2 bit

(CKCON.0)

CPU clock mode

erased

0

12-clock mode

(default)

erased

1

6-clock mode

programmed

X

6-clock mode

Philips Semiconductors

Product data

P83C654X2/P87C654X2

80C51 8-bit microcontroller family

16 kB OTP/ROM,

256B RAM, low voltage (2.7 to 5.5 V), low power, high speed

(30/33 MHz)

2004 Apr 20

11

OSCILLATOR CHARACTERISTICS

XTAL1 and XTAL2 are the input and output, respectively, of an

inverting amplifier. The pins can be configured for use as an

on-chip oscillator.

To drive the device from an external clock source, XTAL1 should be

driven while XTAL2 is left unconnected. Minimum and maximum

high and low times specified in the data sheet must be observed.

This device is configured at the factory to operate using 12 clock

periods per machine cycle, referred to in this datasheet as "12-clock

mode". It may be optionally configured on commercially available

EPROM programming equipment to operate at 6 clocks per machine

cycle, referred to in this datasheet as "6-clock mode". (This yields

performance equivalent to twice that of standard 80C51 family

devices). Also see next page.

RESET

A reset is accomplished by holding the RST pin HIGH for at least

two machine cycles (12 oscillator periods in 6-clock mode, or 24

oscillator periods in 12-clock mode), while the oscillator is running.

To insure a good power-on reset, the RST pin must be HIGH long

enough to allow the oscillator time to start up (normally a few

milliseconds) plus two machine cycles. At power-on, the voltage on

V

CC

and RST must come up at the same time for a proper start-up.

Ports 1, 2, and 3 will asynchronously be driven to their reset

condition when a voltage above V

IH (min.)

is applied to RESET. The

value on the EA pin is latched when RST is deasserted and has no

further effect.

LOW POWER MODES

Stop Clock Mode

The static design enables the clock speed to be reduced down to

0 MHz (stopped). When the oscillator is stopped, the RAM and

Special Function Registers retain their values. This mode allows

step-by-step utilization and permits reduced system power

consumption by lowering the clock frequency down to any value. For

lowest power consumption the Power-down mode is suggested.

Idle Mode

In the idle mode (see Table 2), the CPU puts itself to sleep while all

of the on-chip peripherals stay active. The instruction to invoke the

idle mode is the last instruction executed in the normal operating

mode before the idle mode is activated. The CPU contents, the

on-chip RAM, and all of the special function registers remain intact

during this mode. The idle mode can be terminated either by any

enabled interrupt (at which time the process is picked up at the

interrupt service routine and continued), or by a hardware reset

which starts the processor in the same manner as a power-on reset.

Power-Down Mode

To save even more power, a Power-down mode (see Table 2) can

be invoked by software. In this mode, the oscillator is stopped and

the instruction that invoked power-down is the last instruction

executed. The on-chip RAM and Special Function Registers retain

their values down to 2 V and care must be taken to return V

CC

to the

minimum specified operating voltages before the Power-down mode

is terminated.

Either a hardware reset or external interrupt can be used to exit from

power-down. Reset redefines all the SFRs but does not change the

on-chip RAM. An external interrupt allows both the SFRs and the

on-chip RAM to retain their values.

To properly terminate power-down, the reset or external interrupt

should not be executed before V

CC

is restored to its normal

operating level and must be held active long enough for the

oscillator to restart and stabilize (normally less than 10 ms).

With an external interrupt, INT0 and INT1 must be enabled and

configured as level-sensitive. Holding the pin LOW restarts the

oscillator but bringing the pin back HIGH completes the exit. Once

the interrupt is serviced, the next instruction to be executed after

RETI will be the one following the instruction that put the device into

power-down.

POWER-OFF FLAG

The Power-Off Flag (POF) is set by on-chip circuitry when the V

CC

level on the P8xC654X2 rises from 0 to 5 V. The POF bit can be set

or cleared by software allowing a user to determine if the reset is the

result of a power-on or a warm start after power-down. The V

CC

level must remain above 3 V for the POF to remain unaffected by

the V

CC

level.

Low-Power EPROM operation (LPEP)

The EPROM array contains some analog circuits that are not

required when V

CC

is less than 4 V, but are required for a V

CC

greater than 4 V. The LPEP bit (AUXR.4), when set, will power-down

these analog circuits resulting in a reduced supply current. This bit

should be set ONLY for applications that operate at a V

CC

less than

4 V.

Design Consideration

When the idle mode is terminated by a hardware reset, the device

normally resumes program execution, from where it left off, up to

two machine cycles before the internal reset algorithm takes control.

On-chip hardware inhibits access to internal RAM in this event, but

access to the port pins is not inhibited. To eliminate the possibility of

an unexpected write when Idle is terminated by reset, the instruction

following the one that invokes Idle should not be one that writes to a

port pin or to external memory.

ONCE

TM

Mode

The ONCE ("On-Circuit Emulation") Mode facilitates testing and

debugging of systems without the device having to be removed from

the circuit. The ONCE Mode is invoked by:

1. Pull ALE LOW while the device is in reset and PSEN is HIGH;

2. Hold ALE LOW as RST is deactivated.

While the device is in ONCE Mode, the Port 0 pins go into a float

state, and the other port pins and ALE and PSEN are weakly pulled

HIGH. The oscillator circuit remains active. While the device is in

this mode, an emulator or test CPU can be used to drive the circuit.

Normal operation is restored when a normal reset is applied.

Programmable Clock-Out

A 50 % duty cycle clock can be programmed to come out on P1.0.

This pin, besides being a regular I/O pin, has two alternate

functions. It can be programmed:

1. to input the external clock for Timer/Counter 2, or

2. to output a 50 % duty cycle clock ranging from 122 Hz to 8 MHz at

a 16 MHz operating frequency (61 Hz to 4 MHz in 12-clock mode).

To configure the Timer/Counter 2 as a clock generator, bit C/T2 (in

T2CON) must be cleared and bit T20E in T2MOD must be set. Bit

TR2 (T2CON.2) also must be set to start the timer.

Philips Semiconductors

Product data

P83C654X2/P87C654X2

80C51 8-bit microcontroller family

16 kB OTP/ROM,

256B RAM, low voltage (2.7 to 5.5 V), low power, high speed

(30/33 MHz)

2004 Apr 20

12

The Clock-Out frequency depends on the oscillator frequency and

the reload value of Timer 2 capture registers (RCAP2H, RCAP2L)

as shown in this equation:

Oscillator Frequency

n

(65536

*

RCAP2H, RCAP2L)

n =

2 in 6-clock mode

4 in 12-clock mode

Where (RCAP2H,RCAP2L) = the content of RCAP2H and RCAP2L

taken as a 16-bit unsigned integer.

In the Clock-Out mode Timer 2 roll-overs will not generate an

interrupt. This is similar to when it is used as a baud-rate generator.

It is possible to use Timer 2 as a baud-rate generator and a clock

generator simultaneously. Note, however, that the baud-rate and the

Clock-Out frequency will be the same.

Table 2.

External Pin Status During Idle and Power-Down Mode

MODE

PROGRAM MEMORY

ALE

PSEN

PORT 0

PORT 1

PORT 2

PORT 3

Idle

Internal

1

1

Data

Data

Data

Data

Idle

External

1

1

Float

Data

Address

Data

Power-down

Internal

0

0

Data

Data

Data

Data

Power-down

External

0

0

Float

Data

Data

Data

Philips Semiconductors

Product data

P83C654X2/P87C654X2

80C51 8-bit microcontroller family

16 kB OTP/ROM,

256B RAM, low voltage (2.7 to 5.5 V), low power, high speed

(30/33 MHz)

2004 Apr 20

13

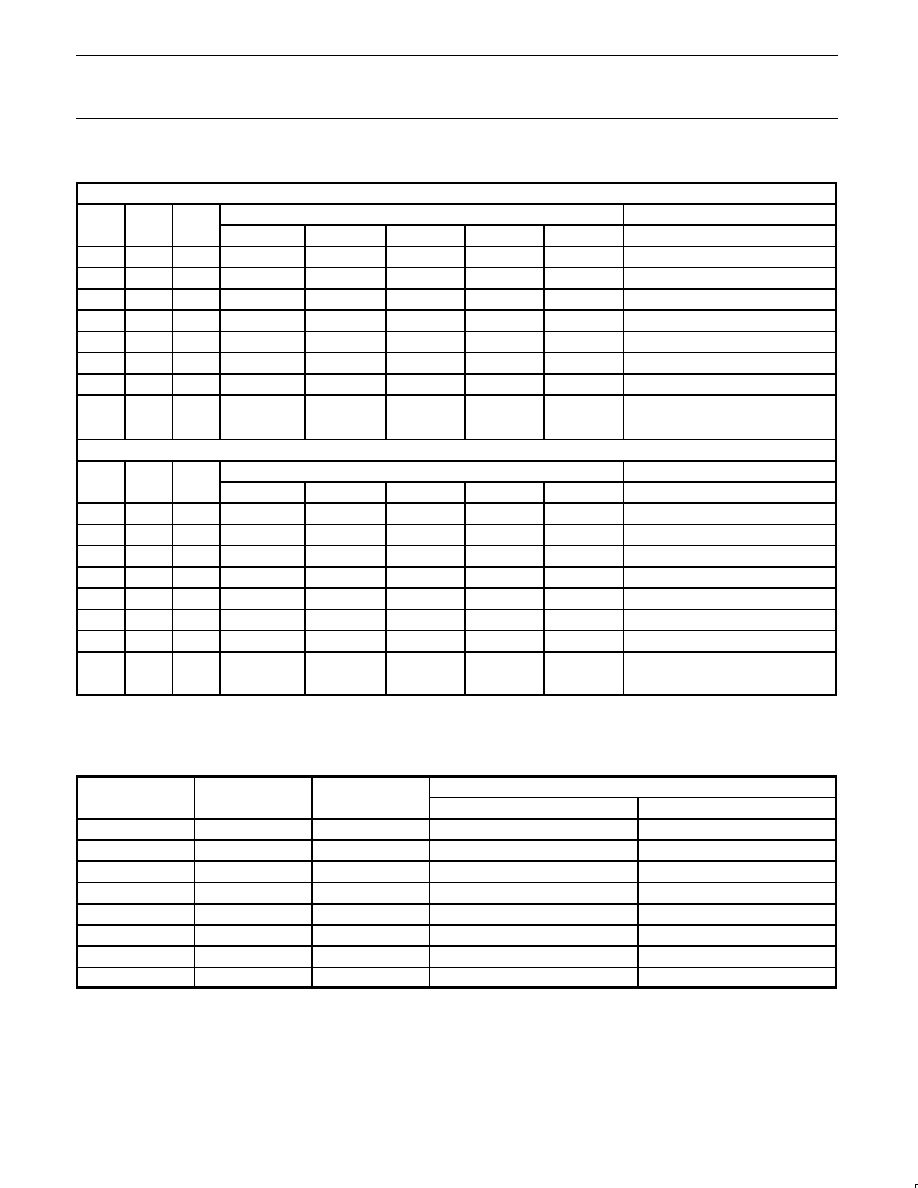

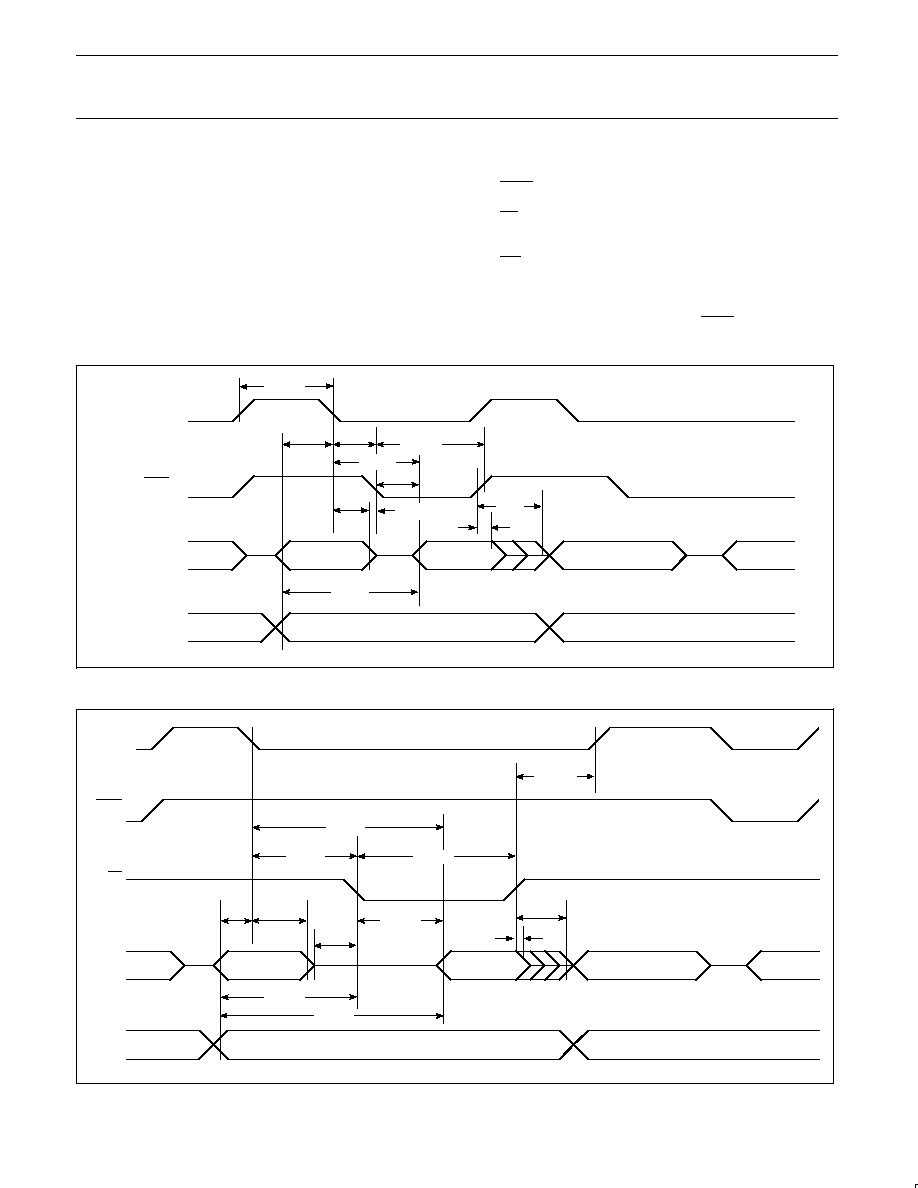

TIMER 0 AND TIMER 1 OPERATION

Timer 0 and Timer 1

The "Timer" or "Counter" function is selected by control bits C/T in

the Special Function Register TMOD. These two Timer/Counters

have four operating modes, which are selected by bit-pairs (M1, M0)

in TMOD. Modes 0, 1, and 2 are the same for both Timers/Counters.

Mode 3 is different. The four operating modes are described in the

following text.

Mode 0

Putting either Timer into Mode 0 makes it look like an 8048 Timer,

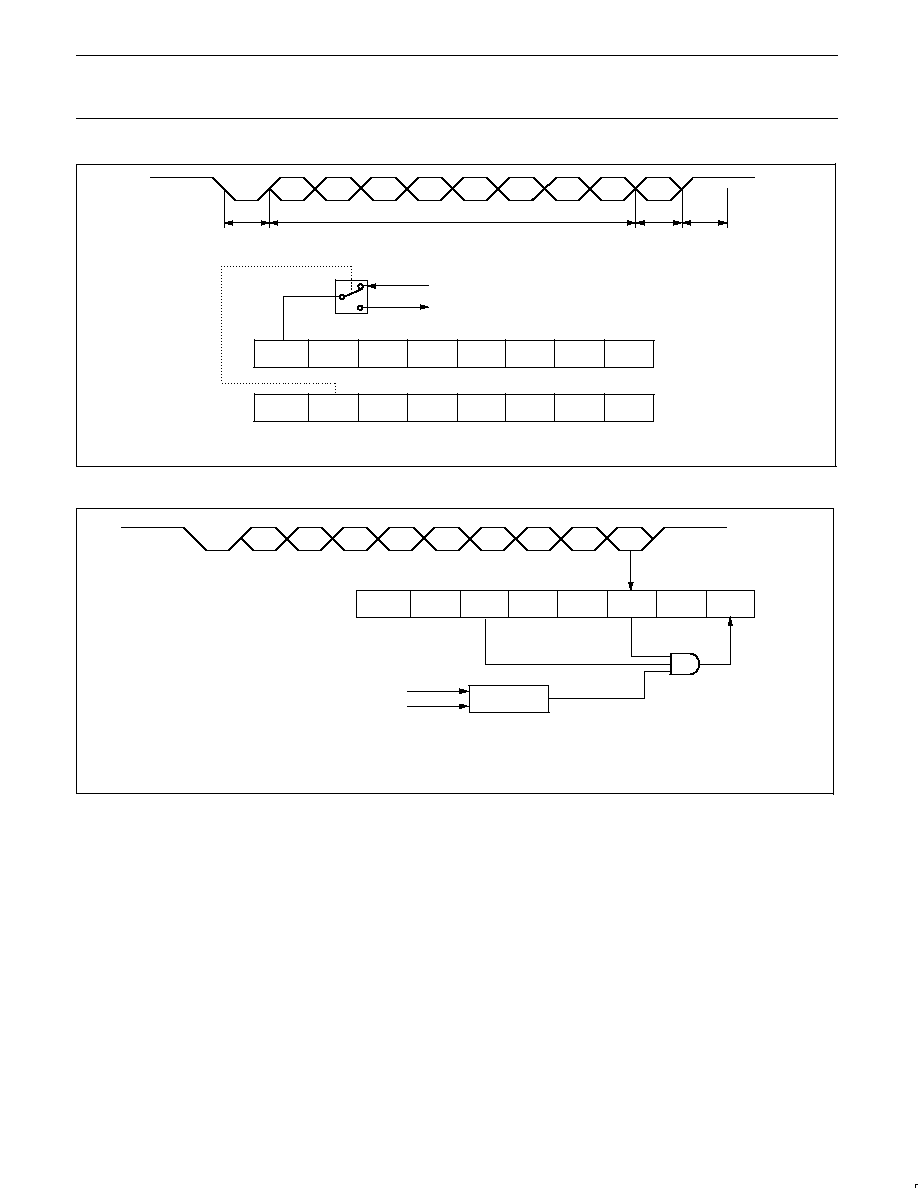

which is an 8-bit Counter with a divide-by-32 prescaler. Figure 3

shows the Mode 0 operation.

In this mode, the Timer register is configured as a 13-bit register. As

the count rolls over from all 1s to all 0s, it sets the Timer interrupt

flag TFn. The counted input is enabled to the Timer when TRn = 1

and either GATE = 0 or INTn = 1. (Setting GATE = 1 allows the

Timer to be controlled by external input INTn, to facilitate pulse width

measurements). TRn is a control bit in the Special Function Register

TCON (Figure 4).

The 13-bit register consists of all 8 bits of THn and the lower 5 bits

of TLn. The upper 3 bits of TLn are indeterminate and should be

ignored. Setting the run flag (TRn) does not clear the registers.

Mode 0 operation is the same for Timer 0 as for Timer 1. There are

two different GATE bits, one for Timer 1 (TMOD.7) and one for Timer

0 (TMOD.3).

Mode 1

Mode 1 is the same as Mode 0, except that the Timer register is

being run with all 16 bits.

Mode 2

Mode 2 configures the Timer register as an 8-bit Counter (TLn) with

automatic reload, as shown in Figure 5. Overflow from TLn not only

sets TFn, but also reloads TLn with the contents of THn, which is

preset by software. The reload leaves THn unchanged.

Mode 2 operation is the same for Timer 0 as for Timer 1.

Mode 3

Timer 1 in Mode 3 simply holds its count. The effect is the same as

setting TR1 = 0.

Timer 0 in Mode 3 establishes TL0 and TH0 as two separate

counters. The logic for Mode 3 on Timer 0 is shown in Figure 6. TL0

uses the Timer 0 control bits: C/T, GATE, TR0, and TF0 as well as

pin INT0. TH0 is locked into a timer function (counting machine

cycles) and takes over the use of TR1 and TF1 from Timer 1. Thus,

TH0 now controls the "Timer 1" interrupt.

Mode 3 is provided for applications requiring an extra 8-bit timer on

the counter. With Timer 0 in Mode 3, an 80C51 can look like it has

three Timer/Counters. When Timer 0 is in Mode 3, Timer 1 can be

turned on and off by switching it out of and into its own Mode 3, or

can still be used by the serial port as a baud rate generator, or in

fact, in any application not requiring an interrupt.

GATE

C/T

M1

M0

GATE

C/T

M1

M0

BIT

SYMBOL

FUNCTION

TMOD.3/

GATE

Gating control when set. Timer/Counter "n" is enabled only while "INTn" pin is high and

TMOD.7

"TRn" control pin is set. when cleared Timer "n" is enabled whenever "TRn" control bit is set.

TMOD.2/

C/T

Timer or Counter Selector cleared for Timer operation (input from internal system clock.)

TMOD.6

Set for Counter operation (input from "Tn" input pin).

M1

M0

OPERATING

0

0

8048 Timer: "TLn" serves as 5-bit prescaler.

0

1

16-bit Timer/Counter: "THn" and "TLn" are cascaded; there is no prescaler.

1

0

8-bit auto-reload Timer/Counter: "THn" holds a value which is to be reloaded

into "TLn" each time it overflows.

1

1

(Timer 0) TL0 is an 8-bit Timer/Counter controlled by the standard Timer 0 control bits.

TH0 is an 8-bit timer only controlled by Timer 1 control bits.

1

1

(Timer 1) Timer/Counter 1 stopped.

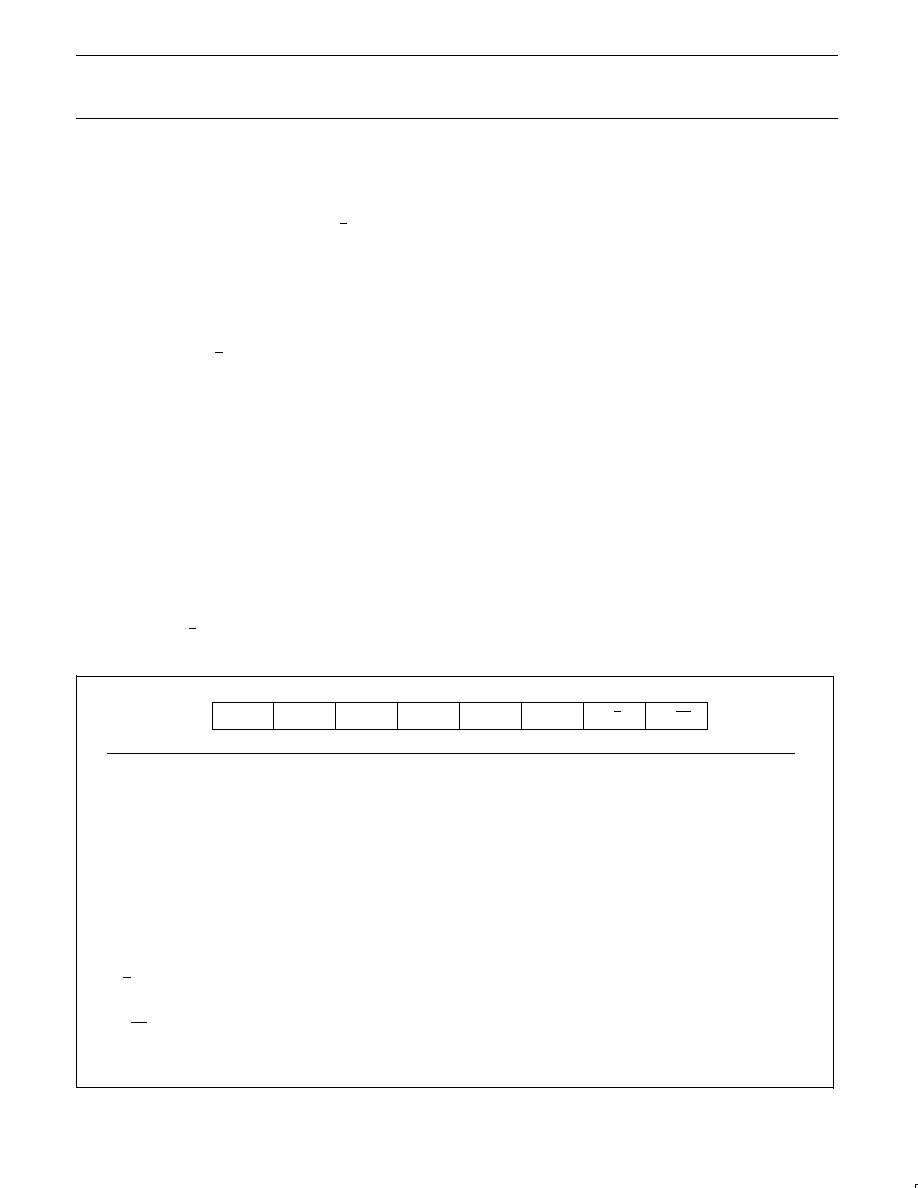

SU01580

TIMER 1

TIMER 0

Not Bit Addressable

TMOD

Address = 89H

Reset Value = 00H

7

6

5

4

3

2

1

0

Figure 2. Timer/Counter 0/1 Mode Control (TMOD) Register

Philips Semiconductors

Product data

P83C654X2/P87C654X2

80C51 8-bit microcontroller family

16 kB OTP/ROM,

256B RAM, low voltage (2.7 to 5.5 V), low power, high speed

(30/33 MHz)

2004 Apr 20

14

INTn Pin

Timer n

Gate bit

TRn

TLn

(5 Bits)

THn

(8 Bits)

TFn

Interrupt

Control

C/T = 0

C/T = 1

SU01618

OSC

˜

d*

Tn Pin

*d = 6 in 6-clock mode; d = 12 in 12-clock mode.

Figure 3. Timer/Counter 0/1 Mode 0: 13-Bit Timer/Counter

IT0

BIT

SYMBOL

FUNCTION

TCON.7

TF1

Timer 1 overflow flag. Set by hardware on Timer/Counter overflow.

Cleared by hardware when processor vectors to interrupt routine, or clearing the bit in software.

TCON.6

TR1

Timer 1 Run control bit. Set/cleared by software to turn Timer/Counter on/off.

TCON.5

TF0

Timer 0 overflow flag. Set by hardware on Timer/Counter overflow.

Cleared by hardware when processor vectors to interrupt routine, or by clearing the bit in software.

TCON.4

TR0

Timer 0 Run control bit. Set/cleared by software to turn Timer/Counter on/off.

TCON.3

IE1

Interrupt 1 Edge flag. Set by hardware when external interrupt edge detected.

Cleared when interrupt processed.

TCON.2

IT1

Interrupt 1 type control bit. Set/cleared by software to specify falling edge/low level triggered

external interrupts.

TCON.1

IE0

Interrupt 0 Edge flag. Set by hardware when external interrupt edge detected.

Cleared when interrupt processed.

TCON.0

IT0

Interrupt 0 Type control bit. Set/cleared by software to specify falling edge/low level

triggered external interrupts.

SU01516

IE0

IT1

IE1

TR0

TF0

TR1

TF1

Bit Addressable

TCON

Address = 88H

Reset Value = 00H

7

6

5

4

3

2

1

0

Figure 4. Timer/Counter 0/1 Control (TCON) Register

Philips Semiconductors

Product data

P83C654X2/P87C654X2

80C51 8-bit microcontroller family

16 kB OTP/ROM,

256B RAM, low voltage (2.7 to 5.5 V), low power, high speed

(30/33 MHz)

2004 Apr 20

15

TLn

(8 Bits)

TFn

Interrupt

Control

C/T = 0

C/T = 1

THn

(8 Bits)

Reload

INTn Pin

Timer n

Gate bit

TRn

SU01619

OSC

˜

d*

Tn Pin

*d = 6 in 6-clock mode; d = 12 in 12-clock mode.

Figure 5. Timer/Counter 0/1 Mode 2: 8-Bit Auto-Reload

TL0

(8 Bits)

TF0

Interrupt

Control

TH0

(8 Bits)

TF1

Interrupt

Control

TR1

INT0 Pin

Timer 0

Gate bit

TR0

SU01620

C/T = 0

C/T = 1

*d = 6 in 6-clock mode; d = 12 in 12-clock mode.

OSC

˜

d*

OSC

˜

d*

T0 Pin

Figure 6. Timer/Counter 0 Mode 3: Two 8-Bit Counters

Philips Semiconductors

Product data

P83C654X2/P87C654X2

80C51 8-bit microcontroller family

16 kB OTP/ROM,

256B RAM, low voltage (2.7 to 5.5 V), low power, high speed

(30/33 MHz)

2004 Apr 20

16

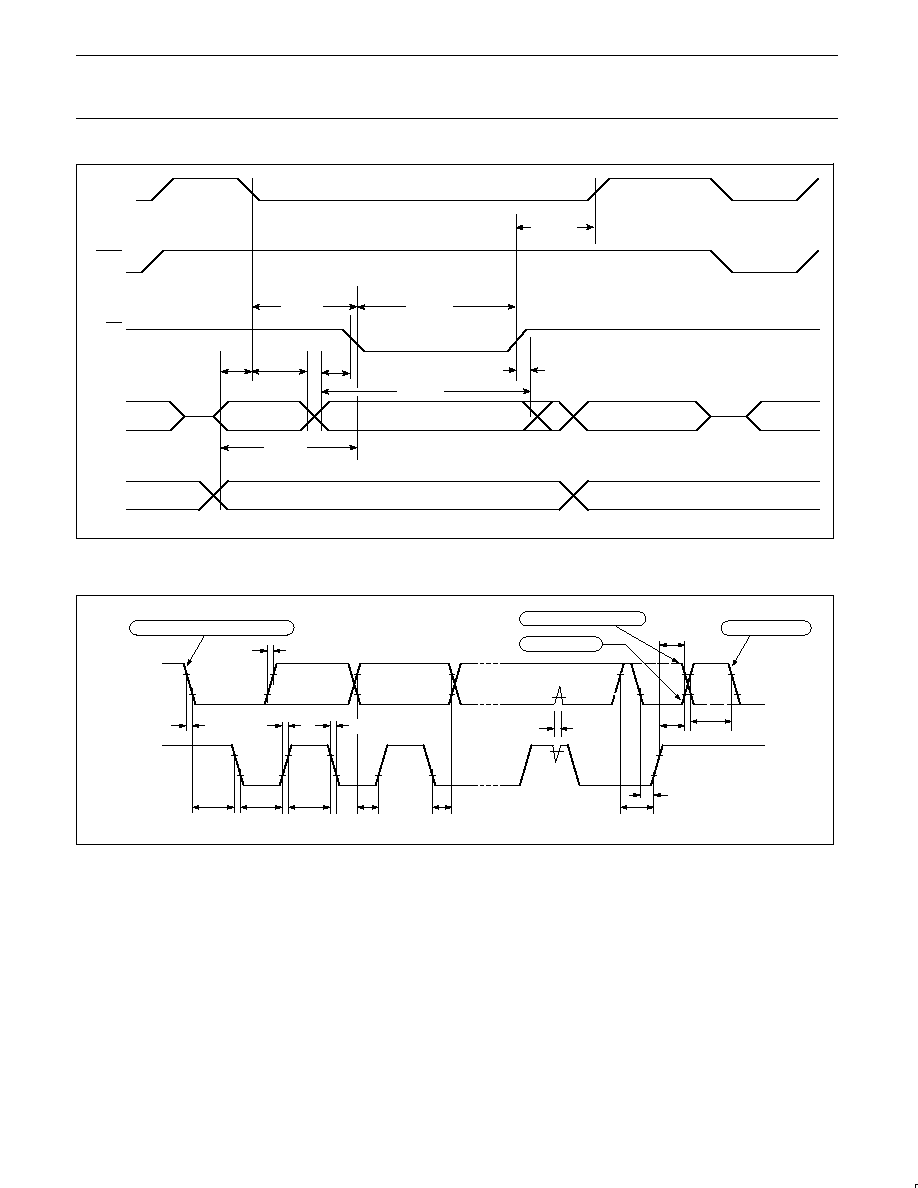

TIMER 2 OPERATION

Timer 2

Timer 2 is a 16-bit Timer/Counter which can operate as either an

event timer or an event counter, as selected by C/T2 in the special

function register T2CON (see Figure 7). Timer 2 has three operating

modes: Capture, Auto-reload (up or down counting), and Baud Rate

Generator, which are selected by bits in the T2CON as shown in

Table 3.

Capture Mode

In the capture mode there are two options which are selected by bit

EXEN2 in T2CON. If EXEN2 = 0, then timer 2 is a 16-bit timer or

counter (as selected by C/T2 in T2CON) which, upon overflowing

sets bit TF2, the timer 2 overflow bit. This bit can be used to

generate an interrupt (by enabling the Timer 2 interrupt bit in the

IE register). If EXEN2 = 1, Timer 2 operates as described above, but

with the added feature that a 1- to -0 transition at external input

T2EX causes the current value in the Timer 2 registers, TL2 and

TH2, to be captured into registers RCAP2L and RCAP2H,

respectively. In addition, the transition at T2EX causes bit EXF2 in

T2CON to be set, and EXF2 like TF2 can generate an interrupt

(which vectors to the same location as Timer 2 overflow interrupt.

The Timer 2 interrupt service routine can interrogate TF2 and EXF2

to determine which event caused the interrupt). The capture mode is

illustrated in Figure 8 (There is no reload value for TL2 and TH2 in

this mode. Even when a capture event occurs from T2EX, the

counter keeps on counting T2EX pin transitions or osc/6 pulses

(osc/12 in 12-clock mode).).

Auto-Reload Mode (Up or Down Counter)

In the 16-bit auto-reload mode, Timer 2 can be configured (as either

a timer or counter [C/T2 in T2CON]) then programmed to count up

or down. The counting direction is determined by bit DCEN (Down

Counter Enable) which is located in the T2MOD register (see

Figure 9). When reset is applied the DCEN = 0 which means Timer

2 will default to counting up. If DCEN bit is set, Timer 2 can count up

or down depending on the value of the T2EX pin.

Figure 10 shows Timer 2 which will count up automatically since

DCEN = 0. In this mode there are two options selected by bit

EXEN2 in T2CON register. If EXEN2 = 0, then Timer 2 counts up to

0FFFFH and sets the TF2 (Overflow Flag) bit upon overflow. This

causes the Timer 2 registers to be reloaded with the 16-bit value in

RCAP2L and RCAP2H. The values in RCAP2L and RCAP2H are

preset by software means.

If EXEN2 = 1, then a 16-bit reload can be triggered either by an

overflow or by a 1-to-0 transition at input T2EX. This transition also

sets the EXF2 bit. The Timer 2 interrupt, if enabled, can be

generated when either TF2 or EXF2 are 1.

In Figure 11 DCEN = 1 which enables Timer 2 to count up or down.

This mode allows pin T2EX to control the direction of count. When a

logic 1 is applied at pin T2EX Timer 2 will count up. Timer 2 will

overflow at 0FFFFH and set the TF2 flag, which can then generate

an interrupt, if the interrupt is enabled. This timer overflow also

causes the 16-bit value in RCAP2L and RCAP2H to be reloaded

into the timer registers TL2 and TH2.

When a logic 0 is applied at pin T2EX this causes Timer 2 to count

down. The timer will underflow when TL2 and TH2 become equal to

the value stored in RCAP2L and RCAP2H. Timer 2 underflow sets

the TF2 flag and causes 0FFFFH to be reloaded into the timer

registers TL2 and TH2.

The external flag EXF2 toggles when Timer 2 underflows or overflows.

This EXF2 bit can be used as a 17th bit of resolution if needed. The

EXF2 flag does not generate an interrupt in this mode of operation.

(MSB)

(LSB)

Symbol

Position

Name and Significance

TF2

T2CON.7

Timer 2 overflow flag set by a Timer 2 overflow and must be cleared by software. TF2 will not be set

when either RCLK or TCLK = 1.

EXF2

T2CON.6

Timer 2 external flag set when either a capture or reload is caused by a negative transition on T2EX and

EXEN2 = 1. When Timer 2 interrupt is enabled, EXF2 = 1 will cause the CPU to vector to the Timer 2

interrupt routine. EXF2 must be cleared by software. EXF2 does not cause an interrupt in up/down

counter mode (DCEN = 1).

RCLK

T2CON.5

Receive clock flag. When set, causes the serial port to use Timer 2 overflow pulses for its receive clock

in modes 1 and 3. RCLK = 0 causes Timer 1 overflow to be used for the receive clock.

TCLK

T2CON.4

Transmit clock flag. When set, causes the serial port to use Timer 2 overflow pulses for its transmit clock

in modes 1 and 3. TCLK = 0 causes Timer 1 overflows to be used for the transmit clock.

EXEN2

T2CON.3

Timer 2 external enable flag. When set, allows a capture or reload to occur as a result of a negative

transition on T2EX if Timer 2 is not being used to clock the serial port. EXEN2 = 0 causes Timer 2 to

ignore events at T2EX.

TR2

T2CON.2

Start/stop control for Timer 2. A logic 1 starts the timer.

C/T2

T2CON.1

Timer or counter select. (Timer 2)

0 = Internal timer (OSC/6 in 6-clock mode or OSC/12 in 12-clock mode)

1 = External event counter (falling edge triggered).

CP/RL2

T2CON.0

Capture/Reload flag. When set, captures will occur on negative transitions at T2EX if EXEN2 = 1. When

cleared, auto-reloads will occur either with Timer 2 overflows or negative transitions at T2EX when

EXEN2 = 1. When either RCLK = 1 or TCLK = 1, this bit is ignored and the timer is forced to auto-reload

on Timer 2 overflow.

TF2

EXF2

RCLK

TCLK

EXEN2

TR2

C/T2

CP/RL2

SU01251

Figure 7. Timer/Counter 2 (T2CON) Control Register

Philips Semiconductors

Product data

P83C654X2/P87C654X2

80C51 8-bit microcontroller family

16 kB OTP/ROM,

256B RAM, low voltage (2.7 to 5.5 V), low power, high speed

(30/33 MHz)

2004 Apr 20

17

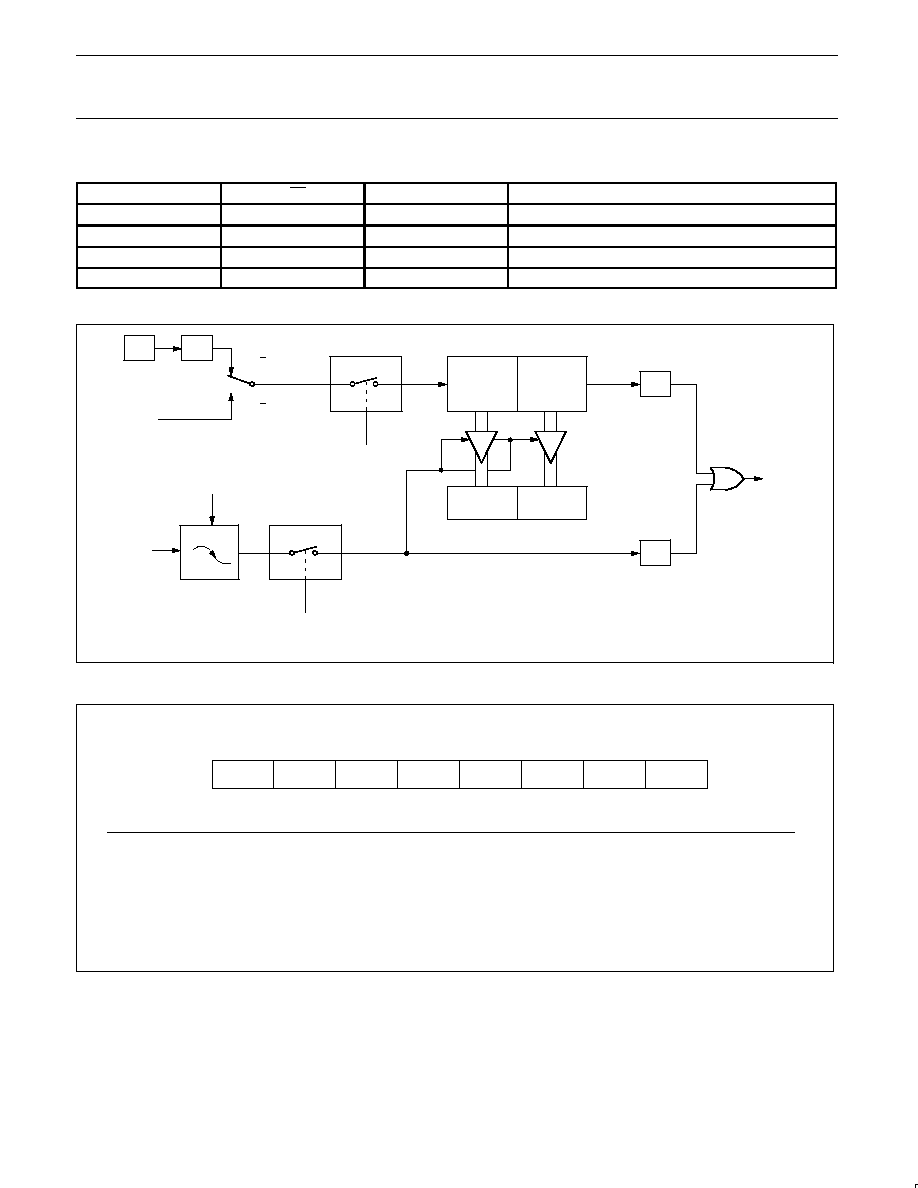

Table 3.

Timer 2 Operating Modes

RCLK + TCLK

CP/RL2

TR2

MODE

0

0

1

16-bit Auto-reload

0

1

1

16-bit Capture

1

X

1

Baud rate generator

X

X

0

(off)

OSC

˜

n*

C/T2 = 0

C/T2 = 1

TR2

Control

TL2

(8 BITS)

TH2

(8 BITS)

TF2

RCAP2L

RCAP2H

EXEN2

Control

EXF2

Timer 2

Interrupt

T2EX Pin

Transition

Detector

T2 Pin

Capture

SU01252

* n = 6 in 6-clock mode, or 12 in 12-clock mode.

Figure 8. Timer 2 in Capture Mode

Not Bit Addressable

Symbol

Function

--

Not implemented, reserved for future use.*

T2OE

Timer 2 Output Enable bit.

DCEN

Down Count Enable bit. When set, this allows Timer 2 to be configured as an up/down counter.

--

--

--

--

--

--

T2OE

DCEN

SU00729

7

6

5

4

3

2

1

0

*

User software should not write 1s to reserved bits. These bits may be used in future 8051 family products to invoke new features.

In that case, the reset or inactive value of the new bit will be 0, and its active value will be 1. The value read from a reserved bit is

indeterminate.

Bit

T2MOD

Address = 0C9H

Reset Value = XXXX XX00B

Figure 9. Timer 2 Mode (T2MOD) Control Register

Philips Semiconductors

Product data

P83C654X2/P87C654X2

80C51 8-bit microcontroller family

16 kB OTP/ROM,

256B RAM, low voltage (2.7 to 5.5 V), low power, high speed

(30/33 MHz)

2004 Apr 20

18

OSC

˜

n*

C/T2 = 0

C/T2 = 1

TR2

CONTROL

TL2

(8 BITS)

TH2

(8 BITS)

TF2

RCAP2L

RCAP2H

EXEN2

CONTROL

EXF2

TIMER 2

INTERRUPT

T2EX PIN

TRANSITION

DETECTOR

T2 PIN

RELOAD

SU01253

* n = 6 in 6-clock mode, or 12 in 12-clock mode.

Figure 10. Timer 2 in Auto-Reload Mode (DCEN = 0)

˜

n*

C/T2 = 0

C/T2 = 1

TL2

TH2

TR2

CONTROL

T2 PIN

SU01254

FFH

FFH

RCAP2L

RCAP2H

(UP COUNTING RELOAD VALUE)

T2EX PIN

TF2

INTERRUPT

COUNT

DIRECTION

1 = UP

0 = DOWN

EXF2

OVERFLOW

(DOWN COUNTING RELOAD VALUE)

TOGGLE

OSC

* n = 6 in 6-clock mode, or 12 in 12-clock mode.

Figure 11. Timer 2 Auto Reload Mode (DCEN = 1)

Philips Semiconductors

Product data

P83C654X2/P87C654X2

80C51 8-bit microcontroller family

16 kB OTP/ROM,

256B RAM, low voltage (2.7 to 5.5 V), low power, high speed

(30/33 MHz)

2004 Apr 20

19

C/T2 = 0

C/T2 = 1

TR2

Control

TL2

(8-bits)

TH2

(8-bits)

˜

16

RCAP2L

RCAP2H

EXEN2

Control

EXF2

Timer 2

Interrupt

T2EX Pin

Transition

Detector

Reload

˜

2

"0"

"1"

RX Clock

˜

16

TX Clock

"0"

"1"

"0"

"1"

Timer 1

Overflow

Note availability of additional external interrupt.

SMOD

RCLK

TCLK

SU01629

n = 1 in 6-clock mode

n = 2 in 12-clock mode

OSC

˜

n

T2 Pin

Figure 12. Timer 2 in Baud Rate Generator Mode

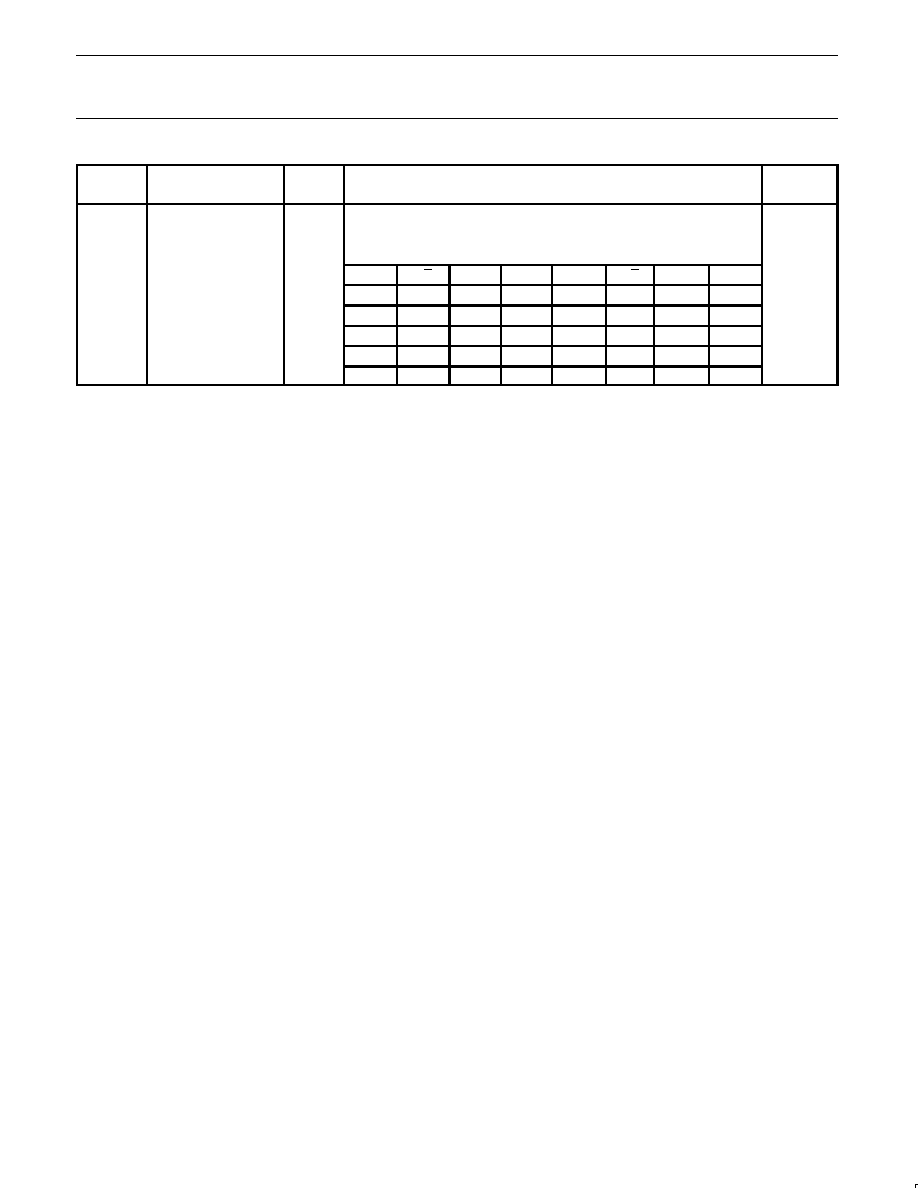

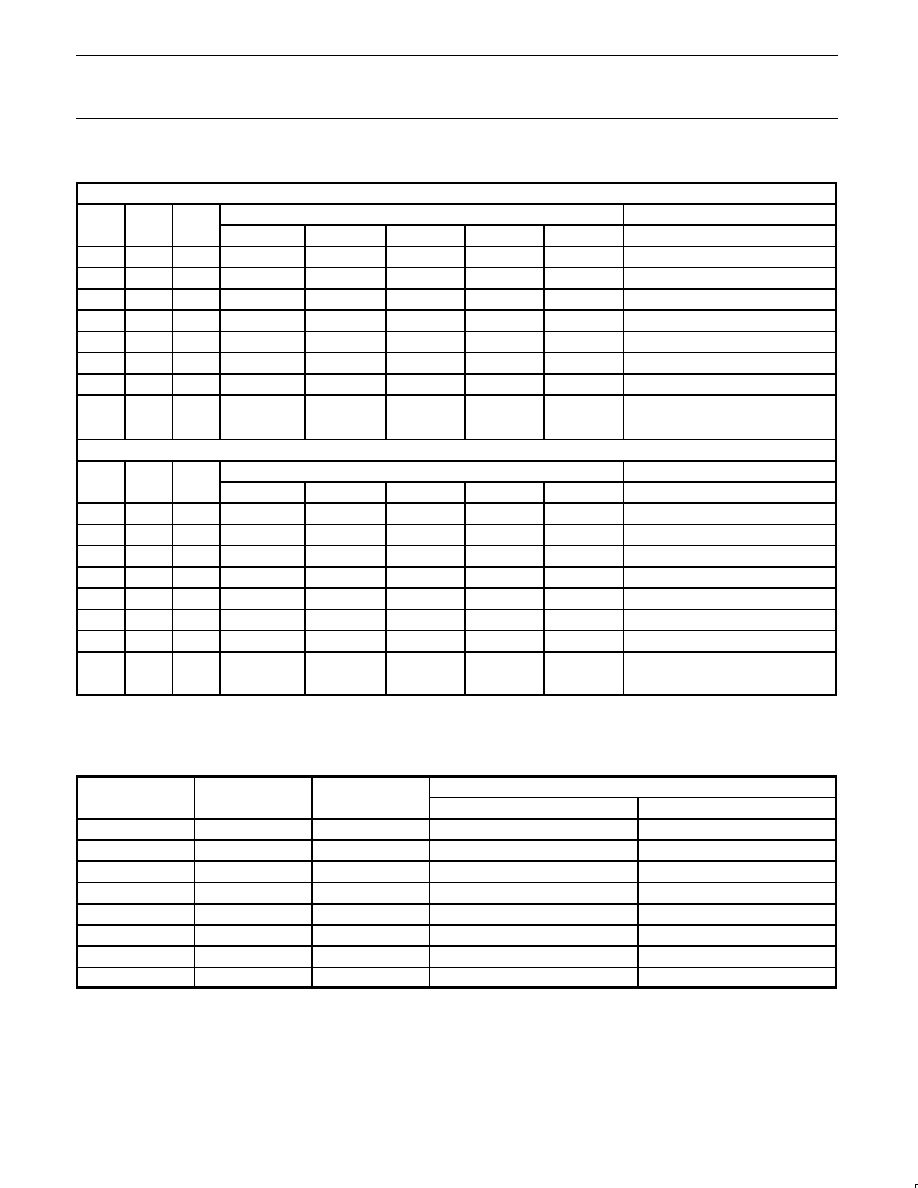

Table 4.

Timer 2 Generated Commonly Used

Baud Rates

Baud Rate

Timer 2

12-clock

mode

6-clock

mode

Osc Freq

RCAP2H

RCAP2L

375 k

750 k

12 MHz

FF

FF

9.6 k

19.2 k

12 MHz

FF

D9

4.8 k

9.6 k

12 MHz

FF

B2

2.4 k

4.8 k

12 MHz

FF

64

1.2 k

2.4 k

12 MHz

FE

C8

300

600

12 MHz

FB

1E

110

220

12 MHz

F2

AF

300

600

6 MHz

FD

8F

110

220

6 MHz

F9

57

Baud Rate Generator Mode

Bits TCLK and/or RCLK in T2CON (Table 4) allow the serial port

transmit and receive baud rates to be derived from either Timer 1 or

Timer 2. When TCLK = 0, Timer 1 is used as the serial port transmit

baud rate generator. When TCLK = 1, Timer 2 is used as the serial

port transmit baud rate generator. RCLK has the same effect for the

serial port receive baud rate. With these two bits, the serial port can

have different receive and transmit baud rates ≠ one generated by

Timer 1, the other by Timer 2.

Figure 12 shows the Timer 2 in baud rate generation mode. The baud

rate generation mode is like the auto-reload mode,in that a rollover in

TH2 causes the Timer 2 registers to be reloaded with the 16-bit value

in registers RCAP2H and RCAP2L, which are preset by software.

The baud rates in modes 1 and 3 are determined by Timer 2's

overflow rate given below:

Modes 1 and 3 Baud Rates

+

Timer 2 Overflow Rate

16

The timer can be configured for either "timer" or "counter" operation.

In many applications, it is configured for "timer" operation (C/T2 = 0).

Timer operation is different for Timer 2 when it is being used as a

baud rate generator.

Usually, as a timer it would increment every machine cycle (i.e.,

1

/

6

the oscillator frequency in 6-clock mode,

1

/

12

the oscillator

frequency in 12-clock mode). As a baud rate generator, it

increments at the oscillator frequency in 6-clock mode (

OSC

/

2

in

12-clock mode). Thus the baud rate formula is as follows:

Oscillator Frequency

[ n *

[65536

*

(RCAP2H, RCAP2L)]]

Modes 1 and 3 Baud Rates =

* n =

16 in 6-clock mode

32 in 12-clock mode

Where:

(RCAP2H, RCAP2L)= The content of RCAP2H and

RCAP2L taken as a 16-bit unsigned integer.

The Timer 2 as a baud rate generator mode shown in Figure 12, is

valid only if RCLK and/or TCLK = 1 in T2CON register. Note that a

rollover in TH2 does not set TF2, and will not generate an interrupt.

Thus, the Timer 2 interrupt does not have to be disabled when

Timer 2 is in the baud rate generator mode. Also if the EXEN2

(T2 external enable flag) is set, a 1-to-0 transition in T2EX

(Timer/counter 2 trigger input) will set EXF2 (T2 external flag) but

will not cause a reload from (RCAP2H, RCAP2L) to (TH2,TL2).

Therefore when Timer 2 is in use as a baud rate generator, T2EX

can be used as an additional external interrupt, if needed.

Philips Semiconductors

Product data

P83C654X2/P87C654X2

80C51 8-bit microcontroller family

16 kB OTP/ROM,

256B RAM, low voltage (2.7 to 5.5 V), low power, high speed

(30/33 MHz)

2004 Apr 20

20

When Timer 2 is in the baud rate generator mode, one should not try

to read or write TH2 and TL2. As a baud rate generator, Timer 2 is

incremented every state time (osc/2) or asynchronously from pin T2;

under these conditions, a read or write of TH2 or TL2 may not be

accurate. The RCAP2 registers may be read, but should not be

written to, because a write might overlap a reload and cause write

and/or reload errors. The timer should be turned off (clear TR2)

before accessing the Timer 2 or RCAP2 registers.

Table 4 shows commonly used baud rates and how they can be

obtained from Timer 2.

Summary of Baud Rate Equations

Timer 2 is in baud rate generating mode. If Timer 2 is being clocked

through pin T2 (P1.0) the baud rate is:

Baud Rate

+

Timer 2 Overflow Rate

16

If Timer 2 is being clocked internally, the baud rate is:

Baud Rate

+

f

OSC

[ n *

[65536

*

(RCAP2H, RCAP2L)]]

* n =

16 in 6-clock mode

32 in 12-clock mode

Where f

osc

= Oscillator Frequency

To obtain the reload value for RCAP2H and RCAP2L, the above

equation can be rewritten as:

RCAP2H, RCAP2L

+

65536

*

f

OSC

n *

Baud Rate

Timer/Counter 2 Set-up

Except for the baud rate generator mode, the values given for T2CON

do not include the setting of the TR2 bit. Therefore, bit TR2 must be

set, separately, to turn the timer on. see Table 5 for set-up of Timer 2

as a timer. Also see Table 6 for set-up of Timer 2 as a counter.

Table 5.

Timer 2 as a Timer

T2CON

MODE

INTERNAL CONTROL

(Note 1)

EXTERNAL CONTROL

(Note 2)

16-bit Auto-Reload

00H

08H

16-bit Capture

01H

09H

Baud rate generator receive and transmit same baud rate

34H

36H

Receive only

24H

26H

Transmit only

14H

16H

Table 6.

Timer 2 as a Counter

TMOD

MODE

INTERNAL CONTROL

(Note 1)

EXTERNAL CONTROL

(Note 2)

16-bit

02H

0AH

Auto-Reload

03H

0BH

NOTES:

1. Capture/reload occurs only on timer/counter overflow.

2. Capture/reload occurs on timer/counter overflow and a 1-to-0 transition on T2EX (P1.1) pin except when Timer 2 is used in the baud rate

generator mode.

Philips Semiconductors

Product data

P83C654X2/P87C654X2

80C51 8-bit microcontroller family

16 kB OTP/ROM,

256B RAM, low voltage (2.7 to 5.5 V), low power, high speed

(30/33 MHz)

2004 Apr 20

21

FULL-DUPLEX ENHANCED UART

Standard UART operation

The serial port is full duplex, meaning it can transmit and receive

simultaneously. It is also receive-buffered, meaning it can

commence reception of a second byte before a previously received

byte has been read from the register. (However, if the first byte still

hasn't been read by the time reception of the second byte is

complete, one of the bytes will be lost.) The serial port receive and

transmit registers are both accessed at Special Function Register

SBUF. Writing to SBUF loads the transmit register, and reading

SBUF accesses a physically separate receive register.

The serial port can operate in 4 modes:

Mode 0:

Serial data enters and exits through RxD. TxD outputs

the shift clock. 8 bits are transmitted/received (LSB first).

The baud rate is fixed at 1/12 the oscillator frequency in

12-clock mode or 1/6 the oscillator frequency in 6-clock

mode.

Mode 1:

10 bits are transmitted (through TxD) or received

(through RxD): a start bit (0), 8 data bits (LSB first), and

a stop bit (1). On receive, the stop bit goes into RB8 in

Special Function Register SCON. The baud rate is

variable.

Mode 2:

11 bits are transmitted (through TxD) or received

(through RxD): start bit (0), 8 data bits (LSB first), a

programmable 9th data bit, and a stop bit (1). On

Transmit, the 9th data bit (TB8 in SCON) can be

assigned the value of 0 or 1. Or, for example, the parity

bit (P, in the PSW) could be moved into TB8. On receive,

the 9th data bit goes into RB8 in Special Function

Register SCON, while the stop bit is ignored. The baud

rate is programmable to either 1/32 or 1/64 the oscillator

frequency in 12-clock mode or 1/16 or 1/32 the oscillator

frequency in 6-clock mode.

Mode 3:

11 bits are transmitted (through TxD) or received

(through RxD): a start bit (0), 8 data bits (LSB first), a

programmable 9th data bit, and a stop bit (1). In fact,

Mode 3 is the same as Mode 2 in all respects except

baud rate. The baud rate in Mode 3 is variable.

In all four modes, transmission is initiated by any instruction that

uses SBUF as a destination register. Reception is initiated in Mode 0

by the condition RI = 0 and REN = 1. Reception is initiated in the

other modes by the incoming start bit if REN = 1.

Multiprocessor Communications

Modes 2 and 3 have a special provision for multiprocessor

communications. In these modes, 9 data bits are received. The 9th

one goes into RB8. Then comes a stop bit. The port can be

programmed such that when the stop bit is received, the serial port

interrupt will be activated only if RB8 = 1. This feature is enabled by

setting bit SM2 in SCON. A way to use this feature in multiprocessor

systems is as follows:

When the master processor wants to transmit a block of data to one

of several slaves, it first sends out an address byte which identifies

the target slave. An address byte differs from a data byte in that the

9th bit is 1 in an address byte and 0 in a data byte. With SM2 = 1, no

slave will be interrupted by a data byte. An address byte, however,

will interrupt all slaves, so that each slave can examine the received

byte and see if it is being addressed. The addressed slave will clear

its SM2 bit and prepare to receive the data bytes that will be coming.

The slaves that weren't being addressed leave their SM2s set and

go on about their business, ignoring the coming data bytes.

SM2 has no effect in Mode 0, and in Mode 1 can be used to check

the validity of the stop bit. In a Mode 1 reception, if SM2 = 1, the

receive interrupt will not be activated unless a valid stop bit is

received.

Serial Port Control Register

The serial port control and status register is the Special Function

Register SCON, shown in Figure 13. This register contains not only

the mode selection bits, but also the 9th data bit for transmit and

receive (TB8 and RB8), and the serial port interrupt bits (TI and RI).

Baud Rates

The baud rate in Mode 0 is fixed: Mode 0 Baud Rate = Oscillator

Frequency / 12 (12-clock mode) or / 6 (6-clock mode). The baud

rate in Mode 2 depends on the value of bit SMOD in Special

Function Register PCON. If SMOD = 0 (which is the value on reset),

and the port pins in 12-clock mode, the baud rate is 1/64 the

oscillator frequency. If SMOD = 1, the baud rate is 1/32 the oscillator

frequency. In 6-clock mode, the baud rate is 1/32 or 1/16 the

oscillator frequency, respectively.

Mode 2 Baud Rate =

2

SMOD

n

(Oscillator Frequency)

Where:

n = 64 in 12-clock mode, 32 in 6-clock mode

The baud rates in Modes 1 and 3 are determined by the Timer 1 or

Timer 2 overflow rate.

Using Timer 1 to Generate Baud Rates

When Timer 1 is used as the baud rate generator (T2CON.RCLK

= 0, T2CON.TCLK = 0), the baud rates in Modes 1 and 3 are

determined by the Timer 1 overflow rate and the value of SMOD as

follows:

Mode 1, 3 Baud Rate =

2

SMOD

n

(Timer 1 Overflow Rate)

Where:

n = 32 in 12-clock mode, 16 in 6-clock mode

The Timer 1 interrupt should be disabled in this application. The

Timer itself can be configured for either "timer" or "counter"

operation, and in any of its 3 running modes. In the most typical

applications, it is configured for "timer" operation, in the auto-reload

mode (high nibble of TMOD = 0010B). In that case the baud rate is

given by the formula:

Mode 1, 3 Baud Rate =

2

SMOD

n

Oscillator Frequency

12

[256≠(TH1)]

Where:

n = 32 in 12-clock mode, 16 in 6-clock mode

One can achieve very low baud rates with Timer 1 by leaving the

Timer 1 interrupt enabled, and configuring the Timer to run as a

16-bit timer (high nibble of TMOD = 0001B), and using the Timer 1

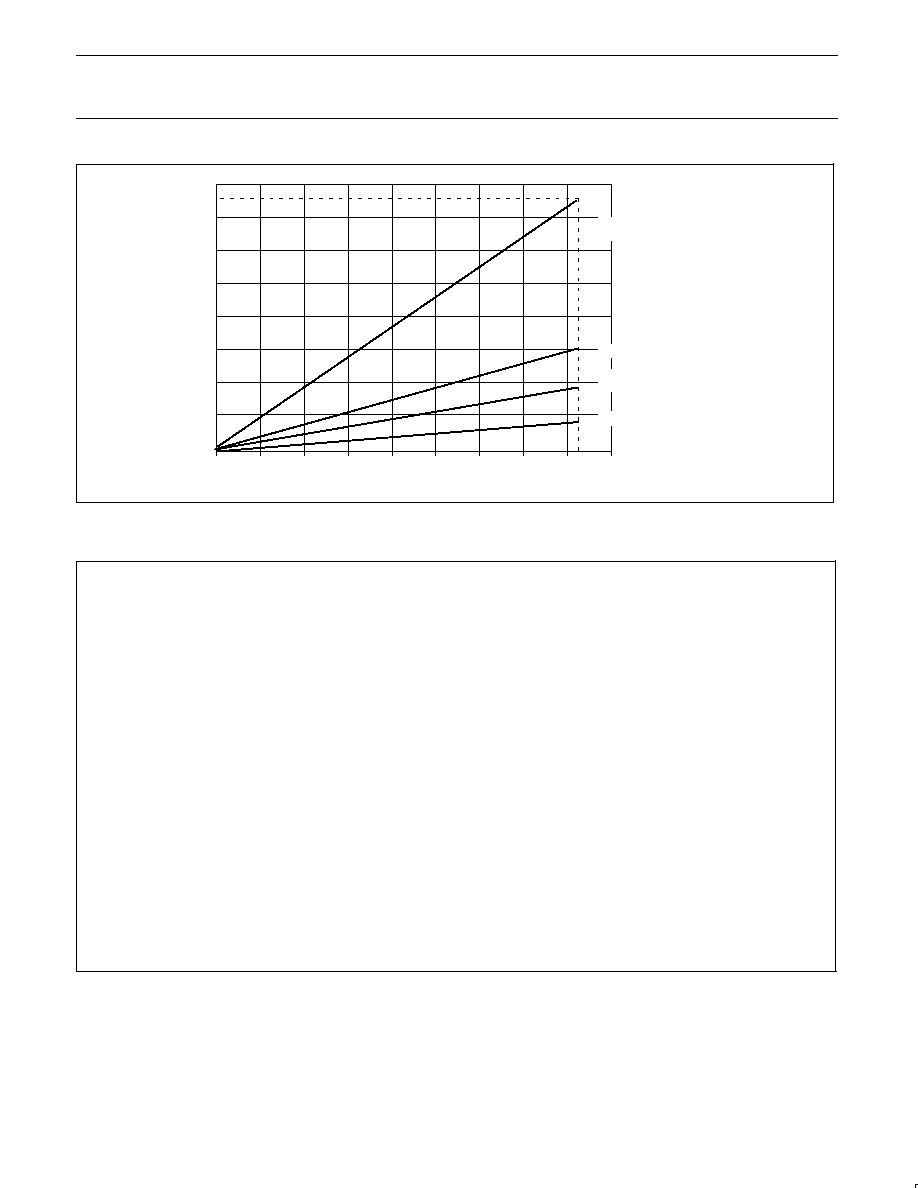

interrupt to do a 16-bit software reload. Figure 14 lists various

commonly used baud rates and how they can be obtained from

Timer 1.

Philips Semiconductors

Product data

P83C654X2/P87C654X2

80C51 8-bit microcontroller family

16 kB OTP/ROM,

256B RAM, low voltage (2.7 to 5.5 V), low power, high speed

(30/33 MHz)

2004 Apr 20

22

SM2

Enables the multiprocessor communication feature in Modes 2 and 3. In Mode 2 or 3, if SM2 is set to 1, then Rl will not be

activated if the received 9th data bit (RB8) is 0. In Mode 1, if SM2=1 then RI will not be activated if a valid stop bit was not

received. In Mode 0, SM2 should be 0.

REN

Enables serial reception. Set by software to enable reception. Clear by software to disable reception.

TB8

The 9th data bit that will be transmitted in Modes 2 and 3. Set or clear by software as desired.

RB8

In Modes 2 and 3, is the 9th data bit that was received. In Mode 1, it SM2=0, RB8 is the stop bit that was received. In Mode 0,

RB8 is not used.

TI

Transmit interrupt flag. Set by hardware at the end of the 8th bit time in Mode 0, or at the beginning of the stop bit in the other

modes, in any serial transmission. Must be cleared by software.

RI

Receive interrupt flag. Set by hardware at the end of the 8th bit time in Mode 0, or halfway through the stop bit time in the other

modes, in any serial reception (except see SM2). Must be cleared by software.

SM0

SM1

SM2

REN

TB8

RB8

TI

RI

Where SM0, SM1 specify the serial port mode, as follows:

SM0

SM1

Mode

Description

Baud Rate

0

0

0

shift register

f

OSC

/12 (12-clock mode) or f

OSC

/6 (6-clock mode)

0

1

1

8-bit UART

variable

1

0

2

9-bit UART

f

OSC

/64 or f

OSC

/32 (12-clock mode) or f

OSC

/32 or f

OSC

/16 (6-clock mode)

1

1

3 9-bit

UART

variable

SU01626

Bit Addressable

SCON

Address = 98H

Reset Value = 00H

7

6

5

4

3

2

1

0

Figure 13. Serial Port Control (SCON) Register

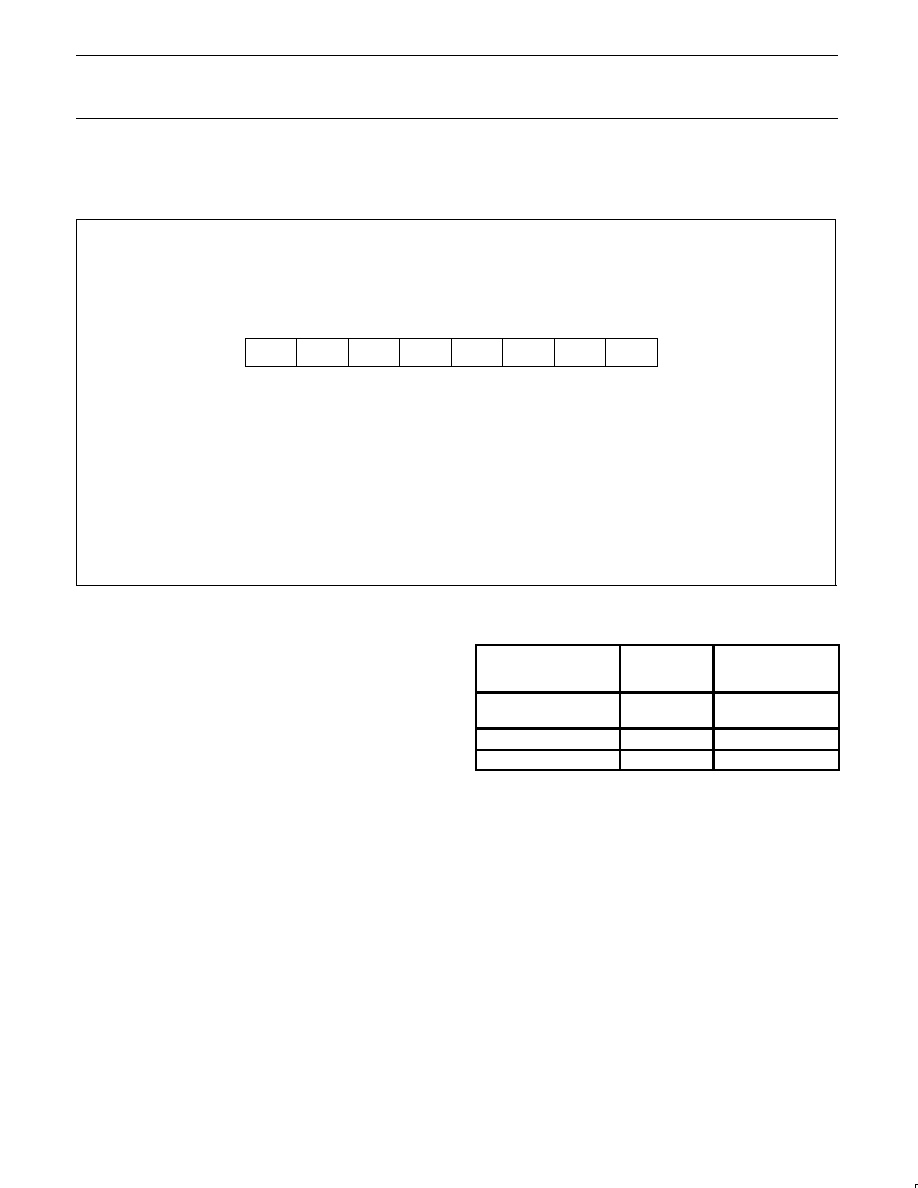

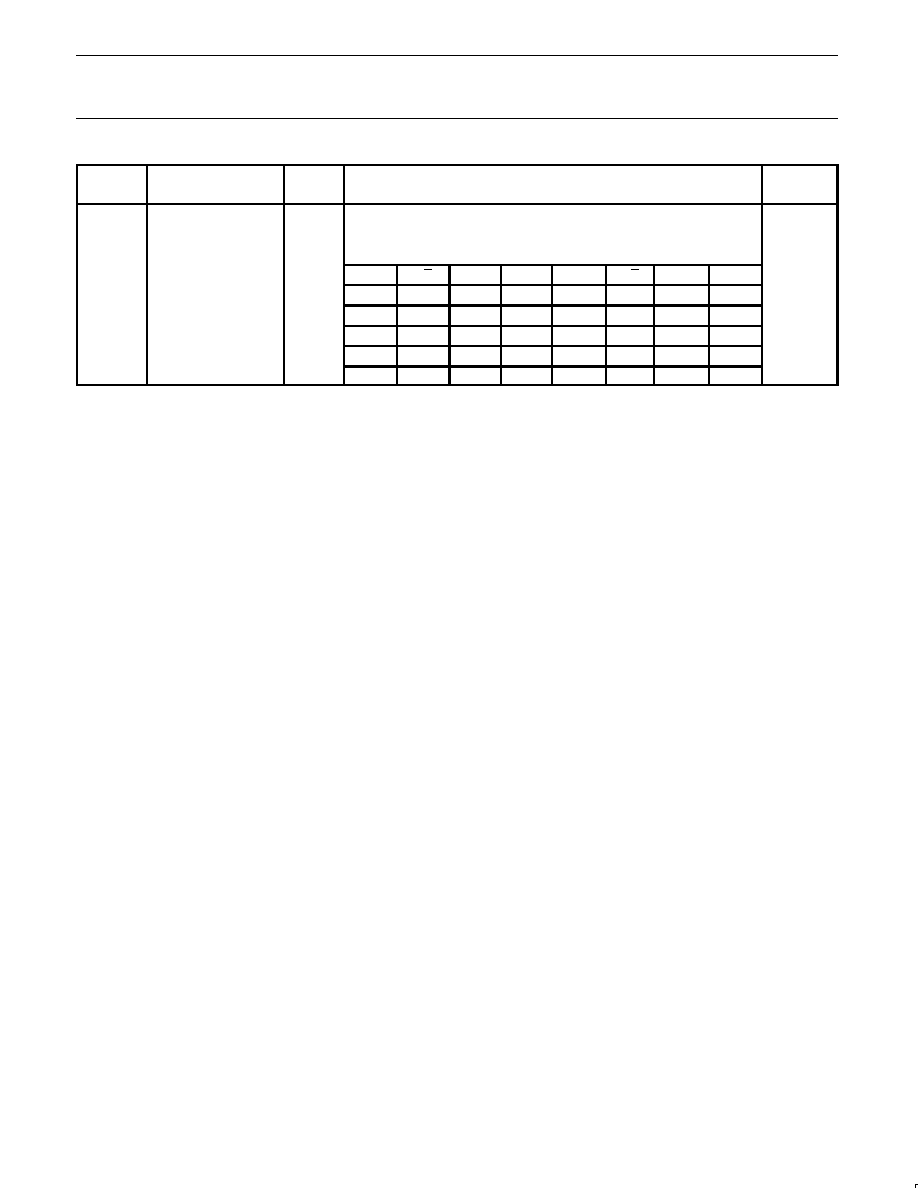

Baud Rate

f

SMOD

Timer 1

Mode

12-clock mode

6-clock mode

f

osc

SMOD

C/T

Mode

Reload Value

Mode 0 Max

1.67 MHz

3.34 MHz

20 MHz

X

X

X

X

Mode 2 Max

625 k

1250 k

20 MHz

1

X

X

X

Mode 1, 3 Max

104.2 k

208.4 k

20 MHz

1

0

2

FFH

Mode 1, 3

19.2 k

38.4 k

11.059 MHz

1

0

2

FDH

9.6 k

19.2 k

11.059 MHz

0

0

2

FDH

4.8 k

9.6 k

11.059 MHz

0

0

2

FAH

2.4 k

4.8 k

11.059 MHz

0

0

2

F4H

1.2 k

2.4 k

11.059 MHz

0

0

2

E8H

137.5

275

11.986 MHz

0

0

2

1DH

110

220

6 MHz

0

0

2

72H

110

220

12 MHz

0

0

1

FEEBH

Figure 14. Timer 1 Generated Commonly Used Baud Rates

More About Mode 0

Serial data enters and exits through RxD. TxD outputs the shift

clock. 8 bits are transmitted/received: 8 data bits (LSB first). The

baud rate is fixed a 1/12 the oscillator frequency (12-clock mode) or

1/6 the oscillator frequency (6-clock mode).

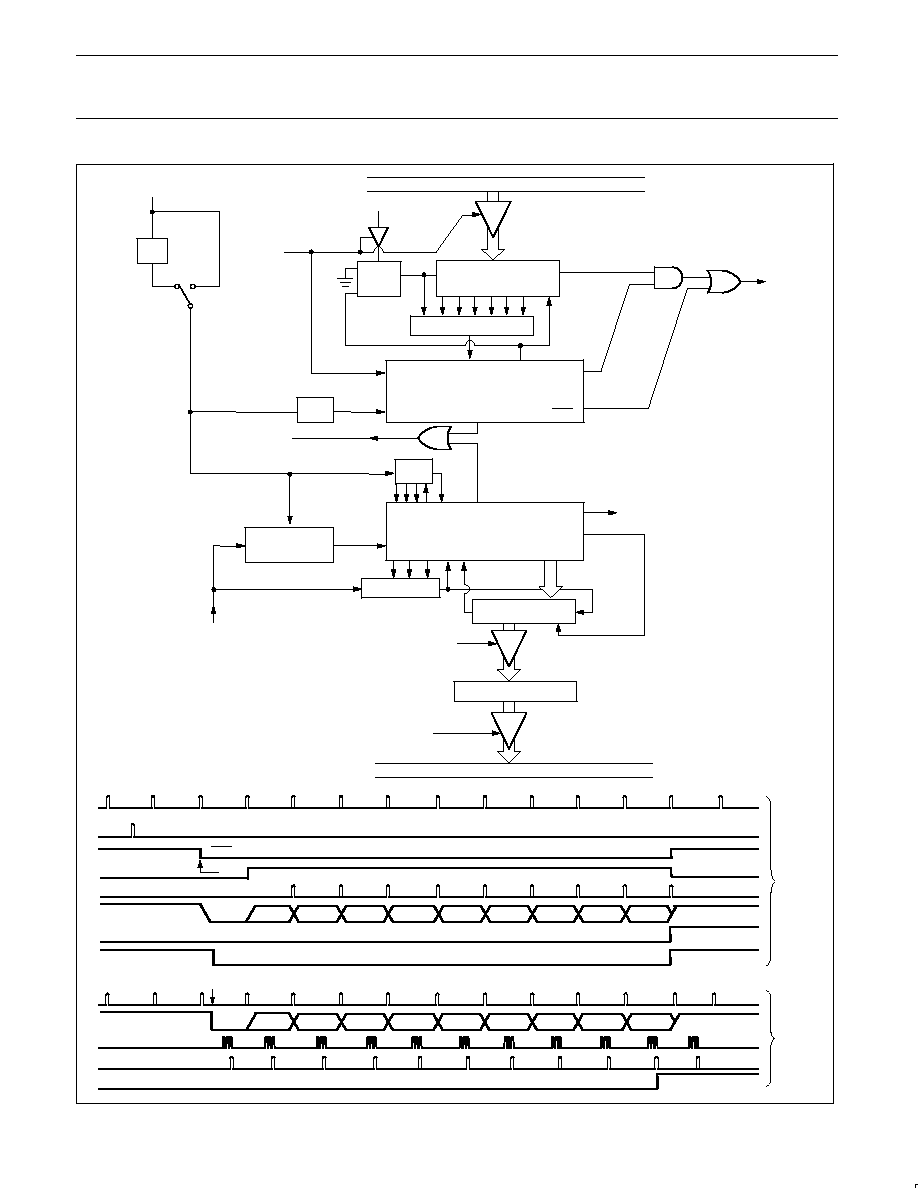

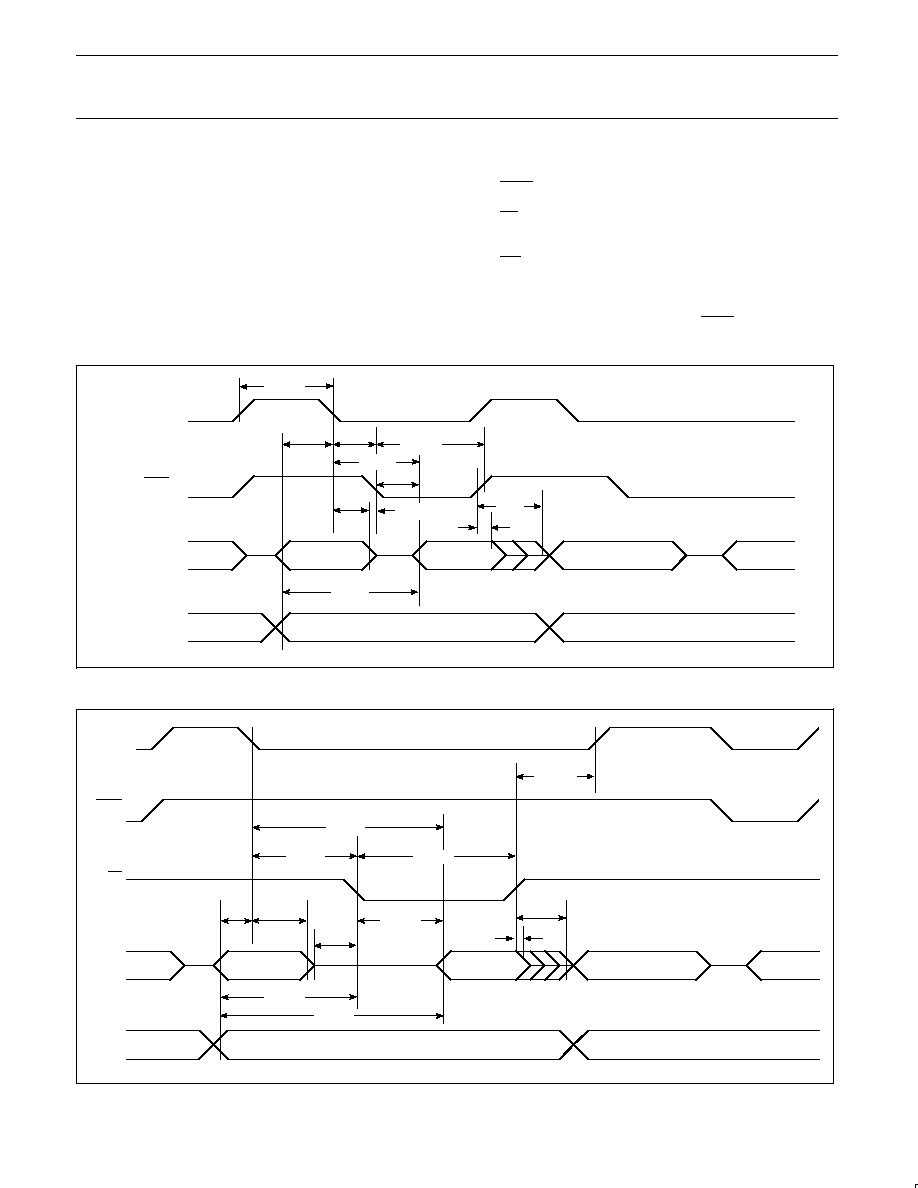

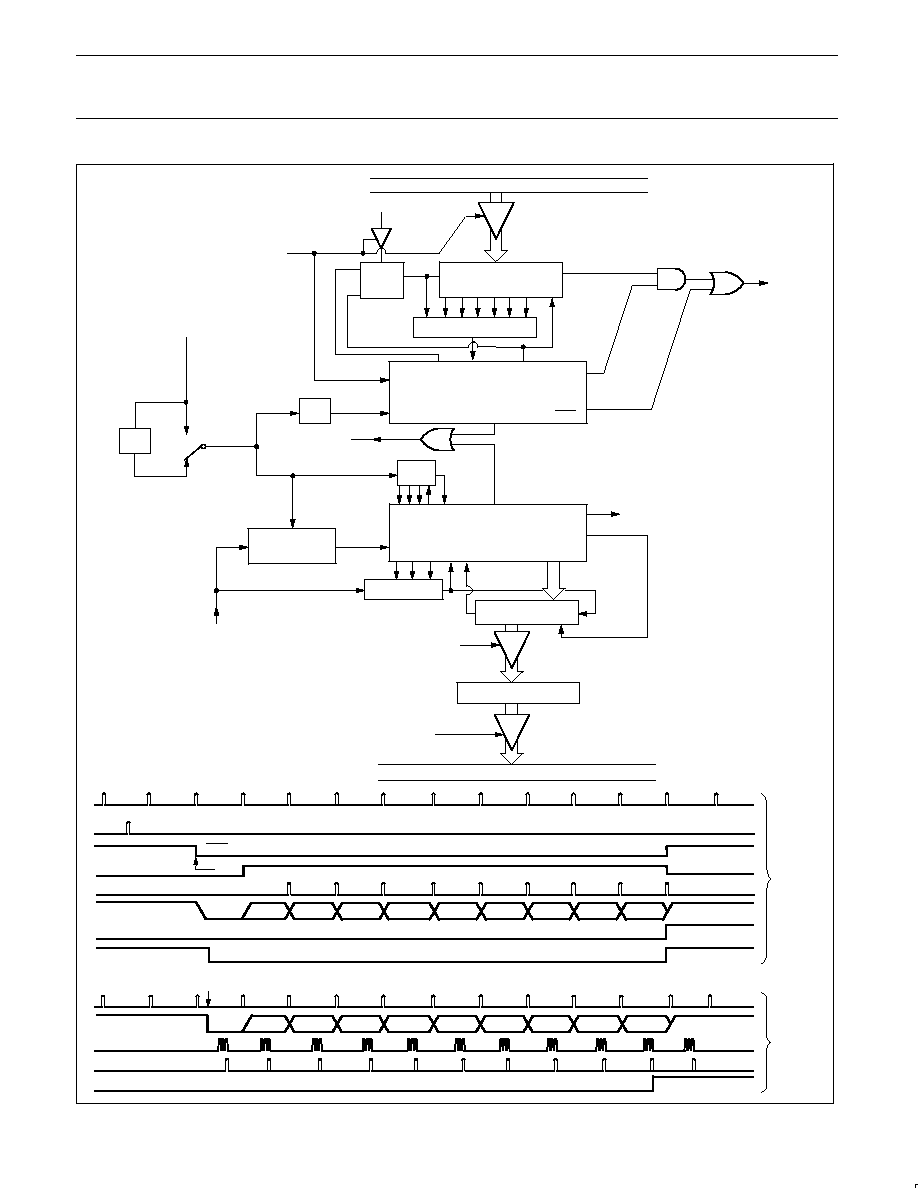

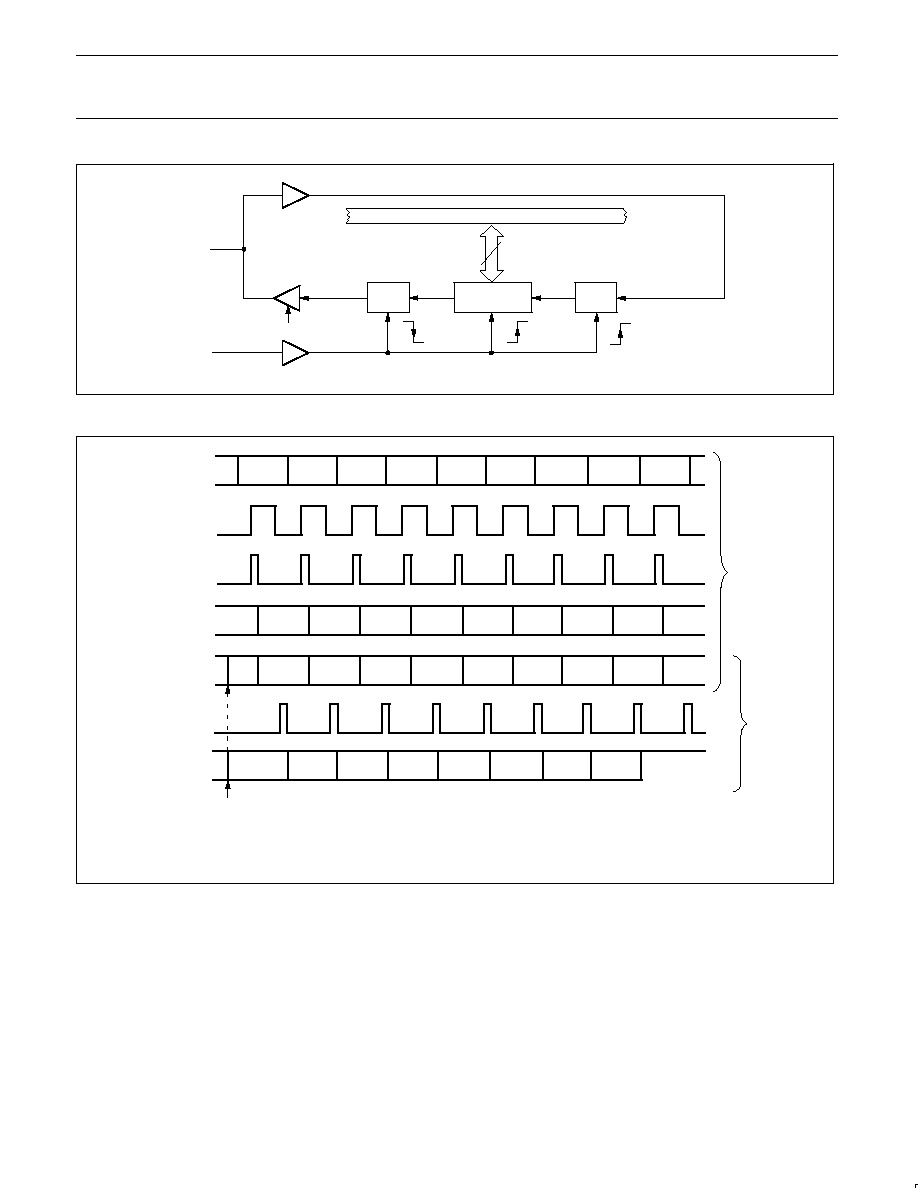

Figure 15 shows a simplified functional diagram of the serial port in

Mode 0, and associated timing.

Transmission is initiated by any instruction that uses SBUF as a

destination register. The "write to SBUF" signal at S6P2 also loads a

1 into the 9th position of the transmit shift register and tells the TX

Control block to commence a transmission. The internal timing is

such that one full machine cycle will elapse between "write to SBUF"

and activation of SEND.

SEND enables the output of the shift register to the alternate output

function line of P3.0 and also enable SHIFT CLOCK to the alternate

output function line of P3.1. SHIFT CLOCK is LOW during S3, S4,

and S5 of every machine cycle, and HIGH during S6, S1, and S2. At

S6P2 of every machine cycle in which SEND is active, the contents

of the transmit shift are shifted to the right one position.

As data bits shift out to the right, zeros come in from the left. When

the MSB of the data byte is at the output position of the shift register,

then the 1 that was initially loaded into the 9th position, is just to the

left of the MSB, and all positions to the left of that contain zeros.

This condition flags the TX Control block to do one last shift and

then deactivate SEND and set T1. Both of these actions occur at

S1P1 of the 10th machine cycle after "write to SBUF."

Reception is initiated by the condition REN = 1 and R1 = 0. At S6P2

of the next machine cycle, the RX Control unit writes the bits

11111110 to the receive shift register, and in the next clock phase

activates RECEIVE.

RECEIVE enable SHIFT CLOCK to the alternate output function line

of P3.1. SHIFT CLOCK makes transitions at S3P1 and S6P1 of

every machine cycle. At S6P2 of every machine cycle in which

RECEIVE is active, the contents of the receive shift register are

Philips Semiconductors

Product data

P83C654X2/P87C654X2

80C51 8-bit microcontroller family

16 kB OTP/ROM,

256B RAM, low voltage (2.7 to 5.5 V), low power, high speed

(30/33 MHz)

2004 Apr 20

23

shifted to the left one position. The value that comes in from the right

is the value that was sampled at the P3.0 pin at S5P2 of the same

machine cycle.

As data bits come in from the right, 1s shift out to the left. When the

0 that was initially loaded into the rightmost position arrives at the

leftmost position in the shift register, it flags the RX Control block to

do one last shift and load SBUF. At S1P1 of the 10th machine cycle

after the write to SCON that cleared RI, RECEIVE is cleared as RI is

set.

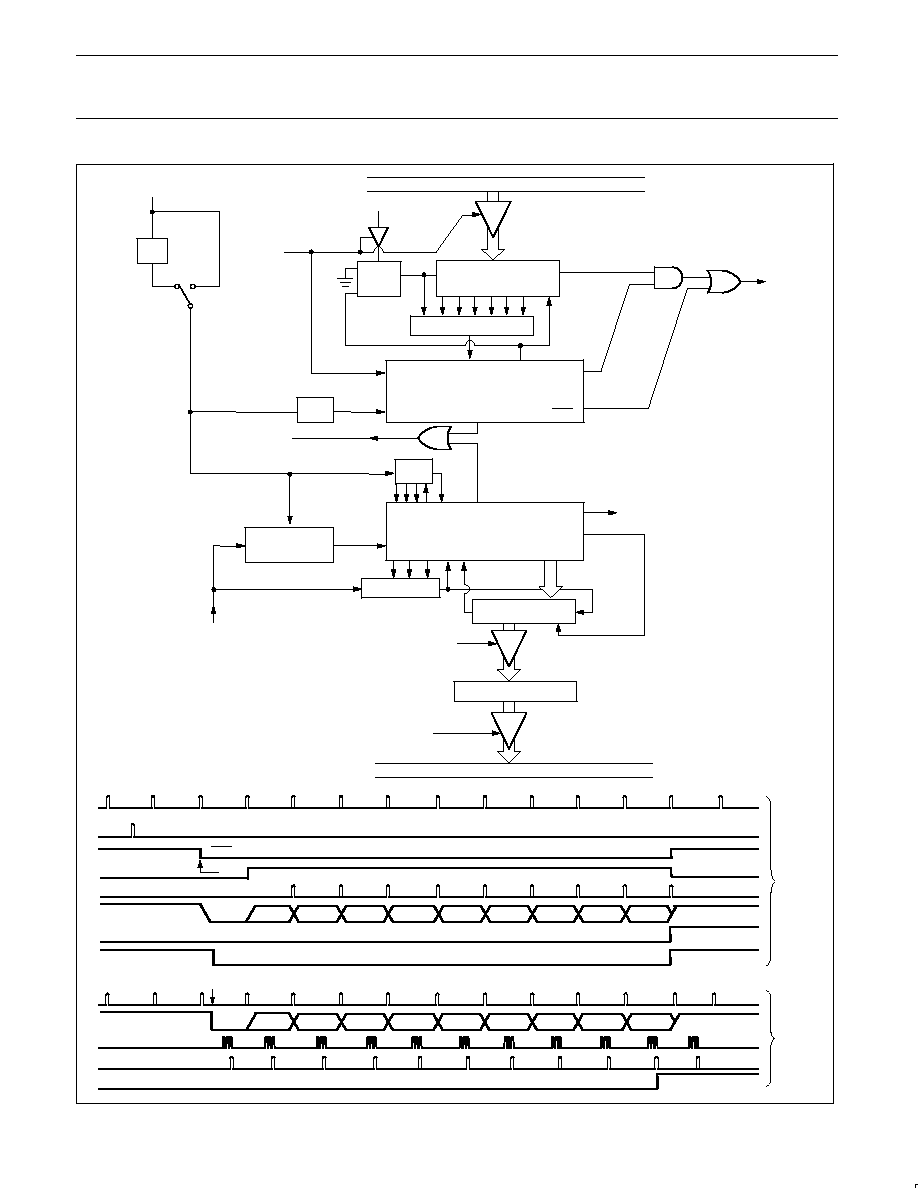

More About Mode 1

Ten bits are transmitted (through TxD), or received (through RxD): a

start bit (0), 8 data bits (LSB first), and a stop bit (1). On receive, the

stop bit goes into RB8 in SCON. In the 80C51 the baud rate is

determined by the Timer 1 or Timer 2 overflow rate.

Figure 16 shows a simplified functional diagram of the serial port in

Mode 1, and associated timings for transmit receive.

Transmission is initiated by any instruction that uses SBUF as a

destination register. The "write to SBUF" signal also loads a 1 into

the 9th bit position of the transmit shift register and flags the TX

Control unit that a transmission is requested. Transmission actually

commences at S1P1 of the machine cycle following the next rollover

in the divide-by-16 counter. (Thus, the bit times are synchronized to

the divide-by-16 counter, not to the "write to SBUF" signal.)

The transmission begins with activation of SEND which puts the

start bit at TxD. One bit time later, DATA is activated, which enables

the output bit of the transmit shift register to TxD. The first shift pulse

occurs one bit time after that.

As data bits shift out to the right, zeros are clocked in from the left.

When the MSB of the data byte is at the output position of the shift

register, then the 1 that was initially loaded into the 9th position is

just to the left of the MSB, and all positions to the left of that contain

zeros. This condition flags the TX Control unit to do one last shift

and then deactivate SEND and set TI. This occurs at the 10th

divide-by-16 rollover after "write to SBUF."

Reception is initiated by a detected 1-to-0 transition at RxD. For this

purpose RxD is sampled at a rate of 16 times whatever baud rate

has been established. When a transition is detected, the

divide-by-16 counter is immediately reset, and 1FFH is written into

the input shift register. Resetting the divide-by-16 counter aligns its

rollovers with the boundaries of the incoming bit times.

The 16 states of the counter divide each bit time into 16ths. At the

7th, 8th, and 9th counter states of each bit time, the bit detector

samples the value of RxD. The value accepted is the value that was

seen in at least 2 of the 3 samples. This is done for noise rejection.

If the value accepted during the first bit time is not 0, the receive

circuits are reset and the unit goes back to looking for another 1-to-0

transition. This is to provide rejection of false start bits. If the start bit

proves valid, it is shifted into the input shift register, and reception of

the rest of the frame will proceed.

As data bits come in from the right, 1s shift out to the left. When the

start bit arrives at the leftmost position in the shift register (which in

mode 1 is a 9-bit register), it flags the RX Control block to do one

last shift, load SBUF and RB8, and set RI. The signal to load SBUF

and RB8, and to set RI, will be generated if, and only if, the following

conditions are met at the time the final shift pulse is generated.:

1. RI = 0, and

2. Either SM2 = 0, or the received stop bit = 1.

If either of these two conditions is not met, the received frame is

irretrievably lost. If both conditions are met, the stop bit goes into

RB8, the 8 data bits go into SBUF, and RI is activated. At this time,

whether the above conditions are met or not, the unit goes back to

looking for a 1-to-0 transition in RxD.

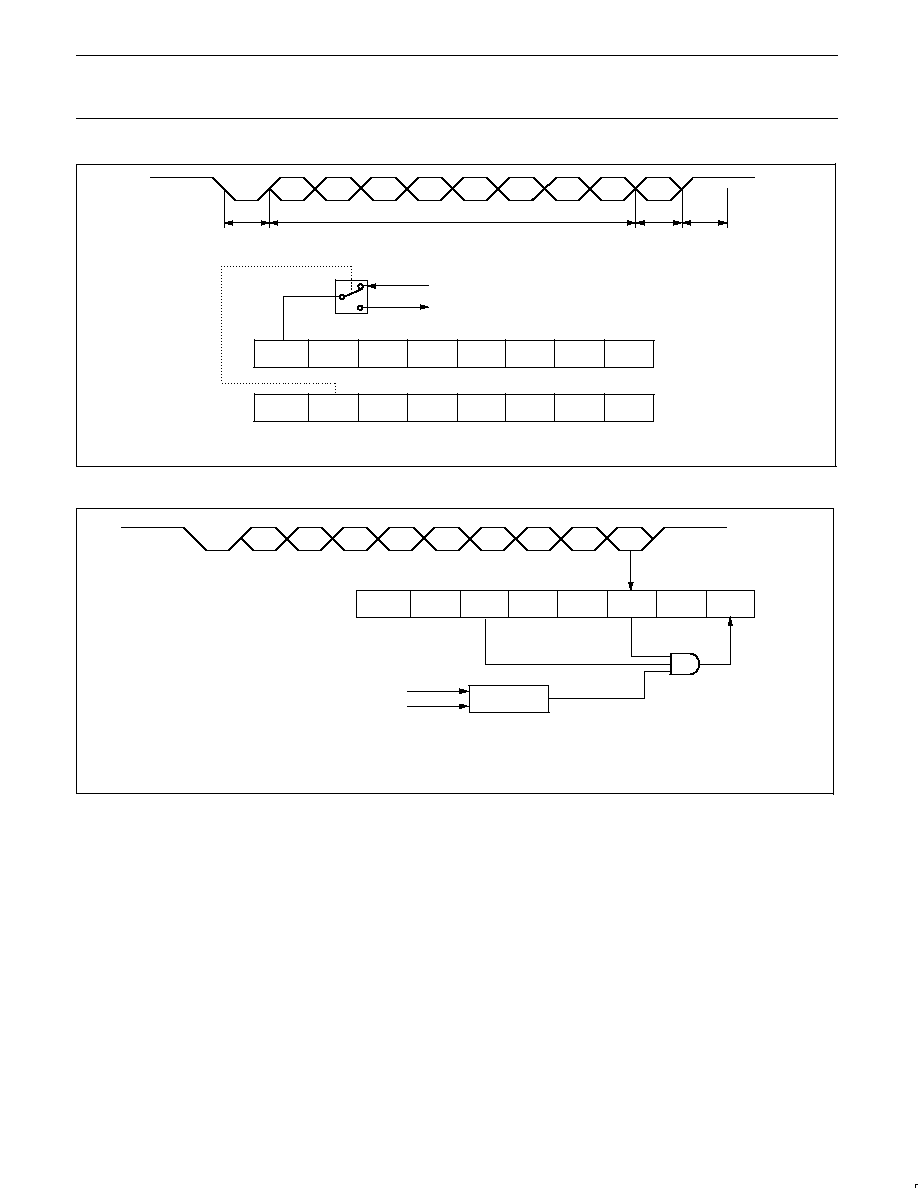

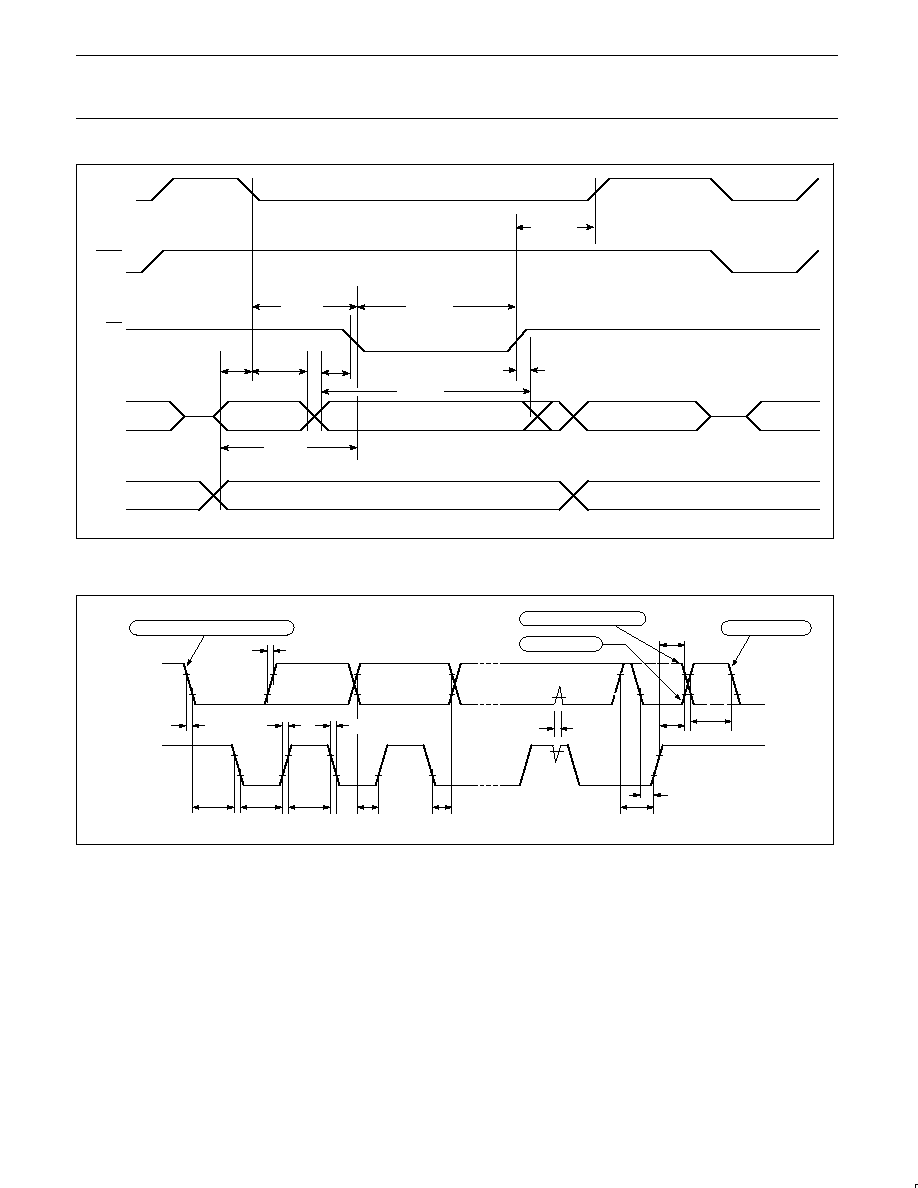

More About Modes 2 and 3

Eleven bits are transmitted (through TxD), or received (through

RxD): a start bit (0), 8 data bits (LSB first), a programmable 9th data

bit, and a stop bit (1). On transmit, the 9th data bit (TB8) can be

assigned the value of 0 or 1. On receive, the 9the data bit goes into

RB8 in SCON. The baud rate is programmable to either 1/32 or 1/64

(12-clock mode) or 1/16 or 1/32 the oscillator frequency (6-clock

mode) the oscillator frequency in Mode 2. Mode 3 may have a

variable baud rate generated from Timer 1 or Timer 2.

Figures 17 and 18 show a functional diagram of the serial port in

Modes 2 and 3. The receive portion is exactly the same as in Mode

1. The transmit portion differs from Mode 1 only in the 9th bit of the

transmit shift register.

Transmission is initiated by any instruction that uses SBUF as a

destination register. The "write to SBUF" signal also loads TB8 into

the 9th bit position of the transmit shift register and flags the TX

Control unit that a transmission is requested. Transmission

commences at S1P1 of the machine cycle following the next rollover

in the divide-by-16 counter. (Thus, the bit times are synchronized to

the divide-by-16 counter, not to the "write to SBUF" signal.)

The transmission begins with activation of SEND, which puts the

start bit at TxD. One bit time later, DATA is activated, which enables

the output bit of the transmit shift register to TxD. The first shift pulse

occurs one bit time after that. The first shift clocks a 1 (the stop bit)

into the 9th bit position of the shift register. Thereafter, only zeros

are clocked in. Thus, as data bits shift out to the right, zeros are

clocked in from the left. When TB8 is at the output position of the

shift register, then the stop bit is just to the left of TB8, and all

positions to the left of that contain zeros. This condition flags the TX

Control unit to do one last shift and then deactivate SEND and set

TI. This occurs at the 11th divide-by-16 rollover after "write to SUBF."

Reception is initiated by a detected 1-to-0 transition at RxD. For this

purpose RxD is sampled at a rate of 16 times whatever baud rate

has been established. When a transition is detected, the

divide-by-16 counter is immediately reset, and 1FFH is written to the

input shift register.

At the 7th, 8th, and 9th counter states of each bit time, the bit

detector samples the value of R-D. The value accepted is the value

that was seen in at least 2 of the 3 samples. If the value accepted

during the first bit time is not 0, the receive circuits are reset and the

unit goes back to looking for another 1-to-0 transition. If the start bit

proves valid, it is shifted into the input shift register, and reception of

the rest of the frame will proceed.

As data bits come in from the right, 1s shift out to the left. When the

start bit arrives at the leftmost position in the shift register (which in

Modes 2 and 3 is a 9-bit register), it flags the RX Control block to do

one last shift, load SBUF and RB8, and set RI.

The signal to load SBUF and RB8, and to set RI, will be generated

if, and only if, the following conditions are met at the time the final

shift pulse is generated.

1. RI = 0, and

2. Either SM2 = 0, or the received 9th data bit = 1.

If either of these conditions is not met, the received frame is

irretrievably lost, and RI is not set. If both conditions are met, the

received 9th data bit goes into RB8, and the first 8 data bits go into