| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: SAA2502 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

DATA SHEET

Preliminary specification

Supersedes data of 1997 Apr 18

File under Integrated Circuits, IC01

1997 Nov 17

INTEGRATED CIRCUITS

SAA2502

ISO/MPEG Audio Source Decoder

1997 Nov 17

2

Philips Semiconductors

Preliminary specification

ISO/MPEG Audio Source Decoder

SAA2502

CONTENTS

1

FEATURES

2

APPLICATIONS

3

GENERAL DESCRIPTION

4

ORDERING INFORMATION

5

BLOCK DIAGRAM

6

PINNING

7

FUNCTIONAL DESCRIPTION

7.1

Basic functionality

7.2

Clock generator module

7.2.1

External sample clock

7.2.2

Free running internal sample clock

7.2.3

Locked internal sample clock

7.2.4

Limited sampling frequency support for internal

sampling clocks

7.3

Input interface module

7.3.1

Master input mode

7.3.2

Slave input mode

7.3.3

Buffer controlled input mode

7.4

Decoder core

7.4.1

Frame synchronization to input data streams

7.4.2

Master input mode bit rate generation

7.4.3

Sample clock generation

7.4.4

Decoder precision

7.4.5

Scale factor CRC protection

7.4.6

Handling of errors in the coded input data

7.4.7

Dynamic range compression

7.4.8

Baseband audio processing

7.4.9

Decoder latency time

7.5

Output interface module

7.5.1

I

2

S output

7.5.2

SPIDF output

7.5.3

Bit serial analog output

7.6

Control interface module

7.6.1

Resetting

7.6.2

Interrupts

7.6.3

Microcontroller interface

7.6.4

Initialization

7.6.5

Transfer protocols

7.6.6

Local registers

8

APPENDIX

8.1

L3 interface specification

8.1.1

Introduction

8.1.2

Example of a data transfer

8.1.3

Timing requirements

8.1.4

Timing

9

LIMITING VALUES

10

DC CHARACTERISTICS

11

AC CHARACTERISTICS

11.1

Host interface: CDATA, CCLK and CMODE

12

APPLICATION INFORMATION

13

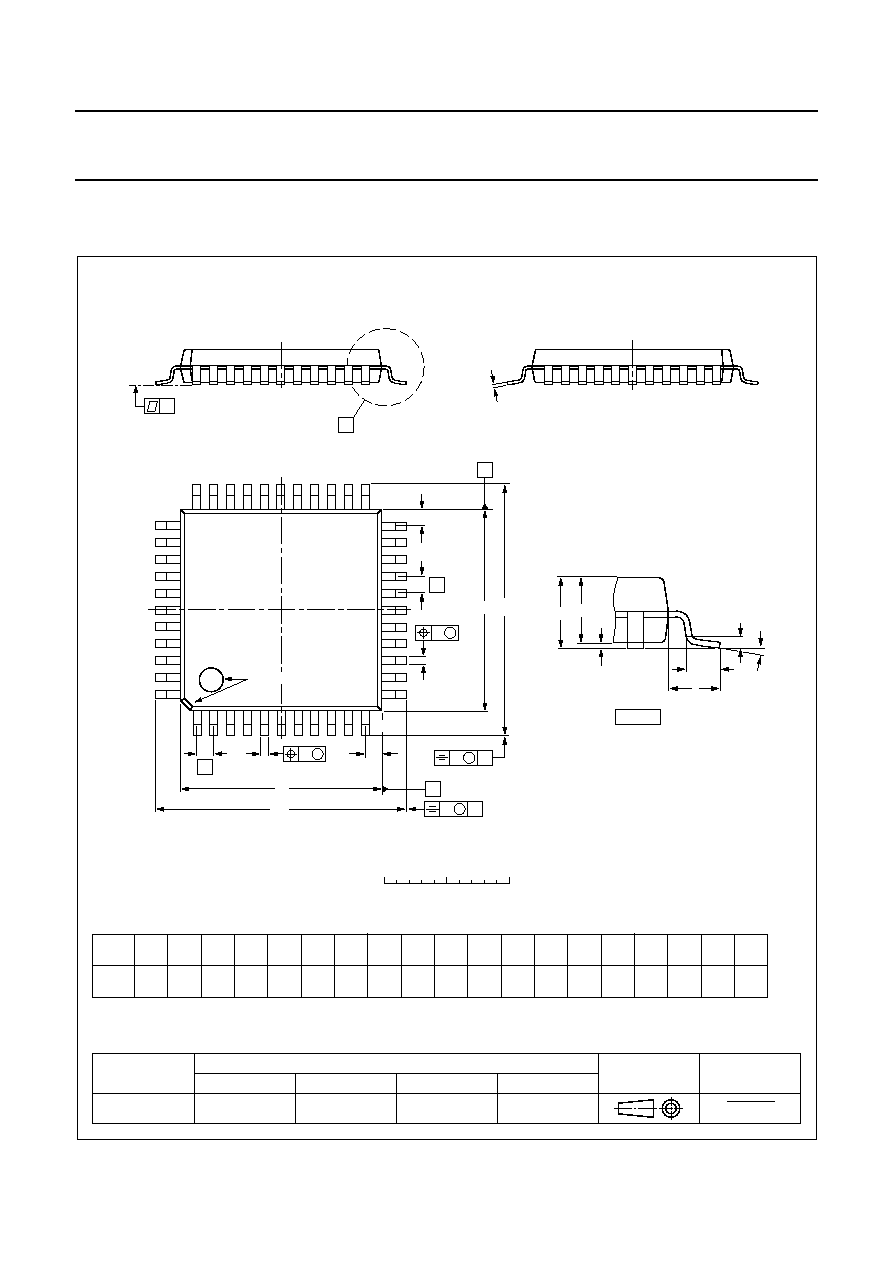

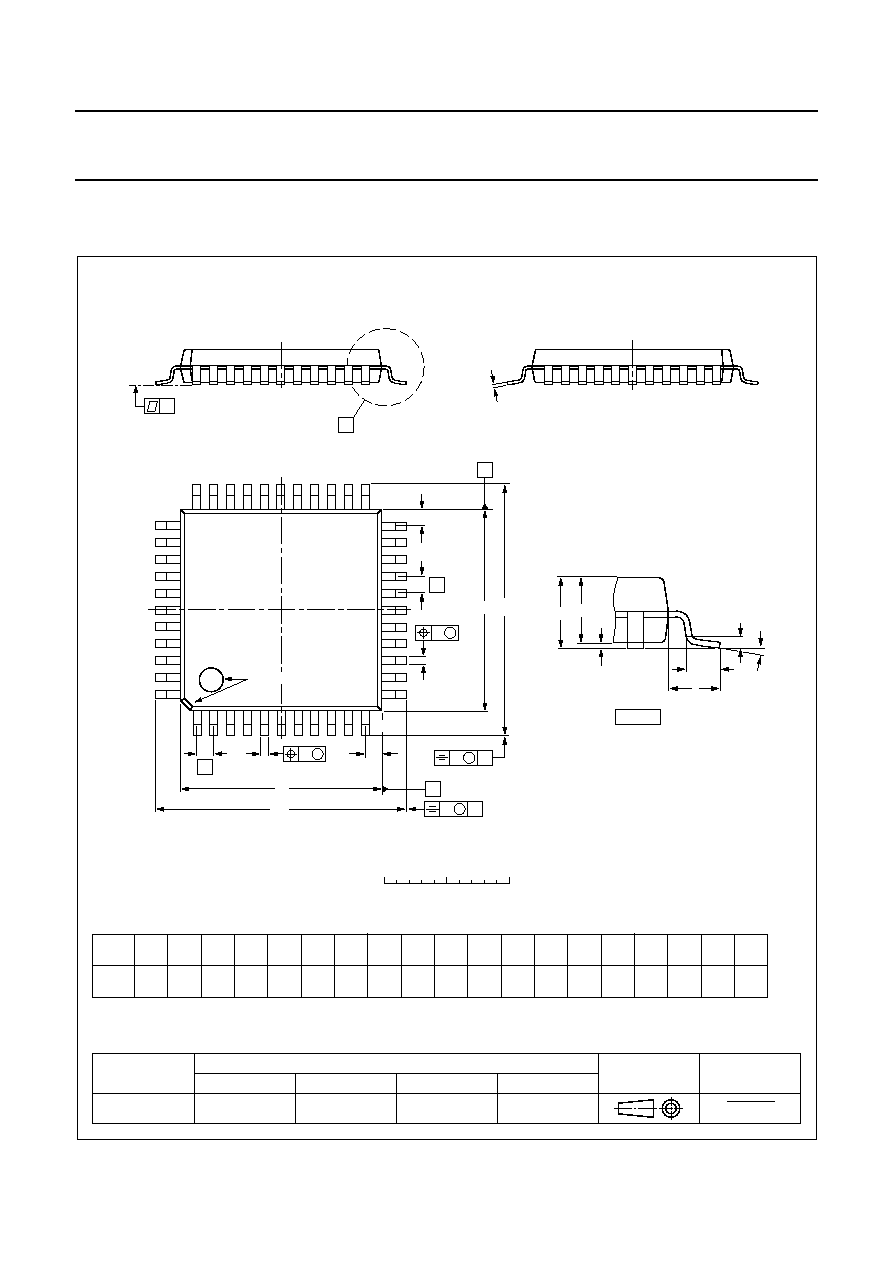

PACKAGE OUTLINE

14

SOLDERING

14.1

Introduction

14.2

Reflow soldering

14.3

Wave soldering

14.4

Repairing soldered joints

15

DEFINITIONS

16

LIFE SUPPORT APPLICATIONS

1997 Nov 17

3

Philips Semiconductors

Preliminary specification

ISO/MPEG Audio Source Decoder

SAA2502

1

FEATURES

∑

Low sampling frequency decoding possibilities (24 kHz,

22.05 kHz and 16 kHz) of MPEG2 are supported

∑

A variety of output formats are supported: I

2

S, SPDIF

and 256 or more times oversampled bit serial analog

stereo

∑

Automatic internal dynamic range compression

algorithm using programmable compression

parameters

∑

Non byte-aligned coded input data is handled

∑

Built-in provisions to generate high quality sampling

clocks for all six supported sampling frequencies; these

sampling clocks may locked to an external PLL to

support an extensive list of input data reference clock

frequencies

∑

Bit-rate and sampling-rate settings may be overruled by

the microcontroller while the SAA2502 is trying to

establish frame synchronization

∑

Input interface mode which requests data based on

input buffer content, enables the handling of variable

bit-rate input streams and input data offered in (fixed

length) bursts

∑

An interrupt output pin which can generate interrupt

requests at the occurrence of various events;

consequently polling by the microcontroller is not

needed in most situations

∑

L3 and the I

2

C-bus microcontroller interface protocols

are supported

∑

The control interface is always fully operational (also

while STOP is asserted)

∑

CRC protection of scale factors is provided for all

supported sample frequencies.

2

APPLICATIONS

∑

Astra Digital Radio (ADR)

∑

Digital Audio Broadcast (DAB)

∑

Digital Versatile Disc (DVD)

∑

Digital Video Broadcast (DVB)

∑

General purpose MPEG2 audio decoding.

3

GENERAL DESCRIPTION

The SAA2502 is a second generation ISO/MPEG audio

source decoder. The device specification has been

enhanced with respect to the SAA2500 and SAA2501 ICs

and therefore it offers in principle all features of its

predecessors.

It supports layer I and II of MPEG1 and the MPEG2

requirements for a stereo decoder.

4

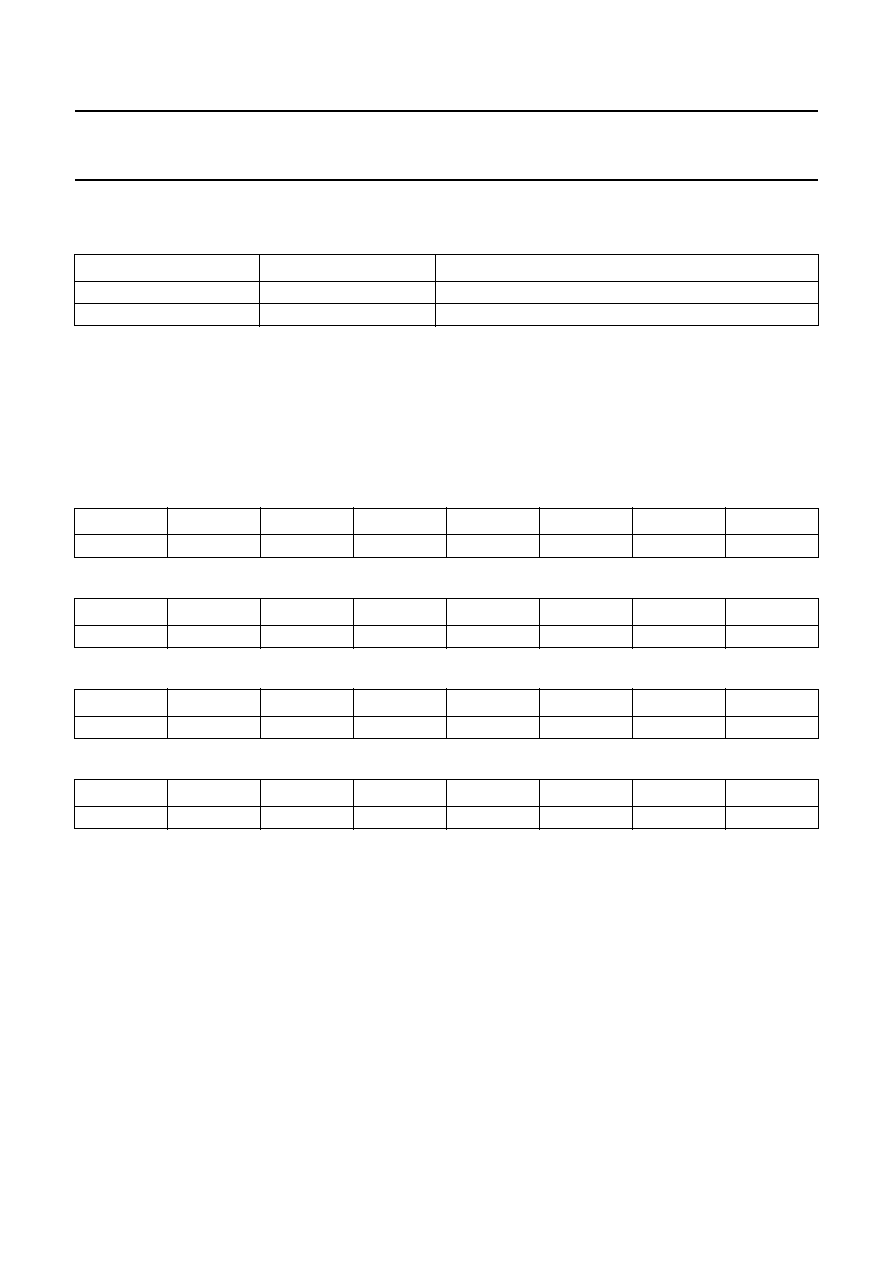

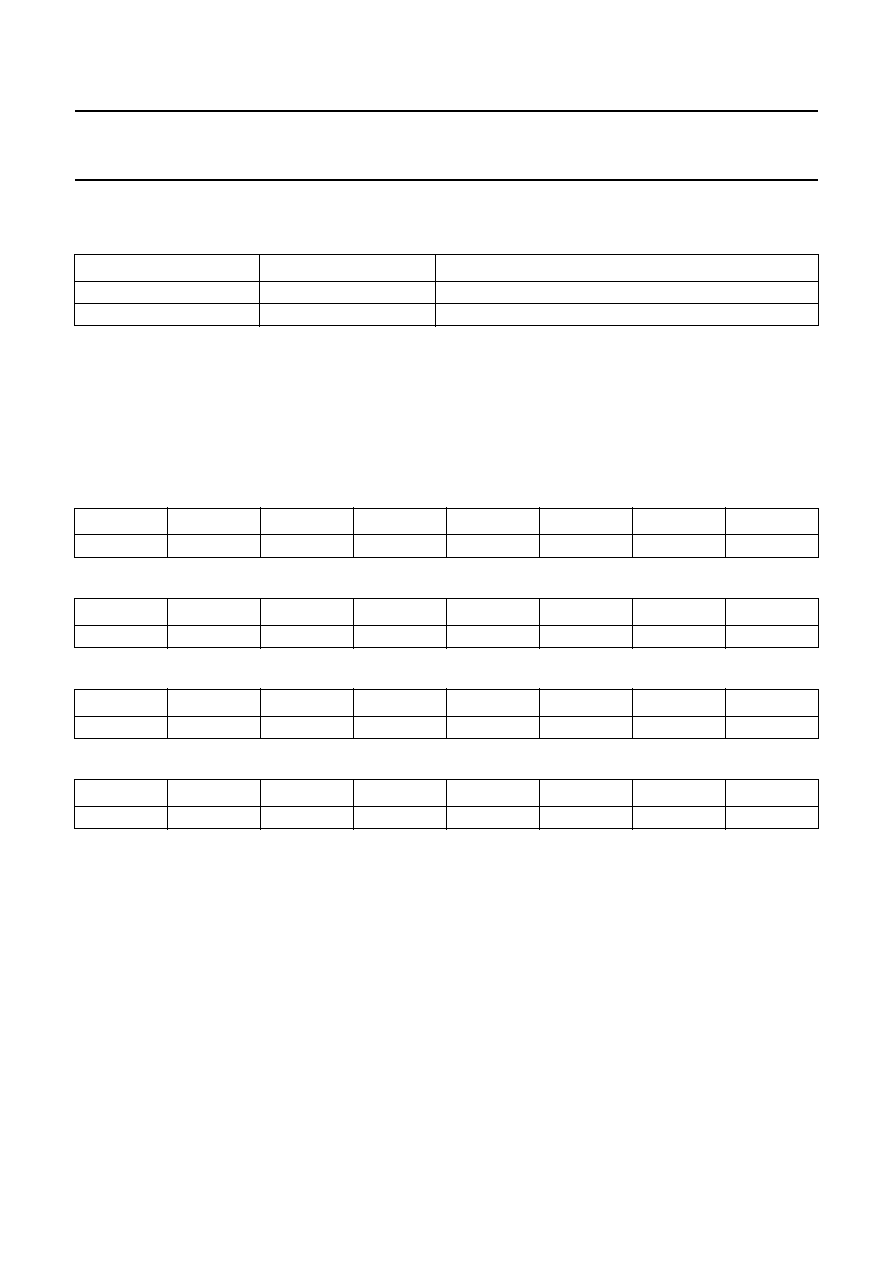

ORDERING INFORMATION

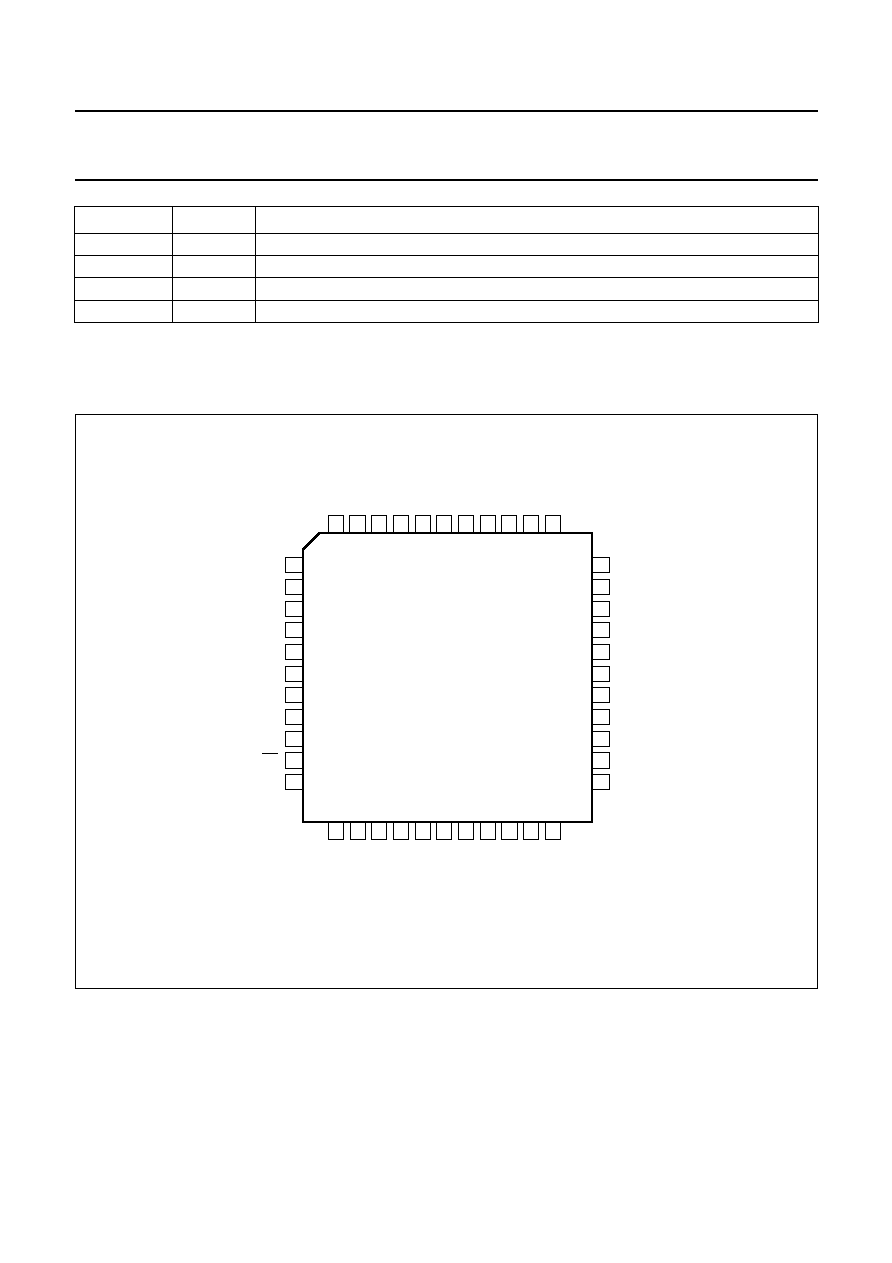

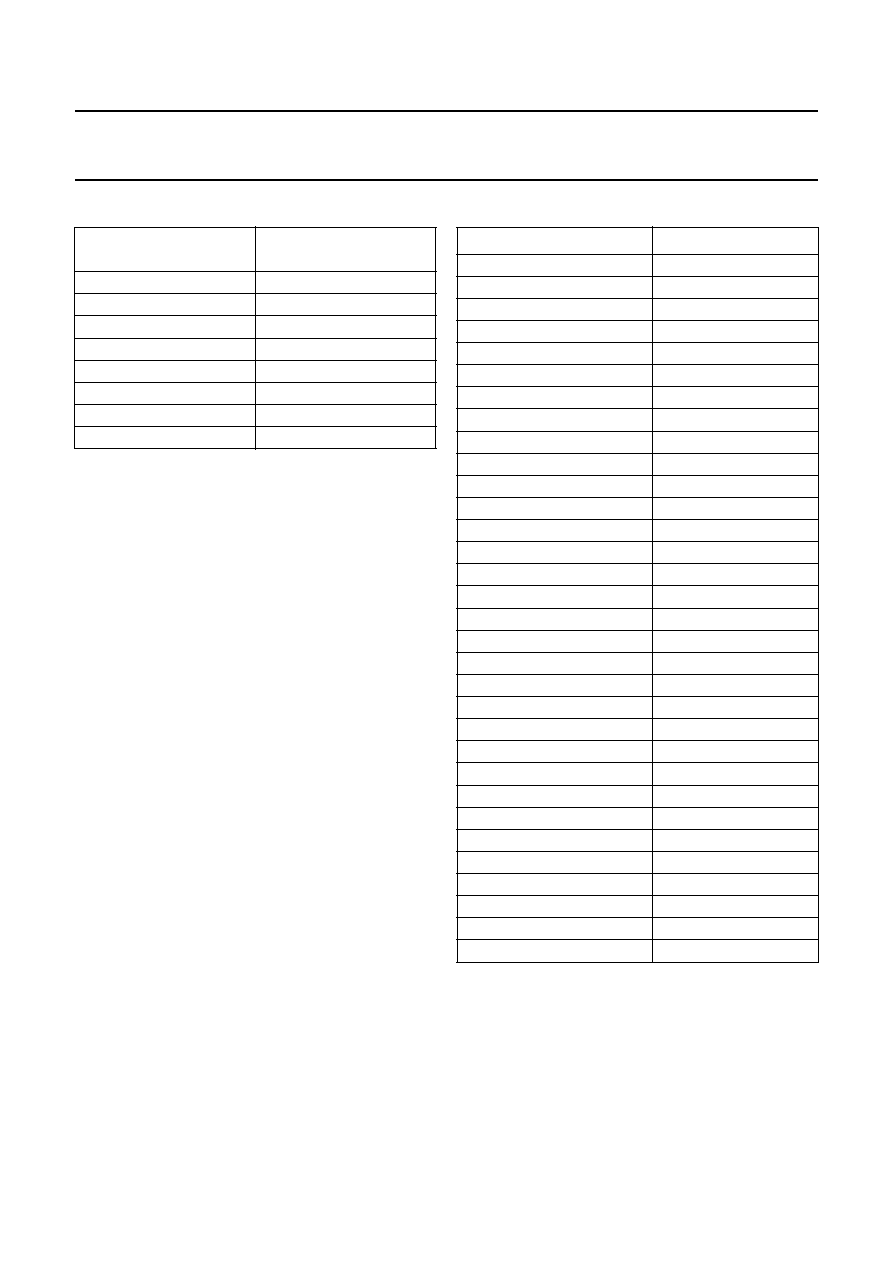

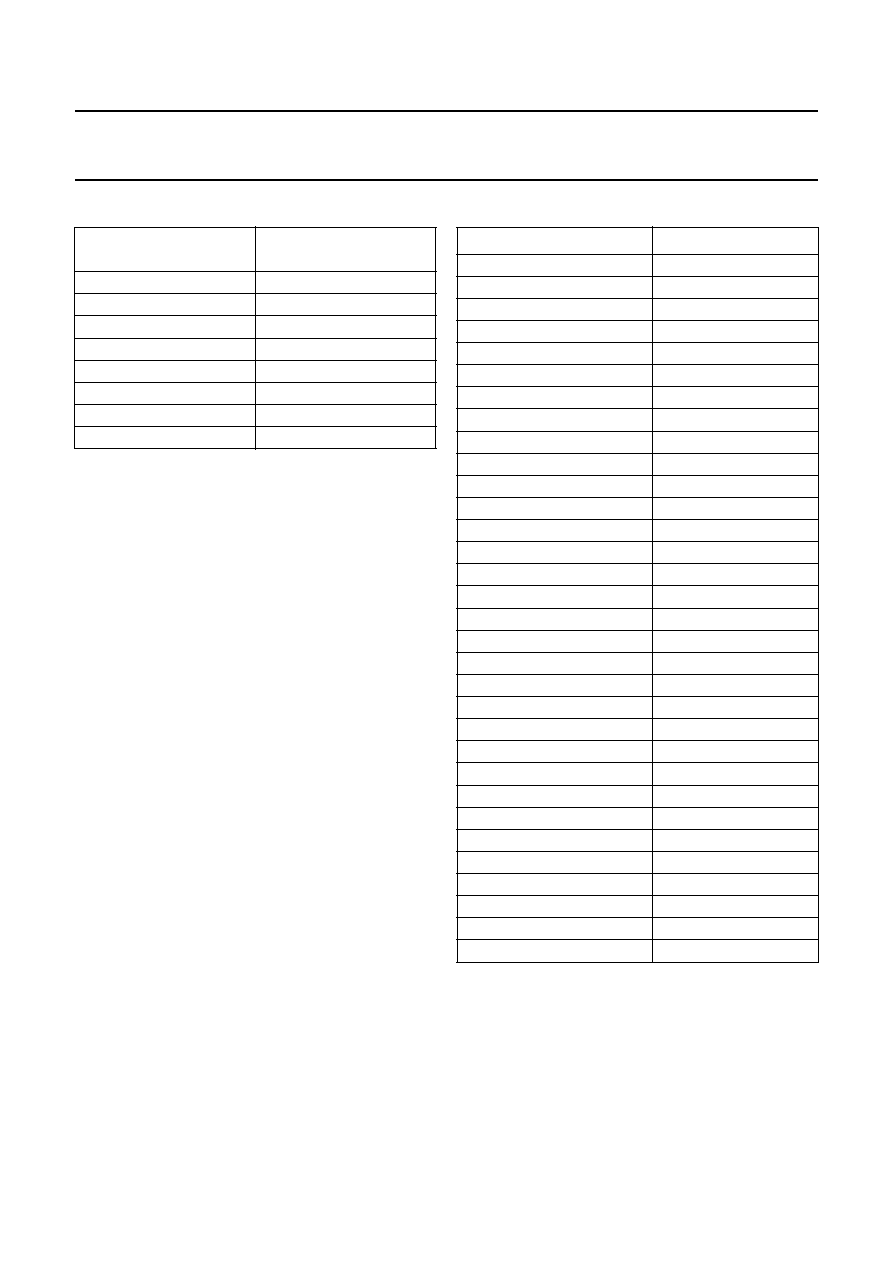

TYPE NUMBER

PACKAGE

NAME

DESCRIPTION

VERSION

SAA2502H

QFP44

plastic quad flat package; 44 leads (lead length 1.3 mm);

body 10

◊

10

◊

1.75 mm

SOT307-2

1997 Nov 17

4

Philips Semiconductors

Preliminary specification

ISO/MPEG Audio Source Decoder

SAA2502

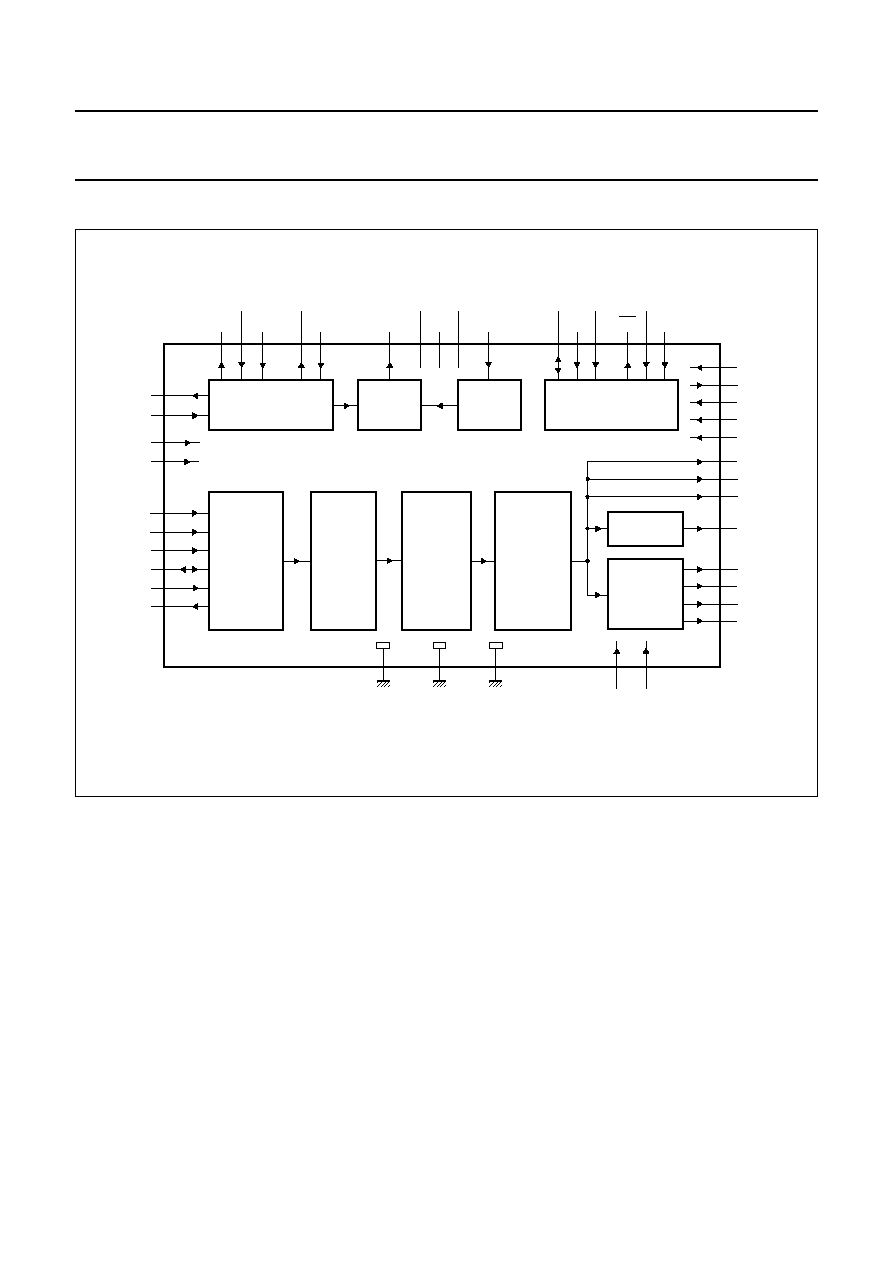

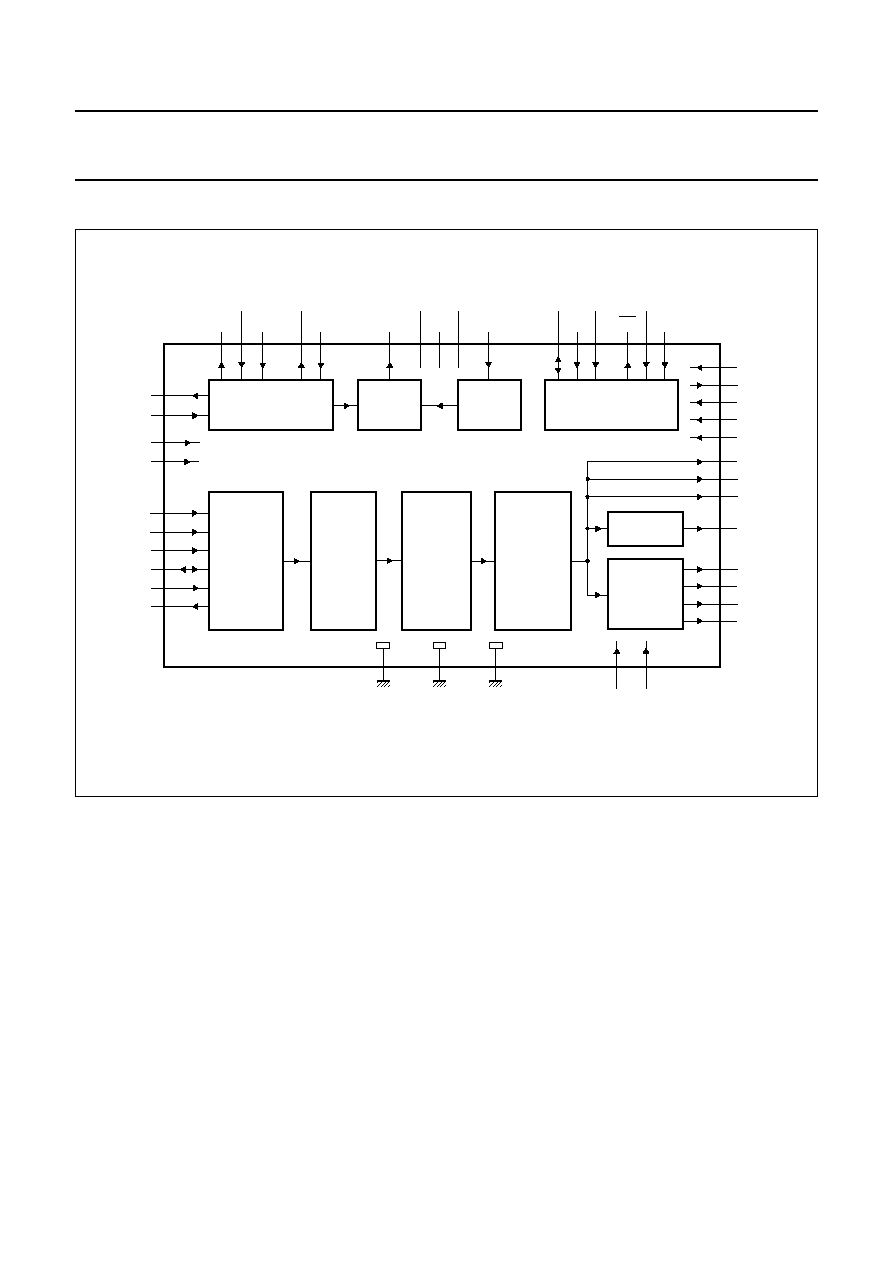

5

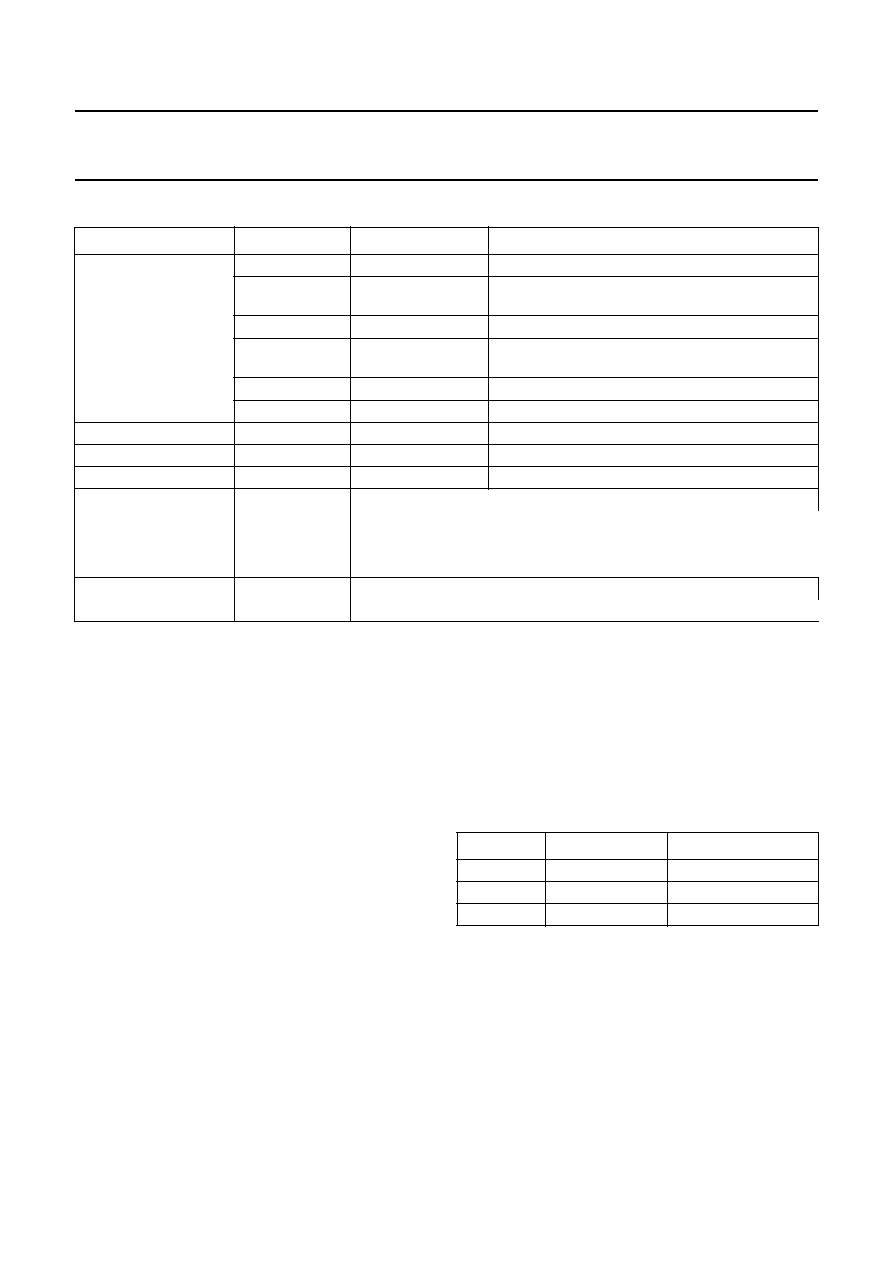

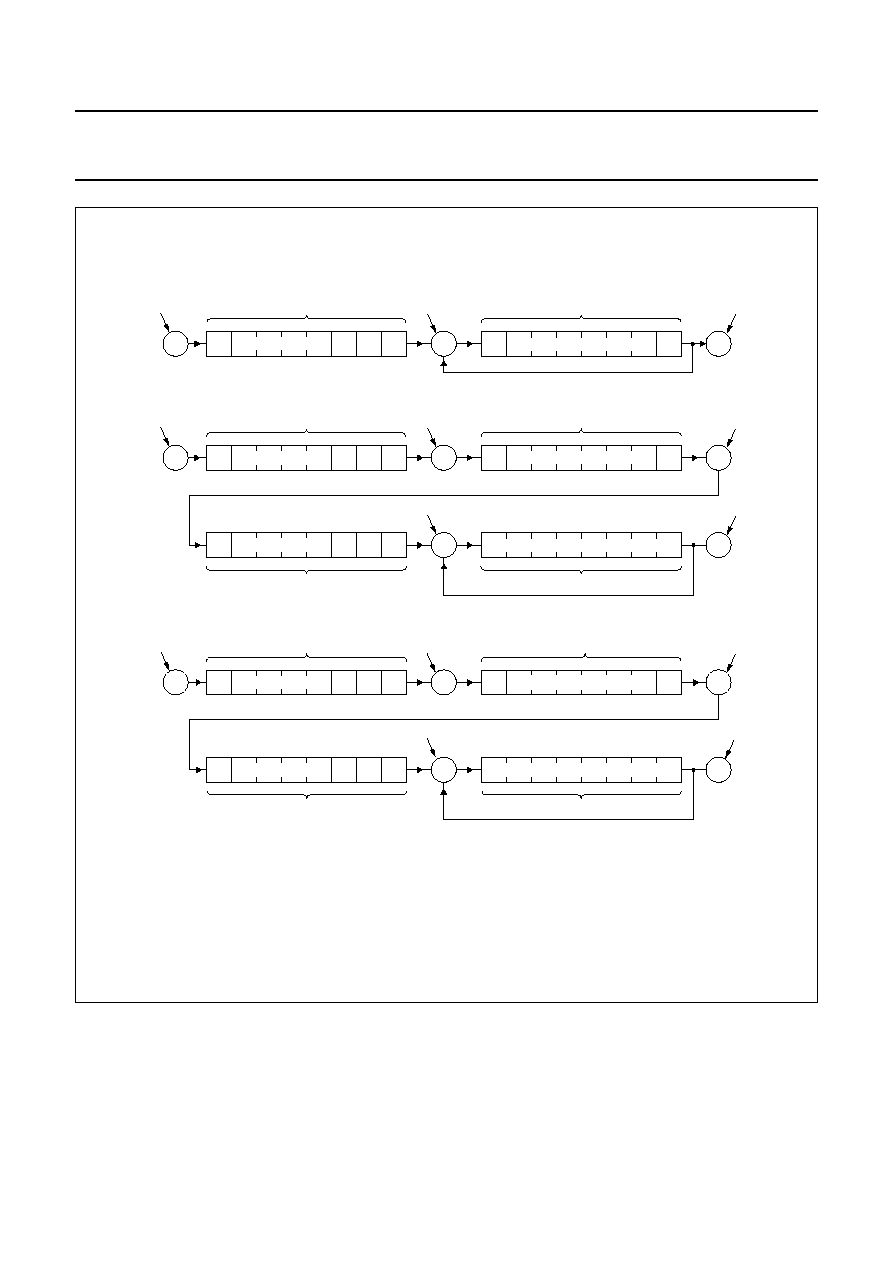

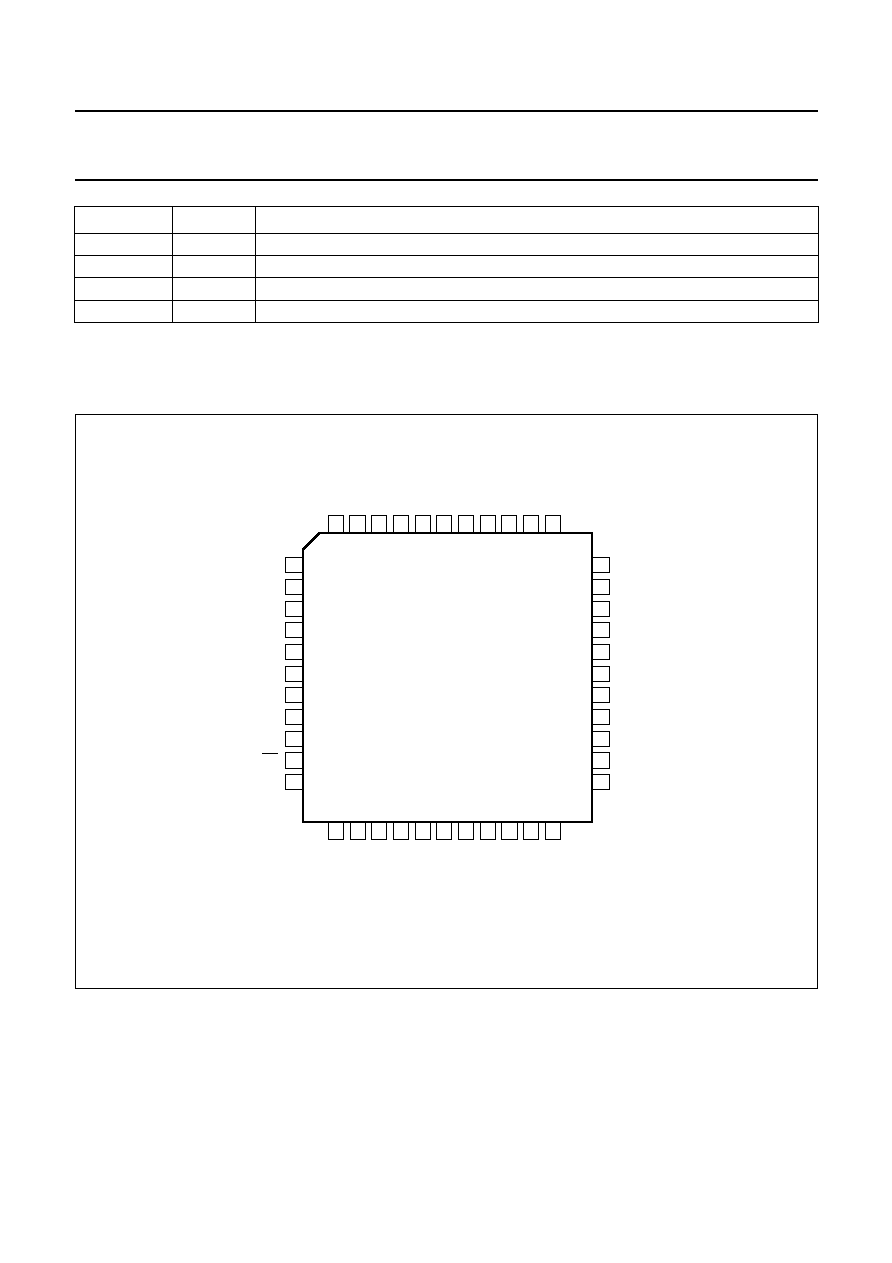

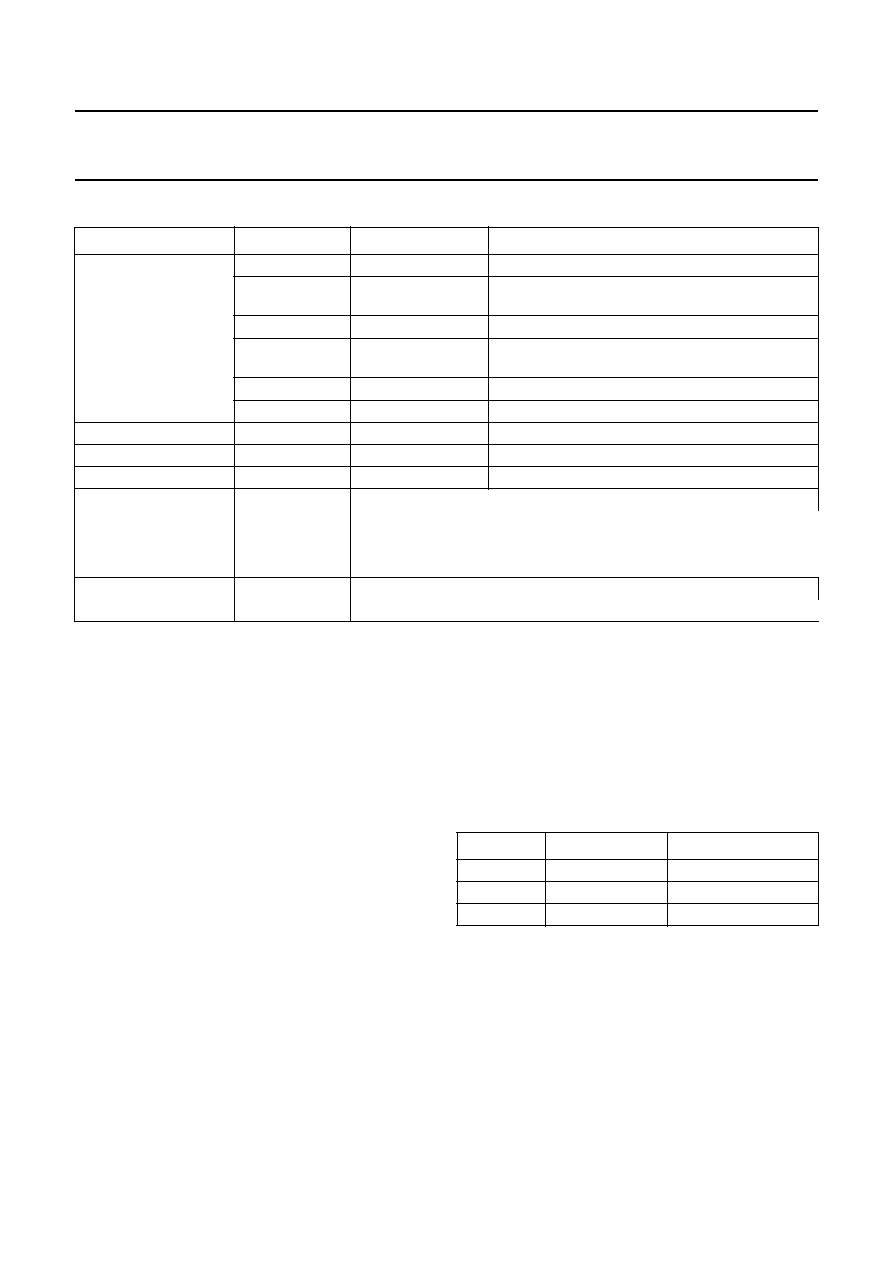

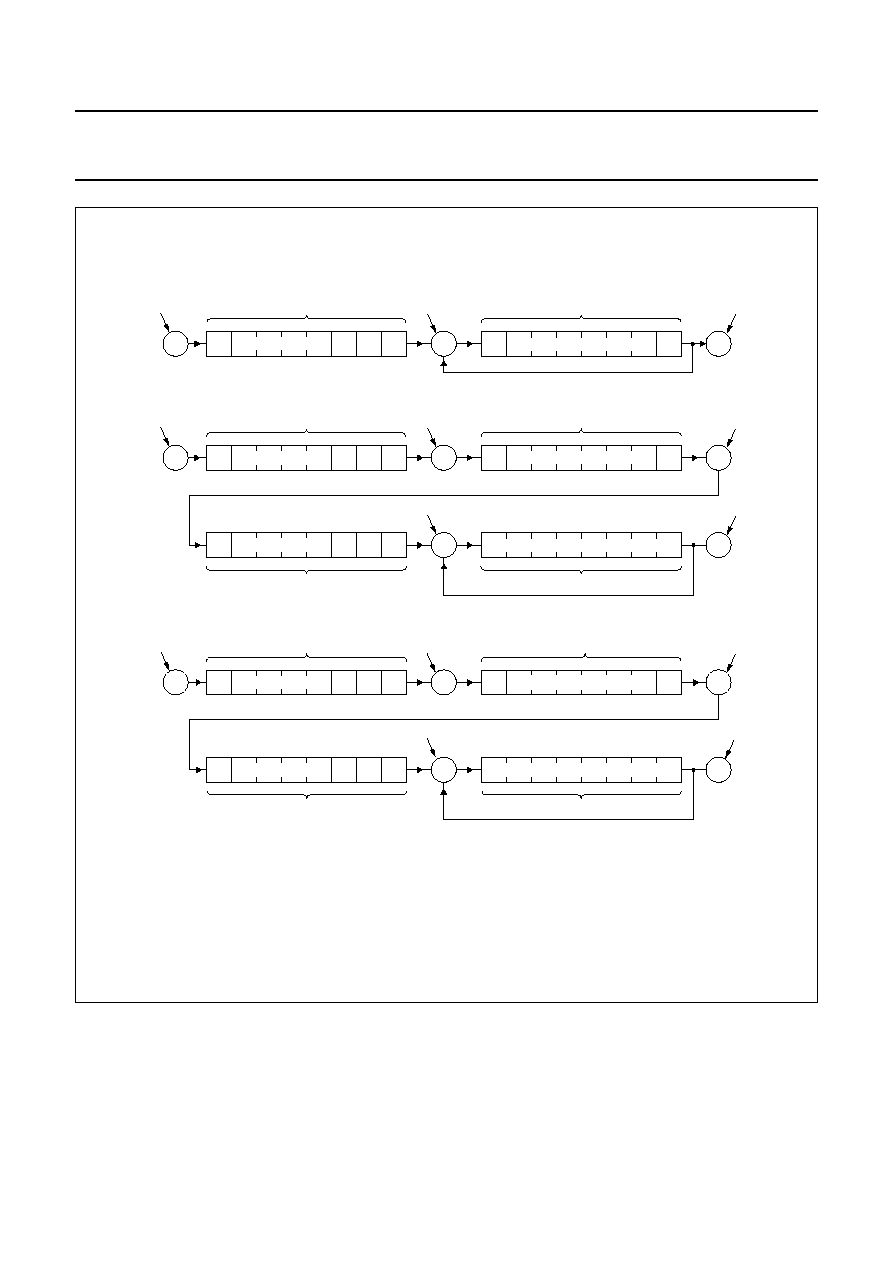

BLOCK DIAGRAM

Fig.1 Block diagram.

handbook, full pagewidth

MGE469

INPUT

INTERFACE

DEMULTI-

PLEXER

DEQUANTI-

ZATION

AND

SCALING

SYNTHESIS

SUB-BAND

FILTER

DIGITAL-TO-

ANALOG

CONVERTER

SPDIF

ENCODER

CLOCK GENERATOR

PHASE

COMPA-

RATOR

DIVIDER

DECODING

CONTROL

1

25

40

43

15

17

19

14

20

13

16

28

42

37

36

35

34

38

39

6

4

2

3

5

21

24

41

33

11

12

10

9

7

8

22

23

26

27

29

32

31

18 30 44

SAA2502

MCLKOUT

MCLKIN

MCLK24

X22OUT

X22IN

PHDIF

VDD1

VDD2

VDD3

REFCLK

CDATA

CCLK

CMODE

INT

STOP

RESET

TDI

TDO

TCK

TMS

TRST

SD

SCK

WS

SPDIF

LFTPOS

LFTNEG

RGTPOS

RGTNEG

REFN

REFP

GND1

GND2

GND3

CDRQ

CDVAL

CDCL

CDSY

CDEF

CD

TC1

TC0

FSCLKIN

FSCLK

1997 Nov 17

5

Philips Semiconductors

Preliminary specification

ISO/MPEG Audio Source Decoder

SAA2502

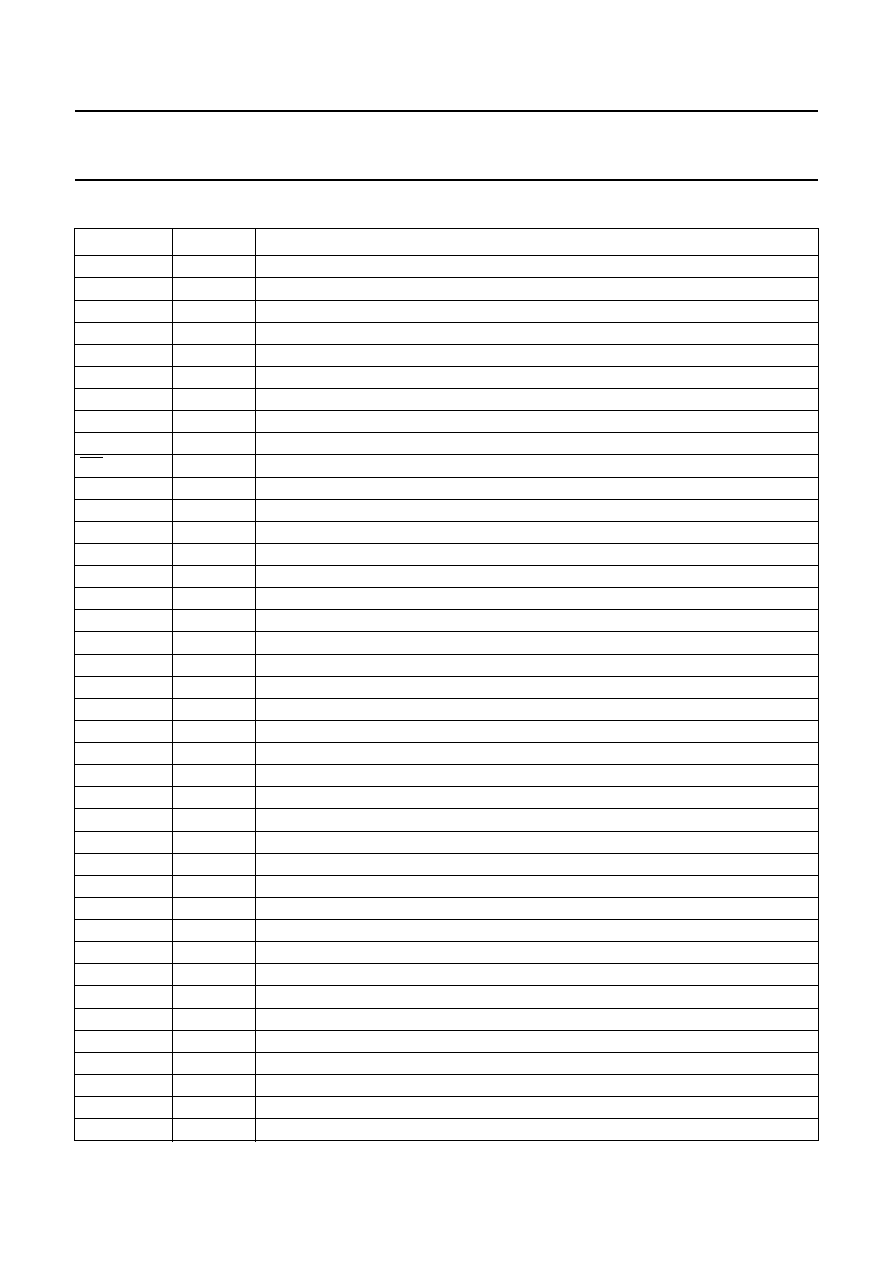

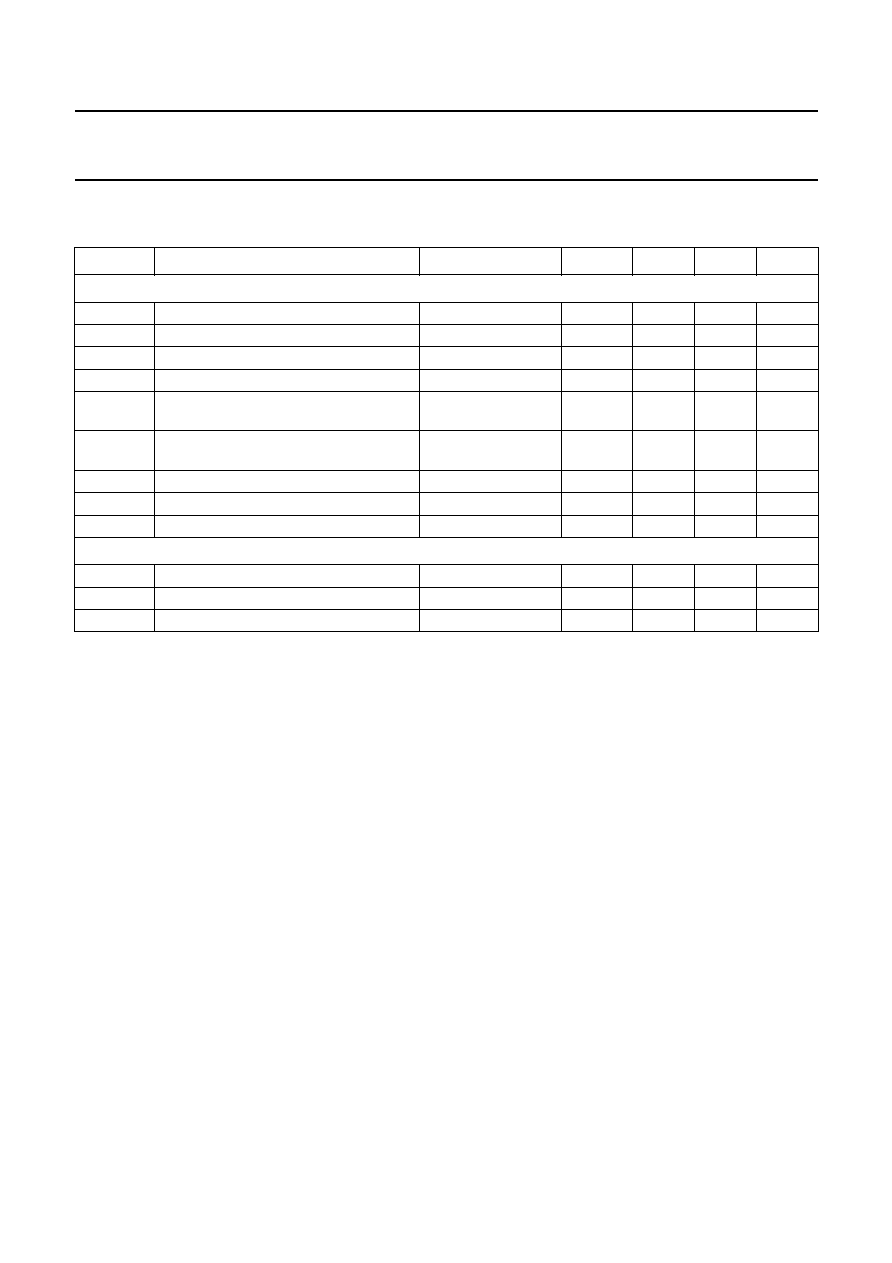

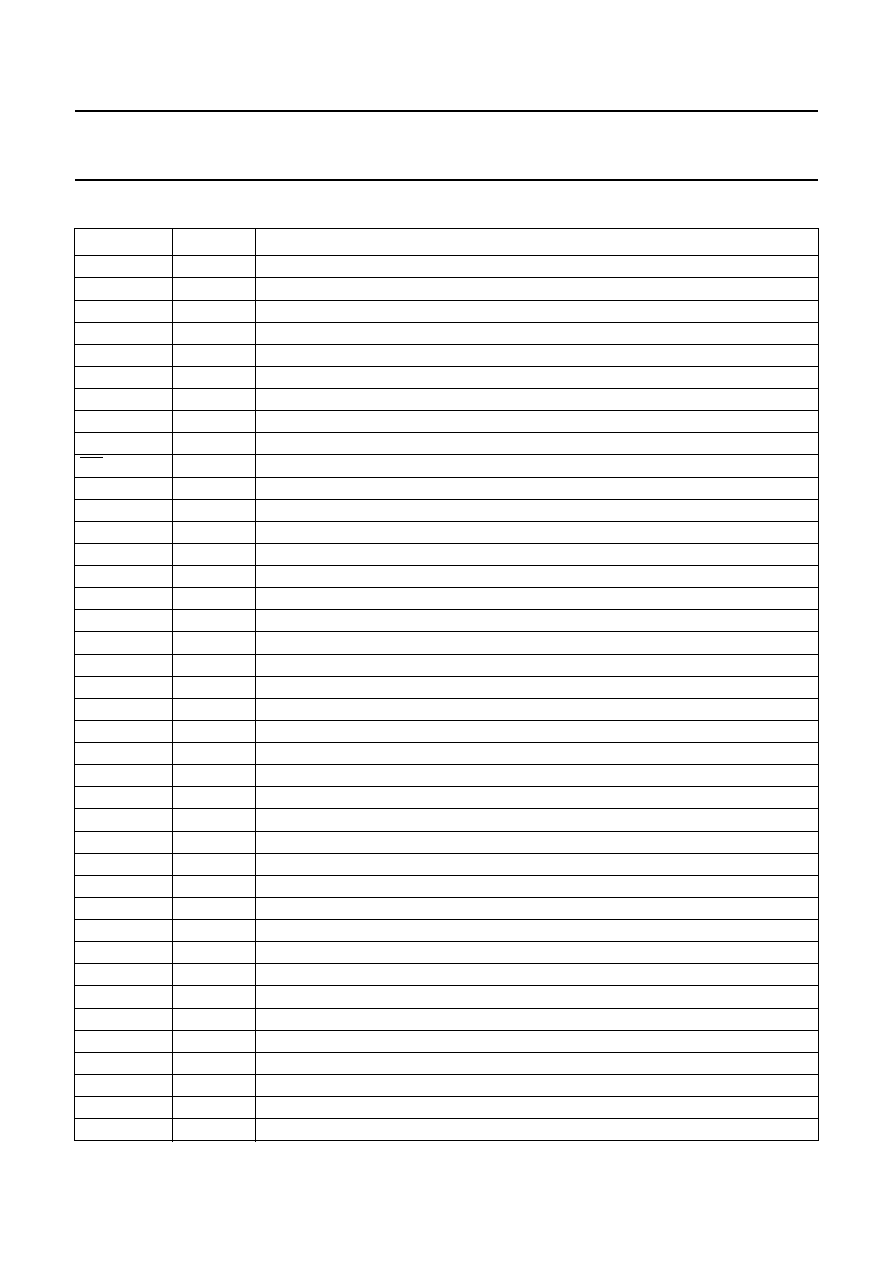

6

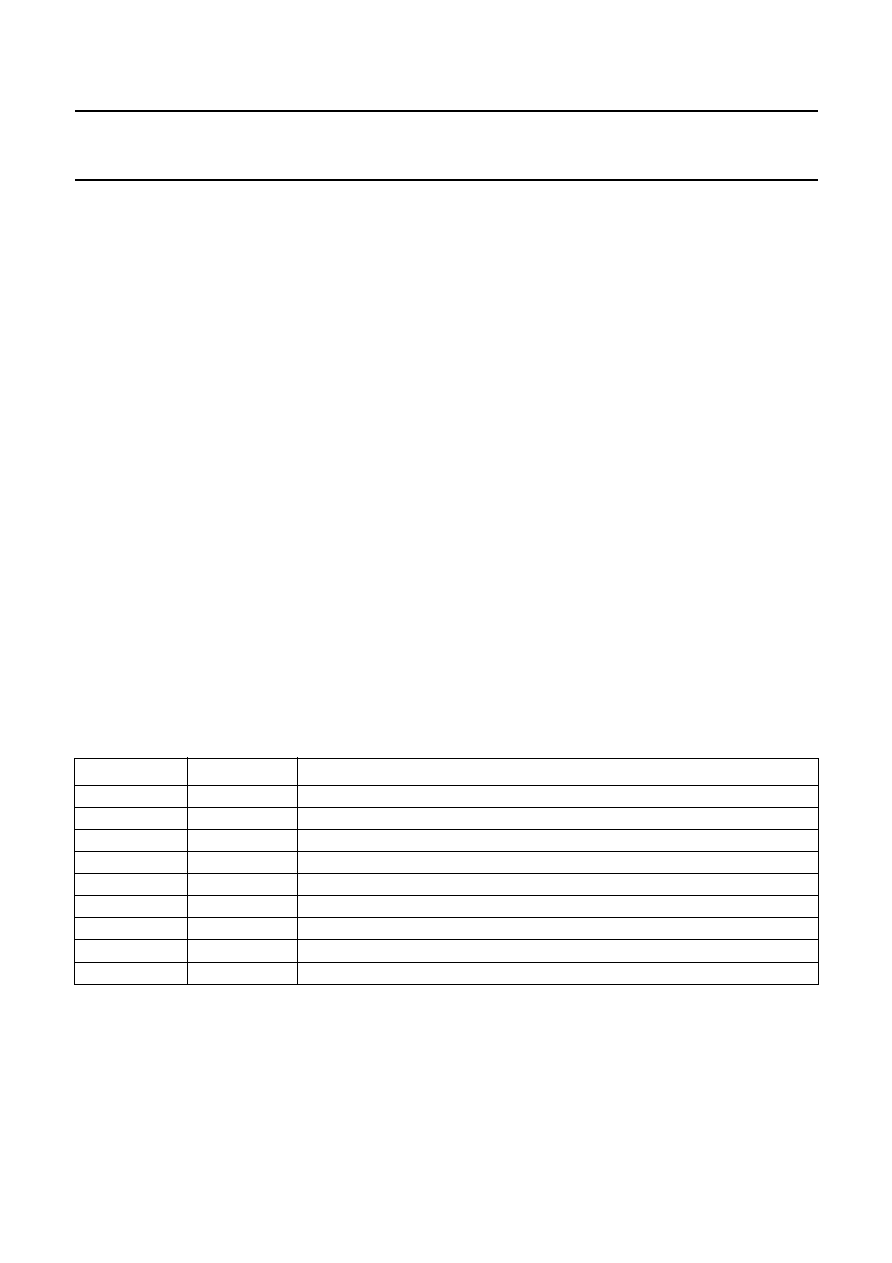

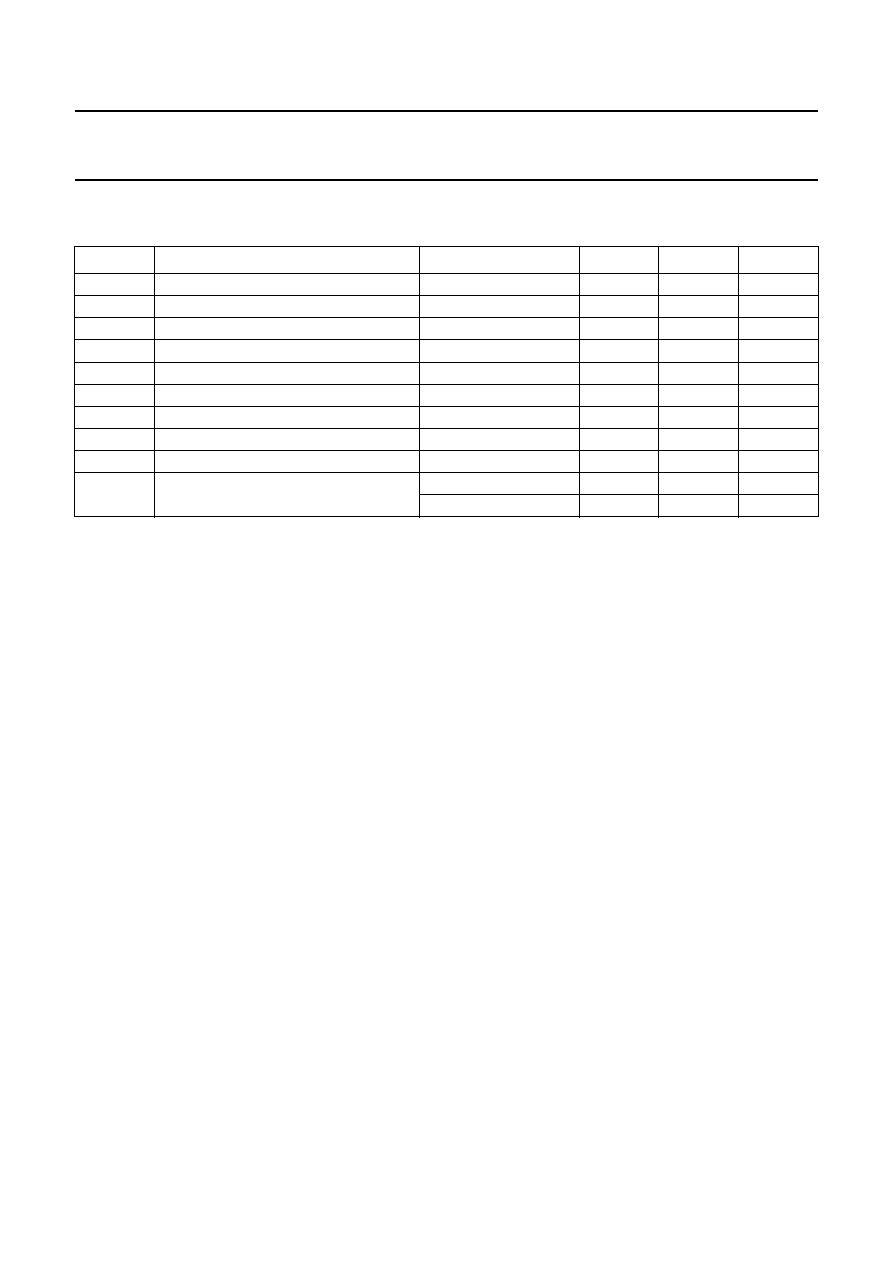

PINNING

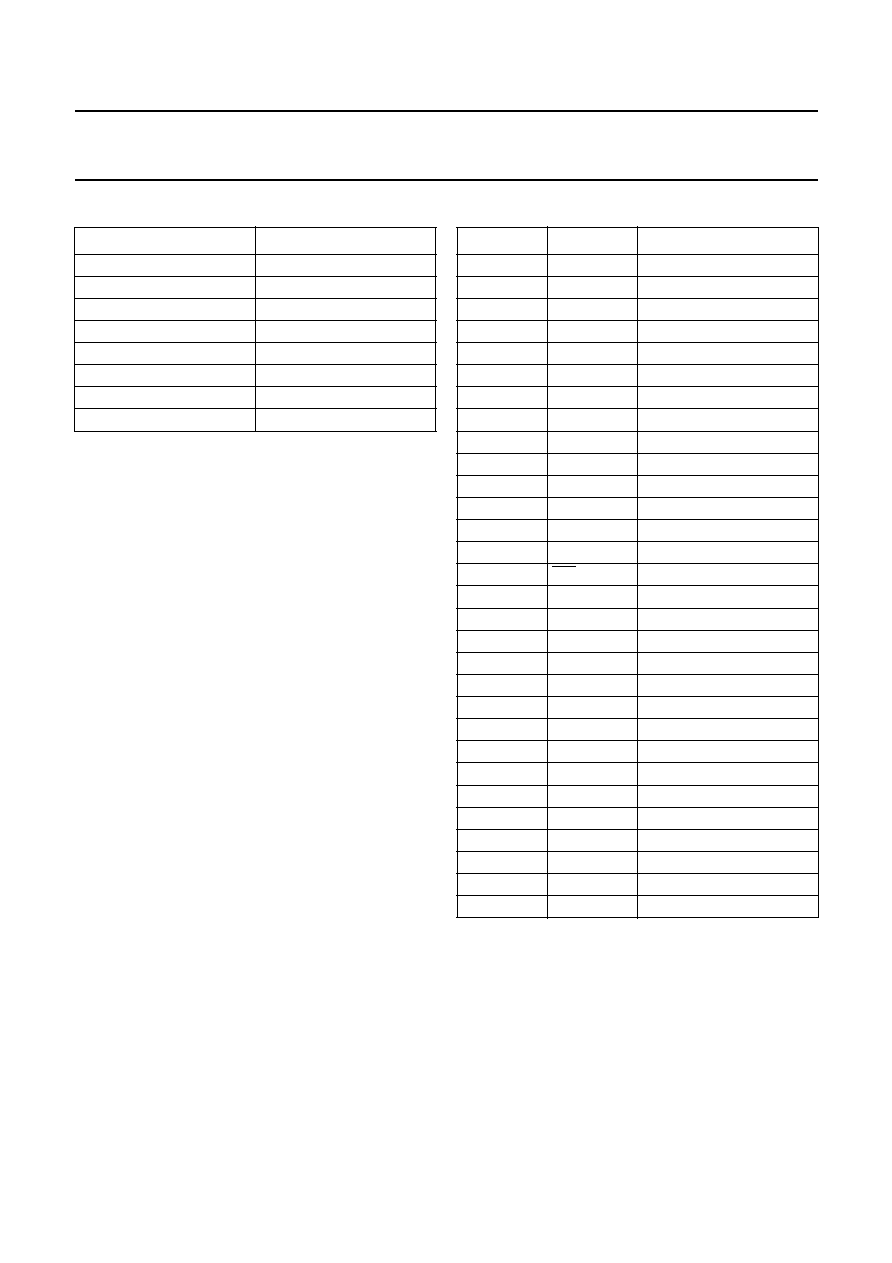

SYMBOL

PIN

DESCRIPTION

FSCLK

1

sample rate clock output; buffered signal

SCK

2

baseband audio data I

2

S clock output

SD

3

baseband audio I

2

S data output

WS

4

baseband audio data I

2

S word select output

TRST

5

boundary scan test reset input

SPDIF

6

SPDIF baseband audio output

CCLK

7

L3 clock/I

2

C-bus bit clock input

CDATA

8

L3 data/I

2

C-bus serial data input/output; note 1

CMODE

9

L3 mode (address/data select input)

INT

10

interrupt request output; active LOW; note 1

RESET

11

master reset input

STOP

12

soft reset/stop decoding input

CDRQ

13

coded data request output

CDCL

14

coded data bit clock input/output; note 2

CD

15

MPEG coded data input

GND1

16

ground 1

CDEF

17

coded data error flag input

V

DD1

18

supply voltage 1

CDSY

19

coded data byte or frame sync input

CDVAL

20

coded data valid flag input

TMS

21

boundary scan test mode select input

REFCLK

22

PLL reference clock input

PHDIF

23

PLL phase comparator output; note 2

TCK

24

boundary scan test clock input

FSCLKIN

25

sample rate clock input

X22IN

26

22.579 MHz clock oscillator input or signal input

X22OUT

27

22.579 MHz clock oscillator output

GND2

28

ground 2

MCLK24

29

master clock frequency indication input

V

DD2

30

supply voltage 2

MCLKOUT

31

master clock oscillator output

MCLKIN

32

master clock oscillator input or signal input

TDI

33

boundary scan test data input

RGTPOS

34

analog right channel positive output

RGTNEG

35

analog right channel negative output

REFN

36

low reference voltage input for analog outputs

REFP

37

high reference voltage input for analog outputs

LFTNEG

38

analog left channel negative output

LFTPOS

39

analog left channel positive output

TC0

40

factory test scan chain control 0 input

1997 Nov 17

6

Philips Semiconductors

Preliminary specification

ISO/MPEG Audio Source Decoder

SAA2502

Notes

1. Output type is: open-drain.

2. Output type is: 3-state.

TDO

41

boundary scan test data output

GND3

42

ground 3

TC1

43

factory test scan chain control 1 input

V

DD3

44

supply voltage 3

SYMBOL

PIN

DESCRIPTION

Fig.2 Pin configuration.

1

2

3

4

5

6

7

8

9

10

11

33

32

31

30

29

28

27

26

25

24

23

12

13

14

15

16

17

18

19

20

21

22

44

43

42

41

40

39

38

37

36

35

34

SAA2502

MGE468

TDI

MCLKIN

MCLKOUT

VDD2

GND2

X22OUT

X22IN

FSCLKIN

TCK

PHDIF

FSCLK

SCK

SD

WS

TRST

SPDIF

CDATA

CMODE

RESET

MCLK24

TC1

GND3

TDO

TC0

LFTPOS

LFTNEG

REFN

RGTNEG

RGTPOS

V

DD3

REFP

CDRQ

CDCL

CD

GND1

CDEF

V

DD1

CDVAL

TMS

REFCLK

STOP

CDSY

CCLK

INT

1997 Nov 17

7

Philips Semiconductors

Preliminary specification

ISO/MPEG Audio Source Decoder

SAA2502

7

FUNCTIONAL DESCRIPTION

7.1

Basic functionality

From a functional point of view, several blocks can be

distinguished in the SAA2502. A clock generator section

derives the internally and externally required clock signals

from its clock inputs. The input interface section receives

or requests coded input data in one of the supported input

interface modes. The demultiplexer processor handles

frame synchronization, parsing, demultiplexing and error

concealment of the input data stream The de-quantization

and scaling processor performs the transformation and

scaling operations on the (demultiplexed) coded sample

representations in the input bitstream to yield sub-band

domain samples.

The sub-band samples are transferred to the synthesis

sub-band filter bank processor which reconstructs the

baseband audio samples. The output interface block

transforms the audio samples to the output formats

required by the different output ports.

The decoding control block houses the I

2

C-bus/L3

microcontroller interface, and handles the response to

external control signals. This section enables the

application to configure the SAA2502, to read its decoding

status, to read ancillary data and so on.

Several pins are reserved for boundary scan test (5 pins)

and factory test scan chain control (2 pins).

7.2

Clock generator module

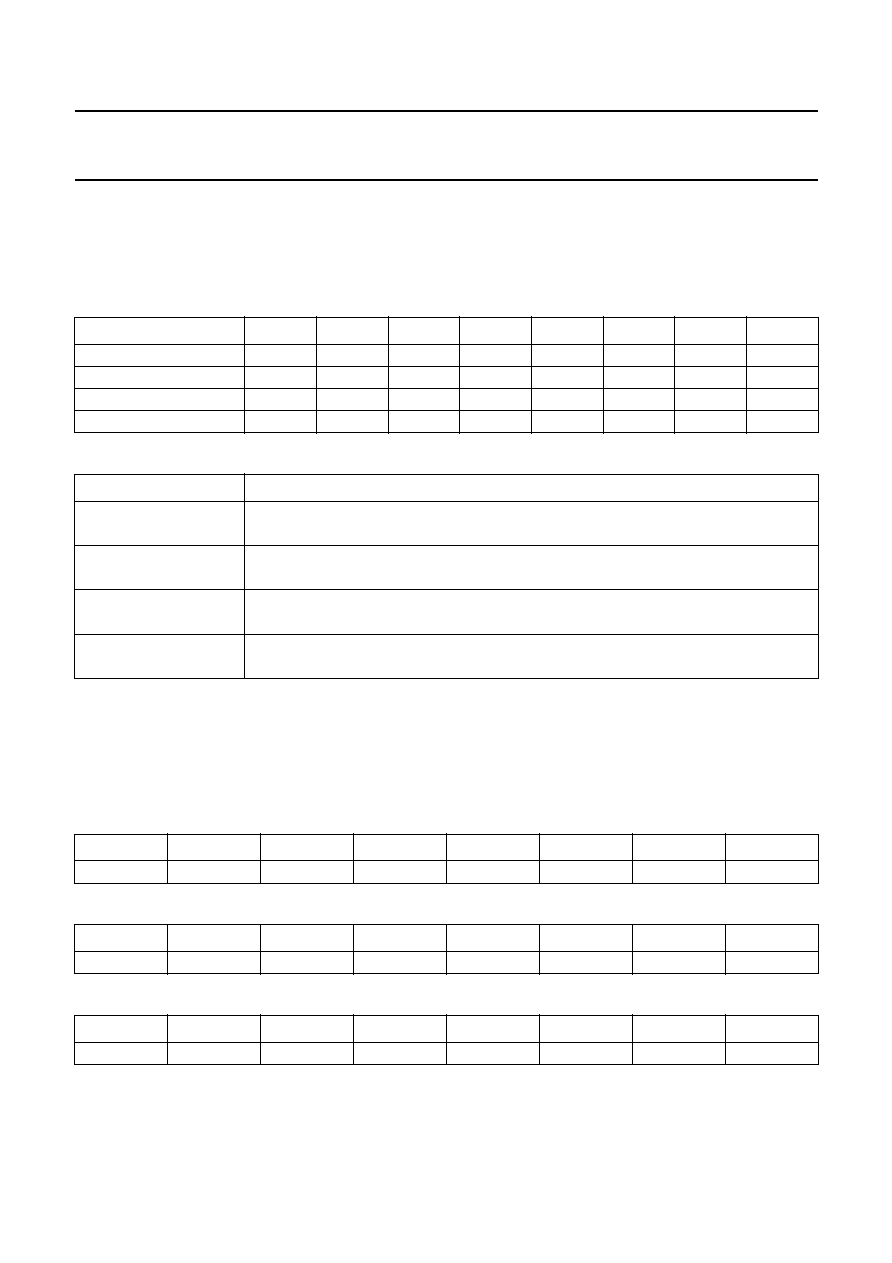

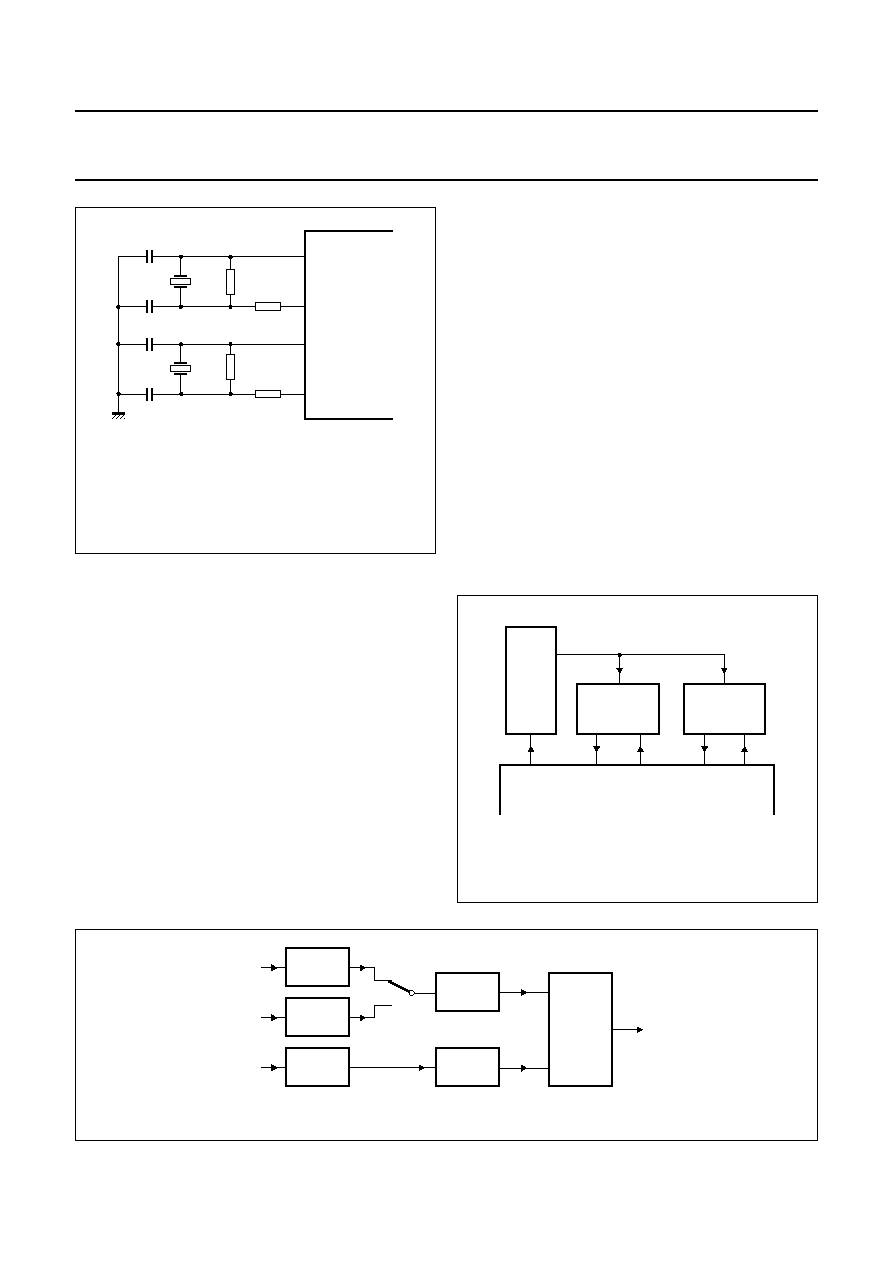

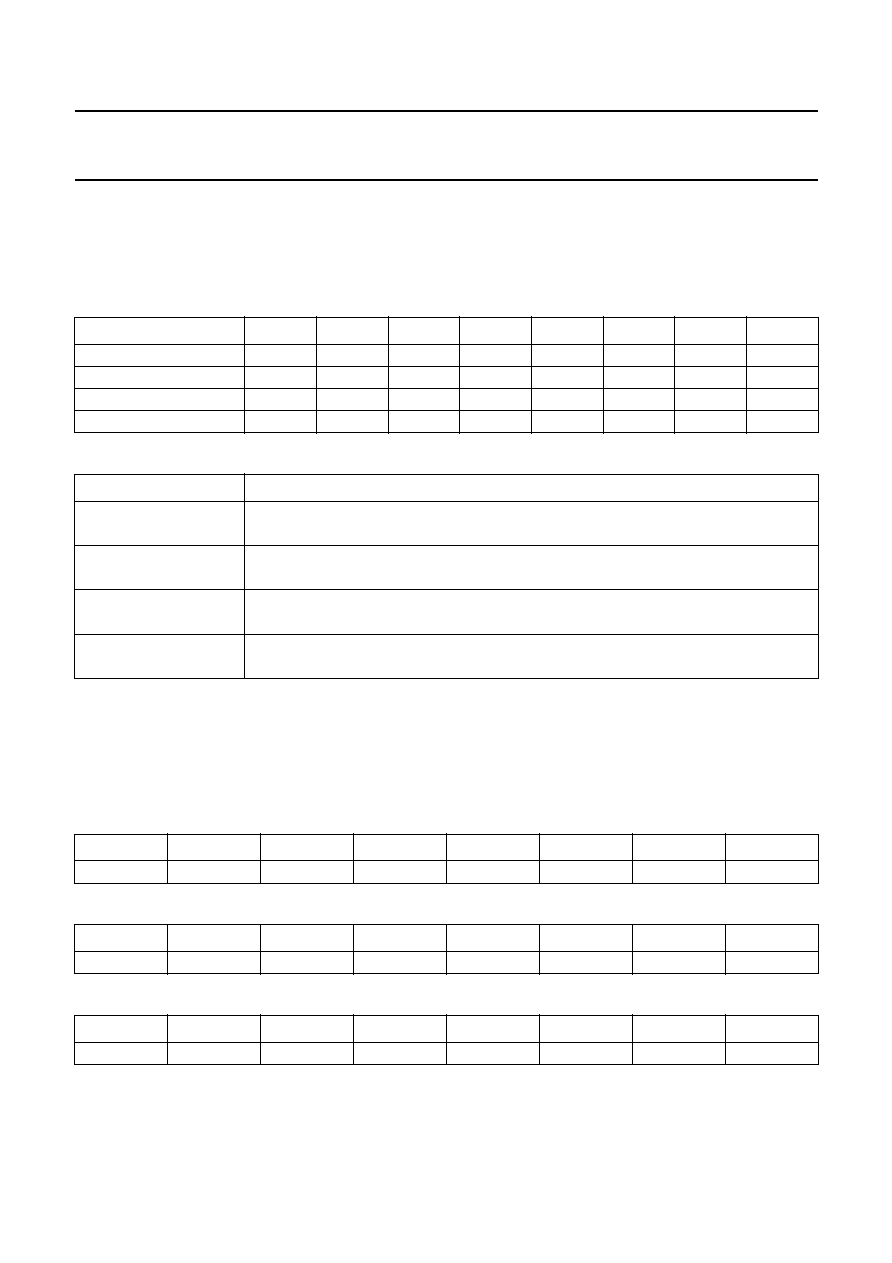

The SAA2502 clock interfacing is designed for application

versatility. It consists of 9 signals (see Table 1).

The clock generator provides the following clock signals:

∑

Internal sample clocks

∑

External buffered sample clock FSCLK

∑

Processor master clock

∑

Coded input data bit clock

∑

Coded input data request clock

The module can be configured to operate in 3 different

modes of operation:

∑

External sample clock mode

∑

Free running internal sample clock mode

∑

Locked internal sample clock mode.

Clock generator operation mode must be stationary while

the device is in normal operation. Changing mode should

always be followed by a (soft) reset.

f

input bit rate

32

-----------------------------------

=

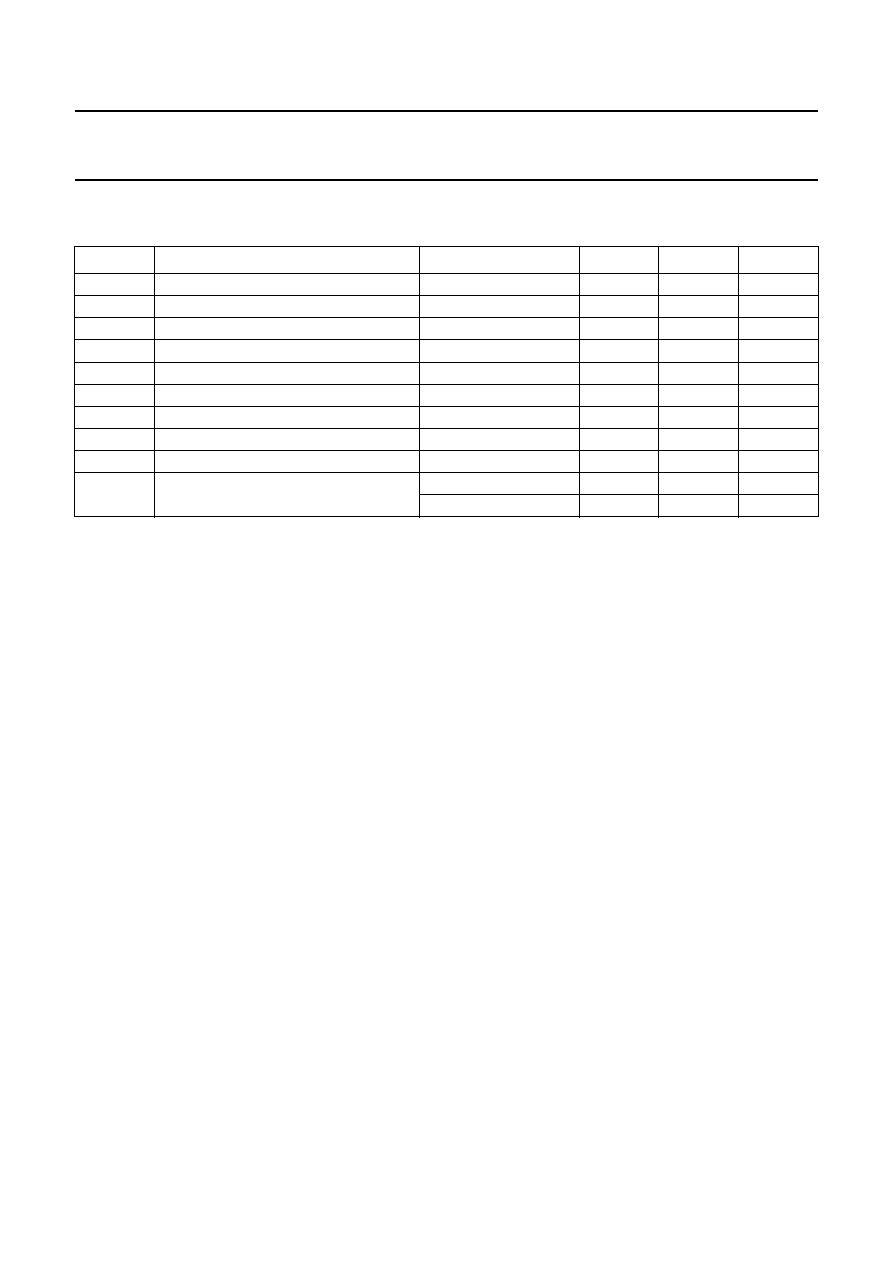

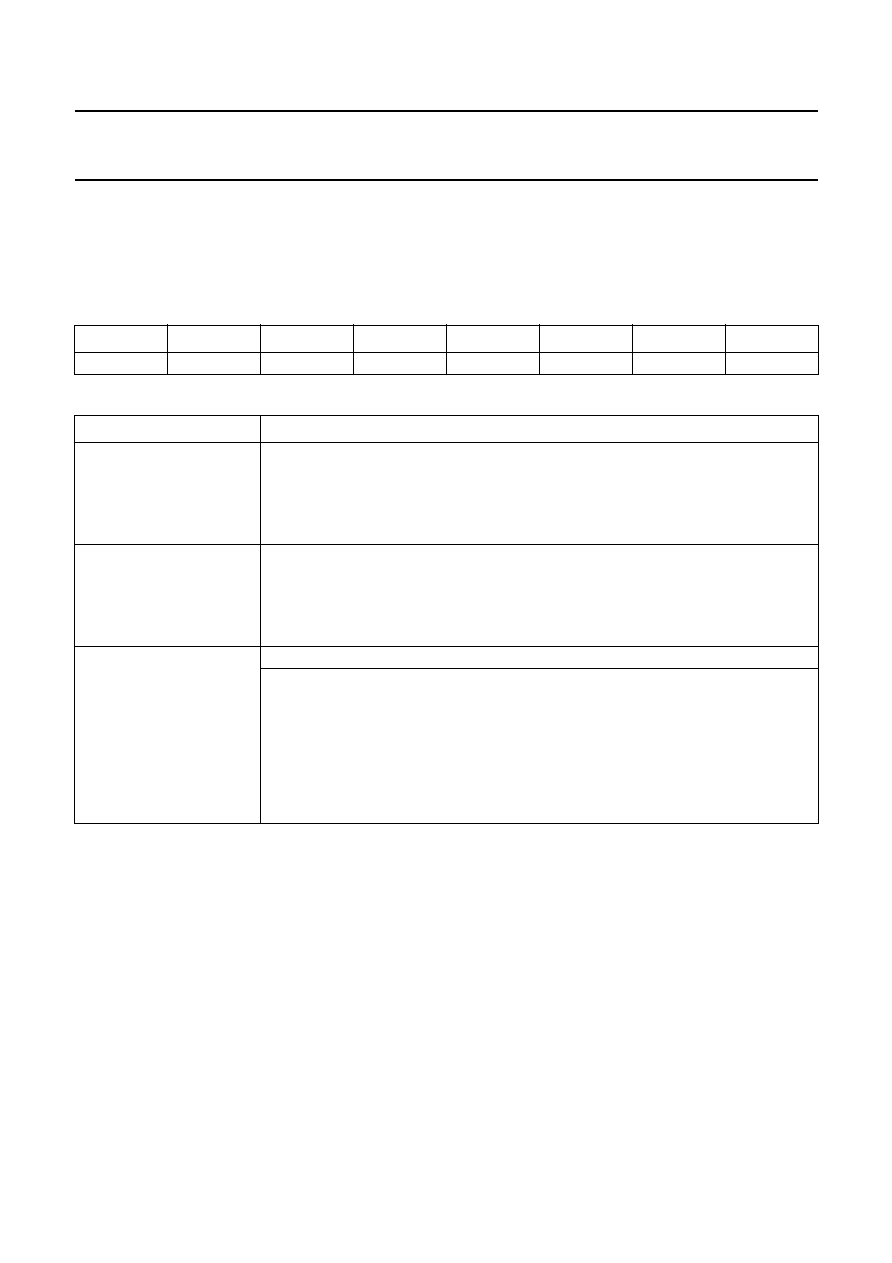

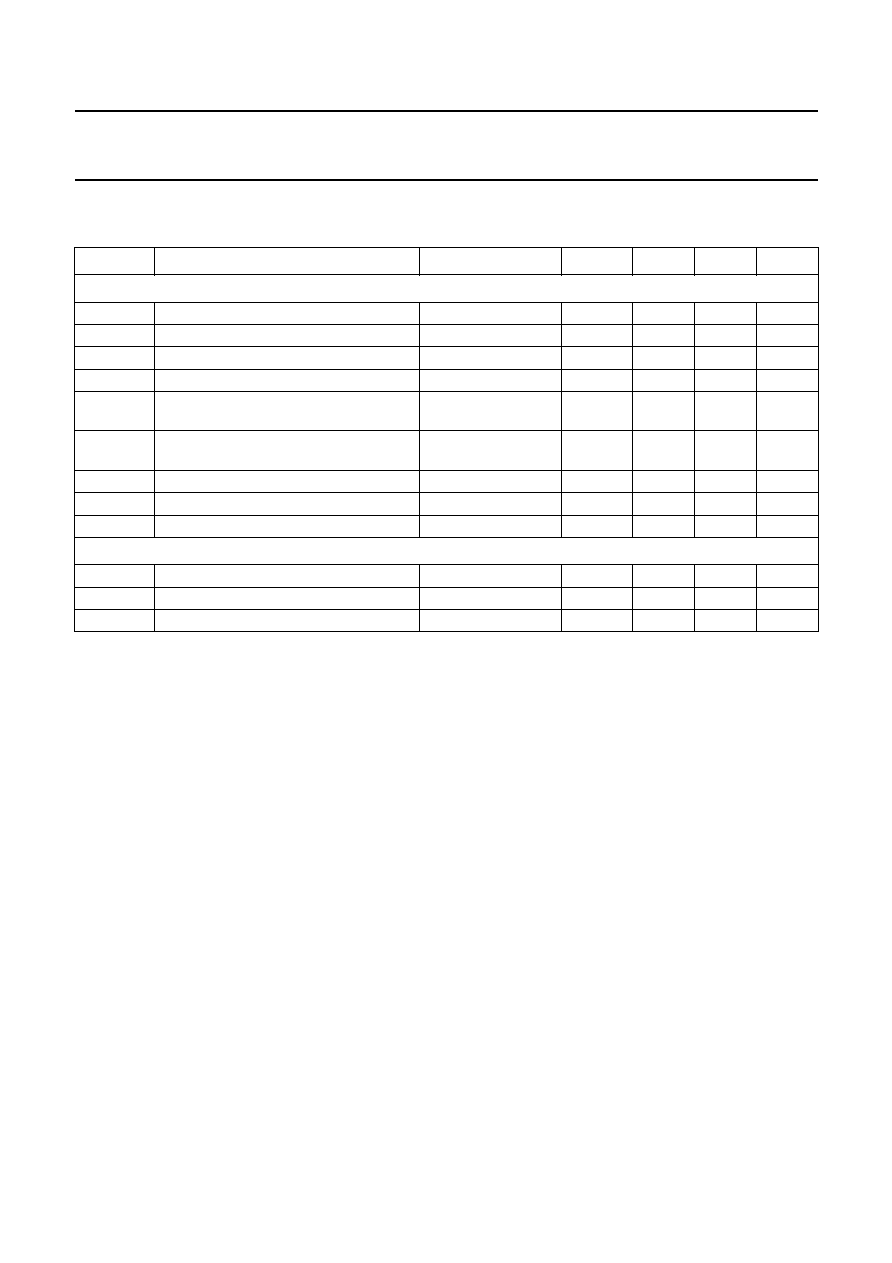

Table 1

Clock interfacing signals

SIGNAL

DIRECTION

FUNCTION

MCLKIN

input

master clock oscillator input or signal input

MCLKOUT

output

master clock oscillator output

MCLK24

input

master clock frequency indication

X22IN

input

22.5792 MHz clock oscillator input or signal input

X22OUT

output

22.5792 MHz clock oscillator output

FSCLKIN

input

external sample rate clock signal input

FSCLK

output

sample rate clock signal output

REFCLK

input

coded input data rate reference clock

PHDIF

output

phase difference indication output between reference clock and sample clock

1997 Nov 17

8

Philips Semiconductors

Preliminary specification

ISO/MPEG Audio Source Decoder

SAA2502

7.2.1

E

XTERNAL SAMPLE CLOCK

In applications where a 256

◊

f

s

sample clock is available,

the use of external crystals may be avoided by putting the

SAA2502 clock generator module in `external sample

clock mode'. Such mode setting may be realized by setting

control flag FSCINP of the control interface. In this event

the sample clock has to be provided to the FSCLKIN clock

input. If sample rate switching should be supported,

required clock frequency changes are the responsibility of

the application. After such a clock frequency change,

enforcement of a soft reset is advised.

In external sample clock mode (and only in that mode) the

clock generator module is able to accept a 384

◊

f

s

sample

clock input. If that mode of operation is desired the control

flag FSC384 should be set.

The FSCLK output is normally disabled in this mode.

If enabled (by setting control flag FSCENA) FSCLK will

produce a buffered copy of FSCLKIN.

X22IN, X22OUT, REFCLK and PHDIF are not used in this

mode. X22IN and REFCLK should be connected to GND

or V

DD

.

MCLKIN is used to provide the (free running) master clock.

This may either be achieved by applying a correct clock

signal to MCLKIN or by connecting a crystal between

MCLKIN and MCLKOUT. In external sample clock mode

(and only in that mode) the master clock may deviate from

24.576 MHz. The master clock frequency value required

depends on the state of pin MCLK24 (see Table 2).

Table 2

Master clock frequency setting by MCLK24

7.2.2

F

REE RUNNING INTERNAL SAMPLE CLOCK

This is the default mode of operation: 256

◊

f

s

for all six

supported sample rates is generated internally from the

clock frequencies supplied to MCLKIN (24.576 MHz) and

X22IN (22.5792 MHz) as shown in Table 3.

MCLK24

FREQUENCY

MINIMUM

MAXIMUM

GND

256

◊

f

s

12.288 MHz

(256

◊

48 kHz)

V

DD

512

◊

f

s

24.576 MHz

(512

◊

48 kHz)

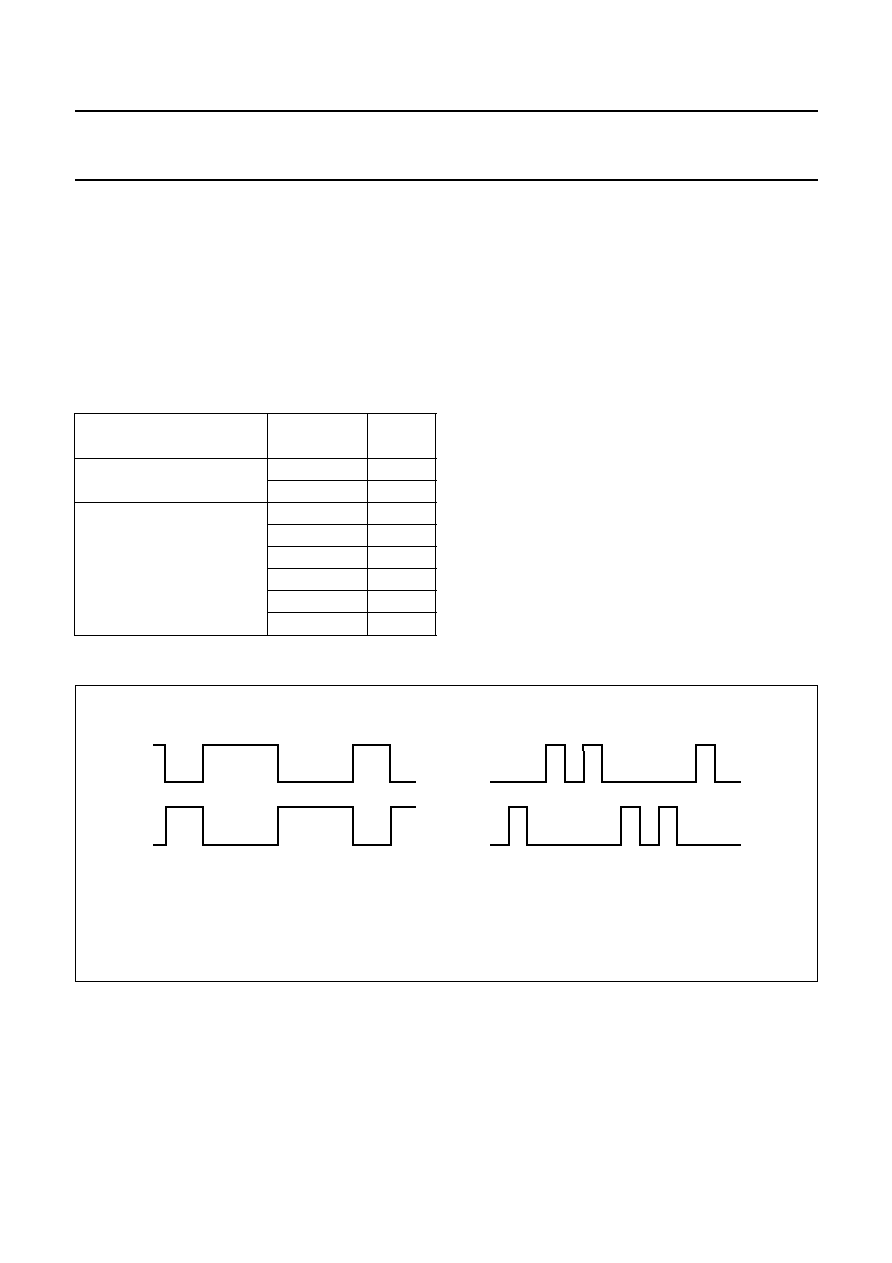

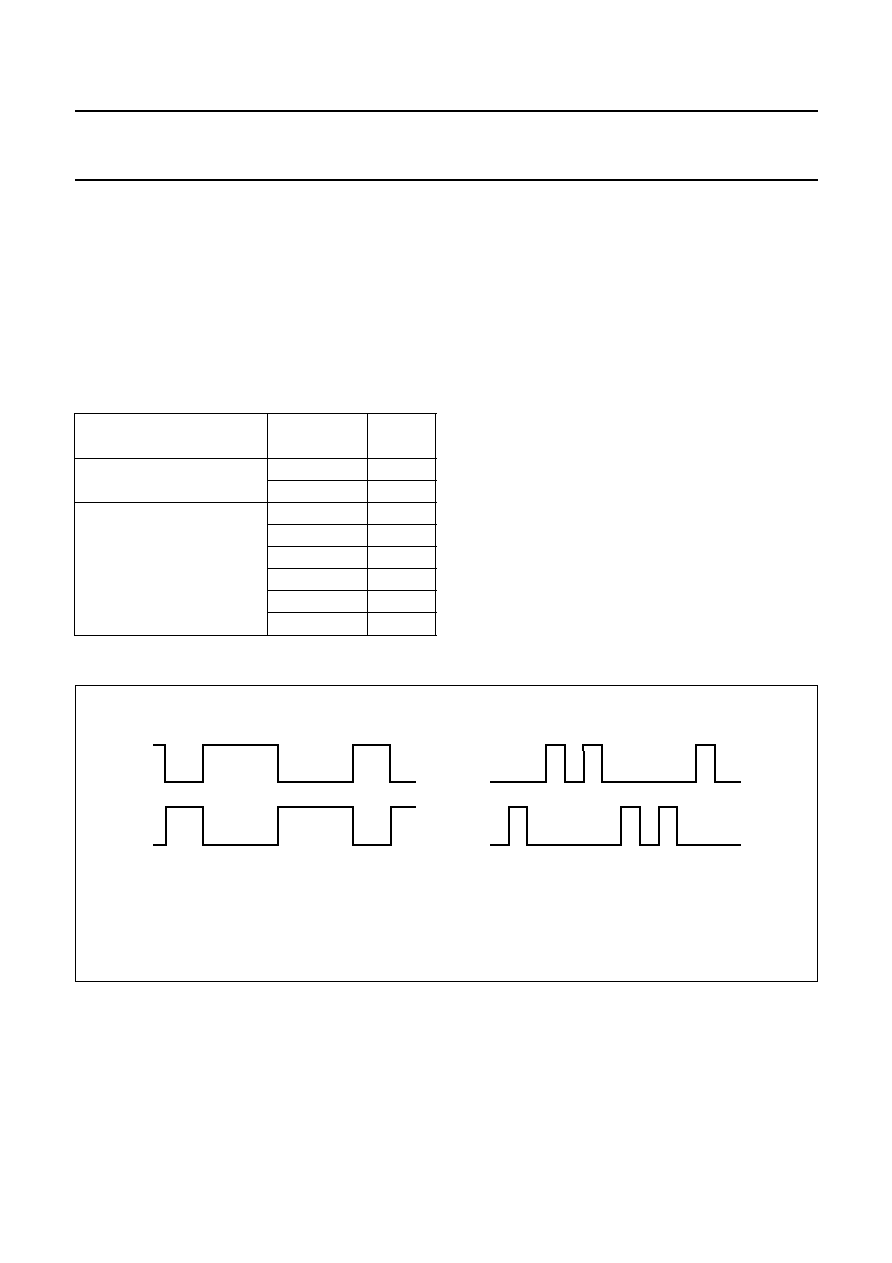

Table 3

Internal sample clock (default mode)

Note

1. Asymmetrical FSCLK.

The main advantage of this mode is that the SAA2502

determines automatically which sampling rate is active

from the sampling rate setting of the input data bit stream,

and then selects either MCLKIN or X22IN divided by the

correct number as the sample clock source.

Therefore this mode is particularly suited in applications

supporting dynamically varying sampling rates.

The required clocks may either be applied to MCLKIN

(respectively to X22IN) or be generated by connecting a

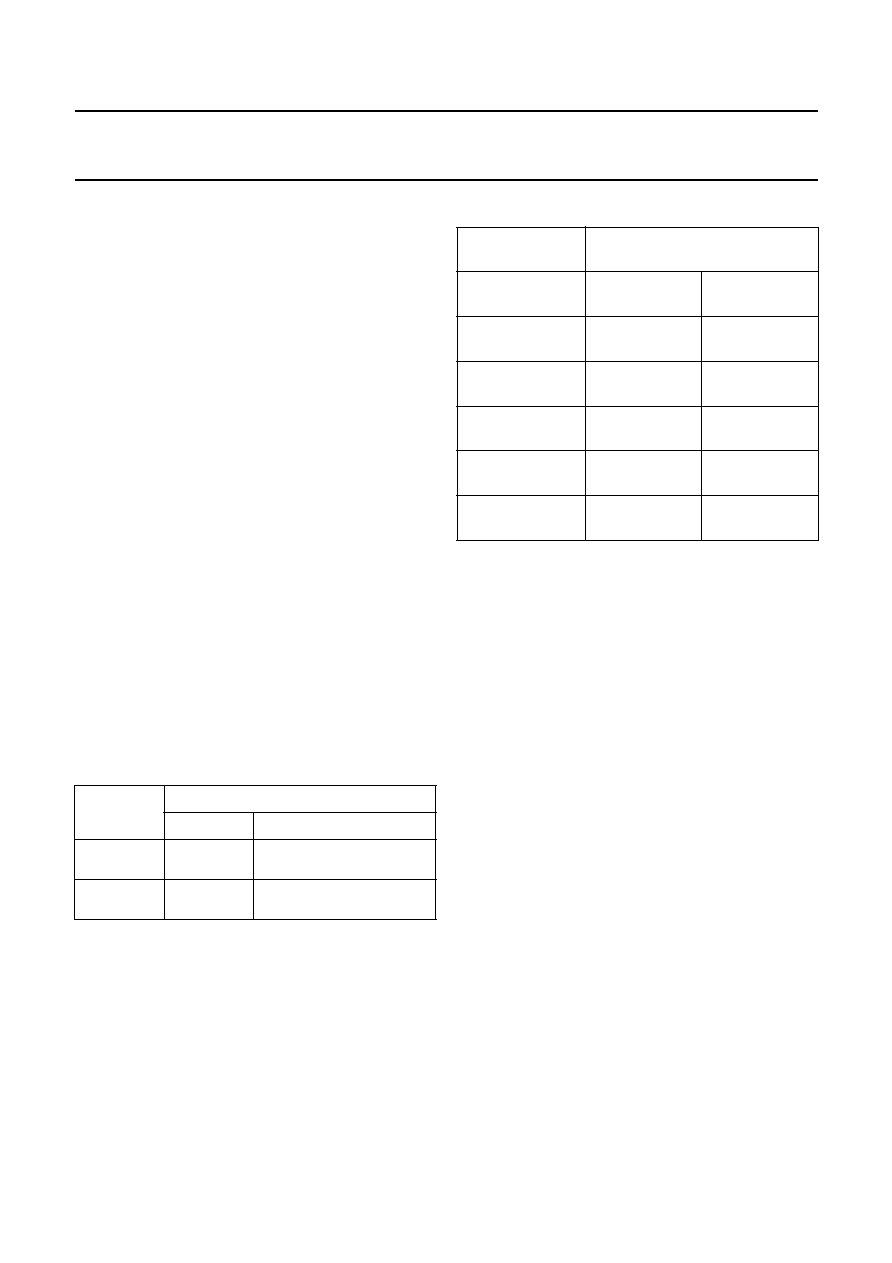

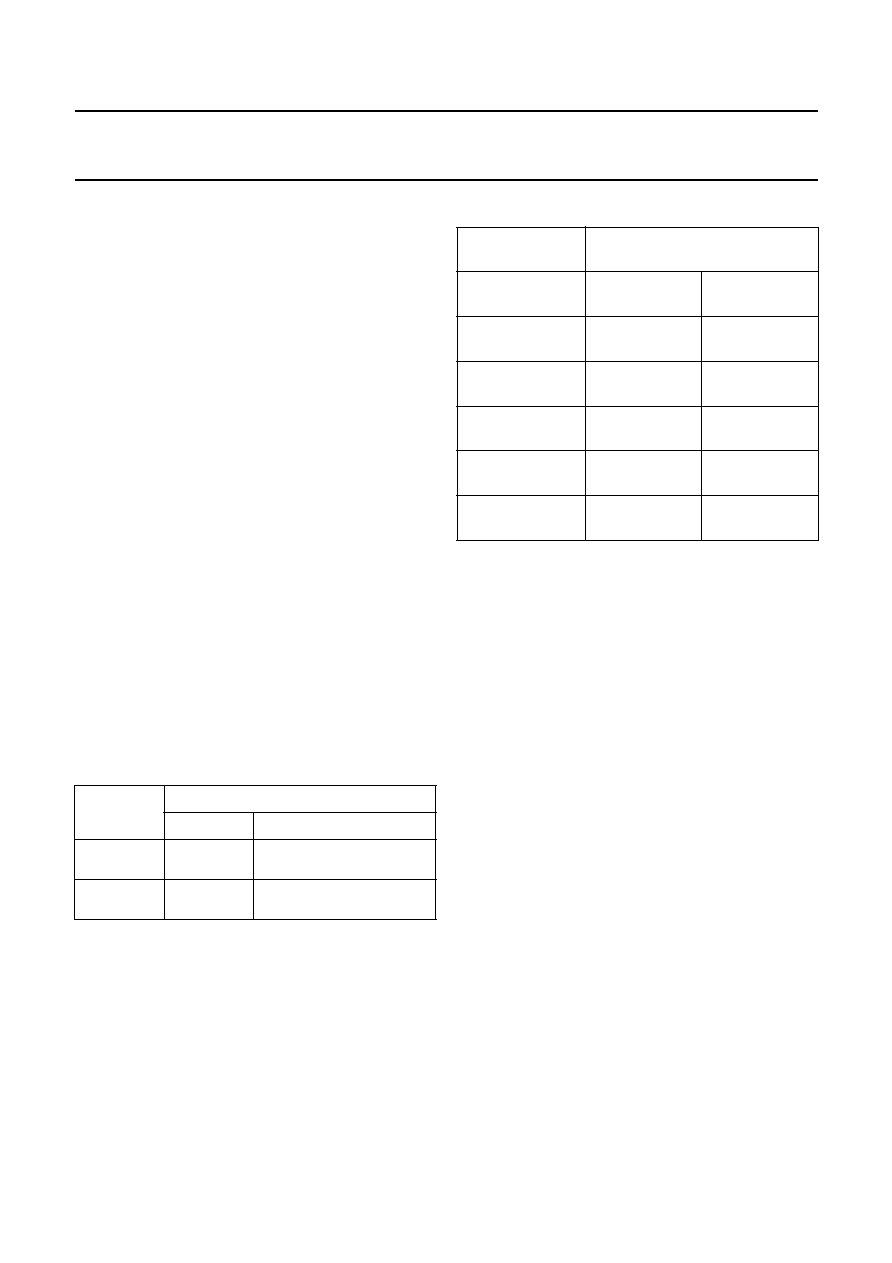

crystal between MCLKIN and MCLKOUT (respectively

between X22IN and X22OUT).

The recommended crystal oscillator configuration is

shown in Fig.3. The specified component values only

apply to crystals with a low equivalent series resistance

of <40

.

FSCLKIN, REFCLK and PHDIF are not used in this mode

(FSCLKIN and REFCLK should be connected to V

SS

or

V

DD

). MCLK24 has to be connected to V

DD

, while the

control flags FSCINP and FSC384 should be left in their

default (cleared) states. If the FSCLK output is enabled (by

setting control flag FSCENA) FSCLK will produce a

buffered version of 256

◊

f

s

.

SAMPLE

FREQUENCY

RESULTANT FREQUENCIES

(MHz)

256

◊

48 kHz

12.288

256

◊

44.1 kHz

11.2896

256

◊

32 kHz

8.192

(1)

256

◊

24 kHz

6.144

256

◊

22.05 kHz

5.6448

256

◊

16 kHz

4.096

24.576

2

------------------

22.5792

2

---------------------

24.576

3

------------------

24.576

4

------------------

22.5792

4

---------------------

24.576

6

------------------

1997 Nov 17

9

Philips Semiconductors

Preliminary specification

ISO/MPEG Audio Source Decoder

SAA2502

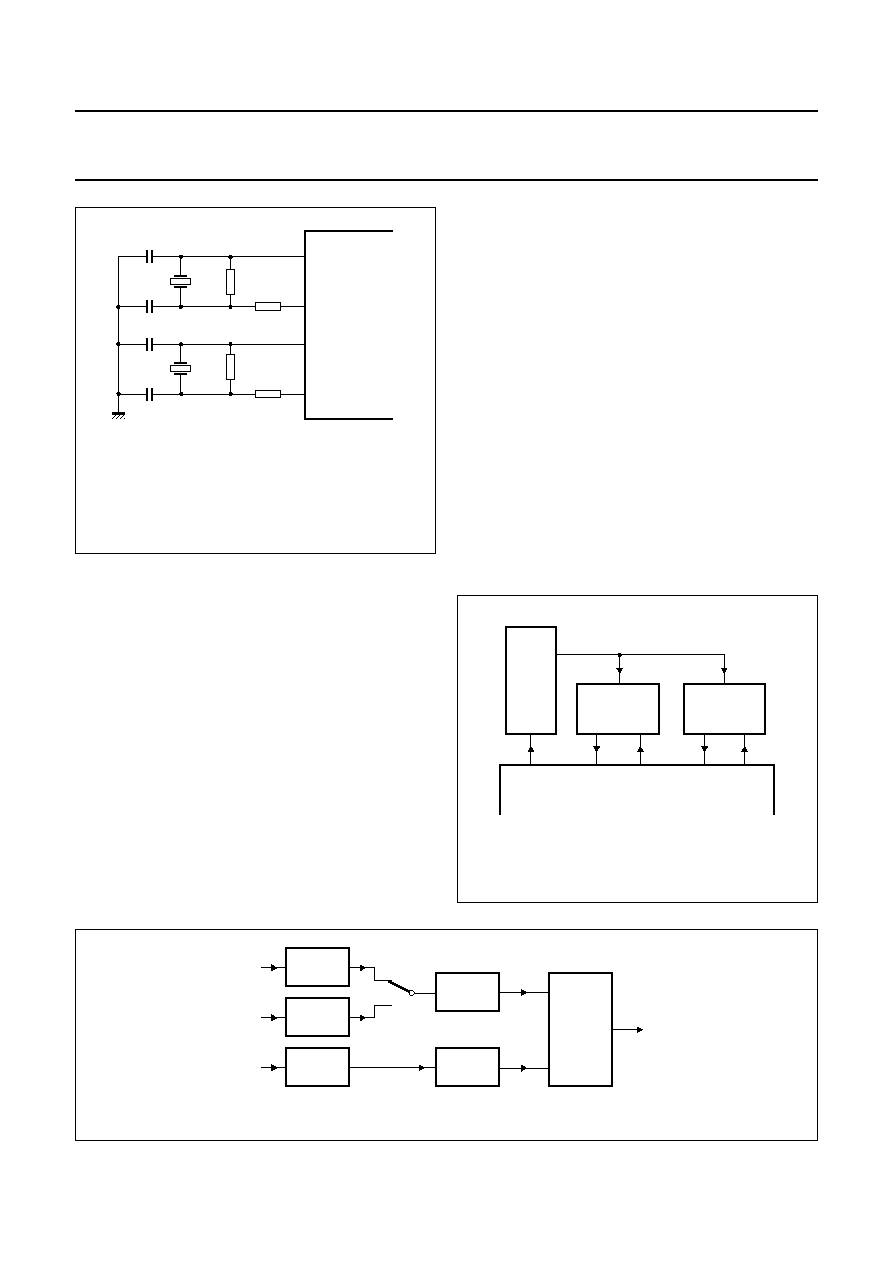

7.2.3

L

OCKED INTERNAL SAMPLE CLOCK

This mode differs from the previous one in just a single

aspect: the REFCLK and PHDIF pins are used to realize a

Phase-Locked Loop (PLL) which locks the 256

◊

f

s

sample

clock to the REFCLK reference clock. Because the real

goal is locking sample clock and bit rate, a reference clock

should be used which has a fixed relation to the input bit

rate. An example of such a PLL realization is shown in

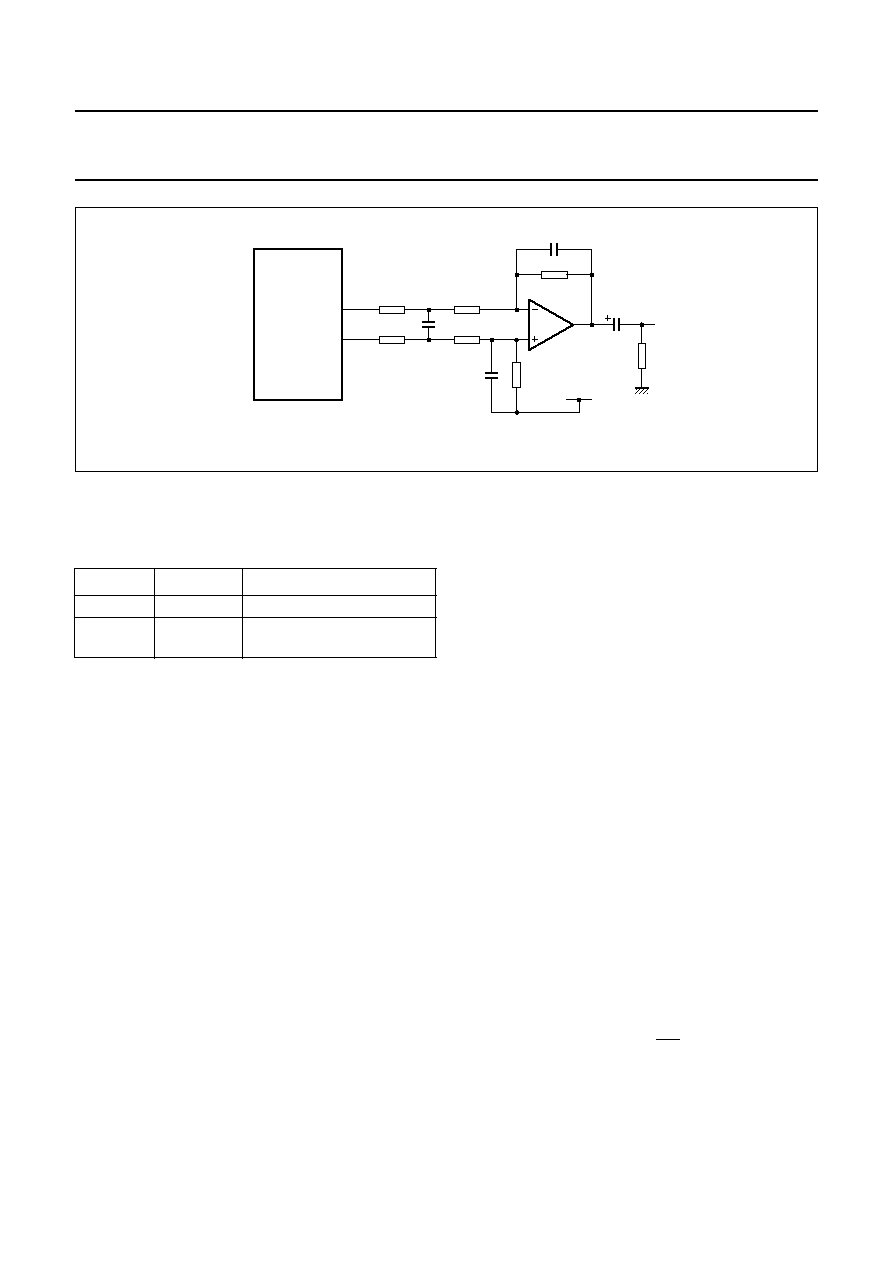

Fig.4.

The phase comparator output PHDIF generates a signal

with a DC component proportional to the phase difference

between the internal signals SIG and REF (see Fig.5).

The 22.5792 MHz signal X22IN is divided by 147 and the

24.576 MHz signal MCLKIN is divided by 160. This results

in the same frequency (153.6 kHz) in both events.

One of the two signals is selected as input for the

programmable divide by N

1

unit. The selector is controlled

handbook, halfpage

MGE470

C2

C1

C3

C4

X1

X2

R1

R4

R2

R3

26

27

32

31

SAA2502

Fig.3 Crystal oscillator components.

C1 = C2 = C3 = C4 = 10 pF;

R1 = R4 = 100 k

;

R2 = R3 = 1 k

;

X1 = 22.5792 MHz;

X2 = 24.5760 MHz.

in such a way that SIG and 256

◊

f

s

will stem from the

same source. The divisor N

1

is programmable with

(1 to 16)

◊

8 as possible values.

REF on the other hand is derived from the REFCLK input.

Two programmable dividers in series are used here. N

2

may adopt one of 4 possible values: 5, 25, 125 or 625

while N

3

can be programmed to be 1 to 32. Because both

inputs of the phase comparator have to operate at identical

frequencies the next equation has to be obeyed:

or, written differently:

For a list of supported REFCLK frequency values

see Chapter 8.

The mode of operation of the phase comparator in Fig.5 is

programmable via the control flag PHSMOD:

REFCLK

N

2

N

3

◊

--------------------------

156.6 kHz

N

1

---------------------------

=

REFCLK

153.6 kHz

N

2

◊

N

3

◊

N

1

------------------------------------------------------

=

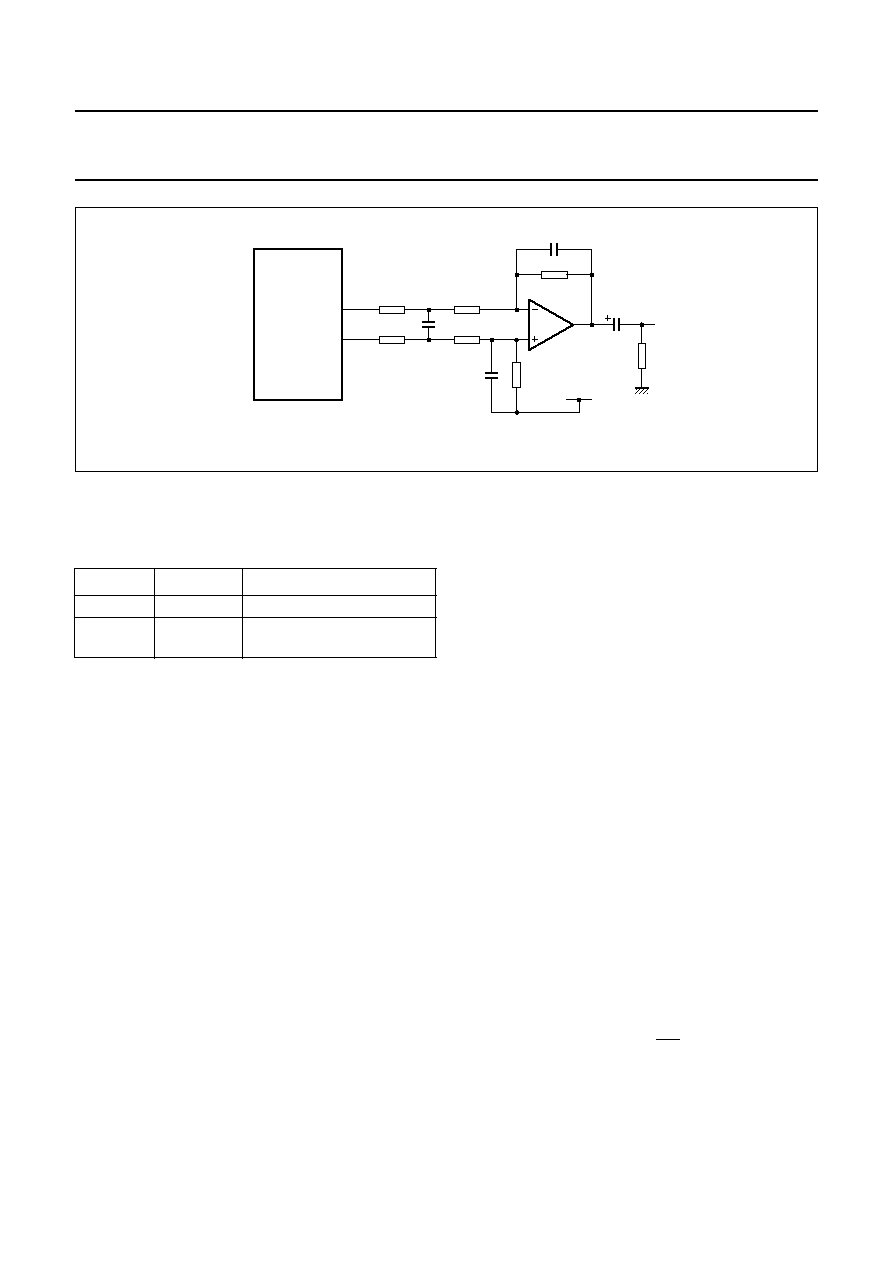

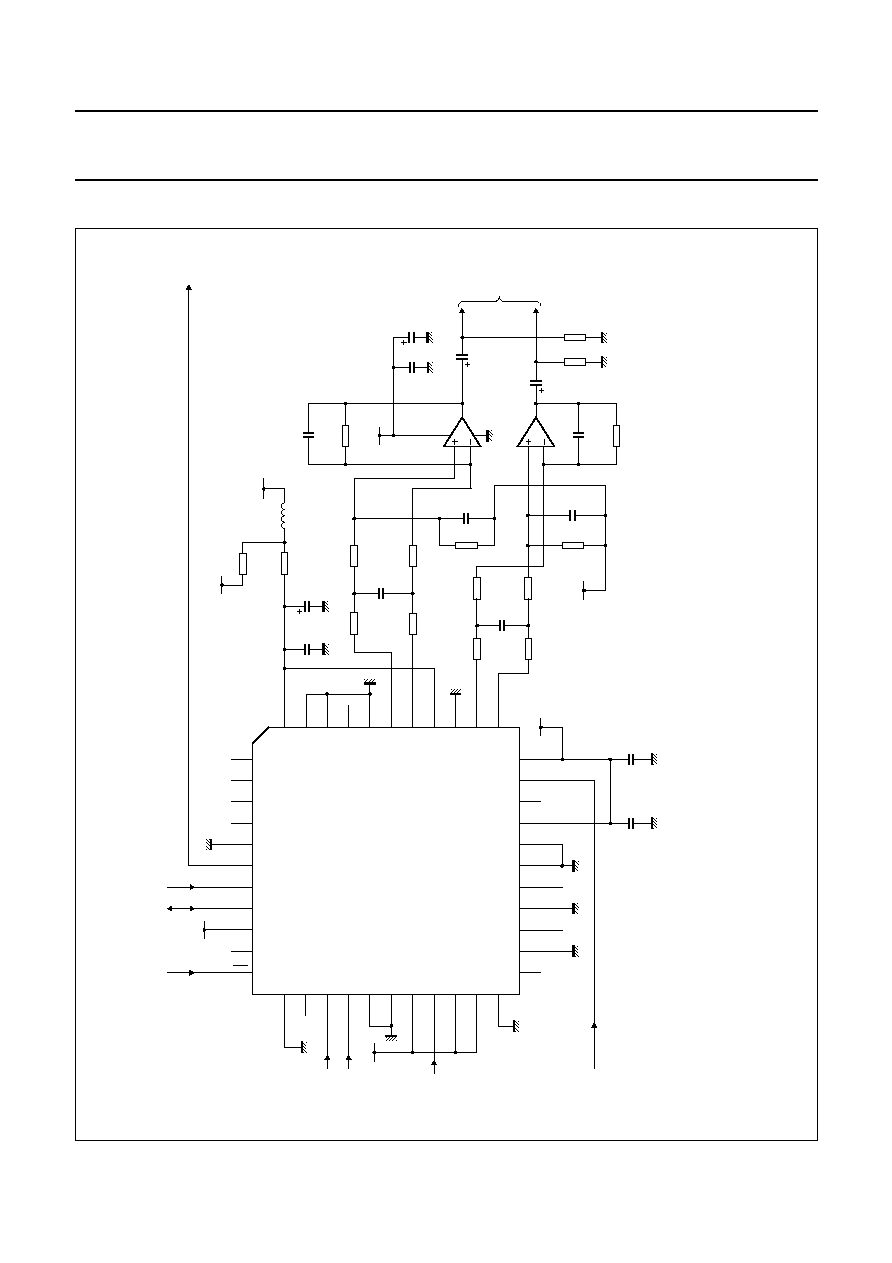

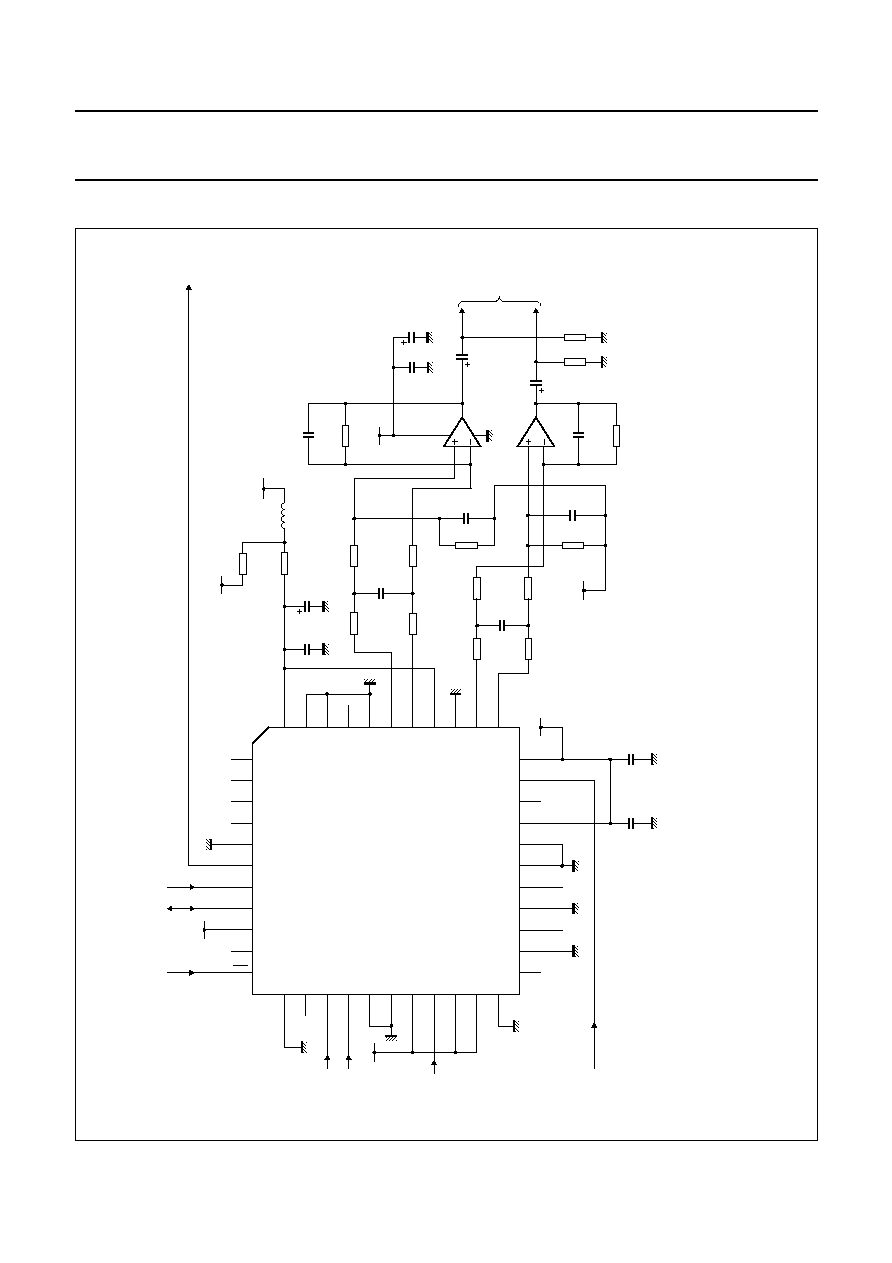

Fig.4 External PLL components.

handbook, halfpage

MGE471

LOW-

PASS

FILTER

24.576 MHz

VCXO

22.5792 MHZ

VCXO

PHDIF

MCLKIN

MCLKOUT

X22IN X22OUT

SAA2502

Fig.5 SAA2502 phase comparator.

handbook, full pagewidth

MGE472

DIVIDE BY

147

DIVIDE BY

160

DIVIDE BY

N2

DIVIDE BY

N3

DIVIDE BY

N1

PHASE

COMPA-

RATOR

X22IN

MCLKIN

REFCLK

153.6 kHz

SIG

REF

PHDIF

1997 Nov 17

10

Philips Semiconductors

Preliminary specification

ISO/MPEG Audio Source Decoder

SAA2502

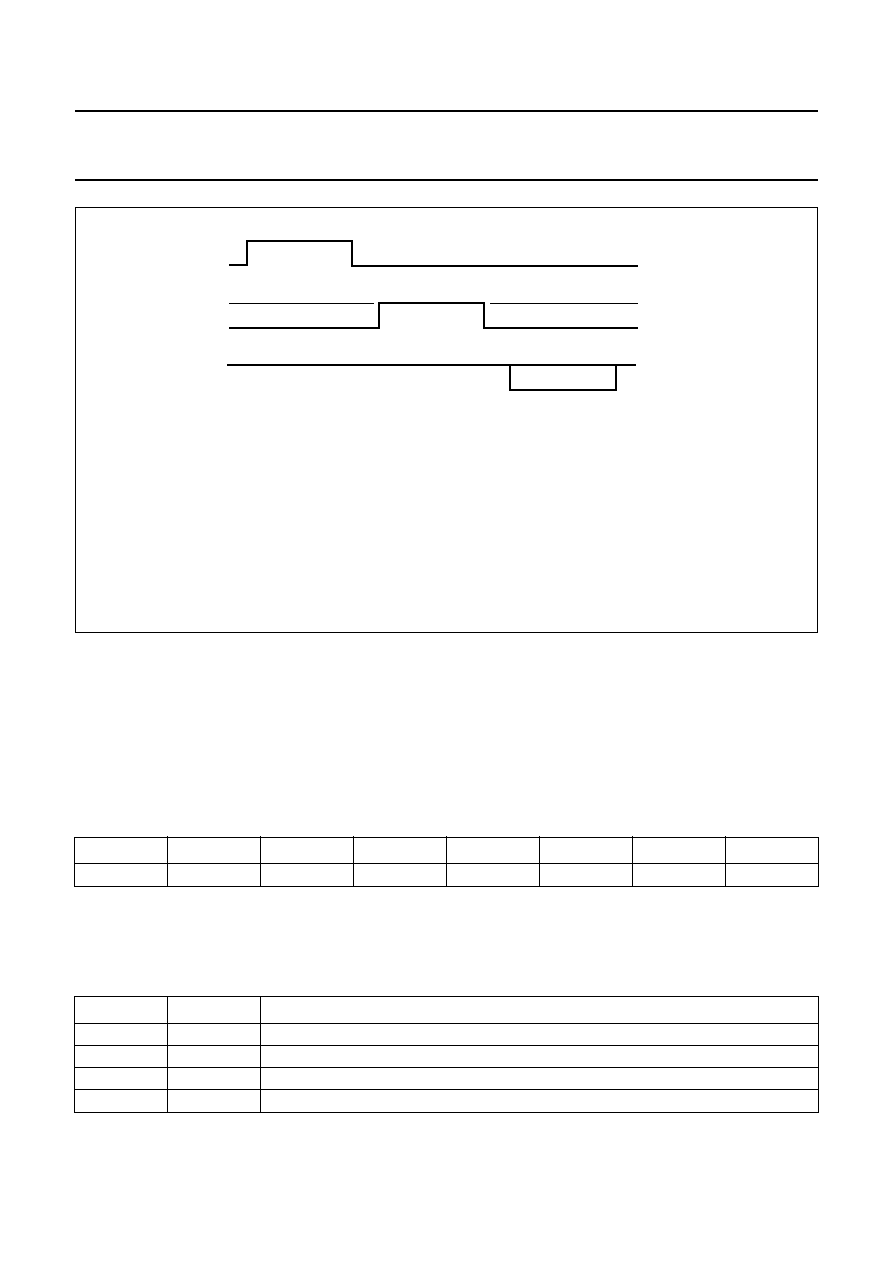

7.2.3.1

XOR mode

PHDIF is the XOR function of SIG and REF. The frequency

is twice the frequency of SIG and REF. The PHDIF output

carries a signal, switching between GND and V

DD

, with an

average value V

avg

which is a function of the phase

difference between SIG and REF (see left part of Fig.6).

The locking range in this mode of operation is maximum

for even values of N

3

(180 degrees phase difference) but

less for odd values of N

3

. It is minimum for N

3

= 3

(120 degrees phase difference).

7.2.3.2

Edge triggered mode

PHDIF is only influenced by the rising edges of SIG and

REF. Consequently its frequency is equal to the SIG and

REF frequency.

The electrical behaviour of the PHDIF output pin in this

mode is special:

PHDIF is HIGH from the rising edge of REF to the rising

edge of SIG and 3-stated elsewhere if REF is leading and

PHDIF is low from rising edge of SIG to rising edge of REF

and 3-stated elsewhere if REF is trailing. Therefore PHDIF

is NOT 3-stated during a portion t

up

of each cycle when it

acts as a pull-up device or during a portion t

down

of each

cycle when it acts as a pull-down device (see right part of

Fig.6).

As a result the locking range is always 360 degrees phase

difference. The output behaviour as function of phase

difference is non-symmetrical with reference to the vertical

axis, but a reversed mode is also available (by setting the

control flag PHSRVS).

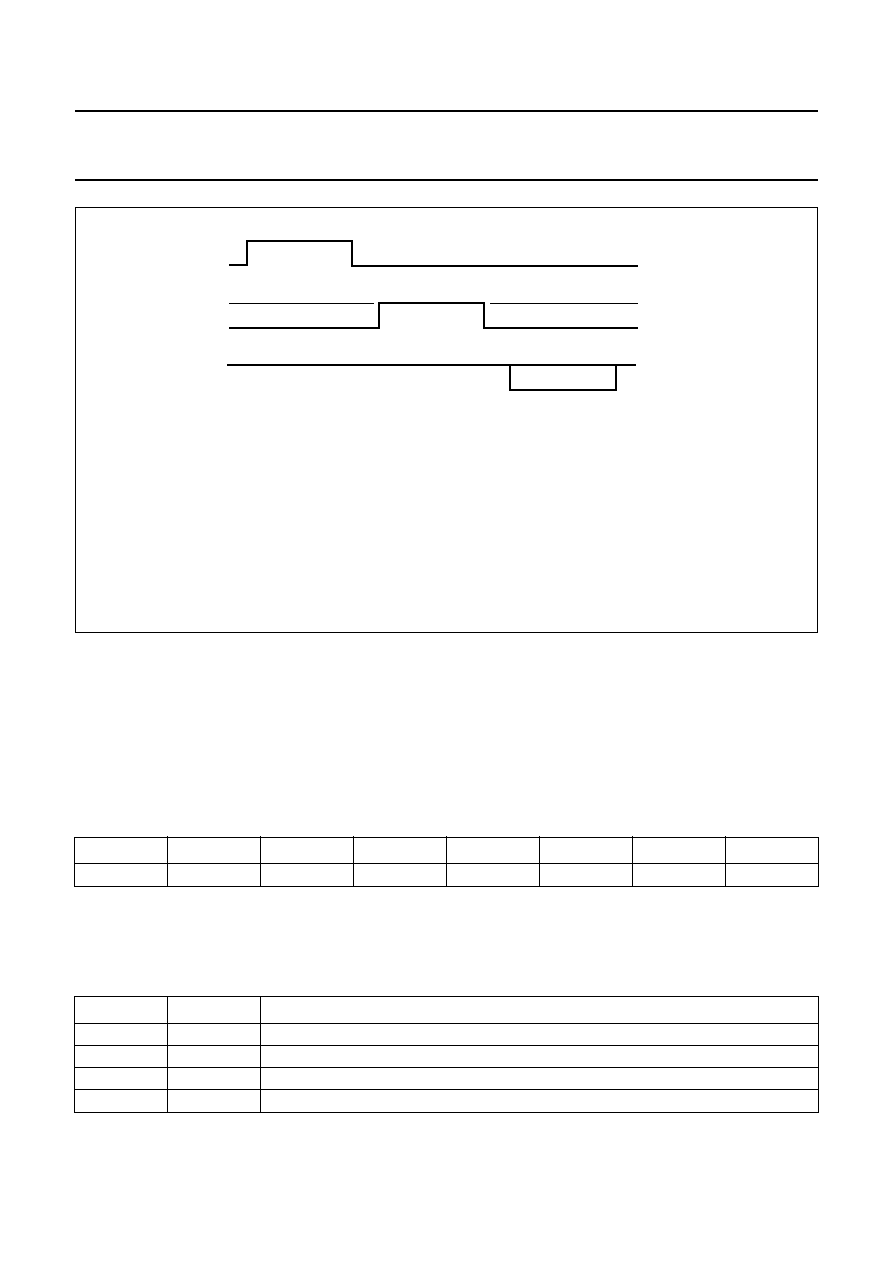

Fig.6 PHDIF output behaviour.

handbook, full pagewidth

MGE473

REF to SIG phase difference

REF to SIG phase difference

max

min

0

o

180

o

360

o

-

180

o

0

o

+

180

o

0

1

5/6

1/6

Vavg

VDD

100%

100%

0%

tup

tdown

T

t1

t2

T

t

PHDIF

3-stated

XOR mode

edge triggered mode

1997 Nov 17

11

Philips Semiconductors

Preliminary specification

ISO/MPEG Audio Source Decoder

SAA2502

7.2.4

L

IMITED SAMPLING FREQUENCY SUPPORT FOR

INTERNAL SAMPLING CLOCKS

7.2.4.1

When sampling frequency is limited to

44.1 and/or 22.05 kHz:

In this event MCLKIN is only required to generate the

master clock frequency. Consequently the remarks on

MCLKIN frequency also apply in this special case.

7.2.4.2

When sampling frequency is limited to

48, 32, 24 and/or 16 kHz:

In this event X22IN is not required. Therefore X22IN

should be connected to V

SS

or V

DD

, but it is more efficient

to apply any available clock signal to X22IN. Because

44.1 kHz is the default initial sampling frequency it may

also be advisable to over-rule the sampling frequency after

a hard reset.

7.3

Input interface module

The input interface module handles the reception of the

coded input data stream.

The module can be configured to operate in 3 distinct

modes of operation:

∑

The master input mode

∑

The slave input mode

∑

The buffer controlled input mode.

Input interface mode must be stationary while the device is

in normal operation. Changing mode will result in an

(automatically generated) internal soft reset.

The inputs CD, CDVAL, CDEF and CDSY are all clocked

at the rising edge of the CDCL bit clock.

CDRQ changes at the falling edge of CDCL.

CDVAL = logic 0 indicates that CD and CDEF should be

ignored while CDVAL = logic 1 indicates that CD is a valid

coded input stream data bit (CDEF is then its error

attribute).

CDEF = logic 0 means that the value of CD may be

assumed to be reliable while CDEF = logic 1 means that

the value of CD is flagged as insecure (e.g. due to erratic

non-correctable channel behaviour). The value of CDEF

may be different for each data bit, but is combined by the

SAA2502 for every group of 8 (byte aligned) valid coded

input bits.

CDSY will only have effect when the SYMOD control flags

are set to 10 or 11. When SYMOD = 10 the valid input bit

at a rising edge of CDSY marks the start of a new byte

(when SYMOD = 11 it marks the start of a new MPEG

audio frame). Note that just the rising edge of CDSY is

important, the falling edge has no meaning.

If CDSY is used with SYMOD = 10 leading edges must be

frequent enough to assure fast byte alignment, if used with

SYMOD = 11 a leading edge must be present every frame.

Leading edges of CDSY may occur while CDVAL is

(implicitly) high. Alternatively, a situation as shown in Fig.8

is also allowed, where CDSY has a rising edge while

CDVAL is low, i.e. during invalid data. The first valid CD bit

after the rising edge of CDVAL is then interpreted as the

first byte or frame bit.

The output pin CDRQ is used to request new coded input

data.

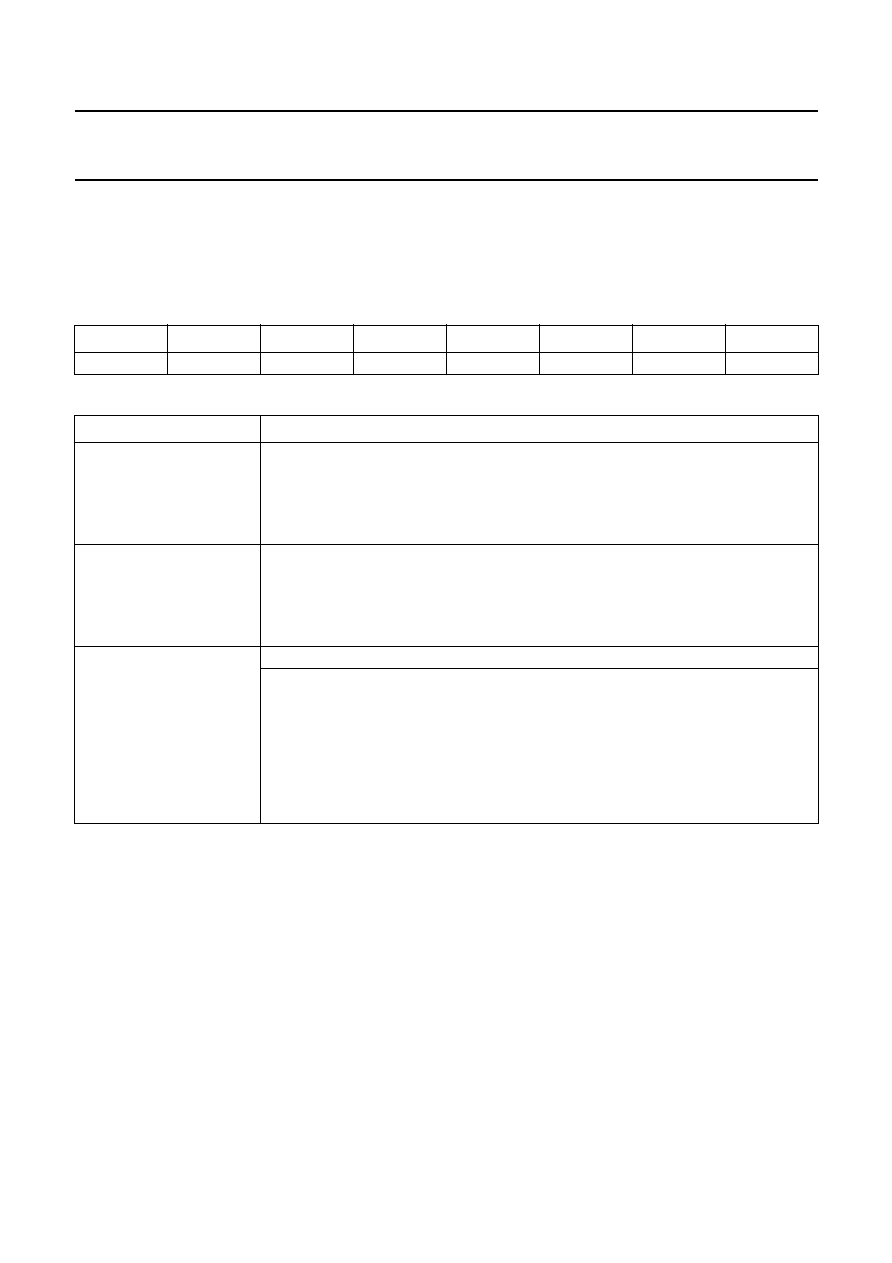

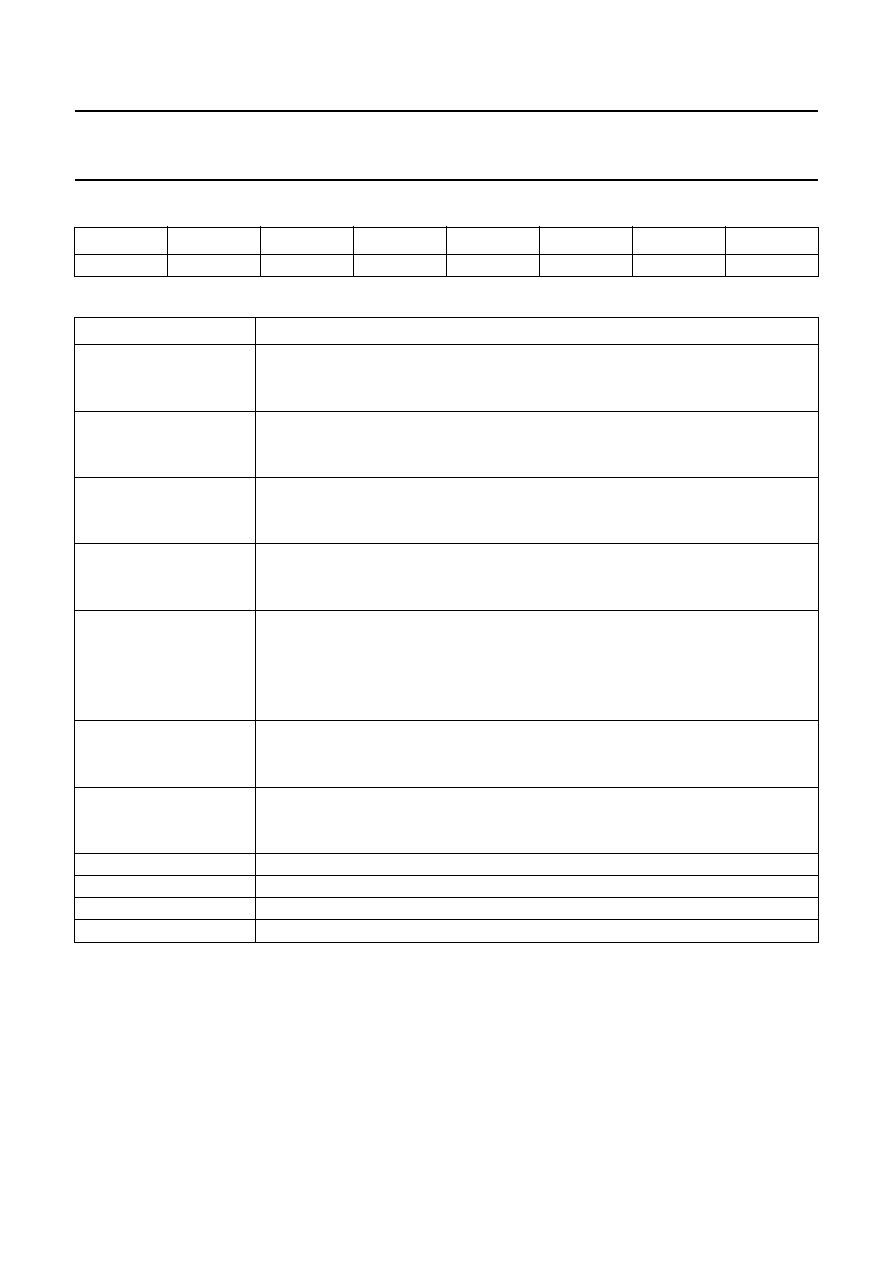

Table 4

Signals of coded data input interface

SIGNAL

DIRECTION

FUNCTION

CD

input

coded data input bit

CDVAL

input

coded data bit valid flag

CDEF

input

coded data bit error flag

CDSY

input

coded data sync (start of byte/frame) indication

CDCL

input/output

coded data bit clock

CDRQ

output

coded data request

1997 Nov 17

12

Philips Semiconductors

Preliminary specification

ISO/MPEG Audio Source Decoder

SAA2502

7.3.1

M

ASTER INPUT MODE

Master input mode is the default mode of operation. This

mode may also be enforced by setting the INMOD control

flags to 00. Which means that the SAA2502 will generate

requests for input data at regular intervals. CDVAL is not

used in this mode (it should be connected to V

SS

or V

DD

).

CDVAL is implicitly assumed to be logic 1 during the 2nd

up to (and including) the 17th bit slot after a rising or a

falling edge of CDRQ (see Fig.7). Thus signal CD should

carry the coded data in bursts of 16 valid bits.

In this mode the CDRQ frequency is locked to (i.e. derived

from) the 256

◊

f

s

clock. Its average value equals the bit

rate divided by 32.

The bit clock CDCL is output, its frequency is fixed:

when MCLK24 = logic 1

when MCLK24 = logic 0.

MCLK

32

------------------

MCLK

16

------------------

MPEG free format bit rate is NOT allowed in this mode.

Assume N is the number of CDCL periods between two

transitions of CDRQ, and R is the number of CDCL periods

to obtain the effective bit rate E (in kbits/s) at a CDCL

frequency of 768 kHz, i.e.

.

The SAA2502 keeps the average value of N exactly at R,

but individual values of N may vary between

N = round (R)

-

2 and N = round (R) +2.

7.3.2

S

LAVE INPUT MODE

Slave input mode is activated by setting the INMOD control

flags to 0 1. Which means that the SAA2502 will accept

input data as presented by the application. In this mode it

is the responsibility of the application to maintain locking

between the 256

◊

f

s

sample clock and the average bit

rate.

R

16

768

◊

E

----------------------

=

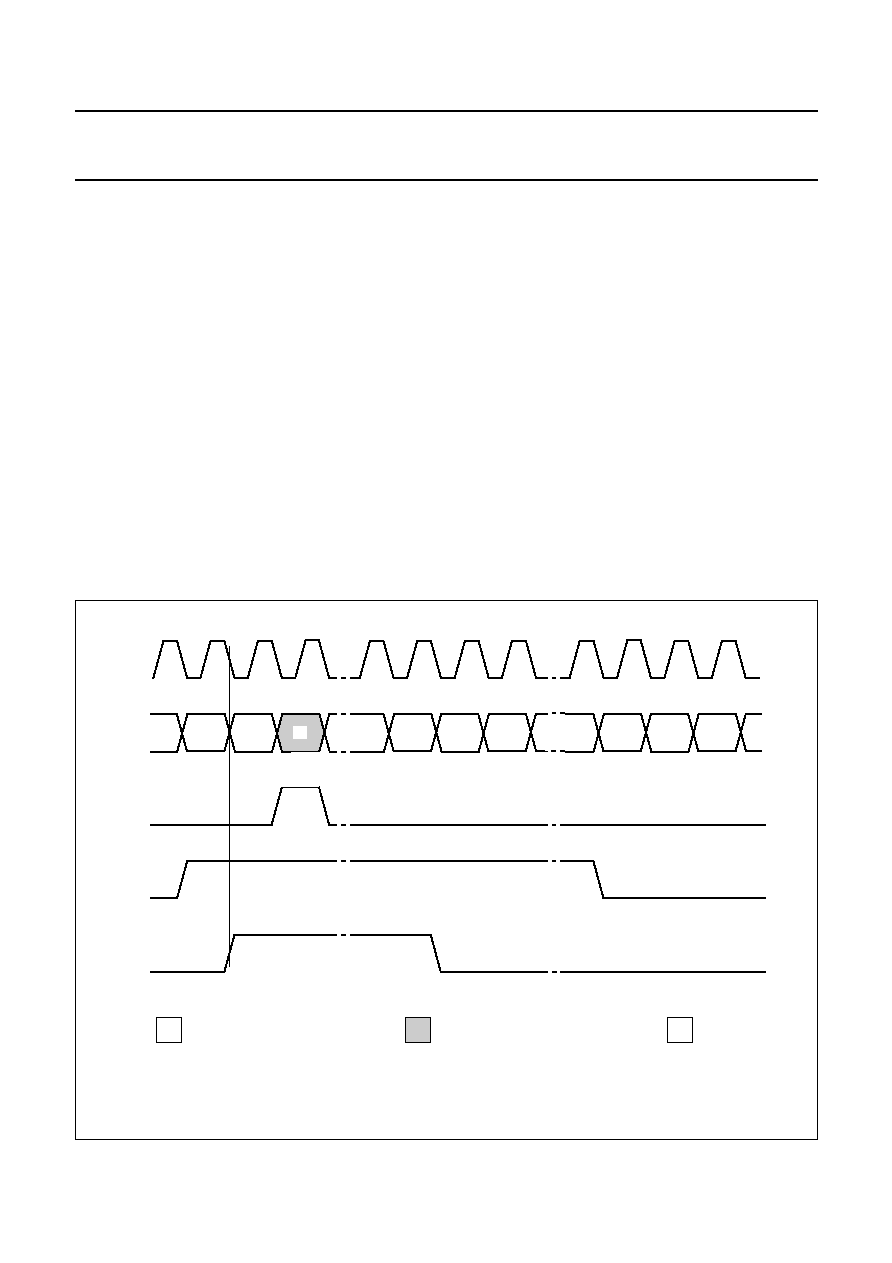

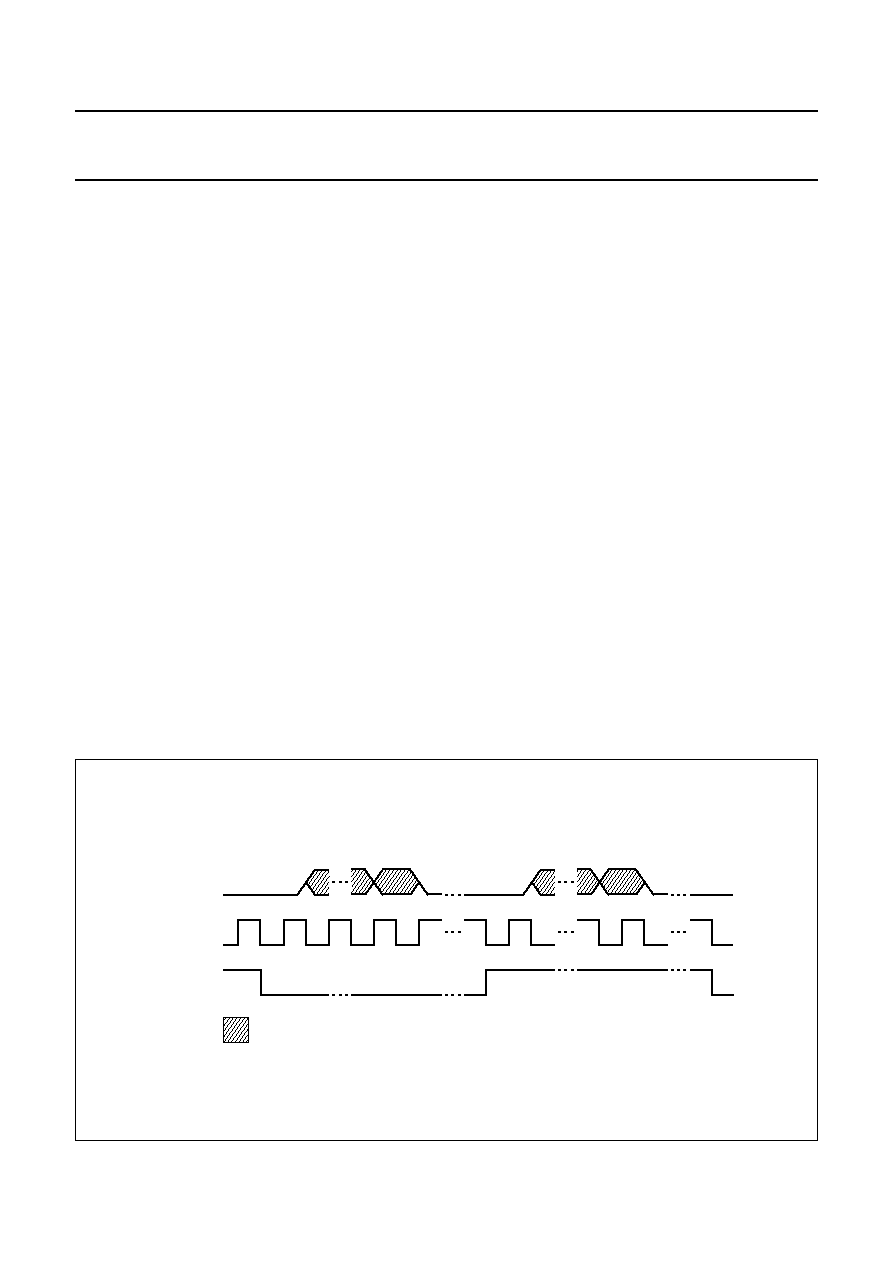

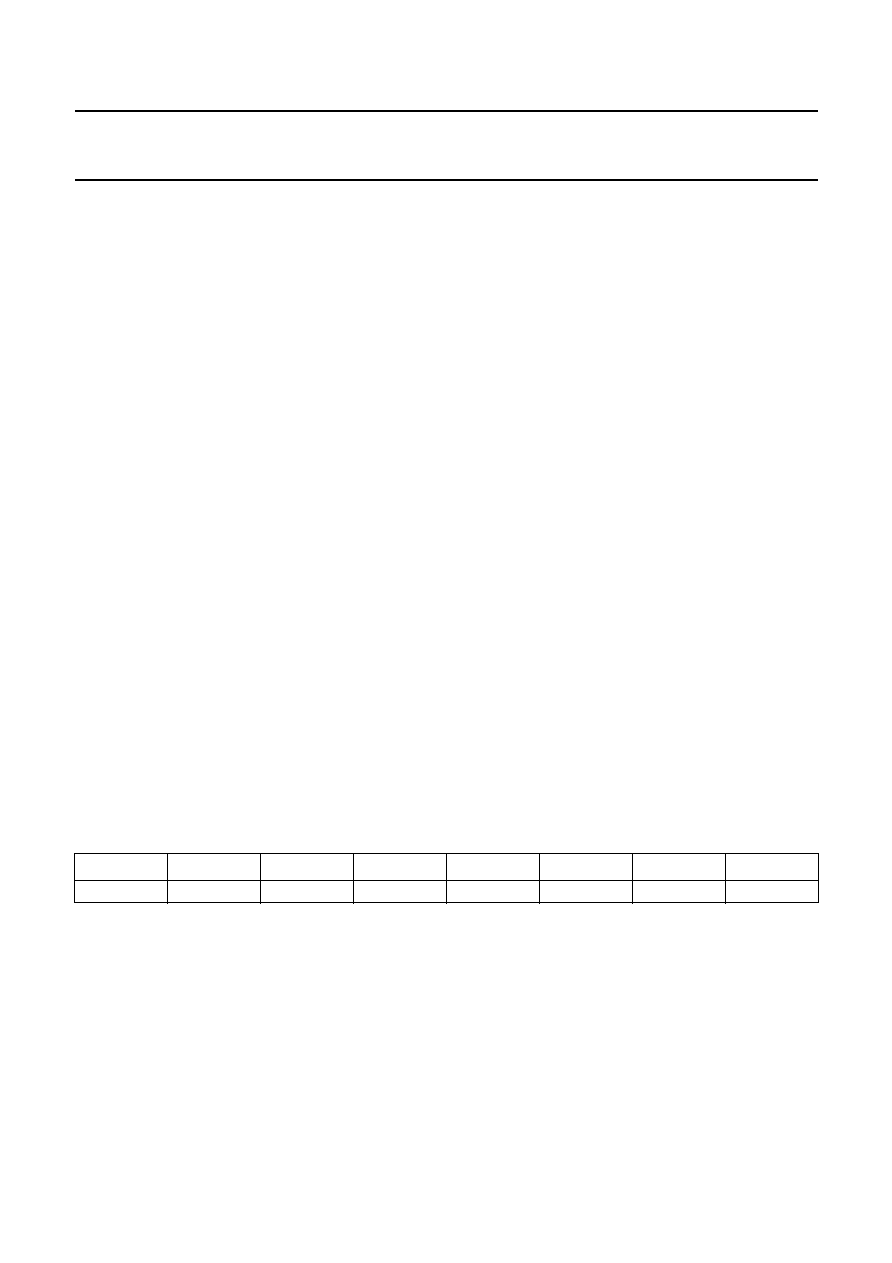

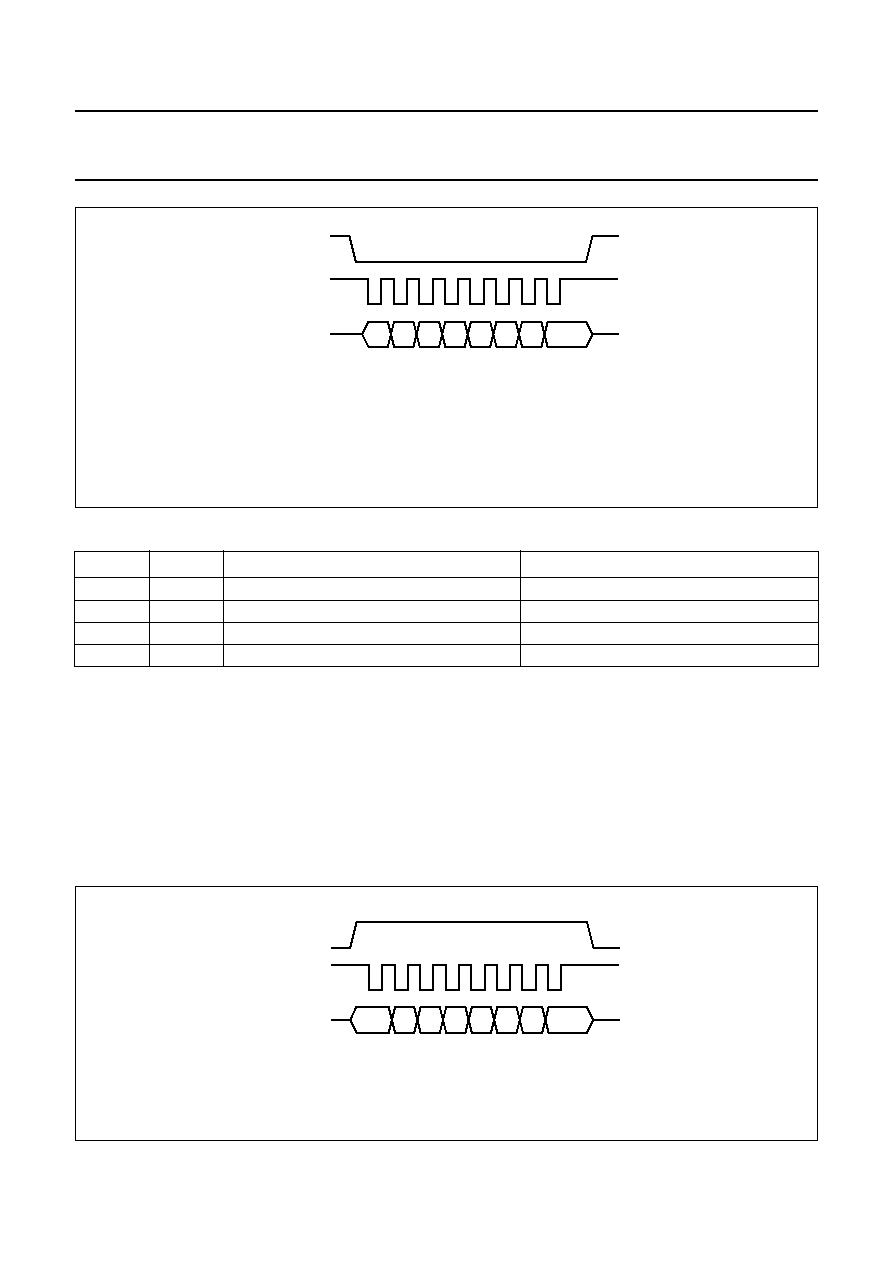

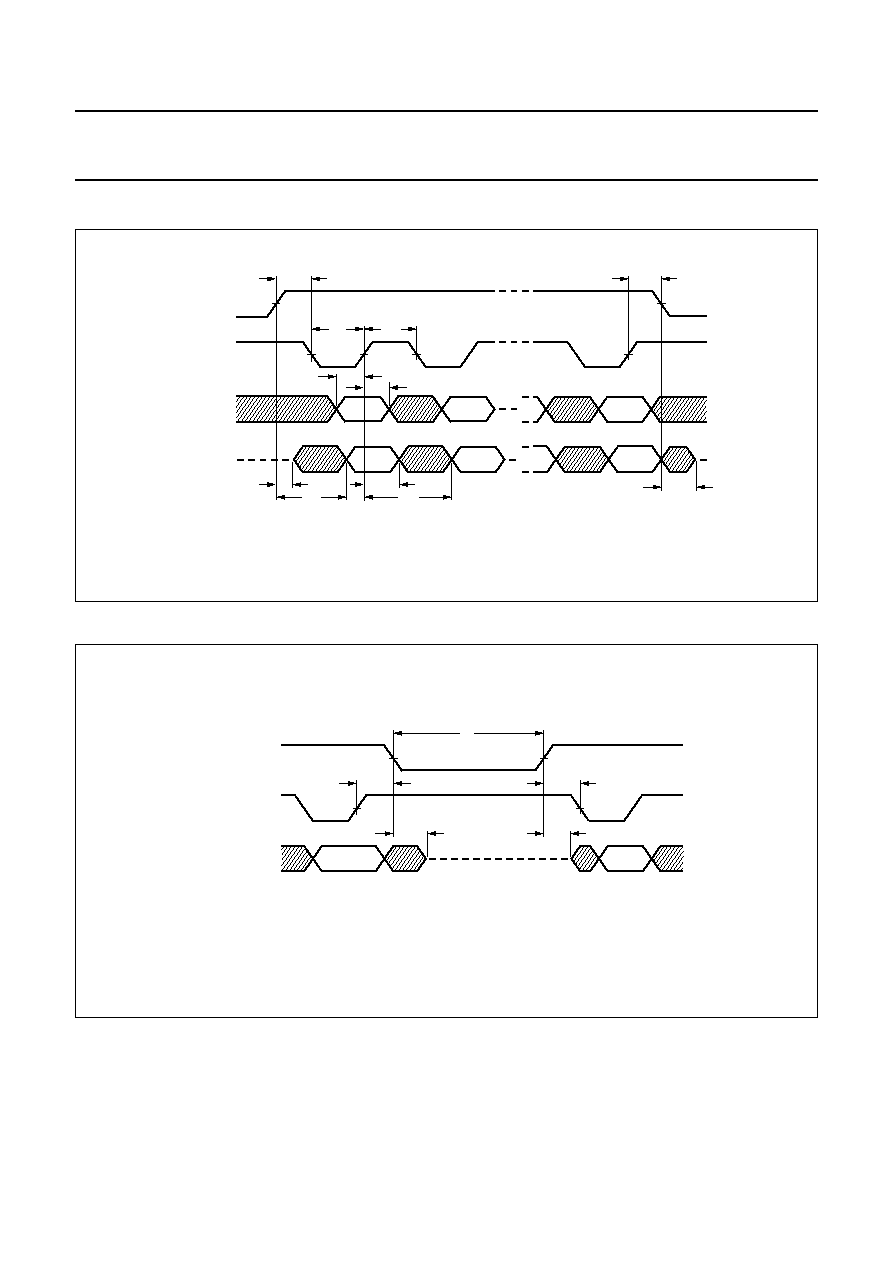

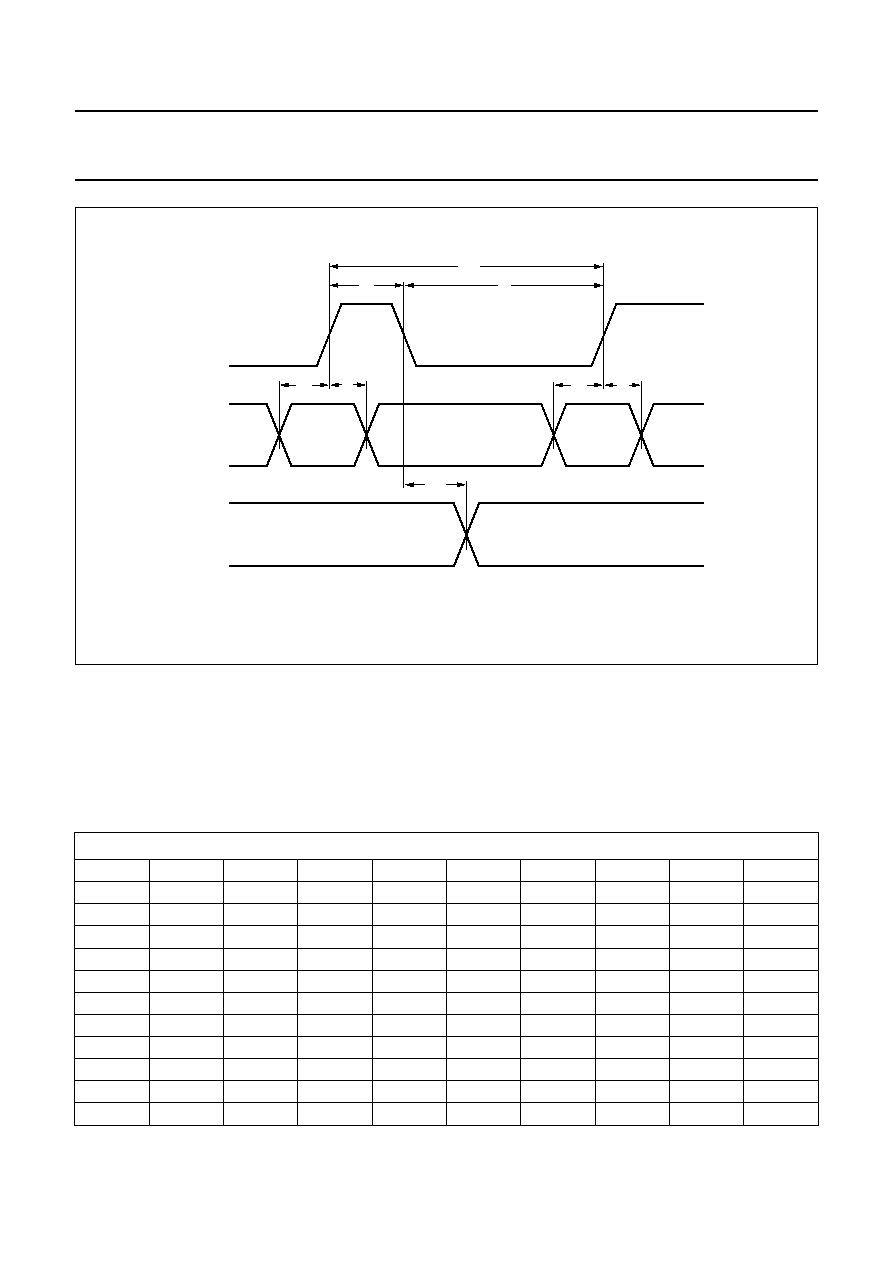

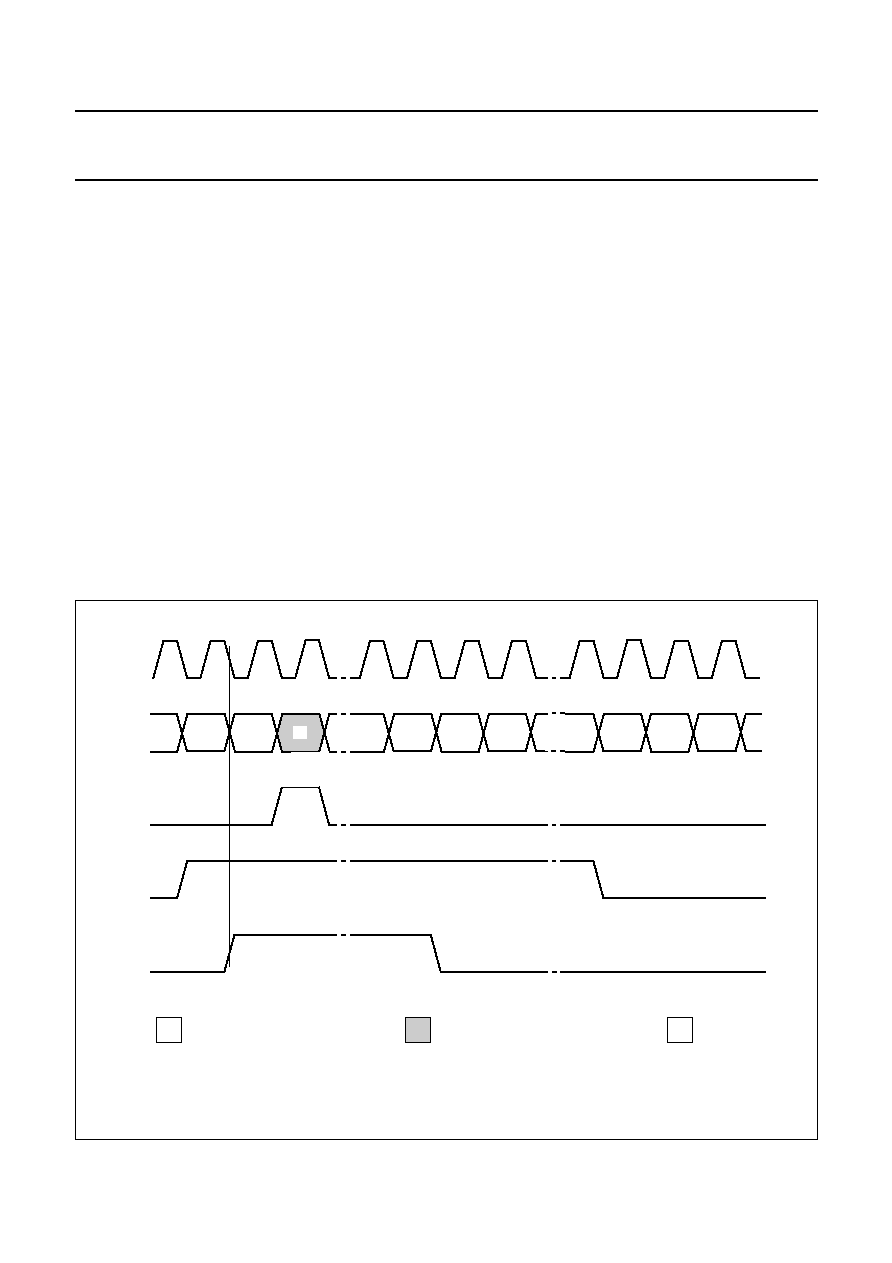

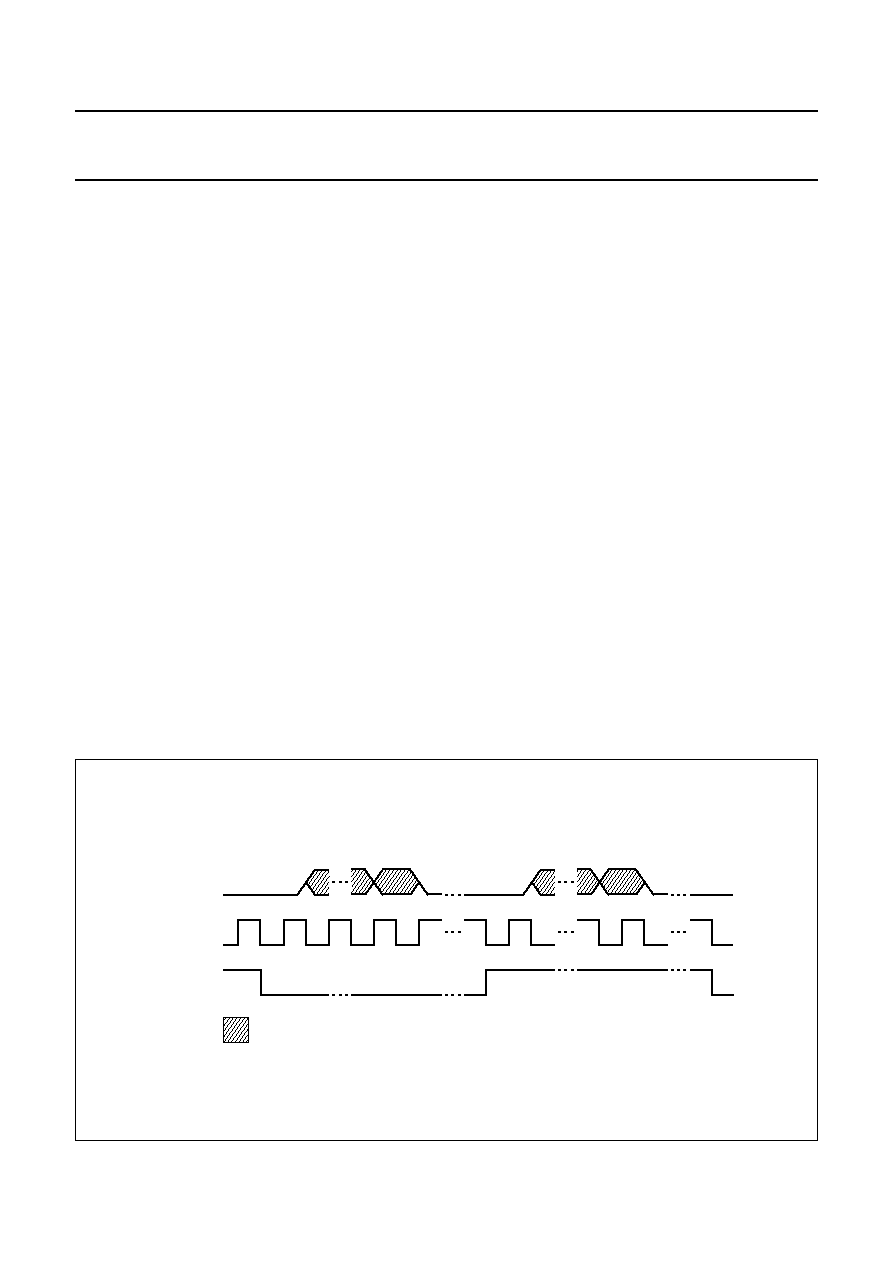

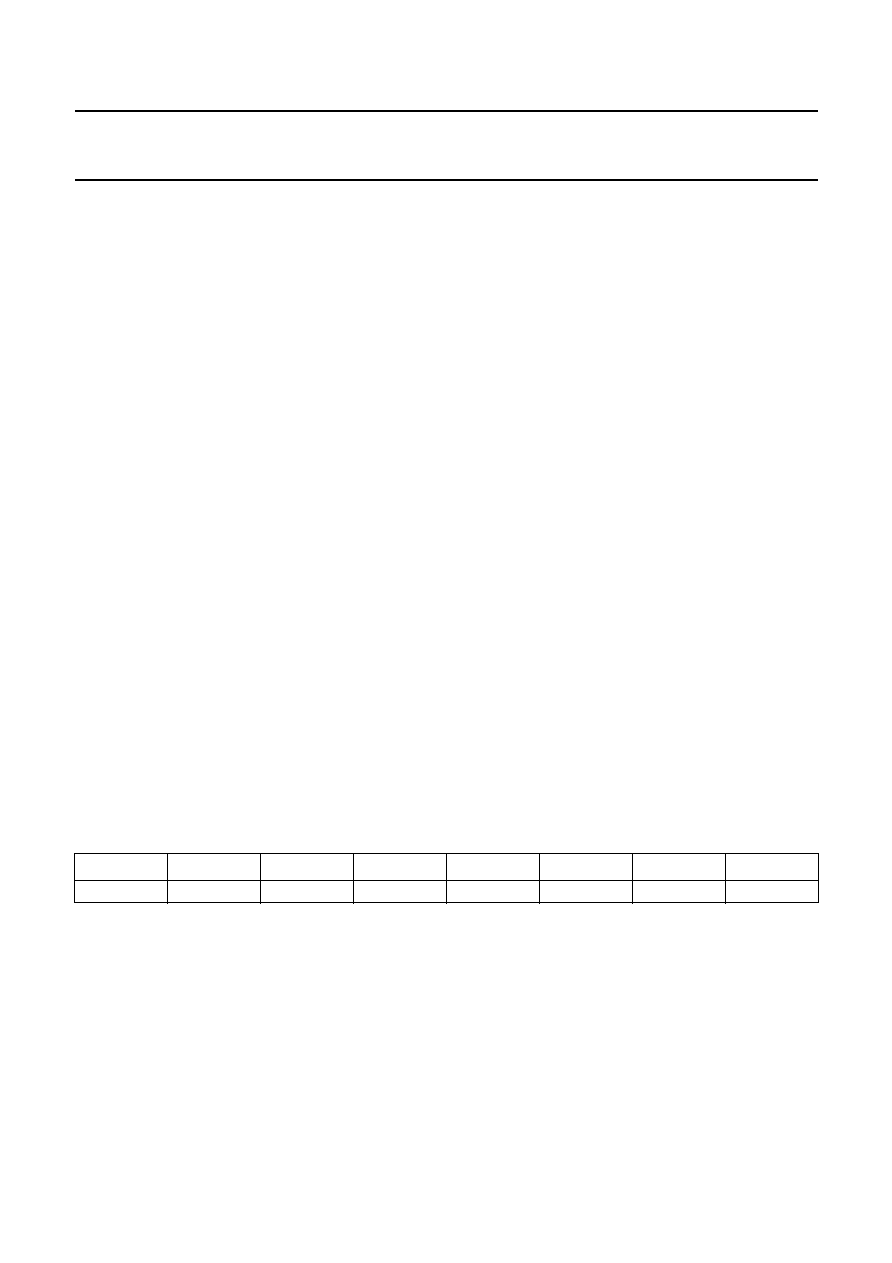

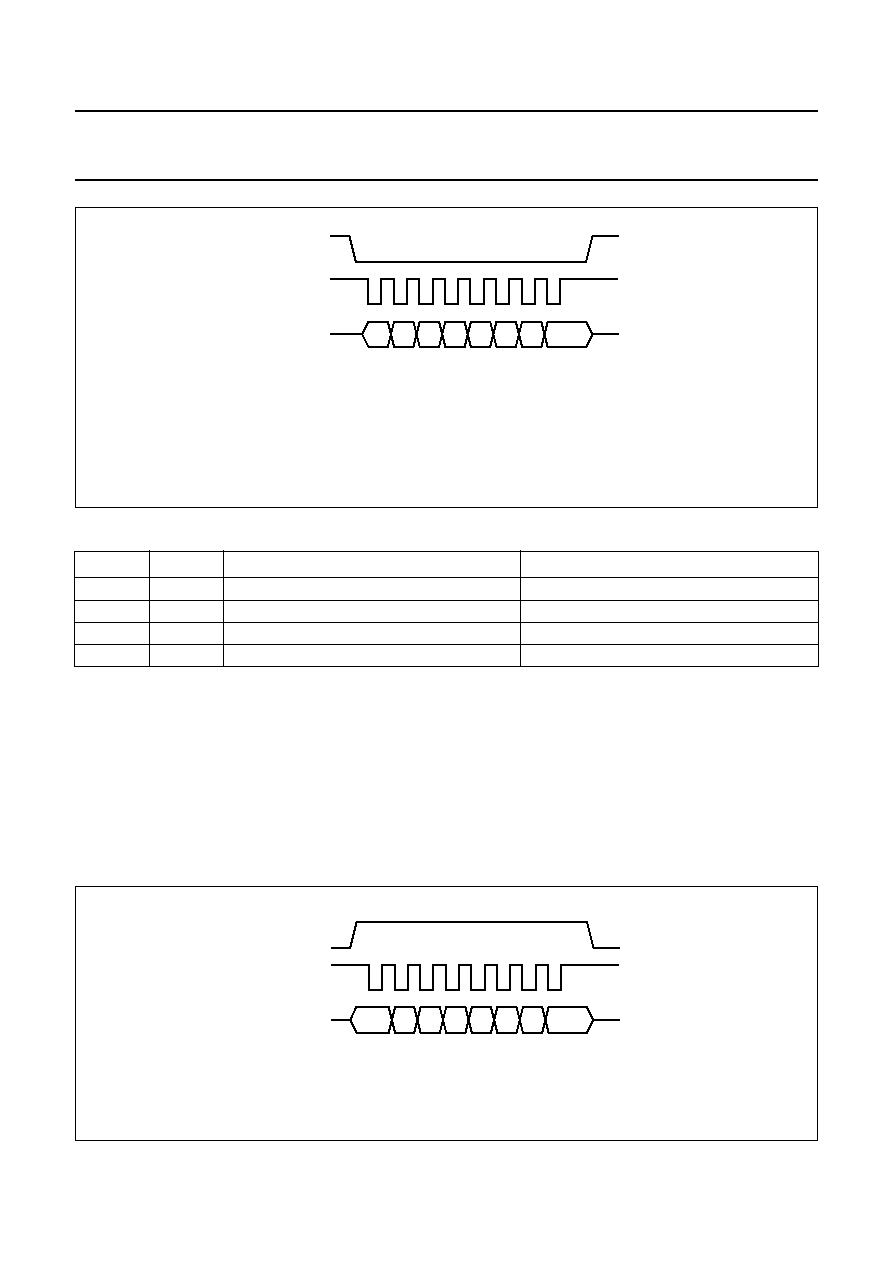

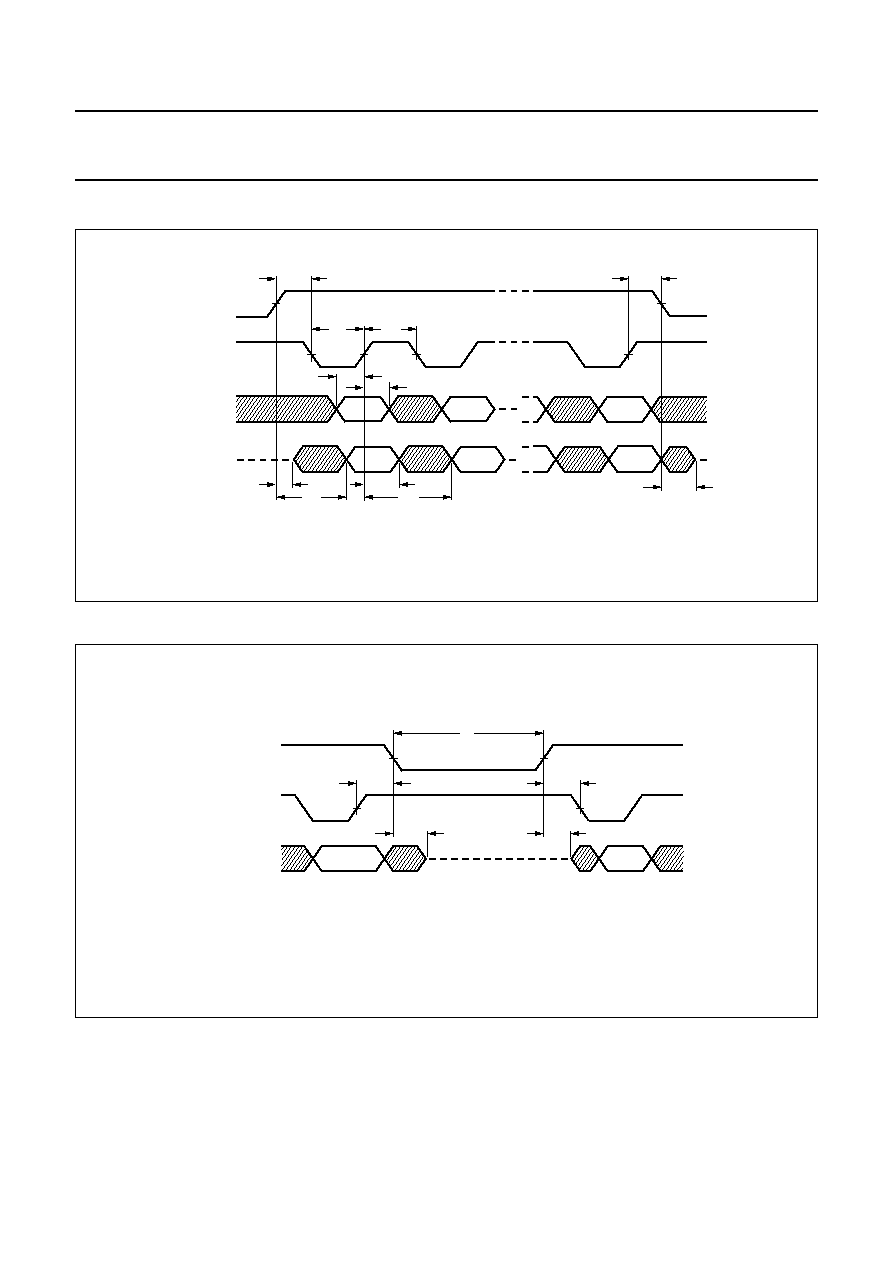

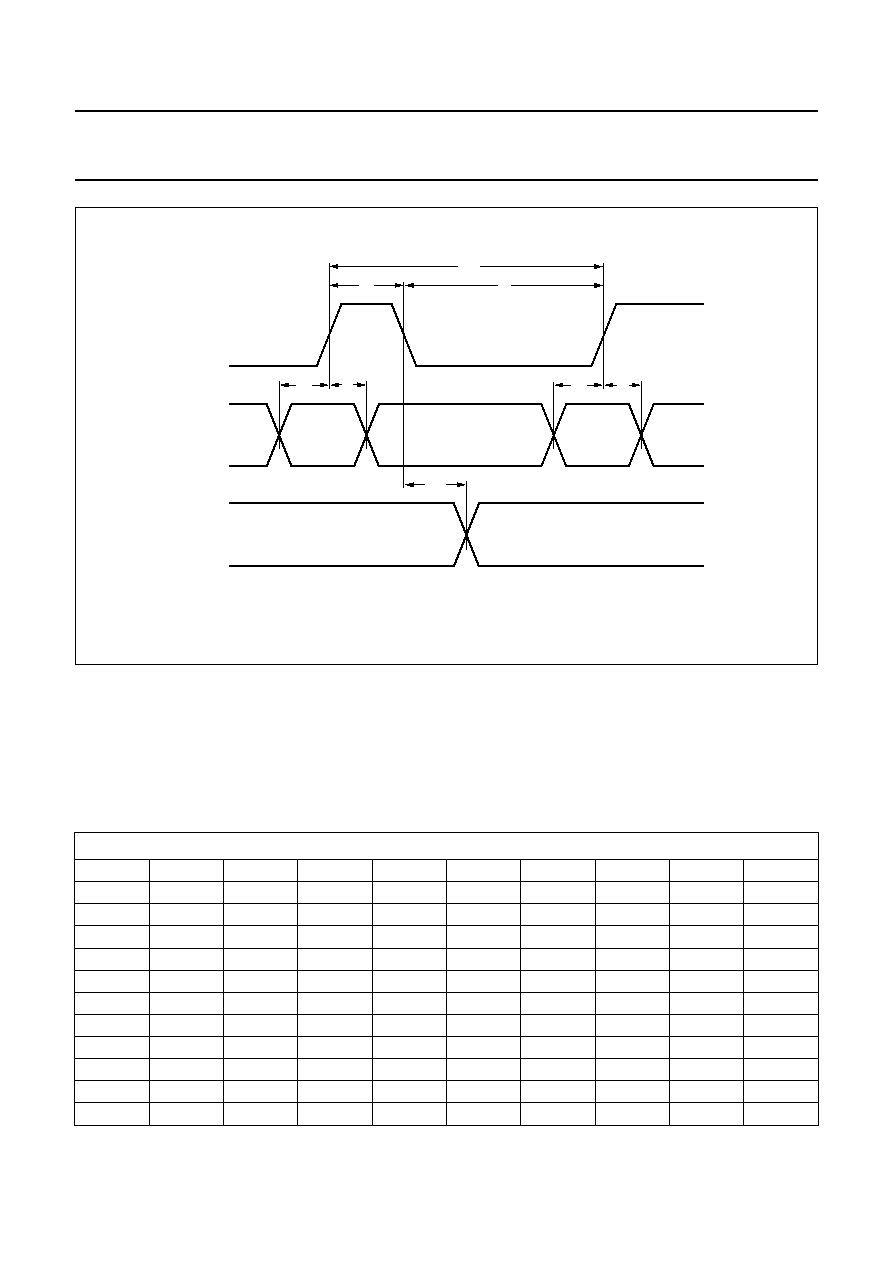

Fig.7 Master mode input data format.

,,

,,

,,

,,

,,,

,,,

,,

,,

,,

,,

,,

,,

handbook, full pagewidth

MGE474

CDCL

CD

CDEF

CDRQ

CDSY

unreliable data bit (example)

start of byte or frame

1

1

2

2

14

valid data

valid but unreliable data

invalid data

15

16

,

1997 Nov 17

13

Philips Semiconductors

Preliminary specification

ISO/MPEG Audio Source Decoder

SAA2502

The bit clock CDCL is input, its frequency is determined by

the application, however certain minimum and maximum

values have to be obeyed.

MPEG free format bit rate is allowed in this mode.

CDVAL = logic 1 indicates valid data. In this way, burst

input data is supported.

The speed at which data may be transferred to the input

interface is restricted. Transfer of an MPEG frame is

illustrated in Fig.9. It shows the transfer of all Nf bits of one

frame between time 0 and Tf, where Tf corresponds to

384 sample periods (MPEG layer I input data) or

1152 sample periods (MPEG layer II input data). In the

figure, an example of an actual transfer characteristic is

drawn. Input data may be transferred at a speed higher

than bit rate (i.e. CDCL may have a frequency higher than

bit rate).

Ideally the data transfer of the first frame is in a single

burst. In practice multiple bursts are allowed, provided that

the data transfer is always within

±

128 CDCL cycles of the

ideal data transfer.

Subsequent frames may also have multiple bursts, but the

data transfer must always be within

±

128 CDCL cycles of

both the first frame data transfer and the ideal single burst

transfer characteristics. All frames must start within the

first four bytes of a data burst.

The transfer characteristic has a slope equal to CDCL

frequency during the bursts (when CDVAL is high) and is

horizontal outside the bursts (when CDVAL is low; no bits

are transferred). The frequency of CDCL has to be

constant (except when CDVAL is low) in normal operation;

any change of CDCL frequency should be followed by a

(soft) reset.

For DAB applications there is an exception to the rule that

data transfer is always within

±

128 CDCL cycles of the

ideal single burst characteristic.

When the sampling frequency is 24 kHz and the CDCL

frequency is 384 kbits/s, it is allowed to send an input

frame in two bursts of equal length. The first bit of a frame

must be the first bit of a burst, while the last bit of a frame

must be the last bit of a burst.

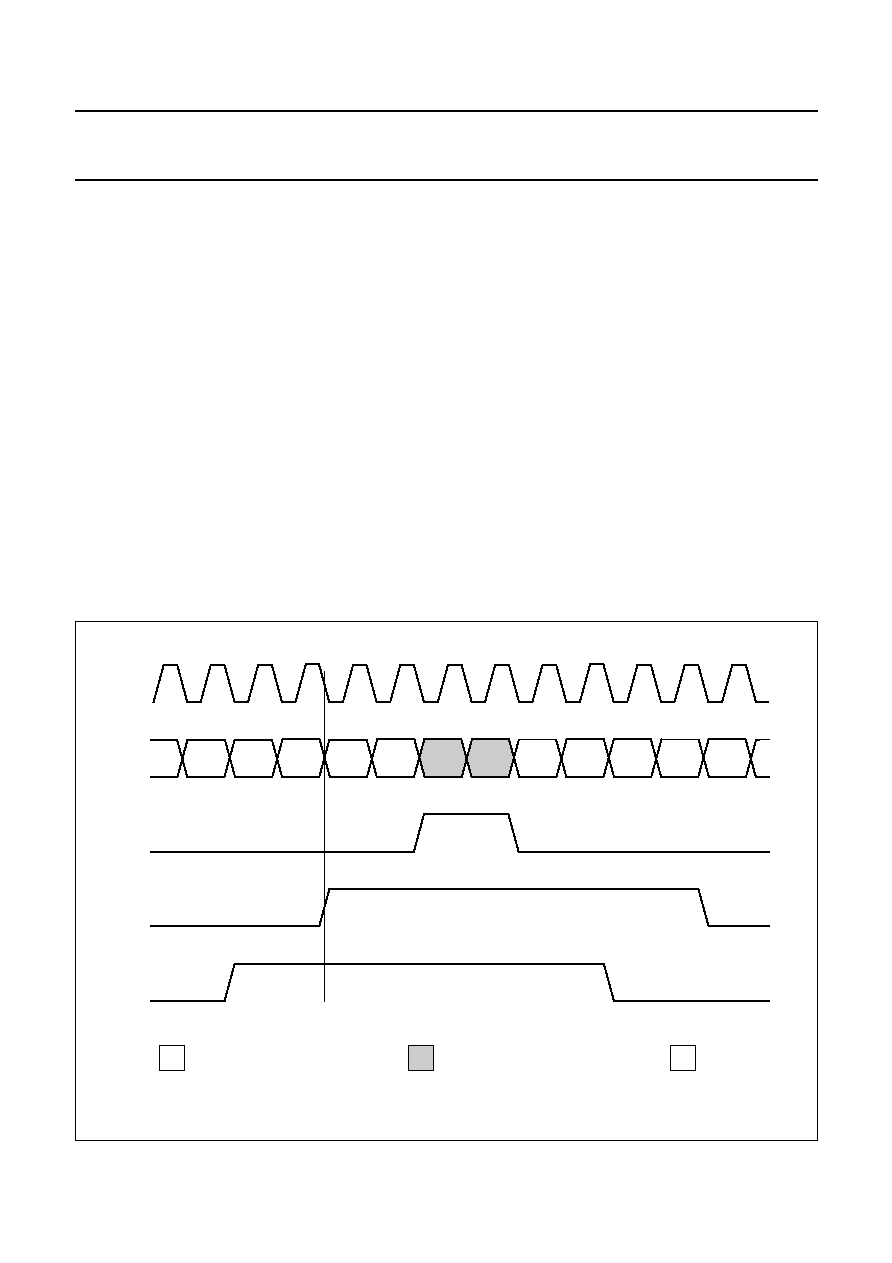

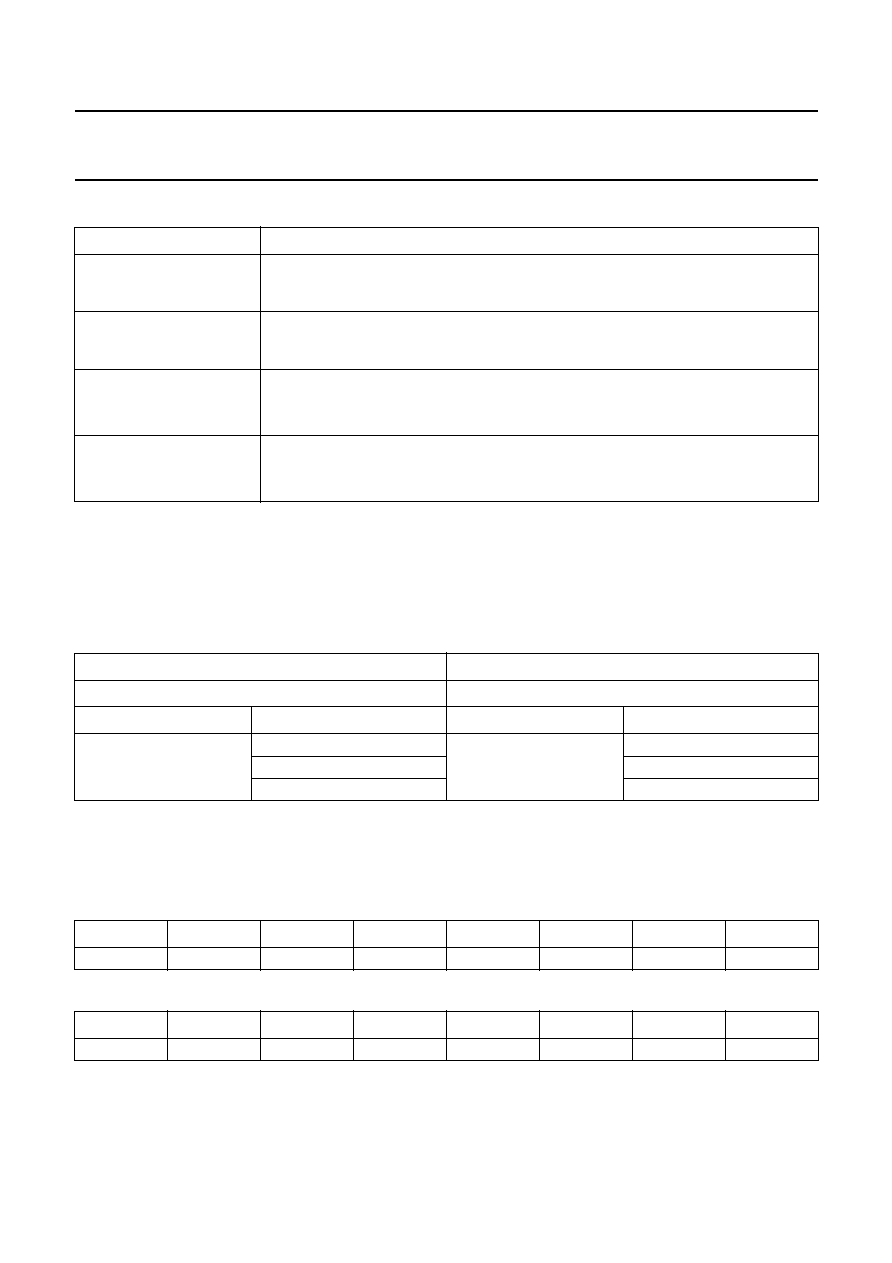

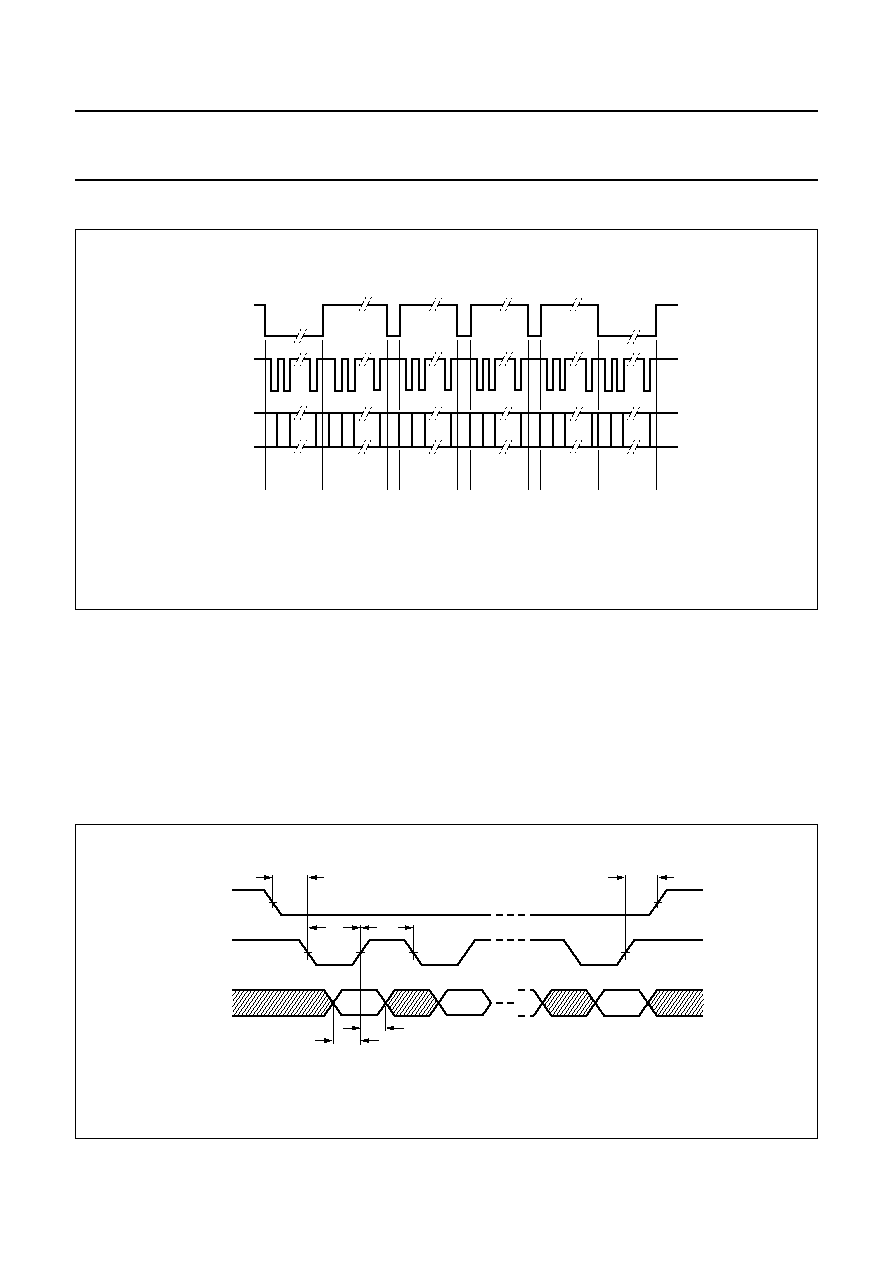

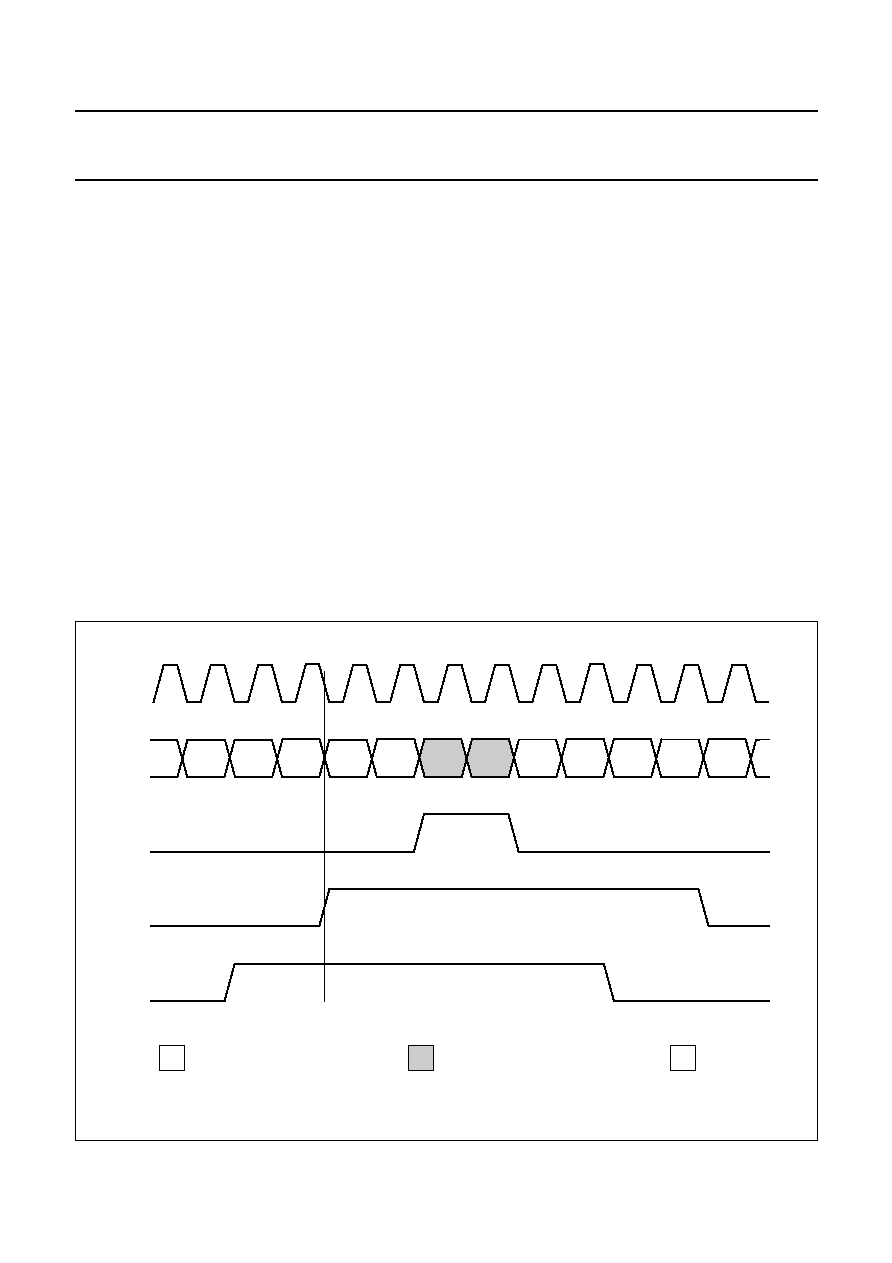

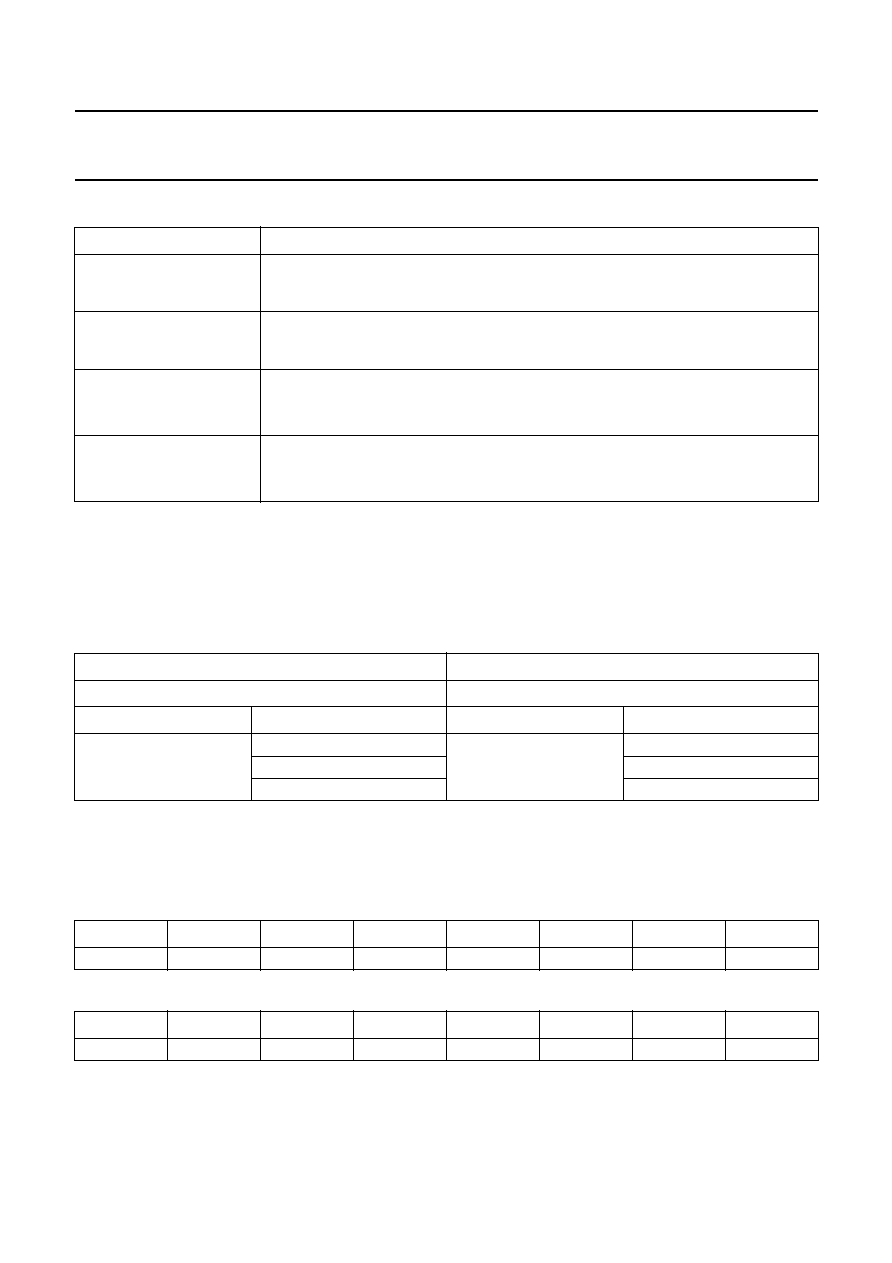

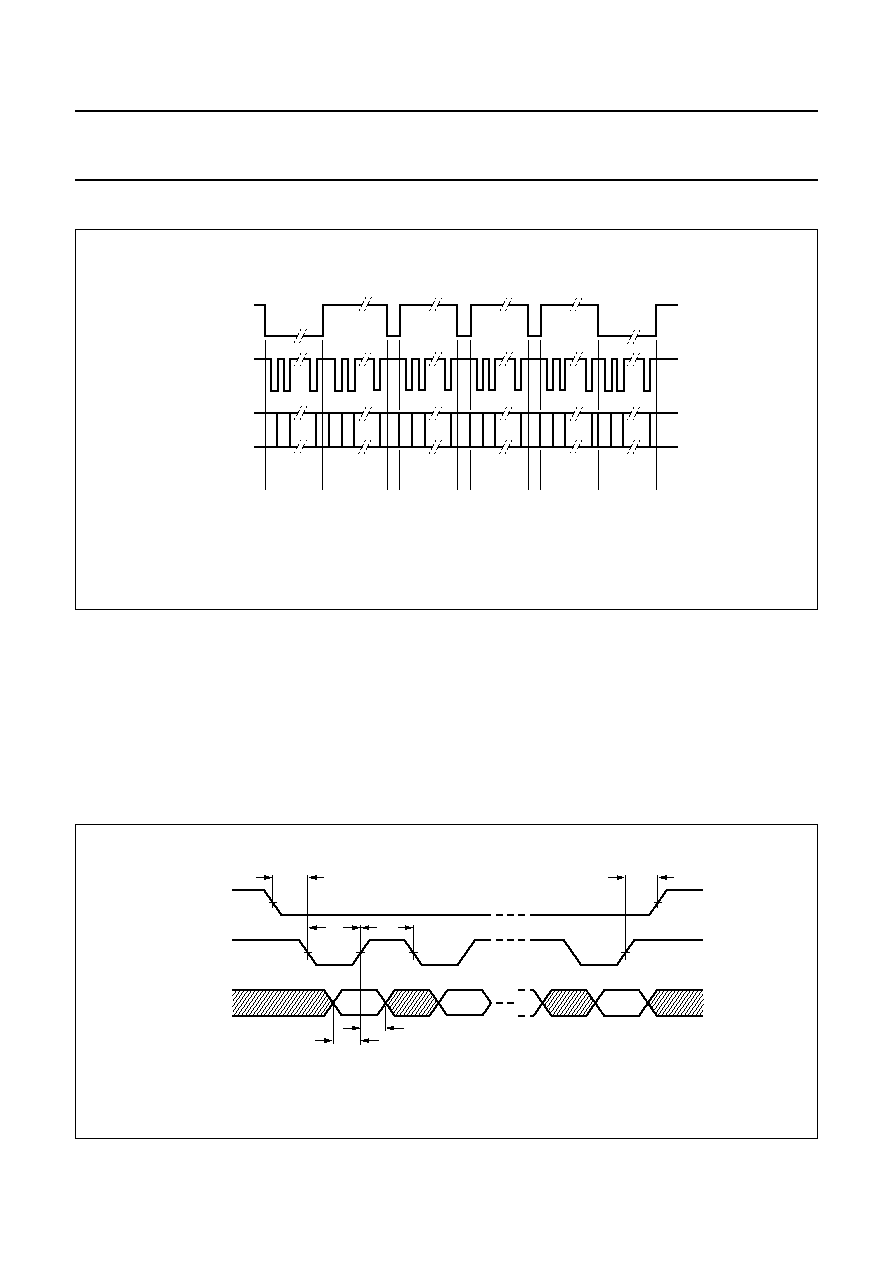

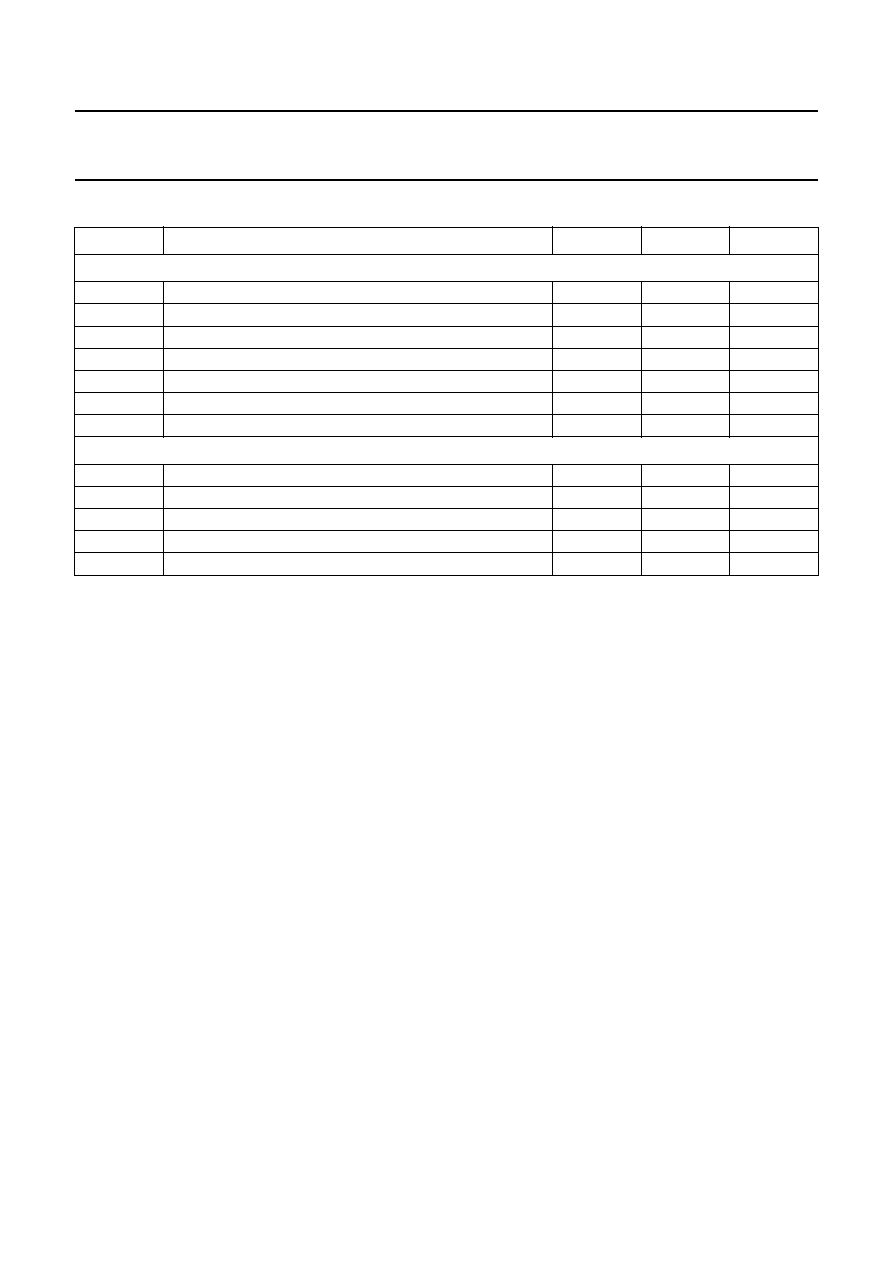

Fig.8 Slave mode input data format.

,,

,,

,,,

,,,

,,

,,

,,,

,,,

,,

,,

,,

,,

handbook, full pagewidth

MGE475

CDCL

CD

CDEF

CDVAL

CDSY

unreliable data bits (example)

start of byte or frame

valid data

valid but unreliable data

invalid data

,,

1997 Nov 17

14

Philips Semiconductors

Preliminary specification

ISO/MPEG Audio Source Decoder

SAA2502

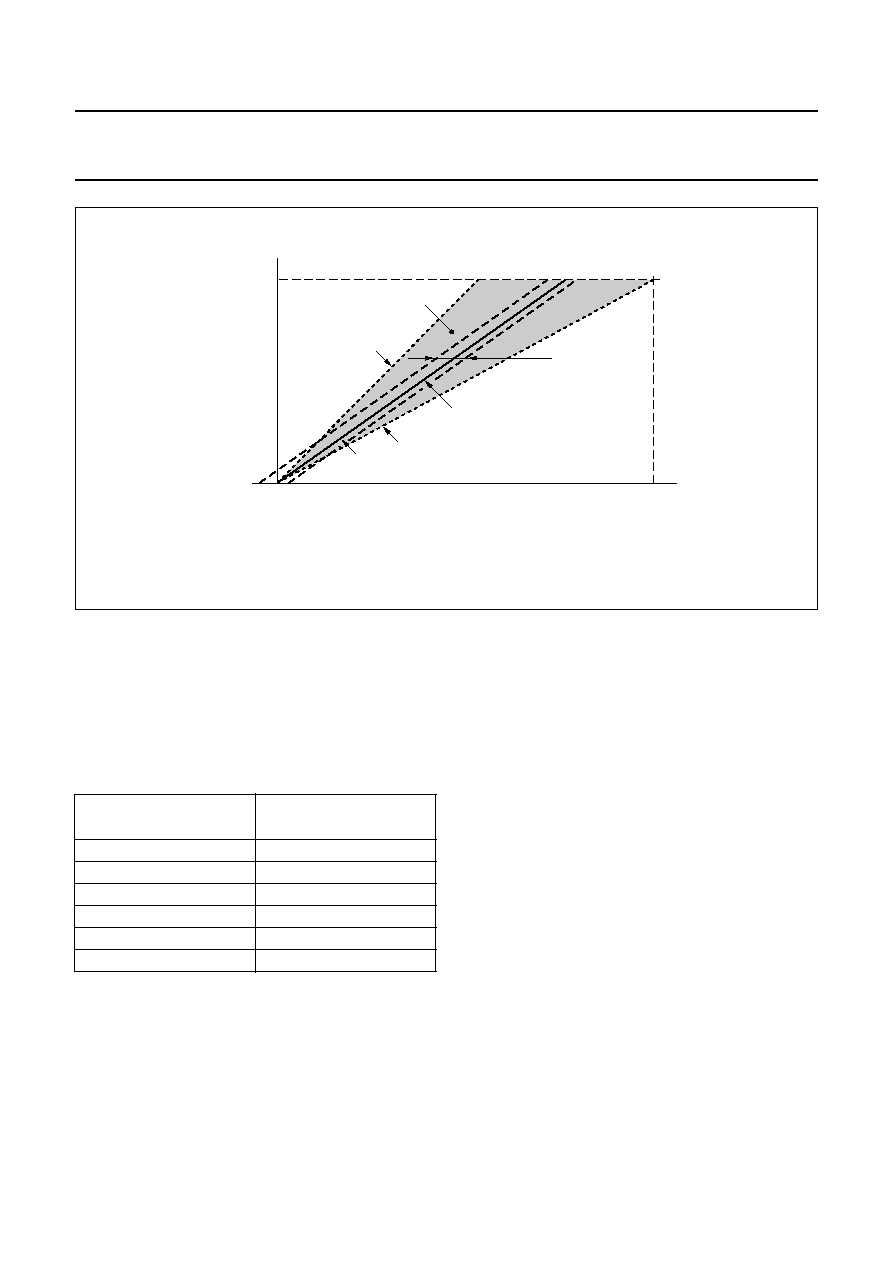

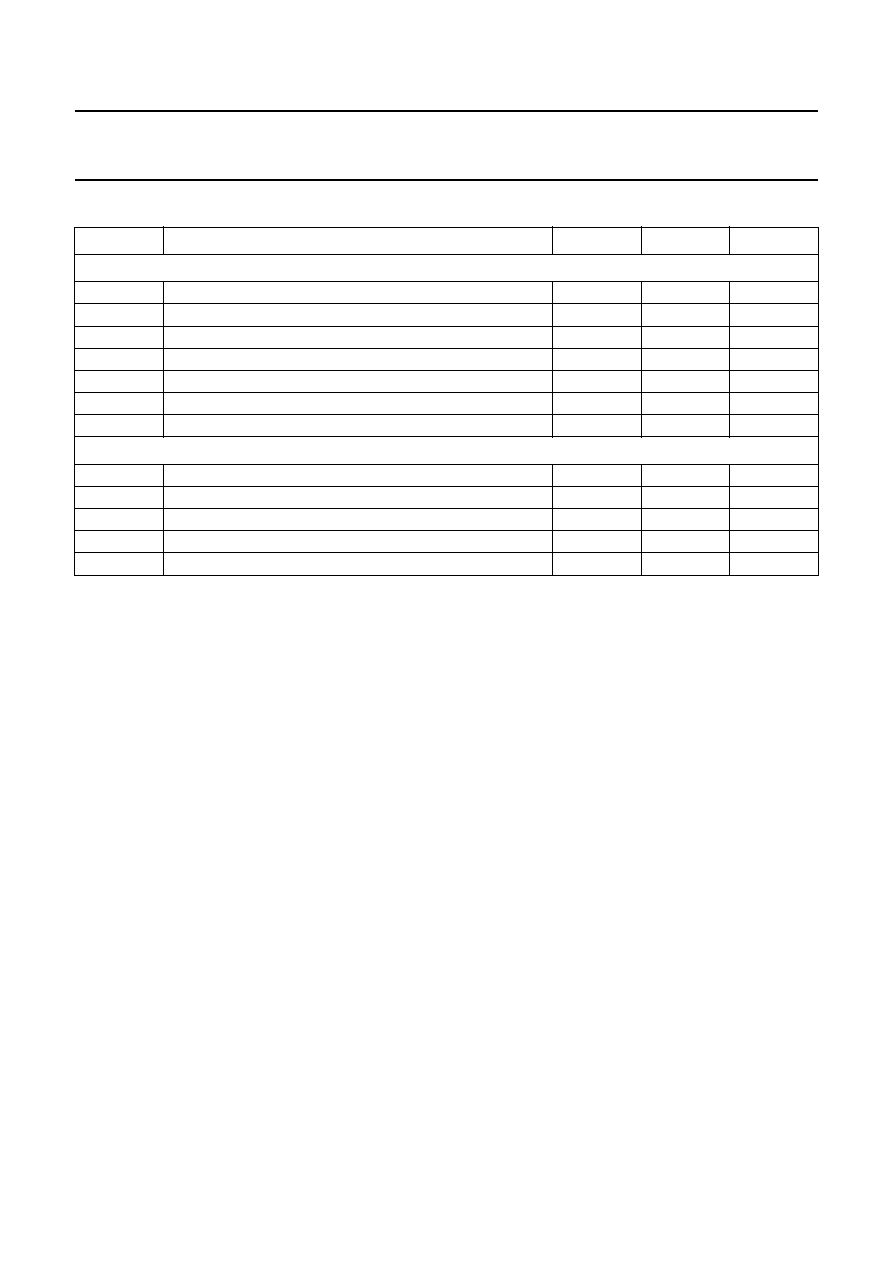

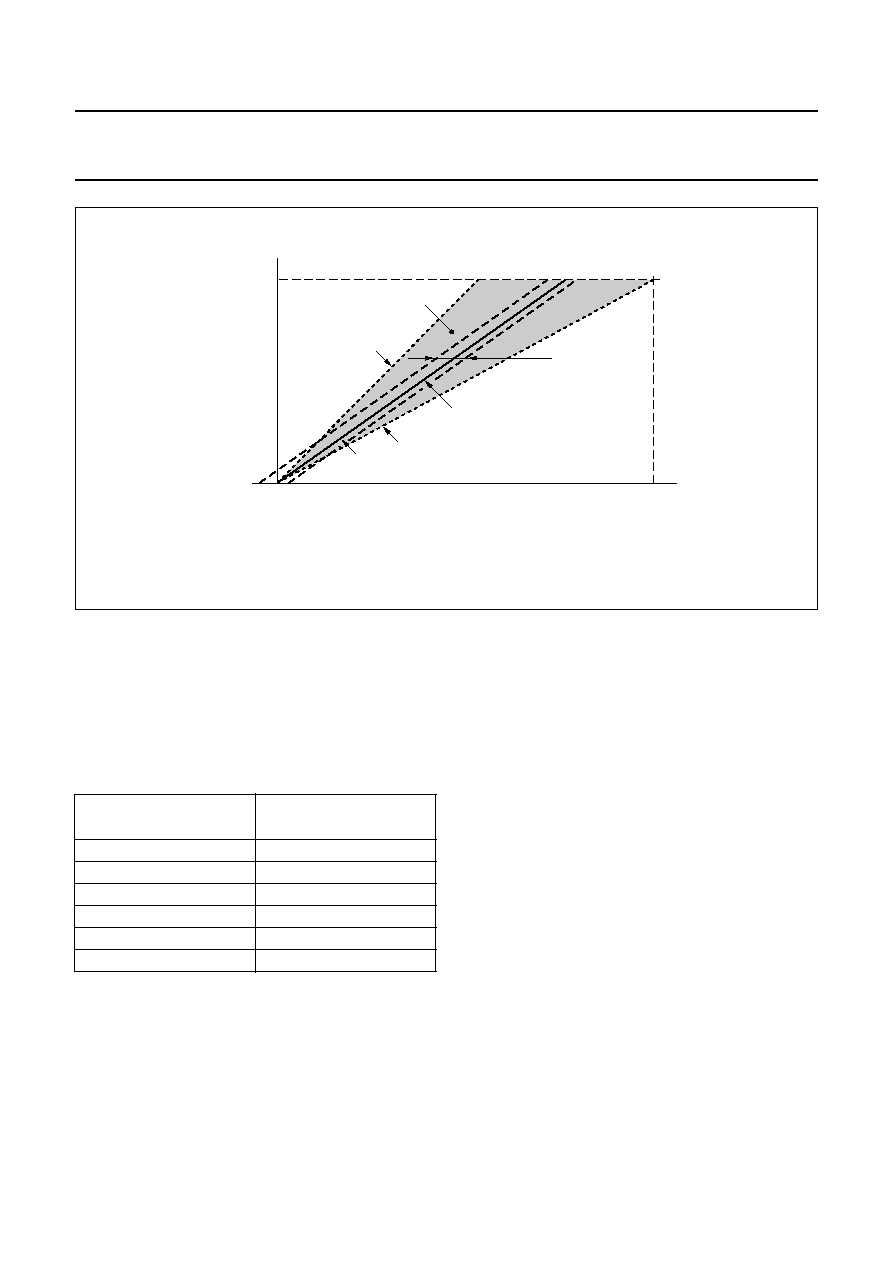

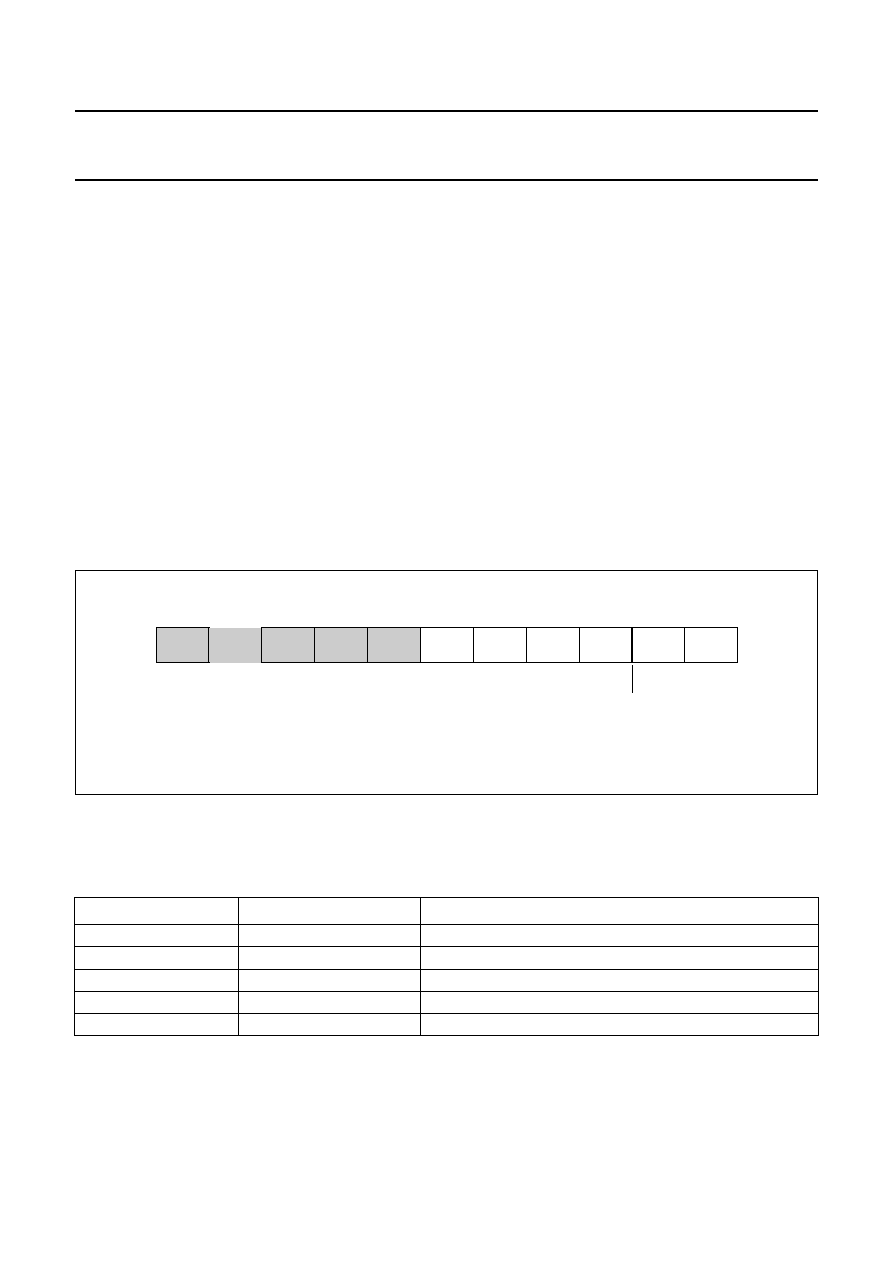

Fig.9 Slave input data transferring speed.

(1) Ideal frame transfer characteristics are restricted to this area.

(2) Ideal frame transfer characteristic (example).

handbook, full pagewidth

MGE476

slope = CDCL frequency

slope = input bit rate

(2)

jitter limits

slope = maximum

CDCL frequency

Nf

transferred

input bits

0

0

time

Tf

(1)

The shaded area in Fig.9 represents the restrictions to the

transfer characteristic of a frame. The characteristic may

not cross the shown upper limit of the shaded area in order

to prevent input buffer underflow and/or overflow.

The slope of the upper limit is determined by the sample

frequency as shown in Table 5.

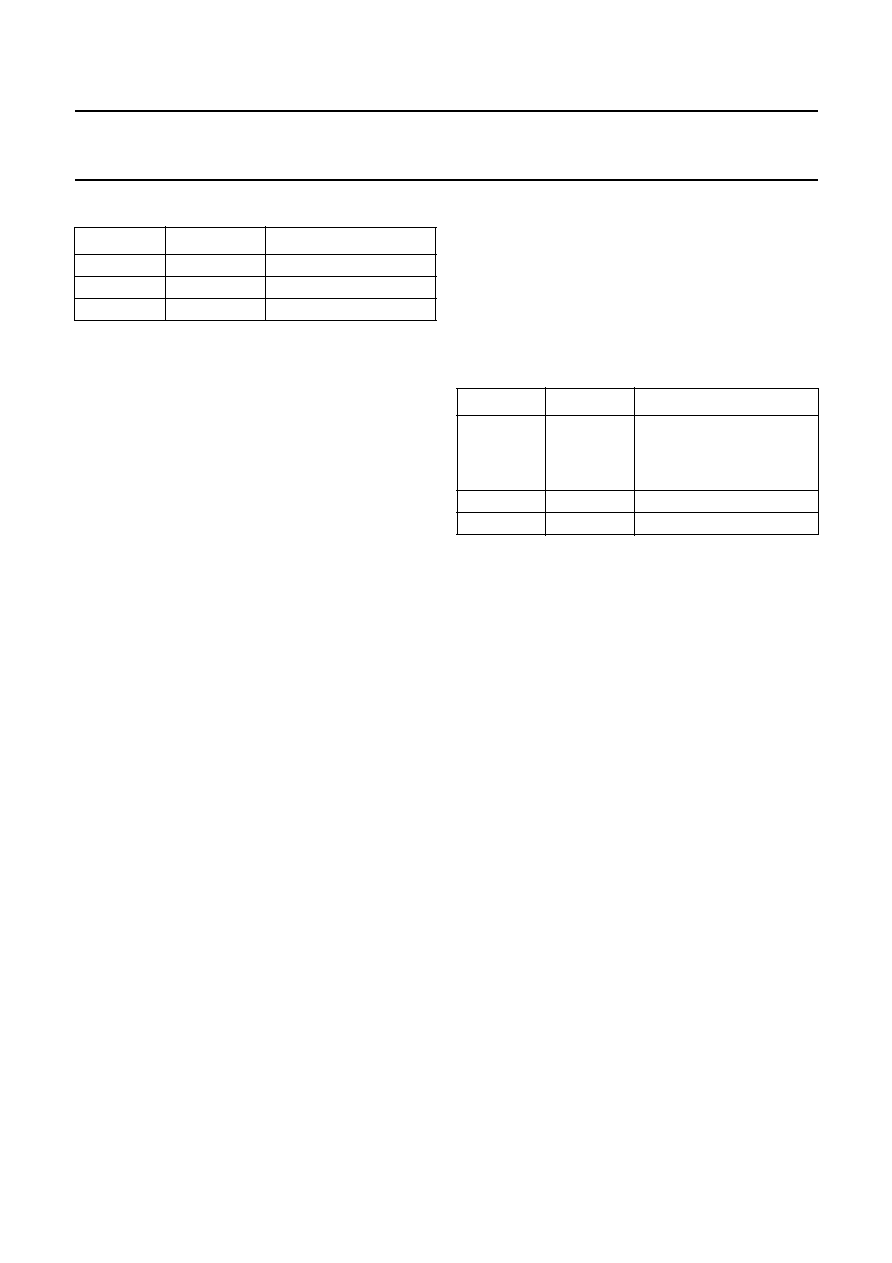

Table 5

Slope of the upper limit determined by sampling

frequency

SAMPLE FREQUENCY

(kHz)

MAXIMUM CDCL

FREQUENCY (kbits/s)

48

768

44.1

705.6

32

512

24

384

22.05

352.8

16

256

1997 Nov 17

15

Philips Semiconductors

Preliminary specification

ISO/MPEG Audio Source Decoder

SAA2502

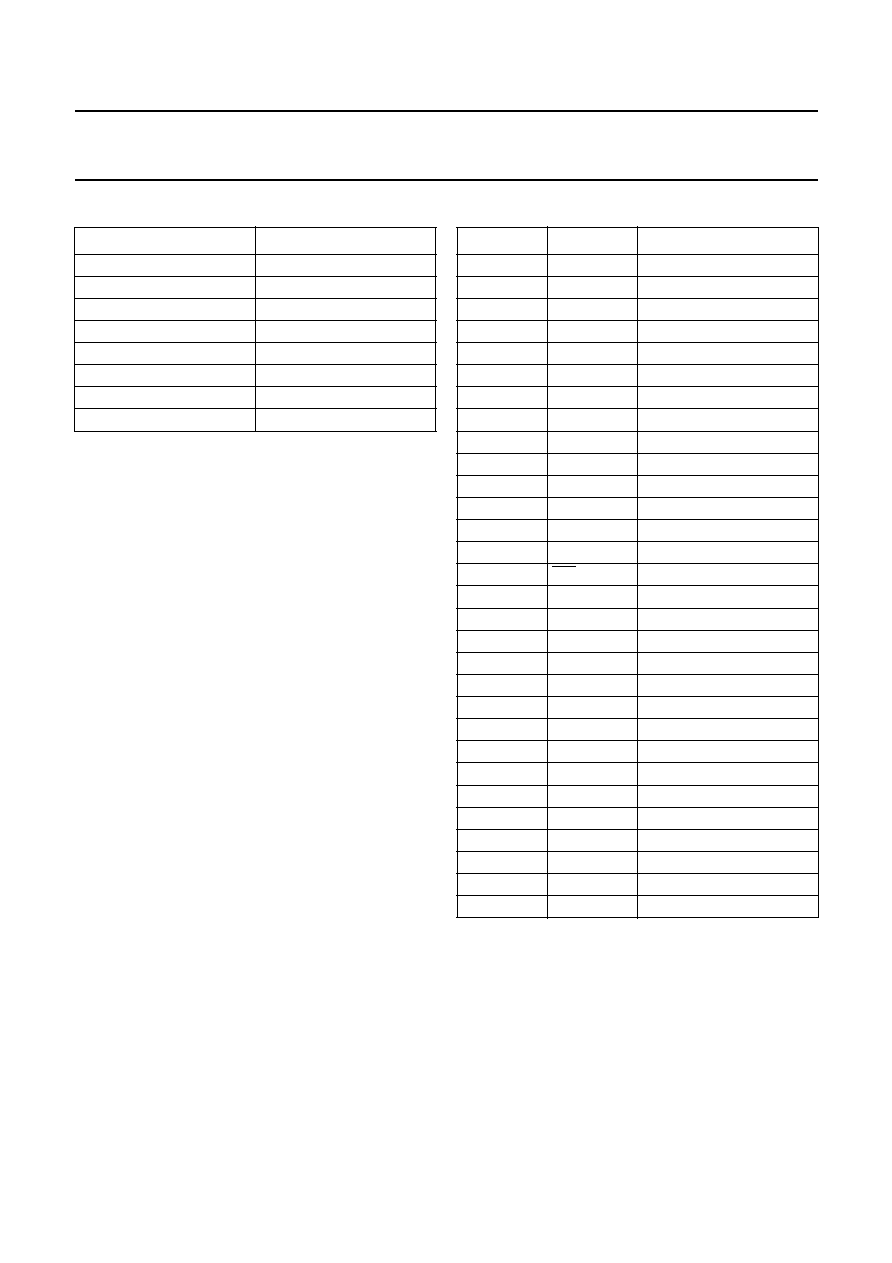

7.3.3

B

UFFER CONTROLLED INPUT MODE

(see Fig.10)

Buffer controlled input mode is activated by setting the

INMOD control flags to 1X, which means that the SAA2502

will request data based on the amount of input bytes

currently residing in the input buffer.

The bit clock CDCL is output, its frequency is fixed:

when MCLK24 = logic 1

when MCLK24 = logic 0.

In this mode CDRQ = logic 1 is an indication that new input

data is required. CDVAL = logic 1 indicates the delivery of

valid data. The application should react to the event of an

input data request as follows:

∑

One byte of input data should be delivered within

16 CDCL cycles. If CDRQ remains high the next byte

MCLK

32

------------------

MCLK

16

------------------

should be delivered and so on until CDRQ is dropped.

Delivery of subsequent bytes while CDRQ remains

HIGH should be uninterrupted (CDVAL should stay

HIGH)

∑

There is also an option for the application to deliver part

of the input data later. Despite violating the conditions in

the previous paragraph, this is allowed, but with

consequences for the input buffer latency time.

MPEG free format bit rate is allowed in this mode.

Dynamically varying bit rate may be supported in this

mode. Whether such support is desired or not is indicated

by the following input mode bits:

∑

INPMOD = 10 means bit rate is assumed to be (quasi)

static

∑

INPMOD = 11 means bit rate is assumed to be dynamic.

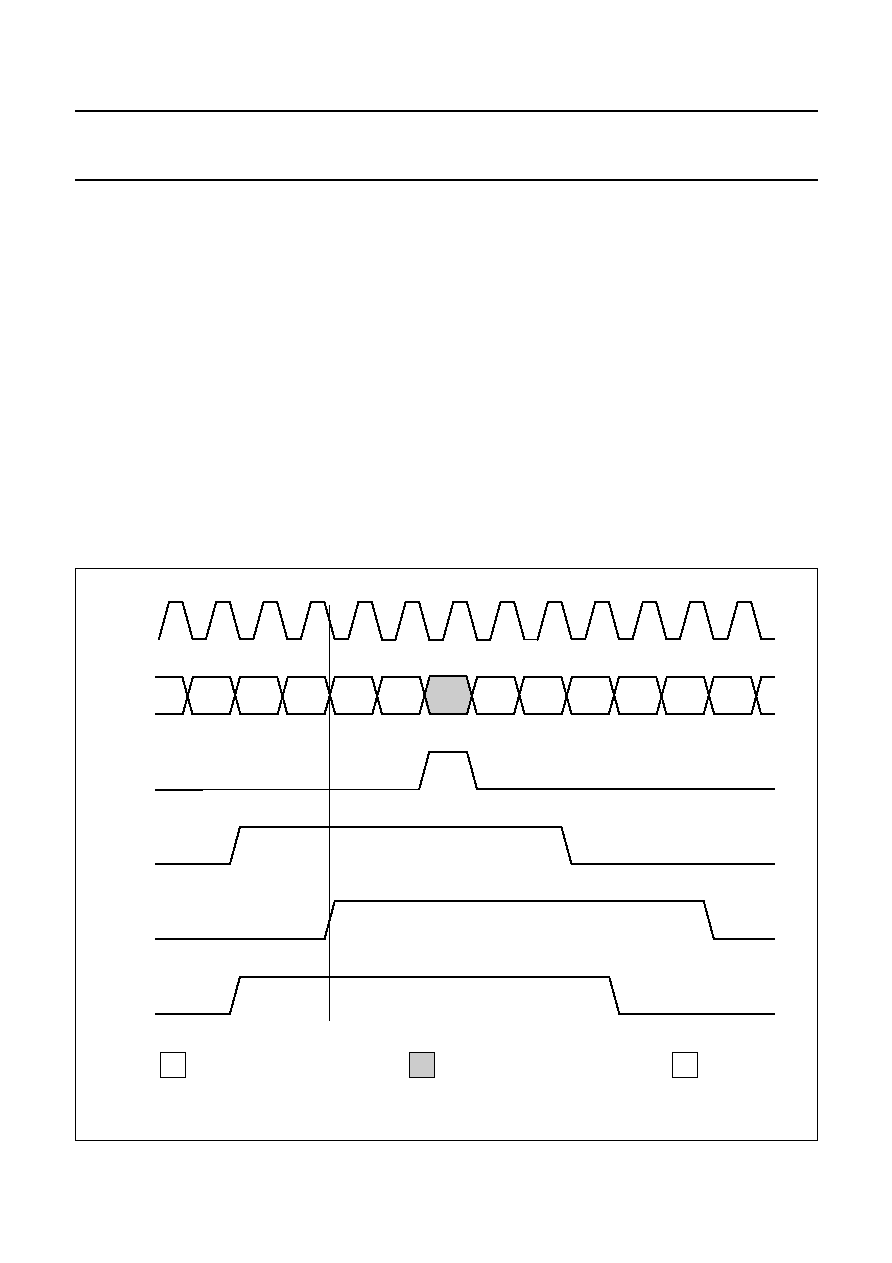

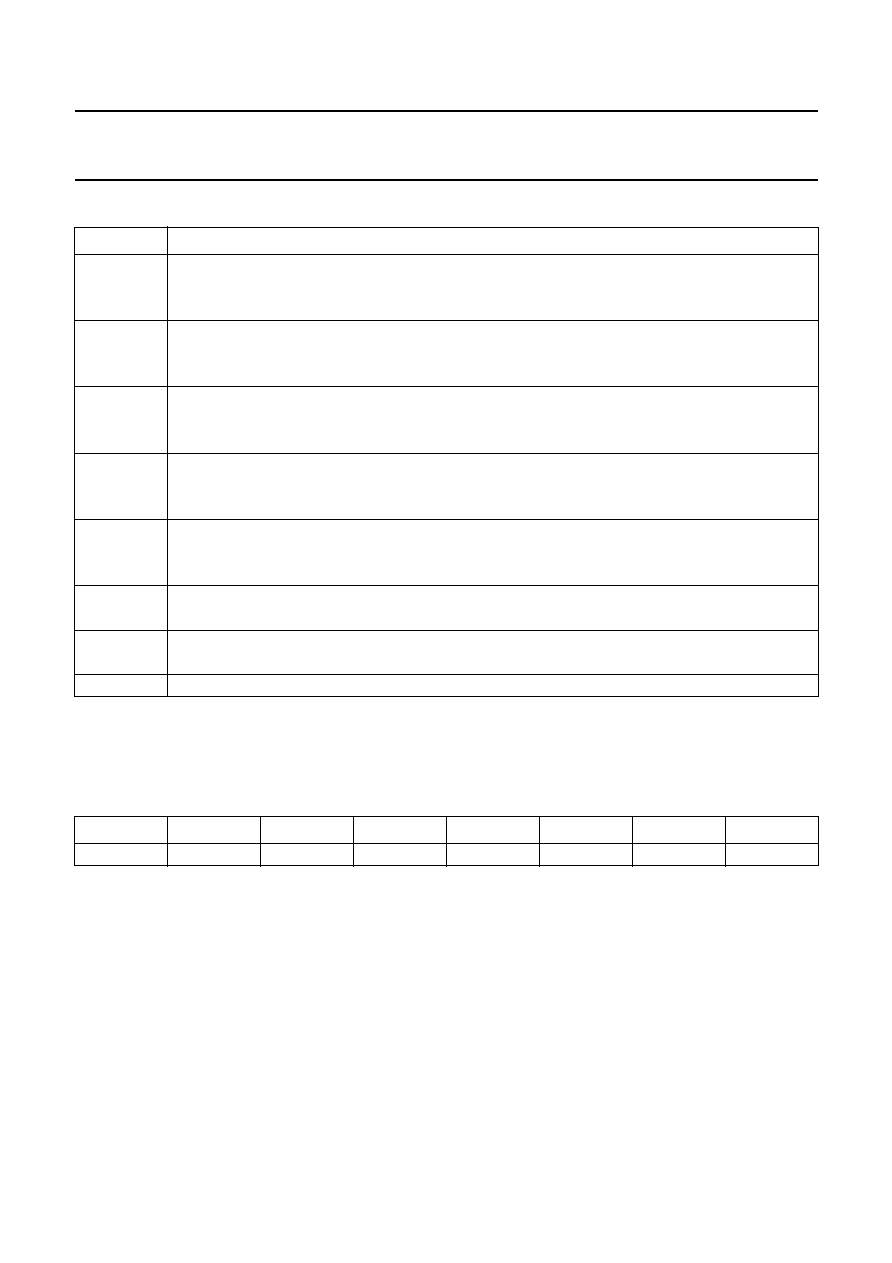

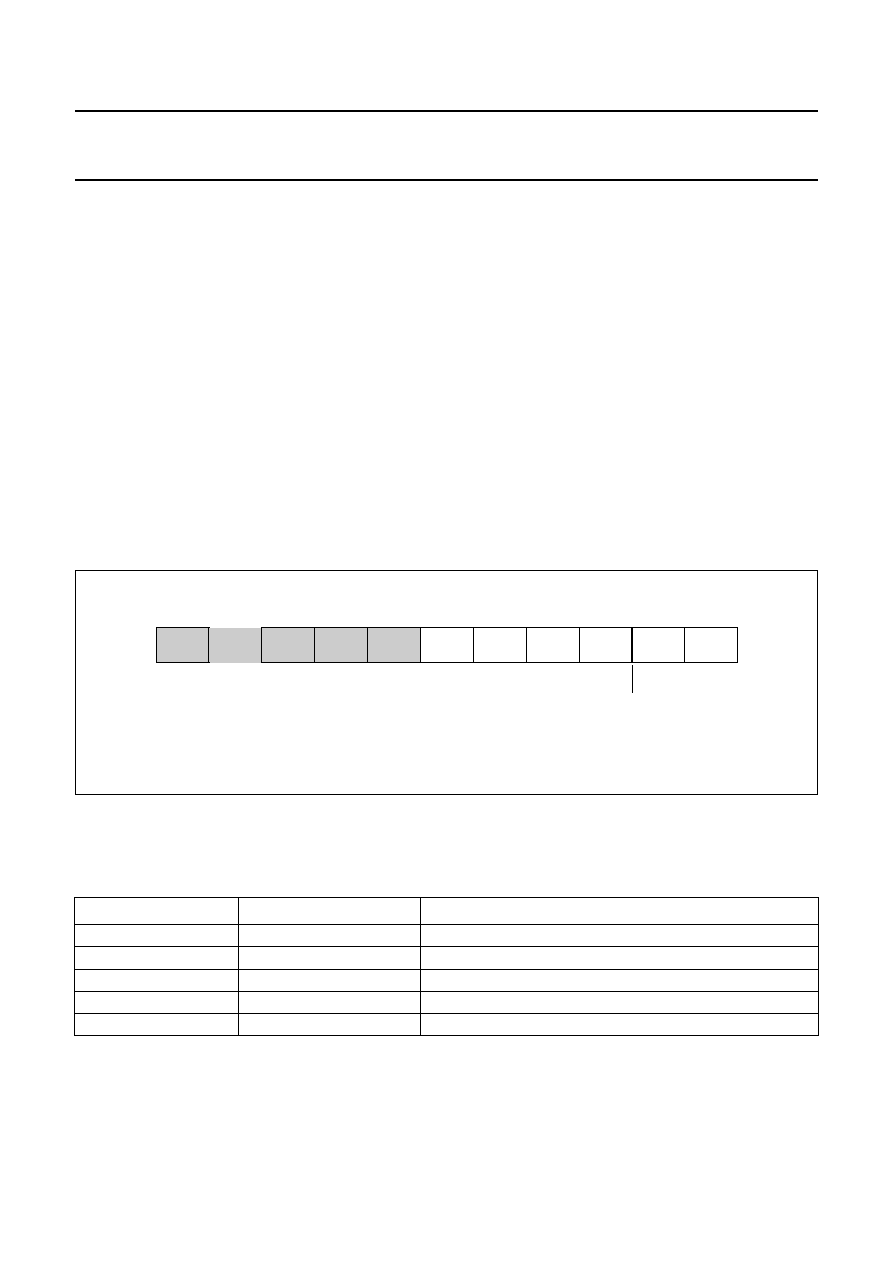

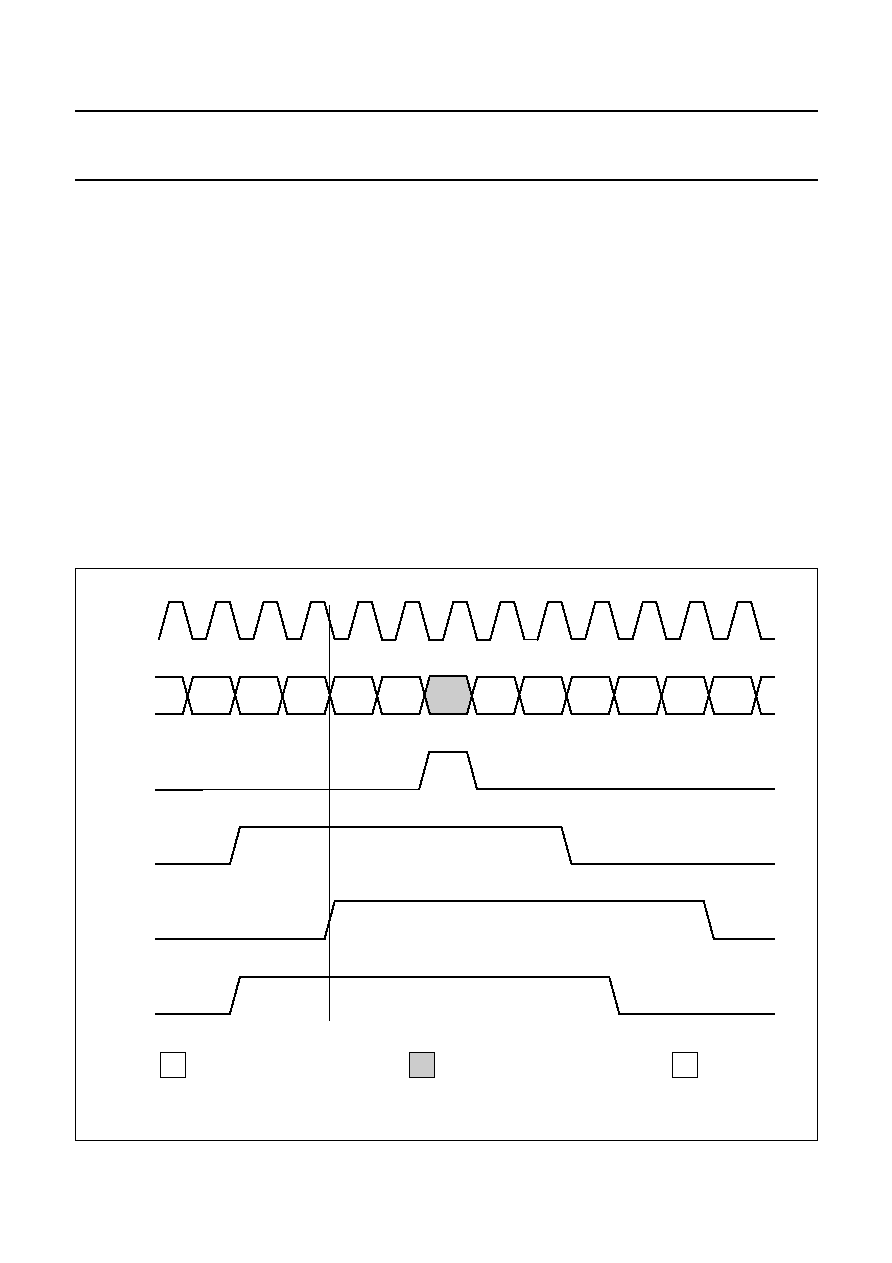

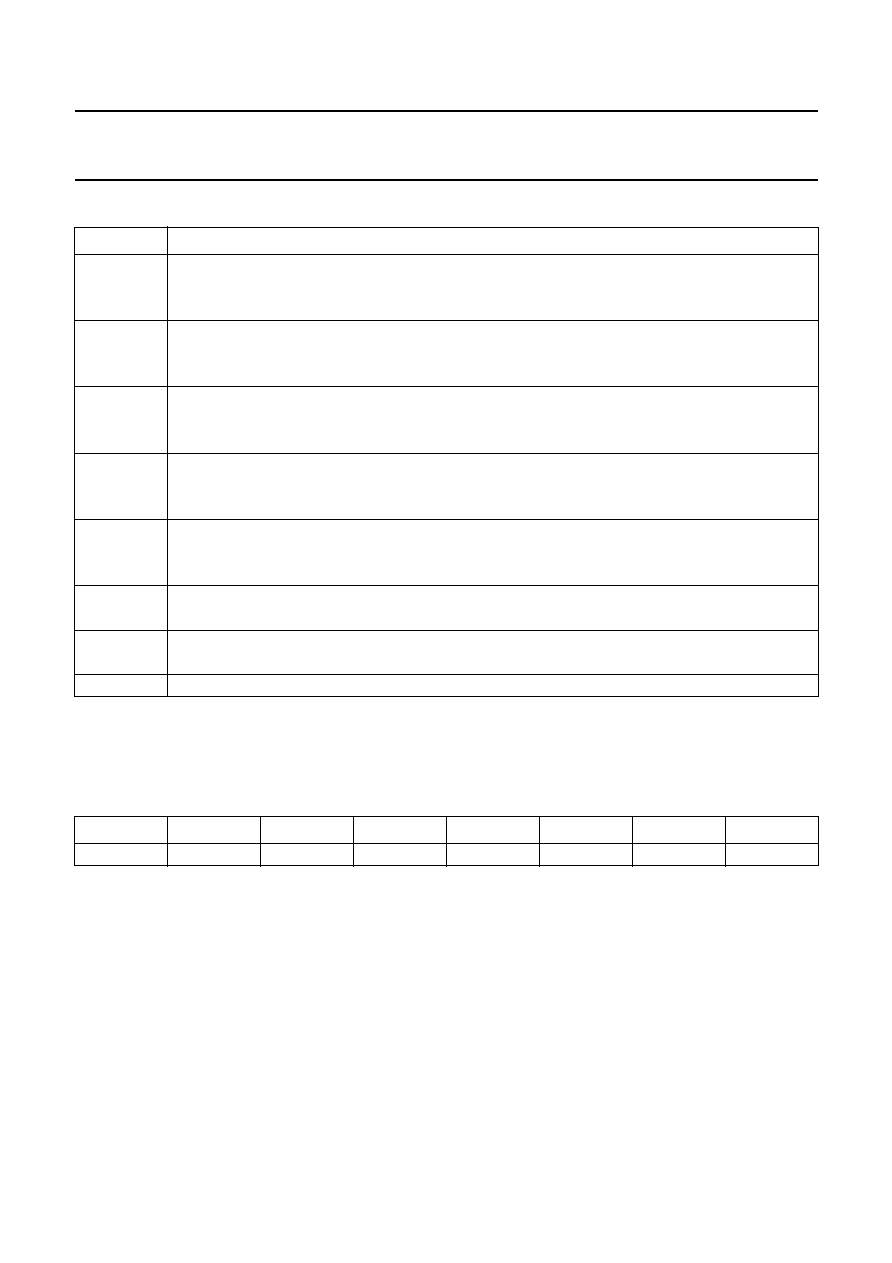

Fig.10 Buffer controlled mode input data format.

,,,

,,,

,,

,,

,,

,,

,,

,,

,,

,,

,,

,,

handbook, full pagewidth

MGE477

CDCL

CD

CDEF

CDRQ

CDVAL

CDSY

unreliable data bit (example)

start of byte or frame

valid data

valid but unreliable data

invalid data

,,

,,

1997 Nov 17

16

Philips Semiconductors

Preliminary specification

ISO/MPEG Audio Source Decoder

SAA2502

7.4

Decoder core

The SAA2502 fully complies with MPEG1 (layer I and II)

and MPEG2 (layer I and II, L

0

and R

0

channels). Also

some DAB specific features are supported. Free format bit

rate is not supported in master input mode. Several

aspects of the decoding process and audio

post-processing features are offered.

7.4.1

F

RAME SYNCHRONIZATION TO INPUT DATA STREAMS

The SAA2502 has to localize the start of a frame before

decoding may begin. The process of locating the start of a

frame is called frame synchronization. There are

4 different modes of frame synchronization available.

These modes are in order of decreasing speed of frame

synchronization.

7.4.1.1

Frame sync pulse mode

In this mode the start of each frame is marked by a rising

edge of the CDSY input pin. It is the fastest and most

reliable method of frame synchronization. It is activated by

loading 11 into the SYMOD control flags.

7.4.1.2

Byte aligned mode

This default mode may also be enforced by loading 10 into

the SYMOD control flags. The start of a frame is located by

detection of the 14-bit sync pattern 111111111111X1.

The probability of correct sync detection is enhanced by

the fact that a rising edge of the CDSY input pin marks a

location which is byte aligned with frame bounds. A rising

edge of CDSY is not required at every byte edge but

should occur at regular intervals for reliable frame

synchronization.

7.4.1.3

Layer II non-byte aligned mode

This mode may be entered by loading 01 into the SYMOD

control flags. Frame start is found by detection of the 15-bit

sync pattern 111111111111X10.

As this pattern is slightly longer than the previous one and

also contains at least one 1-to-0 transition, it may be used

to obtain frame synchronization in the absence of any

external alignment indication (CDSY is ignored and

therefore may be left floating).

7.4.1.4

General non-byte aligned mode

This mode may be entered by loading 00 into the SYMOD

control flags. Frame start is detected by alternating

searches for a 15-bit sync pattern 111111111111X10

(identical to the layer II mode search pattern) and a15-bit

sync pattern 0111111111111X1.

Because valid MPEG streams exist that do not contain the

first pattern while other valid MPEG streams do not contain

the second pattern a time-out counter will always be active

in this mode. Time-out length is set to slightly more then

72 ms which is the length of the longest audio frame.

The second pattern operates for layer I and layer II, but

successful synchronization is only guaranteed when the

last bit of the previous frame equals logic 0. Consequently

this mode synchronizes to layer I input bit streams only if

frames at least sometimes end with a logic 0 bit. Both

patterns contain the 1-to-0 or 0-to-1 transition required for

a reliable start-of-frame detection in the absence of

external alignment information.

If the SAA2502 starts at a random place in the bit stream,

it may take up to one frame before a sync pattern or sync

pulse is encountered. Because sync patterns may be

emulated by frame content, detection of a sync is always

followed by a verification period to check whether the sync

is located at the start of a frame. The length of the

verification period depends on the presence of CRC

protection and/or a free format bit rate index. During sync

search and verification the baseband audio outputs are

muted. If verification fails the synchronization process is

restarted.

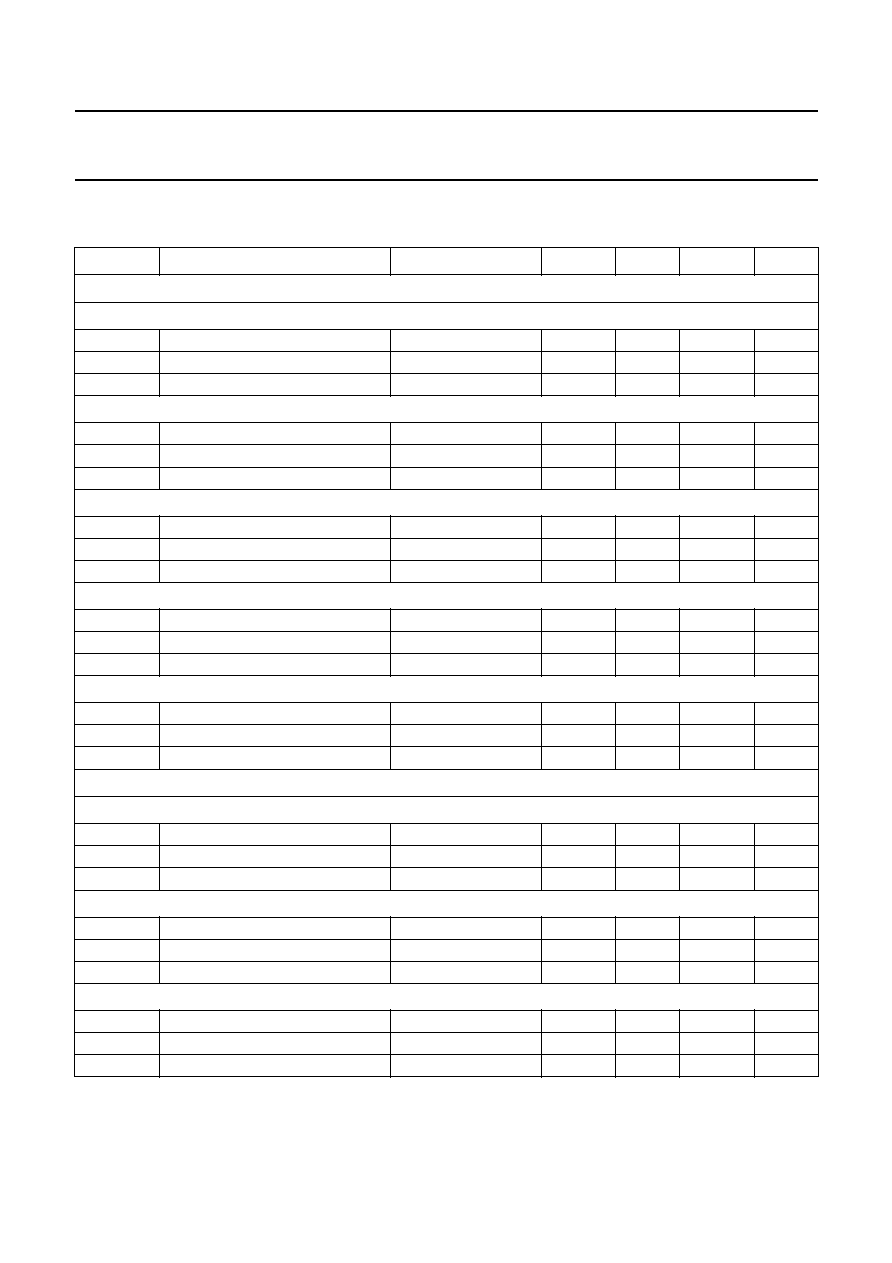

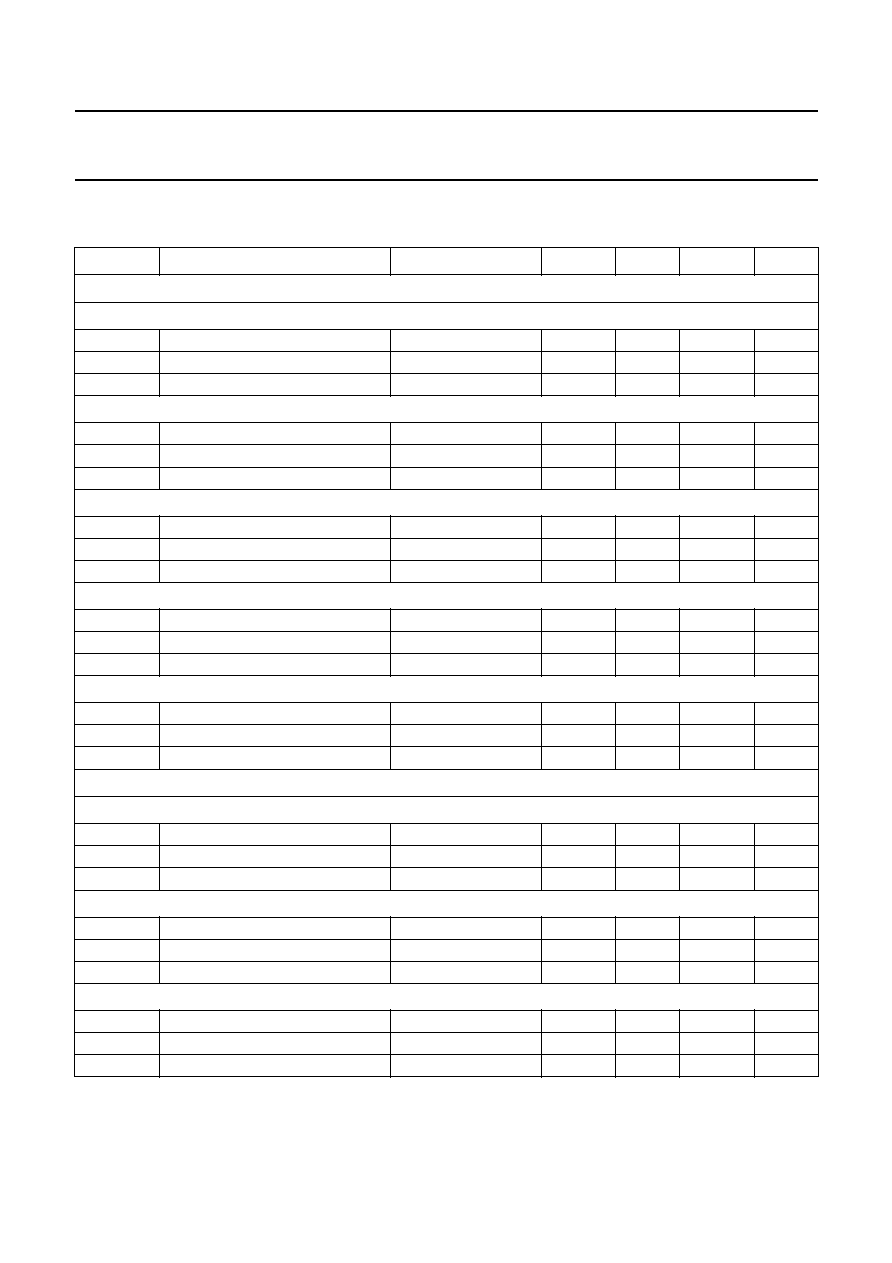

Table 6

Frame sync verification

INPUT DATA FORMAT

LENGTH OF VERIFICATION PERIOD

FREE FORMAT BIT RATE

NON-FREE FORMAT BIT RATE

MPEG; no CRC

2 frame bit rate

1 frame

MPEG with CRC

1 frame

0 frame

1997 Nov 17

17

Philips Semiconductors

Preliminary specification

ISO/MPEG Audio Source Decoder

SAA2502

7.4.2

M

ASTER INPUT MODE BIT RATE GENERATION

When master input mode is used, the SAA2502 fetches

input data at the effective bit rate. However after a hard

reset the input requests input data at the default bit rate

until synchronization has been established as shown in

Table 7.

When the clock generator mode is `free running internal

sample clock' or `locked internal sample clock' the default

input bit rate is always 384 kbits/s. When the mode is

`external sample clock' the SAA2502 derives the selected

bit rate from the signal FSCLKIN. But initially it has no

indication of the current sampling rate corresponding to

FSCLKIN. Therefore the bit rate of 384 kbits/s is

generated at an assumed sampling frequency of 44.1 kHz.

For different sample rates, the bit rate changes

proportionally.

The consequence is that while the SAA2502 is

synchronizing after a hard reset, the application should be

able to supply input data at the given default bit rate until

synchronization is established. Alternatively there is also

the possibility to overrule default bit rate setting and

sample rate setting using the control interface while

synchronization has not been established.

The speed at which input data is requested by the input in

master mode is changed in one of the following events:

∑

When input synchronization is established at the end of

the verification phase and the bit rate index of the

decoded bit stream indicates a bit rate different from the

one currently selected. In this event, the bit rate is

adapted to the new index.

∑

When the signal STOP is raised while the STOPRQ

control flag = logic 1, input requesting is halted.

Requesting resumes at the last selected input bit rate

when the STOP signal is dropped.

In all other events (including when the SAA2502 loses

synchronization), the last selected input bit rate is

maintained.

Whenever the selected bit rate changes while dynamic bit

rate is not enabled, the SAA2502 will generate internally a

soft reset resulting in a soft mute of the output interfaces

and a decoder restart in order to re-initialize internal buffer

settings.

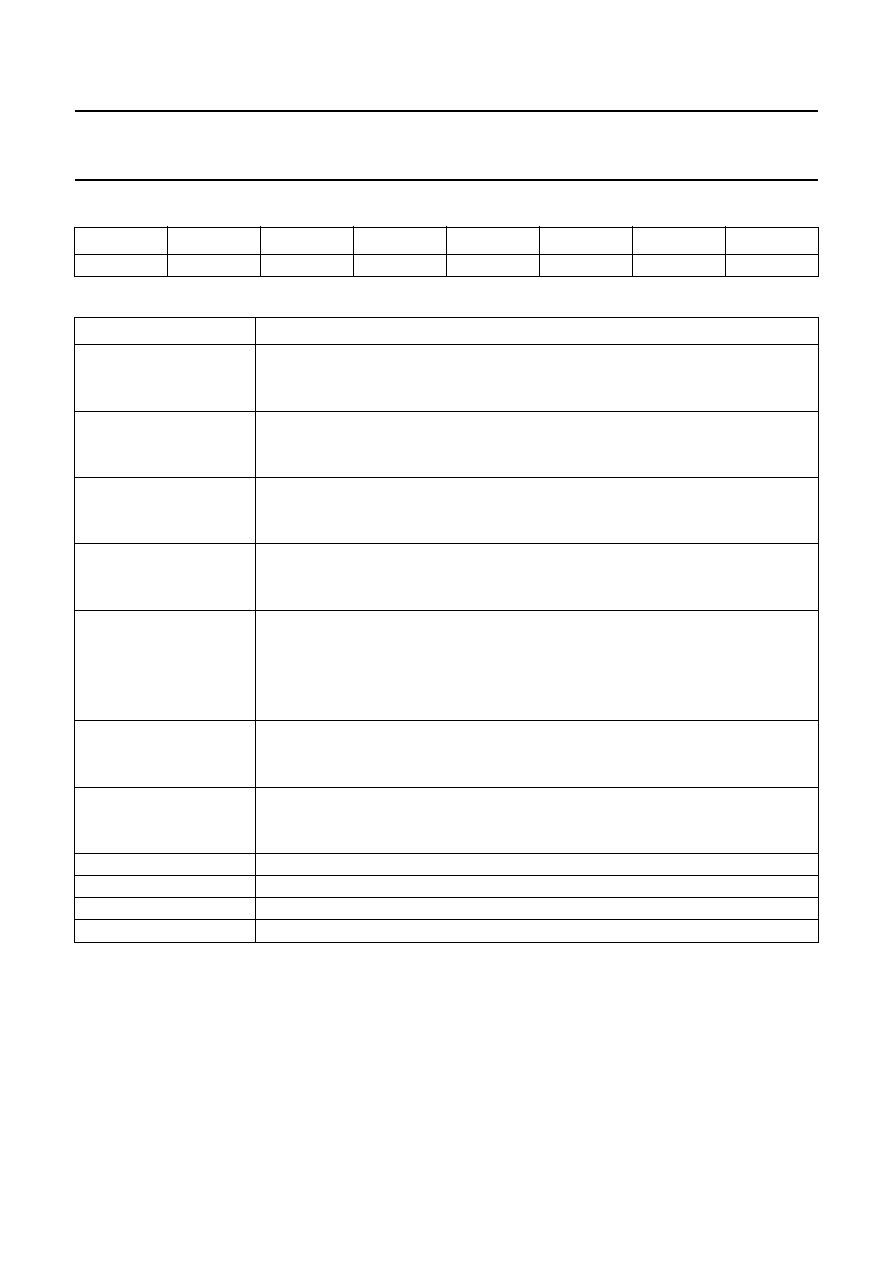

Table 7

Establishment of default bit rate

CLOCK GENERATOR MODE

FSCLKIN (kHz)

DEFAULT BIT RATE (kbits/s)

Free running internal clock

don't care

384

Locked internal clock

don't care

384

External sample clock

256 or 384

◊

48

417.96

256 or 384

◊

44.1

384

256 or 384

◊

32

278.64

256 or 384

◊

24

208.98

256 or 384

◊

22.05

192

256 or 384

◊

16

139.32

1997 Nov 17

18

Philips Semiconductors

Preliminary specification

ISO/MPEG Audio Source Decoder

SAA2502

7.4.3

S

AMPLE CLOCK GENERATION

When the `external sample clock' mode of the clock

generator is used, the application must know the sample

rate. FSCLKIN has to be applied, with a frequency which

is a multiple of the sample rate. The (sample rate

dependent) output interface timing signals will be

generated from FSCLKIN. This mode will normally be

used in applications with a fixed sample rate. Should the

sample rate change, then a soft reset is strongly advised.

When one of the remaining clock generator modes is used,

the SAA2502 selects the active sample rate automatically,

and generates the required sample rate related timing

signals from its MCLKIN and X22IN clock inputs. Soft

resets at sample rate changes are generated

automatically. After a hard reset, a sample rate of 44.1 kHz

by default is selected. Such default setting may be

overruled using the control interface.

SCK, WS and SPDIF will show frequency changes in any

of the following 3 situations:

∑

When the SAA2502 establishes synchronization to the

coded data input bit stream at a sample rate different

from the one previously selected

∑

When the current (default) sample rate is overruled by

the control interface

∑

When the clock generator mode is changed, resulting in

a switch from or to the `external sample clock mode.

In all those situation the phase of WS and the data content

of SPDIF will be continuous.

In all other events SCK, WS and SPDIF remain operating

without phase or frequency changes and the sample rate

selection remains unchanged.

7.4.4

D

ECODER PRECISION

During decoding several multiply operations are carried

out on coded samples. The results of these operations

have to be rounded in order to keep the word length

required for internal number representation within

reasonable limits. Accumulation of these rounding errors is

kept at a very low level in order to assure precise audio

output samples. SAA2502 precision is specified using the

output of the MPEG reference decoder based on double

precision floating point calculations as a reference.

Differences between that reference decoder and SAA2502

output manifest themselves as white noise.

Two contributions to this noise may be identified:

∑

Noise resulting from internal rounding on intermediate

results

∑

Noise resulting from rounding of final output samples

to 16, 18, 20 or 22 bits (depending on selected output

accuracy).

Table 8 shows the effective noise level figures. (unit is

1 LSB of 22-bit accuracy output). Except for 22-bit

accuracy, output rounding is by far the dominant effect.

Consequently the SAA2502 may be considered a

professional level high precision decoder.

Table 8

Effective noise level figures

Note

1. The output rounding part of this precision is valid only for I

2

S and SPDIF outputs.

OUTPUT ACCURACY

(BITS)

INTERMEDIATE

ROUNDING

OUTPUT ROUNDING

(1)

TOTAL NOISE LEVEL

22

0.6

0.3

0.7

20

0.6

1.2

1.3

18

0.6

4.6

4.7

16

0.6

18.5

18.5

1997 Nov 17

19

Philips Semiconductors

Preliminary specification

ISO/MPEG Audio Source Decoder

SAA2502

7.4.5

S

CALE FACTOR

CRC

PROTECTION

MPEG specifies an optional 16 bit CRC that may be used

to verify whether an important part of each audio frame is

received correctly. The following data items is protected by

this CRC:

∑

Bytes 3 and 4 of the first 4 bytes of each frame,

containing most of the frame header information

∑

Allocation information

∑

Scale factor select information (layer II only).

The scale factors are not protected by this scheme.

The DAB specification includes CRC protection for scale

factors. The 32 sub-bands are divided into the following

4 blocks:

Block 0 = sub-bands 0 to 3

Block 1 = sub-bands 4 to 7

Block 2 = sub-bands 8 to 15

Block 3 = sub-bands 16 to 31.

Each block is protected by an 8-bit CRC if that block of

sub-bands is (partly) inside the current sub-band limit.

The required scale factor CRCs are stored in the last bytes

of the previous audio frame:

∑

The last two bytes of each frame are reserved for

ancillary data; DAB specification calls this Fixed

Program Associated Data (FPAD)

∑

Minimum 2 and maximum 4 bytes before FPAD are

reserved for scale factor CRCs. The number of CRC

bytes present is be derived from the sub-band limit of the

following audio frame

∑

Bytes before the CRCs are available for more ancillary

data; DAB specification calls this extended Program

Associated Data (XPAD), as far as not occupied by

MPEG coded input data.

The DAB type of scale factor CRC protection, extended to

all valid sample frequency plus bit rate combinations of

MPEG1 and MPEG2, and to layer I, is fully supported by

the SAA2502. (DAB is restricted to MPEG1 layer II, to

48 kHz sample frequency and does not support free

format bit rate). Requirements for scale factor CRC

handling is indicated by the SFCRC control flag.

7.4.6

H

ANDLING OF ERRORS IN THE CODED INPUT DATA

The SAA2502 is able to handle certain types of errors in

the input data. Three error categories will be handled:

∑

Errors flagged by the coded input data error flag CDEF

∑

CRC failures (if MPEG and/or scale factor error

protection is active)

∑

MPEG audio frame syntax errors.

Error flags in the input data will effect the decoding process

if the corrupted data is inside the header, bit allocation or

scale factor select information part of a frame (then the

SAA2502 will `soft' mute that frame) or inside the scale

factor field (then the most recent valid scale factor of the

same sub-band will be copied).

Error flags in other data fields will be ignored. If MPEG

and/or scale factor CRCs are active the CRC result has

priority over CDEF flags inside the protected fields. In

applications where the MPEG CRC is always present, the

protection bit (which is not CRC protected) in the MPEG

header may be overruled by setting control flag CRCACT.

Thus the SAA2502 is robust for data errors in the

protection bit.

1997 Nov 17

20

Philips Semiconductors

Preliminary specification

ISO/MPEG Audio Source Decoder

SAA2502

7.4.7

D

YNAMIC RANGE COMPRESSION

The baseband audio output resulting from MPEG

decoding has a high dynamic range (theoretically

>200 dB, practically up to 120 dB for the 22-bit output

mode).This feature is very attractive from the high quality

audio standpoint of view, but such high dynamic range is

undesirable when there is a relatively high level of

background noise (e.g. for car radio). For those

applications the SAA2502 offers the possibility of built in

dynamic range compression:

∑

Internal dynamic range compression is offered. Thus

any standard MPEG encoded bit stream may be

compressed i.e. no added compression information is

required.

∑

The dynamic range compression algorithm is fully

parameterised. All major characteristics are

programmable through the control interface:

≠ Level of compression

≠ Maximum compression

≠ Compression offset

≠ Compression release rate (compression attack rate

has to be fixed).

The dynamic range compression algorithm is based on a

(in time varying) amplification factor, which is equally

applied to all audio output samples. The value of the

amplification factor is calculated on basis of the current

audio output power level for each (sub)frame of 384 output

samples. The applied power to amplification curve is

shown in Fig.11. All characteristics of the curve are

programmable:

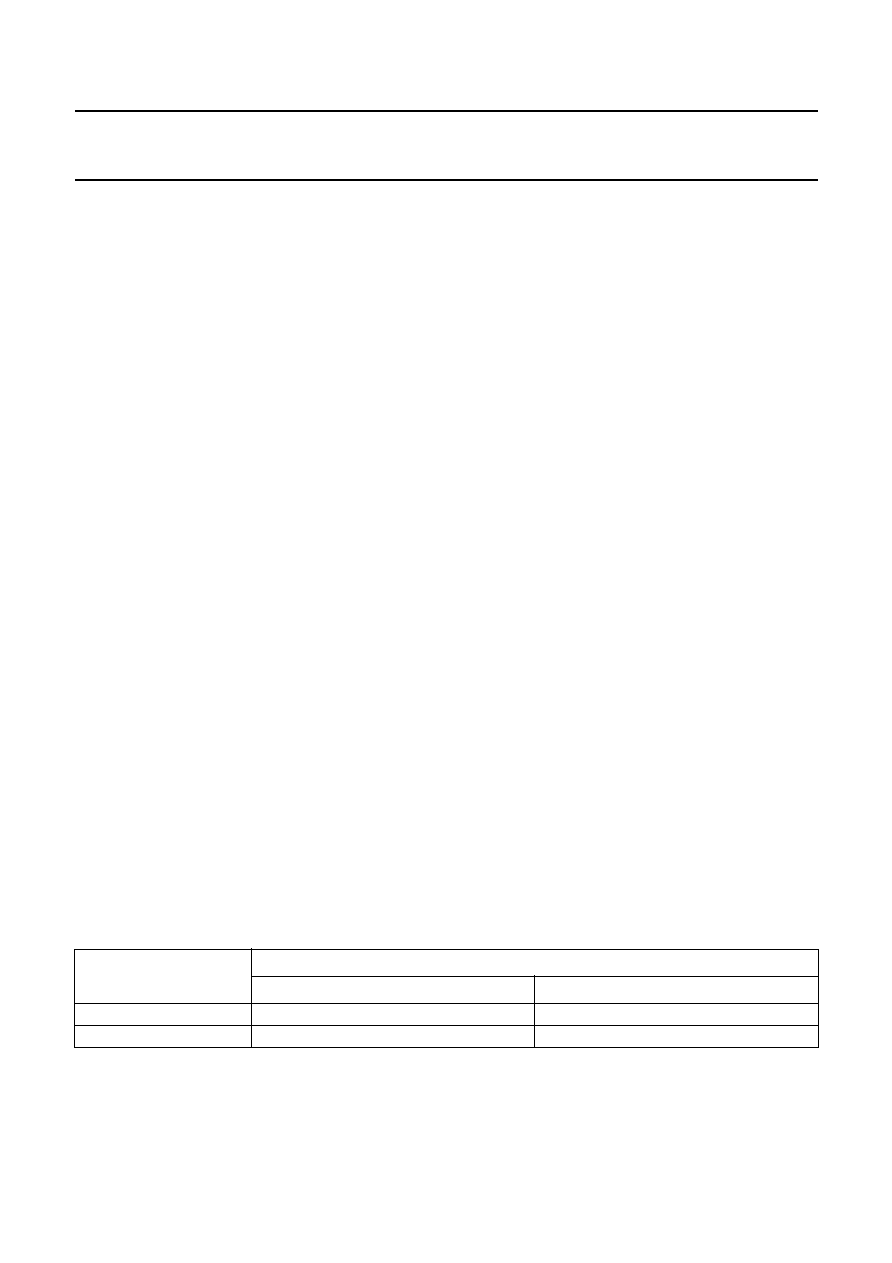

∑

Compression slope minimum = 0, maximum = 0.996

∑

Maximum amplification minimum = 0 dB,

maximum = 23.81 dB

∑

Offset minimum = 0 dB, maximum = 47.81 dB.

Offset values close to 0 dB may result in clipped output

signals. This is especially true for signals with a high

amplitude-to-power ratio (an extreme example of such a

signal is a maximum amplitude unit impulse).

The occurrence of this effect can be avoided by selecting

an offset value close to or greater than 15 dB.

In the context of dynamic range compression definition,

the 0 dB power reference level is defined as a sine wave

shaped output signal with maximum amplitude in just one

(right or left) channel.

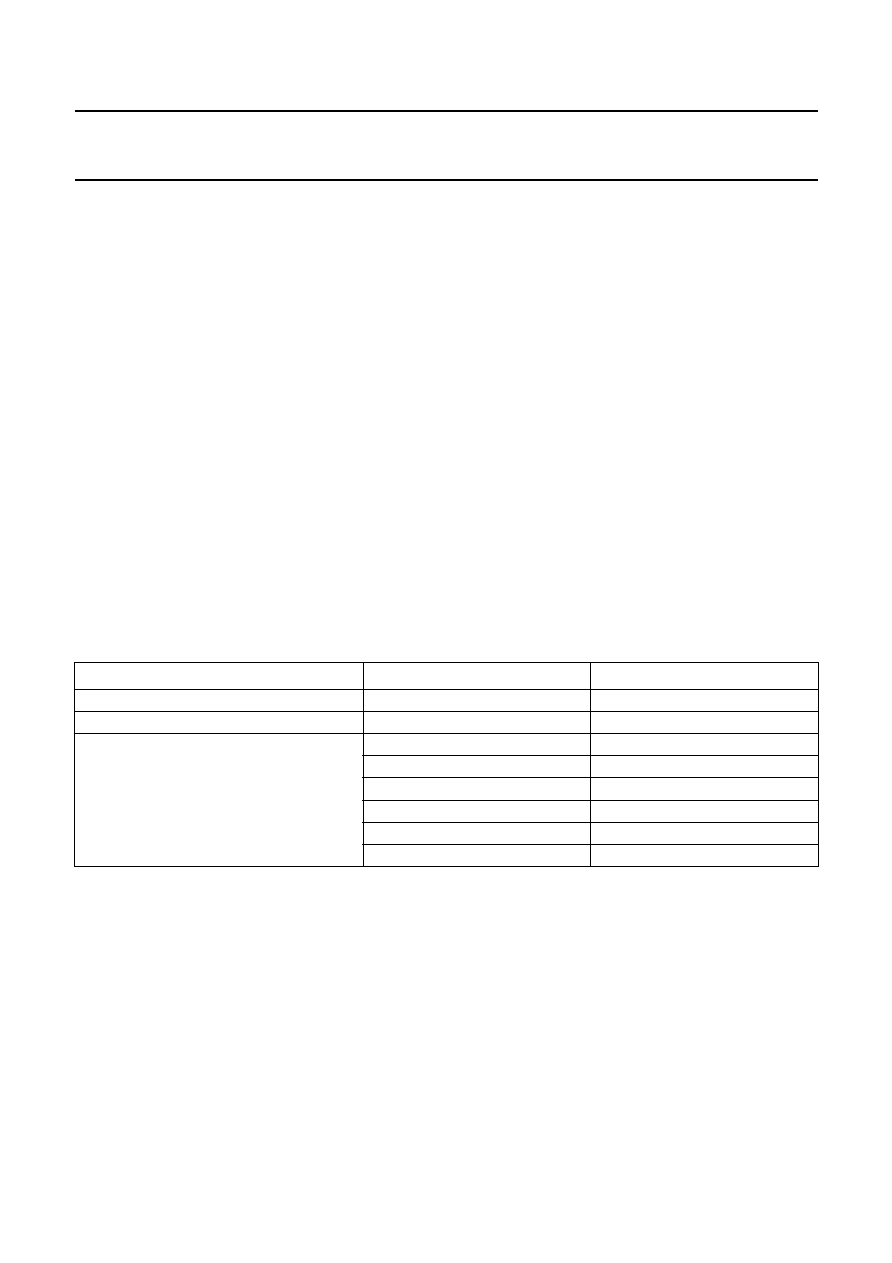

The calculation will result in an new amplification factor

every 384 samples (i.e. from 8 ms at 48 kHz to 24 ms at

16 kHz sample rate). Subsequent amplification factors

may vary considerably.

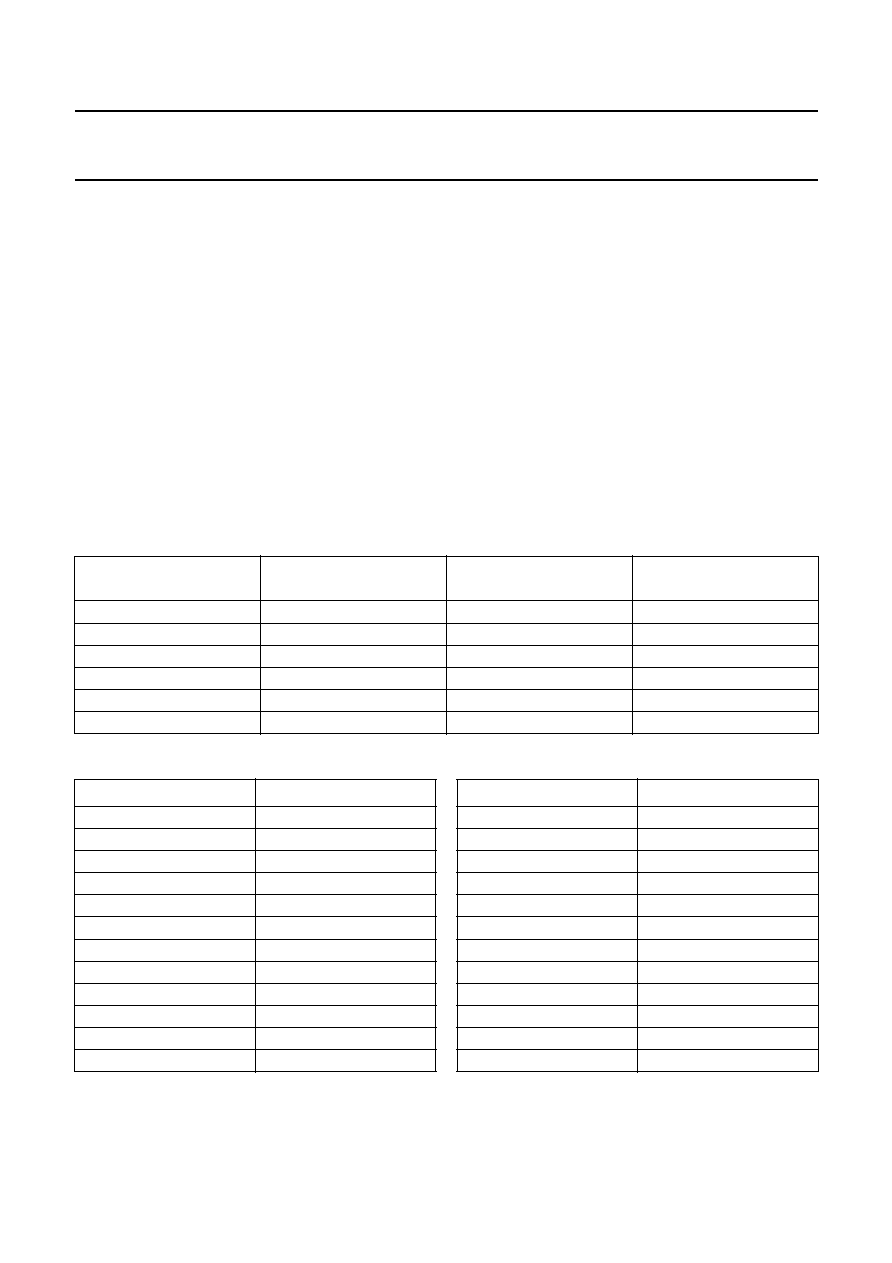

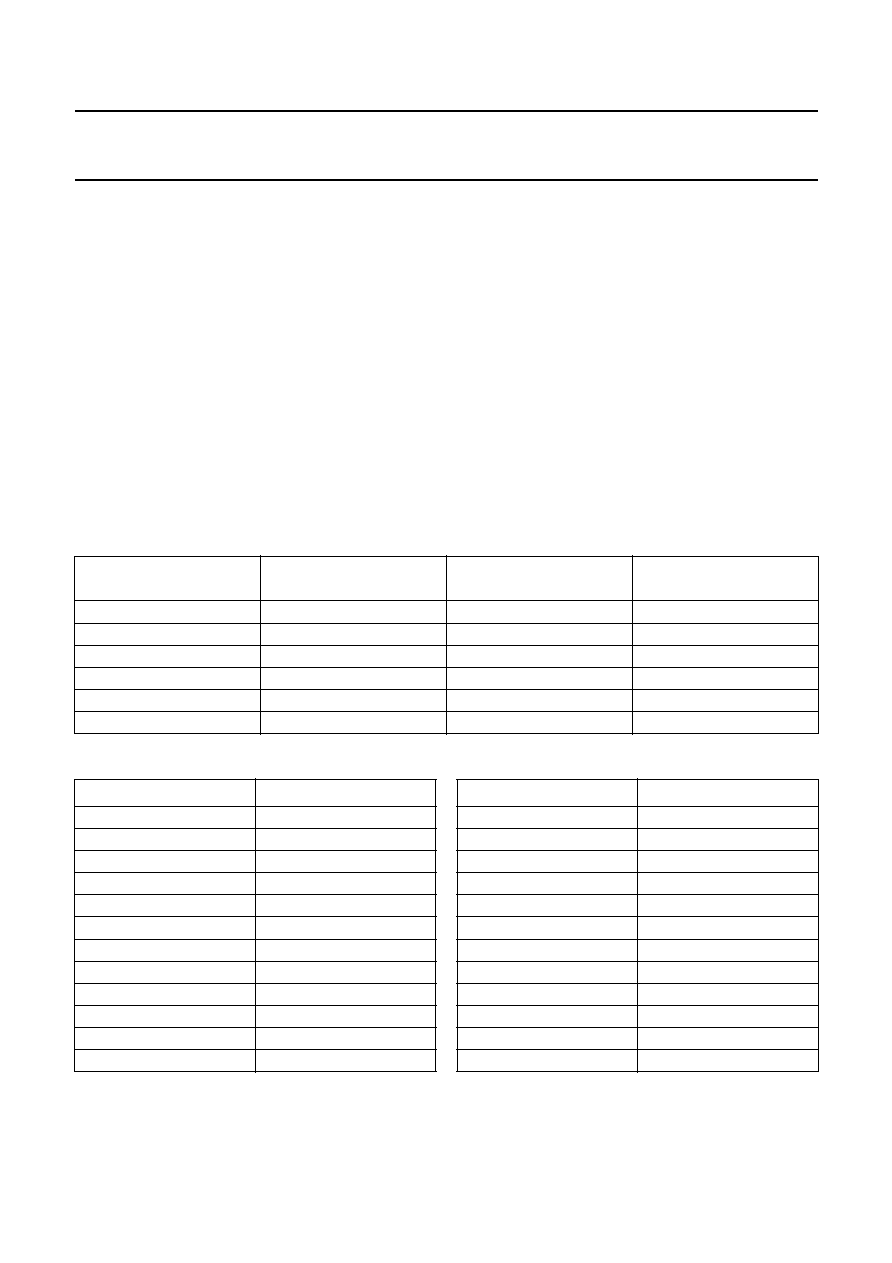

An example showing two large step type discontinuation is

shown in Fig.12. It is undesirable to apply large increasing

amplification steps immediately. Consequently increasing

the amplification factor is limited to the `release rate' which

is also programmable:

∑

Minimum release rate =

(1.46 dB/s at 48 kHz; 0.488 dB/s at 16 kHz)

∑

Maximum release rate =

(46.87 dB/s at 48 kHz; 15.625 dB/s at 16 kHz).

Decreasing amplification factors, must be applied almost

immediately to avoid overflow when the audio power

increases rapidly; thus attack rate is non-programmable

and fast.

0.0117 dB

384 samples

----------------------------------

0.375 dB

384 samples

----------------------------------

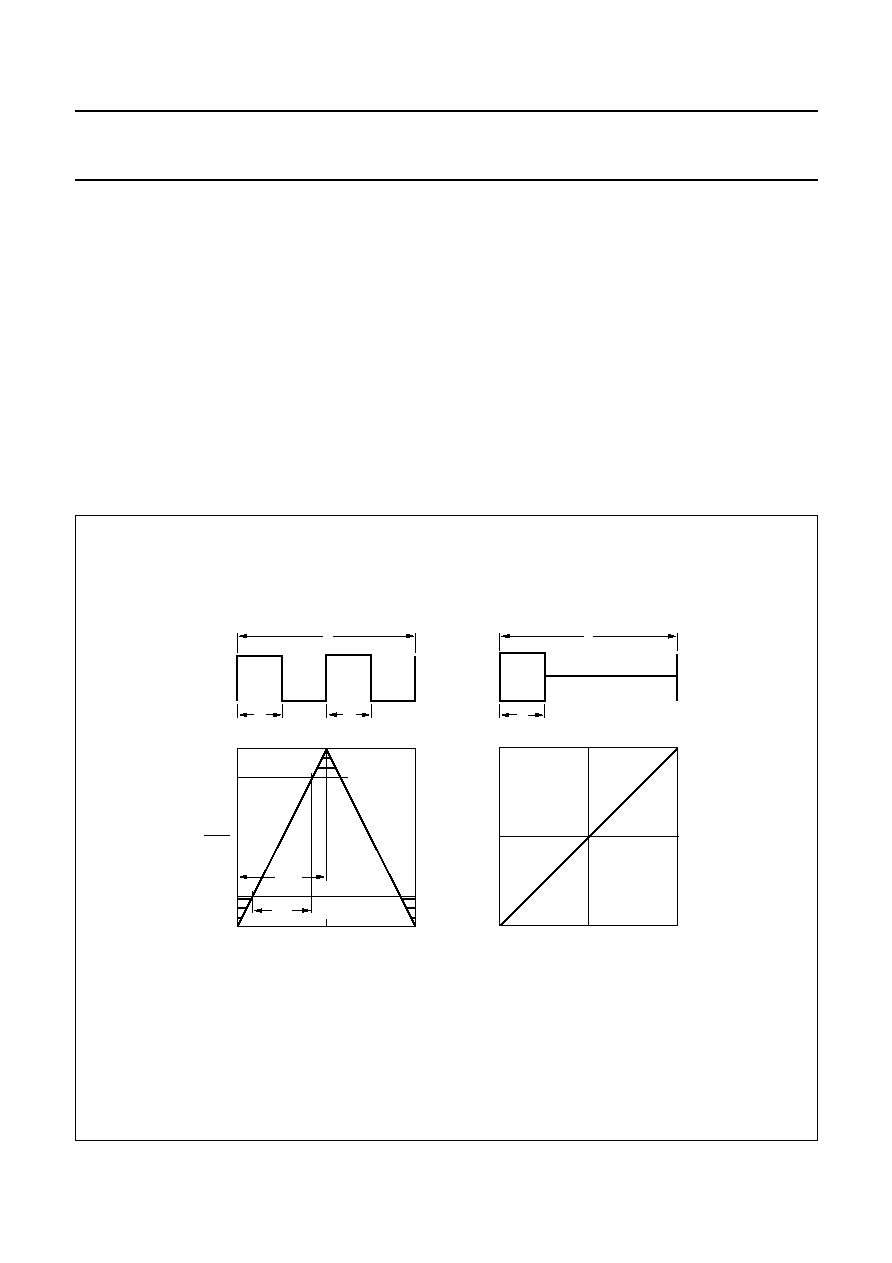

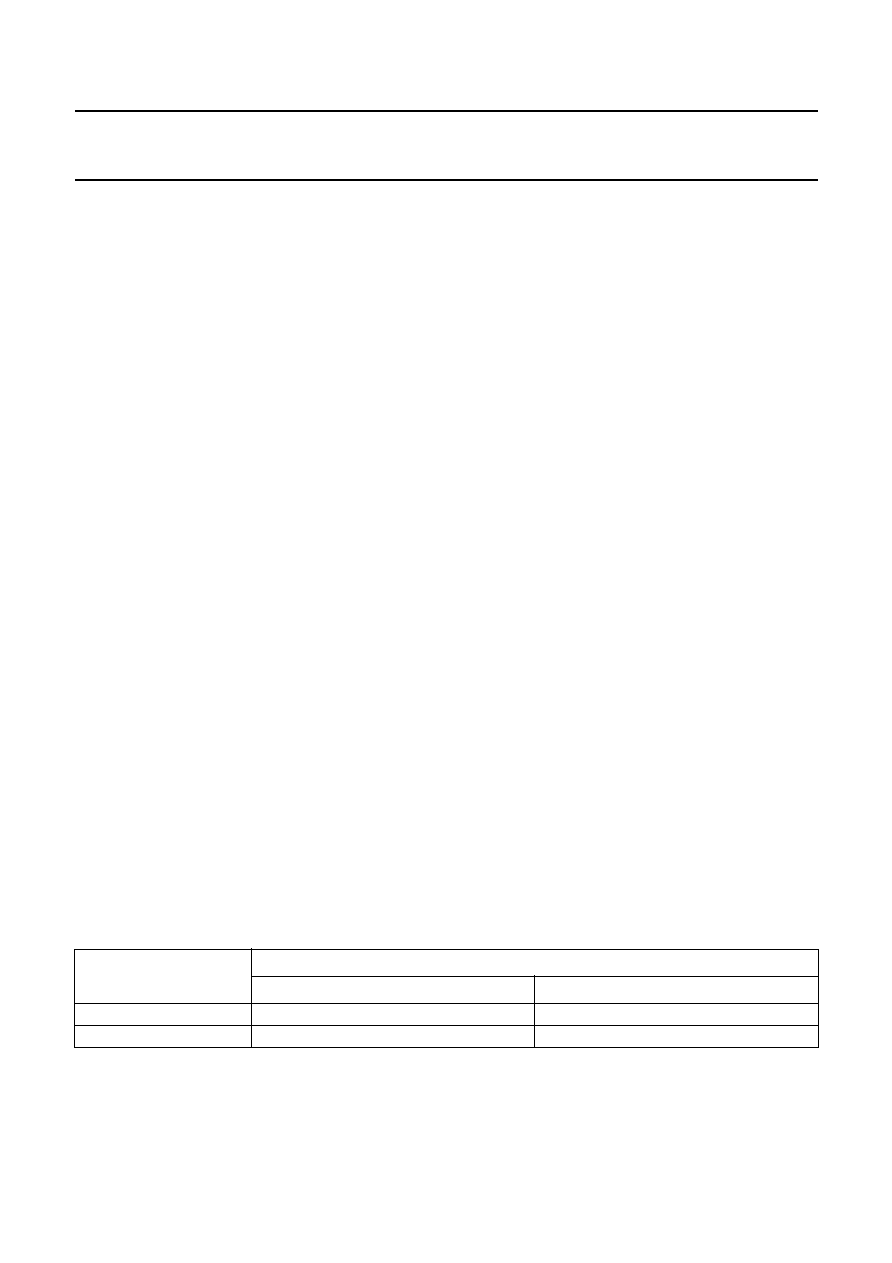

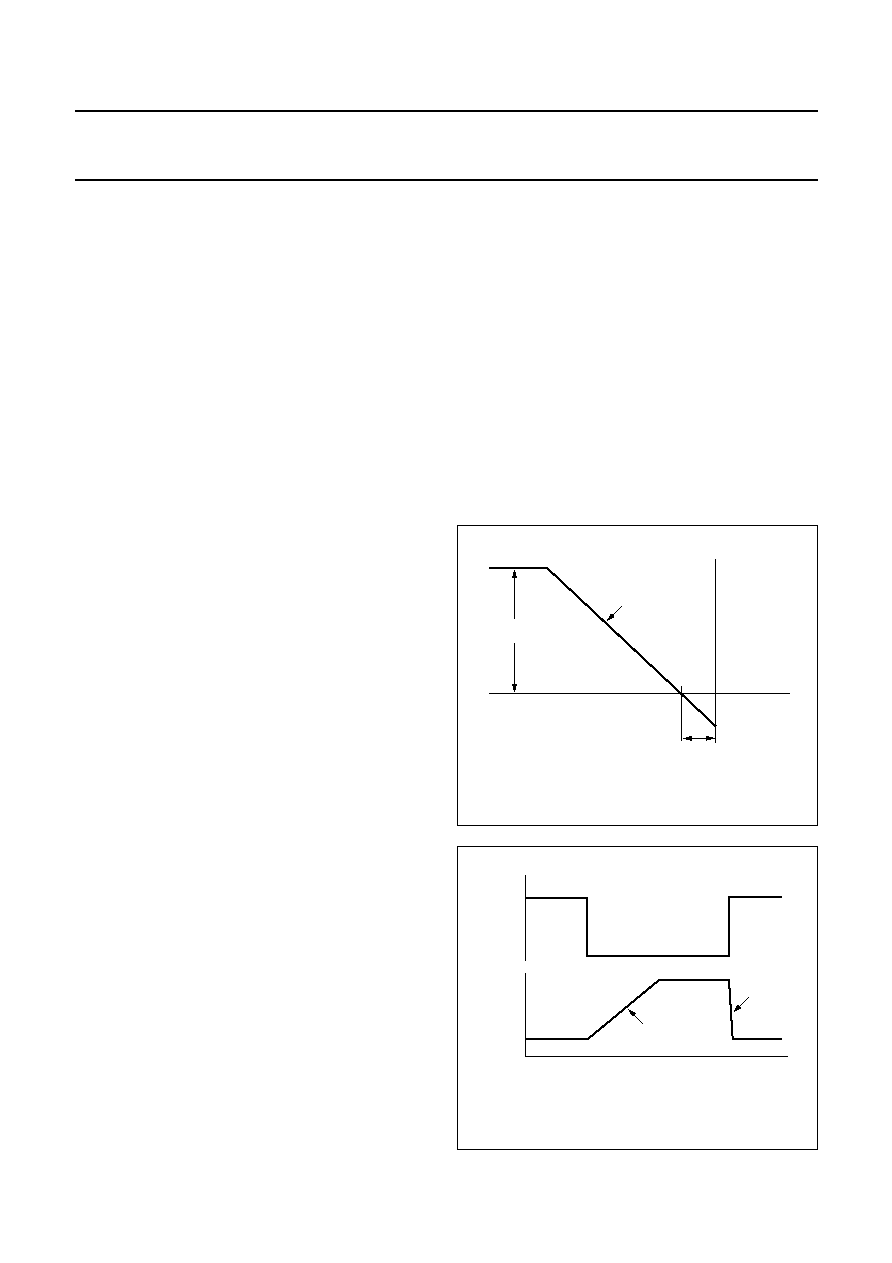

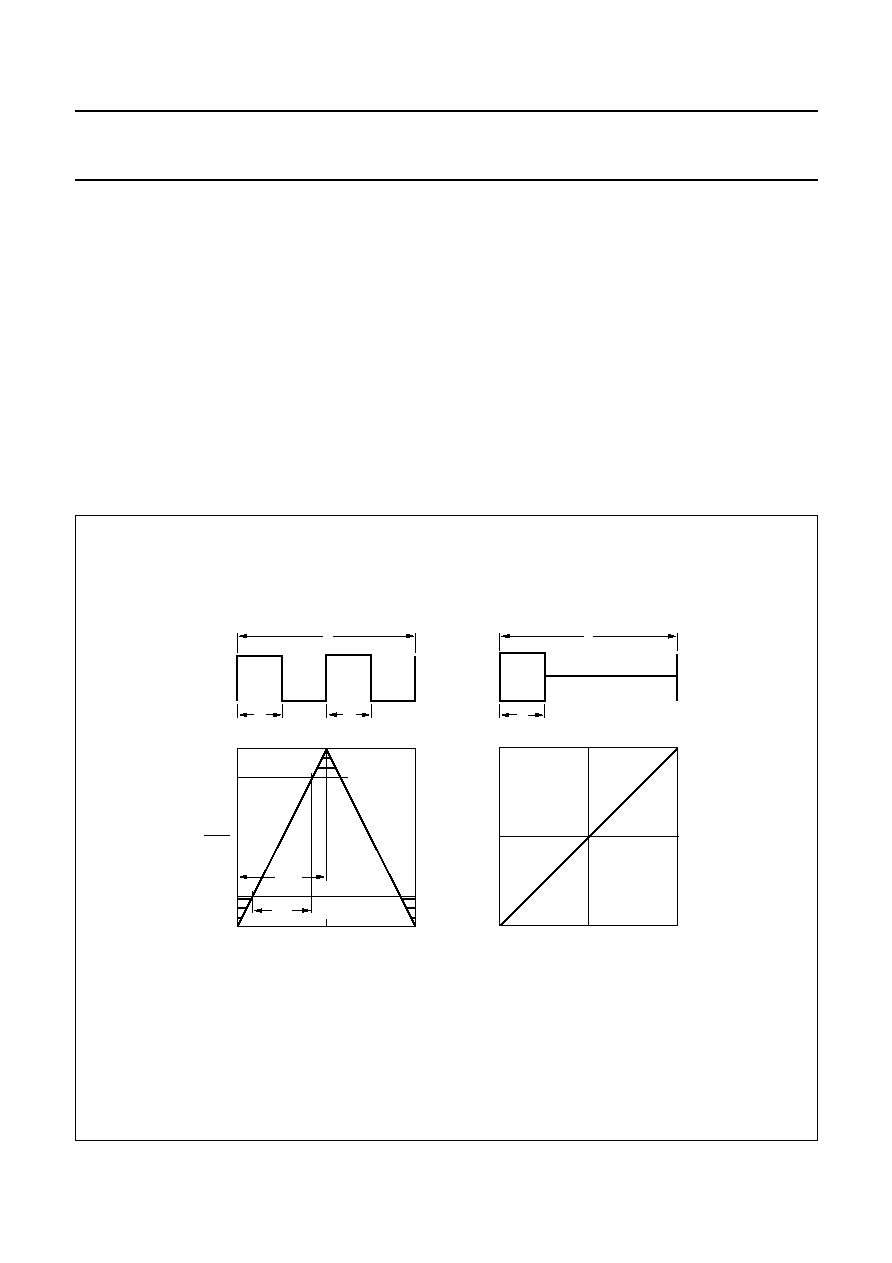

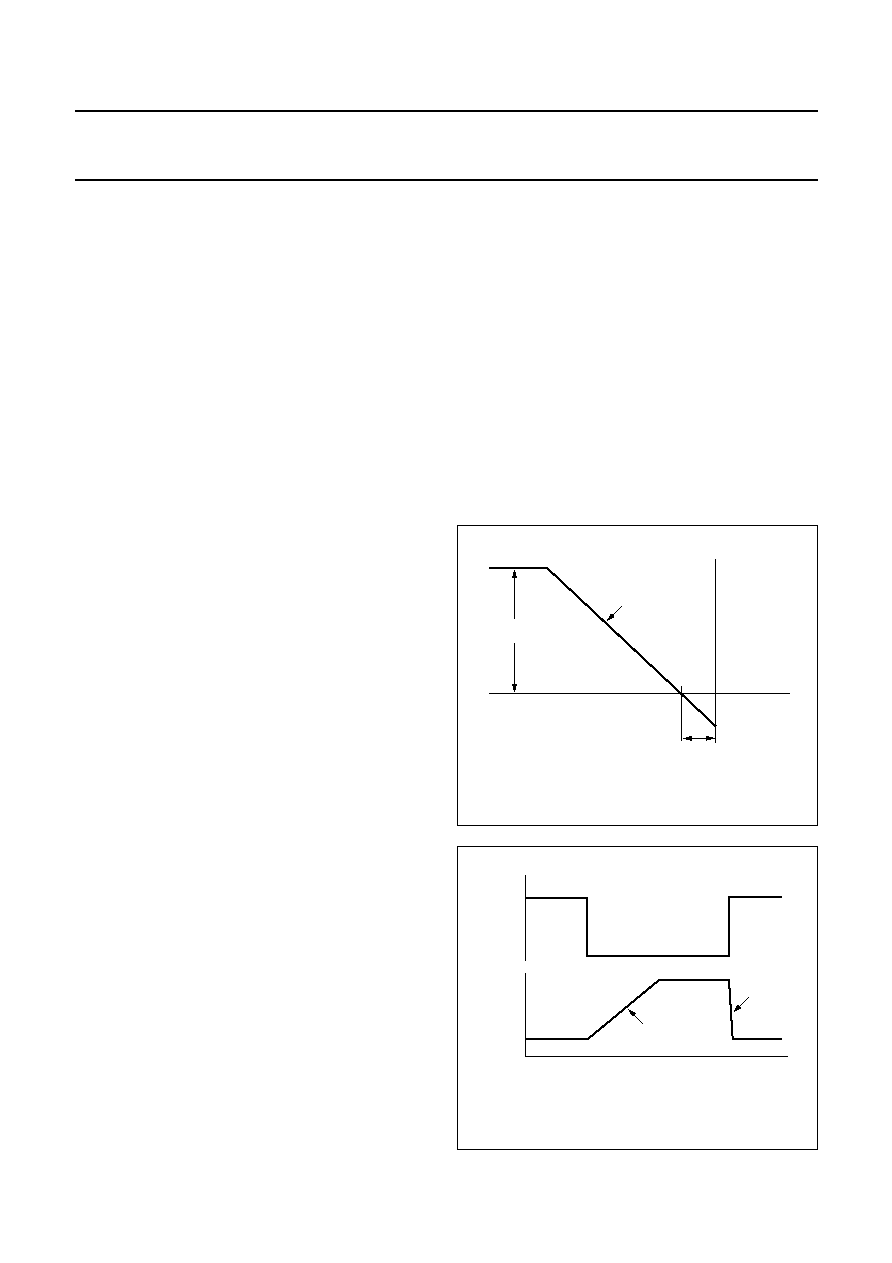

Fig.11 Dynamic range compression characteristic.

handbook, halfpage

MGE478

maximum

amplification

compression

slope

amplification

(dB)

0 dB

power (dB)

offset

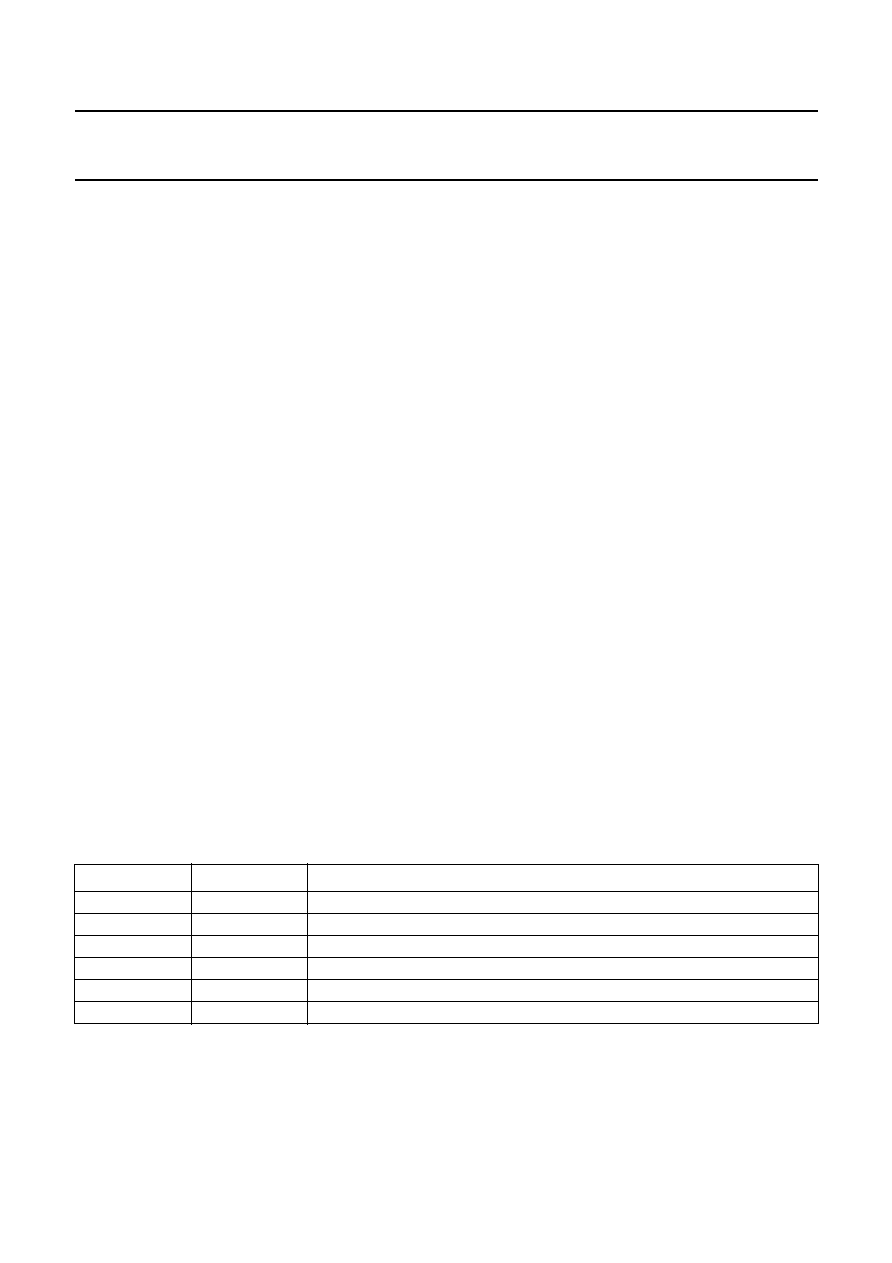

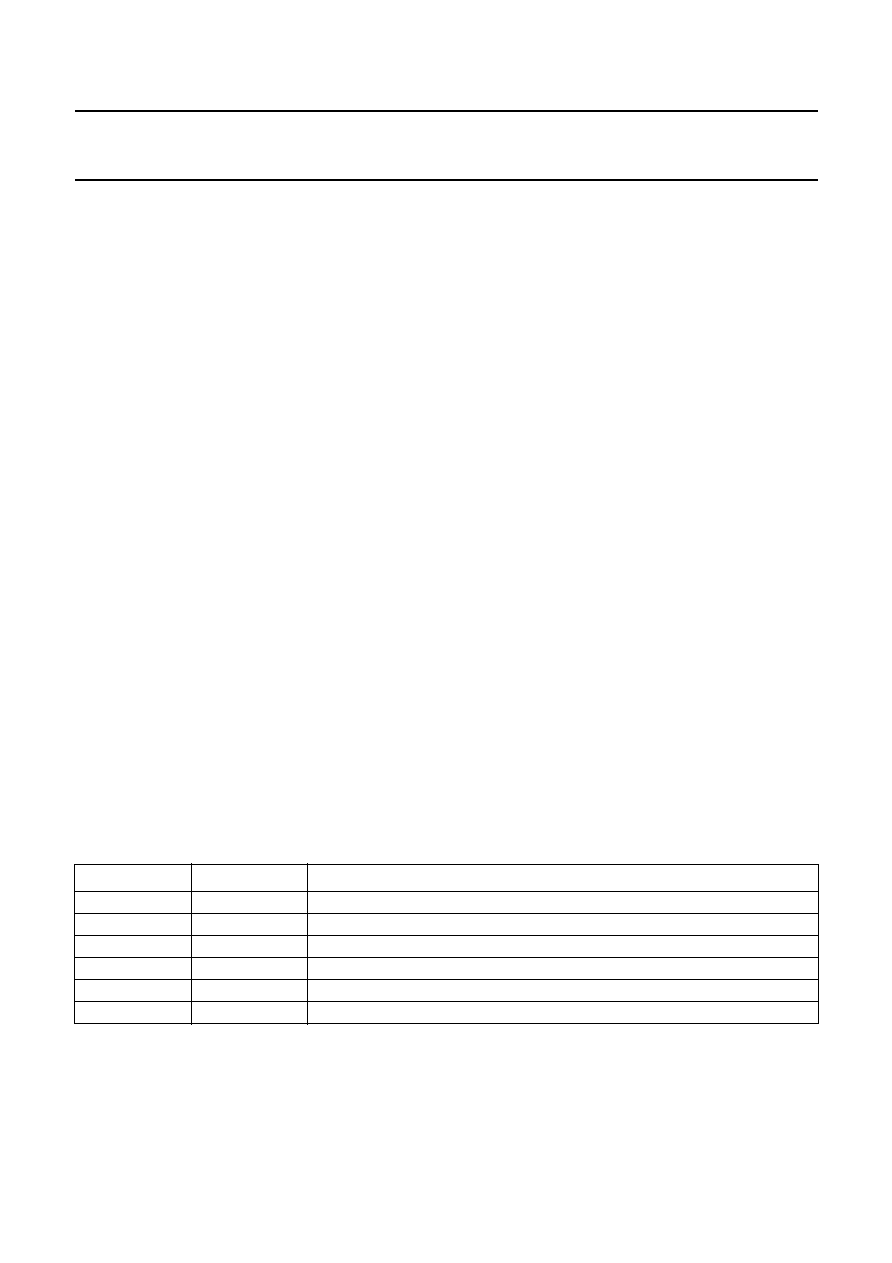

Fig.12 Amplification change rates.

handbook, halfpage

MGE479

audio

signal

power

amplifi-

cation

release

rate

attack

rate

time

1997 Nov 17

21

Philips Semiconductors

Preliminary specification

ISO/MPEG Audio Source Decoder

SAA2502

7.4.8

B

ASEBAND AUDIO PROCESSING

Baseband audio de-emphasis as indicated in the MPEG

input data stream is performed digitally inside the

SAA2502. The included `Audio Processing Unit' (APU)

see Fig.19, may be used to apply programmable

inter-channel crosstalk or independent channel volume

control.

The APU attenuation coefficients LL, LR, RL and RR may

be changed dynamically by the microcontroller, writing

their 8-bit indices to the SAA2502 through its control

interface. The coefficient changes become effective within

one sample period after writing. To avoid audible clicks at

coefficient changes, the transition from the current

attenuation to the next is smoothed. The relationship

between the APU coefficient index and the actual

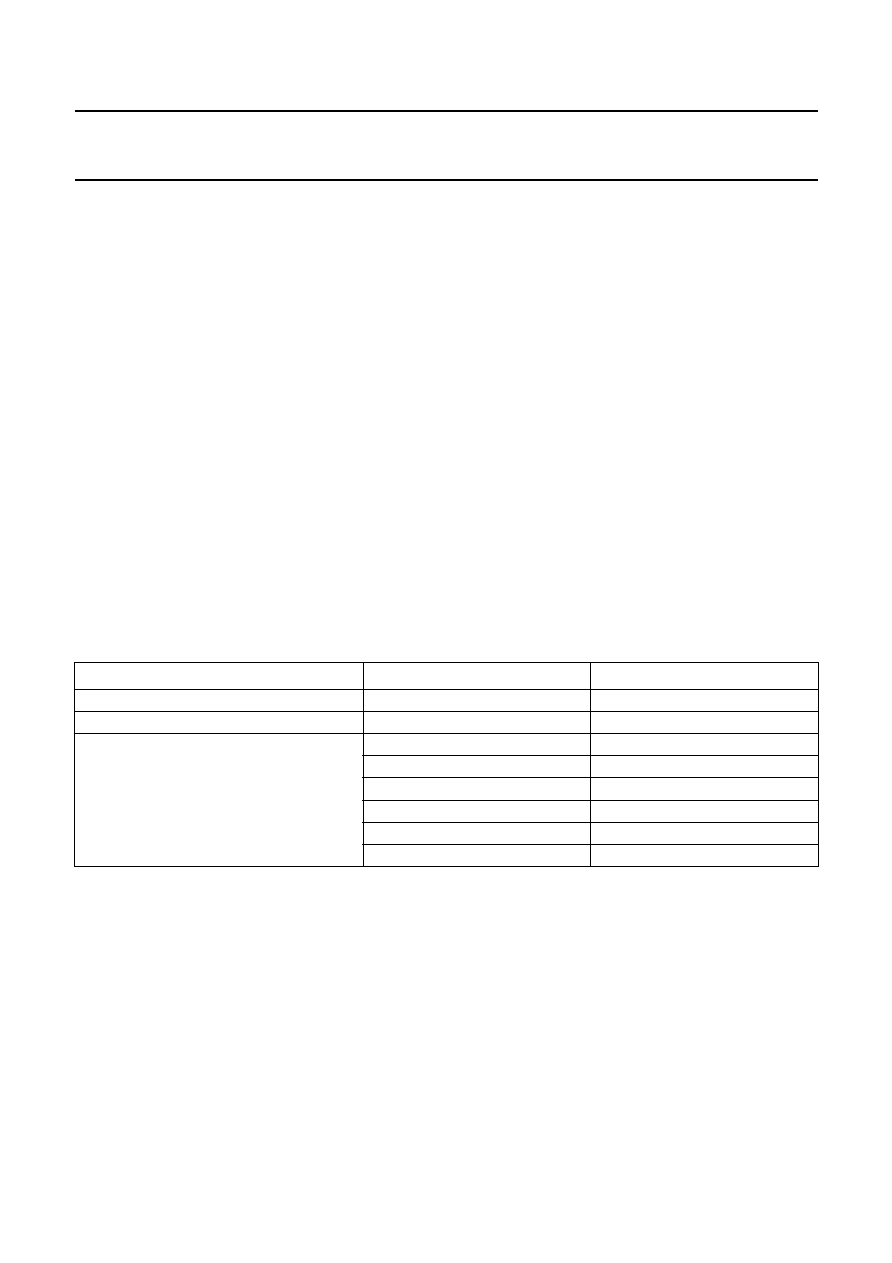

coefficient (i.e. the gain) is shown in Fig.14 and in Table 9

For coefficient index 0 to 64 the step size is

-

3

/

16

dB and

for coefficient index 64 to 255 the step size is

-

3

/

8

dB.

The APU has no built-in overflow protection, so the

application must assure that the output signals of the APU

cannot exceed the 0 dB level. For an update of the APU

coefficients, it may be required to increase some of the

coefficients and decrease some others. The APU

coefficients are always written sequentially in a fixed

sequence LL, LR, RL and RR. Therefore, to prevent

(temporary) internal APU data overflow, the following

sequence of steps may be necessary:

1. Write LL, LR, RL and RR, but change only decreasing

coefficients. Overwrite increasing coefficients with

their old value (therefore do not change these yet).

2. Write LL, LR, RL and RR again, but now change

increasing coefficients, keeping the other ones

unchanged.

Table 9

APU coefficient index and actual coefficient.

APU COEFFICIENT INDEX C

APU

COEFFICIENT

BINARY

DECIMAL

00000000 to 00111111

0 to 63

01000000 to 11111110

64 to 254

11111111

255

0

2

C

32

------

≠

2

C

32

≠

(

)

16

-----------------------

≠

Fig.13 Audio Processing Unit (APU).

handbook, halfpage

left decoded

audio

samples

LR

LL

RL

left output

audio

samples

right decoded

audio

samples

RR

right output

audio

samples

MGB493

Fig.14 Relation between APU coefficient index and

gain.

(1) Step

-

3

/

16

dB per coefficient increment.

(2) Step

-

3

/

8

dB per coefficient increment.

handbook, halfpage

MGE480

0

0

-

12

-

83.25

254 255

(2)

(1)

APU coefficient index

gain

(dB)

64

1997 Nov 17

22

Philips Semiconductors

Preliminary specification

ISO/MPEG Audio Source Decoder

SAA2502

7.4.9

D

ECODER LATENCY TIME

Latency time is defined as elapsed time between the

moment that the first byte of an audio frame is delivered to

the SAA2502 and the moment that the output response

resulting from the first (sub-band) sample of the same

frame reaches its maximum.

Latency time results from the addition of two internal

latency contributions: t

latency

= t

proc

+ t

buf

.

∑

The processing latency time (t

proc

) is sample frequency

dependent (see Table 10).

∑

The input buffer latency time (t

buf

) is input interface

mode dependent.

Precision of latency time calculation is sampling rate and

bit rate dependent. Maximum deviation is roughly plus or

minus 4 sample periods.

7.4.9.1

Master and slave input interface modes

Input buffer latency time t

buf

= (minimum of t

buf1

and

t

buf2

) + cr

◊

3.52 ms:

∑

t

buf1

is sample frequency dependent (see Table 10)

∑

t

buf2

is input bit rate dependent (see Table 11 and

Table 12)

∑

cr is the ratio between maximum and actual value of

MCLKIN frequency.

For slave input interface mode NOT the average input bit

rate should be used for table look-up, but CDCL frequency

(input bit rate during the burst). For free format bit rates the

table should be interpolated (t

buf2

is proportional to

1/bit rate).

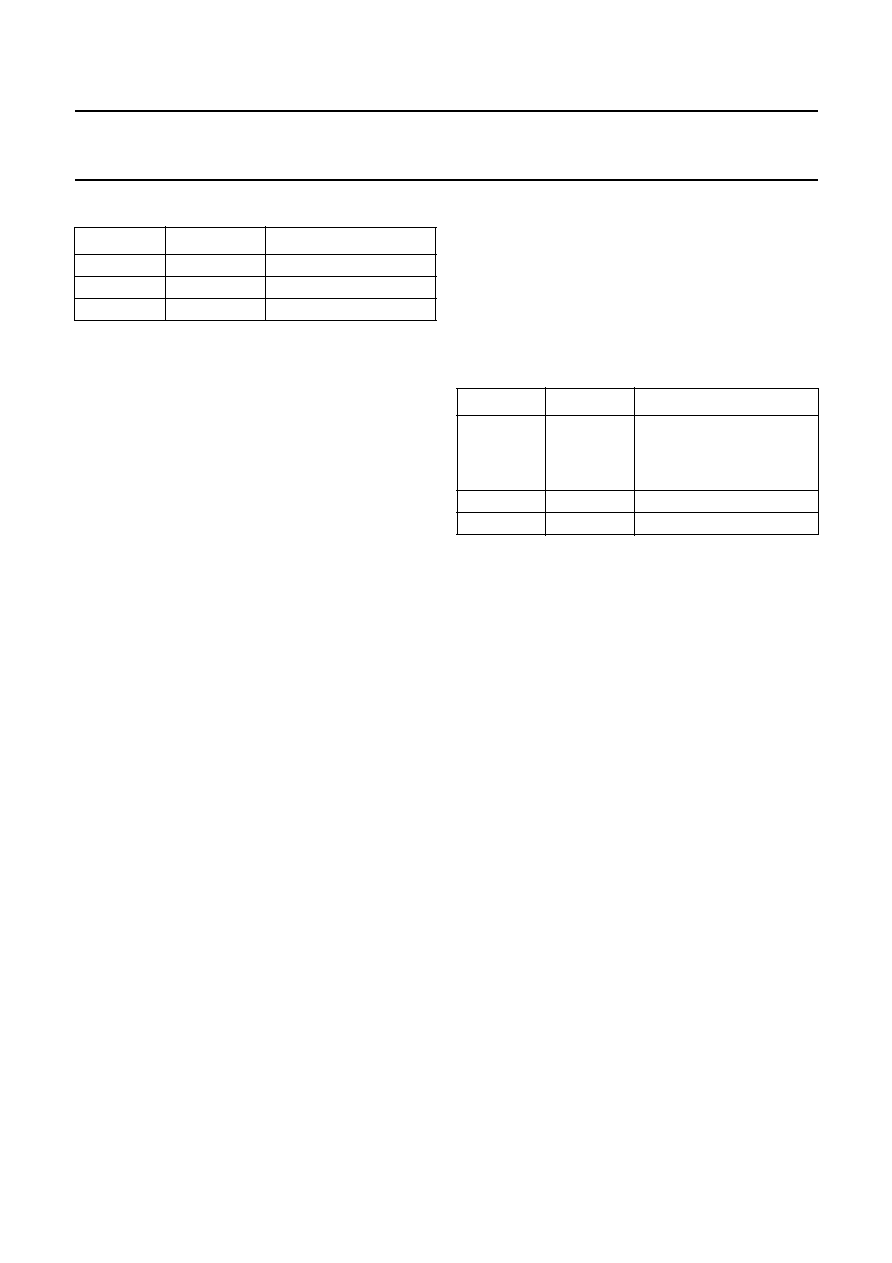

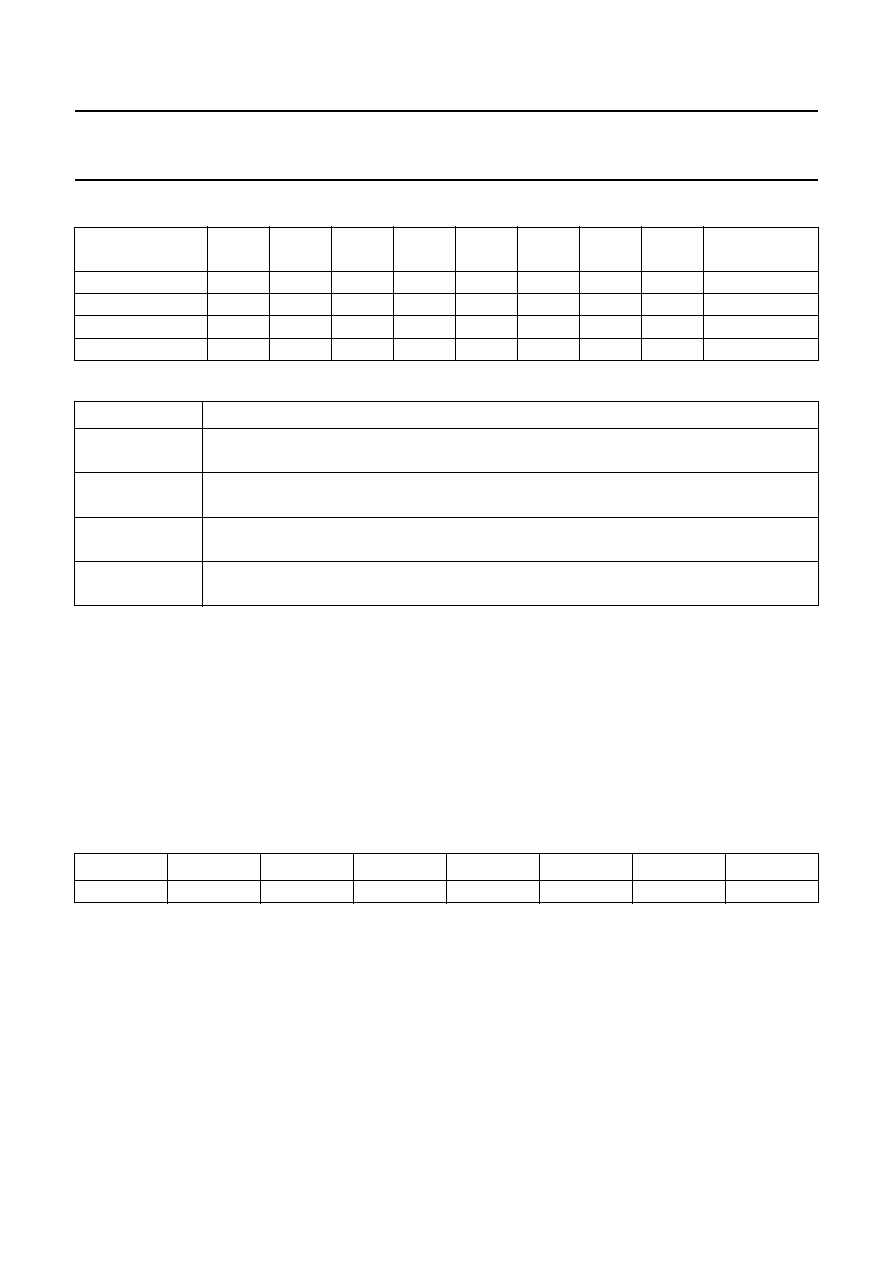

Table 10 Processing latency time

SAMPLE FREQUENCY

(kHz)

t

proc

(ms)

t

buf1

LAYER I (ms)

t

buf1

LAYER II (ms)

48

6.67

8.00

24.00

44.1

7.26

8.71

26.12

32

10.00

12.00

36.00

24

13.33

16.00

48.00

22.05

14.51

17.41

52.24

16

20.00

24.00

72.00

Table 11 Buffer latency time; high bit rate

BIT RATE (kbits/s)

t

buf2

(ms)

448

5.52

384

6.44

320

7.73

256

9.66

192

12.88

160

15.45

128

19.31

96

25.75

64

38.63

48

51.50

32

77.25

16

154.50

Table 12 Buffer latency time; low bit rate

BIT RATE (kbits/s)

t

buf2

(ms)

416

5.94

352

7.02

288

8.58

224

11.04

176

14.05

144

17.17

112

22.07

80

30.90

56

44.14

40

61.80

24

103.00

8

309.00

1997 Nov 17

23

Philips Semiconductors

Preliminary specification

ISO/MPEG Audio Source Decoder

SAA2502

7.4.9.2

Buffer controlled input mode

Input buffer latency time behaviour is relatively complex in

this mode.

At start-up (i.e. during the search-for-frame sync) latency

time is very small (t

buf

< 2 ms) because the input buffer

remains empty.

After a frame sync is detected, normal decoding starts and

the buffer fills up to its desired fill level. That level will result

in a buffer latency time t

buf2

(see Tables 11 and 12, t

buf1

plays no role) for constant bit rate operation.

It is more complex for variable bit rates, at high bit rates the

buffer will hold only a fraction of a frame, while at low bit

rates it may hold many frames (each possibly of a different

bit rate). Also input buffer content may deviate from the

desired level because data consumption rate at the output

of the buffer may be high during short periods while

replenishing is limited by CDCL frequency.

As a result buffer latency time in buffer controlled input

mode may be predicted more or less accurately only at

(re)start time.

Another consequence of buffer behaviour at very low bit

rates in this mode is that buffer latency time values may

become large. Therefore it might be possible that the

SAA2502 will request data, which is not (yet) available.

In those situations the SAA2502 is requesting more data

than required; storage of more than one complete frame in

the input buffer is never necessary.

Consequently the application may delay delivery of

requested data until it becomes available without any

effect on correct SAA2502 operation. This option

constitutes delayed delivery possibility.

7.5

Output interface module

The output interface module produces stereo baseband

output samples in three different formats at the same time:

∑

I

2

S

∑

SPDIF

∑

256 times oversampled bit serial analog.

Any of the three outputs may be enabled or disabled in

order to save dissipation and minimize EMC generation in

applications that do not need all of them.

Decoded mono streams and the (user) selected channel of

dual channel streams are presented at both (left and right)

output channels.

If indicated in the coded input data, de-emphasis filtering

is performed digitally on the output data, thus avoiding the

need of external analog de-emphasis filter circuitry.

7.5.1

I

2

S

OUTPUT

This output interface section generates decoded

baseband audio data in I

2

S format (see Fig.15).

The I

2

S output interface section consists of 3 signals

(see Table 13).

Fig.15 I

2

S output serial data transfer format.

handbook, full pagewidth

WS

SCK

SD

MSB

left sample

LSB

MSB

right sample

LSB

1

16/18/20/22

32

1

16/18/20/22

32

valid data

MGB502

1997 Nov 17

24

Philips Semiconductors

Preliminary specification

ISO/MPEG Audio Source Decoder

SAA2502

Table 13 Signals of output interfacing

The frequency of clock SCK is 64 times the sample

frequency.

The signal SD is the serial baseband audio data, sample

by sample (left/right interleaved; the left sample and the

right immediately following it form one stereo pair). 32 bits

are transferred per sample per channel. The samples are

transmitted in two's complement, MSB first. The output

samples are rounded to either 16, 18, 20 or 22 bit

precision, selectable by the control interface flags RND1

and RND0. The remainder of the 32 transferred bits per

sample per channel are zero.

The word select signal WS indicates the channel of the

output samples (LOW if left, HIGH if right).

7.5.2

SPIDF

OUTPUT

7.5.2.1

SPIDF format

The SPDIF data format is frame based. One SPDIF frame

represents one audio sampling period. Complete frames

must be transmitted at the audio sample rate. Every frame

comprises two sub-frames, each of 32 bits. The data is

transmitted in bi-phase mark modulated format to ensure

a zero DC component.

Four bits of data at the beginning of each sub-frame are

assigned to frame and sub-frame synchronization, which

is achieved using a set of 3 output sequences which

violate the bi-phase mark rules. The audio samples

occupy 24 bits (bits 4 to 27), transmitted LSB first.

Depending on the selected accuracy the 2, 4, 6 or 8 LSBs

will be logic 0.

Bits 28 to 31 are occupied by the validity flag for the audio

sample, a channel status bit (each super-frame of

192 frames contains two groups of 192 channel status

bits, one for each channel), a user data bit, and a parity bit

(even parity for bits 4 to 31). These bits are described

respectively as V, U, C and P in the SPDIF specification.

The synchronization for the channel status frame is

achieved by a pair of preamble violation sequences.

The synchronization for the user channel data is

embedded within the data.

SIGNAL

DIRECTION

FUNCTION

SCK

output

data clock

SD

output

baseband audio data

WS

output

word select

7.5.2.2

Frame synchronization patterns (Bits 0 to 3,

SPDIF subframe)

The frame synchronization patterns are based on bi-phase

violations. They are sent as shown in Table 14

The sequences are sent in place of 4 bi-phase coded

bits 0 to 3. They are not bi-phase coded, but are sent as

they are.

Table 14 Frame synchronization patterns

7.5.2.3

Validity flag (bit 28, SPDIF subframe, V bit)

The V bit is intended to indicate an invalid data sample.

Equipment connected to the interface is expected to

perform interpolations across small numbers of invalid

(V = logic 1) samples. Owing to the manner in which data

is decoded in the SAA2502, and the sub-band processing

of the signal, an input data error affects output audio

signals in a complex way.

There is not a simple relationship between input errors and

damaged audio samples. Therefore the validity flag value

is made programmable (through the control interface unit)

Control software can use this bit in any way required.

7.5.2.4

User channel data (bit 29, SPDIF subframe,

U bit)

There is a single user data channel. Two bits of data in this

channel are transmitted in each frame. For this minimum

implementation only the possibility to send single byte user

messages to the user channel is offered. Each byte sent

will be preceded by a single logic 1 valued start bit.

The 8 bits of the user message are then sent LSB first.

7.5.2.5

Channel status data (bit 30, SPDIF sub-frame,

C bit)

A group of C channel status bits consists of 192 bits.

Two groups of channel status bits are transmitted every

super-frame (one group for each channel) at a rate of one

bit per sub-frame. In this application, both channel status

words will be identical.

BINARY

PATTERN

DESCRIPTION

11101000

B

left sub-frame follows.

SPDIF super-frame starts.

Bit 0 of left C channel will

be sent in this subframe

11100100

W

right subframe follows

11100010

M

left subframe follows

1997 Nov 17

25

Philips Semiconductors

Preliminary specification

ISO/MPEG Audio Source Decoder

SAA2502

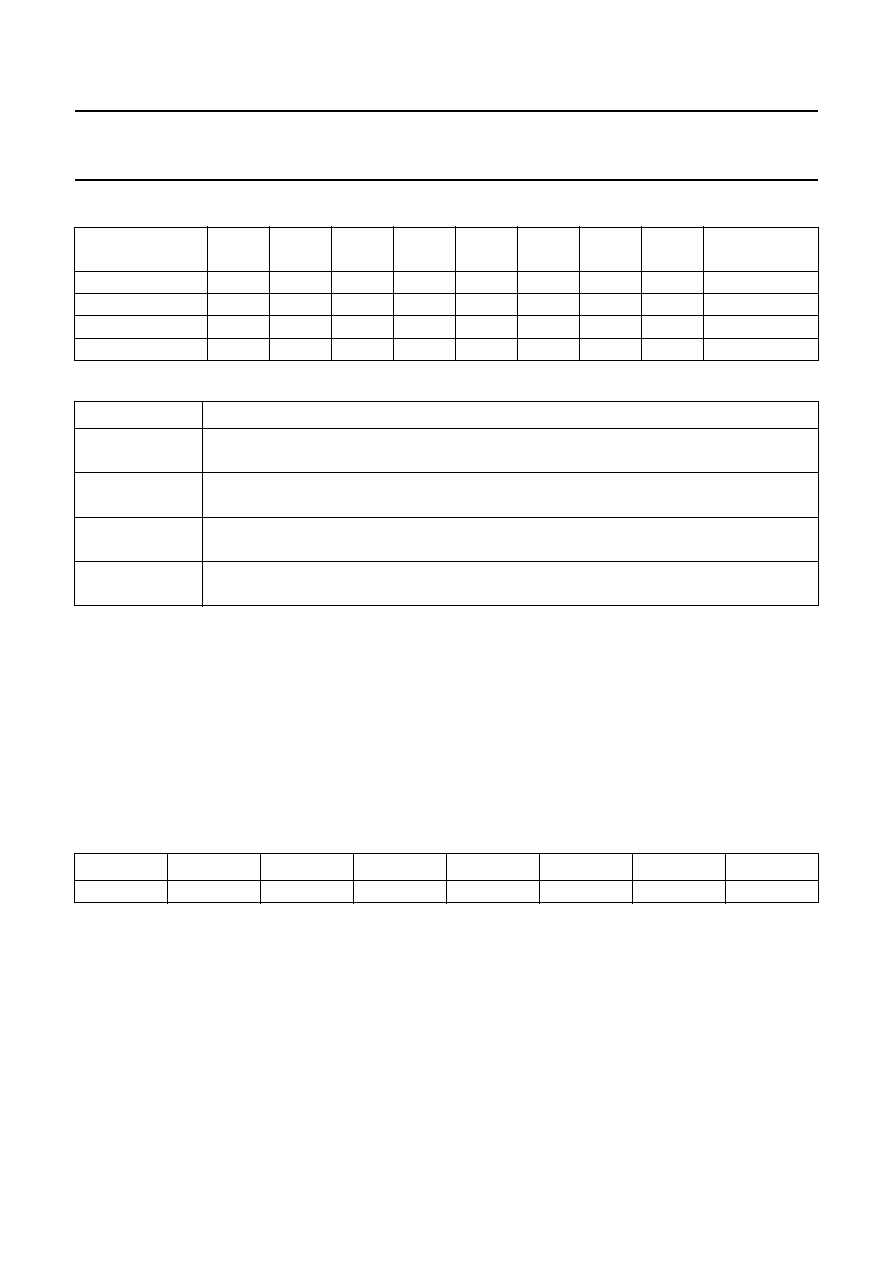

Table 15 Channel status data

Notes

1. This field is filled according to clause 4.2.2.2 of the SPDIF standard `Channel status data format for digital audio

equipment for consumer use' (mode 0).

2. The low sample frequencies of MPEG2 are not defined yet. In order to be able to follow future standardization, the

code sent for the three remaining sampling frequencies (24, 22.05 and 16 kHz) is programmable through the

controller interface.

3. The remaining 162 bits of each channel status word will all be logic 0. Individual bits of the status channel will be sent

bit 0 first.

DESCRIPTION

BITS

FIELD

INDICATION

Control field; note 1

0

0

indicates consumer use

1

0

logic 1 reserved for digital data and further

standardization

2

C

logic 0 = copy prohibited; logic 1 = copy permitted

3 and 4

00

no pre-emphasis (SAA2502 has automatic

de-emphasis)

5

0

2 channel audio data

6 and 7

00

mode 0 indication

Category code

8 to 15

00000000

2 channel

Source number

16 to 19

0000

don't care

Channel number

20 to 23

0000

don't care

Sample frequency;

note 2

24 to 27

field filled in accordance with clause 4.2.2.2 of the SPDIF standard:

0100 = 48 kHz

0000 = 44.1 kHz

1100 = 32 kHz

Clock accuracy; note 3

28 and 29

field filled in accordance with clause 4.2.2.2 of the SPDIF standard:

00= level II (normal accuracy of 0.1%)

7.5.2.6

Parity (bit 31, SPDIF sub-frame, P bit)

Even parity is generated on the 28 sub-frame data bits

(4 to 31) in bit 31.

7.5.2.7

SPDIF control

The SPDIF interface will be controlled by the

microcontroller via the control interface. The V bit is copied

into each SPDIF subframe (once for each data sample).

The C bit is inserted twice per SPDIF super-frame into the

channel status data (bit 2 in each C channel). The user

byte is inserted into the user channel (preceded by a start

bit) immediately after reception through the control

interface, otherwise the user channel is filled with logic 0s.

Table 16 SPDIF interface control

7.5.2.8

Channel status

The sampling frequency bits (bits 24 to 27) are derived

from the sampling frequency index bits of the input data

stream

7.5.2.9

User data

Only single 8 bit messages are sent. Individual messages

should be time separated far enough to insert at least

9 logic 0s in between (for easy synchronization at the

receiver end at random entry points in the stream).

BIT/BYTE

DEFAULT

RESULT

V bit

default = logic 0

valid audio data

C bit

default = logic 1

digital copy permitted

U byte

uuuuuuuu

8 bits user byte

1997 Nov 17

26

Philips Semiconductors

Preliminary specification

ISO/MPEG Audio Source Decoder

SAA2502

7.5.3

B

IT SERIAL ANALOG OUTPUT

In order to serve applications which require low to medium

performance stereo audio output, two bit serial analog

outputs are provided (one for each channel). The on-chip

DACs each consist of three functional blocks in series:

∑

4

◊

f

s

up-sampling filter

∑

AC and DC dithering block

∑

N

◊

f

s

noise shaper; see Table 17.

Table 17 Value of N for N

◊

f

s

noise shaper

MODE

SAMPLE

RATE

VALUES

External sample clock mode

FSC384 = 0

N = 256

FSC384 = 1

N = 384

Other clock generator modes f

s

= 48 kHz

N = 256

f

s

= 44.1 kHz

N = 256

f

s

= 32 kHz

N = 384

f

s

= 24 kHz

N = 512

f

s

= 22.05 kHz N = 512

f

s

= 16 kHz

N = 768

The two analog outputs deliver a `pulse density modulated'

signal, switching between REFN and REFP. The format is

programmable (through the control interface):

∑

Non return-to-zero format (subsequent logic 1 pulses

are merged)

∑

Return-to-zero format (subsequent logic 1 pulses are

separated by logic 0 levels).

The quality of the analog output signal depends on several

external factors:

∑

Stability and decoupling of the analog supply

∑

Absence of jitter on the sample clock

∑

Which external low-pass filter circuit is used

∑

The layout of the low-pass filter.

The recommended external low-pass filter is shown in

Fig.17. With this circuit the DACs performance is <

-

75 dB

(THD + N)/S with a 1 kHz sine wave, measured over the

bandwidth 20 Hz to 20 kHz. The amplifier in the low-pass

filter circuit is the Class AB stereo headphone driver

TDA1308.

The recommended DAC output format is non

return-to-zero, this has a better signal-to-noise ratio than

the return-to-zero format.

Fig.16 Bit serial output formats.

handbook, full pagewidth

MGE481

LFTPOS

RGTPOS

LFTNEG

RGTNEG

bit serial data

0

1

1

0

0

1

0

1

1

0

0

1

non-return-to-zero

(recommended)

return-to-zero

1997 Nov 17

27

Philips Semiconductors

Preliminary specification

ISO/MPEG Audio Source Decoder

SAA2502

handbook, full pagewidth

MBH974

220 pF

+

2.5 V

220 pF

390 pF

TDA1308T

SAA2502H

neg

pos

output

11 k

10 k

10 k

10 k

10 k

100

µ

F

11 k

10 k

Fig.17 External low-pass filters

7.6

Control interface module

7.6.1

R

ESETTING

Table 18 Resetting is performed by 2 signals

A rising edge of the signal STOP triggers the next event.

The decoding process is interrupted and the input buffer is

flushed. Consequently audio frame synchronization is

abandoned and the decoder starts searching for a new

sync in the coded input data stream. In the meantime the

output interface is soft muted (i.e. the output signal fades

away in approximately 500 samples).

There are several other events that have the same effect

as a rising edge of the STOP signal:

∑

Change of the current MPEG layer in the input stream

∑

Change of the current sampling frequency in the input

stream

∑

Change of the current bit rate in the input stream

(variable bit rate is NOT supported)

∑

Change of current input interface mode

(INMOD1 and 0) and/or audio frame synchronization

mode (SYMOD1 and 0) setting

∑

Enforcement of a soft reset through the control interface.

There is also a level triggered effect which remains

provided STOP is asserted. When the STOPRQ control

flag is set input data requesting will be halted, otherwise

normal input interface behaviour will continue at the bit rate

that was valid before STOP assertion but all data is

SIGNAL

DIRECTION

FUNCTION

STOP

input

soft reset and stop decoding

RESET

input

hard reset: force default

settings

considered to be unreliable (as if CDEF were asserted).

Consequently frame synchronization and decoding will not

resume until STOP is de-asserted.

The hard reset signal RESET has the same effect as

STOP but it will also force the control interface settings into

their default states. RESET must stay high during at least

24 MCLKIN periods if MCLK24 = logic 1 or 12 MCLKIN

periods if MCLK24 = logic 0.

7.6.2

I

NTERRUPTS

The SAA2502 is able to generate an interrupt upon the

occurrence of one or more of the following events:

∑

Status bit DST0 has been set (i.e. ancillary/PAD data,

frame headers and error report are available)

∑

Rising edge of STOP input signal

∑

MPEG CRC check failed

∑

Status bit INSYNC has been set

∑

Status bit INSYNC has been cleared.

For more information on these items see Sections 7.6.6.1

and 7.6.6.9.

Each of these interrupts sources may be enabled or

disabled as required by the application. After a hard reset

all interrupt sources are disabled. When the host

processor is interrupted by the SAA2502 it should read the

interrupt event register to find out which event or events

caused the interrupt. Reading this register will also clear all

pending interrupts.

The interrupt pin is active LOW (INT = logic 0 indicates an