1999 Oct 27

2

Philips Semiconductors

Preliminary specification

Standard TV microcontrollers with

On-Screen Display (OSD)

SAA55xx

CONTENTS

1

FEATURES

2

GENERAL DESCRIPTION

3

QUICK REFERENCE DATA

4

ORDERING INFORMATION

5

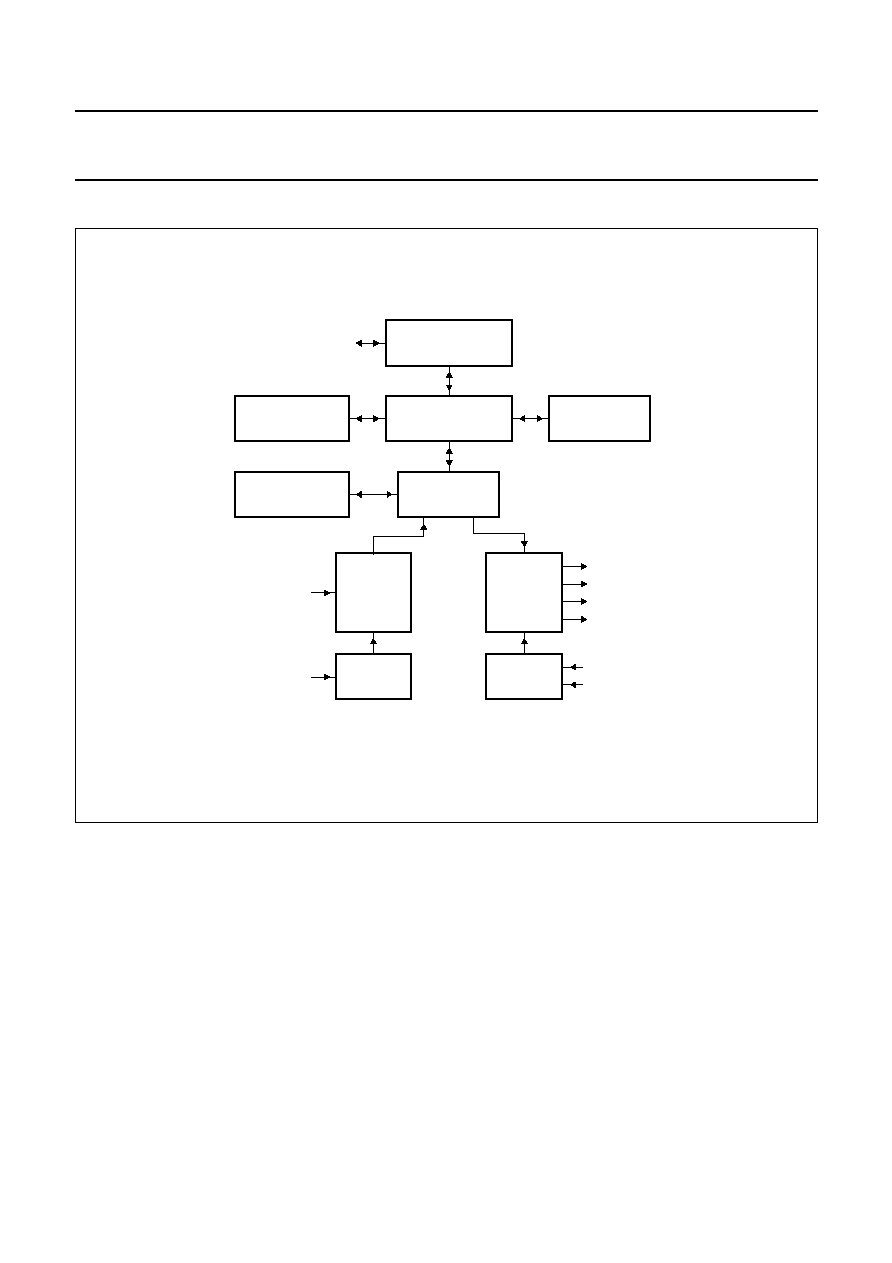

BLOCK DIAGRAM

6

PINNING INFORMATION

6.1

Pinning

6.2

Pin description

7

MICROCONTROLLER

7.1

Microcontroller features

8

MEMORY ORGANISATION

8.1

Security bits - program and verify

8.2

RAM organisation

8.3

Data memory

8.4

SFR memory

8.5

Character set feature bits

8.6

External (auxiliary) memory

9

POWER-ON RESET

10

REDUCED POWER MODES

10.1

Idle mode

10.2

Power-down mode

10.3

Standby mode

11

I/O FACILITY

11.1

I/O ports

11.2

Port type

11.3

Port alternate functions

11.4

LED support

12

INTERRUPT SYSTEM

12.1

Interrupt enable structure

12.2

Interrupt enable priority

12.3

Interrupt vector address

12.4

Level/edge interrupt

13

TIMER/COUNTER

14

WATCHDOG TIMER

14.1

Watchdog Timer operation

15

PULSE WIDTH MODULATORS

15.1

PWM control

15.2

Tuning Pulse Width Modulator (TPWM)

15.3

Software ADC (SAD)

16

I

2

C-BUS SERIAL I/O

16.1

I

2

C-bus port selection

17

MEMORY INTERFACE

17.1

Memory structure

17.2

Memory mapping

17.3

Addressing memory

17.4

Page clearing

18

DATA CAPTURE

18.1

Data Capture Features

18.2

Broadcast service data detection

18.3

VPS acquisition

18.4

WSS acquisition

19

DISPLAY

19.1

Display features

19.2

Display mode

19.3

Display feature descriptions

19.4

Character and attribute coding

19.5

Screen and global controls

19.6

Screen colour

19.7

Text display control

19.8

Display positioning

19.9

Character set

19.10

Display synchronization

19.11

Video/data switch (fast blanking) polarity

19.12

Video/data switch adjustment

19.13

RGB brightness control

19.14

Contrast reduction

20

MEMORY MAPPED REGISTERS

21

LIMITING VALUES

22

CHARACTERISTICS

22.1

I

2

C-bus characteristics

23

QUALITY AND RELIABILITY

23.1

Group A

23.2

Group B

23.3

Group C

24

APPLICATION INFORMATION

25

ELECTROMAGNETIC COMPATIBILITY

(EMC) GUIDELINES

26

PACKAGE OUTLINE

27

SOLDERING

27.1

Introduction to soldering through-hole mount

packages

27.2

Soldering by dipping or by solder wave

27.3

Manual soldering

27.4

Suitability of through-hole mount IC packages

for dipping and wave soldering methods

28

DEFINITIONS

29

LIFE SUPPORT APPLICATIONS

30

PURCHASE OF PHILIPS I

2

C COMPONENTS

1999 Oct 27

3

Philips Semiconductors

Preliminary specification

Standard TV microcontrollers with

On-Screen Display (OSD)

SAA55xx

1

FEATURES

�

Single-chip microcontroller with integrated On-Screen

Display (OSD)

�

Versions available with integrated data capture

�

One Time Programmable (OTP) memory for both

program Read Only Memory (ROM) and character sets

�

Single power supply: 3.0 to 3.6 V

�

5 V tolerant digital inputs and I/O

�

29 I/O lines via individual addressable controls

�

Programmable I/O for push-pull, open-drain and

quasi-bidirectional

�

Two port lines with 8 mA sink (at <0.4 V) capability, for

direct drive of Light Emitting Diode (LED)

�

Single crystal oscillator for microcontroller, OSD and

data capture

�

Power reduction modes: Idle and Power-down

�

Byte level I

2

C-bus with dual port I/O

�

Pin compatibility throughout family

�

Operating temperature:

-

20 to +70

�

C.

2

GENERAL DESCRIPTION

The SAA55xx standard family of microcontrollers are a

derivative of the Philips industry-standard 80C51

microcontroller, and are intended for use as the central

control mechanism in a television receiver. They provide

control functions for the television system, OSD, and some

versions include an integrated data capture and display

function.

The data capture hardware has the capability of decoding

and displaying both 525 and 625-line World System

Teletext (WST), Video Programming System (VPS) and

Wide Screen Signalling (WSS) information. The same

display hardware is used both for Teletext and OSD, which

means that the display features available give greater

flexibility to differentiate the TV set.

The SAA55xx standard family offers a range of

functionality from non-text, 16-kbyte program ROM and

256-byte Random Access Memory (RAM), to a 10-page

text version, 64-kbyte program ROM and 1.2-kbyte RAM.

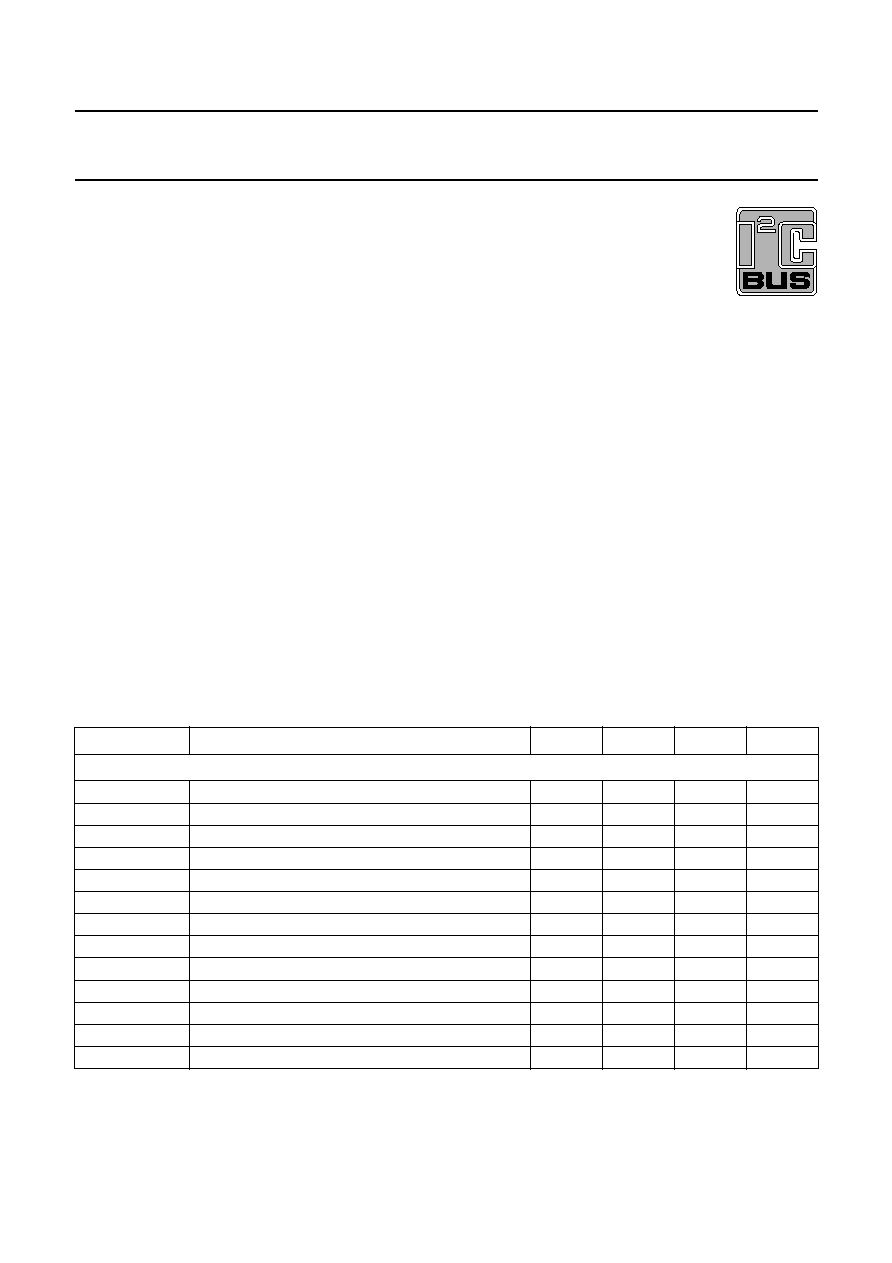

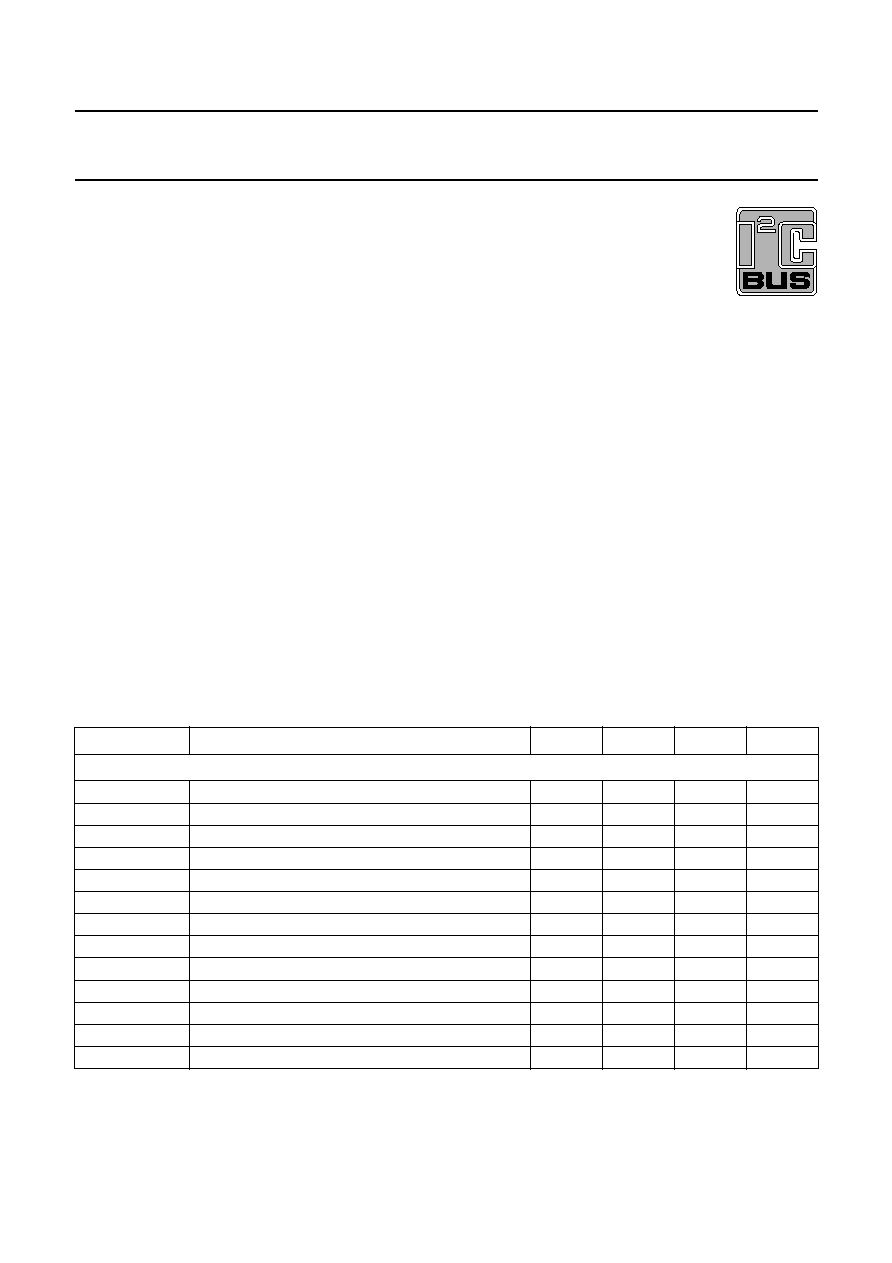

3

QUICK REFERENCE DATA

SYMBOL

PARAMETER

MIN.

TYP.

MAX.

UNIT

Supply

V

DDX

any supply voltage (V

DD

to V

SS

)

3.0

3.3

3.6

V

I

DDP

periphery supply current

1

-

-

mA

I

DDC

core supply current

-

15

18

mA

I

DDC(id)

Idle mode core supply current

-

4.6

6

mA

I

DDC(pd)

Power-down mode core supply current

-

0.76

1

mA

I

DDC(stb)

Standby mode core supply current

-

5.11

6.50

mA

I

DDA

analog supply current

-

45

48

mA

I

DDA(id)

Idle mode analog supply current

-

0.87

1.0

mA

I

DDA(pd)

Power-down mode analog supply current

-

0.45

0.7

mA

I

DDA(stb)

Standby mode analog supply current

-

0.95

1.20

mA

f

xtal

crystal frequency

-

12

-

MHz

T

amb

operating ambient temperature

-

20

-

+70

�

C

T

stg

storage temperature

-

55

-

+125

�

C

1999 Oct 27

4

Philips Semiconductors

Preliminary specification

Standard TV microcontrollers with

On-Screen Display (OSD)

SAA55xx

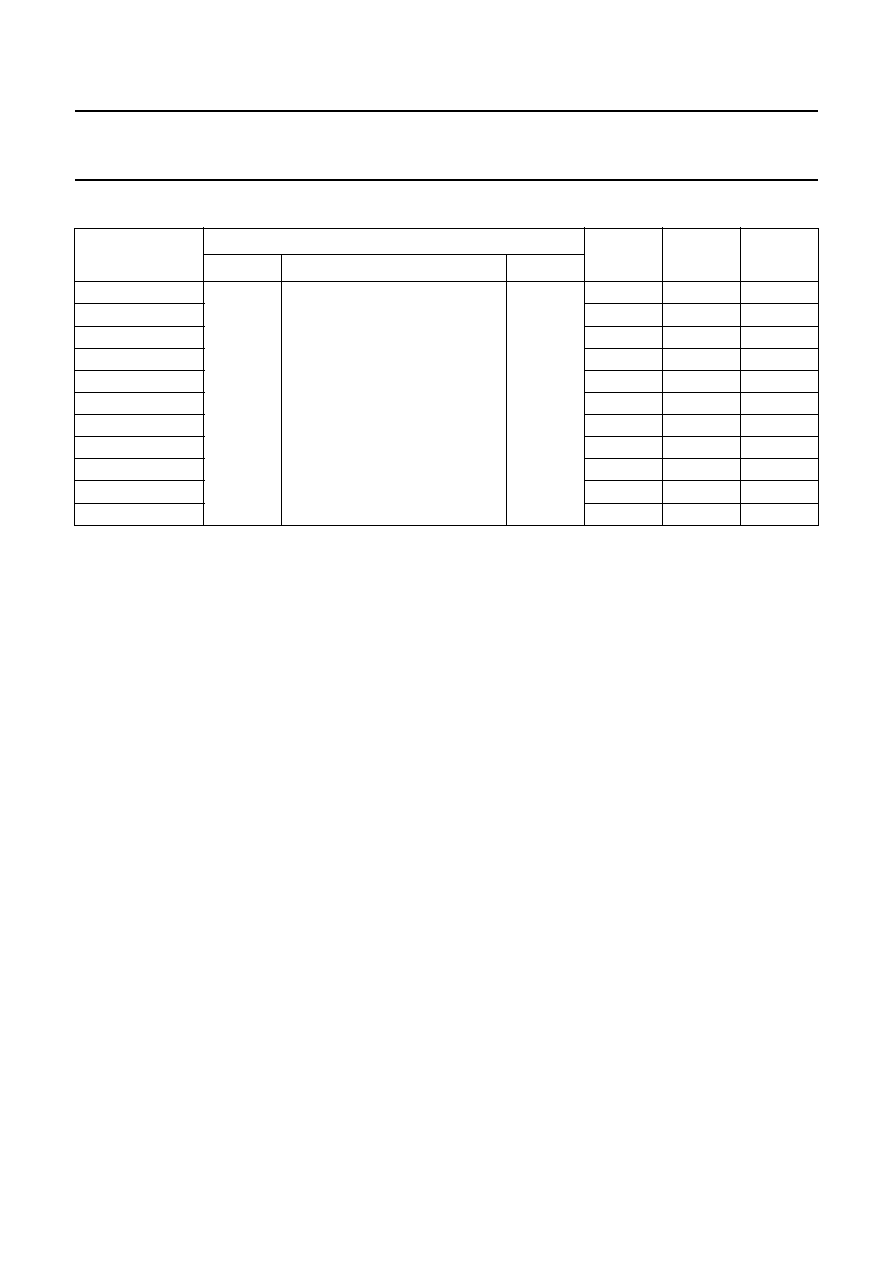

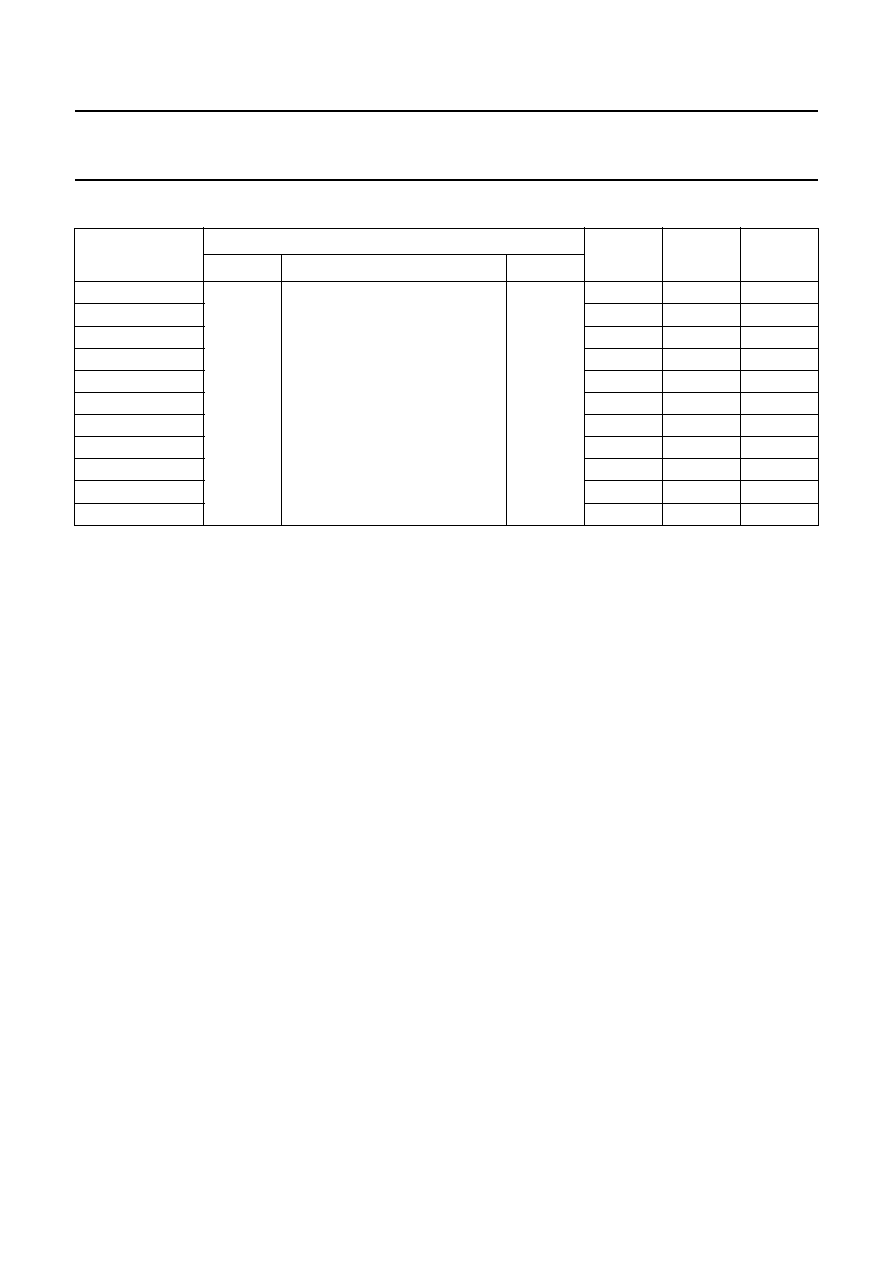

4

ORDERING INFORMATION

Notes

1. `nnnn' is a four digit number uniquely referencing the microcontroller program mask.

2. For details of the LQFP100 package, please contact your local regional office for availability.

TYPE NUMBER

(1)

PACKAGE

(2)

ROM

RAM

TEXT

PAGES

NAME

DESCRIPTION

VERSION

SAA5500PS/nnnn

SDIP52

plastic shrink dual in-line package;

52 leads (600 mil)

SOT247-1

16-kbyte

256-byte

-

SAA5501PS/nnnn

32-kbyte

512-byte

-

SAA5502PS/nnnn

48-kbyte

256-byte

-

SAA5503PS/nnnn

64-kbyte

512-byte

-

SAA5520PS/nnnn

16-kbyte

256-byte

1

SAA5521PS/nnnn

32-kbyte

512-byte

1

SAA5522PS/nnnn

48-kbyte

750-byte

1

SAA5523PS/nnnn

64-kbyte

1-kbyte

1

SAA5551PS/nnnn

32-kbyte

750-byte

10

SAA5552PS/nnnn

48-kbyte

1-kbyte

10

SAA5553PS/nnnn

64-kbyte

1.2-kbyte

10