1998 Apr 09

2

Philips Semiconductors

Product specification

Multimedia bridge, high performance

Scaler and PCI circuit (SPCI)

SAA7146A

CONTENTS

1

FEATURES

1.1

Video processing

1.2

Audio processing

1.3

Scaling

1.4

Interfacing

1.5

General

2

GENERAL DESCRIPTION

3

QUICK REFERENCE DATA

4

ORDERING INFORMATION

5

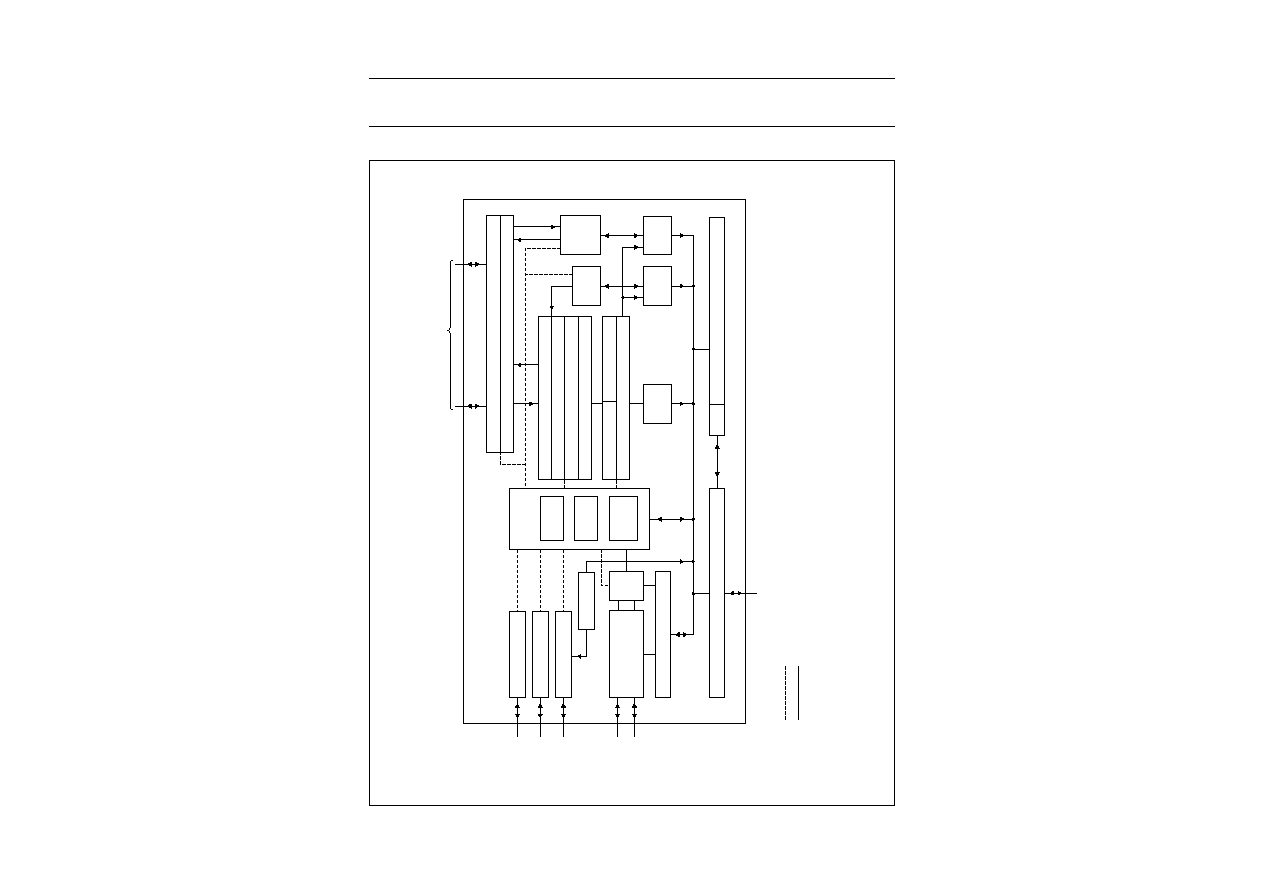

BLOCK DIAGRAM

6

PINNING

7

FUNCTIONAL DESCRIPTION

7.1

General

7.2

PCI interface

7.3

Main control

7.4

Register Programming Sequencer (RPS)

7.5

Status and interrupts

7.6

General Purpose Inputs/Outputs (GPIO)

7.7

Event counter

7.8

Video processing

7.9

High Performance Scaler (HPS)

7.10

Binary Ratio Scaler (BRS)

7.11

Video data formats on the PCI-bus

7.12

Scaler register

7.13

Scaler event description

7.14

Clipping

7.15

Data Expansion Bus Interface (DEBI)

7.16

Audio interface

7.17

I

2

C-bus interface

7.18

SAA7146A register tables

8

BOUNDARY SCAN TEST

8.1

Initialization of boundary scan circuit

8.2

Device identification codes

9

ELECTRICAL OPERATING CONDITIONS

10

CHARACTERISTICS

11

APPLICATION EXAMPLE

12

PACKAGE OUTLINES

13

SOLDERING

13.1

Introduction

13.2

Reflow soldering

13.3

Wave soldering

13.4

Repairing soldered joints

14

DEFINITIONS

15

LIFE SUPPORT APPLICATIONS

16

PURCHASE OF PHILIPS I

2

C COMPONENTS

1998 Apr 09

3

Philips Semiconductors

Product specification

Multimedia bridge, high performance

Scaler and PCI circuit (SPCI)

SAA7146A

1

FEATURES

1.1

Video processing

�

Full size, full speed video delivery to and from the frame

buffer or virtual system memory enables various

processing possibilities for any external PCI device

�

Full bandwidth PCI-bus master write and read (up to

132 Mbytes/s)

�

Virtual memory support (4 Mbytes per DMA channel)

�

Processing of maximum 4095 active samples per line

and maximum 4095 lines per frame

�

Vanity picture (mirror) for video phone and video

conferencing applications

�

Video flip (upside down picture)

�

Colour space conversion with gamma correction for

different kinds of displays

�

Chroma Key generation and utilization

�

Pixel dithering for low resolution video output formats

�

Brightness, contrast and saturation control

�

Video and Vertical Blanking Interval (VBI) synchronized

programming of internal registers with Register

Programming Sequencer (RPS), ability to control two

asynchronous data streams simultaneously

�

Memory Management Unit (MMU) supports virtual

demand paging memory management (Windows, Unix,

etc.)

�

Rectangular clipping of frame buffer areas minimizes

PCI-bus load

�

Random shape mask clipping protects selectable areas

of frame buffer

�

3

�

128 Dword video FIFO with overflow detection and

`graceful' recovery.

1.2

Audio processing

�

Time Slot List (TSL) processing for flexible control of

audio frames up to 256 bits on 2 asynchronous

bidirectional digital audio interfaces simultaneously

(4 DMA channels)

�

Video synchronous audio capture, e.g. for sound cards

�

Various synchronization modes to support I

2

S and other

different audio and DSP data formats

�

Audio input level monitoring enables peak control via

software

�

Programmable bit clock generation for master and slave

applications.

1.3

Scaling

�

Scaling of video pictures down to randomly sized

windows (vertical down to 1 : 1024; horizontal down to

1 : 256)

�

High Performance Scaler (HPS) offers two-dimensional,

phase correct data processing for improved signal

quality of scaled video data, especially for compression

applications

�

Horizontal and vertical FIR filters with up to 65 taps

�

Horizontal upscaling (zoom) supports e.g. CCIR to

square pixel conversion

�

Additional Binary Ratio Scaler (BRS) supports CIF and

QCIF formats, especially for video phone and video

conferencing.

1.4

Interfacing

�

Dual D1 (8-bit, CCIR 656) video I/O interface

�

DMSD2 compatible (16-bit YUV) video input interface

�

Supports various packed (pixel dithering) and planar

video output formats

�

Data Expansion Bus Interface (DEBI) for interfacing with

e.g. MPEG or JPEG decoders with Intel (ISA like) and

Motorola (68000 like) protocol style, capability for

immediate and block mode (DMA) transfers with up to

23 Mbytes/s peak data rate

�

5 digital audio I/O ports

�

4 independent user configurable General Purpose I/O

Ports (GPI/O) for interrupt and status processing

�

PCI interface (release 2.1)

�

I

2

C-bus interface (bus master).

1998 Apr 09

4

Philips Semiconductors

Product specification

Multimedia bridge, high performance

Scaler and PCI circuit (SPCI)

SAA7146A

1.5

General

�

Subsystem (board) vendor ID support for board

identification via software driver

�

Internal arbitration control

�

Diagnostic support and event analysis

�

Programmable Vertical Blanking Interval (VBI) data

region for e.g. to support INTERCAST, teletext, closed

caption and similar applications

�

3.3 V supply enables reduced power consumption, 5 V

tolerant I/Os for 5 V PCI signalling environment.

2

GENERAL DESCRIPTION

The SAA7146A, Multimedia PCI-bridge, is a highly

integrated circuit for DeskTop Video (DTV) applications.

The device provides a number of interface ports that

enable a wide variety of video and audio ICs to be

connected to the PCI-bus thus supporting a number of

video applications in a PC. One example of the application

capabilities is shown in Fig.49.

Figure 1 shows the various interface ports and the main

internal function blocks.

3

QUICK REFERENCE DATA

4

ORDERING INFORMATION

SYMBOL

PARAMETER

MIN.

TYP.

MAX.

UNIT

V

DDD

digital supply voltage

3.0

3.3

3.6

V

I

DDD(tot)

total digital supply current

-

400

-

mA

V

i

; V

o

data input/output levels

TTL compatible

f

LLC

LLC input clock frequency

-

-

32

MHz

f

PCI

PCI input clock frequency

-

-

33

MHz

f

I2S

I

2

S input clock frequency

-

-

12.5

MHz

T

amb

operating ambient temperature

0

-

70

�

C

TYPE NUMBER

PACKAGE

NAME

DESCRIPTION

VERSION

SAA7146AH

QFP160

plastic quad flat package; 160 leads (lead length 1.95 mm);

body 28

�

28

�

3.4 mm; high stand-off height

SOT322-1

SAA7146AHZ

SQFP208

plastic shrink quad flat package; 208 leads (lead length 1.3 mm);

body 28

�

28

�

3.4 mm

SOT316-1

1998

Apr

09

5

Philips Semiconductors

Product specification

Multimedia bridge, high performance

Scaler and PCI circuit (SPCI)

SAA7146A

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

5

BLOCK DIAGRAM

o

k, full pagewidth

MHB044

GPIO PORT

I/O

RPS

SAA7146A

TASK 1

COLOUR SPACE CV. GAMMA CORRECTION

PIXEL-FORMATTER/DITHER

TASK 2

EVENT

MANAGER

I

2

C-BUS MASTER

control

data

I

2

C-bus

I

2

S1-bus

I

2

S2-bus

DEBI PORT

Intel/

Motorola

DEBI FIFO

AUDIO FIFO

PCI INTERFACE

PCI BUS

DMA AND INTERNAL ARBITRATION CONTROLLER

MMU

TSL

AUDIO INPUT/OUTPUT

AUDIO INPUT/OUTPUT

VIDEO

FIFO1

VIDEO

FIFO2

CLIPPING

UNIT

BINARY

RATIO

SCALER

VIDEO

FIFO3

8-BIT D1 INPUT/OUTPUT

8-BIT D1 INPUT/OUTPUT

REAL TIME VIDEO INTERFACE

Dual D1 or 16-bit YUV

16-BIT YUV IN

HIGH PERFORMANCE SCALER

H-FILTER/SCALER

V-FILTER/SCALER

YUV/RGB

YUV

YUV

YUV

VIDEO-FLIP/MIRROR

Fig.1 Block diagram.