| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: TDA4887PS | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Document Outline

- 1 FEATURES

- 2 GENERAL DESCRIPTION

- 3 ORDERING INFORMATION

- 4 QUICK REFERENCE DATA

- 5 BLOCK DIAGRAM

- 6 PINNING

- 7 FUNCTIONAL DESCRIPTION

- 8 LIMITING VALUES

- 9 THERMAL CHARACTERISTICS

- 10 CHARACTERISTICS

- 11 I 2 C-BUS PROTOCOL

- 12 TEST AND APPLICATION INFORMATION

- 13 INTERNAL CIRCUITRY

- 14 PACKAGE OUTLINE

- 15 SOLDERING

- 16 DATA SHEET STATUS

- 17 DEFINITIONS

- 18 DISCLAIMERS

- 19 PURCHASE OF PHILIPS I 2 C COMPONENTS

DATA SHEET

Product specification

File under Integrated Circuits, IC02

2001 Oct 19

INTEGRATED CIRCUITS

TDA4887PS

160 MHz bus-controlled monitor

video preamplifier

2001 Oct 19

2

Philips Semiconductors

Product specification

160 MHz bus-controlled monitor video

preamplifier

TDA4887PS

CONTENTS

1

FEATURES

2

GENERAL DESCRIPTION

3

ORDERING INFORMATION

4

QUICK REFERENCE DATA

5

BLOCK DIAGRAM

6

PINNING

7

FUNCTIONAL DESCRIPTION

7.1

Signal input stage

7.2

Electronic potentiometer stages

7.3

Output stage

7.4

Pedestal blanking

7.5

Output clamping and feedback references

7.6

Clamping and blanking pulses

7.7

On Screen Display insertion and OSD contrast

7.8

Subcontrast adjustment, contrast modulation

and beam current limiting

7.9

I

2

C-bus control

7.10

I

2

C-bus data buffer

8

LIMITING VALUES

9

THERMAL CHARACTERISTICS

10

CHARACTERISTICS

11

I

2

C-BUS PROTOCOL

12

TEST AND APPLICATION INFORMATION

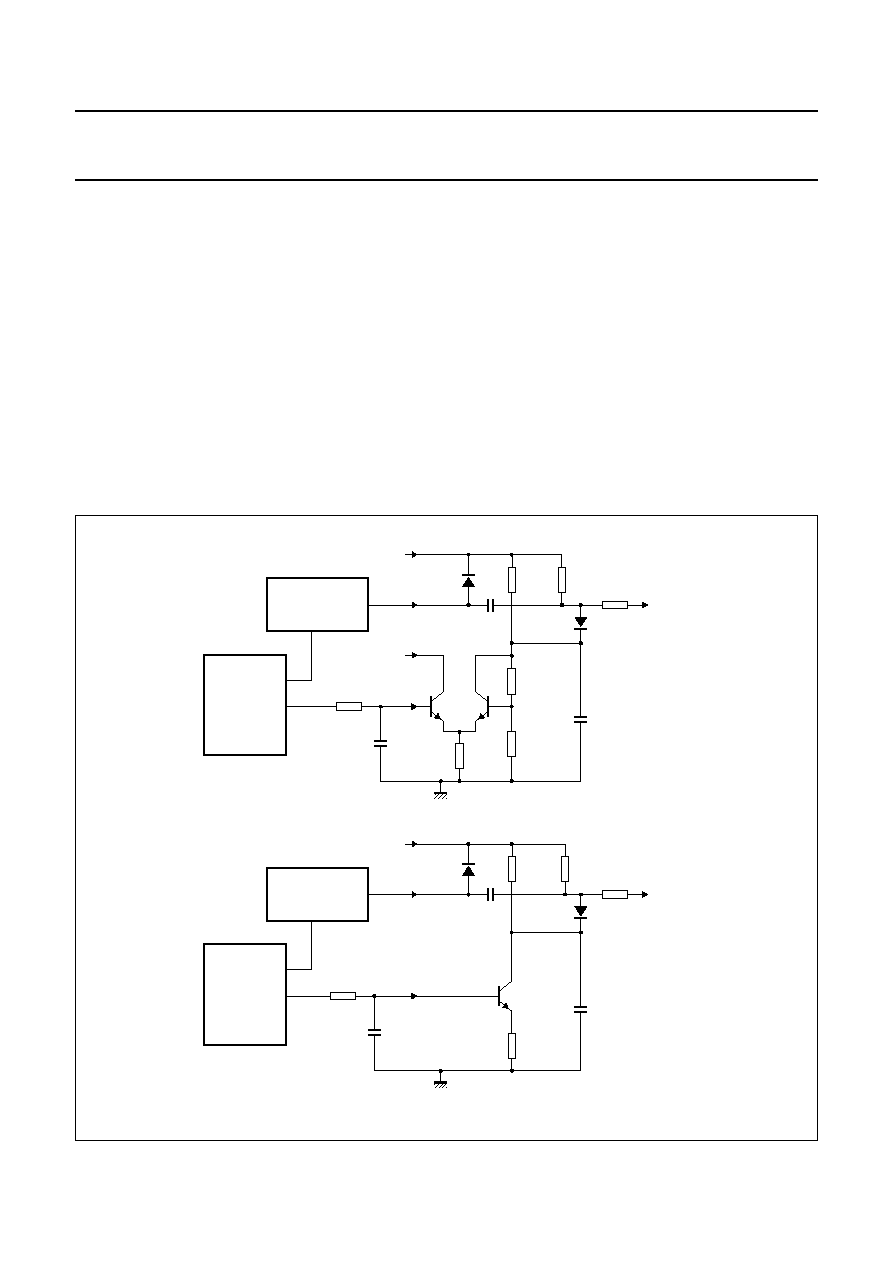

12.1

Test board

12.2

Application board with monolithic post amplifier

12.3

Building the application board

12.4

Application hints

13

INTERNAL CIRCUITRY

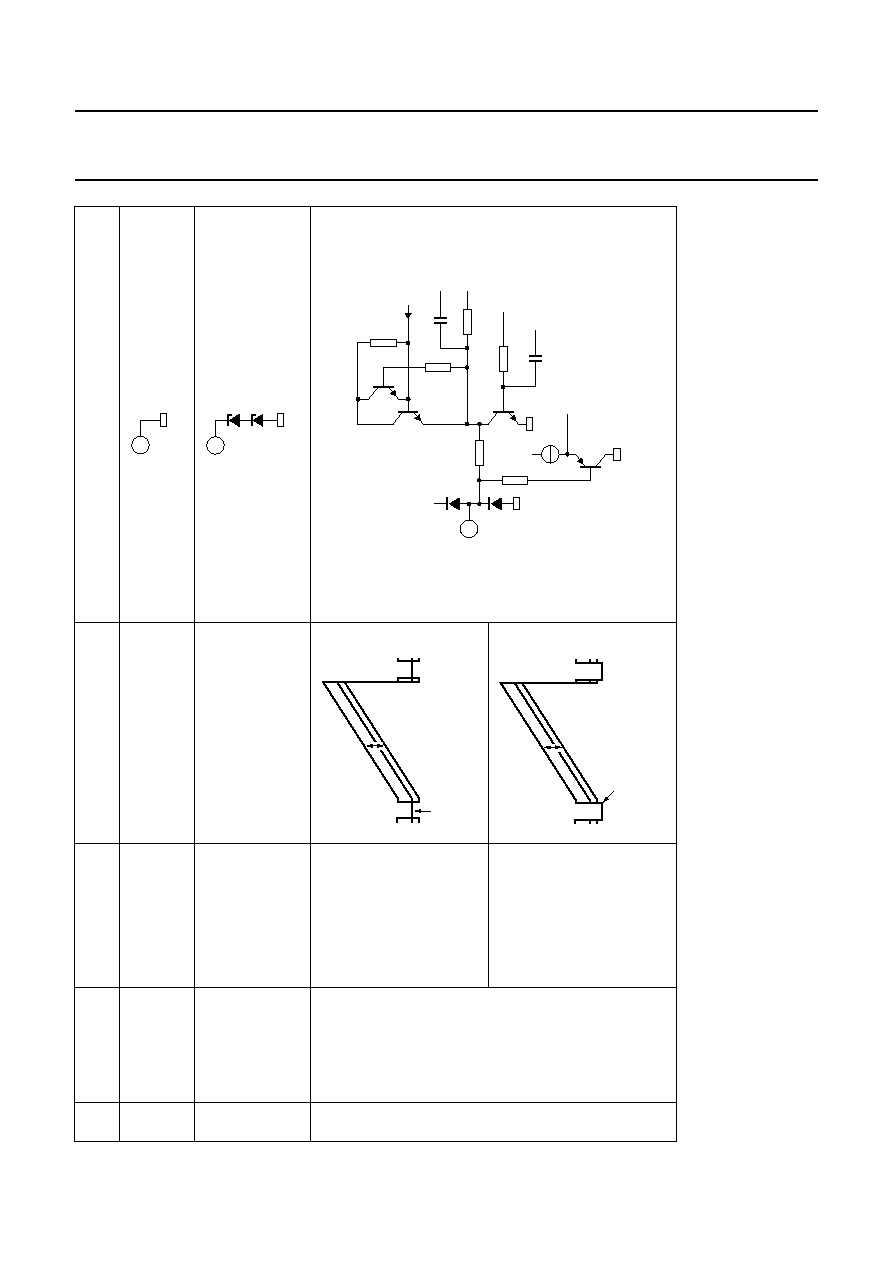

14

PACKAGE OUTLINE

15

SOLDERING

15.1

Introduction to soldering through-hole mount

packages

15.2

Soldering by dipping or by solder wave

15.3

Manual soldering

15.4

Suitability of through-hole mount IC packages

for dipping and wave soldering methods

16

DATA SHEET STATUS

17

DEFINITIONS

18

DISCLAIMERS

19

PURCHASE OF PHILIPS I

2

C COMPONENTS

2001 Oct 19

3

Philips Semiconductors

Product specification

160 MHz bus-controlled monitor video

preamplifier

TDA4887PS

1

FEATURES

∑

160 MHz pixel rate

∑

2.7 ns rise time, 3.6 ns fall time

∑

I

2

C-bus control

∑

I

2

C-bus data buffer for synchronization of adjustments

∑

8-bit Digital-to-Analog Converters (DACs)

∑

200 ns input clamping pulse

∑

4.6 V (p-p) output signal

∑

Brightness control with grey scale tracking for

user-friendly performance (4 dB more than TDA4885

and TDA4886)

∑

Brightness control without grey scale tracking for easy

alignment

∑

On Screen Display (OSD) mixing with 50 MHz pixel rate

∑

OSD contrast

∑

Negative feedback for DC-coupled cathodes

∑

Especially for AC-coupled cathodes

≠ Bus controlled black level adaptable to post amplifier

type

≠ Internal positive feedback

≠ DAC outputs for black level restoration

∑

Integrated black level storage capacitors

∑

Beam current limiting

∑

Subcontrast/contrast modulation

∑

Adjustable pedestal blanking

∑

Sync clipping.

2

GENERAL DESCRIPTION

The TDA4887PS is a monolithic integrated RGB

preamplifier for colour monitor systems (e.g. 15" and 17")

with I

2

C-bus control and OSD. In addition to bus control,

beam current limiting and contrast modulation are

possible. The IC offers brightness control with or without

grey scale tracking for easy alignment. The signals are

amplified to drive commonly used video modules or

discrete solutions. A choice can be made between

individual black level control with negative feedback from

the cathode (DC coupling), or black level control with

positive feedback and three DAC outputs for external

cut-off control (AC coupling).

The circuit can be used with special advantages in

conjunction with the TDA485x monitor deflection IC family.

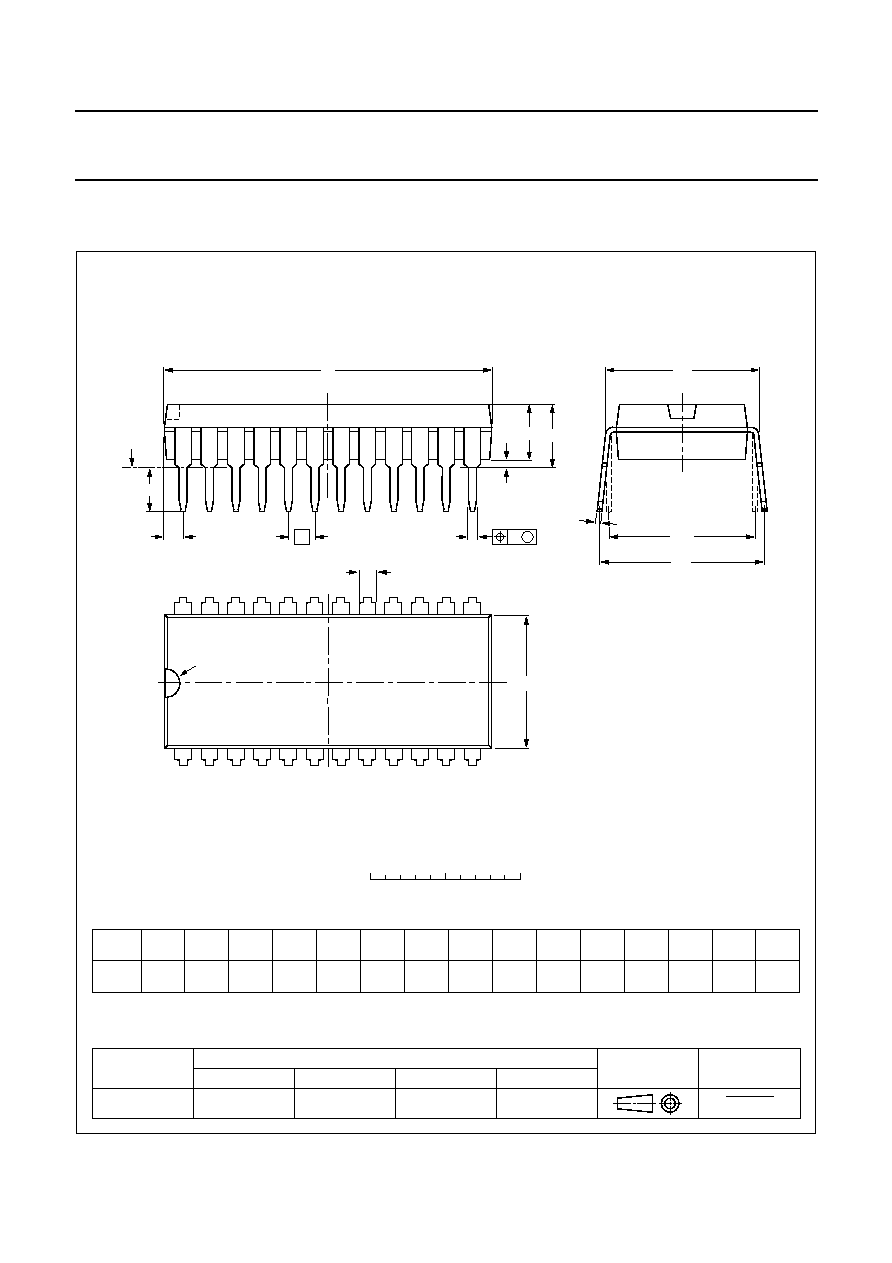

3

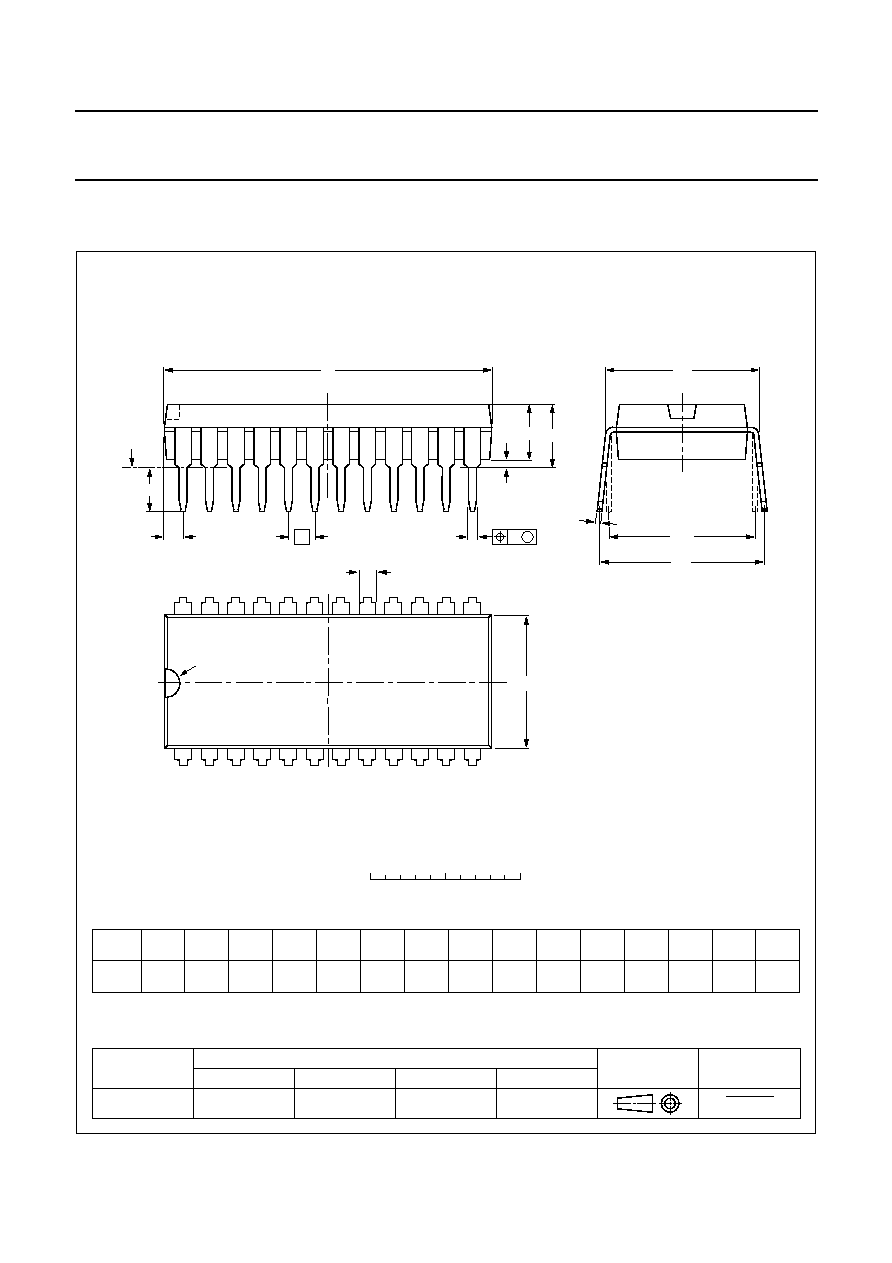

ORDERING INFORMATION

TYPE NUMBER

PACKAGE

NAME

DESCRIPTION

VERSION

TDA4887PS

SDIP24

plastic shrink dual in-line package; 24 leads (400 mil)

SOT234-1

2001 Oct 19

4

Philips Semiconductors

Product specification

160 MHz bus-controlled monitor video

preamplifier

TDA4887PS

4

QUICK REFERENCE DATA

SYMBOL

PARAMETER

CONDITIONS

MIN.

TYP.

MAX.

UNIT

V

P

supply voltage (pin 7)

7.6

8.0

8.8

V

I

P

supply current (pin 7)

-

25

30

mA

V

P(n)

supply voltage; channels 1, 2 and 3

(pins 21, 18 and 15)

7.6

8.0

8.8

V

I

P(n)

supply current; channels 1, 2 and 3

(pins 21, 18 and 15)

-

20

25

mA

V

i(n)(b-w)

input voltage; channels 1, 2 and 3

(pins 6, 8 and 10) (black-to-white value)

-

0.7

1.0

V

V

o(n)(b-w)(max)

maximum output voltage swing

(black-to-white value); channels 1,

2 and 3 (pins 22, 19 and 16)

maximum contrast;

maximum gain;

V

i(n)(b-w)

= 0.7 V; R

L

= 2 k

4.2

4.6

4.9

V

V

o(n)

output voltage level (pins 22,

19 and 16)

0.1

-

V

P(n)

-

1

V

I

o(n)(source)(M)

peak output source current

(pins 22, 19 and 16)

during fast positive signal

transients

-

40

-

-

mA

I

o(n)(sink)(M)

peak output sink current

(pins 22, 19 and 16)

during fast negative signal

transients

-

-

20

mA

V

bl(n)(ref)

black level reference voltage

(pins 22, 19 and 16)

typical values

DC coupling

control bit FPOL = 0

0.5

-

2.0

V

AC coupling

control bit FPOL = 1;

no pedestal blanking

0.53

-

1.89

V

t

r(n)

rise time of fast transients at signal

outputs (pins 22, 19 and 16)

-

2.7

-

ns

t

f(n)

fall time of fast transients at signal

outputs (pins 22, 19 and 16)

-

3.6

-

ns

V

o(n)

overshoot/undershoot at signal outputs

(pins 22, 19 and 16)

input rise/fall times = 1 ns;

maximum colour signal

-

-

10

%

ct(f)

crosstalk suppression by frequency

f = 50 MHz

25

-

-

dB

C

contrast control: colour signal related to

maximum colour signal

-

45

-

0

dB

G

track

tracking of output colour signals of

channels 1, 2 and 3

contrast control from

maximum to minimum

-

0

0.5

dB

G

gain control related to maximum gain

-

13.5

-

0

dB

V

bl(n)

brightness control (difference between

video black level and reference black

level at signal outputs related to

maximum colour signal)

control bit BRI = 0

-

10

-

+33

%

V

DA(n)

brightness control range (DAC output

voltages for AC coupling or internal

feedback reference voltage for DC

coupling)

from maximum to

minimum; control bit

BRI = 1

-

1.4

-

0

V

2001 Oct 19

5

Philips Semiconductors

Product specification

160 MHz bus-controlled monitor video

preamplifier

TDA4887PS

V

FB/Rn

DAC output voltage range without

brightness control (for black level

restoration) (pins 23, 20 and 17)

control bit FPOL = 1;

control bit BRI = 0

3.95

-

5.75

V

V

OSDn(max)

maximum OSD colour signal related to

maximum colour signal

(pins 22, 19 and 16)

maximum OSD contrast;

maximum gain

-

96

-

%

OC

OSD colour signal related to maximum

OSD colour signal

OSD contrast control from

maximum to minimum

-

12

-

0

dB

SYMBOL

PARAMETER

CONDITIONS

MIN.

TYP.

MAX.

UNIT

2001

Oct

19

6

Philips Semiconductors

Product specification

160 MHz b

us-controlled monitor video

preamplifier

TD

A4887PS

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

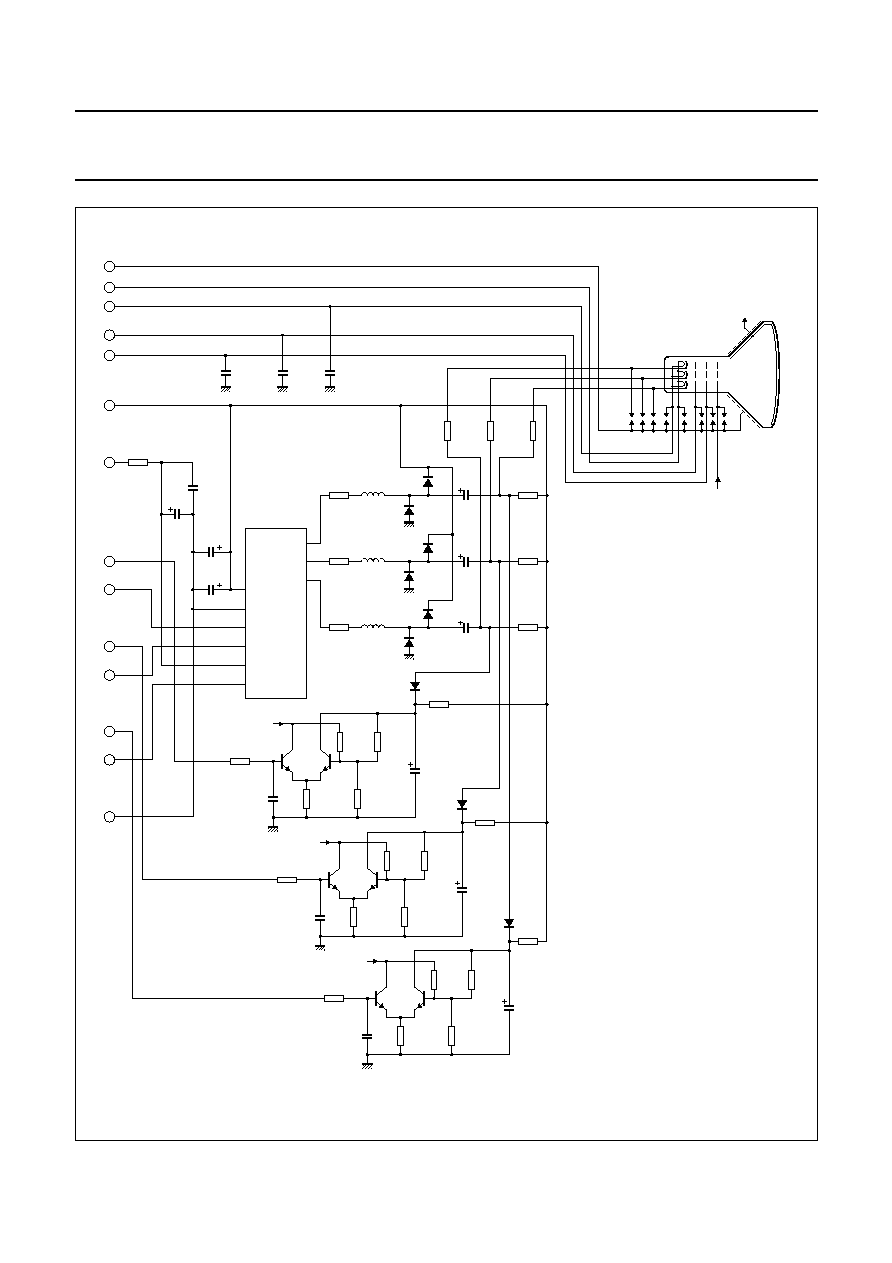

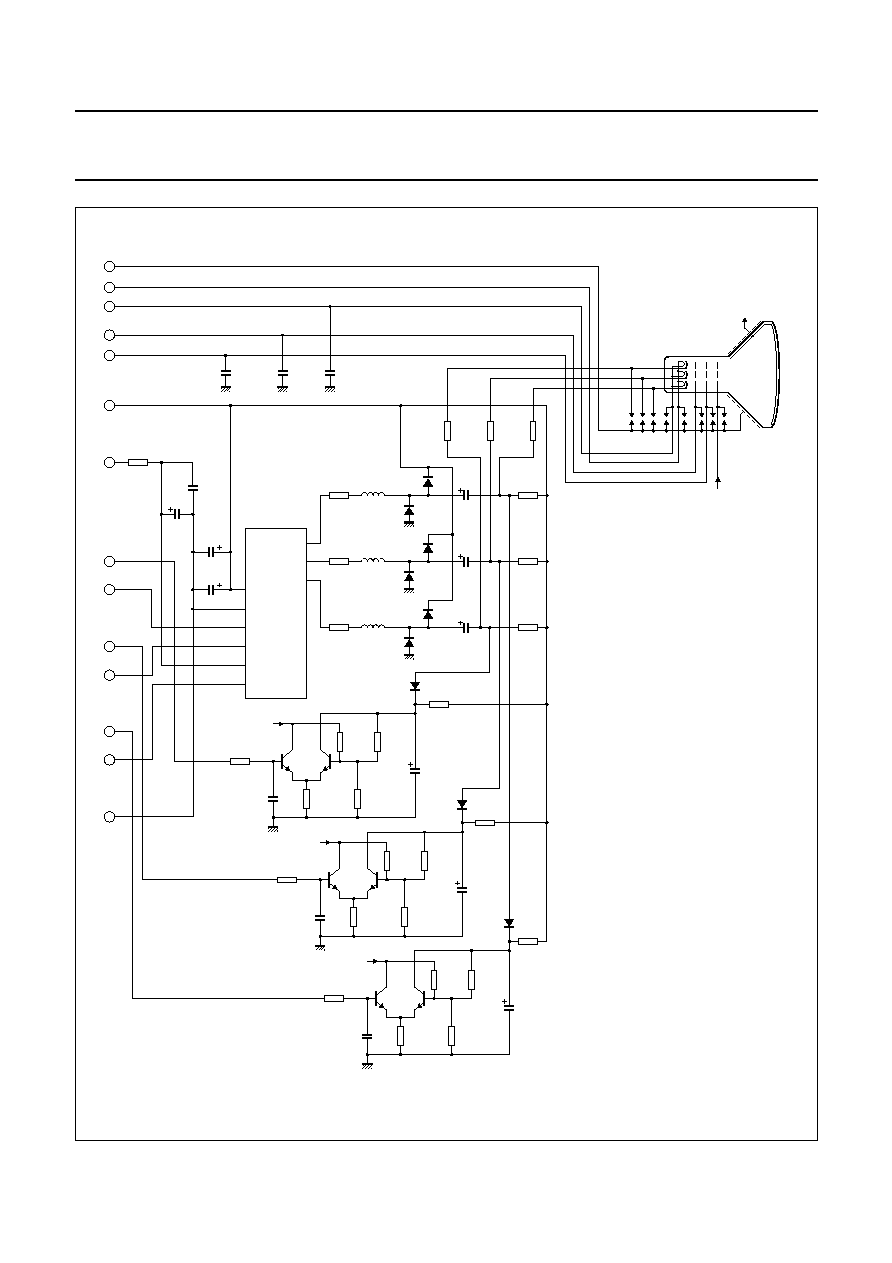

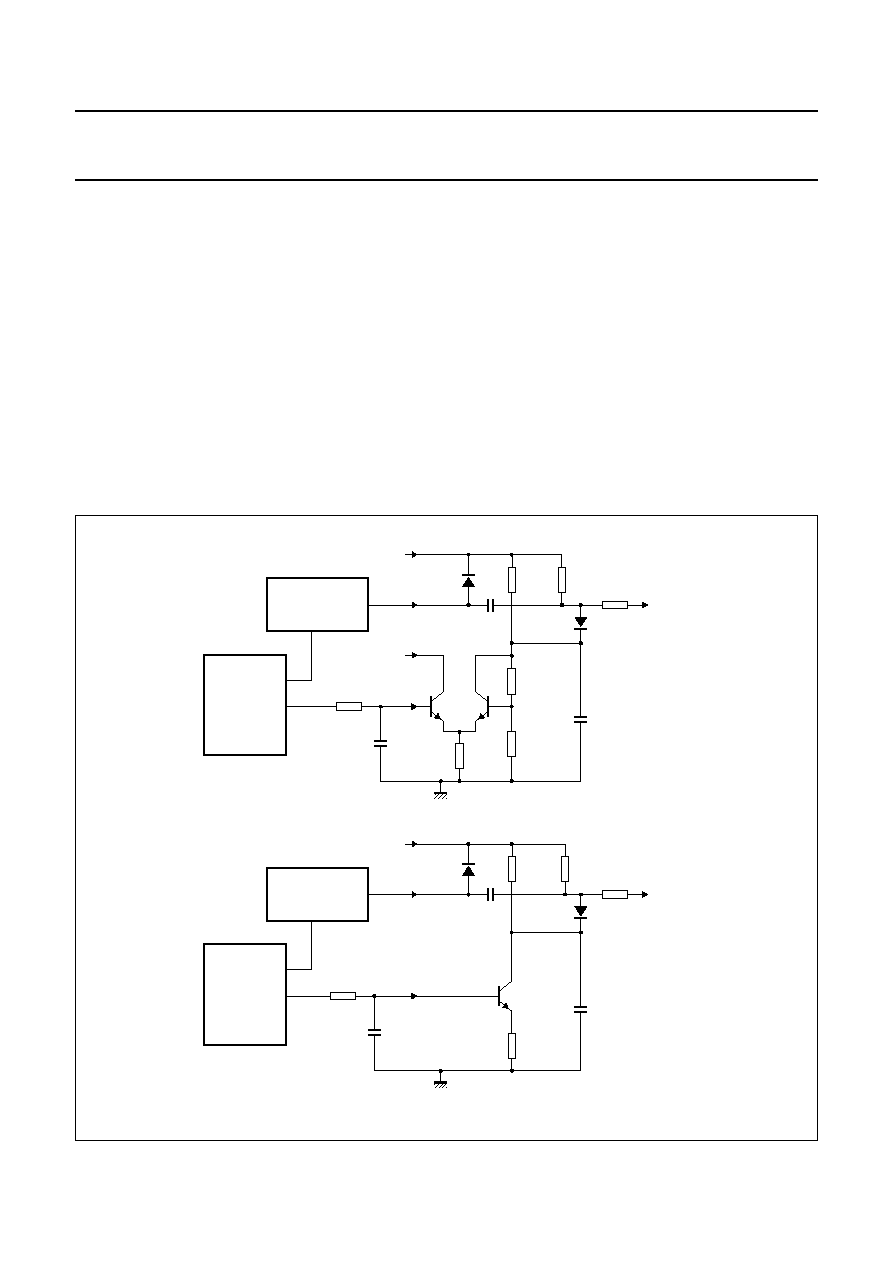

5

BLOCK DIA

GRAM

b

ook, full pagewidth

MHB943

INPUT

CLAMPING

BLANKING

INPUT

CLAMPING

BLANKING

INPUT

CLAMPING

BLANKING

CONTRAST

LIM

VI2

VI3

DISO

DISV

FPOL

BRI

CONTRAST

CONTRAST

REGISTER

I

2

C-BUS

12

13

SDA

SCL

24

VI1

6

8

10

SUBCONTRAST

CONTRAST MODULATION

LIMITING

OSD

CONTRAST

OSD

CONTRAST

OSD

CONTRAST

4

8-BIT

DAC

4-BIT

DAC

8

4

8

8

8

8

DISO

1

2

3

4

FBL OSD1 OSD2 OSD3

fast

blanking

OSD INPUT

input clamping

CHANNEL 1

REFERENCE

BRIGHTNESS

SWITCH

AC BLACK

LEVEL

BRIGHTNESS

GAIN

GAIN

GAIN

BRIGHTNESS

BRIGHTNESS

BRIGHTNESS

BLANKING

8-BIT

DAC

8-BIT

DAC

8-BIT

DAC

8-BIT

DAC

2

2-BIT

DAC

3

8

8

3-BIT

DAC

8-BIT

DAC

8-BIT

DAC

8

8-BIT

DAC

7

9

GND

SUPPLY

VP

5

11

INPUT CLAMPING

VERTICAL BLANKING

BLANKING

OUTPUT CLAMPING

PEDESTAL

BLANKING

PEDESTAL

BLANKING

PEDESTAL

BLANKING

HFB

CLI

DISV

FB/R3

VP3

VO3

GNDX

15

16

14

17

FB/R2

VP2

VO2

18

19

20

FPOL

BRI

FPOL

FB/R1

VP1

VO1

21

22

23

blanking

blanking

output

clamping

TDA4887PS

CHANNEL 2

REFERENCE

FPOL

FPOL

CHANNEL 3

REFERENCE

FPOL

FPOL

Fig.1 Block diagram.

2001 Oct 19

7

Philips Semiconductors

Product specification

160 MHz bus-controlled monitor video

preamplifier

TDA4887PS

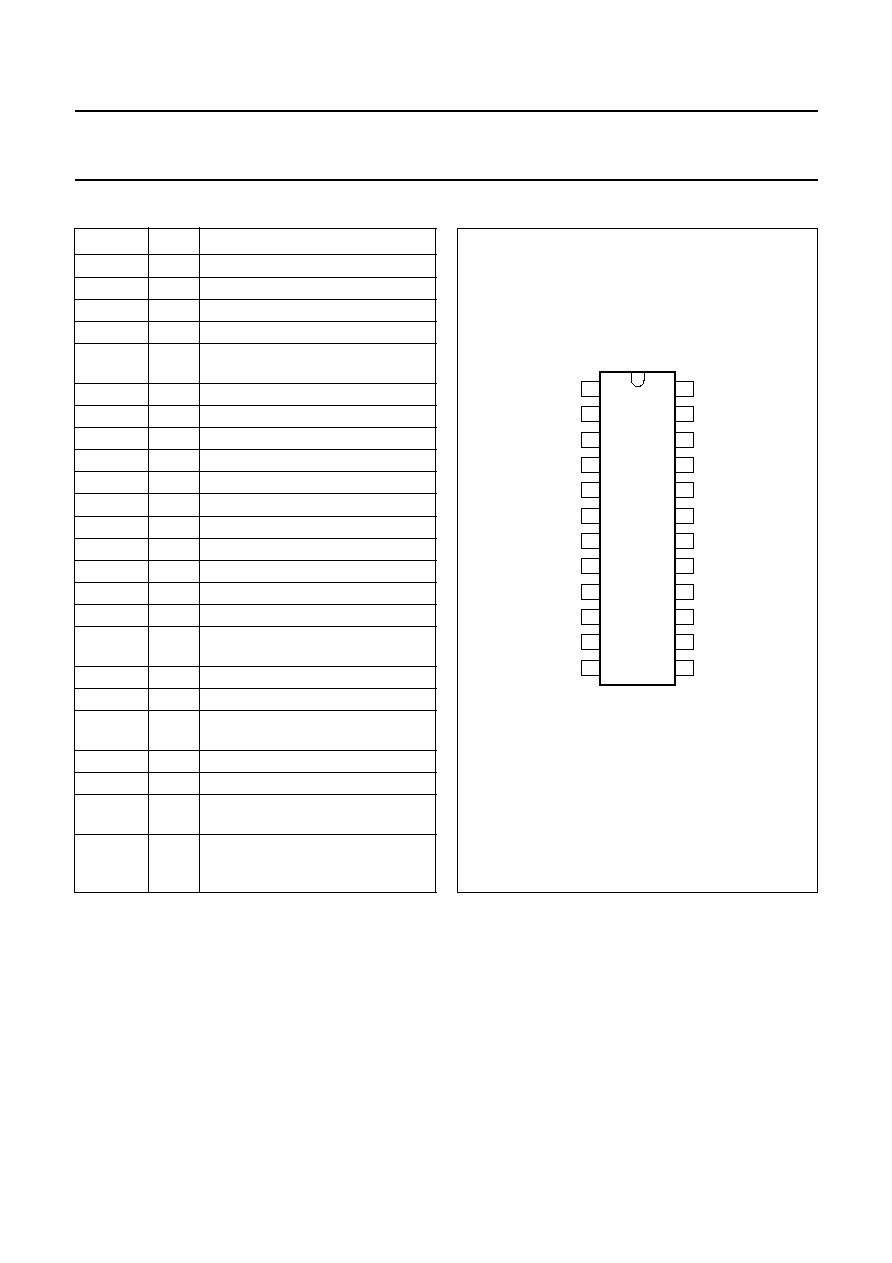

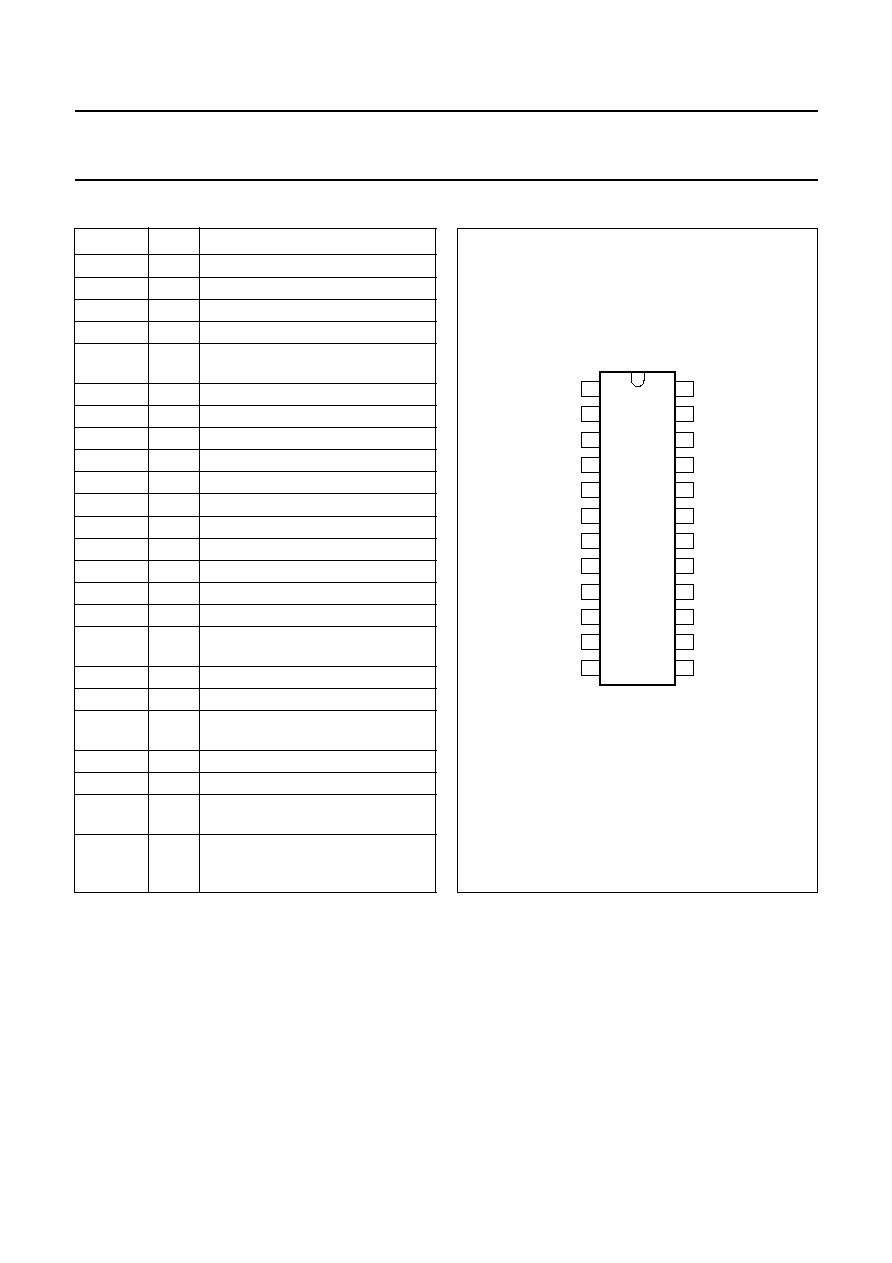

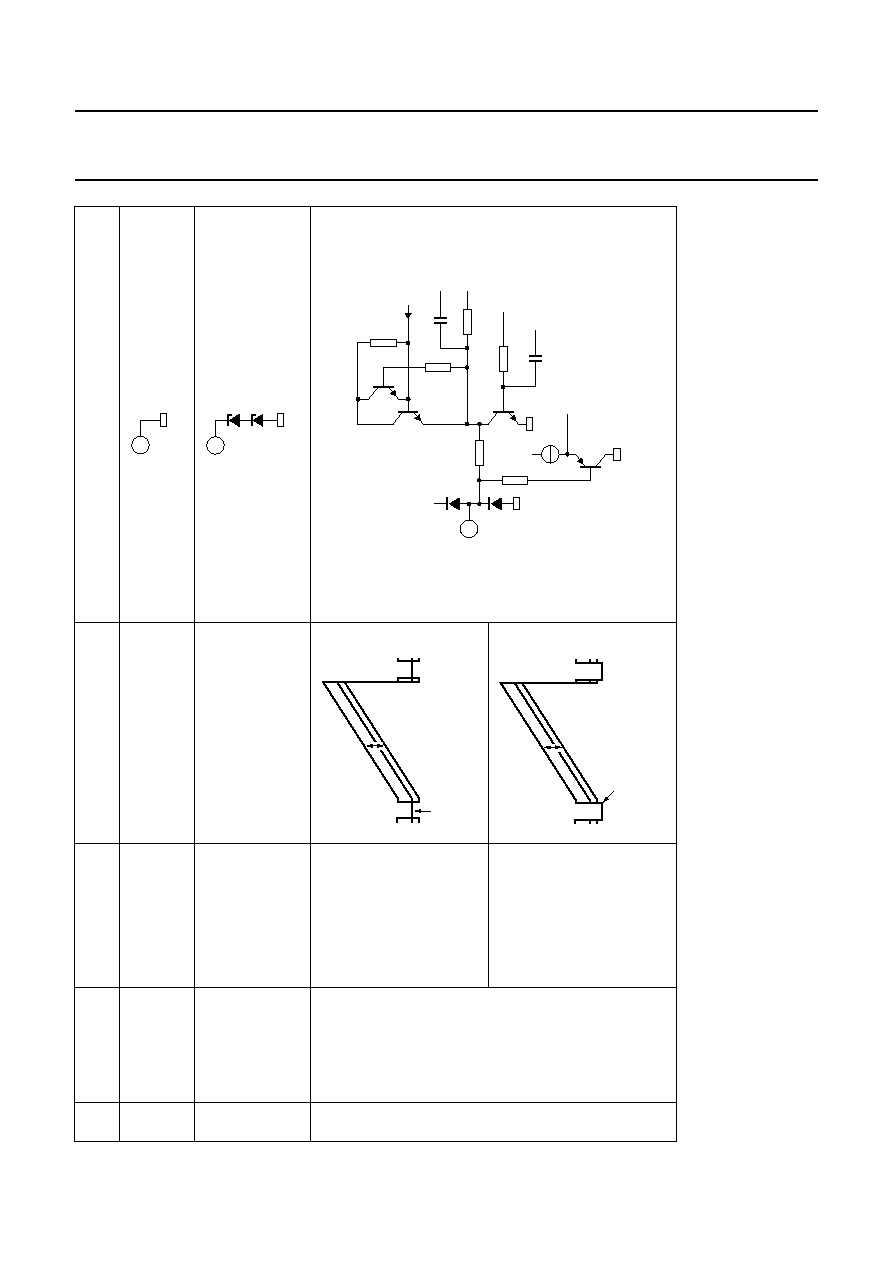

6

PINNING

SYMBOL

PIN

DESCRIPTION

FBL

1

fast blanking input for OSD insertion

OSD

1

2

OSD input, channel 1

OSD

2

3

OSD input, channel 2

OSD

3

4

OSD input, channel 3

CLI

5

input clamping and vertical blanking

input

V

I1

6

signal input, channel 1

V

P

7

supply voltage

V

I2

8

signal input, channel 2

GND

9

ground

V

I3

10

signal input, channel 3

HFB

11

output clamping and blanking input

SDA

12

I

2

C-bus serial data input/output

SCL

13

I

2

C-bus clock input

GNDX

14

ground signal, channels 1, 2 and 3

V

P3

15

supply voltage, channel 3

V

O3

16

signal output, channel 3

FB/R

3

17

feedback input/reference voltage

output channel 3

V

P2

18

supply voltage, channel 2

V

O2

19

signal output, channel 2

FB/R

2

20

feedback input/reference voltage

output, channel 2

V

P1

21

supply voltage, channel 1

V

O1

22

signal output, channel 1

FB/R

1

23

feedback input/reference voltage

output, channel 1

LIM

24

subcontrast adjustment, contrast

modulation and beam current

limiting input

handbook, halfpage

FBL

OSD1

OSD2

OSD3

CLI

VI1

VP

VI2

GND

VI3

HFB

SDA

LIM

FB/R1

VO1

VP1

VO2

VP2

FB/R2

FB/R3

VO3

VP3

GNDX

SCL

MHB919

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

TDA4887PS

Fig.2 Pin configuration.

2001 Oct 19

8

Philips Semiconductors

Product specification

160 MHz bus-controlled monitor video

preamplifier

TDA4887PS

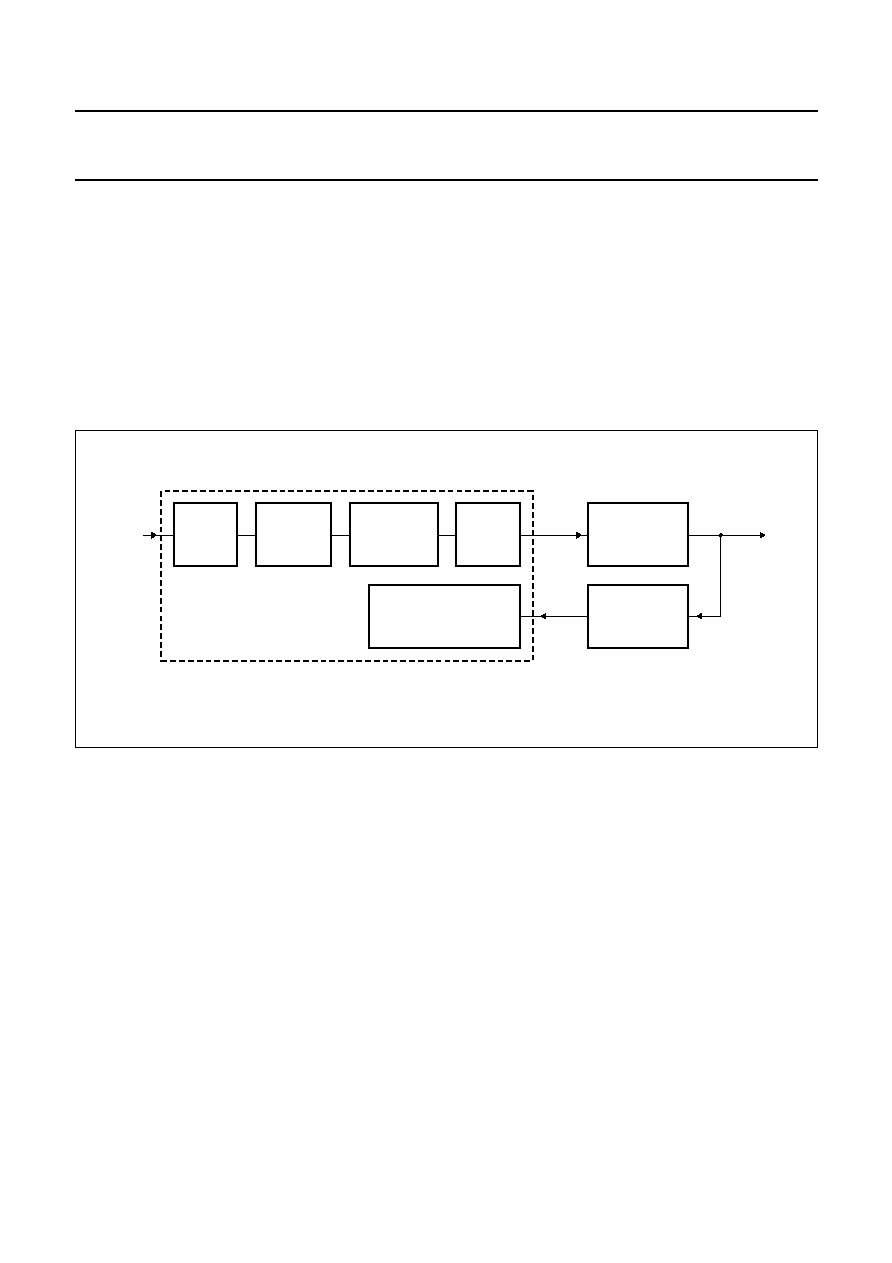

7

FUNCTIONAL DESCRIPTION

Refer also to block diagram (Fig.1) and definitions of levels

and signals (Chapter 10).

7.1

Signal input stage

The RGB input signals are capacitively coupled into the

TDA4887PS from a low-ohmic source (75

recommended) and actively clamped to the internal

reference black level during signal black level. The signal

amplitude is 0.7V

i(b-w)

and should not exceed 1 V. The

high-ohmic input impedance of the TDA4887PS allows the

coupling capacitor to be relatively small (10 nF

recommended). The coupling capacitor also functions as a

storage capacitor between clamping pulses. Very small

input currents will discharge the coupling capacitor

resulting in black output signals for missing input clamping

pulses.

Composite signals will not disturb normal operation

because a clipping circuit cuts all signal parts below black

level.

A fast signal blanking circuit included in the input stage is

driven by several blanking pulses (see Section 7.6) and

control bit DISV = 1. During the off condition the internal

reference black level is inserted instead of the input

signals.

7.2

Electronic potentiometer stages

7.2.1

C

ONTRAST CONTROL

The contrast control is driven by an 8-bit DAC via the

I

2

C-bus. The input signals related to the internal reference

black level can be adjusted simultaneously by contrast

control with a control range of 32 dB (typical). The nominal

setting is for maximum contrast.

7.2.2

B

RIGHTNESS CONTROL

7.2.2.1

Brightness control with grey scale tracking

The brightness control is driven by an 8-bit DAC via the

I

2

C-bus; brightness control with grey scale tracking is

selected when control bit BRI = 0.

With brightness control, the video black level is shifted in

relation to the reference black level simultaneously for all

three channels. With a negative setting (up to 10% of the

maximum signal amplitude) dark signal parts will be lost in

ultra black; for positive settings (up to 33% of the maximum

signal amplitude) the background will alter from black to

grey. At nominal brightness setting (40H) there is no shift.

The brightness setting is also valid for OSD signals. During

blanking and output clamping the video black level will be

blanked to the reference black level (brightness blanking).

The brightness information is inserted before the gain

potentiometers, background colour temperature will not

change with brightness setting (grey scale tracking).

7.2.2.2

Brightness control without grey scale tracking

Brightness control without grey scale tracking is selected

when control bit BRI = 1.

The brightness information will be mixed with the DAC

outputs for external black level restoration (FPOL = 1,

AC-coupled cathodes) or internal feedback reference

voltages (FPOL = 0, DC-coupled cathodes). This allows a

simple bus-controlled brightness setting without grey scale

tracking. With AC-coupled cathodes this is equivalent to

brightness control via grid G1.

7.2.3

G

AIN CONTROL AND GREY SCALE TRACKING

The gain control is driven by an 8-bit DAC via the I

2

C-bus.

Gain control is used for white point adjustment (correction

for different voltage-to-light amplification of the three

colour channels) and therefore individually for R, G and B.

The video signals related to the reference black level can

be gain-controlled within a range of 14 dB (typical). This

range is large enough to accommodate the maximum

output amplitude for different applications. The nominal

setting is maximum gain. The gain setting is also valid for

OSD signals and brightness shift (BRI = 0), therefore the

complete `grey scale' is effected by gain control.

7.3

Output stage

In the output stage the nominal input signal will be

amplified to provide a 4.6 V (typical) output colour signal at

maximum contrast and maximum gain settings. Reference

or pedestal black levels are adjusted by output clamping.

In order to achieve fast rise and fall times of the output

signals with minimum crosstalk between the channels,

each signal stage has its own supply voltage pin.

2001 Oct 19

9

Philips Semiconductors

Product specification

160 MHz bus-controlled monitor video

preamplifier

TDA4887PS

7.4

Pedestal blanking

The pedestal blanking is driven by a 2-bit DAC via the

I

2

C-bus. Pedestal blanking inserts a negative output level

related to the reference black level (should always

correspond to the `extended cut-off voltage' at the

cathode) during blanking and output clamping. In this way

retrace lines during vertical flyback are suppressed

(blanking to spot cut-off). The depth of pedestal blanking

(voltage difference between reference black level and

pedestal black level) is bus-controlled (2 bits, 0 to 13.5%

of the maximum colour signal) and does not change with

any other control or adjustment. The pedestal blanking

level is used for output clamping instead of the reference

black level (see Section 7.5). If the pedestal blanking level

is the most negative output signal and if the application is

for AC-coupled cathodes, a very simple black level

restoration with a DC diode clamp can be used.

7.5

Output clamping and feedback references

The aim of the output clamping is to set the reference black

level of the signal outputs to a value which corresponds to

the `extended cut-off voltage' of the CRT cathodes. With

missing output clamping pulses the integrated storage

capacitors will be discharged resulting in output signals

going to switch-off voltage. If using pedestal blanking, the

pedestal black level will be controlled by output clamping

(see Fig.5). It is therefore not allowed to change the

pedestal depth after black level adjustment of the monitor.

Feedback references are driven via the I

2

C-bus and

controlled by an 8-bit DAC for DC feedback references or

by a 3-bit DAC for AC feedback references:

1. DC-coupled cathodes (control bit FPOL = 0)

The cathode voltage is divided by a voltage divider and

fed back to the IC (pins FB/R

1

, FB/R

2

and FB/R

3

).

During the output clamping pulse it is compared with a

bus-controlled feedback reference voltage with a

range of approximately 5.75 to 3.95 V. Any difference

will lead to a reference black level correction

(subaddress 0BH = 00H) or pedestal black level

correction (subaddress 0BH

00H) by charging or

discharging the integrated capacitors that store the

black level information between the output clamping

pulses. The DC voltages of the output stages should

be designed in such a way that the reference black

level/pedestal black level is within the range of

0.5 to 2.4 V at the preamplifier output.

For correct operation it is necessary that there is

enough headroom for ultra black signals (negative

brightness setting and pedestal blanking). Any clipping

with the video supply voltage at the cathode can

disturb the signal rise/fall times or the black level

stabilization.

After power-on, the control bit FPOL is set to logic 1

and all alignment registers are set to logic 0 resulting

in the reference black level at its lowest level (0.53 V)

with no output signal. Normal operation starts after all

data registers have been refreshed via the I

2

C-bus.

Brightness control with grey scale tracking (control bit

BRI = 0) can be used as well as brightness control

without grey scale tracking (control bit BRI = 1) using

the mixing function of bus-controlled brightness offset

(0 to

-

1.4 V) to feedback reference voltages

(see Section 7.2).

2. AC-coupled cathodes (control bit FPOL = 1)

For applications with AC-coupled cathodes the signal

outputs are fed back internally. During the output

clamping pulse they are compared with a bus

controlled feedback reference voltage (0.5 to 1.9 V).

These values ensure a good adaptability to both

discrete and integrated post amplifiers.

For black level restoration, the DAC outputs (FB/R

1

,

FB/R

2

and FB/R

3

) with a range of approximately

3.95 to 5.75 V can be used. Pedestal blanking is

recommended because it allows use of a simple

restoration circuit. After power-on, the DAC outputs

will be at maximum output voltage (register value

logic 0), so when using a non-inverting amplifier for the

reference voltages the monitor will start with black.

Brightness control with grey scale tracking (control bit

BRI = 0) can be used as well as simple brightness

control without grey scale tracking (control bit BRI = 1)

using the mixing function of bus controlled brightness

offset (0 to

-

1.4 V) to DAC output voltages

(see Section 7.2).

2001 Oct 19

10

Philips Semiconductors

Product specification

160 MHz bus-controlled monitor video

preamplifier

TDA4887PS

7.6

Clamping and blanking pulses

There are two pins for clamping and blanking purposes

(pins CLI and HFB):

1. Pin CLI (input clamping, vertical blanking)

The pin CLI of TDA4887PS can be connected directly

to pin CLBL of e.g. TDA4855 sync processor for input

clamping pulses and vertical blanking pulses.

Input clamping pulses and blanking pulses are

completely separated from the sandcastle input, that

means there is normally (outside detected vertical

blanking) no blanking during input clamping and the

clamping pulse is not suppressed during vertical

blanking.

The input pulse is scanned with two thresholds:

a) 1.4 V (typical) for vertical blanking

b) 3 V (typical) for input clamping.

In order to separate the vertical blanking pulse from

the sandcastle pulse it is necessary that the input

clamping pulse has rise/fall times faster than 75 ns/V

during the transition from 1.2 to 3.5 V and vice versa.

The leading edge of the internal vertical blanking pulse

is delayed by typically 270 ns (after the end of an input

clamping pulse or the beginning of a separate blanking

pulse), the trailing edge is delayed by typically 115 ns.

During the vertical blanking pulse signal blanking,

brightness blanking and pedestal blanking will be

activated. In buffered mode, the leading edge of the

internal vertical blanking pulse is used to synchronize

data transmitted via the I

2

C-bus (see Section 7.10.1).

For correct input clamping the input signals have to be

at black level during the input clamping pulse.

2. Pin HFB (output clamping and blanking)

The input pulse (e.g. horizontal flyback pulse) is

scanned with two thresholds. If the input pulse

exceeds the first threshold (typically 1.4 V) signal

blanking, brightness blanking and pedestal blanking

will be activated. If the input pulse exceeds the second

threshold (typically 3 V) output clamping will be

activated additionally.

Especially for applications with DC-coupled cathodes

(FPOL = 0), it is useful that the leading edge of the

(internal) clamping pulse is slightly delayed with

respect to the leading edge of the (internal) blanking

pulse in order to avoid initial misclamping due to the

delay of the feedback signal from the cathodes.

7.7

On Screen Display insertion and OSD contrast

On Screen Display (OSD) insertion and OSD contrast are

controlled by a 4-bit DAC driven via the I

2

C-bus.

If the fast blanking input signal at pin FBL exceeds the

threshold (typically 1.4 V) the input signals are blanked

(signal blanking) and OSD signals are enabled. Then, any

signal at pins OSD

1

, OSD

2

or OSD

3

exceeding the same

threshold will create an insertion signal with an amplitude

of 100% of the maximum colour signal. The amplitude can

be controlled by OSD contrast (driven via the I

2

C-bus) with

a range of 12 dB. The OSD signals are inserted at the

same point as the contrast-controlled input signals and will

be treated with brightness and gain control as with normal

input signals.

Identical pulses at OSD signal input pins and FBL have to

be handled very carefully. Each difference in pulse delay

at the inputs will produce glitches at pulse edges at signal

outputs.

When control bit DISO = 1 the OSD signal insertion and

fast blanking (pin FBL) are disabled.

7.8

Subcontrast adjustment, contrast modulation

and beam current limiting

The pin LIM is a linear contrast control pin which allows

subcontrast setting, contrast modulation and beam current

limiting. The maximum contrast is defined by the actual

I

2

C-bus setting. Input signals at pin LIM act on video and

OSD signals and do not affect the contrast bit resolution.

If the pin is not used it should be decoupled with a

capacitor or tied to the supply voltage.

7.8.1

B

EAM CURRENT LIMITING

The open-circuit voltage is approximately 5 V, contrast

reduction starts at input voltages <4.4 V (typical) and

signal amplification will be reduced with descending input

voltages. The input resistance of pin LIM is very high to

make it possible to choose a time constant sufficient for the

open-circuit voltage to recover through the application.

7.8.2

S

UBCONTRAST

In order to fit the maximum signal amplification to the post

amplifier gain, an input voltage of <4.4 V can be used.

7.8.3

C

ONTRAST MODULATION

To achieve brightness uniformity over the screen, scan

dependent contrast modulation is possible. The nominal

input voltage should be <4.4 V having enough margin for

positive and negative modulation.

2001 Oct 19

11

Philips Semiconductors

Product specification

160 MHz bus-controlled monitor video

preamplifier

TDA4887PS

7.9

I

2

C-bus control

The TDA4887PS contains an I

2

C-bus receiver for several

control functions:

∑

Contrast register with control bits BRI, FPOL, DISV and

DISO

∑

Brightness control with 8-bit DAC

∑

Contrast control with 8-bit DAC

∑

OSD contrast control with 4-bit DAC

∑

Gain control for each channel with 8-bit DAC

∑

Internal feedback reference and external reference

voltage control for each channel with 8-bit DAC

∑

Black level for AC coupling with 3-bit DAC

∑

Depth of pedestal blanking with 2-bit DAC.

After power-up and after internal power-on reset of the

I

2

C-bus, the registers are set to the following values (for

most applications these settings guarantee a black screen

after power-up):

∑

Control bit FPOL set to logic 1

∑

Control bits BRI, DISV and DISO set to logic 0

∑

All other alignment registers set to logic 0 (minimum

value for control registers).

After an intermediate power dip, all registers are set to

their initial values and an internal Power-on reset bit will be

set with the consequence that the device will give no

acknowledge on the data byte after being first addressed.

The Power-on reset bit will be reset if the control register

is addressed. It is recommended to then refresh all

registers by using the auto-increment function.

7.10

I

2

C-bus data buffer

7.10.1

B

UFFERED MODE

Adjustments via the I

2

C-bus are synchronized with vertical

blanking pulse at CLI:

∑

Most significant bit (MSB) of subaddress is set to logic 1

∑

Only one I

2

C-bus transmission in buffered mode is

accepted before the start of the vertical blanking pulse;

following transmissions receive no acknowledge

∑

Received data is stored in one internal 8-bit buffer

∑

Adjustments will take effect with detection of the first

vertical blanking pulse after the end of the

acknowledged I

2

C-bus transmission

∑

Waiting for vertical blanking pulse in buffered mode can

be interrupted by Power-on reset

∑

Auto-increment is not possible

∑

Buffered mode should be used for user adjustments

such as contrast, OSD contrast and brightness when a

picture is visible on the monitor.

7.10.2

D

IRECT MODE

Adjustments via the I

2

C-bus take effect immediately:

∑

Most significant bit (MSB) of subaddress is set to logic 0

∑

Number of I

2

C-bus transmissions in direct mode is

unlimited

∑

Adjustments take effect directly at the end of each

I

2

C-bus transmission

∑

Direct mode can be used for all adjustments but large

changes of control values may appear as visual

disturbances in the picture on the monitor

∑

Auto-increment is possible

∑

Vertical blanking pulse is not necessary.

2001 Oct 19

12

Philips Semiconductors

Product specification

160 MHz bus-controlled monitor video

preamplifier

TDA4887PS

8

LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 60134).

Notes

1. No external voltages.

2. Equivalent to discharging a 200 pF capacitor via a 0.75

µ

H inductance (

"SNW-FQ-302B").

3. Equivalent to discharging a 100 pF capacitor via a 1500

series resistor (

"SNW-FQ-302A").

9

THERMAL CHARACTERISTICS

SYMBOL

PARAMETER

CONDITIONS

MIN.

MAX.

UNIT

V

P

supply voltage (pin 7)

0

8.8

V

V

P(n)

supply voltage; channels 1, 2 and 3

(pins 21, 18 and 15)

0

8.8

V

V

i(n)

input voltage; channels 1, 2 and 3

(pins 6, 8 and 10)

-

0.1

V

P

V

V

ext

external DC voltage applied to

pins 1 to 4

-

0.1

V

P

V

pins 5 and 11

-

0.1

V

P

+ 0.7

V

pins 12 and 13

-

0.1

V

P

V

pins 23, 20 and 17

-

0.1

V

P

+ 0.7

V

pins 22, 19 and 16

note 1

note 1

pin 24

-

0.1

V

P

V

I

o(n)(av)

average output current; channels 1, 2 and 3

(pins 22, 19 and 16)

-

20

mA

I

o(n)(M)

peak output current channels 1, 2 and 3

(pins 22, 19 and 16)

-

50

mA

P

tot

total power dissipation

-

1400

mW

T

stg

storage temperature

-

25

+150

∞

C

T

amb

ambient temperature

-

20

+70

∞

C

T

j

junction temperature

-

25

+150

∞

C

V

ESD

electrostatic handling voltage for all pins

machine model

note 2

-

250

+250

V

human body model

note 3

-

3000

+3000

V

SYMBOL

PARAMETER

CONDITIONS

VALUE

UNIT

R

th(j-a)

thermal resistance from junction to ambient

in free air

55

K/W

R

th(j-c)

thermal resistance from junction to case

5

K/W

2001 Oct 19

13

Philips Semiconductors

Product specification

160 MHz bus-controlled monitor video

preamplifier

TDA4887PS

10 CHARACTERISTICS

All voltages and currents are measured in a dedicated test circuit (see Fig.17) optimized for best high frequency

performance; all voltages are measured with respect to GND (pins 9 and 14); V

P

= V

P1,2,3

= 8 V (pins 7, 21, 18 and 15);

T

amb

= 25

∞

C; nominal input signals [0.7 V (p-p) at pins 6, 8 and 10]; maximum colour signals at signal outputs (pins 22,

19 and 16); reference black level (V

bl(ref)

) approximately 0.7 V; nominal setting for brightness; maximum settings for

OSD contrast, contrast and gain; no subcontrast, modulation of contrast or limiting (V

LIM

5 V); no OSD fast blanking

(pin 1 connected to ground); notes 1 to 3; unless otherwise specified.

SYMBOL

PARAMETER

CONDITIONS

MIN.

TYP.

MAX.

UNIT

Supplies

V

P

supply voltage (pin 7)

7.6

8.0

8.8

V

V

P(SO)

supply voltage threshold at

pin 7 at which signal outputs

are switched off

note 1

6.8

7.0

7.2

V

I

P

supply current (pin 7)

note 4

-

25

30

mA

V

P(n)

supply voltage; channels 1,

2 and 3 (pins 21, 18 and 15)

7.6

8.0

8.8

V

I

P(n)

supply current; channels 1,

2 and 3 (pins 21, 18 and 15)

pins 22, 19 and 16

open-circuit;

V

bl(n)(ref)

=

0.7 V;

notes 4 and 5

-

20

25

mA

Input clamping and vertical blanking input, validation of buffered I

2

C-bus data (CLI; pin 5)

V

CLI

input clamping and vertical

blanking input signal

notes 6 and 7

no vertical blanking,

no input clamping

-

0.1

-

+1.2

V

vertical blanking,

no input clamping

1.6

-

2.6

V

input clamping,

no vertical blanking

3.5

-

V

P

V

I

CLI

input current

V

CLI

= 1 V

-

-

0.2

-

µ

A

pin 5 connected to ground;

note 8

-

80

-

45

-

30

µ

A

V

CLI

=

-

0.1 V; note 8

-

250

-

135

-

100

µ

A

t

r/f5

rise/fall time for input

clamping pulse; disable for

vertical blanking

note 6; see Fig.7

-

-

75

ns/V

t

W(CLI)

width of input clamping

pulse

200

-

-

ns

t

W(I2C)(valid)

width of vertical blanking

pulse for validation of

buffered I

2

C-bus data

leading and trailing edge

threshold V

CLI

= 1.4 V;

note 7

10

-

-

µ

s

t

d(I2C)(valid)

delay between leading edge

of vertical blanking pulse

and validation of buffered

I

2

C-bus data

I

2

C-bus buffered mode

transmission completed;

leading edge threshold

V

CLI

= 1.4 V; note 7;

see Fig.7

-

-

2

µ

s

2001 Oct 19

14

Philips Semiconductors

Product specification

160 MHz bus-controlled monitor video

preamplifier

TDA4887PS

t

dead(I2C)

I

2

C-bus receiver dead time

after synchronizing vertical

blanking pulse following a

completed I

2

C-bus buffered

mode transmission

leading edge threshold

V

CLI

= 1.4 V; note 7

15

-

-

µ

s

t

dl5

delay between leading

edges of vertical blanking

input pulse and signal

blanking at signal outputs

V

HFB

< 0.8 V; input pulse

rising and falling edges

= 50 ns/V; threshold for

vertical blanking with rising

edge V

CLI

= 1.4 V; threshold

for vertical blanking with

falling edge V

CLI

= 3 V;

see Fig.7

-

270

-

ns

t

dt5

delay between trailing edges

of vertical blanking input

pulse and signal blanking at

signal outputs

V

HFB

< 0.8 V; input pulse

falling edge = 50 ns/V;

threshold V

CLI

= 1.4 V;

see Fig.7

-

115

-

ns

Output clamping and blanking input (HFB; pin 11)

V

HFB

output clamping and

blanking input signal

note 9

no blanking, no output

clamping

-

0.1

-

+0.8

V

blanking, no output

clamping

2

-

2.6

V

blanking, output clamping

3.5

-

V

P

V

I

HFB

input current

V

HFB

= 0.8 V

-

-

0.4

-

µ

A

pin 11 connected to ground;

note 8

-

80

-

45

-

30

µ

A

V

HFB

=

-

0.1 V; note 8

-

250

-

135

-

100

µ

A

t

W(HFB)

width of output clamping

pulse

V

HFB

= 3 V

1

-

-

µ

s

Video signal inputs; channels 1, 2 and 3 (pins 6, 8 and 10)

V

i(n)(b-w)

input voltage; black-to-white

value (pins 6, 8 and 10)

-

0.7

1.0

V

I

i(n)

DC input current

(pins 6, 8 and 10)

no input clamping;

V

i(n)

= V

i(n)(clamp)

;

T

amb

=

-

20 to +70

∞

C

0.02

0.20

0.35

µ

A

during input clamping;

V

i(n)

= V

i(n)(clamp)

±

0.7 V

±

350

±

420

±

500

µ

A

Signal blanking

ct(blank)

crosstalk suppression from

input to output during

blanking

control bit DISV = 1;

f = 80 MHz

20

-

-

dB

control bit DISV = 1;

f = 120 MHz

10

-

-

dB

SYMBOL

PARAMETER

CONDITIONS

MIN.

TYP.

MAX.

UNIT

2001 Oct 19

15

Philips Semiconductors

Product specification

160 MHz bus-controlled monitor video

preamplifier

TDA4887PS

Clipping of negative input signals (measured at signal outputs)

V

clipp

offset during sync clipping

related to maximum colour

signal

V

i(n)

= V

i(n)(clamp)

;

sync amplitude = 0.3 V;

note 10; see Fig.3

-

0.6

1.2

%

Contrast control; see Fig.8 and note 11

C

colour signal related to

maximum colour signal

FFH (maximum)

-

0

-

dB

00H (minimum)

-

-

45

-

dB

G

track

tracking of output colour

signals of channels 1,

2 and 3

FFH to 40H; note 12

-

0

0.5

dB

Fast blanking (pin 1) and OSD signal insertion; channels 1, 2 and 3 (pins 2, 3 and 4); note 13

V

FBL

fast blanking input signal

(pin 1)

no video signal blanking;

OSD signal insertion

disabled

0

-

1.1

V

video signal blanking;

OSD signal insertion

enabled

1.7

-

V

P

V

V

OSDn

OSD input signal

(pins 2, 3 and 4)

V

FBL

> 1.7 V

no internal OSD signal

insertion

0

-

1.1

V

internal OSD signal

insertion

1.7

-

V

P

V

t

r(OSDn)

rise time of OSD colour

signals (pins 22, 19 and 16)

10 to 90% amplitude; pulse

leading edge = 1.2 ns/V

-

3

4

ns

t

f(OSDn)

fall time of OSD colour

signals (pins 22, 19 and 16)

90 to 10% amplitude; pulse

falling edge = 1.2 ns/V

-

4

7

ns

t

g(n)(CO)

width of (negative going)

OSD signal insertion glitch,

leading edge

(pins 22, 19 and 16)

identical pulses at fast

blanking input (pin 1) and

OSD signal inputs

(pins 2, 3 and 4)

0

4

6

ns

t

g(n)(OC)

width of (negative going)

OSD signal insertion glitch,

trailing edge (pins 22, 19

and 16)

identical pulses at fast

blanking input (pin 1) and

OSD signal inputs (pins 2, 3

and 4)

0

5

6

ns

V

OSDn

overshoot/undershoot of

OSD colour signal related to

actual OSD output pulse

amplitude (pins 22, 19

and 16)

pulse with 1.2 ns/V at OSD

signal inputs (pins 2, 3

and 4)

-

6

10

%

V

OSDn(max)

maximum OSD colour signal

related to maximum colour

signal (pins 22, 19 and 16)

maximum OSD contrast;

maximum gain

90

96

110

%

SYMBOL

PARAMETER

CONDITIONS

MIN.

TYP.

MAX.

UNIT

2001 Oct 19

16

Philips Semiconductors

Product specification

160 MHz bus-controlled monitor video

preamplifier

TDA4887PS

OSD contrast control; see Fig.9 and note 14

OC

OSD colour signal related to

maximum OSD colour signal

0FH (maximum)

-

0

-

dB

00H (minimum)

-

14

-

12

-

10

dB

Subcontrast adjustment, contrast modulation and beam current limiting (pin 24); see Fig.8 and note 15

V

LIM(nom)

nominal input voltage

pin 24 open-circuit

4.7

5.0

5.3

V

V

LIM(start)

starting voltage for linear

contrast and OSD contrast

reduction

4.2

4.4

4.8

V

V

LIM(stop)

stop voltage for linear

contrast and OSD contrast

reduction

-

40 dB below maximum

colour signal (contrast

setting FFH)

1.5

2.0

2.5

V

B

LIM

bandwidth of contrast

modulation

-

3 dB

4

-

-

MHz

I

LIM(max)

maximum input current

V

LIM

= 0 V

-

1

-

+1

µ

A

Brightness control; see Figs 10, 12 and 14 and notes 16 and 17

V

bl(n)

difference between video

black level and reference

black level at signal outputs

related to maximum colour

signal

FFH (maximum); BRI = 0

28

33

38

%

40H (nominal); BRI = 0

-

2

0

+2

%

00H (minimum); BRI = 0

-

12

-

10

-

8

%

V

DA(n)

DAC output voltage shift

(pins 23, 20 and 17)

FPOL = 1, see DAC output

voltages for AC coupling or

feedback reference voltage

shift; FPOL = 0, see internal

feedback reference voltage

for DC coupling

FFH (maximum); BRI = 1

-

-

1.4

-

V

00H (minimum); BRI = 1

-

0

-

V

Gain control; see Fig.11 and note 18

G

video signal related to video

signal at maximum gain

FFH (maximum)

-

0

-

dB

00H (minimum)

-

15

-

13.5

-

12.5

dB

Pedestal blanking; see Fig.5 and note 19

V

bl(n)(PED-VID)

difference between pedestal

black level and video black

level at nominal brightness,

measured at signal outputs

(pins 22, 19 and 16) related

to maximum colour signal

03H (maximum)

-

12

-

13.5

-

%

02H

-

8

-

9

-

%

01H

-

4

-

4.5

-

%

00H (minimum)

-

0

-

%

SYMBOL

PARAMETER

CONDITIONS

MIN.

TYP.

MAX.

UNIT

2001 Oct 19

17

Philips Semiconductors

Product specification

160 MHz bus-controlled monitor video

preamplifier

TDA4887PS

Signal outputs; channels 1, 2 and 3 (pins 22; 19 and 16)

V

o(n)(min)

minimum output voltage

level (pins 22, 19 and 16)

0.01

0.05

0.1

V

V

o(n)(max)

maximum output voltage

level (pins 22, 19 and 16)

arbitrary input signals,

contrast, brightness and

gain adjustments; without

load

V

P(n)

-

2

-

V

P(n)

-

1

V

I

o(n)(source)(max)

maximum output source

current (pins 22, 19 and 16)

-

15

-

-

mA

R

o(n)

output resistance

(pins 22, 19 and 16)

65

75

90

V

o(n)(b-w)(max)

maximum output voltage

swing (black-to-white value);

channels 1, 2 and 3

(pins 22, 19 and 16)

maximum contrast;

maximum gain;

V

i(n)(b-w)

= 0.7 V; R

L

= 2 k

4.2

4.6

4.9

V

I

o(n)(source)(M)

peak output source current

(pins 22, 19 and 16)

during fast positive signal

transients

-

40

-

-

mA

I

o(n)(sink)(M)

peak output sink current

(pins 22, 19 and 16)

during fast negative signal

transients

-

-

20

mA

S/N

signal-to-noise ratio

note 20

48

-

-

dB

Frequency response at signal outputs; channels 1, 2 and 3 (pins 22, 19 and 16)

t

r(n)

rise time of fast transients

(pins 22, 19 and 16)

input rise time = 1 ns;

10 to 90% amplitude;

R

L

= 10 k

; notes 21,

22 and 23;

2.8 V (p-p) signal

amplitude; C

L

= 5 pF

-

2.7

3.8

ns

4.5 V (p-p) signal

amplitude; C

L

= 5 pF

-

3.2

4.2

ns

4.5 V (p-p) signal

amplitude; C

L

= 11 pF

-

3.8

4.5

ns

t

f(n)

fall time of fast transients

(pins 22, 19 and 16)

input fall time = 1 ns;

90 to 10% amplitude;

R

L

= 10 k

; notes 21,

22 and 23;

2.8 V (p-p) signal

amplitude; C

L

= 5 pF

-

3.6

4.5

ns

4.5 V (p-p) signal

amplitude; C

L

= 5 pF

-

3.6

4.5

ns

4.5 V (p-p) signal

amplitude; C

L

= 11 pF

-

5

6

ns

SYMBOL

PARAMETER

CONDITIONS

MIN.

TYP.

MAX.

UNIT

2001 Oct 19

18

Philips Semiconductors

Product specification

160 MHz bus-controlled monitor video

preamplifier

TDA4887PS

V

o(n)

overshoot of output signal

pulse related to actual

output pulse amplitude

(pins 22, 19 and 16)

input rise time = 1 ns;

maximum colour signal

-

-

10

%

undershoot of output signal

pulse related to actual

output pulse amplitude

(pins 22, 19 and 16)

input fall time = 1 ns;

maximum colour signal

-

-

10

%

Crosstalk at signal outputs; channels 1, 2 and 3 (pins 22, 19 and 16)

ct(tr)(n)

transient crosstalk

suppression

(pins 22, 19 and 16)

input rise/fall time = 1 ns;

note 24

10

-

-

dB

ct(f)

crosstalk suppression by

frequency

f = 50 MHz; note 25

25

-

-

dB

f = 100 MHz; note 25

10

-

-

dB

Internal feedback reference voltage for DC coupling; see Fig.12 and note 26

V

ref(DC)

internal reference voltage for

negative feedback polarity

(without brightness control)

FFH; FPOL = 0; BRI = 0

3.7

3.95

4.1

V

00H; FPOL = 0; BRI = 0

5.6

5.75

5.9

V

internal reference voltage for

negative feedback polarity

(with brightness control, see

also brightness control

V

DA(n)

)

FFH; FPOL = 0; BRI = 1;

maximum brightness

2.3

2.55

2.7

V

00H; FPOL = 0; BRI = 1;

minimum brightness

5.6

5.75

5.9

V

Output clamping, feedback inputs for DC coupling; FB/R

1

, FB/R

2

and FB/R

3

(pins 23, 20 and 17)

I

FB/Rn(max)

maximum input current

(pins 23, 20 and 17)

during output clamping;

V

HFB

> 3.5 V; V

FB/Rn

= 0.5 V;

FPOL = 0

-

500

-

200

-

60

nA

V

bl(n)(ref)(min)

minimum reference black

level/minimum pedestal

black level

(pins 22, 19 and 16)

V

HFB

> 3.5 V; FPOL = 0

0.01

0.1

0.5

V

V

bl(n)(ref)(max)

maximum reference black

level/maximum pedestal

black level

(pins 22, 19 and 16)

V

HFB

> 3.5 V; FPOL = 0

2.0

2.8

4.0

V

V

bl(CRT)

black level variation at CRT

FPOL = 0; note 27

-

-

200

mV

V

bl(n)(lf)

black level decrease

between clamping pulses

related to maximum colour

signal (pins 22, 19 and 16)

FPOL = 0; f

line

= 60 kHz;

= 10%

-

0.1

-

%

SYMBOL

PARAMETER

CONDITIONS

MIN.

TYP.

MAX.

UNIT

2001 Oct 19

19

Philips Semiconductors

Product specification

160 MHz bus-controlled monitor video

preamplifier

TDA4887PS

Output clamping; internal feedback (of signal outputs) reference voltage for AC coupling;

see Fig.13 and note 28

V

bl(n)(ref)

reference black level

voltage/pedestal black level

voltage (pins 22, 19 and 16)

V

HFB

> 3.5 V; FPOL = 1

00H (minimum)

0.47

0.53

0.59

V

0FH (maximum)

1.83

1.89

1.95

V

DAC output voltages for AC coupling; FB/R

1

, FB/R

2

and FB/R

3

(pins 23, 20 and 17); see Fig.14 and note 29

V

FB/Rn

DAC output voltage (without

brightness control)

FFH; FPOL = 1; BRI = 0

3.7

3.95

4.1

V

00H; FPOL = 1; BRI = 0

5.6

5.75

5.9

V

DAC output voltage (with

brightness control, see also

brightness control

V

DA(n)

)

FFH; FPOL = 1; BRI = 1;

maximum brightness

2.3

2.55

2.7

V

00H; FPOL = 1; BRI = 1;

minimum brightness

5.6

5.75

5.9

V

R

FB/Rn

output resistance

FPOL = 1

-

100

-

I

FB/Rn(sink)(max)

maximum sink current

FPOL = 1

-

-

400

µ

A

I

FB/Rn(source)(max)

maximum source current

FPOL = 1

-

-

200

-

µ

A

I

2

C-bus inputs; SDA (pin 12), SCL (pin 13); note 30

f

SCL

SCL clock frequency

-

-

100

kHz

V

IL

LOW-level input voltage

0

-

1.5

V

V

IH

HIGH-level input voltage

3

-

5

V

I

IL

LOW-level input current

V

IL

= 0 V

-

10

-

-

µ

A

I

IH

HIGH-level input current

V

IH

= 5 V

-

10

-

-

µ

A

V

OL

LOW-level output voltage

during acknowledge

0

-

0.4

V

I

SDA(ack)

SDA output current (pin 12)

during acknowledge

V

OL

= 0.4 V

3

-

-

mA

V

OL

= 0.6 V

6

-

-

mA

t

o(f)

output fall time

V

SDA

= 3 to 1.5 V; bus

capacitance C

SDA

= 400 pF

-

-

250

ns

V

th(POR)(r)

threshold for Power-on reset

on

rising supply voltage

-

1.5

2.0

V

falling supply voltage

-

3.5

-

V

V

th(POR)(f)

threshold for Power-on reset

off

rising supply voltage

-

-

7

V

falling supply voltage

-

1.5

-

V

SYMBOL

PARAMETER

CONDITIONS

MIN.

TYP.

MAX.

UNIT

2001 Oct 19

20

Philips Semiconductors

Product specification

160 MHz bus-controlled monitor video

preamplifier

TDA4887PS

Notes to the characteristics

1. Definition of levels (see Figs 3 to 5)

Reference black level: this is the level to which the input level is clamped during the input clamping pulse

(V

CLI

> 3.5 V). It is used internally as a reference for the gain settings. It can be observed on the outputs:

a) When the input is at black and the brightness setting is nominal (subaddress 01H = 40H) or control bit BRI = 1

b) During output blanking and clamping (V

HFB

> 3.5 V) if the pedestal blanking depth is set to zero

(subaddress 0BH = 00H).

Video black level: this is the black level of the actual video. At the input it is still equal to the reference black level.

At the output it may deviate from it according to the brightness setting. Contrast setting leaves the video black level

unaltered . Gain setting biases the video black level due to its influence on brightness. This is important for correct

grey scale tracking. It can be observed at the outputs when the input is at black outside output blanking and clamping

pulses (V

HFB

< 0.8 V).

Pedestal black level: this is an ultra black level which deviates from the reference black level by a bus controlled

amount. It can be observed at the output during output blanking and clamping (V

HFB

> 3.5 V; subaddress

0BH

00H).

Switch-off voltage: this is the lowest signal voltage at outputs. The signals will be switched off by discharging the

internal black level storage capacitors if the supply voltage is less than V

P(SO)

. It can be observed at the outputs when

the input is at black, the brightness setting is nominal and V

P

< 6.8 V (subaddress 01H = 40H).

Blanking level: this level equals reference black (subaddress 0BH 1= 00H) or pedestal black. It can be observed at

the outputs during output blanking and clamping (V

HFB

> 3.5 V).

2. Explanation to black level adjustment:

The three reference black levels are aligned correctly when they are made equal to the `extended cut-off levels' of

the three cathodes. Full raster and spot cut-off can only be achieved by enabling the pedestal blanking or by applying

a negative pulse to the grid G1.

Negative feedback for DC-coupled cathodes (control bit FPOL = 0): the actual blanking level on the outputs

depends on the external feedback application for output clamping. The loop will function correctly only if it is within

the control range of V

bl(n)(ref)(min)

to V

bl(n)(ref)(max)

at pins 22, 19 and 16. It should be noted that changing pedestal

blanking in a given application will not affect the blanking level, but instead shifts the video (and needs re-alignment

of the three black levels).

Positive feedback for AC-coupled cathodes (control bit FPOL = 1): the feedback loop for output clamping is

closed internally. The actual blanking level is bus controlled between 0.53 and 1.89 V (subaddress 0AH). It should

be noted that changing pedestal blanking will not affect the blanking level, but instead shifts the video (and

re-alignment of the three black levels is needed).

3. Definition of output signals (see Fig.6):

Colour signal: all positive voltages are referenced to black level at signal outputs.

Maximum colour signal: colour signal with nominal input signal 0.7V

i(b-w)

, maximum contrast setting and maximum

gain setting.

Video signal: all positive voltages referred to reference black level at signal outputs. The video signal is the

superimposing of the brightness information (

V

bl

) and the colour signal.

4. The total supply current I

P(tot)

= I

P

+ I

P1

+ I

P2

+ I

P3

depends on the supply voltage with a factor of approximately

4.4 mA/V and varies in the temperature range from

-

20 to +70

∞

C by approximately

±

5% (V

O(n)

= 0.7 V).

5. The channel supply current I

P1

, I

P2

, I

P3

depends on the signal output current I

O1

, I

O2

, I

O3

, the channel supply voltage

V

P1

, V

P2

, V

P3

and the signal output voltage V

O1

, V

O2

, V

O3

. With I

Px

= I

P(n)

at I

O(n)

= 0, V

P(n)

= 8 V and V

O(n)

= 0.7 V:

I

P(n)

I

Px

I

O(n)

4.4 mA/V

V

P(n)

8 V

≠

(

)

◊

1 mA/V

V

O(n)

0.7 V

≠

(

)

◊

≠

+

+

2001 Oct 19

21

Philips Semiconductors

Product specification

160 MHz bus-controlled monitor video

preamplifier

TDA4887PS

6. Pin 5 should be used for input clamping and blanking during vertical retrace (signal blanking, brightness blanking and

pedestal blanking). With a fast clamping pulse (transition between V

CLI

= 1.2 to 3.5 V and 3.5 to 1.2 V in less than

75 ns/V) no blanking will occur during input clamping.

For 75 ns/V < t

r/f5

280 ns/V the generation of the internal blanking pulse is uncertain. For t

r/f5

> 280 ns/V the

internal blanking pulse will be generated.

If pin 5 is open-circuit, it will activate permanent input clamping and undefined blanking.

7. Pin 5 can be used to synchronize all adjustments via the I

2

C-bus (one by one). With a completed I

2

C-bus

transmission in buffered mode, only the leading edge of a vertical blanking pulse activates an adjustment (see also

Section 7.10).

After the adjustment has been activated (validation of buffered I

2

C-bus data) the I

2

C-bus will be reset and further

transmissions in direct or buffered mode are enabled.

I

2

C-bus transmissions in direct mode need no synchronization pulses.

8. Input voltages less than

-

0.1 V can produce internal substrate currents which disturb the leakage currents at the

signal inputs. An internal protection circuit creates a current for pin voltages of approximately 0 V or with negative

voltage. Feeding clamping and blanking pulses via a resistor (several k

)

protects the pin from negative voltages.

9. Pin 11 should be used for output clamping and/or blanking. If pin 11 is open-circuit, it will activate permanent blanking

and output clamping.

10. Composite signals will not disturb normal operations because an internal clipping circuit cuts all signal parts below

input reference black level (see Fig.3).

11. Contrast control acts on internal colour signals under I

2

C-bus control; subaddress 02H (bit resolution 0.4% of

contrast range).

12.

A

n

: colour signal output amplitude in channel n = 1, 2 or 3 at any contrast setting.

A

n0

: colour signal output amplitude in channel n = 1, 2 or 3 at maximum contrast setting and same gain setting.

13. When OSD fast blanking is active and OSD inputs OSD

1

, OSD

2

and OSD

3

are HIGH (V

FBL

> 1.7 V, V

OSD(n)

> 1.7 V)

the OSD colour signals will be inserted in front of the gain potentiometers. This ensures a correct grey scale of all

video signals. The amplitudes of the inserted OSD signals can be controlled simultaneously by OSD contrast via the

I

2

C-bus.

The inserted black level change (

V

bl

) due to brightness control is not affected by OSD fast blanking.

14. OSD contrast control acts on inserted OSD colour signals under I

2

C-bus control; subaddress 03H (bit resolution

6.7% of OSD contrast range).

15. This pin can be used for subcontrast adjustment, beam current limiting and contrast modulation. Both the video and

OSD contrast are reduced simultaneously (see Figs 8 and 9). Because of the high-ohmic input impedance the pin

should be tied to a voltage of more than 5 V or decoupled with a capacitor (several nF) if not used.

16. Brightness control adds an I

2

C-bus controlled DC offset to the internal colour signal; subaddress 01H (bit resolution

0.4% of brightness range). When control bit BRI = 1 the internal gain dependent brightness control is switched off

and the feedback reference voltages (control bit FPOL = 0) or DAC output voltages for DC restoration (control bit

FPOL = 1) at the cathodes are shifted with brightness control.

17. The voltage difference between video black level and reference black level is related to the colour signal (see note 3)

with nominal 0.7 V (p-p) input signal, at maximum contrast (subaddress 02H = FFH) and for any gain setting.

This voltage difference (in Volts) is proportional to the gain setting (grey scale tracking). Therefore

V

bl

(in percent)

is constant for any gain setting. The given values of

V

bl

are valid only for video black levels higher than the minimum

output voltage level V

o(n)(min)

.

G

track

20

maximum of

A

1

A

10

---------

A

20

A

2

---------

◊

log

A

1

A

10

---------

A

30

A

3

---------

◊

log

A

2

A

20

---------

A

30

A

3

---------

◊

log

◊

dB

=

2001 Oct 19

22

Philips Semiconductors

Product specification

160 MHz bus-controlled monitor video

preamplifier

TDA4887PS

18. Gain control acts on video signals and inserted OSD video signals under I

2

C-bus control; subaddress 04H

(channel 1), 05H (channel 2) and 06H (channel 3; bit resolution 0.4% of gain range respectively).

19. Pedestal blanking produces an ultra black level during blanking and output clamping which is the most negative

signal at the signal output pins. The pedestal depth can be selected by bus control, subaddress 0BH. The reference

black level which should correspond to the `extended cut-off voltage' at the cathodes is approximately

V

bl(n)(PED-VID)

higher (see Fig.5). The use of pedestal blanking with AC-coupled cathodes (control bit FPOL = 1) allows a very

simple black level restoration with a DC diode clamp instead of a complicated pulse restoration circuit.

20. The signal-to-noise ratio is calculated using the formula (range 1 to 120 MHz):

21. The following formula can be used to approximately determine the output rise/fall time for any input rise/fall time other

than 1 ns:

22. The relationship between pixel rate and signal bandwidth is f

-

3dB

= 0.75

◊

f

pixel

, which is a compromise between

excellent and acceptable video performance. The calculation of the pixel-related rise and fall times can be done using

the formula

. Although this formula is valid for low-pass filters of first order only it is used

in most cases for simplified estimations. The pixel rate

is a good approximation for many filter types.

23. Rise and fall times depend on signal amplitude, temperature, external load, black level and supply voltage. The rise

time is affected if the top level of the signal pulse approaches the maximum output voltage level (high black level,

large signal amplitude or low supply voltage). The fall time depends on the black level (increase with decreasing

black level) and on large capacitive loads. Low-ohmic pull-down loads at the outputs helps towards smaller fall times.

Rise and fall times increase with increasing ambient (or crystal) temperature. At maximum operating temperature,

rise and fall times are approximately 0.4 ns longer than at T

amb

= 25

∞

C.

24. Transient crosstalk between any two output pins:

a) Input conditions: any channel (channel A) with nominal input signal and 1 ns rise time. The inputs of the other

two channels (channels B) are capacitively coupled to ground. Gain setting at maximum (FFH). Contrast setting

at maximum (FFH). No limiting/modulation of contrast (V

LIM

4.8 V)

b) Output conditions: black level set to approximately 0.7 V for each channel at signal outputs. Output signals are

V

A

and V

B

respectively

c) Transient crosstalk suppression:

25. Crosstalk by frequency between any two output pins:

a) Input conditions: any channel (channel A) with 0.2 V (p-p) sinusoidal input signal, DC-coupled to approximately

4.3 V, no input clamping. The inputs of the other two channels (channels B) are capacitively coupled to ground.

Gain setting at maximum (FFH). Contrast setting at maximum (FFH). No limiting/modulation of contrast

(V

LIM

4.8 V)

b) Output conditions: control bit FPOL = 1, subaddress 0AH set to 01H, no pedestal blanking, nominal brightness

setting. Output signals are V

A

and V

B

respectively

c) Crosstalk suppression:

S

N

----

20

peak-to-peak value of the maximum signal output voltage

RMS value of the noise output voltage

-------------------------------------------------------------------------------------------------------------------------------------------------------- dB

log

◊

=

t

r/f, measured

2

t

r/f (22,19,16)

2

t

r/f, input

2

1 ns

[

]

2

≠

(

)

+

=

t

r/f

0.35

f

3dB

≠

------------

0.35

0.75

f

pixel

◊

-----------------------------

=

=

f

pixel

0.35

0.75

t

r

◊

---------------------

=

ct(tr)

20

V

A

V

B

------- dB

log

◊

=

ct(f)

20

V

A

V

B

------- dB

log

◊

=

2001 Oct 19

23

Philips Semiconductors

Product specification

160 MHz bus-controlled monitor video

preamplifier

TDA4887PS

26. Control bit FPOL = 0: the internal feedback reference voltages for DC control act under I

2

C-bus control; subaddress

07H (channel 1), 08H (channel 2) and 09H (channel 3); bit resolution 0.4% of voltage range. Rising values of the data

bytes, e.g. 00H to FFH, correspond to rising values of the resulting reference black levels at signal outputs

(pins 22, 19 and 16). The internal feedback reference voltages can be measured at feedback inputs

(pins 23, 20 and 17) during output clamping (V

HFB

> 3.5 V) in closed feedback loop. The feedback loop remains

operative at reference black levels between the specified values of V

o(n)bl(ref)(min)

and V

o(n)bl(ref)(max)

.

Control bit BRI = 1: the internal feedback reference voltages can be shifted under I

2

C-bus control which allows easy

brightness control without grey scale tracking (see Section 7.2.2.2); subaddress 01H (bit resolution 0.4% of voltage

shift range). The superimposition of internal feedback reference and brightness control leads to a voltage output

range of 5.8 to 2.5 V.

27. Slow variations of video supply voltage V

CRT

will be suppressed at the CRT cathode by the clamping feedback loop.

A change of V

CRT

with 5 V leads to a specified change of the cathode voltage.

28. To adapt to different types of post amplifier, the internal feedback reference voltage for AC coupling (control bit

FPOL = 1) acts under I

2

C-bus control; subaddress 0AH (bit resolution 14.29%). The internal feedback reference

voltage can be measured at signal outputs (pins 22, 19 and 16) during output clamping (V

HFB

> 3.5 V); reference

black level or pedestal black level.

29. The DAC output voltages act under I

2

C-bus control for control bit FPOL = 1; subaddress 07H (FB/R

1

), 08H (FB/R

2

)

and 09H (FB/R

3

); bit resolution 0.4% of voltage range respectively. Using an inverting amplifier for DC restoration,

rising values of the data bytes, e.g. 00H to FFH, correspond to changing the light output from dark to bright.

With control bit BRI = 1 the DAC output voltages can be shifted under I

2

C-bus control which allows easy brightness

control without grey scale tracking (see Section 7.2.2.2); subaddress 01H (bit resolution 0.4% of voltage shift range).

The superimposition of black level control and brightness control leads to a voltage output range of 5.8 to 2.5 V.

30. All adjustments via the I

2

C-bus can be synchronized with vertical blanking pulse at pin CLI. This is called I

2

C-bus

transmission in buffered mode. Conversely the adjustments via the I

2

C-bus will take effect immediately in

direct mode.

The timing of I

2

C-bus transmissions in buffered mode is related to the vertical blanking. See Section 7.6 and note 7

for specification of vertical blanking input (pin 5).

2001 Oct 19

24

Philips Semiconductors

Product specification

160 MHz bus-controlled monitor video

preamplifier

TDA4887PS

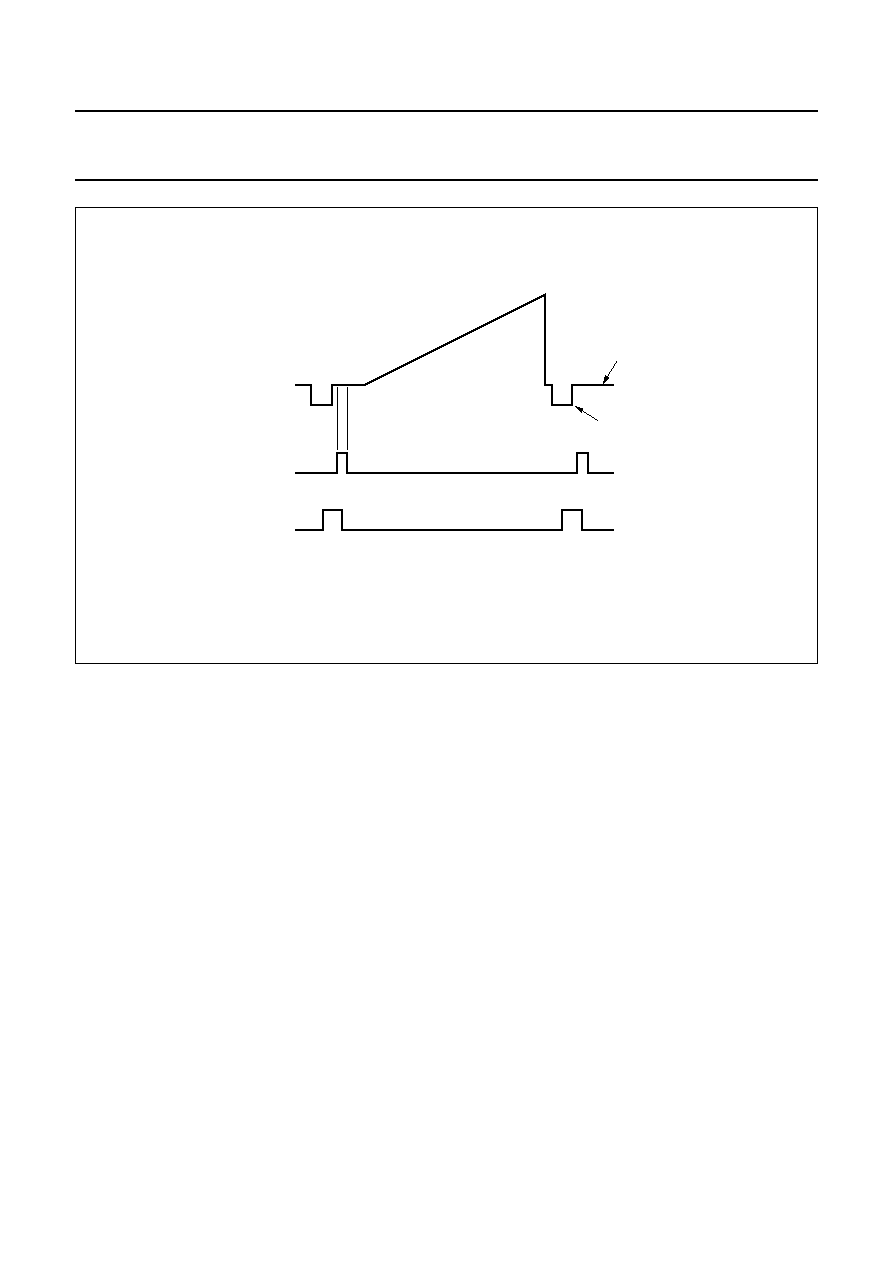

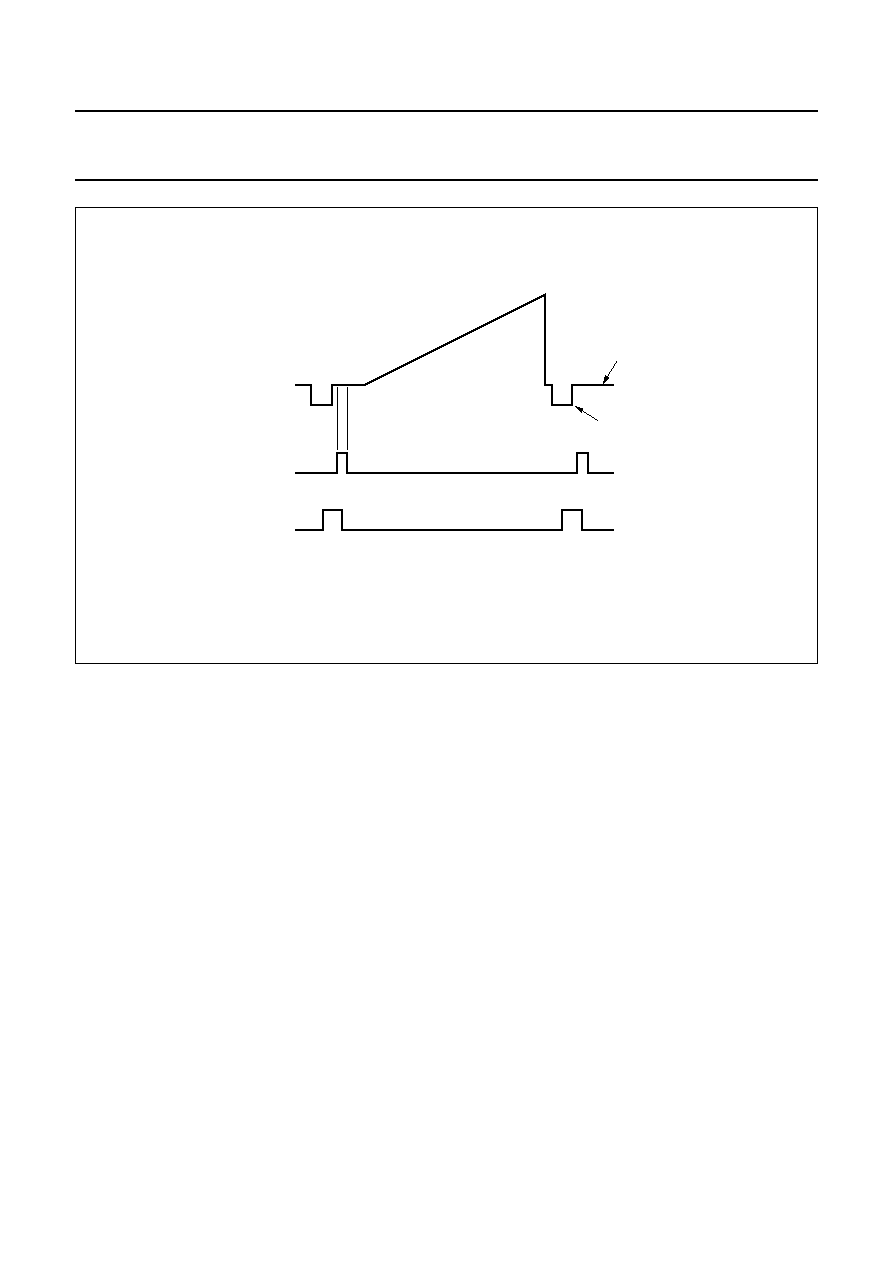

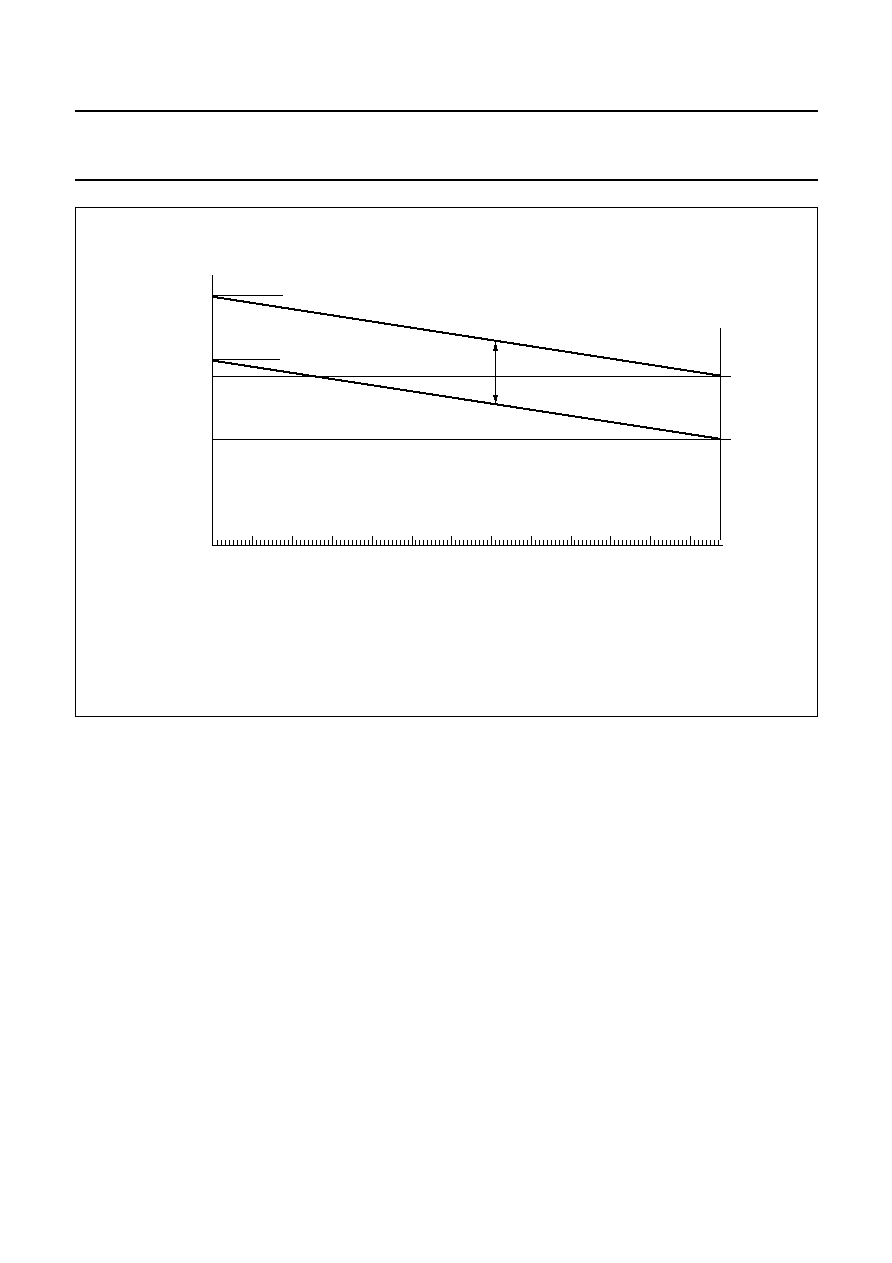

handbook, full pagewidth

MHA344

input video signal

with sync pulses

at pins 6, 8 and 10

input clamping pulses

at pin 5

output clamping

and blanking

input pulses

at pin 11

input reference

black level

the sync pulses are

clipped to reference

black level internally

Fig.3 Definition of input signals.

The input video signals have to be at black level during input clamping.

2001 Oct 19

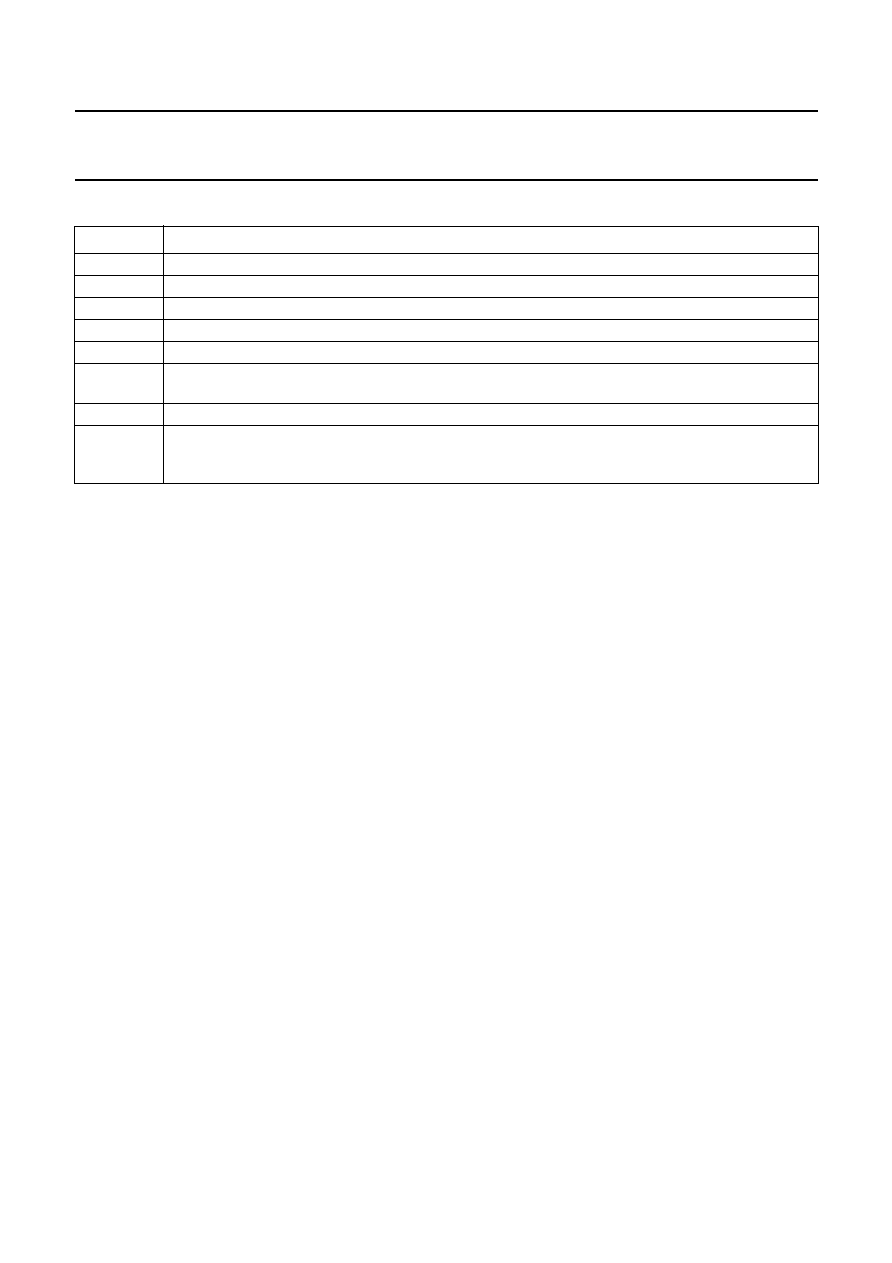

25

Philips Semiconductors

Product specification

160 MHz bus-controlled monitor video

preamplifier

TDA4887PS

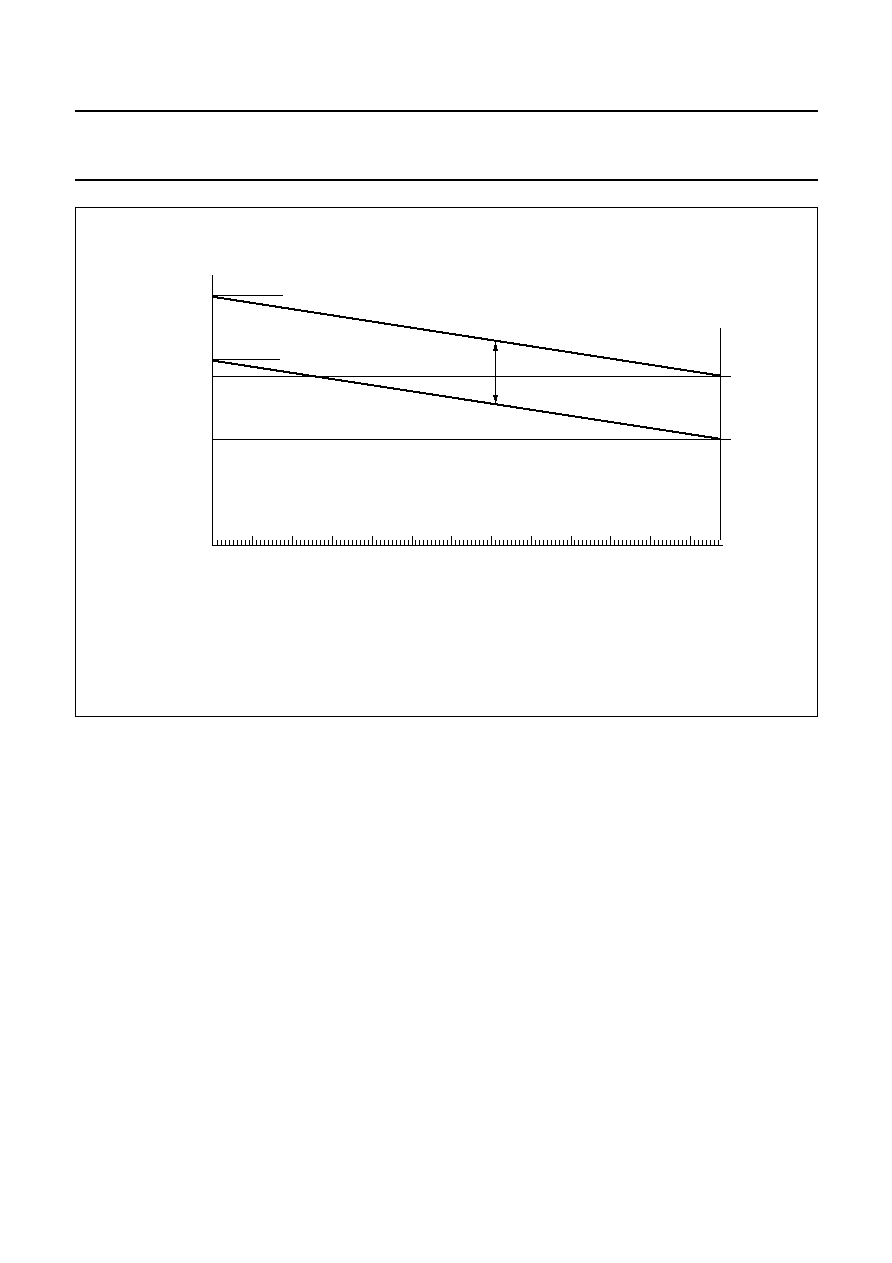

handbook, full pagewidth

signal outputs

at pins 22, 19 and 16

maximum gain setting,

maximum contrast setting,

maximum/nominal/minimum

brightness setting

maximum gain setting,

maximum brightness setting,

maximum/minimum

contrast setting

maximum brightness setting,

maximum contrast setting,

maximum/minimum

gain setting

video black levels

(maximum brightness)

video black level

(maximum brightness)

reference black level

MHB920

reference black level

reference black level

video black levels at

maximum brightness

nominal brightness

minimum brightness

output clamping and

blanking input pulses

at pin 11

switch-off voltage

ground

(1)

(2)

(3)

(1)

(3)

(1)

(3)

switch-off voltage

ground

switch-off voltage

ground

Fig.4 Definition of levels and functions of brightness, contrast and gain with no pedestal blanking.

(1) Maximum.

(2) Nominal.

(3) Minimum.

2001 Oct 19

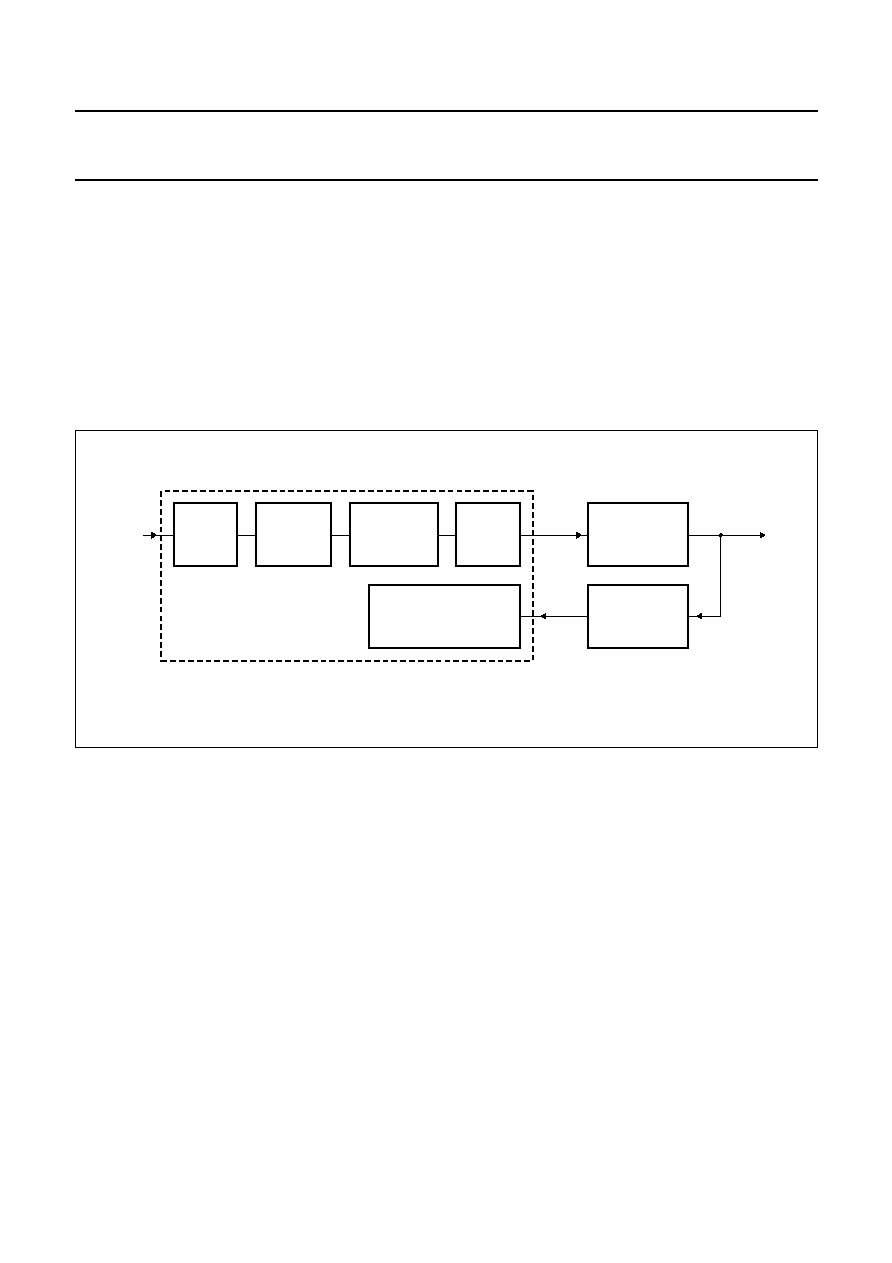

26

Philips Semiconductors

Product specification

160 MHz bus-controlled monitor video

preamplifier

TDA4887PS

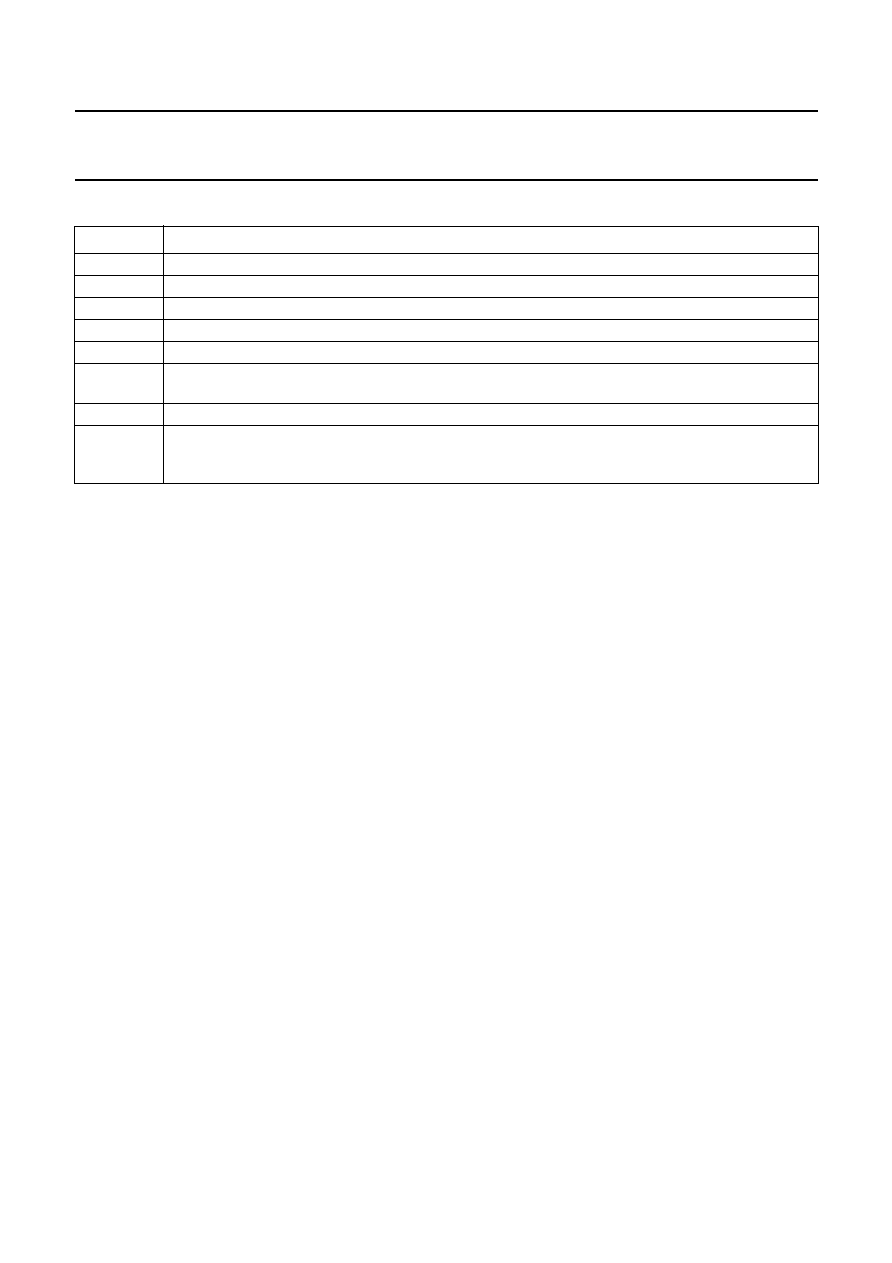

handbook, full pagewidth

no pedestal blanking

maximum gain setting,

maximum contrast setting,

maximum/minimum

brightness setting

reference black level

video black levels at

maximum brightness

minimum brightness

(1)

(2)

switch-off voltage

ground

pedestal blanking

maximum gain setting,

maximum contrast setting,

maximum/minimum

brightness setting

reference black level

pedestal black level

MHB921

video black levels at

maximum brightness

minimum brightness

(1)

(2)

switch-off voltage

ground

signal outputs

at pins 22, 19 and 16

output clamping and

blanking input pulses

at pin 11

Fig.5 Output signals with and without pedestal blanking.

(1) Maximum.

(2) Minimum.

2001 Oct 19