| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: TDA5051AT | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

DATA SHEET

Product specification

Supersedes data of 1997 Sep 19

File under Integrated Circuits, IC11

1999 May 31

INTEGRATED CIRCUITS

TDA5051A

Home automation modem

1999 May 31

2

Philips Semiconductors

Product specification

Home automation modem

TDA5051A

FEATURES

∑

Full digital carrier generation and shaping

∑

Modulation/demodulation frequency set by clock

adjustment, from microcontroller or on-chip oscillator

∑

High clock rate of 6-bit A/D (Digital to Analog) converter

for rejection of aliasing components

∑

Fully integrated output power stage with overload

protection

∑

Automatic Gain Control (AGC) at receiver input

∑

8-bit A/D (Analog to Analog) converter and narrow

digital filtering

∑

Digital demodulation delivering baseband data

∑

Easy compliance with EN50065-1 with simple coupling

network

∑

Few external components for low cost applications

∑

SO16 plastic package.

APPLICATIONS

∑

Home appliance control (air conditioning, shutters,

lighting, alarms and so on)

∑

Energy/heating control

∑

Amplitude Shift Keying (ASK) data transmission using

the home power network.

GENERAL DESCRIPTION

The TDA5051A is a modem IC, specifically dedicated to

ASK transmission by means of the home power supply

network, at 600 or 1200 baud data rate. It operates from a

single 5 V supply.

QUICK REFERENCE DATA

Notes

1. Frequency range corresponding to the EN50065-1 band. However, the modem can operate at any lower oscillator

frequency.

2. The minimum value can be improved by using an external amplifier, see application diagrams Figs 22 and 23.

SYMBOL

PARAMETER

CONDITIONS

MIN.

TYP.

MAX.

UNIT

V

DD

supply voltage

4.75

5.0

5.25

V

I

DD(tot)

total supply current

f

osc

= 8.48 MHz

reception mode

-

28

38

mA

transmission mode (DATA

IN

= 0)

Z

L

= 30

-

47

68

mA

power-down mode

-

19

25

mA

f

cr

carrier frequency

note 1

95

132.5

148.5

kHz

f

osc

oscillator frequency

6.08

8.48

9.504

MHz

V

o(rms)

output carrier signal on CISPR16 load

(RMS value)

120

-

122

dB

µ

V

V

i(rms)

input signal (RMS value)

note 2

82

-

122

dB

µ

V

THD

total harmonic distortion on CISPR16

load with coupling network

-

-

55

-

dB

Z

L

load impedance

1

30

-

BR

baud rate

-

600

1200

bits/s

T

amb

ambient temperature

0

-

70

∞

C

1999 May 31

3

Philips Semiconductors

Product specification

Home automation modem

TDA5051A

ORDERING INFORMATION

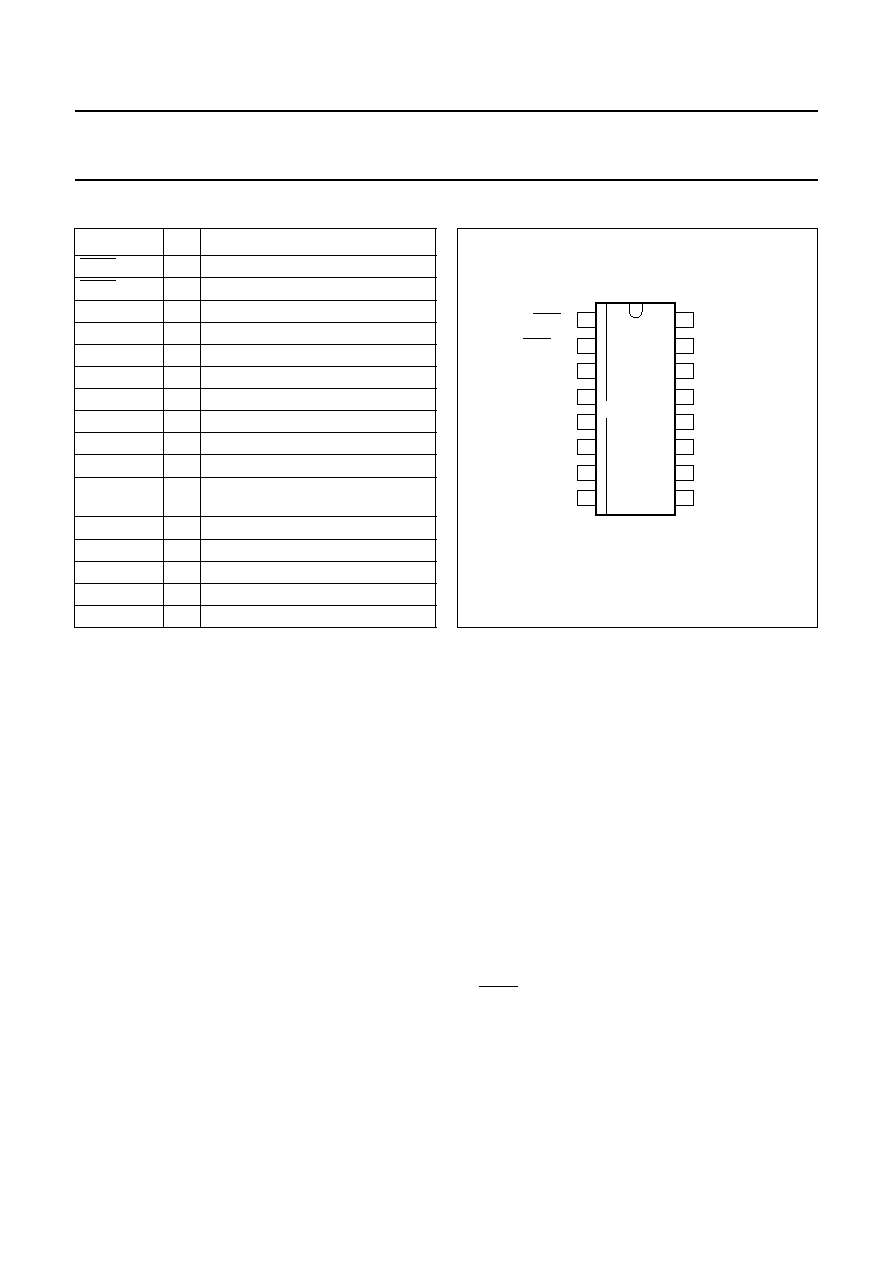

BLOCK DIAGRAM

TYPE

NUMBER

PACKAGE

NAME

DESCRIPTION

VERSION

TDA5051AT

SO16

plastic small outline package; 16 leads; body width 7.5 mm

SOT162-1

Fig.1 Block diagram.

handbook, full pagewidth

MGK832

1

4

7

DGND

5

6

10

AGND

12

VDDA

VDDAP

TXOUT

RXIN

APGND

PD

13

VDDD

3

11

10

9

15

14

8

2

8

U

H

L

D

5

16

ROM

DAC clock

filter clock

OSCILLATOR

DATAOUT

OSC2

OSC1

DIGITAL

DEMODULATOR

DIGITAL

BAND-PASS

FILTER

˜

2

CONTROL LOGIC

D/A

modulated

carrier

TDA5051A

A/D

TEST1

SCANTEST

U/D

COUNT

PEAK

DETECT

POWER

DRIVE

WITH

PROTECTION

6

DATAIN

CLKOUT

1999 May 31

4

Philips Semiconductors

Product specification

Home automation modem

TDA5051A

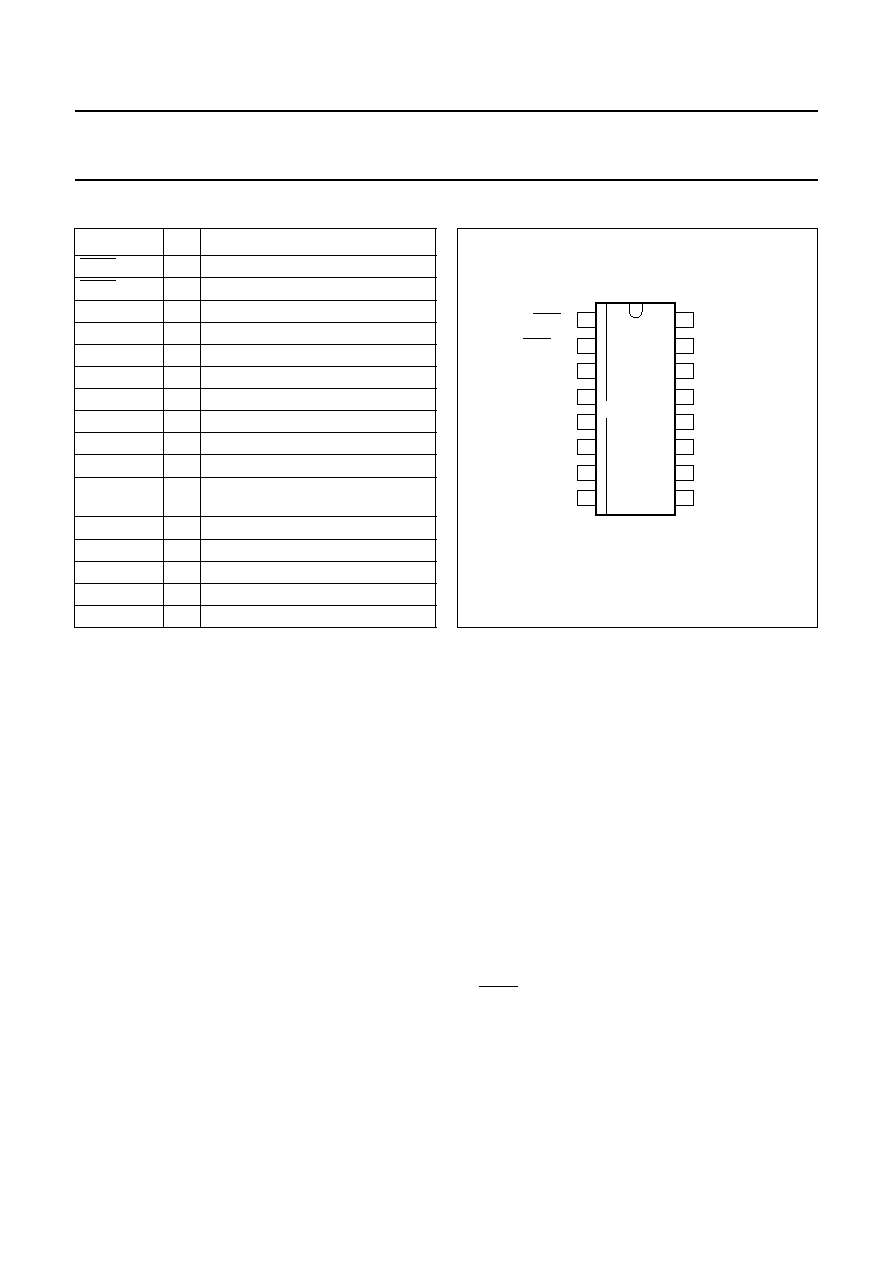

PINNING

SYMBOL

PIN

DESCRIPTION

DATA

IN

1

digital data input (active LOW)

DATA

OUT

2

digital data output (active LOW)

V

DDD

3

digital supply voltage

CLK

OUT

4

clock output

DGND

5

digital ground

SCANTEST

6

test input (LOW in application)

OSC1

7

oscillator input

OSC2

8

oscillator output

APGND

9

analog ground for power amplifier

TX

OUT

10

analog signal output

V

DDAP

11

analog supply voltage for power

amplifier

AGND

12

analog ground

V

DDA

13

analog supply voltage

RX

IN

14

analog signal input

PD

15

power-down input (active HIGH)

TEST1

16

test input (HIGH in application)

Fig.2 Pin configuration.

handbook, halfpage

TDA5051AT

MGK833

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

DATAIN

DATAOUT

VDDD

CLKOUT

DGND

SCANTEST

OSC1

OSC2

APGND

TXOUT

VDDAP

AGND

VDDA

RXIN

PD

TEST1

FUNCTIONAL DESCRIPTION

Both transmission and reception stages are controlled

either by the master clock of the microcontroller or by the

on-chip reference oscillator connected to a crystal. This

ensures the accuracy of the transmission carrier and the

exact trimming of the digital filter, thus making the

performance totally independent of application

disturbances such as component spread, temperature,

supply drift and so on.

The interface with the power network is made by means of

an LC network (see Fig.18). The device includes a power

output stage that feeds a 120 dB

µ

V (RMS) signal on a

typical 30

load.

To reduce power consumption, the IC is disabled by a

power-down input (pin PD): in this mode, the on-chip

oscillator remains active and the clock continues to be

supplied at pin CLK

OUT

. For low-power operation in

reception mode, this pin can be dynamically controlled by

the microcontroller, see Section "Power-down mode".

When the circuit is connected to an external clock

generator (see Fig.6), the clock signal must be applied at

pin OSC1 (pin 7); OSC2 (pin 8) must be left open-circuit.

Fig.7 shows the use of the on-chip clock circuit.

All logic inputs and outputs are compatible with

TTL/CMOS levels, providing an easy connection to a

standard microcontroller I/O port.

The digital part of the IC is fully scan-testable. Two digital

inputs, SCANTEST and TEST1, are used for production

test: these pins must be left open-circuit in functional mode

(correct levels are internally defined by pull-up or

pull-down resistors).

Transmission mode

To provide strict stability with respect to environmental

conditions, the carrier frequency is generated by scanning

the ROM memory under the control of the microcontroller

clock or the reference frequency provided by the on-chip

oscillator. High frequency clocking rejects the aliasing

components to such an extent that they are filtered by the

coupling LC network and do not cause any significant

disturbance. The data modulation is applied through

pin DATA

IN

and smoothly applied by specific digital circuits

to the carrier (shaping). Harmonic components are limited

in this process, thus avoiding unacceptable disturbance of

the transmission channel (according to CISPR16 and

EN50065-1 recommendations). A

-

55 dB Total Harmonic

Distortion (TDH) is reached when the typical LC coupling

network (or an equivalent filter) is used.

1999 May 31

5

Philips Semiconductors

Product specification

Home automation modem

TDA5051A

The DAC and the power stage are set in order to provide

a maximum signal level of 122 dB

µ

V (RMS) at the output.

The output of the power stage (TX

OUT

) must always be

connected to a decoupling capacitor, because of a DC

level of 0.5V

DD

at this pin, which is present even when the

device is not transmitting. This pin must also be protected

against overvoltage and negative transient signals.

The DC level of TX

OUT

can be used to bias a unipolar

transient suppressor, as shown in the application diagram;

see Fig.18.

Direct connection to the mains is done through an LC

network for low-cost applications. However, a HF signal

transformer could be used when power-line insulation has

to be performed.

Reception mode

The input signal received by the modem is applied to a

wide range input amplifier with AGC (

-

6 to +30 dB). This is

basically for noise performance improvement and signal

level adjustment, which ensures a maximum sensitivity of

the ADC. An 8-bit conversion is then performed, followed

by digital band-pass filtering, to meet the CISPR

normalization and to comply with some additional

limitations met in current applications.

CAUTION

In transmission mode, the receiving part of the circuit is

not disabled and the detection of the transmitted signal

is normally performed. In this mode, the gain chosen

before the beginning of the transmission is stored, and

the AGC is internally set to

-

6 dB as long as DATA

IN

is LOW. Then, the old gain setting is automatically

restored.

After digital demodulation, the baseband data signal is

made available after pulse shaping.

The signal pin (RX

IN

) is a high-impedance input which has

to be protected and DC decoupled for the same reasons

as with pin TX

OUT

. The high sensitivity (82 dB

µ

V) of this

input requires an efficient 50 Hz rejection filter (realized by

the LC coupling network), which also acts as an

anti-aliasing filter for the internal digital processing;

see Fig.18.

Data format

T

RANSMISSION MODE

The data input (DATA

IN

) is active LOW: this means that a

burst is generated on the line (pin TX

OUT

) when DATA

IN

pin is LOW.

Pin TX

OUT

is in a high-impedance state as long as the

device is not transmitting. Successive logic 1s are treated

in a Non-Return-to-Zero (NRZ) mode, see pulse shapes in

Figs 8 and 9.

R

ECEPTION MODE

The data output (pin DATA

OUT

) is active LOW; this means

that the data output is LOW when a burst is received.

Pin DATA

OUT

remains LOW as long as a burst is received.

Power-down mode

Power-down input (pin PD) is active HIGH; this means that

the power consumption is minimum when pin PD is HIGH.

Now, all functions are disabled, except clock generation.

LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134).

HANDLING

Inputs and outputs are protected against electrostatic discharge in normal handling. However, to be totally safe, it is

desirable to take normal precautions appropriate to handling MOS devices.

SYMBOL

PARAMETER

MIN.

MAX.

UNIT

V

DD

supply voltage

4.5

5.5

V

f

osc

oscillator frequency

-

12

MHz

T

stg

storage temperature

-

50

+150

∞

C

T

amb

ambient temperature

-

10

+80

∞

C

T

j

junction temperature

-

125

∞

C