Document Outline

- FEATURES

- GENERAL DESCRIPTION

- ORDERING INFORMATION

- SURVEY OF IC TYPES

- QUICK REFERENCE DATA

- BLOCK DIAGRAM

- PINNING

- FUNCTIONAL DESCRIPTION

- I 2 C-BUS SPECIFICATION

- LIMITING VALUES

- THERMAL CHARACTERISTICS

- QUALITY SPECIFICATION

- CHARACTERISTICS

- TEST AND APPLICATION INFORMATION

- PACKAGE OUTLINE

- SOLDERING

- DATA SHEET STATUS

- DEFINITIONS

- DISCLAIMERS

- PURCHASE OF PHILIPS I 2 C COMPONENTS

DATA SHEET

Preliminary specification

Supersedes data of 2000 May 08

2002 Jun 04

INTEGRATED CIRCUITS

TDA933xH series

I

2

C-bus controlled TV display

processors

2002 Jun 04

2

Philips Semiconductors

Preliminary specification

I

2

C-bus controlled TV display processors

TDA933xH series

FEATURES

Available in all ICs:

∑

Can be used in both single scan (50 or 60 Hz) and

double scan (100 or 120 Hz) applications

∑

YUV input and linear RGB input with fast blanking

∑

Separate OSD/text input with fast blanking or blending

∑

Black stretching of non-standard luminance signals

∑

Switchable matrix for the colour difference signals

∑

RGB control circuit with Continuous Cathode Calibration

(CCC), plus white point and black level offset

adjustment

∑

Blue stretch circuit which offsets colours near white

towards blue

∑

Internal clock generation for the deflection processing,

which is synchronized by a 12 MHz ceramic resonator

oscillator

∑

Horizontal synchronization with two control loops and

alignment-free horizontal oscillator

∑

Slow start and slow stop of the horizontal drive pulses

∑

Low-power start-up option for the horizontal drive circuit

∑

Vertical count-down circuit

∑

Vertical driver optimized for DC-coupled vertical output

stages

∑

Vertical and horizontal geometry processing

∑

Horizontal and vertical zoom possibility and vertical

scroll function for application with 16 : 9 picture tubes

∑

Horizontal parallelogram and bow correction

∑

I

2

C-bus control of various functions

∑

Low dissipation.

GENERAL DESCRIPTION

The TDA933xH series are display processors for

`High-end' television receivers which contain the following

functions:

∑

RGB control processor with Y, U and V inputs, a linear

RGB input for SCART or VGA signals with fast blanking,

a linear RGB input for OSD and text signals with a fast

blanking or blending option and an RGB output stage

with black current stabilization, which is realized with the

CCC (2-point black current measurement) system.

∑

Programmable deflection processor with internal clock

generation, which generates the drive signals for the

horizontal, East-West (E-W) and vertical deflection.

The circuit has various features that are attractive for the

application of 16 : 9 picture tubes.

∑

The circuit can be used in both single scan (50 or 60 Hz)

and double scan (100 or 120 Hz) applications.

In addition to these functions, the TDA9331H and

TDA9332H have a multi-sync function for the horizontal

PLL, with a frequency range from 30 to 50 kHz (2f

H

mode)

or 15 to 25 kHz (1f

H

mode), so that the ICs can also be

used to display SVGA signals.

The supply voltage of the ICs is 8 V. They are each

contained in a 44-pin QFP package.

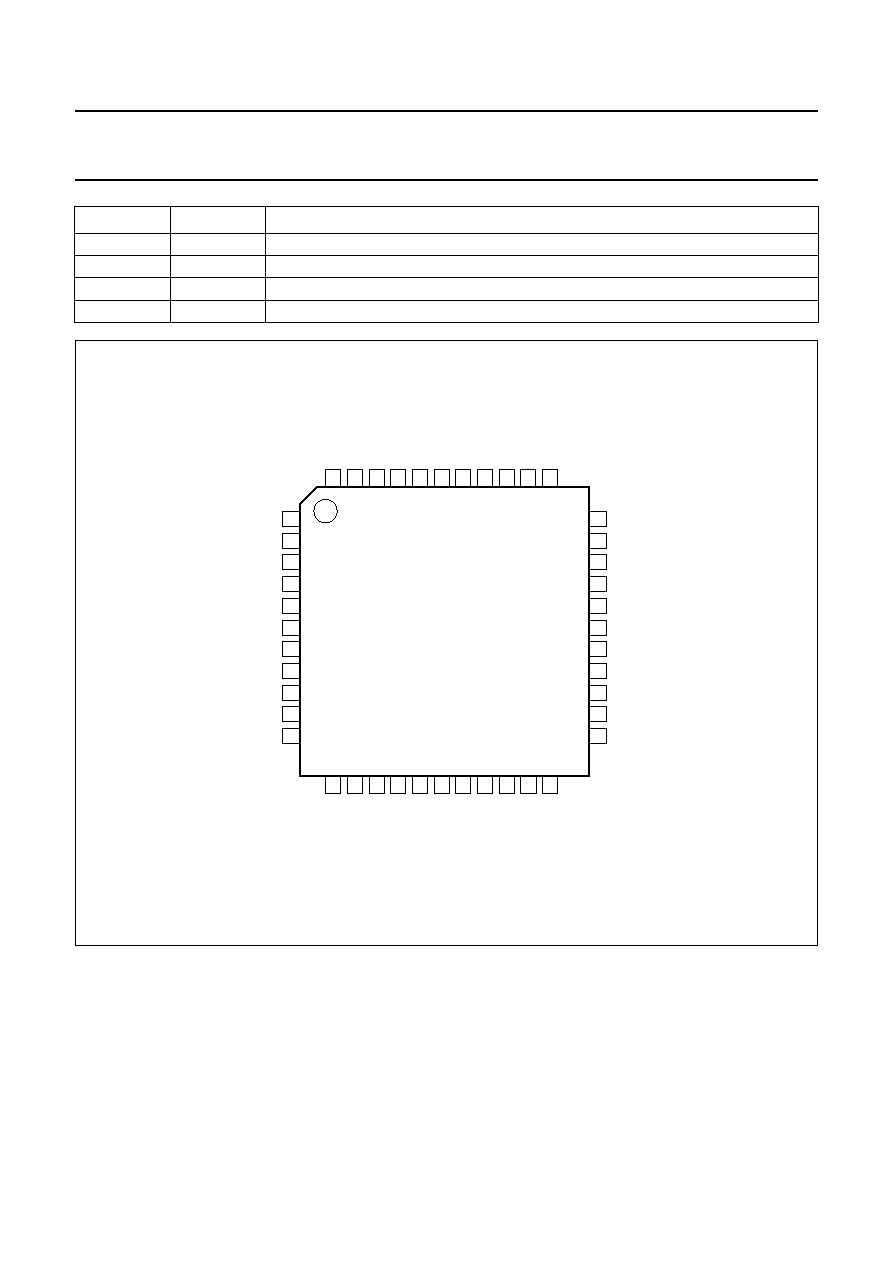

ORDERING INFORMATION

TYPE

NUMBER

PACKAGE

NAME

DESCRIPTION

VERSION

TDA9330H

QFP44

plastic quad flat package; 44 leads (lead length 1.3 mm);

body 10

◊

10

◊

1.75 mm

SOT307-2

TDA9331H

TDA9332H

2002 Jun 04

3

Philips Semiconductors

Preliminary specification

I

2

C-bus controlled TV display processors

TDA933xH series

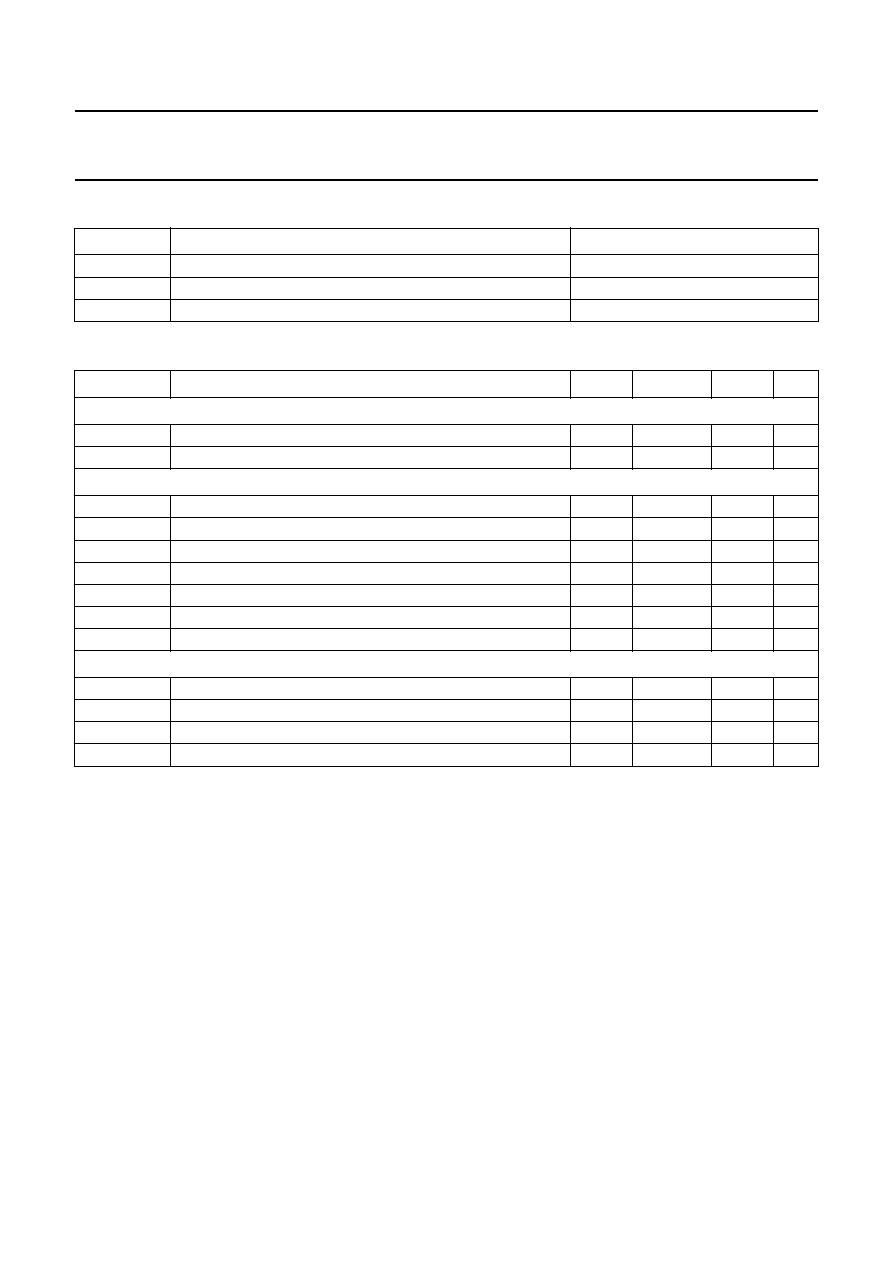

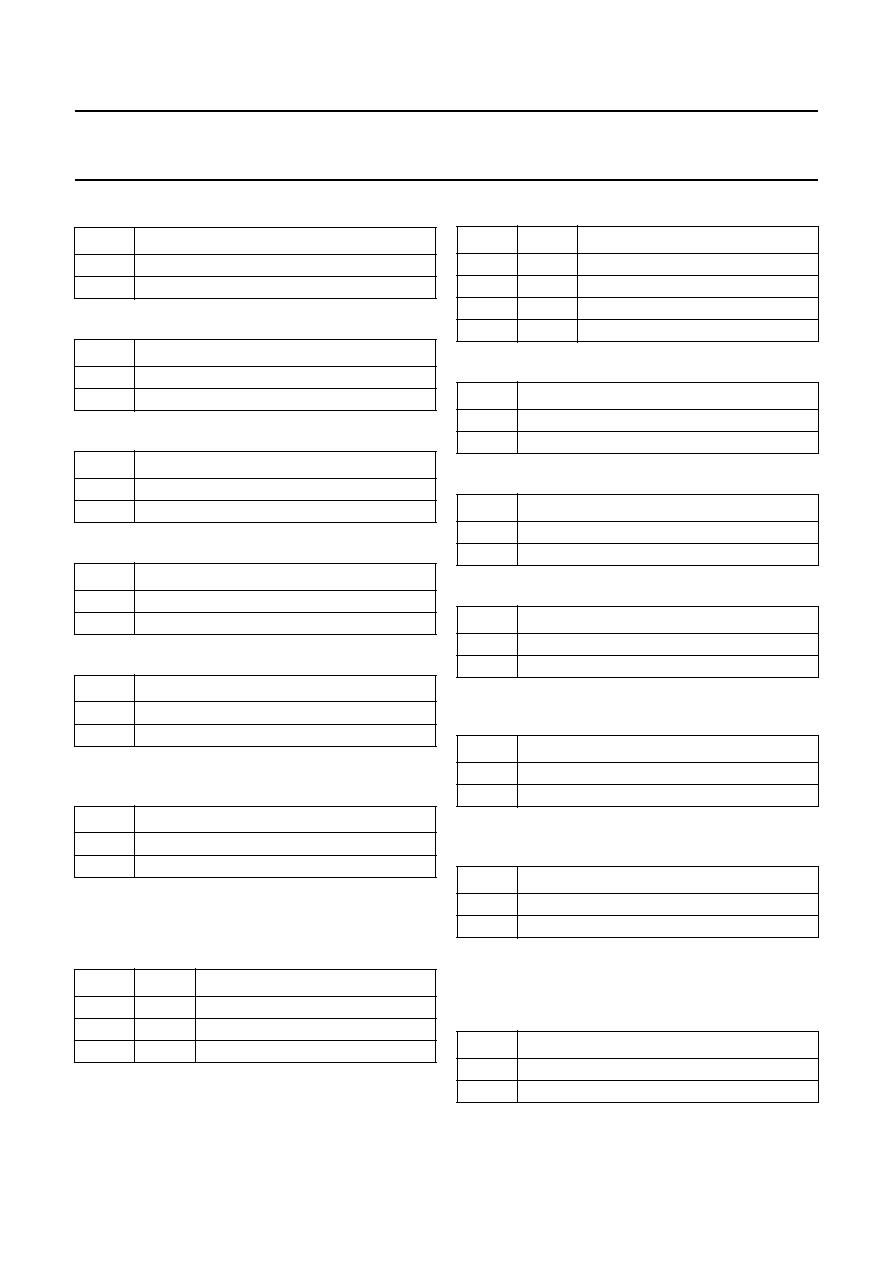

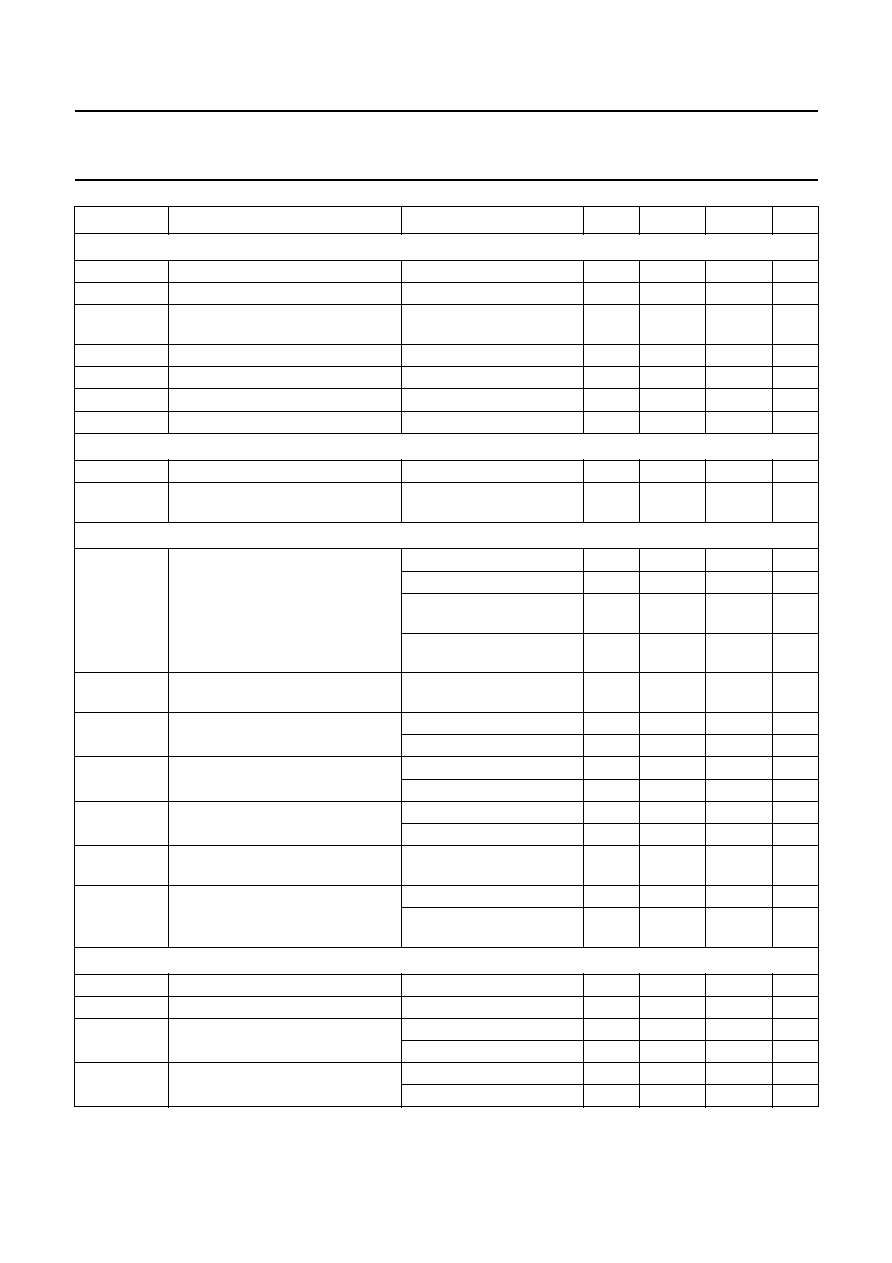

SURVEY OF IC TYPES

QUICK REFERENCE DATA

IC VERSION

VGA MODE

DAC OUTPUT

TDA9330H

no

I

2

C-bus controlled

TDA9331H

yes

proportional to VGA frequency

TDA9332H

yes

I

2

C-bus controlled

SYMBOL

PARAMETER

MIN.

TYP.

MAX.

UNIT

Supply

V

P

supply voltage

-

8.0

-

V

I

P

supply current (V

P1

plus V

P2

)

-

50

-

mA

Input voltages

V

i(Y)(b-w)

luminance input signal (black-to-white value)

-

1.0/0.315

-

V

V

i(U)(p-p)

U input signal (peak-to-peak value)

-

1.33

-

V

V

i(V)(p-p)

V input signal (peak-to-peak value)

-

1.05

-

V

V

i(RGB)(b-w)

RGB input signal (black-to-white value)

-

0.7

-

V

V

i(Hsync)

horizontal sync input (H

D

)

-

TTL

-

V

V

i(Vsync)

vertical sync input (V

D

)

-

TTL

-

V

V

i(IIC)

I

2

C-bus inputs (SDA and SCL)

-

CMOS 5 V

-

V

Output signals

V

o(RGB)(b-w)

RGB output signal amplitude (black-to-white value)

-

2.0

-

V

I

o(hor)

horizontal output current

-

-

10

mA

I

o(ver)(p-p)

vertical output current (peak-to-peak value)

-

0.95

-

mA

I

o(EW)

E-W drive output current

-

-

1.2

mA

2002

Jun

04

4

Philips Semiconductors

Preliminar

y specification

I

2

C-b

us controlled TV displa

y processors

TD

A933xH ser

ies

2002

Jun

04

4

Philips Semiconductors

Preliminar

y specification

I

2

C-b

us controlled TV displa

y processors

TD

A933xH ser

ies

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

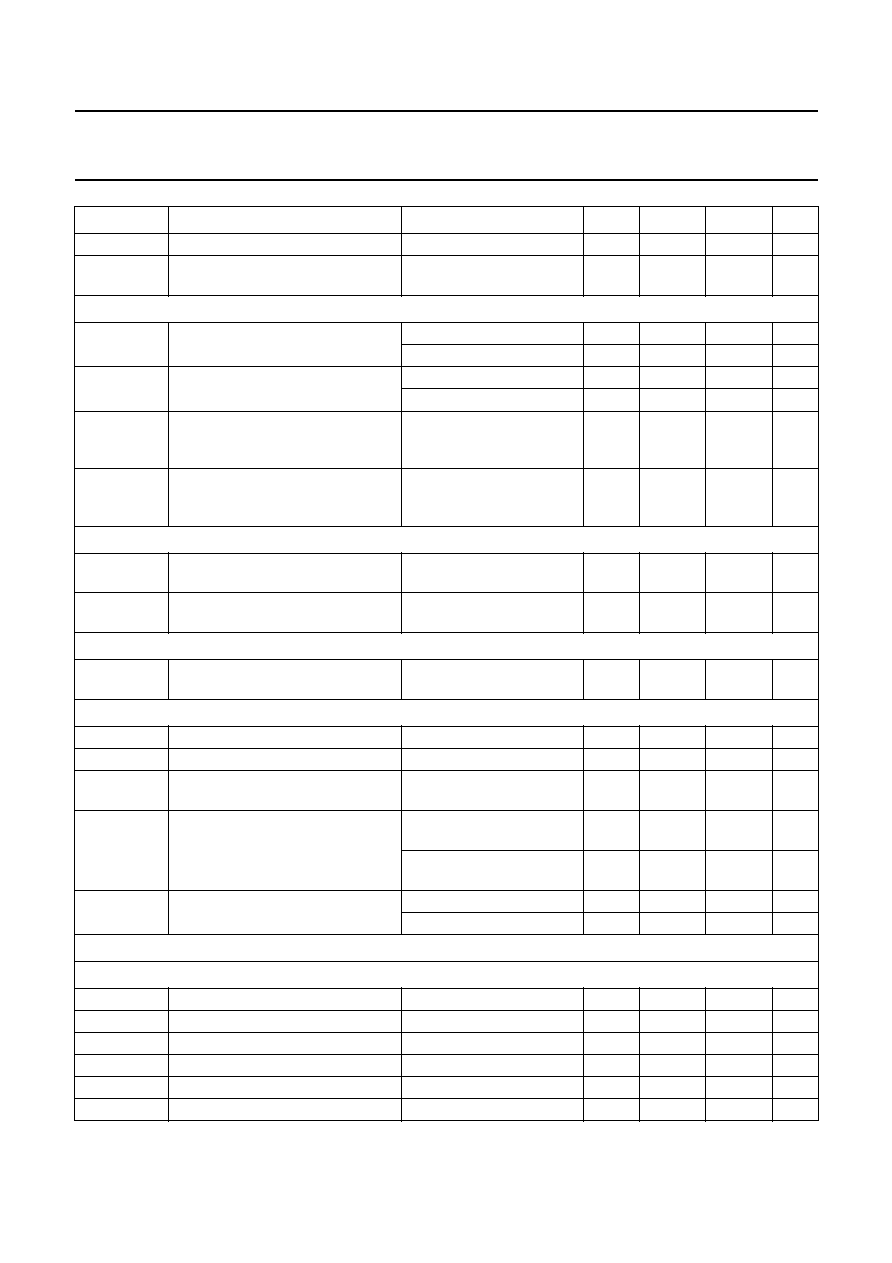

BLOCK DIA

GRAM

handbook, full pagewidth

MGR445

SWITCH

Y

Y

U

V

SAT

CONTR

U

V

SATURATION

CONTROL

COLOUR

DIFFERENCE

MATRIX

R

G

B

CONTRAST

CONTROL

R

G

B

RGB

INSERTION

R

G

G

B

BRI

white

point

WHITE POINT

AND

BRIGHTNESS

CONTROL

R

B

OUTPUT

AMPLIFIER

AND

BUFFER

BLUE STRETCH

40

41

42

28

27

26

YIN

UIN

VIN

RGB-YUV

MATRIX

BLACK

STRETCH

PWL

AND

BEAM

CURRENT

LIMITER

CONTINUOUS

CATHODE

CALIBRATION

44

30

31

32

RI1

GI1

BI1

SUPPLY

H-SHIFT

SOFT

START/STOP

LOW-POWER

START-UP

H/V DIVIDER

19

◊

6-BIT DACs

2

◊

4-BIT DACs

I

2

C-BUS

TRANSCEIVER

10

43

11

25

18

6

19

17

7

39

DECBG

GND1

GND2

23

VP1

DECVD

VP2

CLOCK

GENERATION

AND

1st LOOP

20

21

13

14

22

PHASE-2

LOOP

HORIZONTAL

OUTPUT

15

16

VSC

Iref

RAMP

GENERATOR

1

2

4

VERTICAL

GEOMETRY

3

E-W

GEOMETRY

GEOMETRY CONTROL

24

12

HSEL

33

29

38

37

36

35

34

TDA933xH

BL1

FBCSO

BL2

GI2

RI2

PWL

BI2

BCL

BO

GO

RO

BLKIN

DACOUT

SDA

SCL

VDOA

5

8

9

VDOB

EWO

EHTIN

XTALI

XTALO

LPSU

FLASH

HOUT

SCO

HFB

DPC

HD

VD

Fig.1 Block diagram.

2002 Jun 04

5

Philips Semiconductors

Preliminary specification

I

2

C-bus controlled TV display processors

TDA933xH series

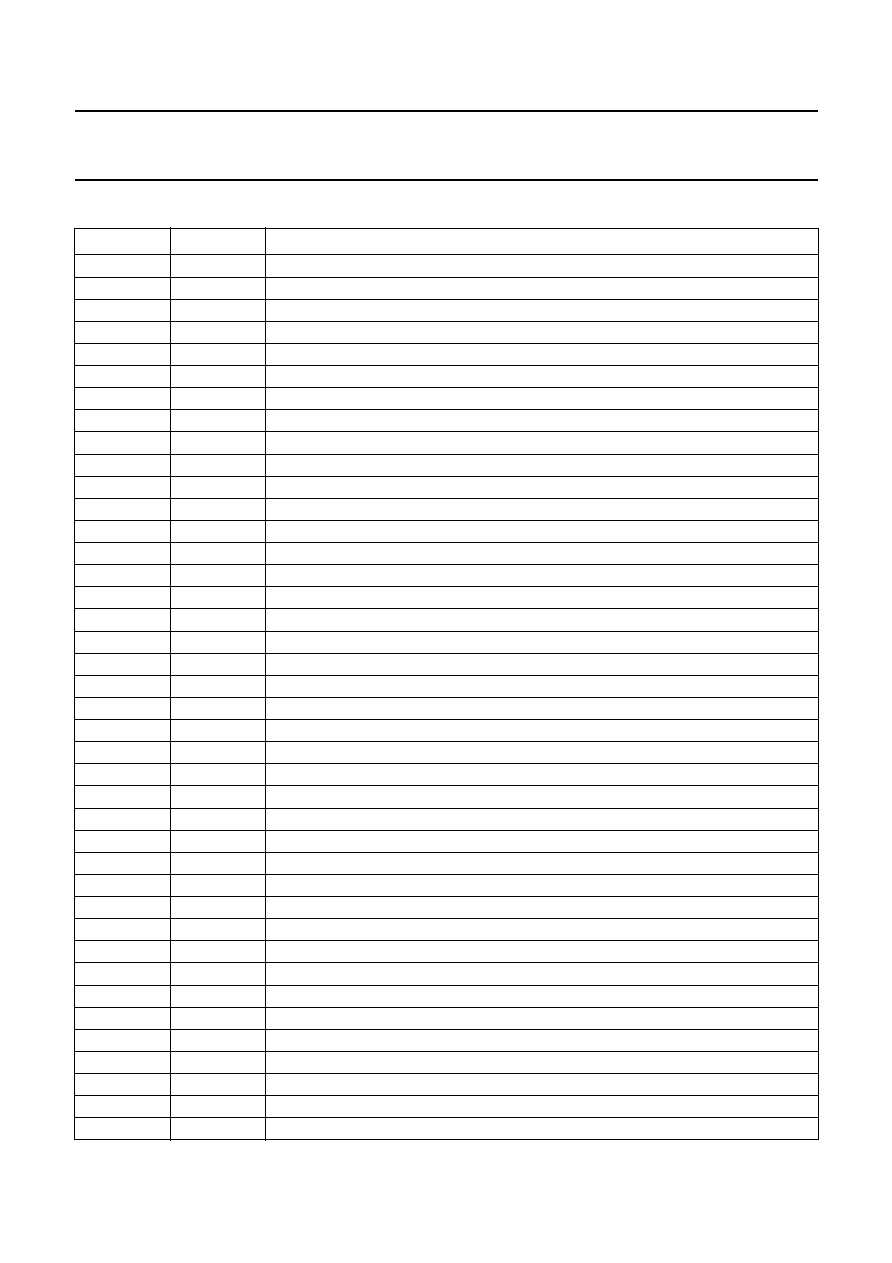

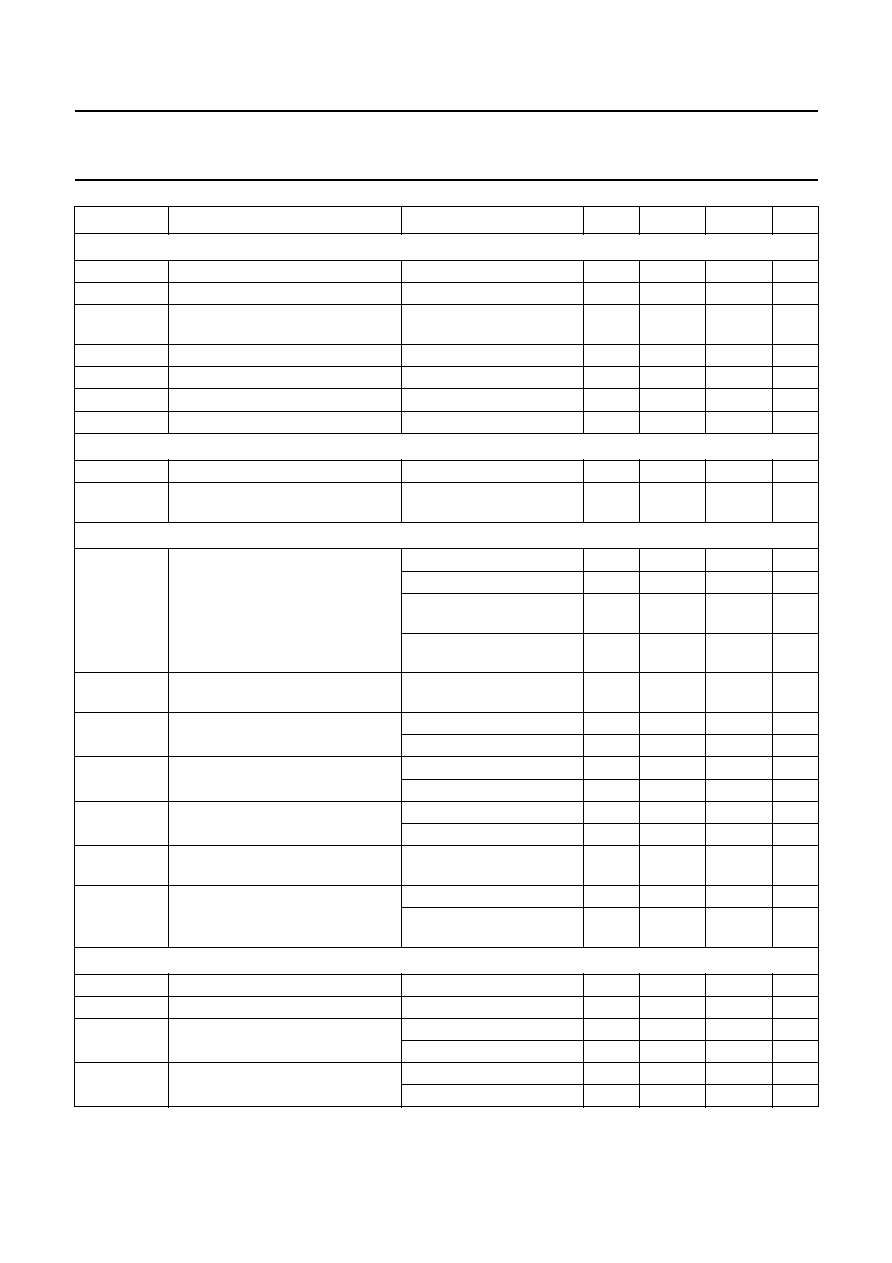

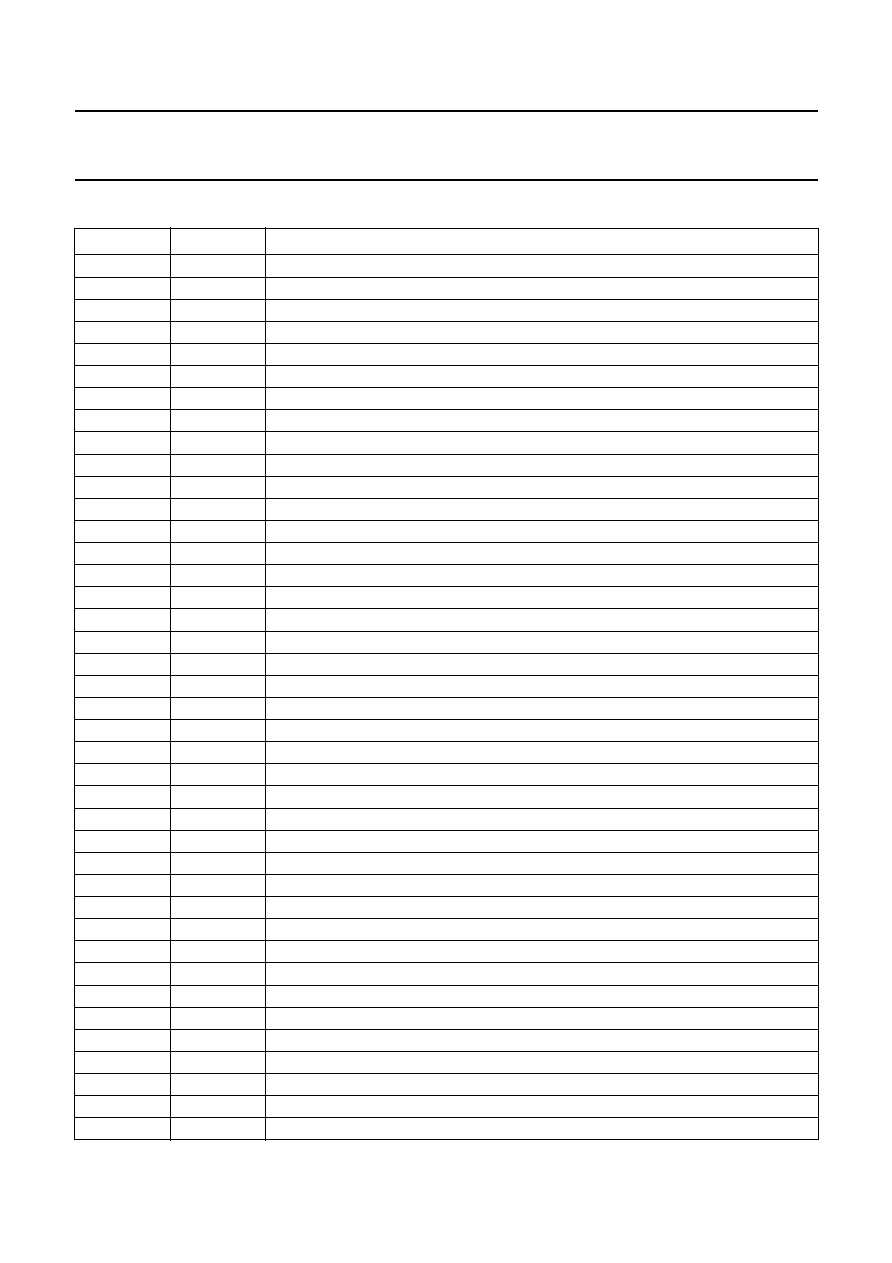

PINNING

SYMBOL

PIN

DESCRIPTION

VDOA

1

vertical drive output A

VDOB

2

vertical drive output B

EWO

3

E-W output

EHTIN

4

EHT compensation input

FLASH

5

flash detection input

GND1

6

ground 1

DEC

VD

7

digital supply decoupling

HOUT

8

horizontal output

SCO

9

sandcastle pulse output

SCL

10

serial clock input

SDA

11

serial data input/output

HSEL

12

selection of horizontal frequency

HFB

13

horizontal flyback pulse input

DPC

14

dynamic phase compensation

VSC

15

vertical sawtooth capacitor

I

ref

16

reference current input

V

P1

17

positive supply 1 (+8 V)

DEC

BG

18

band gap decoupling

GND2

19

ground 2

XTALI

20

crystal input

XTALO

21

crystal output

LPSU

22

low-power start-up supply

V

D

23

vertical sync input

H

D

24

horizontal sync input

DACOUT

25

DAC output

VIN

26

V-signal input

UIN

27

U-signal input

YIN

28

luminance input

FBCSO

29

fixed beam current switch-off input

RI1

30

red 1 input for insertion

GI1

31

green 1 input for insertion

BI1

32

blue 1 input for insertion

BL1

33

fast blanking input for RGB-1

PWL

34

peak white limiting decoupling

RI2

35

red 2 input for insertion

GI2

36

green 2 input for insertion

BI2

37

blue 2 input for insertion

BL2

38

fast blanking/blending input for RGB-2

V

P2

39

positive supply 2 (+8 V)

RO

40

red output

2002 Jun 04

6

Philips Semiconductors

Preliminary specification

I

2

C-bus controlled TV display processors

TDA933xH series

GO

41

green output

BO

42

blue output

BCL

43

beam current limiting input

BLKIN

44

black current input

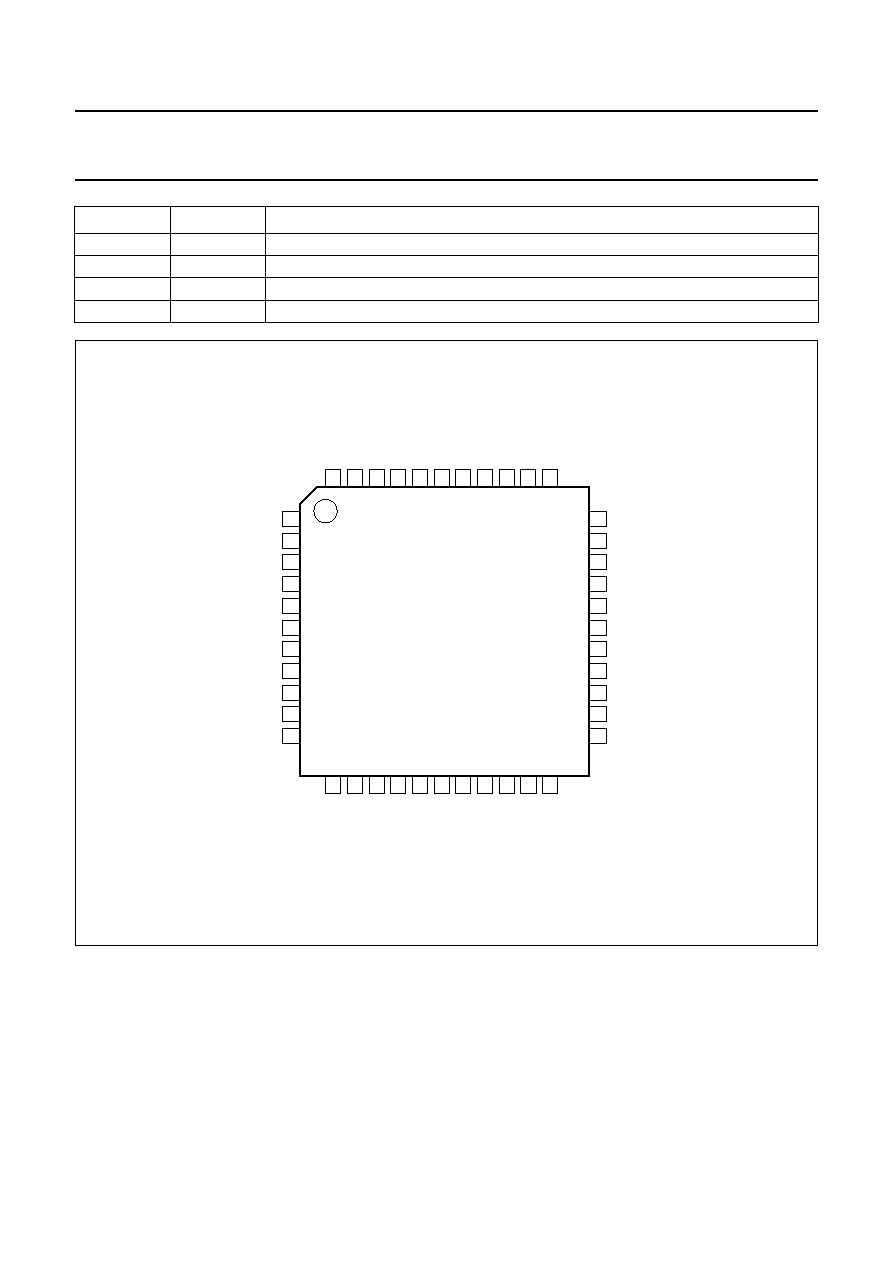

SYMBOL

PIN

DESCRIPTION

handbook, full pagewidth

1

2

3

4

5

6

7

8

9

10

11

33

32

31

30

29

28

27

26

25

24

23

12

13

14

15

16

17

18

19

20

21

22

44

43

42

41

40

39

38

37

36

35

34

TDA933xH

MGR446

BL1

BI1

GI1

RI1

YIN

UIN

VIN

DACOUT

HD

VD

VDOA

VDOB

EWO

EHTIN

FLASH

GND1

HOUT

SCO

SDA

FBCSO

BCL

BO

GO

RO

V

P2

BL2

GI2

RI2

PWL

BLKIN

BI2

HFB

DPC

VSC

I ref

V

P1

DEC

BG

XTALI

XTALO

LPSU

HSEL

GND2

DECVD

SCL

Fig.2 Pin configuration.

2002 Jun 04

7

Philips Semiconductors

Preliminary specification

I

2

C-bus controlled TV display processors

TDA933xH series

FUNCTIONAL DESCRIPTION

RGB control circuit

I

NPUT SIGNALS

The RGB control circuit of the TDA933xH contains three

sets of input signals:

∑

YUV input signals, which are supplied by the input

processor or the feature box. Bit GAI can be used to

switch the luminance input signal sensitivity between

0.45 V (p-p) and 1.0 V (b-w). The nominal input signals

for U and V are 1.33 V (p-p) and 1.05 V (p-p),

respectively. These input signals are controlled on

contrast, saturation and brightness.

∑

The first RGB input is intended for external signals

(SCART in 1f

H

and VGA in 2f

H

applications), which have

an amplitude of 0.7 V (p-p) typical. This input is also

controlled on contrast, saturation and brightness.

∑

The second RGB input is intended for OSD and teletext

signals. The required input signals have an amplitude of

0.7 V (p-p). The switching between the internal signal

and the OSD signal can be realized via a blending

function or via fast blanking. This input is only controlled

on brightness.

Switching between the various sources can be realized via

the I

2

C-bus and by fast insertion switches. The fast

insertion switches can be enabled via the I

2

C-bus.

The circuit contains switchable matrix circuits for the

colour difference signals so that the colour reproduction

can be adapted for PAL/SECAM and NTSC. For NTSC,

two different matrices can be chosen. In addition, a matrix

for high-definition ATSC signals is available.

O

UTPUT AMPLIFIER

The output signal has an amplitude of approximately

2 V (b-w) at nominal input signals and nominal settings of

the controls. The required `white point setting' of the

picture tube can be realized by means of three separate

gain settings for the RGB channels.

To obtain an accurate biasing of the picture tube, a CCC

circuit has been developed. This function is realized by a

2-point black level stabilization circuit.

By inserting two test levels for each gun and comparing the

resulting cathode currents with two different reference

currents, the influence of the picture tube parameters such

as the spread in cut-off voltage can be eliminated.

This 2-point stabilization is based on the principle that the

ratio between the cathode currents is coupled to the ratio

between the drive voltages according to:

The feedback loop makes the ratio between cathode

currents I

k1

and I

k2

equal to the ratio between the

reference currents (which are internally fixed) by changing

the (black) level and the amplitude of the RGB output

signals via two converging loops. The system operates in

such a way that the black level of the drive signal is

controlled to the cut-off point of the gun. In this way, a very

good grey scale tracking is obtained. The accuracy of the

adjustment of the black level is only dependent on the ratio

of internal currents and these can be made very accurately

in integrated circuits. An additional advantage of the

2-point measurement is that the control system makes the

absolute value of I

k1

and I

k2

identical to the internal

reference currents. Because this adjustment is obtained

by adapting the gain of the RGB control stage, this control

stabilizes the gain of the complete channel (RGB output

stage and cathode characteristic). As a result, this 2-point

loop compensates for variations in the gain figures during

life.

An important property of the 2-point stabilization is that the

offset and the gain of the RGB path are adjusted by the

feedback loop. Hence, the maximum drive voltage for the

cathode is fixed by the relationship between the test

pulses, the reference current and the relative gain setting

of the three channels. Consequently, the drive level of the

CRT cannot be adjusted by adapting the gain of the RGB

output stage. Because different picture tubes may require

different drive levels, the typical `cathode drive level'

amplitude can be adjusted by means of an I

2

C-bus setting.

Depending on the selected cathode drive level, the typical

gain of the RGB output stages can be fixed, taking into

account the drive capability of the RGB outputs

(pins 40 to 42). More details about the design are given in

the application report (see also Chapter "Characteristics";

note 11).

The measurement of the high and the low currents of the

2-point stabilization circuit is performed in two consecutive

fields. The leakage current is measured in each field. The

maximum allowable leakage current is 100

µ

A.

For extra flexibility, it also possible to switch the CCC

circuit to 1-point stabilization with the OPC bit. In this

mode, only the black level at the RGB outputs is controlled

by the loop. The cathode drive level setting has no

influence on the gain in this mode. This level should be set

to the nominal value to get the correct amplitude of the

measuring pulses.

I

k1

I

k2

-------

V

dr1

V

dr1

-----------

=

2002 Jun 04

8

Philips Semiconductors

Preliminary specification

I

2

C-bus controlled TV display processors

TDA933xH series

Via the I

2

C-bus, an adjustable offset can be made on the

black level of red and green channels with respect to the

level that is generated by the black current control loop.

These controls can be used to adjust the colour

temperature of the dark part of the picture, independent of

the white point adjustment.

When the TV receiver is switched on, the black current

stabilization circuit is directly activated and the RGB

outputs are blanked. The blanking is switched off as soon

as the loop has stabilized (e.g. the first time that bit BCF

changes from 1 to 0, see also Chapter "Characteristics";

note 15). This ensures that the switch-on time is reduced

to a minimum and is only dependent on the warm-up time

of the picture tube.

The black current stabilization system checks the output

level of the three channels and indicates whether the black

level of the lowest RGB output of the IC is in a certain

window (WBC bit), below or above this window (HBC bit).

This indication can be read from the I

2

C-bus and can be

used for automatic adjustment of voltage V

g2

during the

production of the TV receiver.

When a failure occurs in the black current loop (e.g. due to

an open circuit), status bit BCF is set. This information can

be used to blank the picture tube to avoid damage to the

screen.

The control circuit contains an average beam current

limiting circuit and a peak white level (PWL) circuit. The

PWL detects small white areas in the picture that are not

detected by the average beam current limiter. The PWL

can be adjusted via the I

2

C-bus. A low-pass filter is placed

in front of the peak detector to prevent it from reacting to

short transients in the video signal. The capacitor of the

low-pass filter is connected externally so that the set

maker can adapt the time constant as required. The IC

also contains a soft clipper that limits the amplitude of the

short transients in the RGB output signals. In this way, spot

blooming on, for instance, subtitles is prevented. The

difference between the PWL and the soft clipping level can

be adjusted via the I

2

C-bus in a few steps.

The vertical blanking is adapted to the vertical frequency

of the incoming signal (50 or 100 Hz or, 60 or 120 Hz).

When the flyback time of the vertical output stage is

greater than the 60 Hz blanking time, the blanking can be

increased to the same value as that of the 50 Hz blanking.

This can be set by means of bit LBM.

When no video is available, it is possible to insert a blue

background. This feature can be activated via bit EBB.

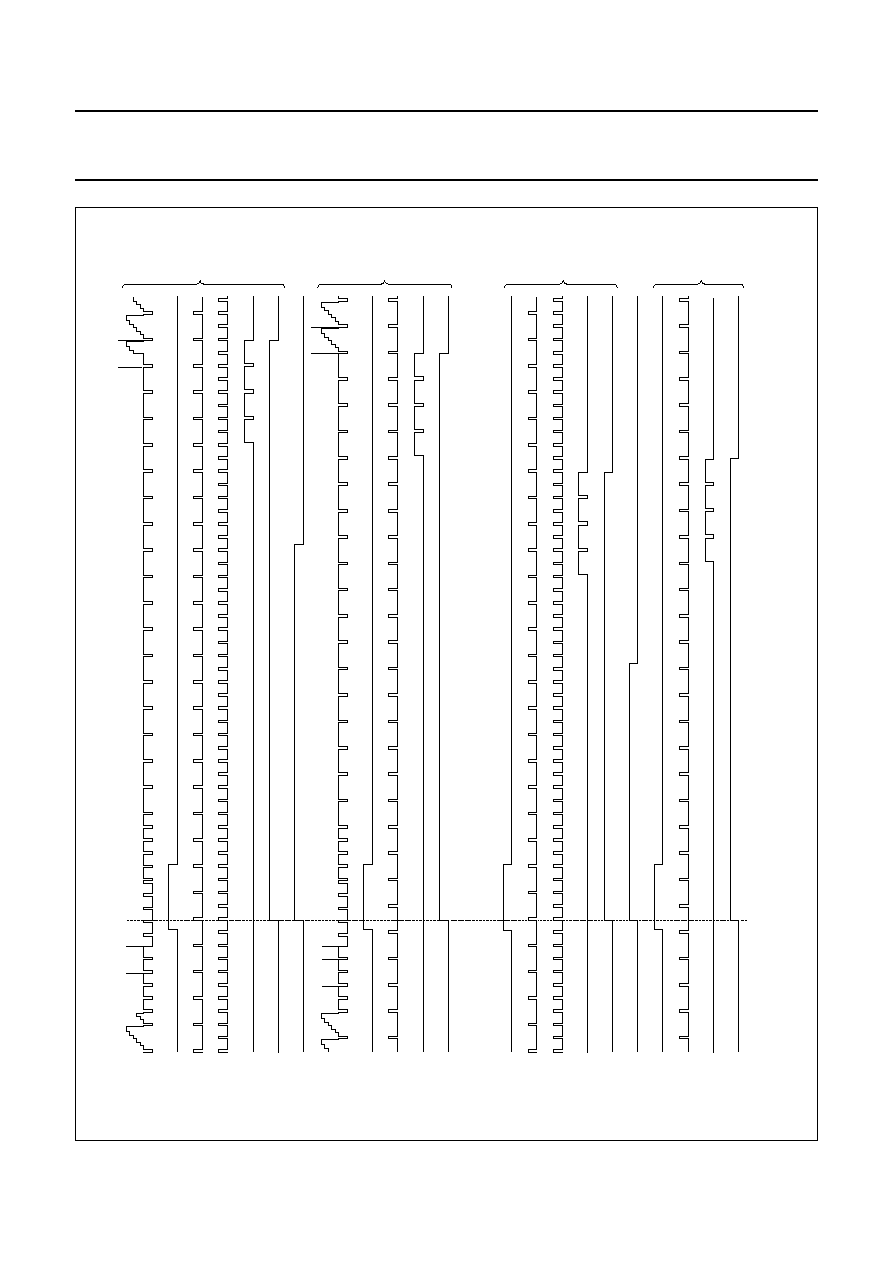

Synchronization and deflection processing

H

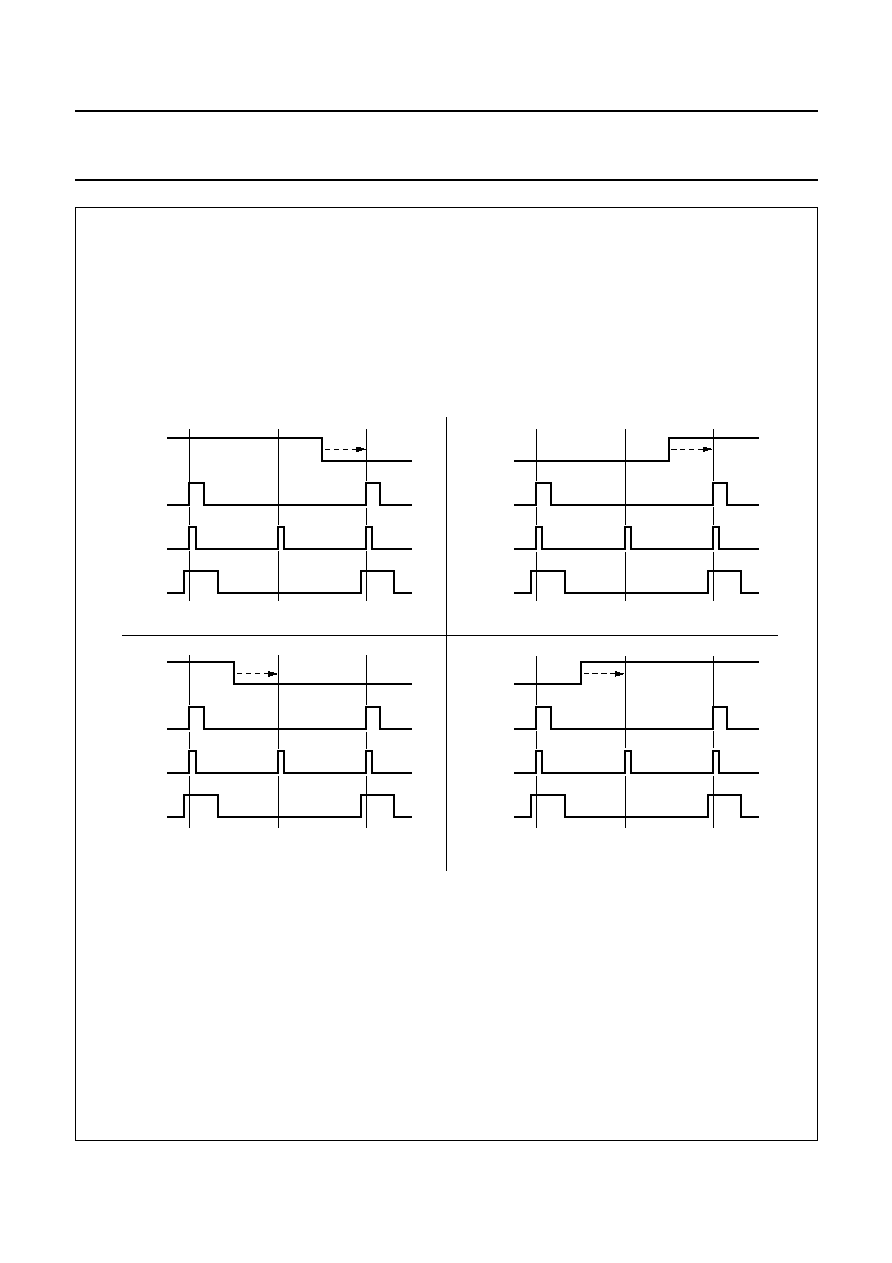

ORIZONTAL SYNCHRONIZATION AND DRIVE CIRCUIT

The horizontal drive signal is obtained from an internal

VCO which runs at a frequency of 440 times (2f

H

mode) or

880 times (1f

H

mode) the frequency of the incoming H

D

signal. The free-running frequency of this VCO is

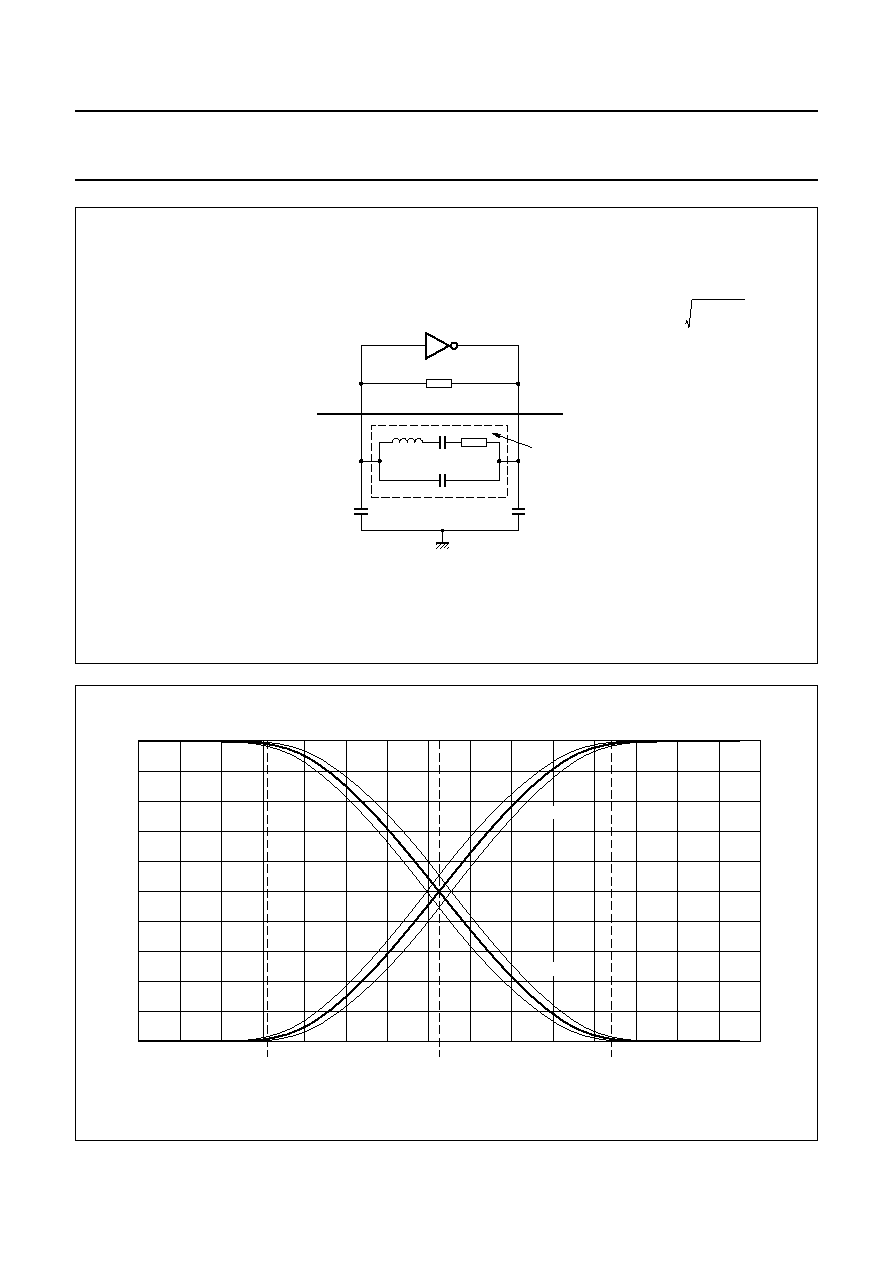

calibrated by a crystal oscillator which needs an external

12 MHz crystal or ceramic resonator as a reference. It is

also possible to supply an external reference signal to the

IC (in this case, the external resonator should be

removed).

The VCO is synchronized to the incoming horizontal H

D

pulse (applied from the feature box or the input processor)

by a PLL with an internal time constant. The frequency of

the horizontal drive signal (1f

H

or 2f

H

) is selected by means

of a switching pin, which must be connected to ground or

left open-circuit.

For HDTV applications, it is possible to change the

free-running frequency of the horizontal drive output. For

the 1080i-60 Hz scanning system the free-running

frequency can be increased to 33.8 kHz with the HDTV bit,

while for the 1080i-50 Hz system (China and Australia) the

free-running frequency can be decreased to 28.5 kHz with

the CDTV bit.

For safety reasons, switching between 1f

H

and 2f

H

modes is only possible when the IC is in the standby

mode.

For the TDA9331H and TDA9332H, it is also possible to

set the horizontal PLL to a `multi-sync' mode by means of

bit VGA. In this mode, the circuit detects the frequency of

the incoming sync pulses and adjusts the centre frequency

of the VCO accordingly by means of an internal

Digital-to-Analog-Converter (DAC). The frequency range

in this mode is 30 to 50 kHz at the output.

The polarities of the incoming H

D

and V

D

pulses are

detected internally. The detected polarity can be read out

via status bits HPOL and VPOL.

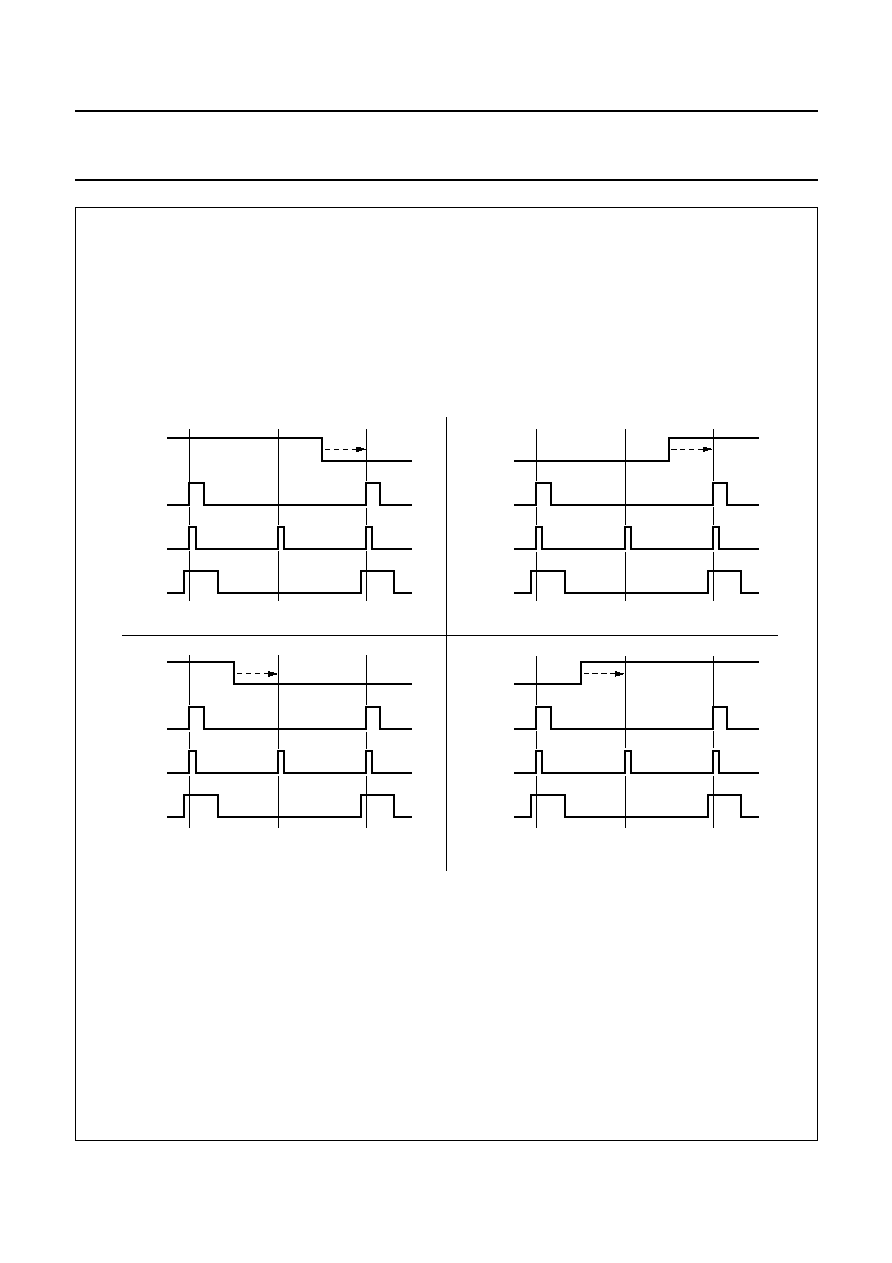

The horizontal drive signal is generated by a second

control loop which compares the phase of the reference

signal (applied from the internal VCO) with the flyback

pulse. The time constant of this loop is set internally. The

IC has a dynamic horizontal phase correction input, which

can be used to compensate phase shifts that are caused

by beam current variations. Additional settings of the

horizontal deflection (which are realized via the second

loop) are the horizontal shift and horizontal parallelogram

and bow corrections (see Chapter "Characteristics";

Fig.16). The adjustments are realized via the I

2

C-bus.

2002 Jun 04

9

Philips Semiconductors

Preliminary specification

I

2

C-bus controlled TV display processors

TDA933xH series

When no horizontal flyback pulse is detected during three

consecutive line periods, status bit NHF is set (output

status byte 01-D3; see Table 3).

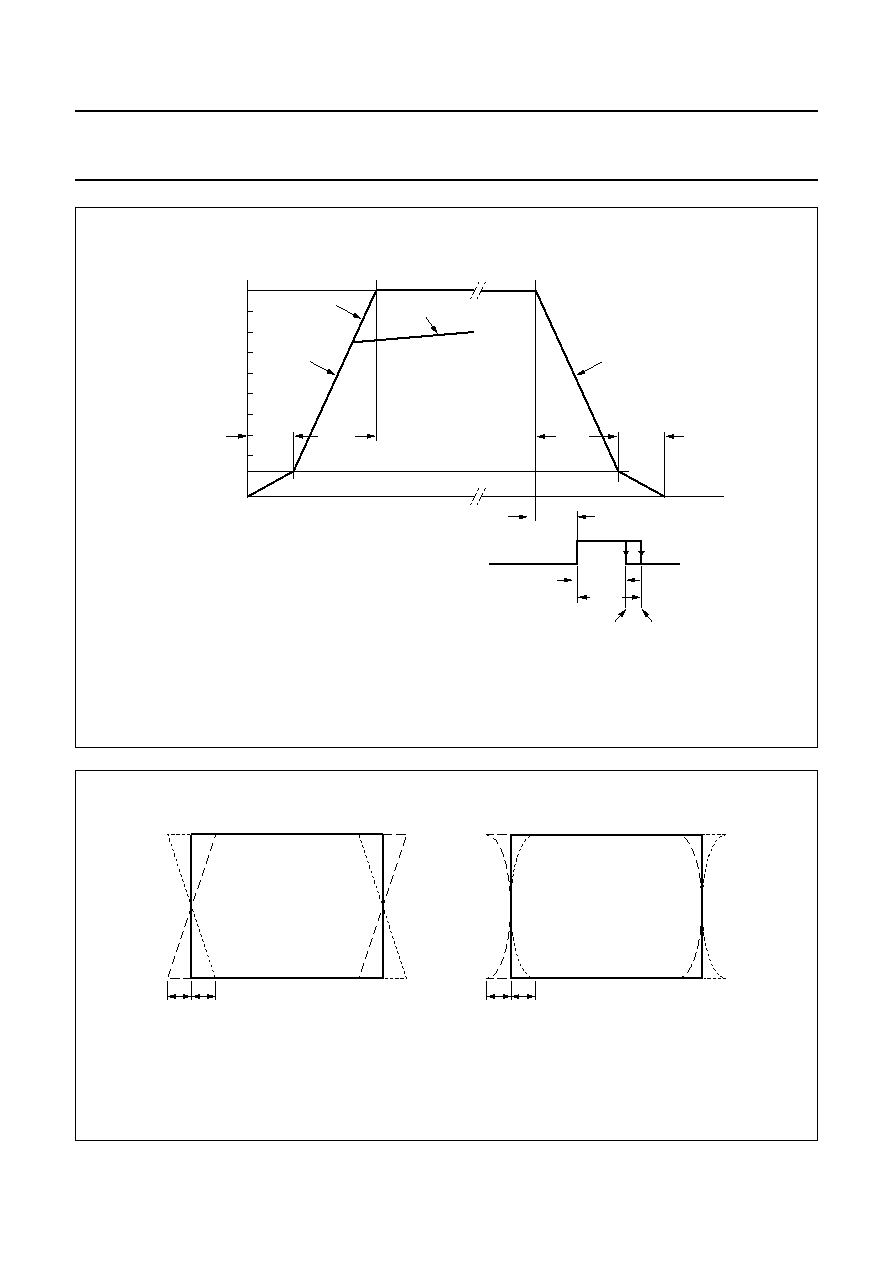

The horizontal drive signal is switched on and off via the

so-called slow-start/slow-stop procedure. This function is

realized by varying the t

on

of the horizontal drive pulse. For

EHT generators without a bleeder, the IC can be set to a

`fixed beam current mode' via bit FBC. In this case, the

picture tube capacitance is discharged with a current of

approximately 1 mA. The magnitude of the discharge

current is controlled via the black current feedback loop.

If necessary, the discharge current can be enlarged with

the aid of an external current division circuit. With the fixed

beam current option activated, it is still possible to have a

black screen during switch-off. This can be realized by

placing the vertical deflection in an overscan position. This

mode is activated via bit OSO.

An additional mode of the IC is the `low-power start-up'

mode. This mode is activated when a supply voltage of 5 V

is supplied to the start-up pin.

The required current for this mode is 3 mA (typ.). In this

condition, the horizontal drive signal has the nominal t

off

and the t

on

grows gradually from zero to approximately

30% of the nominal value. This results in a line frequency

of approximately 50 kHz (2f

H

) or 25 kHz (1f

H

). The output

signal remains unchanged until the main supply voltage is

switched on and the I

2

C-bus data has been received. The

horizontal drive then gradually changes to the nominal

frequency and duty cycle via the slow-start procedure.

The IC can only be switched on and to standby mode when

both standby bits (STB0 and STB1) are changed. The

circuit will not react when only one bit changes polarity.

The IC has a general purpose bus controlled DAC output

with a 6-bit resolution and with an output voltage range

between 0.2 to 4 V. In the TDA9331H, the DC voltage on

this output is proportional to the horizontal line frequency

(only in VGA mode). This voltage can be used to control

the supply voltage of the horizontal deflection stage, to

maintain constant picture width for higher line frequencies.

V

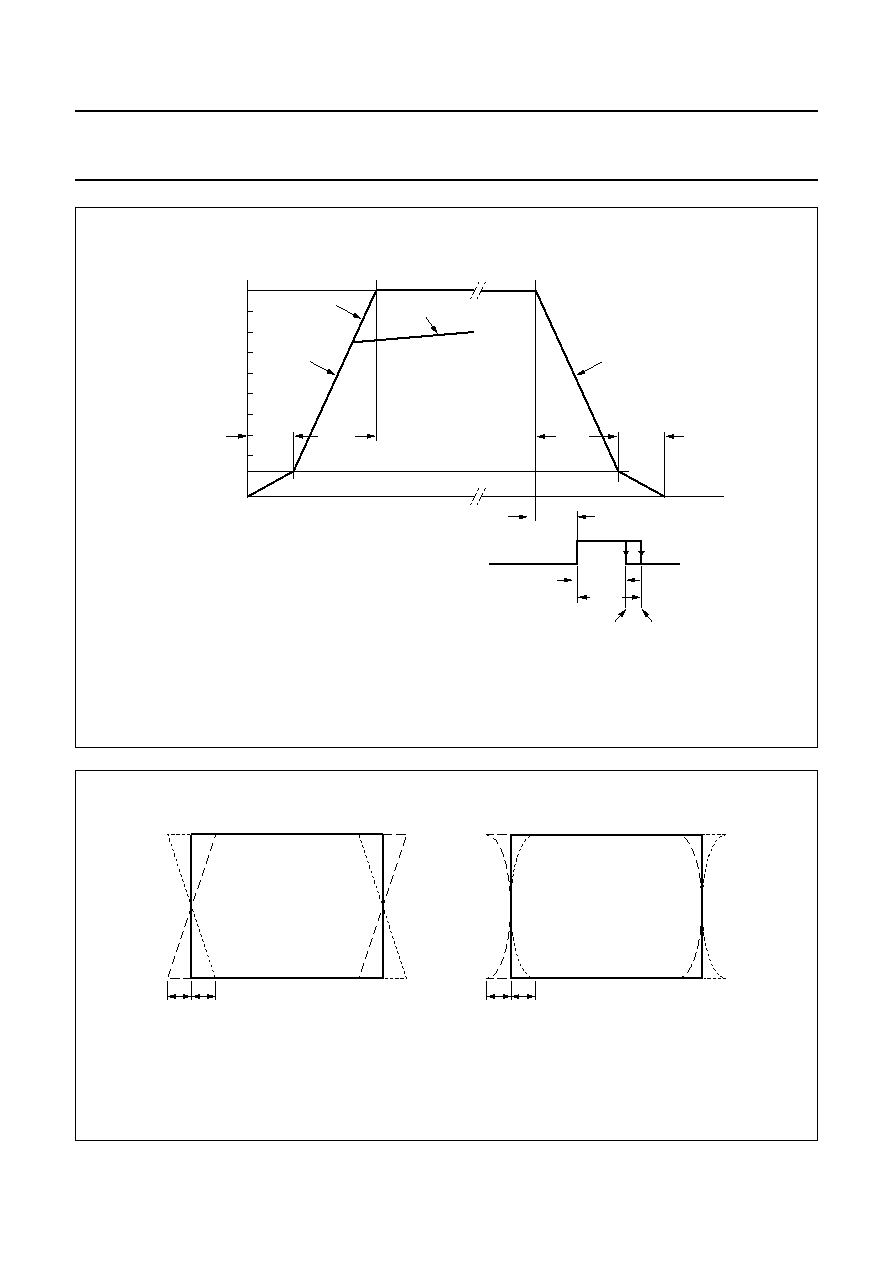

ERTICAL DEFLECTION AND GEOMETRY CONTROL

The drive signals for the vertical and E-W deflection

circuits are generated by a vertical divider, which derives

its clock signal from the line oscillator. The divider is

synchronized by the incoming V

D

pulse, generated by the

input processor or the feature box. The vertical ramp

generator requires an external resistor and capacitor; the

tolerances for these components must be small.

In the normal mode, the vertical deflection operates in

constant slope and adapts its amplitude, depending on the

frequency of the incoming signal (50 or 60 Hz, or

100 or 120 Hz). When the TDA933xH is switched to the

VGA mode, the amplitude of the vertical scan is stabilized

and independent of the incoming vertical frequency. In this

mode, the E-W drive amplitude is proportional to the

horizontal frequency so that the correction on the screen is

not affected.

The vertical drive is realized by a differential output

current. The outputs must be DC-coupled to the vertical

output stage (e.g. TDA8354).

The vertical geometry can be adjusted via the I

2

C-bus.

Controls are possible for the following parameters:

∑

Vertical amplitude

∑

S-correction

∑

Vertical slope

∑

Vertical shift (only for compensation of offsets in output

stage or picture tube)

∑

Vertical zoom

∑

Vertical scroll (shifting the picture in the vertical direction

when the vertical scan is expanded)

∑

Vertical wait, an adjustable delay for the start of the

vertical scan.

With regard to the vertical wait, the following conditions are

valid:

∑

In the 1f

H

TV mode, the start of the vertical scan is fixed

and cannot be adjusted with the vertical wait

∑

In the 2f

H

TV mode, the start of the vertical scan

depends on the value of the Vertical Scan Reference

(VSR) bus bit. If VSR = 0, the start of the vertical scan is

related to the end of the incoming V

D

pulse. If VSR = 1,

it is related to the start. In both cases, the start of the

scan can be adjusted with the vertical wait setting

∑

In the multi-sync mode (TDA9331H and TDA9332H

both in 1f

H

mode and 2f

H

mode), the start of the vertical

scan is related to the start of the incoming V

D

pulse and

can be adjusted with the vertical wait setting.

2002 Jun 04

10

Philips Semiconductors

Preliminary specification

I

2

C-bus controlled TV display processors

TDA933xH series

The minimum value for the vertical wait setting is 8 line

periods. If the setting is lower than 8, the wait period will

remain at 8 line periods.

The E-W drive circuit has a single-ended output. The E-W

geometry can be adjusted on the following parameters:

∑

Horizontal width with increased range because of the

`zoom' feature

∑

E-W parabola/width ratio

∑

E-W upper corner/parabola ratio

∑

E-W lower corner/parabola ratio

∑

E-W trapezium.

The IC has an EHT compensation input which controls

both the vertical and the E-W output signals. The relative

control effect on both outputs can be adjusted via the

I

2

C-bus (sensitivity of vertical correction is fixed; E-W

correction variable).

To avoid damage to the picture tube in the event of missing

or malfunctioning vertical deflection, a vertical guard

function is available at the sandcastle pin (pin SCO). The

vertical guard pulse from the vertical output stage

(TDA835x) should be connected to the sandcastle pin,

which acts as a current sense input. If the guard pulse is

missing or lasts too long, bit NDF is set in the status

register and the RGB outputs are blanked.

If the guard function is disabled via bit EVG, only status

bit NDF is set.

The IC also has inputs for flash and overvoltage protection.

More details about these functions are given in Chapter

"Characteristics"; note 43.

I

2

C-BUS SPECIFICATION

The slave address of the IC is given in Table 1. The circuit

operates up to clock frequencies of 400 kHz. Valid

subaddresses: 00 to 1F, subaddress FE is reserved for

test purposes. The auto-increment mode is available for

subaddresses. It should be noted that the status bytes

cannot be addressed separately, they can only be read via

the auto-increment mode.

Table 1

Slave address (8C)

A6

A5

A4

A3

A2

A1

A0

R/W

1

0

0

0

1

1

0

1/0

2002 Jun 04

11

Philips Semiconductors

Preliminary specification

I

2

C-bus controlled TV display processors

TDA933xH series

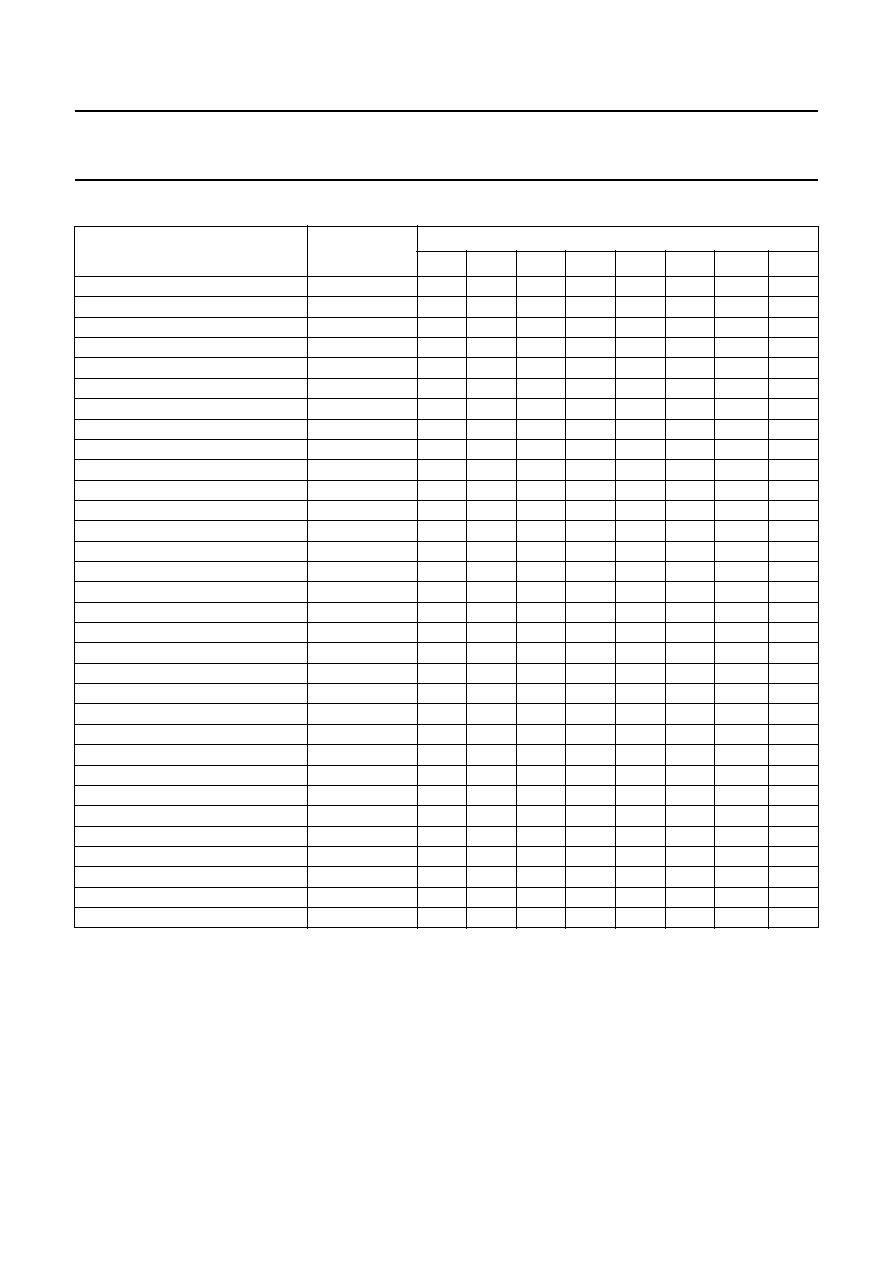

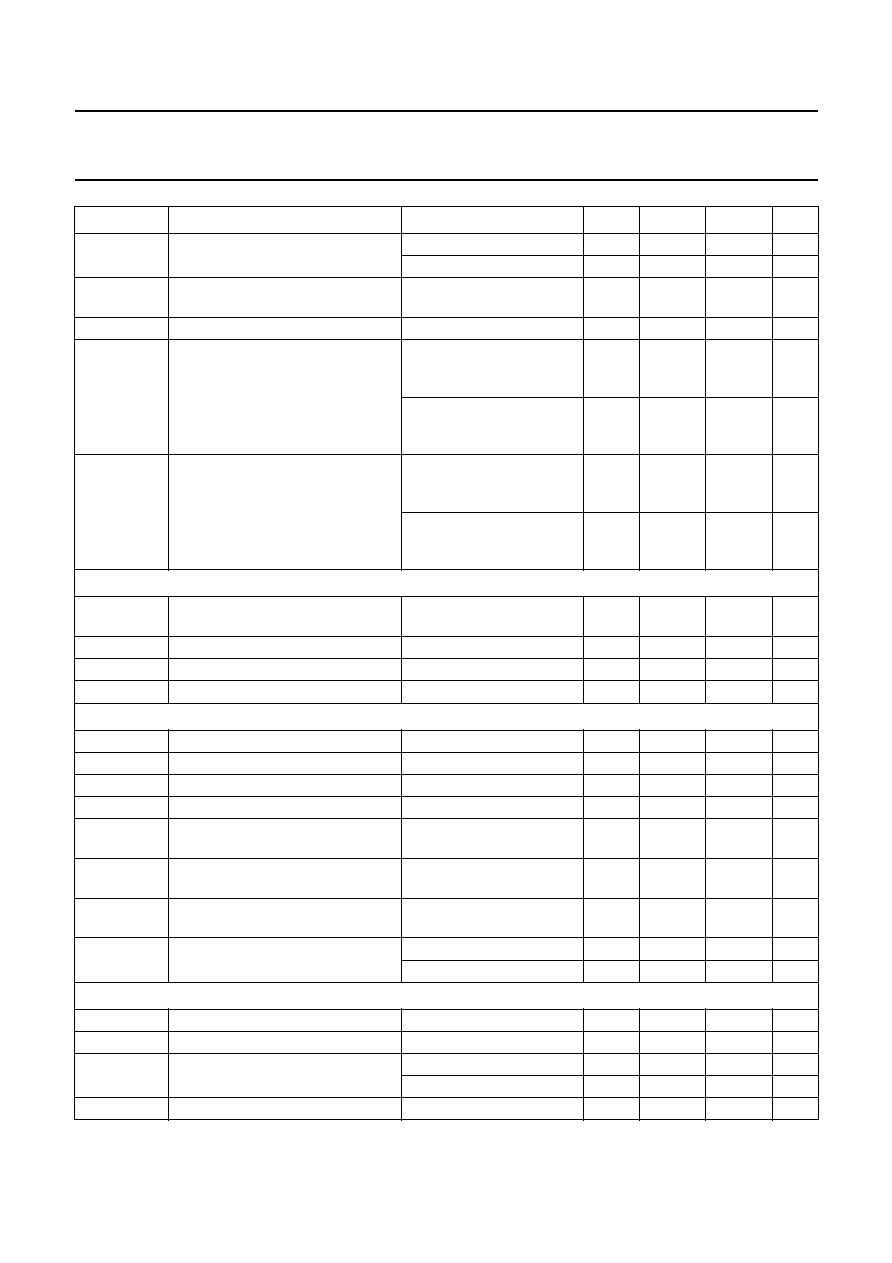

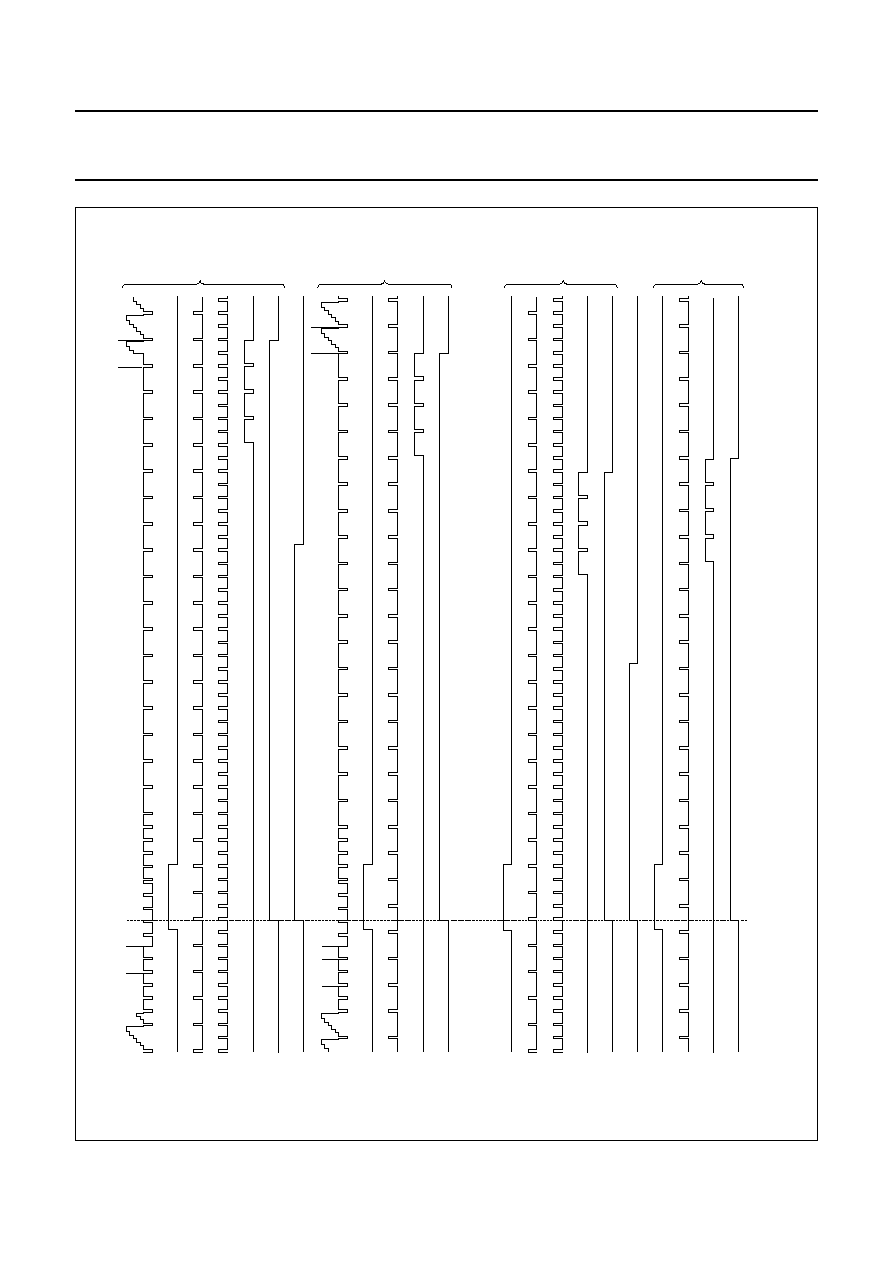

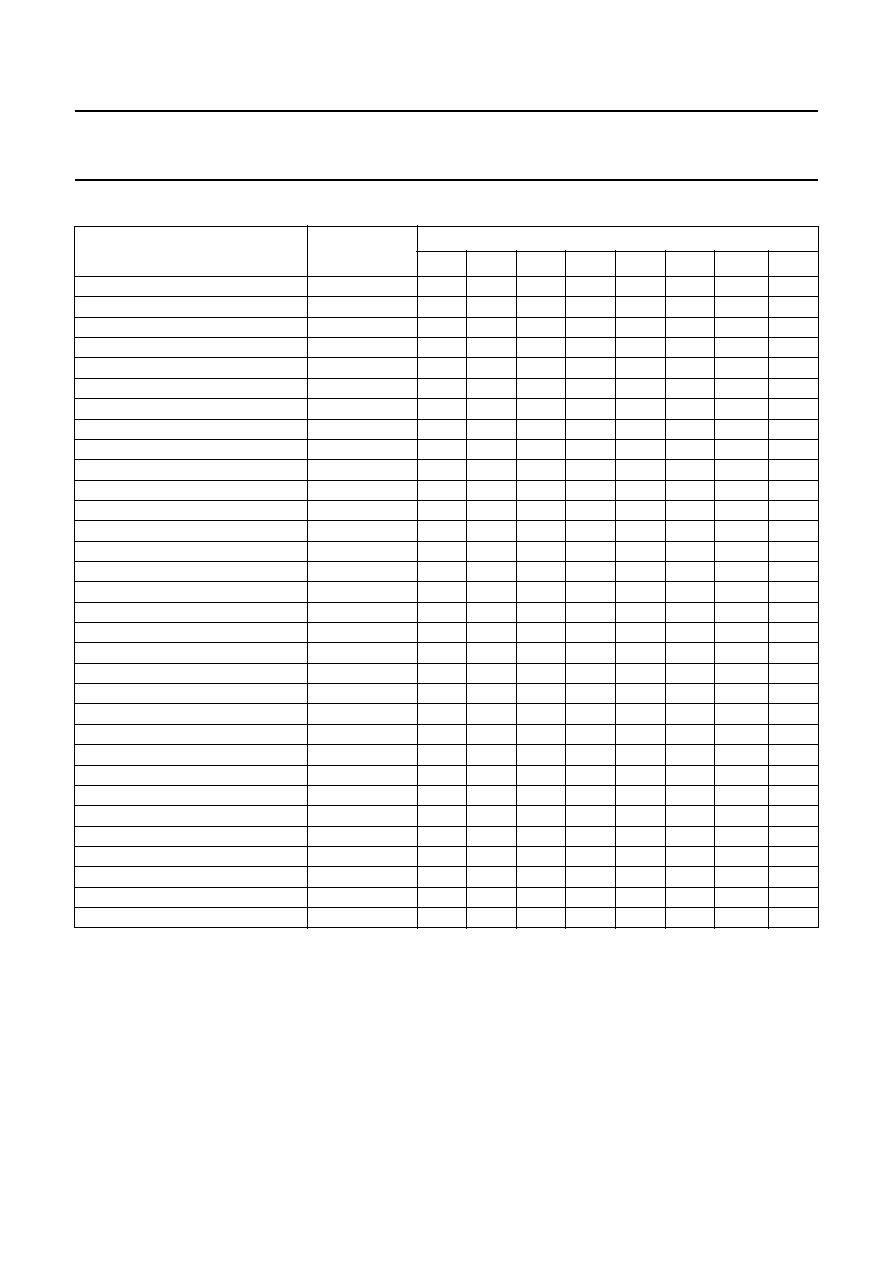

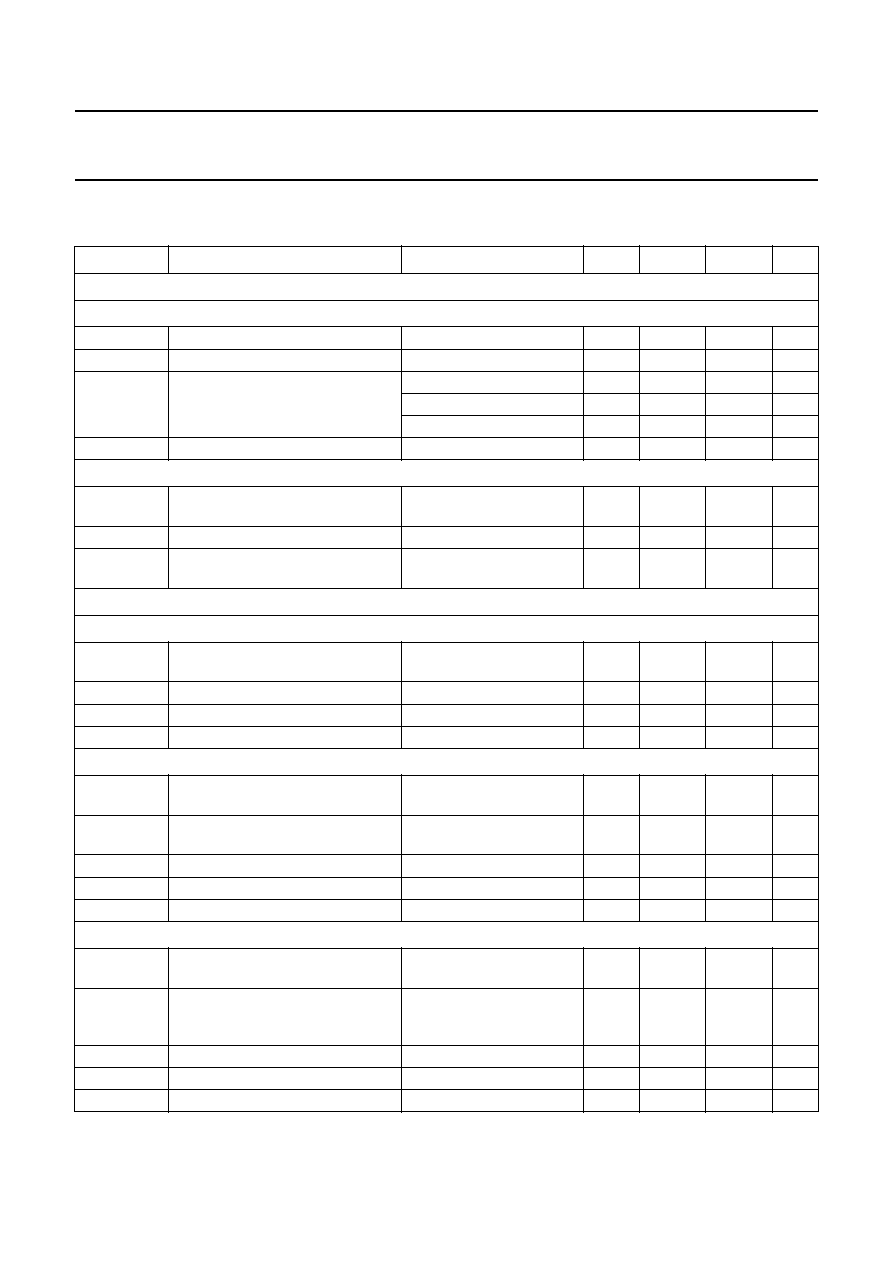

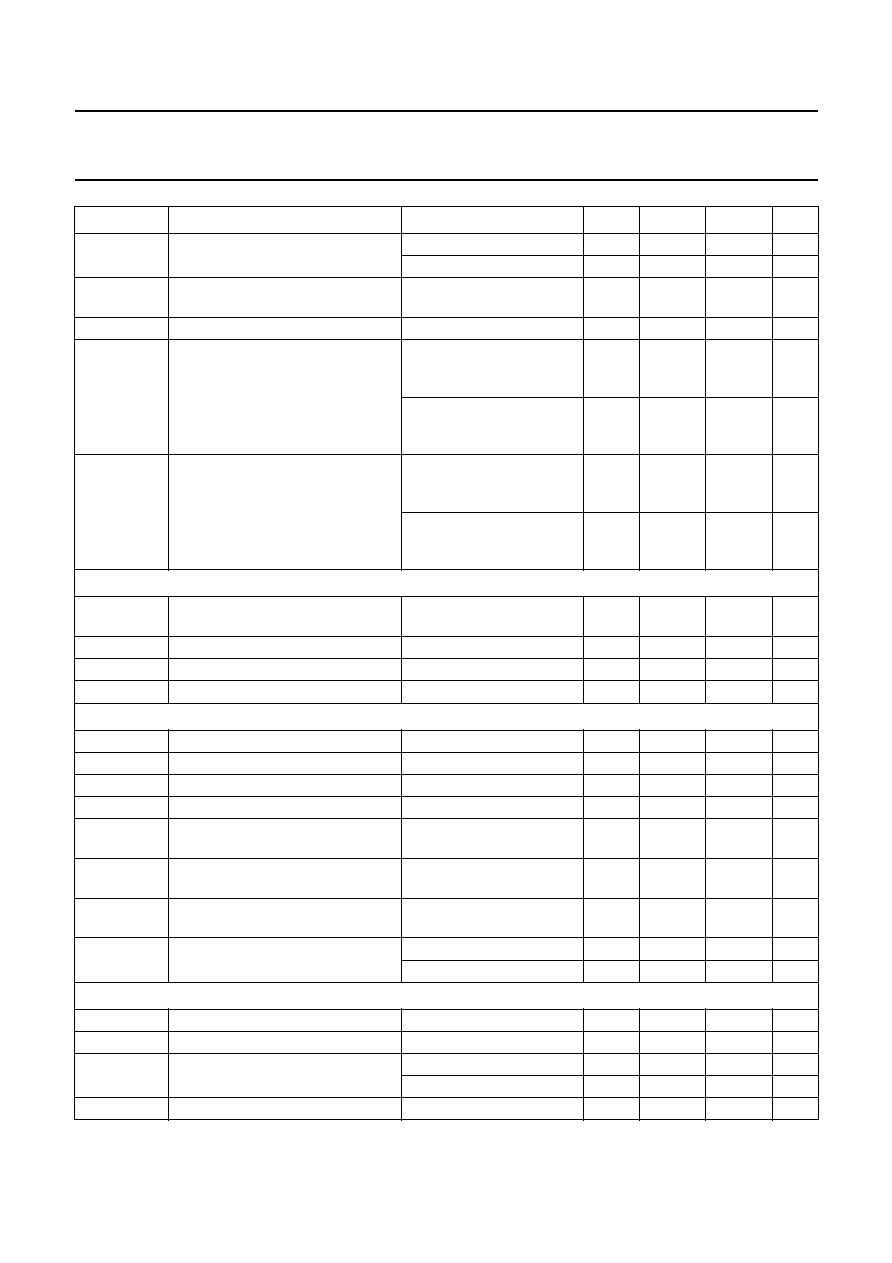

Table 2

Input control bits

Notes

1. For zero parallelogram and bow correction use register value 7 DEC.

2. See Chapter "Characteristics"; note 47.

3. Bit VGA is not available in the TDA9330H.

FUNCTION

SUBADDRESS

(HEX)

DATA BYTE

D7

D6

D5

D4

D3

D2

D1

D0

RGB processing-1

00

MAT

EBB

SBL

RBL

BLS

BKS

IE1

IE2

RGB processing-2

01

MUS

FBC

OBL

AKB

CL3

CL2

CL1

CL0

Wide horizontal blanking

02

HBL

TFBC

GAI

STB0

HB3

HB2

HB1

HB0

Horizontal deflection

03

HDTV

VSR

FAST

STB1

POC

PRD

VGA

(3)

ESS

Vertical deflection

04

OPC

VFF

LBM

DIP

OSO

SVF

EVG

DL

Brightness

05

0

0

A5

A4

A3

A2

A1

A0

Saturation

06

0

0

A5

A4

A3

A2

A1

A0

Contrast

07

0

0

A5

A4

A3

A2

A1

A0

White point R

08

0

0

A5

A4

A3

A2

A1

A0

White point G

09

0

0

A5

A4

A3

A2

A1

A0

White point B

0A

0

0

A5

A4

A3

A2

A1

A0

Peak white limiting

0B

0

0

SC1

SC0

A3

A2

A1

A0

Horizontal shift

0C

0

0

A5

A4

A3

A2

A1

A0

Horizontal parallelogram

(1)

0D

0

0

0

0

A3

A2

A1

A0

E-W width

0E

0

0

A5

A4

A3

A2

A1

A0

E-W parabola/width

0F

0

0

A5

A4

A3

A2

A1

A0

E-W upper corner/parabola

10

0

0

A5

A4

A3

A2

A1

A0

E-W trapezium

11

0

0

A5

A4

A3

A2

A1

A0

E-W EHT compensation sensitivity

12

0

0

A5

A4

A3

A2

A1

A0

Vertical slope

13

0

0

A5

A4

A3

A2

A1

A0

Vertical amplitude

14

0

0

A5

A4

A3

A2

A1

A0

S-correction

15

0

0

A5

A4

A3

A2

A1

A0

Vertical shift

16

0

0

A5

A4

A3

A2

A1

A0

Vertical zoom

17

0

0

A5

A4

A3

A2

A1

A0

Vertical scroll

18

0

0

A5

A4

A3

A2

A1

A0

Vertical wait

19

0

0

0

A4

A3

A2

A1

A0

DAC output

(2)

1A

0

0

A5

A4

A3

A2

A1

A0

Black level offset R

1B

0

0

0

0

A3

A2

A1

A0

Black level offset G

1C

0

0

0

0

A3

A2

A1

A0

Horizontal timing

1D

CDTV

0

0

HDCL

LBL3

LBL2

LBL1

LBL0

E-W lower corner/parabola

1E

0

0

A5

A4

A3

A2

A1

A0

Horizontal bow

(1)

1F

0

0

0

0

A3

A2

A1

A0

2002 Jun 04

12

Philips Semiconductors

Preliminary specification

I

2

C-bus controlled TV display processors

TDA933xH series

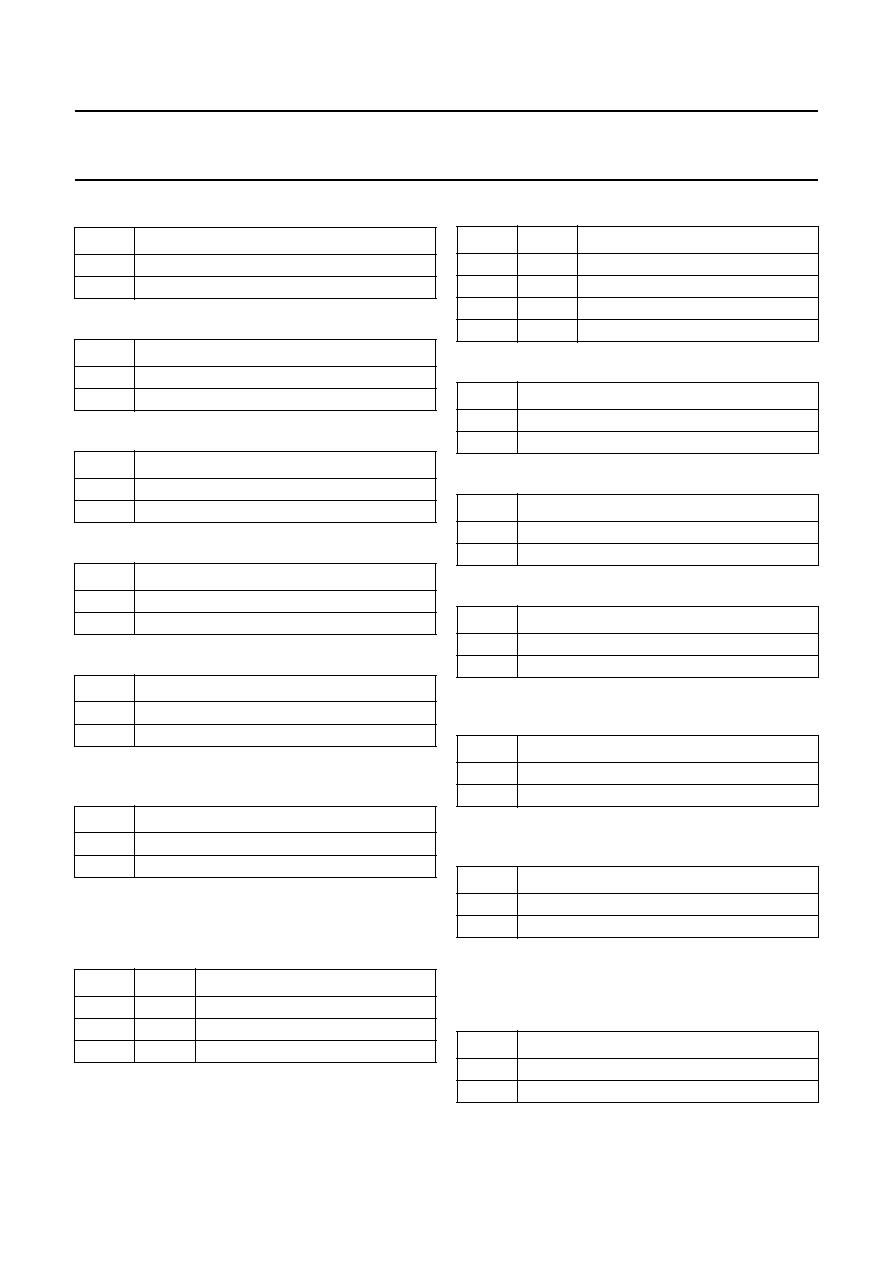

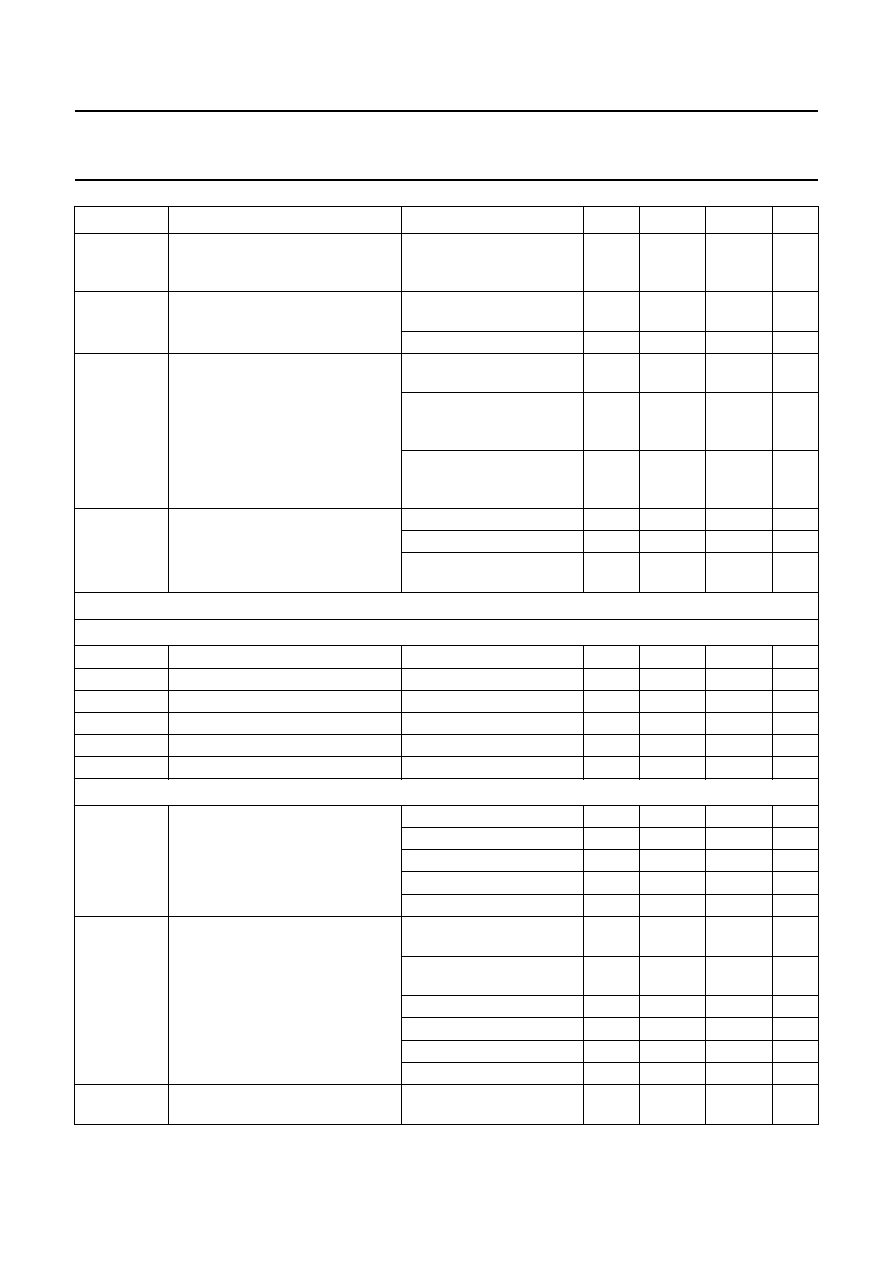

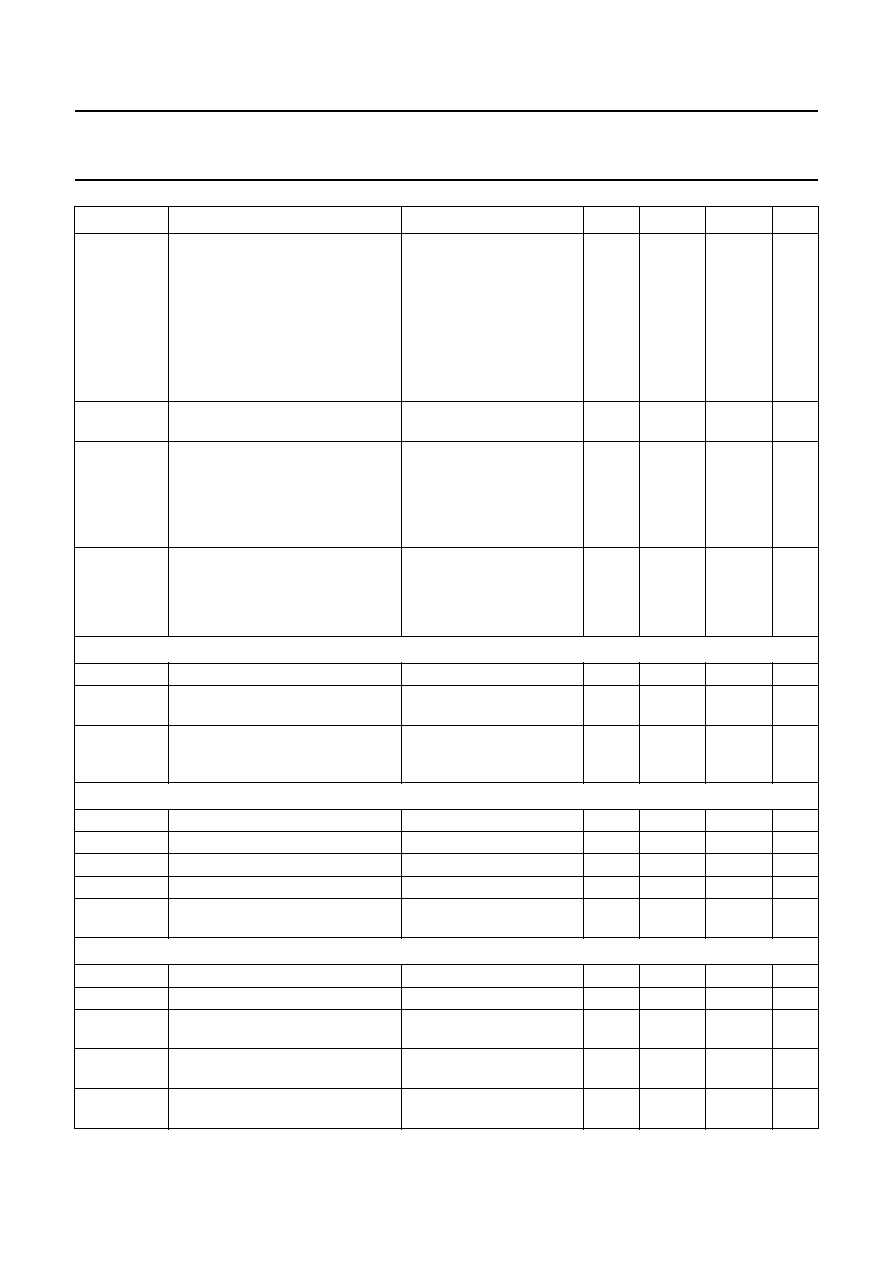

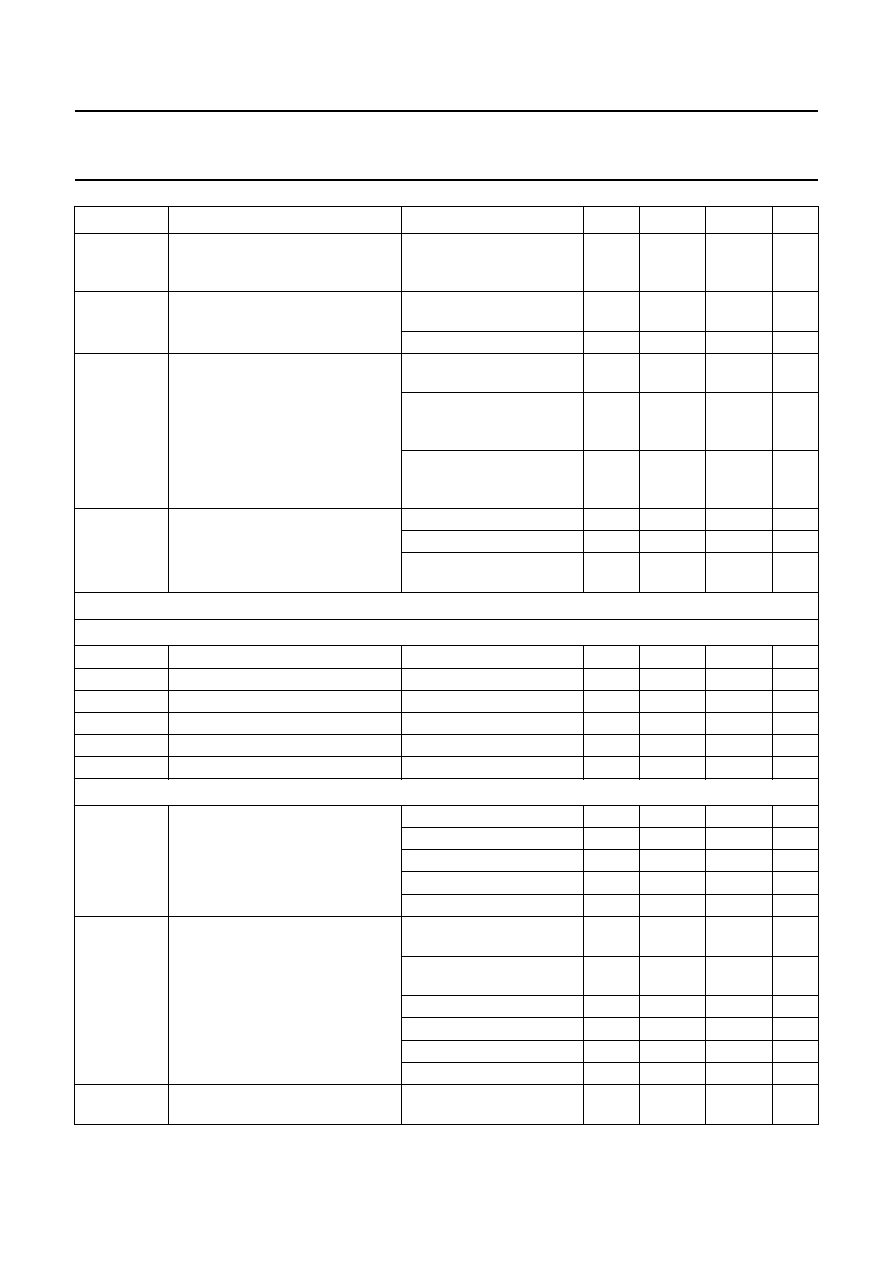

Table 3

Output status bits

FUNCTION

SUBADDRESS

(HEX)

DATA BYTE

D7

D6

D5

D4

D3

D2

D1

D0

Output status bytes

00

POR

FSI

SL

XPR

NDF

IN1

IN2

WBC

01

N2

N3

ID1

ID0

NHF

BCF

FLS

NRF

02

X

X

X

X

X

HPOL

VPOL

HBC

Input control bits

Table 4

Colour difference matrix

Table 5

Enable `blue-back'

Table 6

Service blanking

Table 7

RGB blanking

Table 8

Blue stretch

Table 9

Black stretch

Table 10 Enable fast blanking RGB-1

Table 11 Enable fast blanking RGB-2

Table 12 Fixed beam current switch-off

Table 13 Blending function on OSD; note 1

Note

1. When bit OBL is set to 1, the blending function is

always activated, independent of the setting of bit IE2.

Table 14 Black current stabilization

MAT

MUS

MATRIX POSITION

0

0

PAL

0

1

ATSC

1

0

NTSC Japan

1

1

NTSC USA

EBB

MODE

0

blue-black switched off

1

blue-black switched on

SBL

SERVICE BLANKING MODE

0

off

1

on

RBL

RGB BLANKING

0

not active

1

active

BLS

BLUE STRETCH MODE

0

off

1

on

BKS

BLACK STRETCH MODE

0

off

1

on

IE1

FAST BLANKING

0

not active

1

active

IE2

FAST BLANKING

0

not active

1

active

FBC

MODE

0

switch-off with blanked RGB outputs

1

switch-off with fixed beam current

OBL

MODE

0

OSD via fast blanking

1

OSD via blending function

AKB

OPC

MODE

0

0

2-point control

0

1

1-point control

1

-

not active

2002 Jun 04

13

Philips Semiconductors

Preliminary specification

I

2

C-bus controlled TV display processors

TDA933xH series

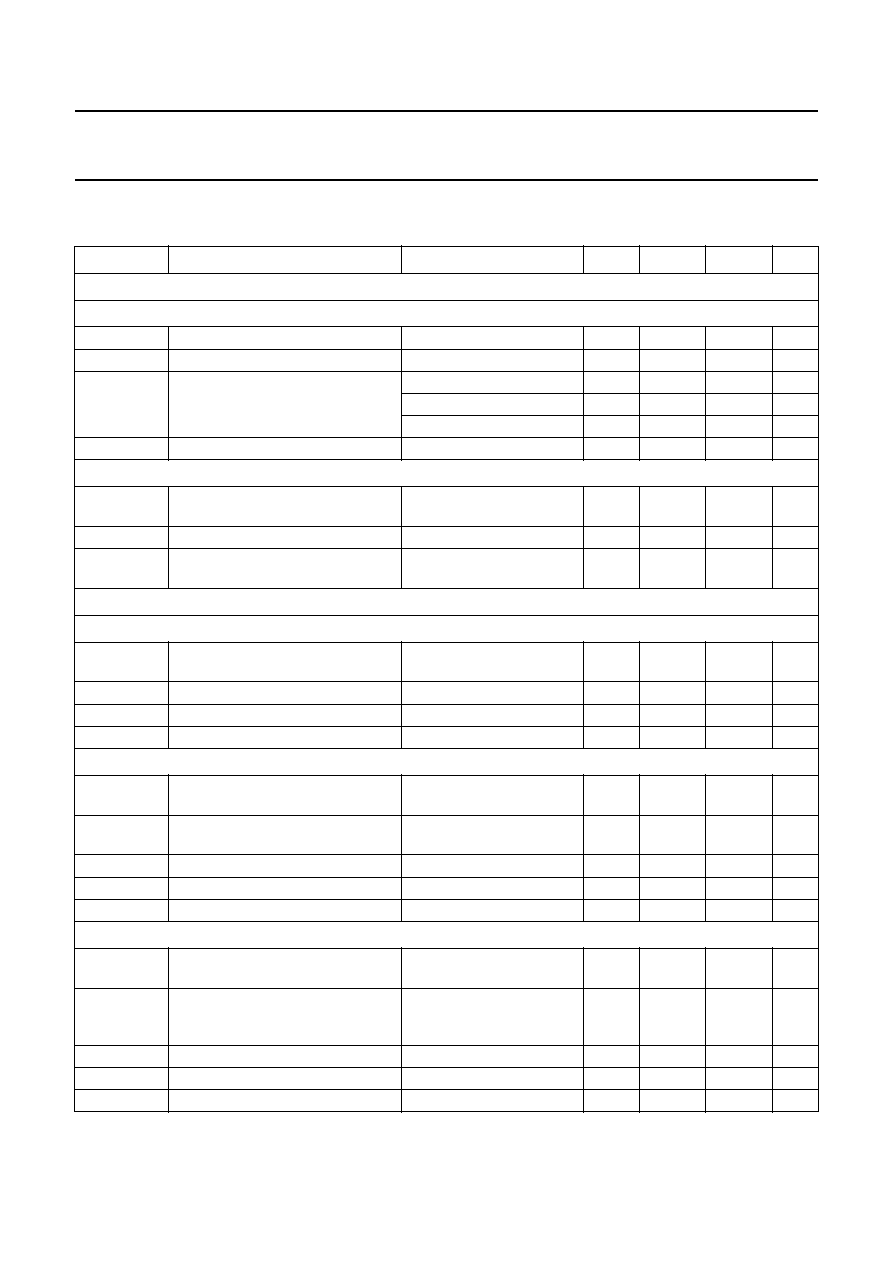

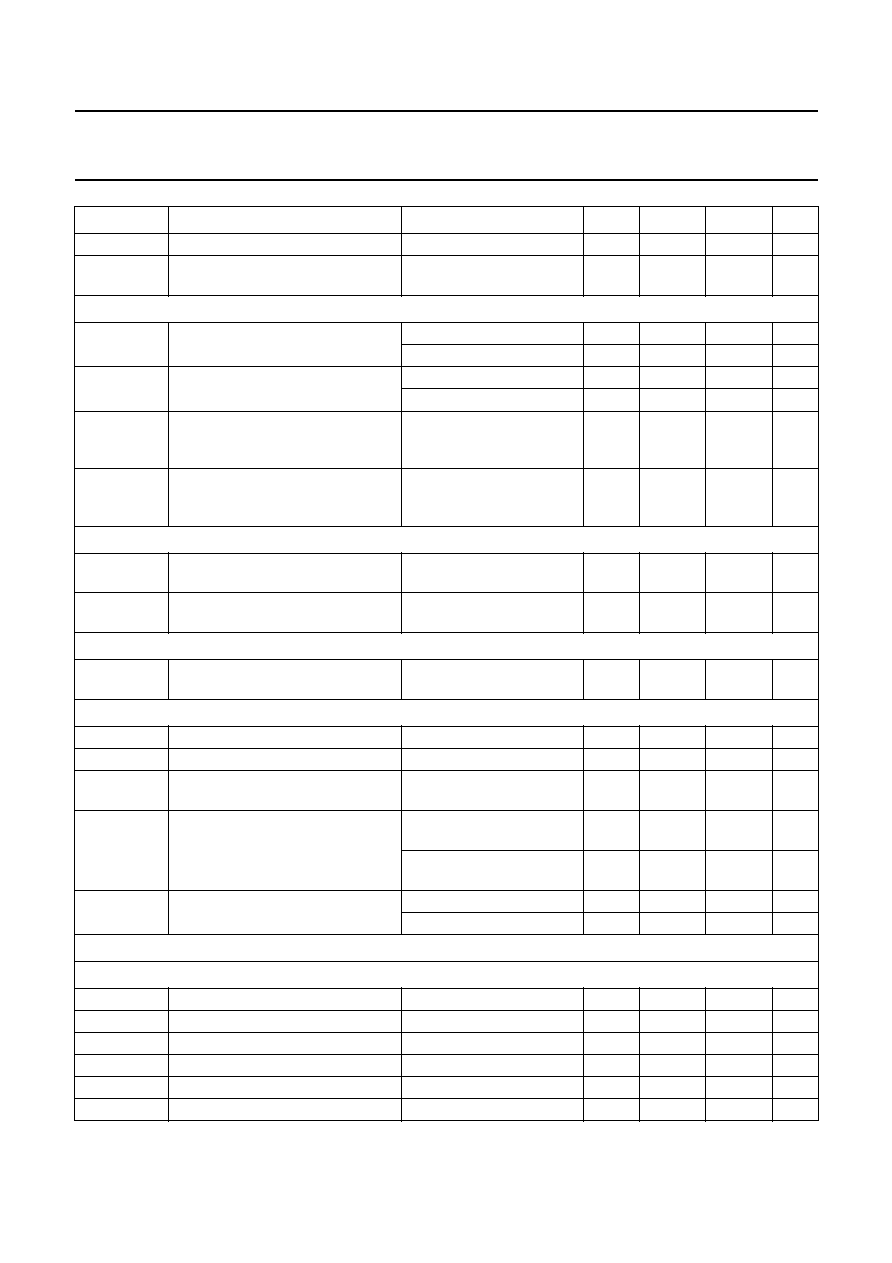

Table 15 Cathode drive level (15 steps; 3.6 V/step)

Note

1. The given values are valid for the following conditions:

a) Nominal CVBS input signal.

b) Settings for contrast and white point nominal.

c) Black and blue stretch switched off.

d) Gain of output stage such that no clipping occurs.

e) Beam current limiting not active.

f) Gamma of picture tube is 2.25.

g) The tolerance on these values is approximately

±

3 V.

Table 16 RGB blanking mode

Table 17 Picture tube discharge time

Note

1. See Chapter "Characteristics"; Fig.15

Table 18 Gain of luminance channel

Table 19 Standby

Table 20 Position of wide blanking (14 steps; 1f

H

mode

0.29

µ

s/step; 2f

H

mode 0.145

µ

s/step)

Note

1. See Chapter "Characteristics"; note 13.

Table 21 Horizontal free-running frequency in TV mode

Table 22 Vertical scan reference in 2f

H

TV mode

Table 23 Time constant phase-1 loop

Table 24 Synchronization mode

Table 25 Overvoltage input mode

CL3

CL2

CL1

CL0

SETTING OF CATHODE

DRIVE AMPLITUDE

(1)

0

0

0

0

41 V (b-w)

1

0

0

0

70 V (b-w)

1

1

1

1

95 V (b-w)

HBL

MODE

0

normal blanking (horizontal flyback)

1

wide blanking

TFBC

MODE

0

18.6 ms

1

25 ms

GAI

MODE

0

normal gain [V

28

= 1 V (b-w)]

1

high gain [V

28

= 0.45 V (p-p)]

STB0

STB1

CONDITION

0

0

horizontal drive off

0

1

no action

1

0

no action

1

1

horizontal drive on

HB3

HB2

HB1

HB0

TIMING OF BLANKING

(1)

1f

H

MODE

2f

H

MODE

0

0

0

0

-

2.03

µ

s

-

1.015

µ

s

0

1

1

1

0

µ

s

0

µ

s

1

1

1

-

2.03

µ

s

1.015

µ

s

HDTV

CDTV

FREQUENCY

1f

H

MODE

2f

H

MODE

0

0

15.7 kHz

31.4 kHz

0

1

14.25 kHz

28.5 kHz

1

-

16.9 kHz

33.8 kHz

VSR

VERTICAL SCAN REFERENCE

0

end of V

D

pulse

1

start of V

D

pulse

FAST

TIME CONSTANT

0

normal

1

increased by 30%

POC

MODE

0

synchronization active

1

synchronization not active

PRD

OVERVOLTAGE MODE

0

detection mode

1

protection mode

2002 Jun 04

14

Philips Semiconductors

Preliminary specification

I

2

C-bus controlled TV display processors

TDA933xH series

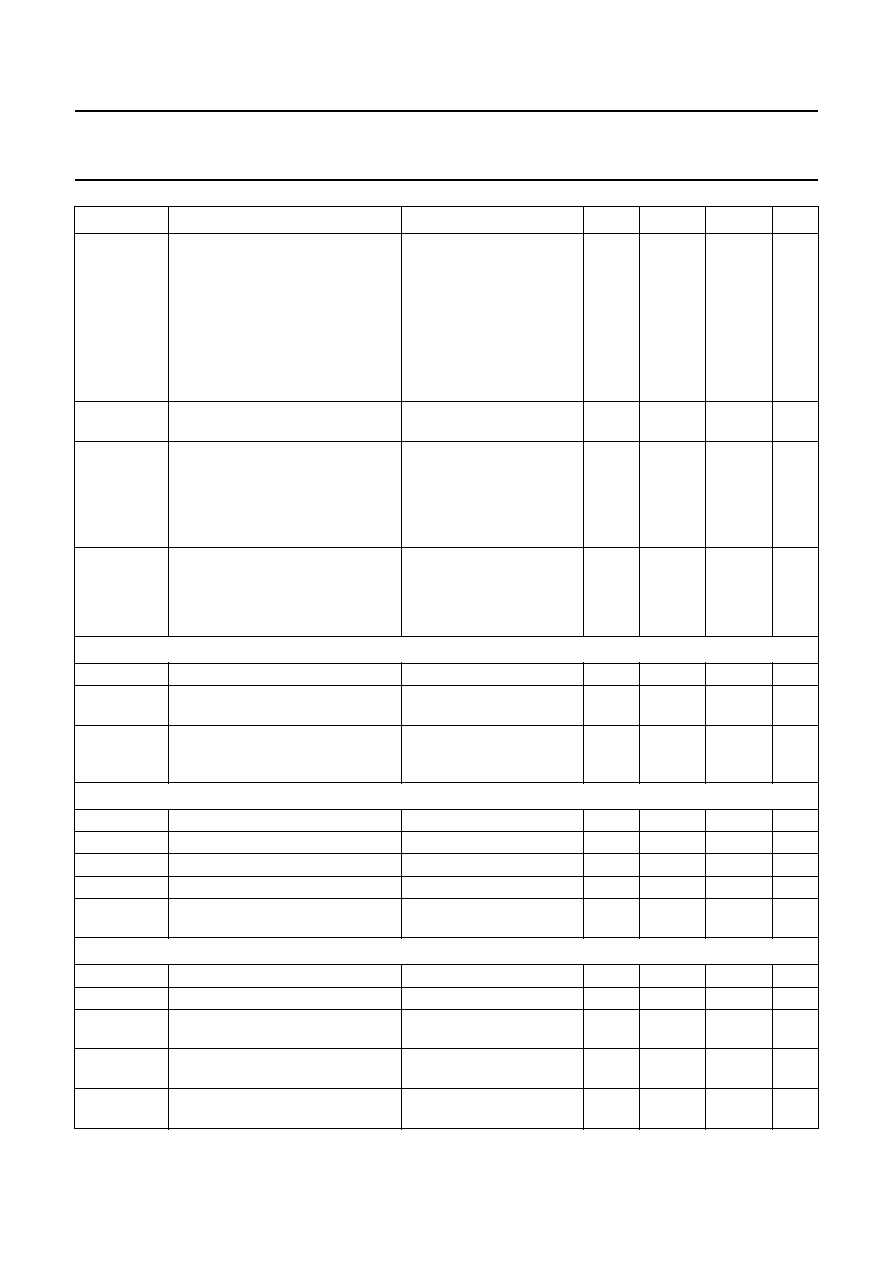

Table 26 Multi-sync mode

Table 27 Extended slow start mode

Table 28 Long blanking mode

Table 29 Vertical free-running frequency in TV mode

Table 30 De-interlace phase

Table 31 Switch-off in vertical overscan

Table 32 Select vertical frequency

Table 33 Enable vertical guard (RGB blanking)

Table 34 Interlace

Table 35 Soft clipping level

Table 36 Clamp pulse timing

Note

1. See Chapter "Characteristics"; note 13.

Table 37 Start line blanking (15 steps; 2 line locked clock

period per step; 1 line period is 440 LLC pulses)

Note

1. See Chapter "Characteristics"; note 13.

Output status bits

Table 38 Power-on reset

Table 39 Field frequency indication

VGA

MODE

0

horizontal frequency fixed by internal

reference

1

multi-sync function switched on

ESS

EXTENDED SLOW START MODE

0

not active

1

active

LBM

BLANKING MODE

0

adapted to standard (50 or 60 Hz)

1

fixed in accordance with 50 Hz standard

VFF

FREQUENCY

0

50 Hz (SVF = 0) or 100 Hz (SVF = 1)

1

60 Hz (SVF = 0) or 120 Hz (SVF = 1)

DIP

PHASE

0

delay of 1st field (start of synchronized V

D

pulse coincides with H-flyback) with 0.5 H

1

delay of 2nd field with 0.5 H

OSO

MODE

0

switch-off undefined

1

switch-off in vertical overscan

SVF

MODE

0

vertical frequency is 50 or 60 Hz

1

vertical frequency is 100 or 120 Hz

EVG

VERTICAL GUARD MODE

0

not active

1

active

DL

STATUS

0

interlace

1

de-interlace

SC1

SC0

VOLTAGE DIFFERENCE

BETWEEN SOFT CLIPPING AND

PWL

0

0

0% above PWL

0

1

5% above PWL

1

0

10% above PWL

1

1

soft clipping off

HDCL

MODE

(1)

0

normal timing

1

HDTV timing

LBL3

LBL2

LBL1

LBL0

START LINE

BLANKING

(1)

0

0

0

0

+14 LLC

0

1

1

1

normal

1

1

1

1

-

16 LLC

POR

MODE

0

normal

1

power-down

FSI

FREQUENCY

0

50 or 100 Hz

1

60 or 120 Hz

2002 Jun 04

15

Philips Semiconductors

Preliminary specification

I

2

C-bus controlled TV display processors

TDA933xH series

Table 40 Phase 1 (

1

) lock indication

Table 41 X-ray protection

Table 42 Output of vertical guard

Table 43 Indication of RGB-1 insertion

Table 44 Indication of RGB-2 insertion

Table 45 Indication of output black level inside/outside

V

g2

alignment window

Note

1. See Chapter "Characteristics"; note 16.

Table 46 IC identification

Table 47 Mask version indication

Table 48 Condition of horizontal flyback

Table 49 Indication of failure in black current circuit

Table 50 Indication of flash detection

Table 51 Locking of reference oscillator to crystal

oscillator

Table 52 Indication of output black level below or above

the middle of V

g2

alignment window

Note

1. See Chapter "Characteristics"; note 16.

Table 53 Polarity of H

D

input pulse

SL

INDICATION

0

not locked

1

locked

XPR

OVERVOLTAGE

0

no overvoltage detected

1

overvoltage detected

NDF

VERTICAL OUTPUT STAGE

0

OK

1

failure

IN1

RGB INSERTION

0

no

1

yes

IN2

RGB INSERTION

0

no

1

yes

WBC

CONDITION

(1)

0

black current stabilization outside window

1

black current stabilization inside window

ID1

ID0

IC VERSION

0

0

TDA9330H

0

1

TDA9332H

1

1

TDA9331H

N2

N3

MASK VERSION

0

0

N1 version

0

1

spare

1

0

N2 version

1

1

N3 version

NHF

CONDITION

0

flyback pulse present

1

flyback pulse not present

BCF

CONDITION

0

normal operation

1

failure in black current stabilization circuit

FLS

CONDITION

0

no flash-over detected

1

flash-over detected

NRF

CONDITION

0

reference oscillator is locked

1

reference oscillator is not locked

HBC

CONDITION

(1)

0

black current stabilization below window

1

black current stabilization above window

HPOL

POLARITY

0

positive

1

negative

2002 Jun 04

16

Philips Semiconductors

Preliminary specification

I

2

C-bus controlled TV display processors

TDA933xH series

Table 54 Polarity of V

D

input pulse

LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 60134).

THERMAL CHARACTERISTICS

VPOL

POLARITY

0

positive

1

negative

SYMBOL

PARAMETER

CONDITIONS

MIN.

MAX.

UNIT

V

P

supply voltage

-

9.0

V

T

stg

storage temperature

-

25

+150

∞

C

T

amb

ambient temperature

0

70

∞

C

T

sol

soldering temperature

for 5 s

-

260

∞

C

T

j

junction temperature

-

150

∞

C

SYMBOL

PARAMETER

CONDITIONS

VALUE

UNIT

R

th(j-a)

thermal resistance from junction to ambient in free air

60

K/W

QUALITY SPECIFICATION

In accordance with

"SNW-FQ-611E-part E".

ESD protection

All pins are protected against ESD by internal protection

diodes, and meet the following specification:

∑

Human body model (R = 1.5 k

; C = 100 pF):

all pins >

±

3000 V

∑

Machine model (R = 0

; C = 200 pF):

all pins >

±

300 V.

Latch-up performance

At an ambient temperature of 50

∞

C all pins meet the

following specification:

∑

Positive stress test: I

trigger

100 mA

or V

pin

1.5

◊

V

CC(max)

∑

Negative stress test: I

trigger

-

100 mA

or V

pin

-

0.5

◊

V

CC(max)

.

At an ambient temperature of 70

∞

C, all pins meet the

specification as mentioned above, with the exception of

pin 32, which can withstand a negative stress current of at

least 50 mA.

2002 Jun 04

17

Philips Semiconductors

Preliminary specification

I

2

C-bus controlled TV display processors

TDA933xH series

CHARACTERISTICS

V

P

= 8 V; T

amb

= 25

∞

C; unless otherwise specified.

SYMBOL

PARAMETER

CONDITIONS

MIN.

TYP.

MAX.

UNIT

Supplies

M

AIN SUPPLY

;

PINS

17

AND

39

V

P1

supply voltage

7.2

8.0

8.8

V

V

POR

power-on reset voltage level

note 1

5.8

6.1

6.5

V

I

P1

supply current

pin 17 plus pin 39

44

50

58

mA

pin 17

-

22

-

mA

pin 39

-

28

-

mA

P

tot

total power dissipation

-

400

-

mW

L

OW

-

POWER START

-

UP

;

PIN

22; see note 2

V

lp(start)(min)

minimum low power start-up

voltage

3.6

4.0

4.4

V

V

P2

maximum allowed voltage

-

5.5

-

V

I

P2

supply current at 5 V start-up

voltage

-

3.0

4.5

mA

RGB control circuit

L

UMINANCE INPUT

;

PIN

28

V

i(Y)(b-w)

luminance input voltage

(black-to-white value)

GAI = 0

-

1.0

1.5

V

Z

i

input impedance

10

-

-

M

C

i

input capacitance

-

-

5

pF

I

i(Y)(clamp)

input current during clamping

-

25

0

+25

µ

A

U/V

INPUTS

;

PINS

27

AND

26

V

i(U)(p-p)

U input signal amplitude

(peak-to-peak value)

-

1.33

2.0

V

V

i(V)(p-p)

V input signal amplitude

(peak-to-peak value)

-

1.05

1.6

V

Z

i

input impedance

10

-

-

M

C

i

input capacitance

-

-

5

pF

I

i(UV)(clamp)

input current during clamping

-

20

0

+25

µ

A

RGB-1

INPUT

(SCART/VGA);

PINS

30

TO

32; note 3

V

i(b-w)

input signal amplitude

(black-to-white value)

-

0.7

1.0

V

V

o

difference between black level of

YUV and RGB-1 signals at the

outputs

-

-

10

mV

Z

i

input impedance

10

-

-

M

C

i

input capacitance

-

-

5

pF

I

i(clamp)

input current during clamping

-

25

0

+25

µ

A

2002 Jun 04

18

Philips Semiconductors

Preliminary specification

I

2

C-bus controlled TV display processors

TDA933xH series

t

d

delay difference for the three

channels

note 5

-

0

-

ns

F

AST BLANKING INPUT

(RGB-1);

PIN

33

V

i(BL1)

input voltage

no data insertion

0

-

0.45

V

data insertion

0.9

-

3.0

V

t

d

delay difference between insertion

to RGB out and RGB in to RGB out

data insertion; note 5

-

10

20

ns

I

i(BL1)

input current

source current; note 6

-

-

0.12

-

0.2

mA

SS

int

suppression of internal RGB

signals

insertion; f

i

= 0 to 10 MHz;

notes 5 and 7

50

55

-

dB

SS

ext

suppression of external RGB

signals

no insertion;

f

i

= 0 to 10 MHz;

notes 5 and 7

50

55

-

dB

RGB-2

INPUT

(OSD/TEXT);

PINS

35

TO

37

V

i(b-w)

input signal amplitude

(black-to-white value)

-

0.7

1.0

V

V

o

difference between black level of

YUV/RGB-1 and RGB-2 signals at

the outputs

-

-

tbf

mV

Z

i

input impedance

10

-

-

M

C

i

input capacitance

-

-

5

pF

I

i(clamp)

input current during clamping

-

40

0

+40

µ

A

t

d

delay difference for the three

channels

note 5

-

0

-

ns

B

LENDING

(

FAST BLANKING

)

INPUT

(RGB-2);

PIN

38; note 8

Blending function (OBL = 1)

V

i(BL2)(1)

input voltage

no data insertion

0

-

0.05

V

50% insertion

0.69

0.725

0.76

V

100% insertion

1.42

1.47

3.0

V

active blending range

0.31

-

1.14

V

Ins

(osd)

percentage of data insertion

V

i

= 0.31 V

0

1

4

%

V

i

= 0.725 V

45

50

55

%

V

i

= 1.14 V

96

99

100

%

internal signal is 50%

48

50

52

%

V

i(max)

slope of blending curve

50% insertion

-

160

-

%/V

Fast blanking function (OBL = 0)

V

i(BL2)(0)

input voltage

no data insertion

0

-

0.3

V

data insertion

0.9

-

3.0

V

SYMBOL

PARAMETER

CONDITIONS

MIN.

TYP.

MAX.

UNIT

2002 Jun 04

19

Philips Semiconductors

Preliminary specification

I

2

C-bus controlled TV display processors

TDA933xH series

General

t

d

delay difference between insertion

to RGB out and RGB in to RGB out

data insertion; note 5

-

20

26

ns

I

i(BL2)

input current

source current; note 6

-

-

1

-

5

µ

A

SS

int

suppression of internal RGB

signals

insertion; f

i

= 0 to 10 MHz;

notes 5 and 7

50

55

-

dB

SS

ext

suppression of external RGB

signals

no insertion;

f

i

= 0 to 10 MHz;

notes 5 and 7

50

55

-

dB

C

OLOUR DIFFERENCE MATRICES

; note 3

PAL/SECAM mode; the matrix results in the following signal

G

-

Y

G

-

Y

-

0.51 (R

-

Y)

-

0.19 (B

-

Y)

ATSC mode; the matrix results in the following signal; note 4

G

-

Y

G

-

Y

-

0.30 (R

-

Y)

-

0.10 (B

-

Y)

NTSC mode; the matrix results in the following modified colour difference signals

MUS bit = 0 (Japan)

R

-

Y

(R

-

Y)*

1.39 (R

-

Y)

-

0.07 (B

-

Y)

G

-

Y

(G

-

Y)*

-

0.46 (R

-

Y)

-

0.15 (B

-

Y)

B

-

Y

(B

-

Y)*

B

-

Y

MUS bit = 1 (USA)

R

-

Y

(R

-

Y)*

1.32 (R

-

Y)

-

0.12 (B

-

Y)

G

-

Y

(G

-

Y)*

-

0.42 (R

-

Y)

-

0.25 (B

-

Y)

B

-

Y

(B

-

Y)*

-

0.03 (R

-

Y) +1.08 (B

-

Y)

C

ONTROLS

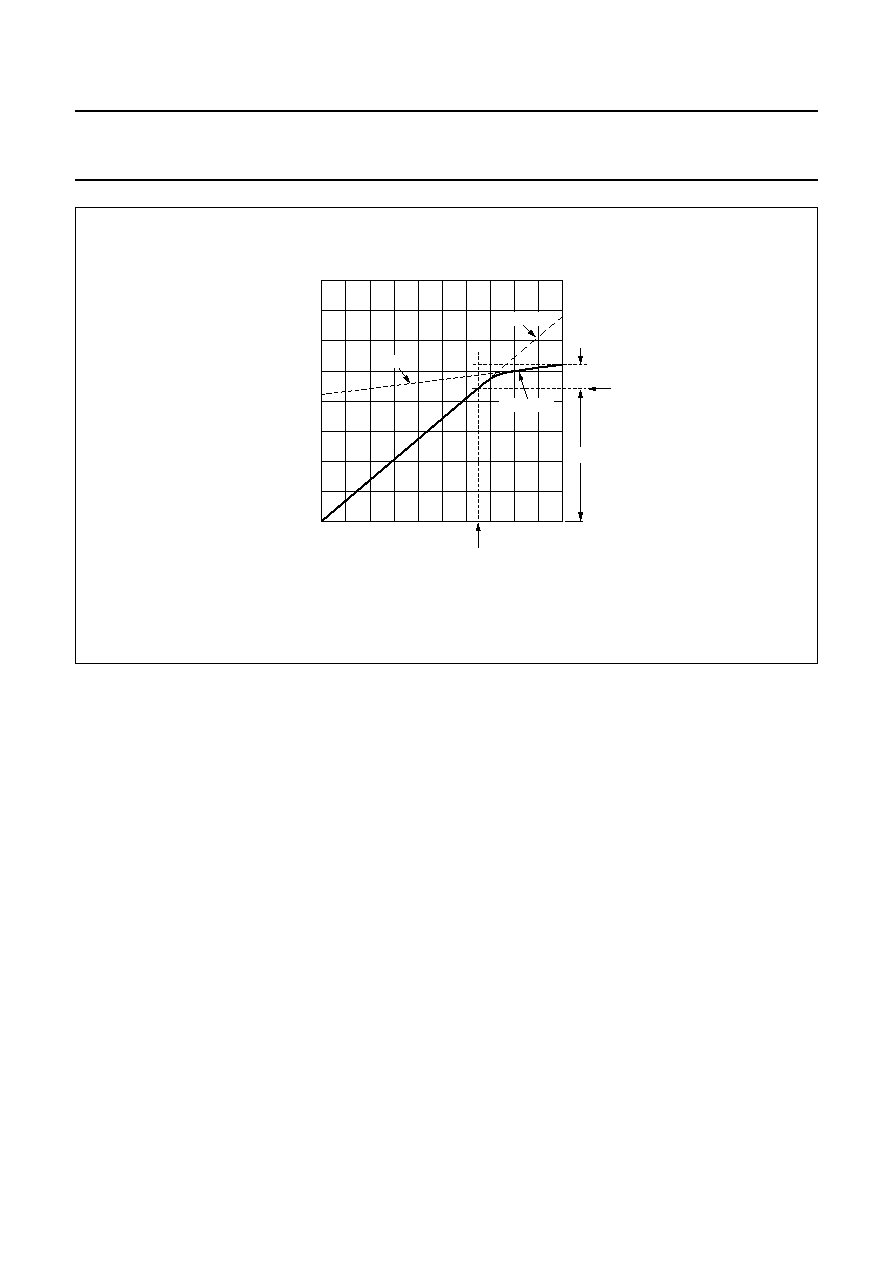

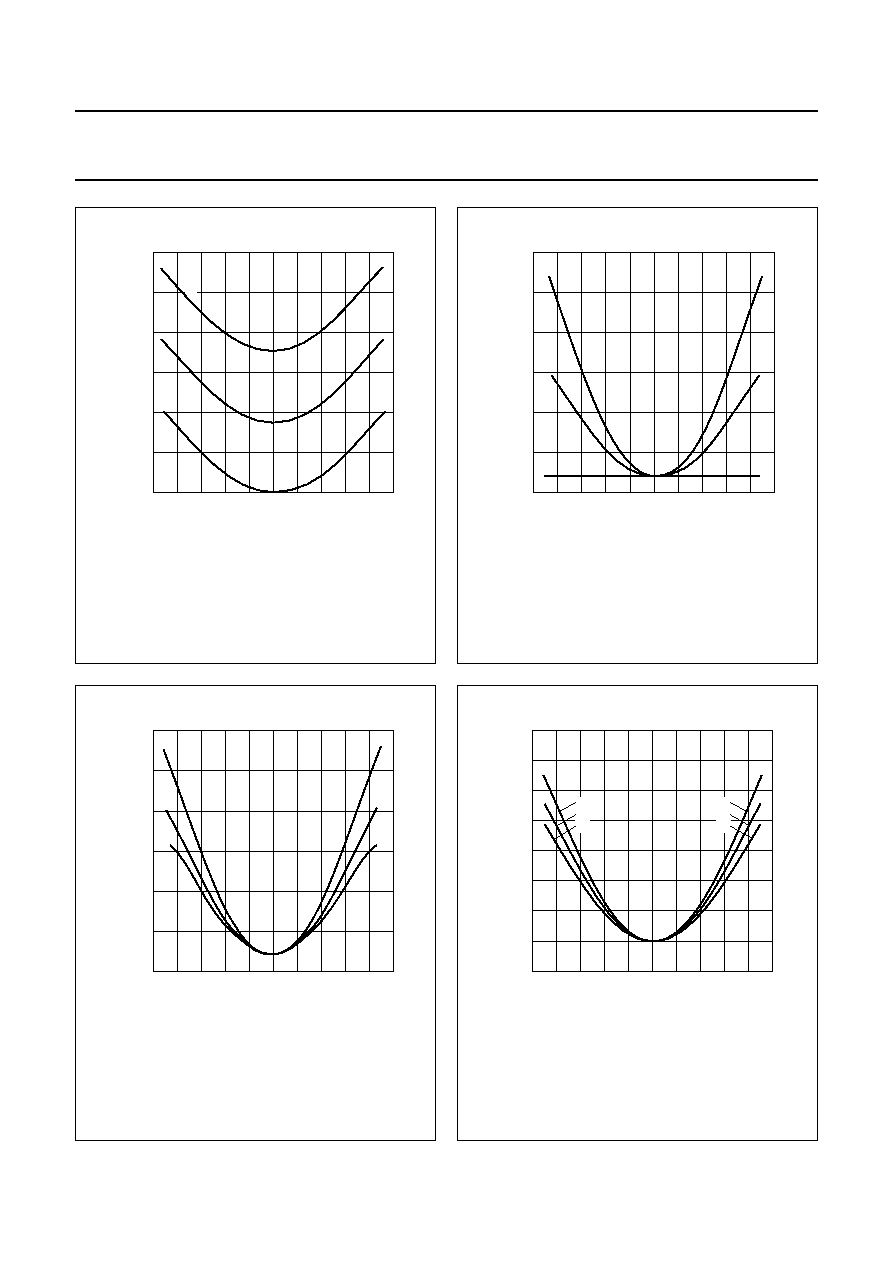

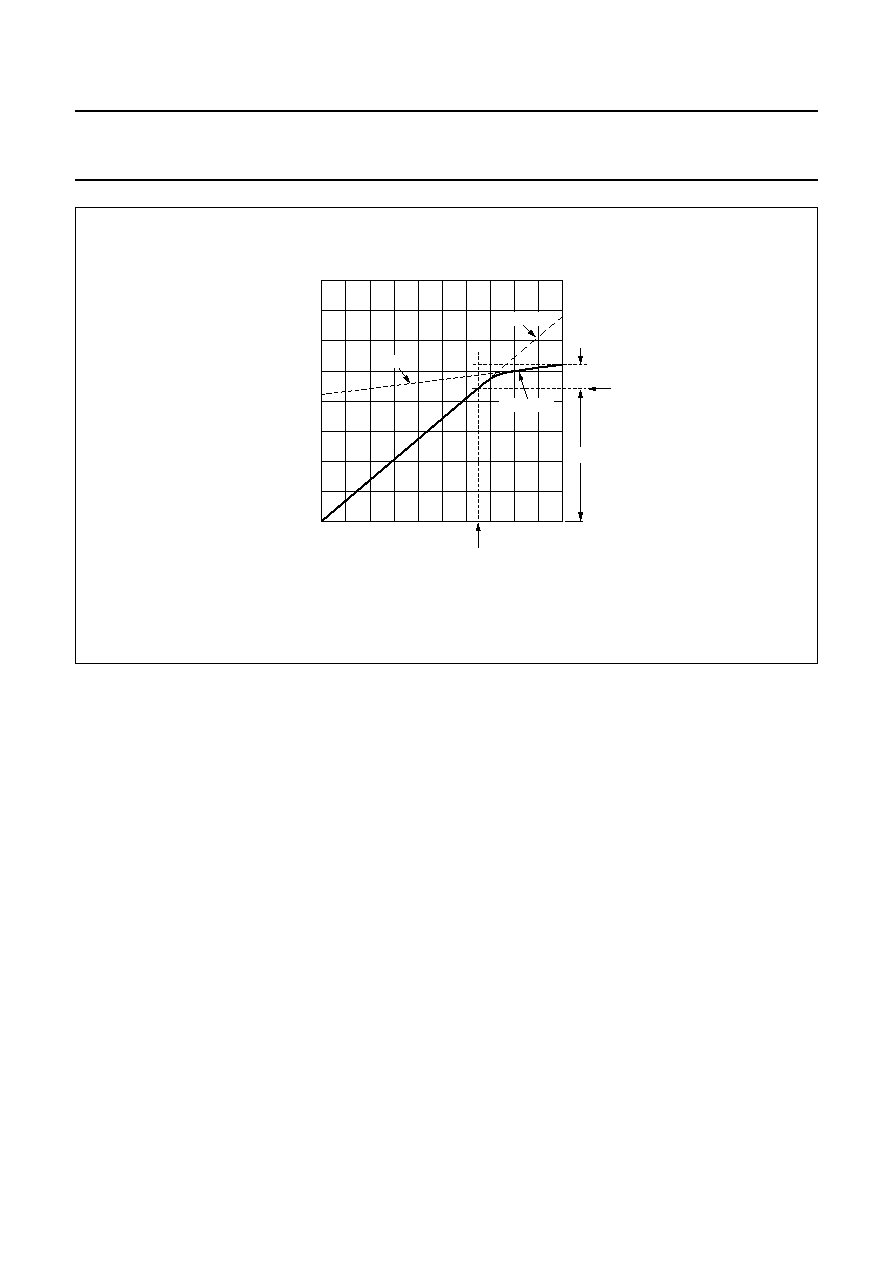

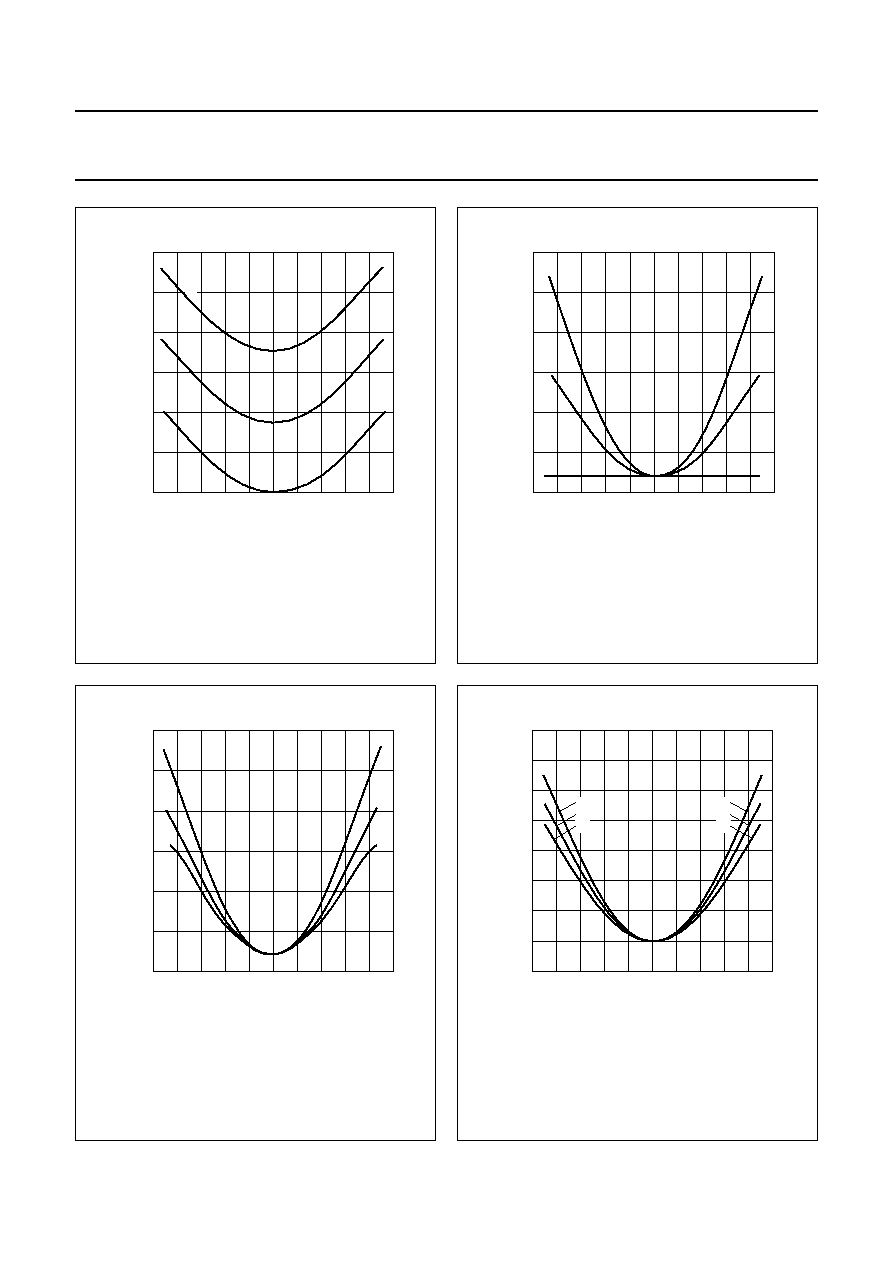

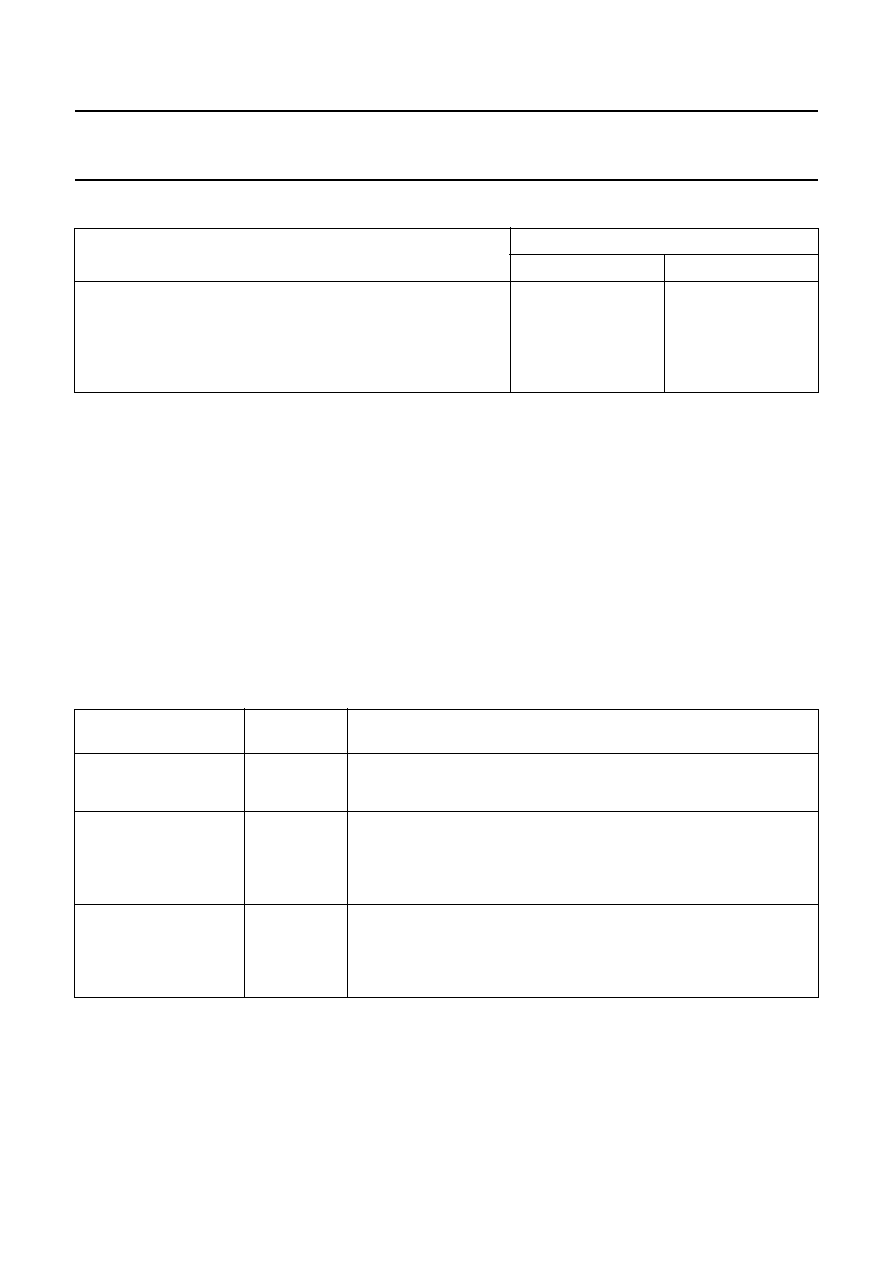

Saturation control; note 9

CR

sat

saturation control range

small signal gain; 63 steps;

see Fig.5

0

-

300

%

CR

sat(nom)

I

2

C-bus setting for nominal

saturation

YUV input signal

-

18 DEC

-

CR

sat(min)

minimum saturation

I

2

C-bus setting 0

-

-

50

-

dB

Contrast control; note 9

CR

contr

contrast control range

63 steps; see Fig.6

-

18

-

dB

tracking between the three

channels over a control range of

10 dB

-

-

0.5

dB

Brightness control; note 9

CR

bri

brightness control range

63 steps; see Fig.7

-

±

1.1

-

V

SYMBOL

PARAMETER

CONDITIONS

MIN.

TYP.

MAX.

UNIT

2002 Jun 04

20

Philips Semiconductors

Preliminary specification

I

2

C-bus controlled TV display processors

TDA933xH series

B

LACK LEVEL STRETCHER

; note 10

V

bl(max)

maximum black level shift

A-to-A; see Fig.8

15

21

27

IRE

V

bl

black level shift

at 100% peak white

-

1

0

+

1

IRE

at 50% peak white

-

1

-

+

3

IRE

at 15% peak white

6

8

10

IRE

RGB

AMPLIFIER OUTPUTS

:

PINS

40

TO

42

V

40-42(b-w)

output signal amplitude

(black-to-white value)

at nominal luminance input

signal and nominal

contrast, cathode drive

level and white-point

adjustment; note 11

-

2.0

-

V

V

o

output voltage range

1

-

V

CC

-

2

V

Z

o

output impedance

note 12

-

120

150

I

sink

sink current

emitter follower output

-

2

-

mA

V

o(RED)(p-p)

output signal amplitude for the `red'

channel (peak-to-peak value)

at nominal settings for

contrast and saturation

control and no luminance

signal at the input (R

-

Y,

PAL); note 11

-

2.1

-

V

V

bl(nom)

nominal black level voltage

-

2.5

-

V

V

bl

black level voltage

when black level

stabilization is switched off

(via AKB bit)

-

2.5

-

V

t

W(blank)

width of video blanking pulse with

bit HBL active

at 1f

H

; note 13

14.4

14.7

15.0

µ

s

at 2f

H

; note 13

7.2

7.35

7.5

µ

s

CR

bl

control range of the black current

stabilization

notes 15 and 16

-

±

1

-

V

V

blank

blanking voltage level

difference with black level;

note 11

-

0.4

-

0.5

-

0.6

V

V

blank(leak)

blanking voltage level during

leakage measurement

-

-

0.1

-

V

V

blank(l)

blanking voltage level during low

measuring pulse

-

0.25

-

V

V

blank(h)

blanking voltage level during high

measuring pulse

-

0.38

-

V

V

(RGB)(mp)

adjustment range of the ratio

between the amplitudes of the

RGB drive voltage and the

measuring pulses

note 11

-

±

6

-

dB

V

bl(WBC)

black level at the output at which

bit WBC is set to 1

nominal value

2.4

2.5

2.6

V

window; note 16

-

±

100

-

mV

bl/

T

variation of black level with

temperature

note 5

-

1.0

-

mV/K

CR

bl

black level offset adjustment range

on red and green channels

15 steps; 10 mV/step

±

70

±

75

±

80

mV

SYMBOL

PARAMETER

CONDITIONS

MIN.

TYP.

MAX.

UNIT

2002 Jun 04

21

Philips Semiconductors

Preliminary specification

I

2

C-bus controlled TV display processors

TDA933xH series

V

bl

relative variation in black level

between the three channels during

variations of

note 5

supply voltage (

±

10%)

nominal controls

-

-

20

mV

saturation (50 dB)

nominal contrast

-

-

20

mV

contrast (20 dB)

nominal saturation

-

-

20

mV

brightness (

±

0.5 V)

nominal controls

-

-

20

mV

temperature (range 40

∞

C)

-

-

20

mV

S/N

signal-to-noise ratio of the output

signals

notes 5 and 17

60

-

-

dB

B

o(Y)(10pF)

luminance bandwidth of output

signals

with 10pF load

capacitance; note 12

luminance input; at

-

3 dB 30

33

-

MHz

RGB-1 input; at

-

3 dB

28

31

-

MHz

RGB-2 input; at

-

3 dB

27

29

-

MHz

B

o(Y)(25pF)

luminance bandwidth of output

signals

with 25pF load capacitance

luminance input; at

-

3 dB 28

31

-

MHz

RGB-1 input; at

-

3 dB

27

30

-

MHz

RGB-2 input; at

-

3 dB

24

26

-

MHz

W

HITE

-

POINT ADJUSTMENT

I

2

C

nom

I

2

C-bus setting for nominal gain

-

32 DEC

-

G

RGB

adjustment range of RGB drive

levels

CL control bits; see

Table 15

±

3.2

±

3.6

±

4.0

dB

G

v

gain control range to compensate

spreads in picture tube

characteristics

white point controls

-

±

3

-

dB

2-

POINT BLACK CURRENT STABILIZATION

;

INPUT PIN

44; note 18

I

ref(l)

amplitude of low reference current

-

8

-

µ

A

I

ref(h)

amplitude of high reference current

-

20

-

µ

A

I

L

acceptable leakage current

-

±

100

-

µ

A

V

Iref

voltage on measurement pin

pin 44; loop closed

3.15

3.3

3.45

V

I

scan(max)

maximum current during scan

pin 44; loop open circuit

note 18

-

-

-

B

EAM CURRENT LIMITING

;

INPUT PIN

43

V

bias

internal bias voltage

3.5

3.6

3.7

V

V

CR

contrast reduction starting voltage

3.1

3.3

3.5

V

V

dif(CR)

voltage difference for full contrast

reduction

2.0

2.2

2.4

V

V

bri

brightness reduction starting

voltage

1.6

1.8

2.0

V

V

dif(BR)

voltage difference for full brightness

reduction

-

1

-

V

SYMBOL

PARAMETER

CONDITIONS

MIN.

TYP.

MAX.

UNIT

2002 Jun 04

22

Philips Semiconductors

Preliminary specification

I

2

C-bus controlled TV display processors

TDA933xH series

I

ch(int)

internal charge current

1.5

2.0

2.5

µ

A

I

dch(max)

maximum discharge current when

the PWL is active

3.5

4.0

4.5

mA

P

EAK WHITE LIMITER

; note 19

I

ch(PWL)

charge current PWL filter pin

pin 34; 1f

H

mode

13

16

19

µ

A

pin 34; 2f

H

mode

26

32

38

µ

A

I

dch(PWL)

discharge current PWL filter pin

pin 34; 1f

H

mode

26

32

38

µ

A

pin 34; 2f

H

mode

50

60

70

µ

A

V

i(Y)(b-w)

Y-input signal amplitude at which

peak white limiter is activated

(black-to-white value)

PWL range, 15 steps; at

maximum contrast

0.65

-

1.0

V

V

o(RGB)(b-w)

RGB output signal amplitude at

which peak white limiter is activated

(black-to-white value)

PWL range, 15 steps;

nominal setting of white

point controls; note 20

2.2

-

3.4

V

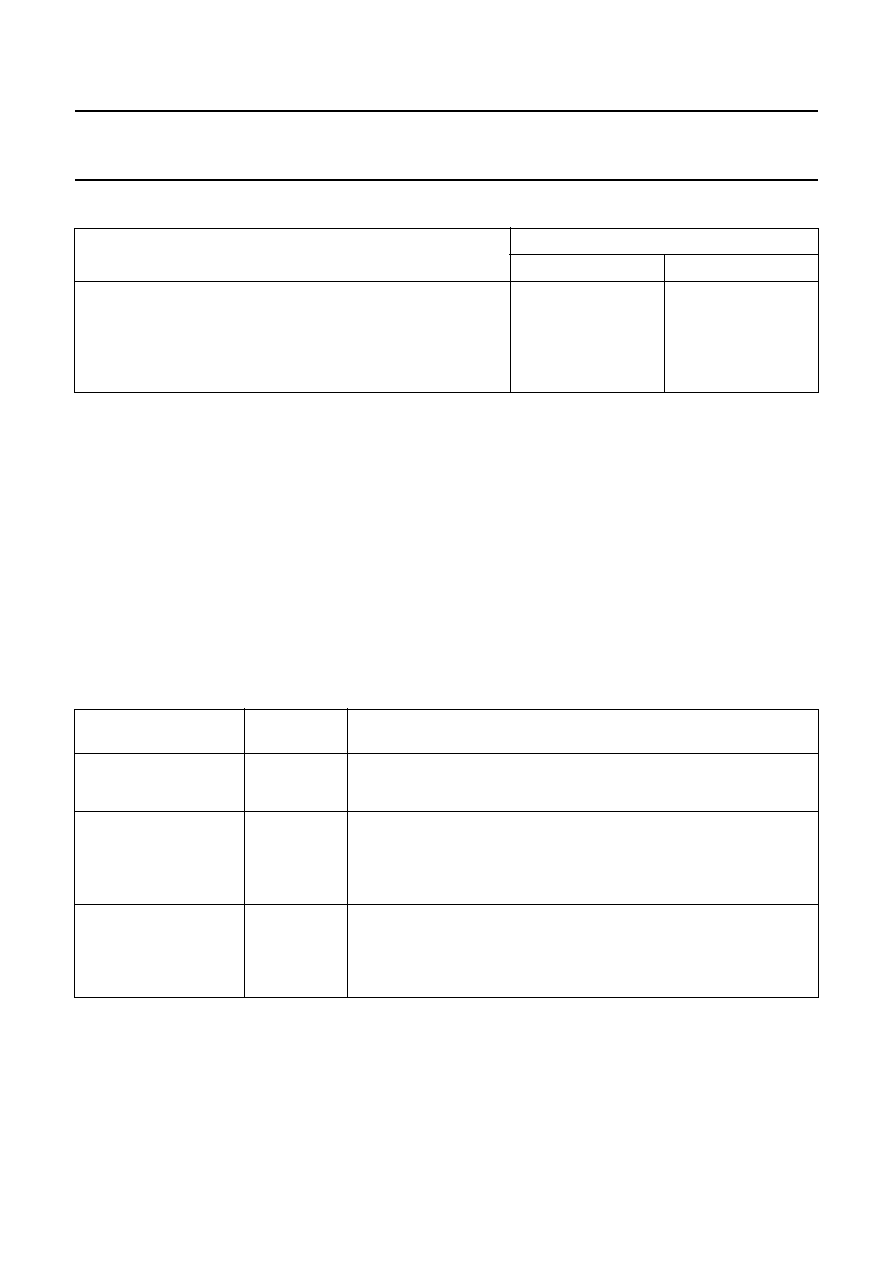

S

OFT CLIPPER

; note 21

G

v(sc)

soft clipper gain reduction

at maximum contrast;

see Fig.9

-

15

-

dB

V

o(clip-pwl)

output level compared to PWL for

100 IRE peak signal

(A+B)/A; see Fig.9

-

118

-

%

BLUE STRETCH

; note 22

G

RG

decrease of small signal gain for

red and green channels

-

17

-

%

F

IXED BEAM CURRENT SWITCH

-

OFF

; notes 23, 24 and 25

V

FBCSO

detection level

1

1.5

2

V

V

i(FBCSO)(max)

maximum input voltage

-

-

5.5

V

I

dch

discharge current when the fixed

beam current function is activated

sink current pin 44; note 26 0.85

1.0

1.15

mA

V

o(max)

maximum output voltage at the

RGB outputs

2-point stabilization;

note 26

-

6.0

-

V

1-point stabilization;

note 26

-

5.6

-

V

t

dch

discharge time of picture tube when

switching to standby

TFBC = 0; see Fig.15

-

18.6

-

ms

TFBC = 1; see Fig.15

-

25

-

ms

Horizontal synchronization and deflection

H

D

INPUT SIGNAL

;

PIN

24

V

IL

LOW-level of input voltage

note 27

-

-

0.8

V

V

IH

HIGH-level of input voltage

note 27

2.0

-

5.5

V

I

i(HD)

input current

-

10

-

+10

µ

A

t

r(HD)

rise time

-

-

100

ns

t

f(HD)

fall time

-

-

100

ns

t

W(HD)

pulse width

200 ns

-

1/4 line

SYMBOL

PARAMETER

CONDITIONS

MIN.

TYP.

MAX.

UNIT

2002 Jun 04

23

Philips Semiconductors

Preliminary specification

I

2

C-bus controlled TV display processors

TDA933xH series

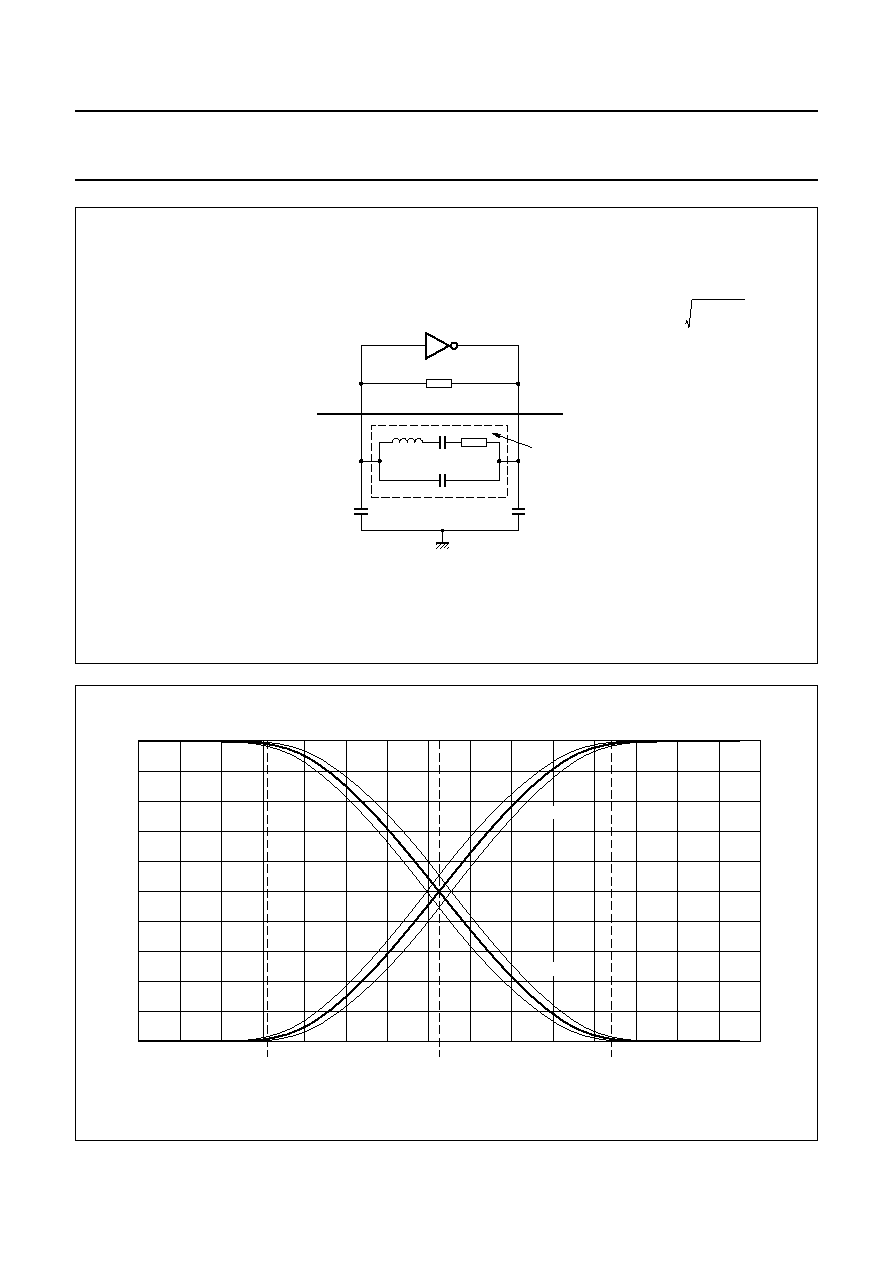

I

NTERNAL REFERENCE SIGNAL

;

CRYSTAL OR RESONATOR CONNECTED TO PINS

20

AND

21; note 28

f

xtal

resonator frequency

-

12

-

MHz

R

s(xtal)

resonator series resistance

C

L

= 60 pF

-

-

30

V

i(stab)(p-p)

stabilized input signal

(peak-to-peak value)

0.5

0.8

1.0

V

g

m(max)

maximum transconductance

4

5

-

mA/V

Z

i

input impedance

50

-

-

k

C

i

input capacitance

-

-

10

pF

C

o

output capacitance

-

-

5

pF

E

XTERNAL REFERENCE SIGNAL

;

INPUT PIN

20

f

XTALI

input signal frequency

-

12

-

MHz

V

i(XTALI)(p-p)

input signal amplitude

(peak-to-peak value)

AC coupled

0.8

-

2

V

F

IRST CONTROL LOOP

; note 29

f

o(nom)

free-running frequency

1f

H

mode; note 30

-

15.7

-

kHz

2f

H

mode; note 30

-

31.4

-

kHz

2f

H

mode; HDTV = 1;

note 30

-

33.8

-

kHz

2f

H

mode; CDTV = 1;

note 30

-

28.5

-

kHz

f

nom

tolerance on free-running

frequency

note 30

-

-

±

1

%

f

h/cr

holding/catching range of PLL

1f

H

mode

±

0.75

±

0.8

±

0.85

kHz

2f

H

mode

±

1.5

±

1.6

±

1.7

kHz

t

line

maximum line time difference per

line

1f

H

mode

-

2

-

+2

µ

s

2f

H

mode

-

1

-

+1

µ

s

f

contr

frequency control range in

multi-sync mode

1f

H

mode

15

-

25

kHz

2f

H

mode

30

-

50

kHz

f

corr

maximum speed of frequency

correction in multi-sync mode

-

-

100

kHz/s

V

HSEL

voltage on pin HSEL

1f

H

mode

0

-

1

V

2f

H

mode; pin must be left

open circuit

4

5

5.5

V

S

ECOND CONTROL LOOP

;

PIN

14

i

/

o

control sensitivity (loop gain)

t

i

/

t

0

500

-

-

µ

s/

µ

s

k

cor

correction factor k

note 31

-

0.5

-

t

contr

control range from start of

horizontal output to mid flyback

1f

H

mode; note 32

0

-

23.6

µ

s

2f

H

mode; note 32

0

-

11.8

µ

s

t

H(shift)

horizontal shift range

1f

H

mode; 63 steps

-

±

4.5

-

µ

s

2f

H

mode; 63 steps

-

±

2.25

-

µ

s

SYMBOL

PARAMETER

CONDITIONS

MIN.

TYP.

MAX.

UNIT

2002 Jun 04

24

Philips Semiconductors

Preliminary specification

I

2

C-bus controlled TV display processors

TDA933xH series

control sensitivity for dynamic

phase compensation

1f

H

mode

-

0.4

-

µ

s/V

2f

H

mode

-

0.2

-

µ

s/V

V

i(DP)(comp)

input voltage range for dynamic

phase compensation

pin 14; note 33

1.5

4

6.5

V

Z

i

input impedance

pin 14; note 33

100

k

t

par(cor)(max)

maximum range of parallelogram

correction

1f

H

mode; end of field;

flyback width 11

µ

s;

note 34

±

0.40

±

0.50

±

0.60

µ

s

2f

H

mode; end of field;

flyback width 5.5

µ

s;

note 34

±

0.20

±

0.25

±

0.30

µ

s

t

bow(cor)(max)

maximum range of bow correction

1f

H

mode; end of field;

flyback width 11

µ

s;

note 34

±

0.40

±

0.50

±

0.60

µ

s

2f

H

mode; end of field;

flyback width 5.5

µ

s;

note 34

±

0.20

±

0.25

±

0.30

µ

s

H

ORIZONTAL FLYBACK INPUT

;

PIN

13

V

sw(HBLNK)

switching level for horizontal

blanking

0.2

0.3

0.4

V

V

sw(p2)

switching level for phase detection

3.8

4.0

4.2

V

V

i(HFB)(max)

maximum input voltage

-

-

V

P

V

Z

i

input impedance

10

-

-

M

H

ORIZONTAL OUTPUT

;

PIN

8,

OPEN COLLECTOR

; note 35

V

OL

LOW-level output voltage

I

o

= 10 mA

-

-

0.3

V

I

o(hor)

maximum allowed output current

-

-

10

mA

V

o(max)

maximum allowed output voltage

-

-

V

P

V

duty factor

V

o

= LOW (t

on

)

51.6

51.8

52.0

%

t

on

switch-on time of horizontal drive

pulse

TV mode, HDTV = 0,

ESS = 0

155

159

163

ms

t

off

switch-off time of horizontal drive

pulse

TV mode, HDTV = 0,

ESS = 0

48

50

52

ms

t

on(ess)

switch-on time for extended slow

start

TV mode, HDTV = 0,

ESS = 1

1150

1175

1200

ms

t

jitter (

)

1f

H

mode; note 36

-

1.4

-

ns

2f

H

mode; note 36

-

1.0

-

ns

S

ANDCASTLE OUTPUT

;

PIN

9; note 37

V

SCO(0)

zero level

0

0.5

1.0

V

I

sink

sink current

0.5

0.7

0.9

mA

V

o(SCO)

output voltage

during clamp pulse

4.2

4.5

4.8

V

during blanking

2.3

2.5

2.7

V

I

source

source current

0.5

0.7

0.9

mA

SYMBOL

PARAMETER

CONDITIONS

MIN.

TYP.

MAX.

UNIT

2002 Jun 04

25

Philips Semiconductors

Preliminary specification

I

2

C-bus controlled TV display processors

TDA933xH series

I

i(grd)

guard pulse input current required

to stop the blanking after a vertical

blanking period

note 38

1.0

-

3.5

mA

t

W(1)

pulse width in 1f

H

mode

clamp pulse, 22 LLC

pulses

-

3.2

-

µ

s

vertical blanking (50/60 Hz)

-

22/17

-

lines

t

W(2)

pulse width in 2f

H

mode

clamp pulse, 22 LLC

pulses

-

1.6

-

µ

s

clamp pulse, HDTV = 1,

HDCL = 1, 18 LLC; see

Fig.11

-

1.22

-

µ

s

vertical blanking;

depends on VWAIT setting;

see Fig.13

-

-

t

d(bk-HD)

delay between start H

D

pulse and

start of clamp pulse

1f

H

mode, 37 LLC pulses

-

5.4

-

µ

s

2f

H

mode, 37 LLC pulses

-

2.7

-

µ

s

2f

H

mode, HDCL = 1,

14 LLC pulses, see Fig.11

-

0.94

-

µ

s

Vertical synchronization and geometry processing

V

D

INPUT SIGNAL

;

PIN

23

V

IL

LOW-level of input voltage

-

-

0.8

V

V

IH

HIGH-level of input voltage

2.0

-

5.5

V

I

i(VD)

input current

-

10

-

+10

µ

A

t

r(VD)

rise time

-

-

100

ns

t

f(VD)