October 1992

2

Philips Semiconductors

Product specification

Low-power frequency synthesizer for

mobile radio communications

UMA1014

FEATURES

∑

Single chip synthesizer; compatible with Philips cellular

radio chipset

∑

Fully programmable RF divider

∑

I

2

C interface for two-line serial bus

∑

On-chip crystal oscillator/TCXO buffer from 3 to 16 MHz

∑

16 reference division ratios allowing 5 to 100 kHz

channel spacing

∑

1/8 crystal frequency output

∑

On-chip out-of-lock indication

∑

Two extra VCO control outputs

∑

Latched synthesizer alarm output

∑

Status register including out-of-lock indication and

power failure

∑

Power-down mode.

APPLICATIONS

∑

Cellular mobile radio (NMT, AMPS, TACS)

∑

Private mobile radio (PMR)

∑

Cordless telephones.

GENERAL DESCRIPTION

The UMA1014 is a low-power universal synthesizer which

has been designed for use in channelized radio

communication. The IC is manufactured in bipolar

technology and is designed to operate at 5 to 100 kHz

channel spacing with an RF input from 50 to 1100 MHz.

The channel is programmed via a standard I

2

C-bus. A

low-power sensitive RF divider is incorporated together

with a dead-zone eliminated, 3-state phase comparator.

The low-noise charge pump delivers 1 mA or 1/2 mA

output current to enable a better compromise between fast

switching and loop bandwidth. A power-down circuit

enables the synthesizer to be set to idle mode.

QUICK REFERENCE DATA

ORDERING INFORMATION

SYMBOL

PARAMETER

MIN.

TYP.

MAX.

UNIT

V

CC

, V

CP

supply voltage range

4.5

5.0

5.5

V

I

CC

+ I

CP

supply current

-

13

-

mA

I

CCpd

I

CC

in power-down

-

2.5

-

mA

f

ref

phase comparator reference frequency

5

-

100

kHz

f

RF

RF input frequency

50

-

1100

MHz

T

amb

operating ambient temperature range

-

40

-

85

∞

C

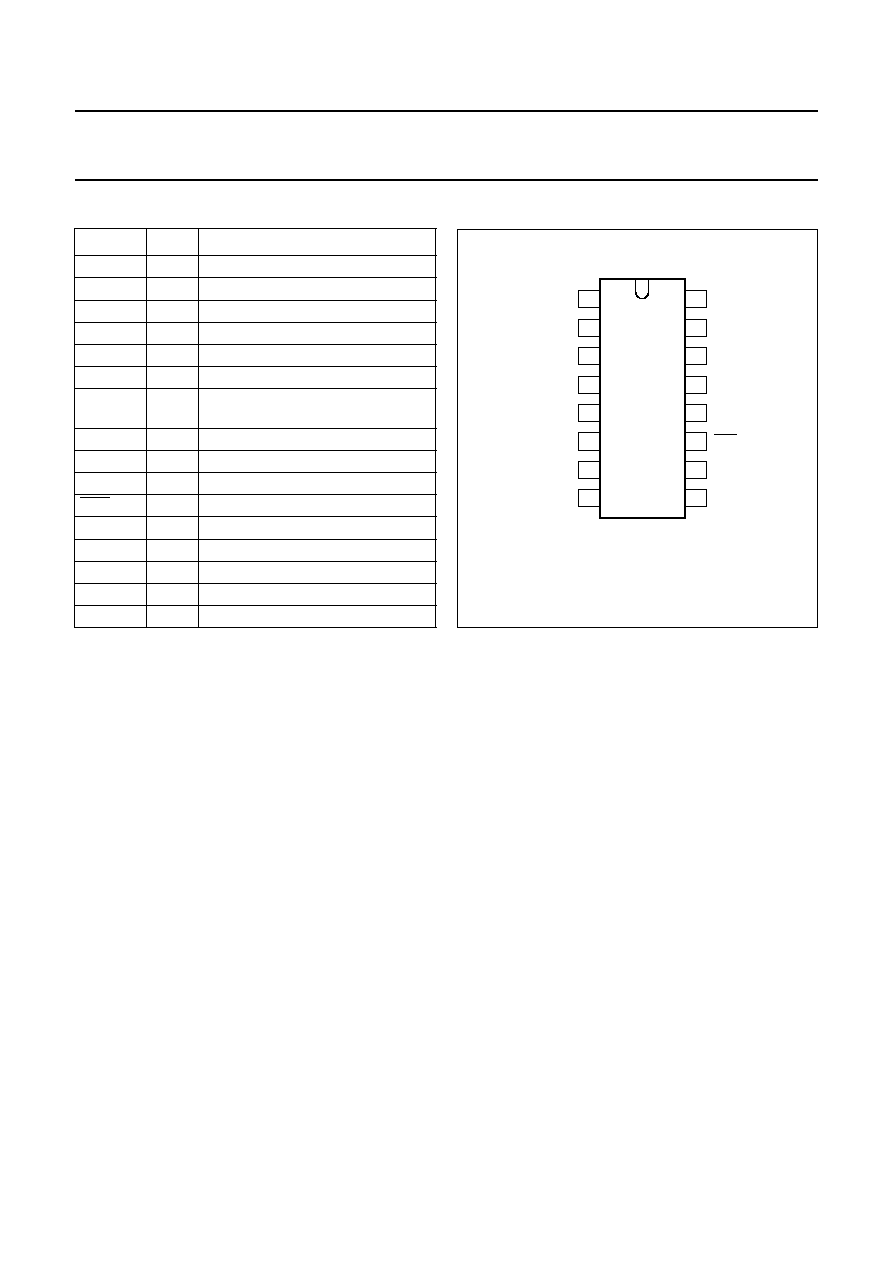

TYPE NUMBER

PACKAGE

NAME

DESCRIPTION

VERSION

UMA1014T

SO16

plastic small outline package; 16 leads; body width 3.9 mm

SOT109-1

October 1992

5

Philips Semiconductors

Product specification

Low-power frequency synthesizer for

mobile radio communications

UMA1014

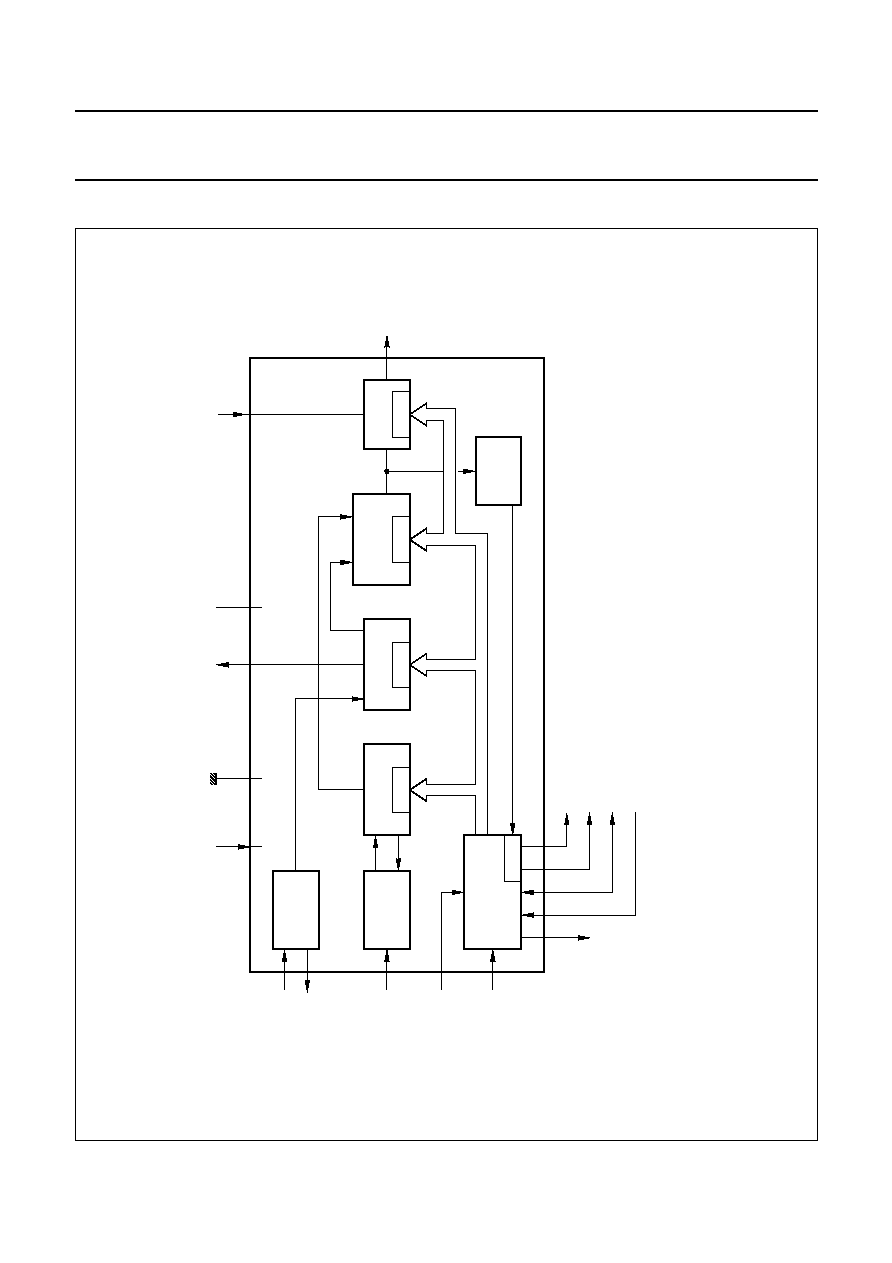

FUNCTIONAL DESCRIPTION

The UMA1014 is a low-power frequency synthesizer for

radio communication which operates in the

50 to 1100 MHz range. The device includes an

oscillator/buffer circuit, a reference divider, an RF divider,

a 3-state phase comparator, a charge pump and a main

control circuit to transfer the serial data into the four

internal 8-bit registers. The V

CC

supply feeds the logic part,

the V

CP

supply feeds the charge-pump only. Both supplies

are +5 V (

±

10%). The power-down facility puts the

synthesizer in the idle mode (all current supplies are

switched off except in the control part). This allows any I

2

C

transfer and all information in the registers is retained thus

enabling fast power-up.

Main divider

The main divider is a pulse swallow type counter which is

fully programmable. After a sensitive input amplifier

(50 mV,

-

13 dBm), the RF signal is applied to a 31/32

duo-modulus counter. The output is then used as the clock

for the 5-bit swallow counter R = (MD4 to MD0) and the

13-bit main counter N = (MD17 to MD5). The ratio is

transferred via the I

2

C-bus to the registers B, C and D, and

then buffered in an 18-bit latch. The ratio in the divider

chain is updated with the new information when the least

significant bit is received (i.e. D0). This update is

synchronized to the output of the divider in order to limit the

phase error during small jumps of the synthesized

frequency.

The main divider can be programmed to any value

between 2048 and 262143 (i.e. 2

18

-

1). If ratio X, below

2048, is sent to the divider, the ratio (X + 2048) will be

programmed. When it is required to switch between

adjacent channels it is possible to program register D only,

thus allowing shorter I

2

C programming time.

Oscillator

The oscillator is a common collector Colpitts type with

external capacitive feedback. The oscillator has very small

temperature drift and high voltage supply rejection. A

TCXO or other type of clock can be used to drive the

oscillator by connecting the source (preferably

AC-coupled) to pin 1 and leaving pin 2 open-circuit. The

oscillator acts as a buffer in this mode and requires no

additional external components. The signal from the clock

source should have a minimum space width of 31 ns.

Reference divider

The reference divider is semi-programmable with 16

division ratios which can be selected via the I

2

C-bus. The

programming uses four bits of the register A (A3 to A0) as

listed in Table 2. These ratios allow the use of a large

number of crystal frequencies from 3 MHz up to 16 MHz.

All main channel spacings can be obtained with a single

crystal/TXCO frequency of 9.6 MHz.

Phase comparator

A diagram of the phase comparator and charge pump is

illustrated in Fig.3.

The phase comparator is both a phase and frequency

detector. The detector comprises dual flip-flops together

with logic circuitry to eliminate the dead-zone. When a

phase error is detected the UP or DOWN signal goes

HIGH. This switches on the corresponding current

generator which produces a source or sink current for the

loop filter. When no phase error is detected PCD goes high

impedance. The final tuning voltage for the VCO is

provided by the loop filter. The charge pump current is

programmable via the I

2

C-bus. When IPCD (bit 5) is set to

logic 1 the charge pump delivers 1 mA; when IPCD is set

to logic 0 the charge pump delivers 0.5 mA.

The phase comparator has a phase inverter logic input

(PHI). This allows the use of inverted or non-inverted loop

filter configurations. It is thus possible to use a passive

loop filter which offers higher performances without an

operational amplifier. The function of the phase

comparator is given in Table 3 and a typical transfer curve

is illustrated in Fig.4.

Out-of-lock detector

An out-of-lock detector using the UP and DOWN signals

from the phase comparator is included on-chip. The pin

VCOA is an open collector output which is forced LOW

during an out-of-lock condition. The same information is

also available via the I

2

C-bus in the status register (bit

OOL). When the phase error (measured at the phase

comparator) is greater than approximately 200 ns, an

out-of-lock condition is immediately flagged. The flag is

only released after 6 reference cycles when the phase

error is less than 200 ns.