PLL202-107

Programmable Clock Generator for SIS 645/650 P4 Chip Sets

47745 Fremont Blvd., Fremont, California 94538 TEL (510) 492-0990 FAX (510) 492-0991 Rev 10/28/02 Page 1

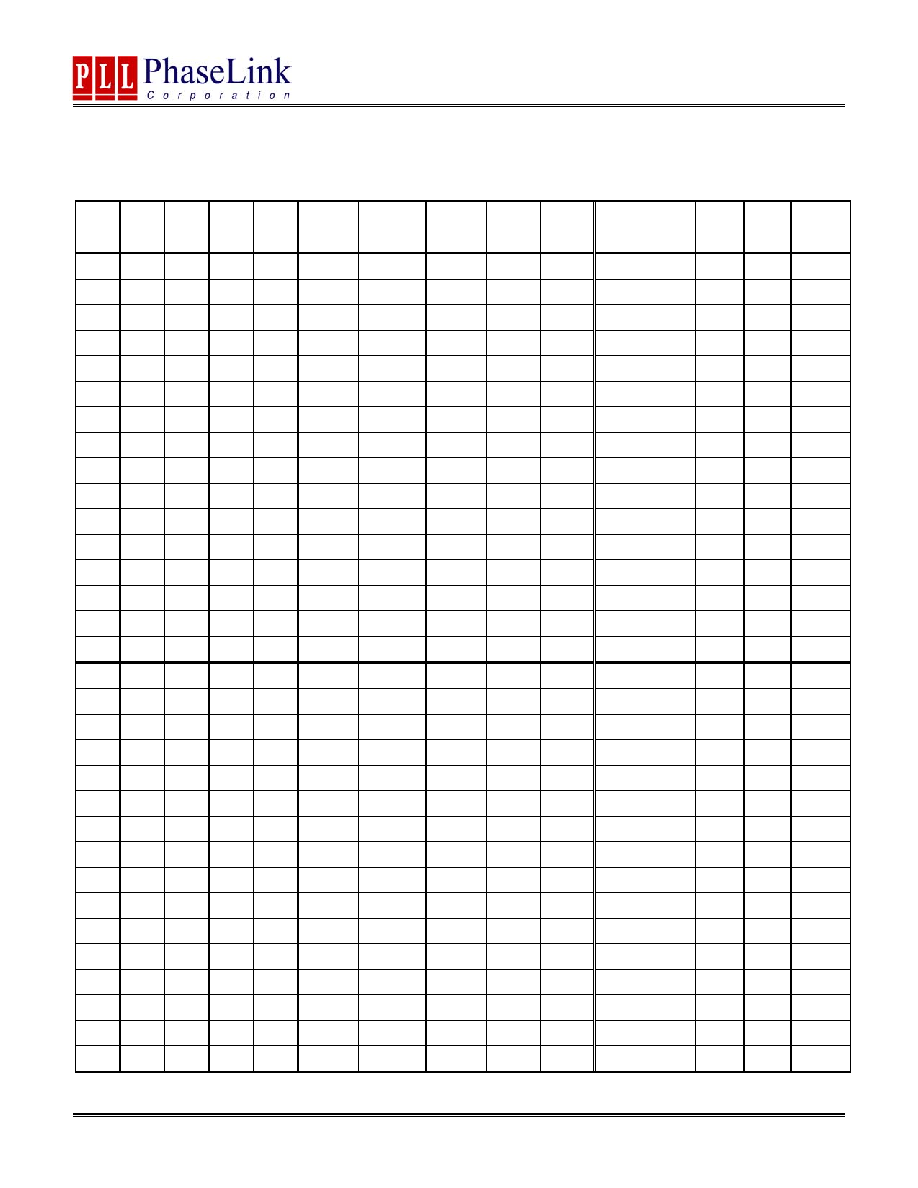

48Mhz

24_48Mhz

PD#

XIN

XOUT

SDATA

SCLK

MULTSEL

XTAL

OSC

I2C

Logic

PLL1

SST

Control

Logic

REF(0:2)

ZCLK (0:1)

AGP (0:1)

PCI (0:5)

PCI_F(0:1)

PLL2

� 2

Watch

Dog

WDRESET#

VDD

VDD

VDD

VDD_CPU

CPUT (0:1)

CPUC (0:1)

PCI_STOP#

CPU_STOP#

FS(0:4)

SDCLK

PD#

FEATURES

� Supports SIS 645/650, 646, 648 Chipsets.

� Programmable Spread Spectrum Modulation

from

�0.1% to �1.5% with step size as small as

�0.012%.

� Selectable Spread Spectrum either center or

down.

� Selectable Spread Spectrum modulation profile.

� AccuSkew

TM,

Programmable Precision skew

tuning channel with maximum

�5% precision

over the variation of temperature, process and

voltage with step size as small as 80ps.

� AccuDrive

TM

Programmable Output Buffer drive

strength with up to +50% or �40%.

� Programmable VCO frequency with one variable

� Programmable Output Divider for CPU, SDRAM,

ZCLK, AGP and PCI.

� 2 differential CPUCLK, 1 SDRAM, 2 ZCLK, 2

AGP, 8 PCI, 1 USB and 3 REF clock outputs.

� 1 programmable 24MHz or 48MHz for SIO.

� Support 2-wire I2C serial bus interface.

� Built-in programmable watchdog timer

� Available in 300 mil 48 pin SSOP.

BLOCK DIAGRAM

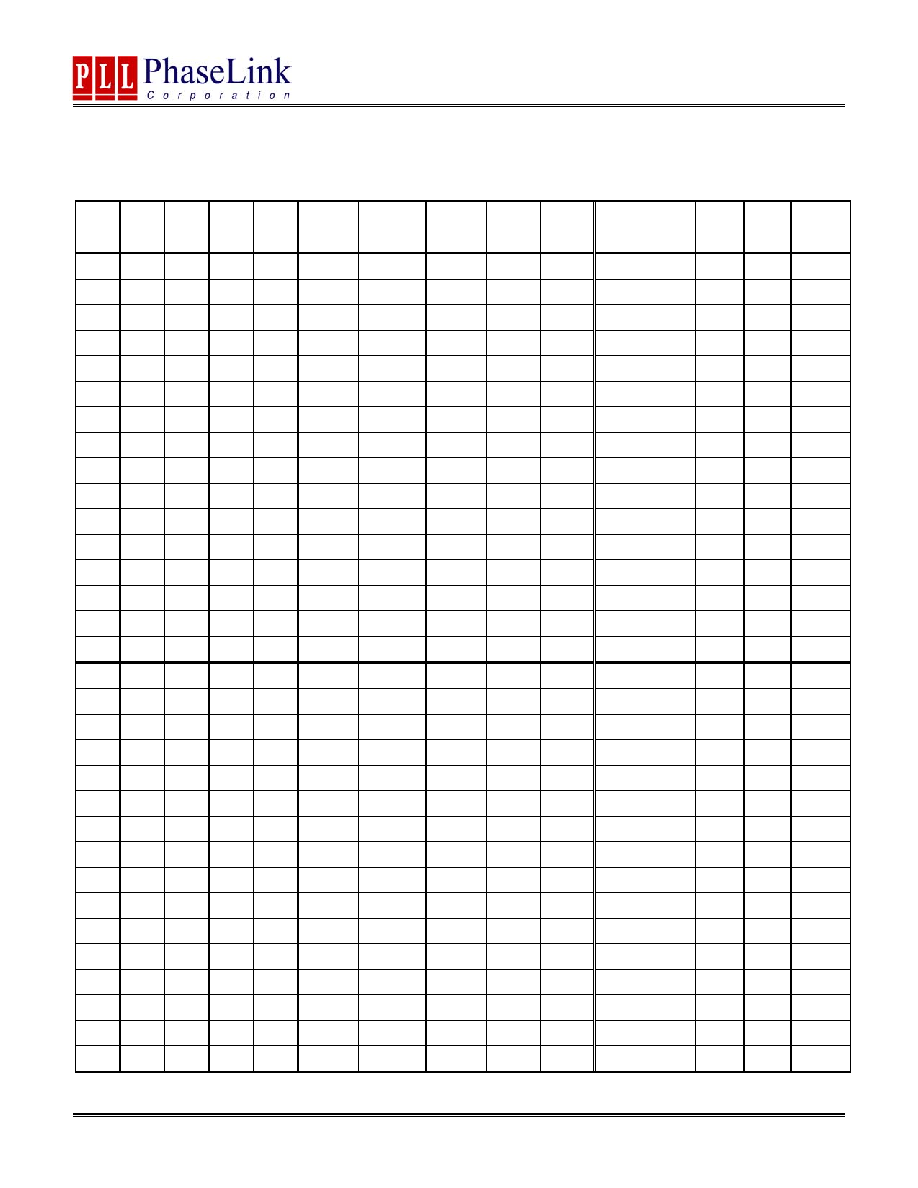

PIN CONFIGURATION

Note:

^:

Pull Up (120k

),

v:

Pull down (120k

), #: Active low,

*

: Bi-directional latched at power-up

POWER GROUP

� VDDREF (3.3V), VSSREF: REF, XIN, XOUT

� VDDPCI (3.3V), VSSPCI: PCI

� VDDAGP (3.3V), VSSAGP: AGP

� VDD48M (3.3V), VSS48M: 48MHz, 24_48MHz

� VDDCPU (3.3V), VSSCPU: CPUT/C_[0:1]

� VDDSD (3.3V), VSSSD: SDCLK

� VDDA (3.3V), VSSA: PLL Analog

� VDDZ (3.3V), VSSZ: ZCLK

KEY SPECIFICATIONS

� CPU - CPU Output Skew < 150ps.

� AGP(Z) - AGP(Z) Output Skew < 175ps

� PCI - PCI Output Skew <500ps

� CPU to SDCLK Skew: -2 to 2 ns (Typ 0ns).

� CPU (early) to AGP Skew: 1 to 4 ns (Typ 2ns).

� CPU (early) to Z Skew: 1 to 4 ns (Typ 2ns).

� CPU (early) to PCI Skew: 1 to 4ns (Typ 2ns).

PLL202-107

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

41

42

44

43

45

46

47

48

VDDPCI

PCI4

VSSPCI

PCI1

PCIF1/FS4*

v

VDDPCI

REF0/FS0*

v

VSSREF

ZCLK0

WDRESET/PCISTOP#

^

PCIF0/FS3*

v

PCI0

PCI5

VSSPCI

VDDREF

XOUT

VSSZ

ZCLK1

VDDZ

PCI2

PCI3

XIN

VSSCPU

CPUT_0

VSSSD

IREF

VSSA

VDDA

CPU_STOP#

^

SDCLK

VSSAGP

AGP0

VSS48M

24_48MHz/MULTSEL*

^

VDDSD

CPUT_1

CPUC_1

CPUC_0

SCLK

SDATA

PD#

^

/Vtt_PWRGD

AGP1

VDDAGP

VDD48M

48MHz

VDDCPU

REF1/FS1*

v

REF2/FS2*

v

PLL202-107

Programmable Clock Generator for SIS 645/650 P4 Chip Sets

PIN DESCRIPTIONS

Name Number

Type

Description

XIN

6

I

14.318Mhz crystal input to be connected to one end of the crystal

XOUT

7

O

14.318Mhz crystal output

REF[0:2]/FS[0:2]

2,3,4

B

14.318Mhz Reference clock output. This pin latch FS[0:2] value at power-

up. (See Frequency Selection table). It has an internal pull down resistor.

PD#/Vtt_PWRGD

33

I

At power-up, this pin is the input of Vtt_PWRGD After the first high to low,

this pin acts as PD# to disable all clock outputs including internal VCO and

crystal clock when Low. When Vtt_PWRGD input is high, FS (0:4) and

MULTSEL0 inputs are latched and all outputs are enabled.

AGP[0:1]

30,31

O

AGP clock output (see Frequency table).

ZCLK[0:1]

9,10

O

Hyper Zip clock output (see Frequency table).

CPU_STOP#

45

I

Stop all CPU clock outputs when low. It has 120K ohm internal pull up

resistor.

WDRESET/

PCI_STOP#

12

B

Watch Dog reset will be generated after timer expires when I2C Enable bit

(Byte12.bit7) is set active. When It is inactive, this pin acts as PCI_STOP

input to stop all PCI clock outputs except PCIF[0:1] when low. It has 120K

ohm internal pull up resistor.

PCI[0:5] 16,17,20

21,22,23

O

PCI clock output (see Frequency table). PCI5 has I2C programmable double

drive strength.

24_48MHz/MULTSEL

26

B

This pin latches the MULTSEL value at power-up. After power-up, this pin

acts as 24_48Mhz clock output with default 24MHz or selection by I2C.

MULTSEL is used to select the current multiplier for the CPU outputs.

If MULTSEL=0, IOH=4XIREF.

If MULTSEL=1, IOH=6XIREF

CPU[C/T]_0

39,40

O

Differential pair output for CPU Host.

CPU[C/T]_1

43,44

O

Differential pair output for CPU Chip Sets.

PCIF[0:1]/FS[3:4]

14,15

B

Bi-directional pin. At power-up, the FS[3:4] input value is latched. After

power-up, this pin acts as PCIF[0:1] output. It has an internal pull-down

resistor.

SDCLK

37

O

SDRAM clock output

48MHz

27

O

USB clock output.

Iref

38

I

This pin establishes the reference current for the CPU differential pairs, it

requires a fixed precision resistor tied to ground in order to establish the

appropriate current.

SDATA

34

B

Serial data inputs for serial interface port.

SCLK

35

I

Serial data inputs for serial interface port.

47745 Fremont Blvd., Fremont, California 94538 TEL (510) 492-0990 FAX (510) 492-0991 Rev 10/28/02 Page 2

PLL202-107

Programmable Clock Generator for SIS 645/650 P4 Chip Sets

PIN DESCRIPTIONS (Continue)

Name Number

Type

Description

VDDPCI

13

P

3.3V Power Supply for PCIF[0:1], PCI[0:5] clock

VDDZ

11

P

3.3V Power Supply for Zclock.

VDDAGP

29

P

3.3V Power Supply for AGP clock.

VDDSD

48

P

3.3V Power Supply for SDCLK clock.

VDD48M

28

P

3.3V Power Supply for 48MHz and 24_48MHz clock

VDDA

36

P

3.3V power for internal PLL.

VDDCPU

42

P

3.3v power supply for CPU[T,C]_[0:1] clocks.

VDDREF

1

P

3.3v power supply for REF[0:2] clocks

VSS 5,8,18,19

27,34,41,46

P Ground.

HOST SWING SELECT FUNCTIONS

MULTISEL0

Board Target

Trace/Term Z

Reference R (Rr)

I

ref

= VDD/(3*Rr)

Output Current

V

oh

@ Z

0

50

Rr = 221

; 1%

Iref = 5.0mA

I

oh

= 4*IREF

1.0V @ 50

1

50

Rr = 475

; 1%

Iref = 2.32 mA

I

oh

= 6*IREF

0.7V @ 50

47745 Fremont Blvd., Fremont, California 94538 TEL (510) 492-0990 FAX (510) 492-0991 Rev 10/28/02 Page 3

PLL202-107

Programmable Clock Generator for SIS 645/650 P4 Chip Sets

FREQUENCY (MHz) SELECTION TABLE

FS4 FS3 FS2 FS1 FS0 CPU SDCLK ZCLK AGP PCI

SST

Amplitude

VCO

(CPU)

N

0 0 0 0 0 66.67 66.67 66.67 66.67

33.33

�0.5% center

400 0.30 14,303

0 0 0 0 1 100.00 133.33 66.67 66.67 33.33

�0.3% center

400 0.45 14,303

0 0 0 1 0 111.17 166.75 66.70 66.70 33.35

�0.3% center

667 0.30 23,851

0 0 0 1 1 100.00 200.00 66.67 66.67 33.33

�0.3% center

400 0.45 14,303

0 0 1 0 0 100.00 100.00 133.33 66.67 33.33

�0.3% center

400 0.45 14,303

0 0 1 0 1 133.40 133.40 133.40 66.70 33.35

�0.3% center

667 0.36 23,851

0 0 1 1 0 133.40 166.75 133.40 66.70 33.35

�0.3% center

667 0.36 23,851

0 0 1 1 1 133.33 200.00 133.33 66.67 33.33

�0.3% center

400 0.60 14,303

0 1 0 0 0 100.00 166.67 66.67 66.67 33.33

�0.3% center 1000 0.18 35,759

0 1 0 0 1 100.00 133.33 133.33 66.67 33.33

�0.3% center

400 0.45 14,303

0 1 0 1 0 111.17 166.75 133.40 66.70 33.35

�0.3% center

667 0.30 23,851

0 1 0 1 1 100.00 200.00 133.33 66.67 33.33

�0.3% center

400 0.45 14,303

0 1 1 0 0 100.00 133.33 100.00 66.67 33.33

�0.3% center

400 0.45 14,303

0 1 1 0 1 133.33 133.33 100.00 66.67 33.33

�0.3% center

400 0.60 14,303

0 1 1 1 0 100.00 166.67 133.33 66.67 33.33

�0.3% center 1000 0.18 35,759

0 1 1 1 1 166.75 133.40 133.40 66.70 33.35

�0.3% center

667 0.45 23,851

1 0 0 0 0 166.67 200.00 133.33 66.67 33.33

�0.3% center 1000 0.30 35,759

1 0 0 0 1 150.00 150.00 120.00 60.00 30.00

�0.3% center

600 0.45 21,455

1 0 0 1 0 140.00 140.00 140.00 70.00 35.00

�0.3% center

700 0.36 25,031

1 0 0 1 1 166.75 166.75 133.40 66.70 33.35

�0.3% center

667 0.45 23,851

1 0 1 0 0 100.00 133.33 66.67 50.00 33.33

�0.3% center

400 0.45 14,303

1 0 1 0 1 100.00 133.33 80.00 50.00 33.33

�0.3% center

400 0.45 14,303

1 0 1 1 0 133.40 133.40 66.70 55.58 33.35

�0.3% center

667 0.36 23,851

1 0 1 1 1 133.40 166.75 83.38 55.58 33.35

�0.3% center

667 0.36 23,851

1 1 0 0 0 111.17 133.40 133.40 66.70 33.35

�0.3% center

667 0.30 23,851

1 1 0 0 1 125.00 166.67 166.67 62.50 33.33

�0.3% center

500 0.45 17,879

1 1 0 1 0 100.00 140.00 140.00 58.33 35.00

�0.3% center

700 0.26 25,031

1 1 0 1 1 120.00 150.00 150.00 60.00 33.33

�0.3% center

600 0.36 21,455

1 1 1 0 0 133.33 133.33 133.33 57.14 33.33

�0.3% center

400 0.60 14,303

1 1 1 0 1 100.00 133.33 133.33 50.00 33.33

�0.3% center

400 0.45 14,303

1 1 1 1 0 180.00 150.00 128.57 60.00 30.00

�0.3% center

900 0.36 32,183

1 1 1 1 1 200.00 200.00 133.33 66.67 33.33

�0.3% center

800 0.45 28,607

47745 Fremont Blvd., Fremont, California 94538 TEL (510) 492-0990 FAX (510) 492-0991 Rev 10/28/02 Page 4

PLL202-107

Programmable Clock Generator for SIS 645/650 P4 Chip Sets

47745 Fremont Blvd., Fremont, California 94538 TEL (510) 492-0990 FAX (510) 492-0991 Rev 10/28/02 Page 5

I2C BUS CONFIGURATION SETTING

Address Assignment

A6 A5 A4 A3 A2 A1 A0 R/W

1 1 0 1 0 0 1 _

Slave

Receiver/Transmitter

Provides both slave write and readback functionality

Data Transfer Rate

Standard mode at 100kbits/s

Data Protocol

This serial interface is designed to allow multiple protocols to write and read from the

controller. It includes Block Read/Write, Block Index Read/Write, Byte Read/Write and Word

Read/Write. In general, the bytes must be accessed in sequential order from lowest to highest

byte. Each byte transferred must be followed by 1 acknowledge bit. A byte transferred without

acknowledged bit will terminate the transfer. The write or read block both begins with the

master sending a slave address and a write condition (0xD2) or a read condition (0xD3).

WRITE MODE

Block

Write

S

Address

D2

A

Command

00

A

A

A

A

A

A P

Block

Index Write

S

Address

D2

A

Command M

=(00~22)

A

A

A

A

A

A P

Byte Write

S

Address

D2

A

Command M'

=(00~22)+128

A

A P

Word Write S

Address

D2

A

Command M'

=(00~22)+128

A

A

A P

READ MODE

Block

Read

S

Address

D2

A

Command

00

A S

A

A

A

A

A

Data

Byte N

A P

Block

Index Read

S

Address

D2

A

Command M

=(00~22)

A S

A

A

A

A

A

Data

Byte M+N-1

A P

Byte Read

S

Address

D2

A

Command M'

=(00~22)+128

A S

A

A P

Word Read S

Address

D2

A

Command M'

=(00~22)+128

A S

A

A

A P

Legend:

S Start

A

P Stop

Data

Byte M

Address

D3

Byte count

N

Data

--------

Data

Byte M+1

Data

Byte M

Data

Byte N

Byte count

N

Data

Byte M

Data

Byte M+1

Data

--------

Data

Byte M+N-1

Data

Byte 2

Data

--------

Byte count

N

Data

Byte 1

Address

D3

Byte count

N

Data

Byte 1

Data

Byte 2

Data

Byte M+1

Data

--------

Address

D3

Data

Byte M

Data

Byte M

Acknowledge to

host

Address

D3

Data

Byte M

Data

Byte M+1