PMC-1981271 (R4)

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC. AND FOR IT'S CUSTOMERS' INTERNAL USE

2001 PMC-Sierra, Inc.

PM5313

PMC-Sierra,Inc.

SONET/SDH Payload Extractor/Aligner for 622 Mbit/s Interfaces

SPECTRA-622

FEATURES

The SPECTRA-622 chip offers the

following features:

∑ Monolithic SONET/SDH

Payload-Extractor/Aligner for use in

STS-12 (STM-4/AU3 or STM-4/AU4) or

STM-12c (STM-4/AU4-4c) interface

applications that operate at serial

interface speeds up to 622.08 Mbit/s.

∑ Provides integrated clock recovery and

clock synthesis to allow a direct interface

to optical modules.

∑ Complies with Bellcore GR-253-CORE

jitter tolerance and intrinsic jitter criteria.

∑ Provides control circuitry required to

comply with WAN clocking requirements

for wander, holdover, and long term

stability.

∑ Provides termination for SONET Section

and Line, and SDH Regenerator Section

and Multiplexer Section

transport-overhead. Also provides

termination for Path overhead of twelve

STS-1 (STM-0/AU3) paths, four STS-3/

3c (STM-1/AU3/AU4) paths, or a single

STS-12c (STM-4/AU4-4c) path.

∑ Maps twelve STS-1 (STM-0/AU3)

payloads, four STS-3/3c (STM-1/AU3/

AU4) payloads, or a single STS-12c

(STM-4/AU4-4c) payload to system

timing references. This accommodates

plesiochronous timing offsets between

the references.

∑ Maps twelve DS3 bit-streams into an

STS-12 (STM-4/AU3) frame.

∑ Configurable on an STS-1 basis to

support a mix of traffic from the DS-3 and

Telecom interfaces.

∑ Provides a Time-Slot Interchange (TSI)

function on the Telecom Add and Drop

buses for grooming twelve STS-1

(STM-0/AU3) paths or four STS-3/3c

(STM-1/AU3/AU4) paths.

∑ Supports line loopback and diagnostic

loopback.

∑ Supports OC-48 (STM-16) applications

with byte interfaces for connection to

an OC-48 front-end device.

∑ Supports diagnostic 2

23

-1

pseudo-random bit-sequence (PRBS)

generation and monitoring.

∑ Provides a standard JTAG test-port for

boundary scan board-test purposes.

∑ Provides a generic 8-bit

microprocessor bus-interface.

∑ Low-power 3.3V CMOS with TTL

compatible inputs and CMOS/TTL

digital outputs. PECL inputs and

outputs are 3.3V and 5V compatible.

∑ Available in a 520-pin SBGA package.

∑ Supports industrial temperature-range

(-40∞C to 85∞C) operation.

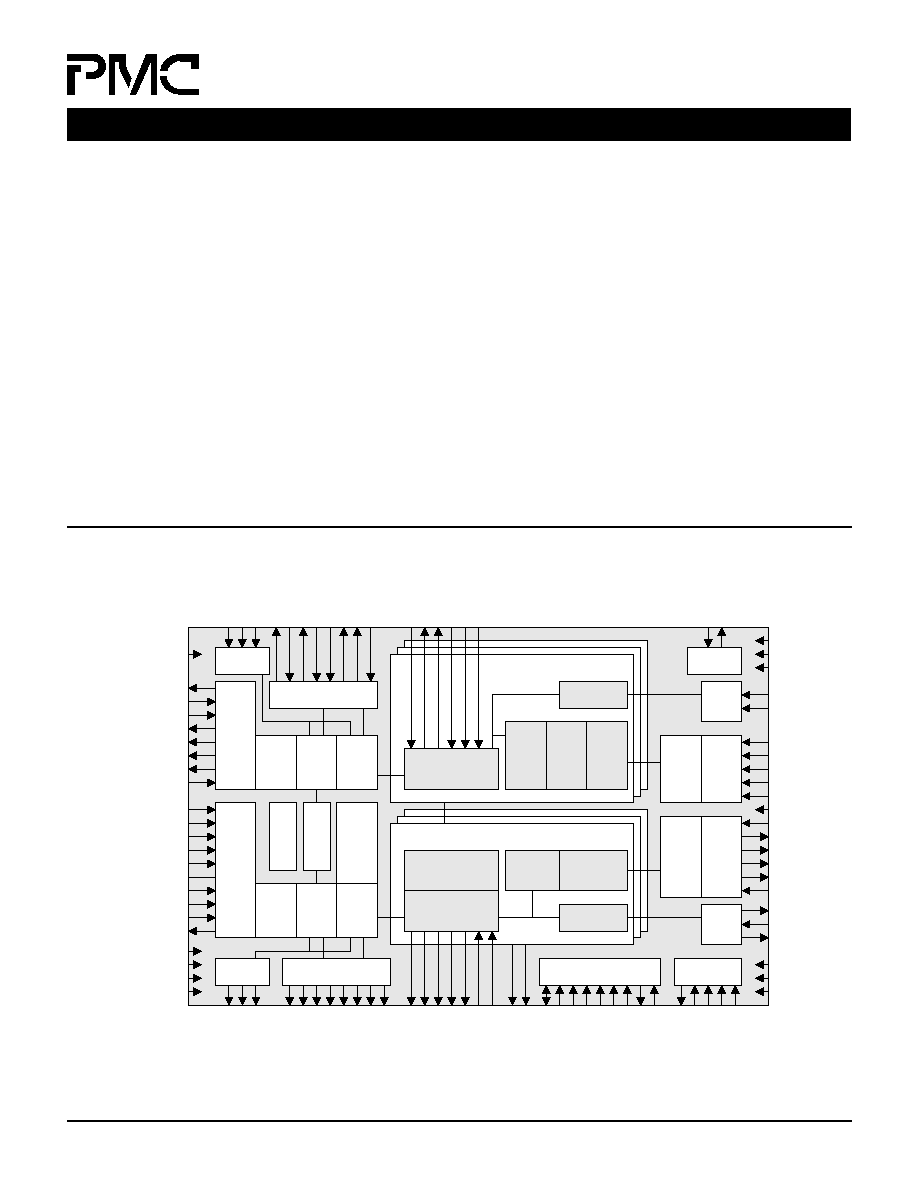

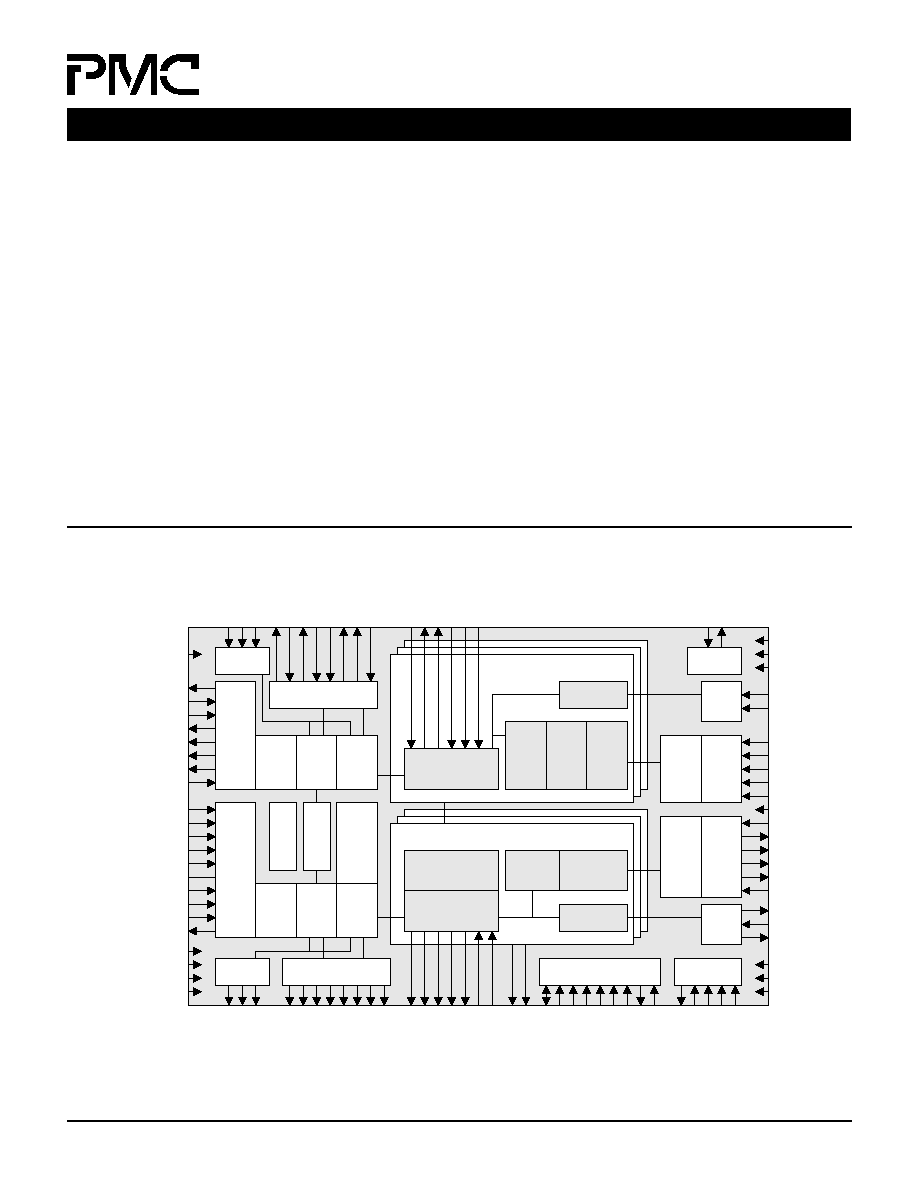

Drop Bus PRBS

Generator/

Monitor

Rx T

e

le

co

m

b

u

s

S

ystem Interface

Rx T

i

m

e

slo

t

Interchange

Rx Telecom

Aligner

Rx Path O/H

Processor

R

x

Li

ne O/H

P

r

ocessor

Rx Se

ctio

n

O/H

P

r

ocessor

Clo

ck

& Da

t

a

Recover

y

R

x

Li

ne Interface

Ad

d

Bu

s

PRBS

Generator/

Moni

tor

Tx

Tel

e

c

o

mbus

S

ystem

Interface

Tx

Ti

mes

l

ot

Interchange

T

x

P

o

inter

Interpreter

Tx

Tel

e

c

o

m

A

l

i

gner

Tx Li

ne O/H

P

r

ocessor

T

x

S

e

ction

O/H

P

r

ocessor

Clo

ck

S

y

nthesi

s

DS3 Mapper

Add Side

Tx Li

ne Interface

Tx Transport O/H

Controller

DS3 Mapper

Drop Side

Receive Path Processing Slice x12

Rx DS3

S

ystem

I/F

Rx

APS Sy

n

c

h

E

x

tractor &

B

i

t E

rror Moni

tor

Serial

Control Port

Microprocessor Interface

JTAG Test

Access Port

Rx Transport O/H

Controller

Path Trace Buffer

Tx Path O/H

Processor

Tx

D

S

3

S

ystem

I/F

Transmit Path Processing Slice x12

Rx Ring

Control Port

Tx Ring

Control Port

S

e

cti

on Trace

B

u

ffer

WAN Syn

c

Co

n

t

r

o

lle

r

TDP

RRCLK+/-

RXD+/-

REFCLK+/-

PECLV

TD[7:0]

TFPI

TPL

TC1J1V1/TFPO

TDCK

TDREF/ TDREF1

TXD+/-

SD

C0, C1

PICLK

PIN[7:0]

FPIN

OOF

ATP[1:0]

PREFEN

PECLREF

DS3TICLK [12:1]

AC1J1V1[4:1]/

AFP[4:1]

APL[4:1]

AD[31:0]

ADP[4:1]

DCK

DC1J1V1[4:1]

DPL[4:1]

DD[31:0]

DDP[4:1]

DFP

DS3TDAT [12:1]

DS3RDAT [12:1]

DS3ROCLK [12:1]

DS3RICLK

ACK

L

O

S/RRCPF

P

D

[

7:0]

RAD

B3

E

RT

COH

RT

CEN

RAL

M

RPOHEN

RPOHCL

K

RPOHF

P

RPOH

RT

OHCL

K

RT

OHF

P

RT

OH

RL

DCL

K, ROHCL

K

RSL

D

, RSOW, RSUC

RSL

DCL

K, ROWCL

K

L

O

F

,

SAL

M

L

RDI/RRCPCL

K

L

A

IS/RRCPDAT

TMS

TC

K

TD

I

TD

O

M

BEB

INT

B

RST

B

RDB/E

WRB,

RWB

CSB

AL

E

A

[

13:0]

TR

S

T

B

RL

D, RL

OW, ROH

TTO

H

E

N

TTO

H

C

L

K

TTO

H

F

P

TTO

H

/

TTO

H

R

E

I

TS

LD

/

T

S

O

W

/

TS

U

C

TS

LD

C

L

K

/

TO

W

C

LK

T

L

AIS/T

RCPDAT

RL

AIS/T

RCPCL

K

T

L

RDI/T

RCPF

P

TP

O

H

T

P

OHRDY

TA

D

/

TA

FP

/

T

A

C

K

TP

O

H

E

N

T

P

OHCL

K

TP

O

H

FP

T

L

D/T

L

OW

/T

OH

TLD

C

L

K

/

TO

W

C

LK

TCLK/PGMTCLK

/TFP

RCLK/PGMRCLK

/RFP

DPAIS

DMODE[1:0]

DPAISFP

DPAISCK

TPAIS

TPAISFP

TPAISCK

S

C

P

I[3:0]

S

C

P

O[1:0]

BLOCK

DIAGRAM

Head Office:

PMC-Sierra, Inc.

8555 Baxter Place

Burnaby, B.C. V5A 4V7

Canada

Tel: 604.415.6000

Fax: 604.415.6200

PM5313 SPECTRA-622

SONET/SDH Payload Extractor/Aligner for 622 Mbit/s Interfaces

To order documentation,

send email to:

document@pmc-sierra.com

or contact the head office,

Attn: Document Coordinator

All product documentation is available

on our web site at:

http://www.pmc-sierra.com

For corporate information,

send email to:

info@pmc-sierra.com

PMC-1981271 (R4)

2001 PMC-Sierra, Inc.

FREEDM-8 is a trademark of

PMC-Sierra, Inc.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC. AND FOR IT'S CUSTOMERS' INTERNAL USE

BACKPLANE/DEVICE MODES

∑ 77.76 MHz Telecom Byte

∑ 19.44 MHz Telecom Byte x 4

∑ Datacom DS-3 x 12

APPLICATIONS

Use the SPECTRA-622 chip in the

following applications:

∑ SONET/SDH Add/Drop Multiplexers

∑ SONET/SDH Terminal Multiplexers

∑ SONET/SDH Digital Cross-Connects

∑ Channelized Routers and Switches

TYPICAL APPLICATIONS

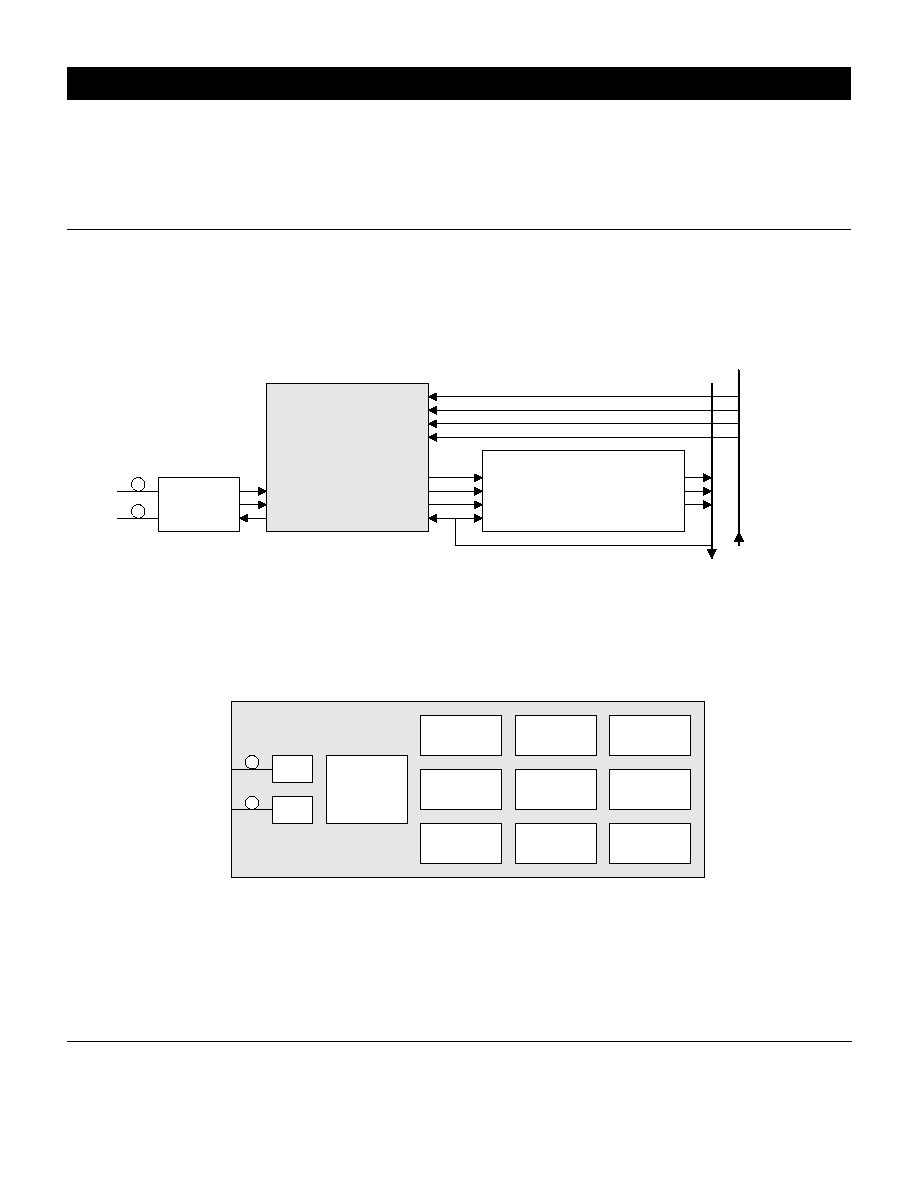

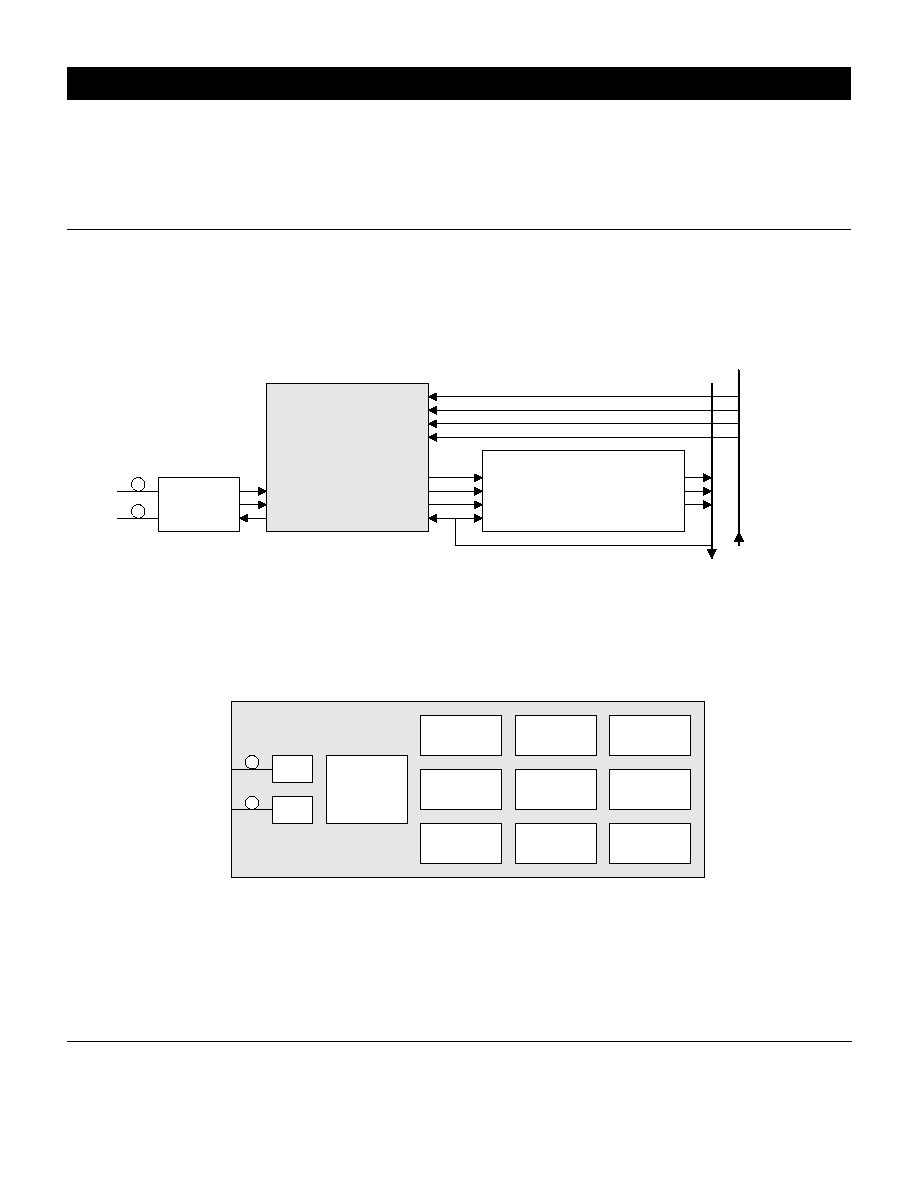

STS-12/STM-4 AGGREGATE INTERFACE WITH TRIBUTARY POINTER PROCESSING AND PERFORMANCE

MONITORING

CHANNELIZED OC-12 INTERFACE FOR HIGH SPEED ROUTERS

PM5363 TUPP+622

Optical

Transceiver

Drop

Add

622 Mbit/s

Optical Interface

77.76 MHz

8-Bit

High-Speed

Telecombus

Interface

RXD +/-

TXD +/-

SD

ACK

AD[7:0], ADP[1]

APL[1]

AC1J1V1[1]

DD[7:0], DDP[1]

DCK

DPL[1]

DC1J1V1[1]

ID[7:0], IDP[1]

IC1J1[1]

HSCLK

IPL[1]

OD[7:0], ODP[1]

OC1J1V1[1]

OPL[1]

PM5313

SPECTRA-622

FREEDM-8

FREEDM-8

FREEDM-8

FREEDM-8

FREEDM-8

FREEDM-8

S/UNI

QJET

S/UNI

QJET

S/UNI

QJET

SPECTRA-

622

Opt

Opt

Channelized

OC-12 Card

622 Mbit/s

Optical

Interface

Bus

Interface