PRODUCTION

PMC-Sierra, Inc.

PM5313 SPECTRA-622

DATASHEET

PMC-1981162

ISSUE 6

SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PMC-Sierra, Inc.

105 - 8555 Baxter Place Burnaby, BC Canada V5A 4V7 604 .415.6000

PM5313

SPECTRA-622

SONET/SDH PAYLOAD

EXTRACTOR/ALIGNER

FOR 622 MBIT/S

DATA SHEET

PROPRIETARY AND CONFIDENTIAL

PRODUCTION

ISSUE 6: SEPTEMBER 2000

PRODUCTION

PMC-Sierra, Inc.

PM5313 SPECTRA-622

DATASHEET

PMC-1981162

ISSUE 6

SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PROPRIETARY AND CONFIDENTIAL

i

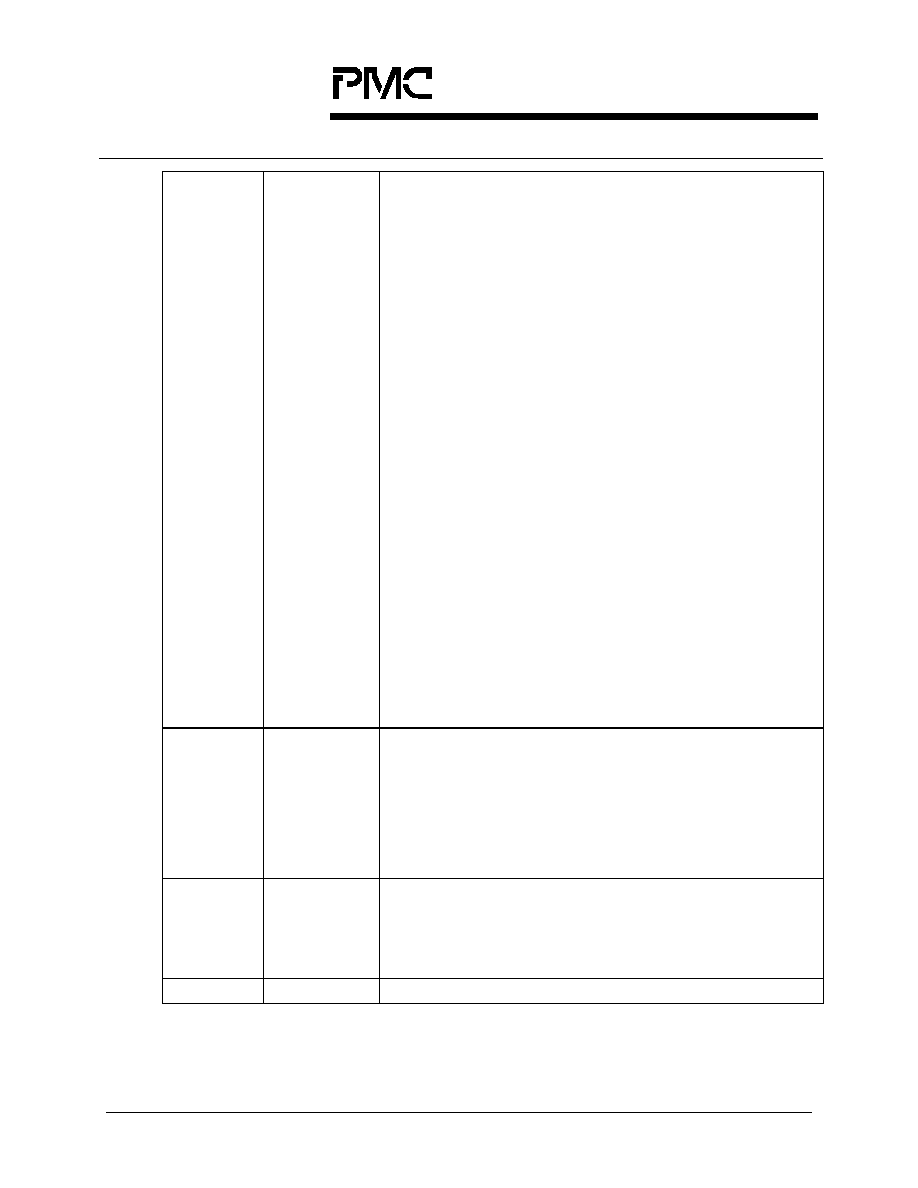

Issue No.

Issue Date

Details of Change

Issue 6

Sept 2000

�

Remove support of in-band G1 reporting on

DROP bus

�

Improve RAD Timing diagram (Fig 60)

�

Pointer justification not generated in PAIS on

DROP bus

�

Specify that the jitter tolerance is according to the

1995 Bellcore spec.

�

Remove the K1 and K2 bytes from the RAD.

�

Specify that a RESET_PATH command will also

clear the performing monitor counters of the

section/line TSBs.Update AC and DC

Characeristic sections according to its final

report..

�

V1 pulse is always outputted on the DROP bus

when the RTAL FIFO is bypassed

�

Add the RESET sequence to enable the TX line

interface and the OUTDATA bit in the CRSI.

�

Specify TFPO timing in serial mode

�

CRU and CSU will track REFCLK while in ROOL

�

Describe RX and TX bypass mode limitations

�

SDLE and RBYP mode can not be set at the

same time.

�

Fix number of bits before a DOOL is declared

from 80 to 96.

�

Bit 7 of register 0090H is now X vs 0.

�

Write to the PMON counter registers will also

trigger a count transfer.

�

SS bits are always 00 when the DPGM is in

autonomous mode.

�

Add

WANS

programming

section

�

Update the RAD and TFPI timing diagrams.

�

Update rev of CRU, GPGM and TTOC.

�

Update the methodology Tools table.

Issue 5

May 2000

�

Added STM1-CONCAT register bits in RPPS and

TPPS configuration.

�

Extend the timing for output pins RSUC, RSOW,

ROH and TDO.

PRODUCTION

PMC-Sierra, Inc.

PM5313 SPECTRA-622

DATASHEET

PMC-1981162

ISSUE 6

SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PROPRIETARY AND CONFIDENTIAL

ii

�

Remove support for the tandem connection

�

Removed RESBYP and TESBYPASS register bits

in RPPS and TPPS configuration. Bypass is no

longer programmable per slice but for all RPPS or

TPPS slices via the RESBYP and TESBYP bits

found in DROP and ADD BUS configuration

registers.

�

Fix RASE filtering spec to 8 frames

�

Correct DLL, APGM and DPGM register bits

description

�

Describe use of ATSI bit in APGM autonomous

mode.

�

Remove support of 12c when both autonomous

mode and DTMODE are use.

�

Specify that FOOF affect only one frame

�

Add

TS

TAD

DC spec.

�

Add power supply filtering and PECL I/O

diagrams

�

Revise RPOH timing diagrams

�

Add BYPASS Rx and TX mode description and

limitation. No support for TUAIS, tx dual mode

and pointer generation by STALs.

�

Specify that activity on the AC1J1V1, ADP and

APL pins can not be detected if ADP is tied high

or low.

Issue 4

�

Revised RPPS alarm bit names, register 0n1C

�

Revised National bit description in the TTOC

register 00C1

�

Revised signal mapping in register 0009

SPECTRA 622 Section Alarm Control #2

�

Added pin description of the Transmit Ring

Control Port

�

Fixed polarity for bit 7, register 0102

�

Added TPIP is held in reset in DS3 mode only

�

Revised TPAIS and DPAIS frame slots to correctly

correspond to slice order

�

Clarified precedence of TOH Overhead port over

TSOW, TSUC, and TLOW

�

Removed some DLL registers

PRODUCTION

PMC-Sierra, Inc.

PM5313 SPECTRA-622

DATASHEET

PMC-1981162

ISSUE 6

SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PROPRIETARY AND CONFIDENTIAL

iii

�

ADD DLL does not exist

�

Clarified description of SSTB/SPTB write trigger

register

�

Revised TTOH, TTOHEN set-up time

�

Clarified SENB bit description in register 0030

�

Clarified bit DC1 description in register 00B4

�

Clarified APGM/DPGM register information

�

Clarified register 1102 description

�

BIP calculation not supported by TPIP

�

Added REFCLK required when generating

DS3ROCLK internally

�

Added pin description for FPIN and TPL

�

Revised RASE description and register definitions

�

Revised bit 6 Path Reset description, register

0000

�

Clarified Protection Switch Byte Failures detection

description

�

Added updates based on preps

�

Remove STS-6c/9c support

�

Fix register bits definitions

�

Fix Tx Ring Control Port definiton

�

Remove B3 verification from ADD bus

�

Revised Recommended BERM settings

Issue 3

July 1999

�

Added FPPOS bit in register 0003

�

Added Register 0016

�

Added SCPII bit in register 000B

�

Uncovered EXT bit in register 1151

�

Added pin number

�

Added boundary scan chain information

Issue 2

April 1999

�

Removed

DS-3

framers

�

Block diagram updated

�

TTOC and RTOC registers added

�

Swapped RASE and SSTB register blocks

Issue 1

Sep 1998

Document created

PRODUCTION

PMC-Sierra, Inc.

PM5313 SPECTRA-622

DATASHEET

PMC-1981162

ISSUE 6

SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S

PROPRIETARY AND CONFIDENTIAL

iv

CONTENTS

1

FEATURES ..................................................................................... 1

1.1

GENERAL ............................................................................ 1

1.2

SONET SECTION AND LINE / SDH REGENERATOR

AND MULTIPLEXER SECTION ........................................... 2

1.3

SONET PATH / SDH HIGH ORDER PATH........................... 3

1.4

SYSTEM SIDE INTERFACES.............................................. 4

2

APPLICATIONS .............................................................................. 6

3

REFERENCES................................................................................ 7

4

DEFINITIONS ................................................................................. 8

5

APPLICATION EXAMPLES ............................................................ 9

6

BLOCK DIAGRAM ........................................................................ 14

7

LOOPBACK MODES .................................................................... 15

8

DESCRIPTION.............................................................................. 16

9

PIN DIAGRAMS ............................................................................ 18

10

PIN DESCRIPTION (520) ............................................................. 23

10.1 SERIAL LINE SIDE INTERFACE SIGNALS....................... 23

10.2 PARALLEL LINE SIDE INTERFACE SIGNALS.................. 26

10.3 RECEIVE AND TRANSMIT CLOCKS ................................ 31

10.4 SECTION/LINE STATUS AND ALARMS SIGNALS ........... 35

10.5 RECEIVE TRANSPORT OVERHEAD EXTRACTION

SIGNALS............................................................................ 42

10.6 TRANSMIT TRANSPORT OVERHEAD INSERTION

SIGNALS............................................................................ 49