168-pin Low Latency, Low Profile SDRAM DIMMs

Preliminary Data Sheet

128MB, 256MB

Enhanced Memory Systems Inc., 1850 Ramtron Dr., Colo Spgs, CO 80921

2001 Enhanced Memory Systems. All rights reserved.

PHONE: (800) 545-DRAM; FAX: (719) 488-9095;

http://www.edram.com

The information contained herein is subject to change without notice.

Revision 1.0

Page 1 of 14

Features

∑

JEDEC Standard 168-pin SDRAM DIMM

∑

Low Latency CAS2 PC133 MHz Modules (2:2:2)

∑

CAS Latency = 2

∑

RAS to CAS Delay = 2

∑

Precharge Delay = 2

∑

Low Profile for 1U Rack Mount Systems

∑

Fast 5.4 ns Clock Access Time

∑

Supports CAS Latency = 2, 3

∑

On-board Serial Presence Detect (SPD)

∑

Unbuffered 168-pin DIMM

∑

4K Refresh / 64 ms

∑

Single 3.3V

±

0.3V Power Supply

Description

The Enhanced Memory Systems 128MB and 256MB low

latency, low profile SDRAM DIMMs are the fastest

unbuffered SDRAM DIMMs available. Low latency (2:2:2)

improves overall performance. The low profile (1.15 inch)

form factor is ideal for 1U rack mount systems. The fast 5.4

ns clock access time allows unbuffered DIMM operation at

133 MHz for lower memory latency, and lower costs than

registered DIMMs.

The 128MB module is organized as 16Mx64, and the

256MB module is organized as 32Mx64. The 128MB and

256MB ECC modules are organized as 16Mx72 and

32Mx72. Each module contains a serial presence EEPROM

programmed by Enhanced Memory Systems, which contains

information on the module type, module organization,

component speed, and other attributes relevant to the system

controller.

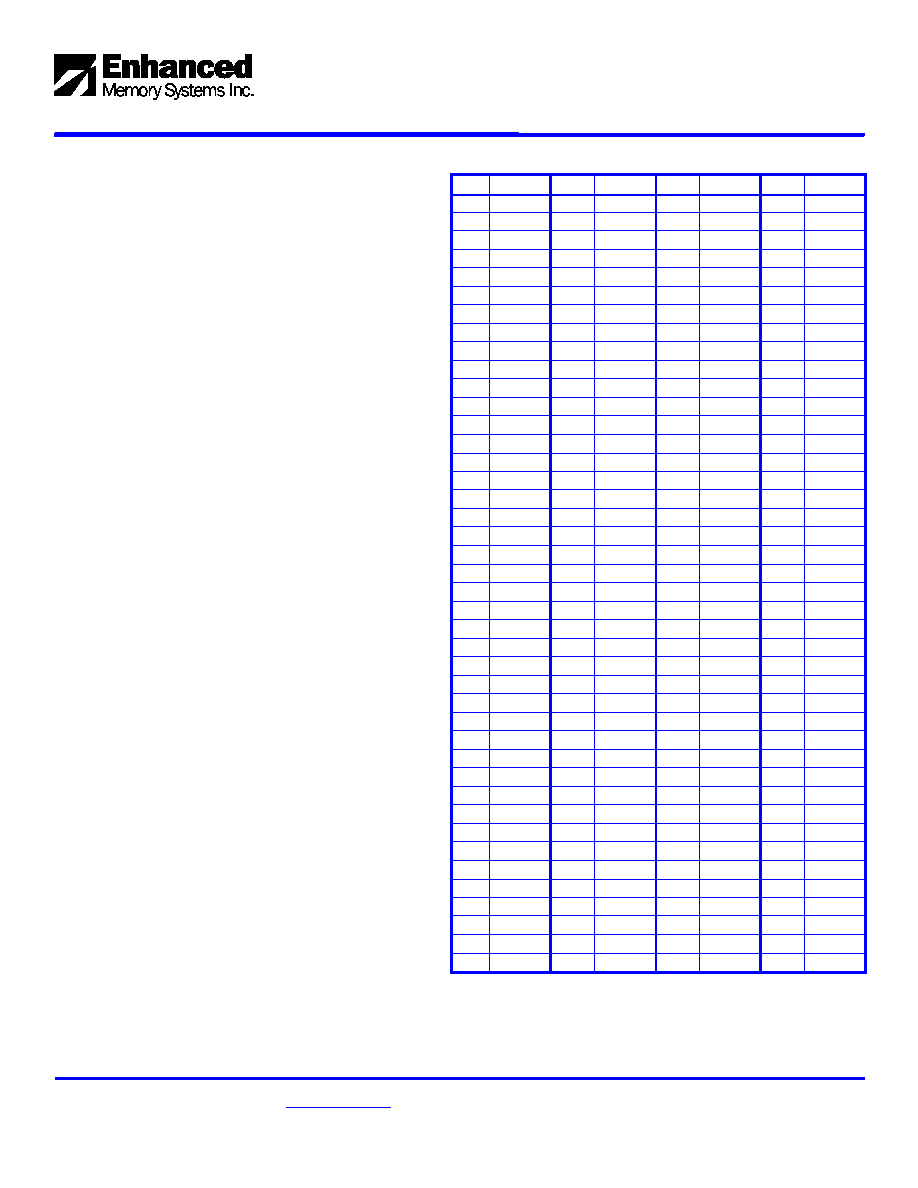

Pin Symbol Pin Symbol Pin Symbol Pin Symbol

1 Vss 43 Vss 85 Vss 127 Vss

2 DQ0 44 DNU 86 DQ32 128 CKE0

3 DQ1 45 S2# 87 DQ33

129 S3#

4 DQ2 46

DQMB2

88 DQ34

130

DQMB6

5 DQ3 47

DQMB3

89 DQ35

131

DQMB7

6 Vdd 48 DNU 90 Vdd 132 RFU

7 DQ4 49 Vdd 91 DQ36

133 Vdd

8 DQ5 50 NC 92 DQ37

134 NC

9 DQ6 51 NC 93 DQ38

135 NC

10 DQ7 52 CB2 94 DQ39 136 CB6

11 DQ8 53 CB3 95 DQ40 137 CB7

12 Vss 54 Vss 96 Vss 138 Vss

13 DQ9 55 DQ16 97 DQ41 139 DQ48

14 DQ10 56 DQ17 98 DQ42 140 DQ49

15 DQ11 57 DQ18 99 DQ43 141 DQ50

16 DQ12 58 DQ19 100 DQ44 142 DQ51

17 DQ13 59 Vdd 101 DQ45 143 Vdd

18 Vdd 60 DQ20 102 Vdd 144

DQ52

19 DQ14 61 NC 103 DQ46 145 NC

20 DQ15 62 NC 104 DQ47 146 NC

21 CB0 63 CKE1 105 CB4 147 NC

22 CB1 64 Vss 106 CB5 148 Vss

23 Vss 65 DQ21

107 Vss 149

DQ53

24 NC 66 DQ22

108 NC 150

DQ54

25 NC 67 DQ23

109 NC 151

DQ55

26 Vdd 68 Vss 110 Vdd 152 Vss

27 WE# 69 DQ24 111 CAS# 153 DQ56

28 DQMB0 70 DQ25 112 DQMB4 154 DQ57

29 DQMB1 71 DQ26 113 DQMB5 155 DQ58

30 S0# 72 DQ27 114 S1# 156

DQ59

31 DNU 73 Vdd 115 RAS# 157 Vdd

32 Vss 74 DQ28

116 Vss 158

DQ60

33 A0 75 DQ29

117 A1 159

DQ61

34 A2 76 DQ30

118 A3 160

DQ62

35 A4 77 DQ31

119 A5 161

DQ63

36 A6 78 Vss 120 A7 162 Vss

37 A8 79 CK2 121 A9 163 CK3

38 A10/AP 80

NC

122 BA0 164

NC

39 BA1 81 WP 123 A11 165 SA0

40 Vdd 82 SDA 124 Vdd 166 SA1

41 Vdd 83 SCL 125 CK1 167 SA2

42 CK0 84 Vdd 126 RFU 168 Vdd

168-pin Low Latency, Low Profile SDRAM DIMMs

128MB, 256MB

Preliminary Data Sheet

Enhanced Memory Systems Inc., 1850 Ramtron Dr., Colo Spgs, CO 80921

2001 Enhanced Memory Systems. All rights reserved.

PHONE: (800) 545-DRAM; FAX: (719) 488-9095;

http://www.edram.com

The information contained herein is subject to change without notice.

Page 2 of 14

Revision 1.0

Pin Descriptions

Symbol Type

Function

CK(0:3) Input

Clocks: All SDRAM input signals are sampled on the positive edge of CK.

CKE(0:1) Input

Clock Enables: CKE activate (high) or deactivate (low) the CK signals. Deactivating the clock initiates the

Power-Down and Self-Refresh operations (all banks idle), or Clock Suspend operation. CKE is synchronous until

the device enters Power-Down and Self-Refresh modes where it is asynchronous until the mode is exited.

S(0:3)# Input

Chip Select: S# enables (low) or disables (high) the command decoder. When the command decoder is

disabled, new commands are ignored but previous operations continue.

RAS#, CAS#,

WE#

Input

Command Inputs: Sampled on the rising edge of CK, these inputs define the command to be executed.

BA(0:1)

Input

Bank Addresses: These inputs define to which of the 4 banks a given command is being applied.

A(0:11) Input

Address Inputs: A0-A11 define the row address during the Bank Activate command. A0-A8 define the column

address during Read and Write commands. A10/AP invokes the Auto-precharge operation. During manual

Precharge commands, A10/AP low specifies a single bank precharge while A10/AP high precharges all banks.

The address inputs are also used to program the Mode Register.

DQ(0:63)

Input/

Output

Data I/O: Data bus inputs and outputs. For Write cycles, input data is applied to these pins and must be set-up

and held relative to the rising edge of clock. For Read cycles, the device drives output data on these pins after

the CAS latency is satisfied.

DQMB(0-7) Input

Data I/O Mask Inputs: DQMB0-7 inputs mask write data (zero latency) and acts as a synchronous output enable

(2-cycle latency) for read data.

CB(0:7)

Input/

Output

ECC Check Bits

V

DD

Supply

Power Supply: +3.3 V

V

SS

Supply

Ground

SDA

Input/

Output

Serial Presence-Detect Data: SDA is a bi-directional pin used to transfer addresses and data into

and data out of the presence-detect portion of the module.

SCL Input

Serial Clock for Presence-Detect: SCL is used to synchronize the presence detect data transfer to

and from the module

SA(0-2)

Input

Presence-Detect Address Inputs: These pins are used to configure the presence detect device.

WP Input

Serial Presence Detect Write Protect: Active high inhibits writes to the SPD EEPROM. WP must be driven low

for normal read/write operations.

RFU

-

Reserved for Future Use: These pins should be left unconnected.

DNU

-

Do not use.

NC

-

No connect - open pin.

168-pin Low Latency, Low Profile SDRAM DIMMs

Preliminary Data Sheet

128MB, 256MB

Enhanced Memory Systems Inc., 1850 Ramtron Dr., Colo Spgs, CO 80921

2001 Enhanced Memory Systems. All rights reserved.

PHONE: (800) 545-DRAM; FAX: (719) 488-9095;

http://www.edram.com

The information contained herein is subject to change without notice.

Revision 1.0

Page 3 of 14

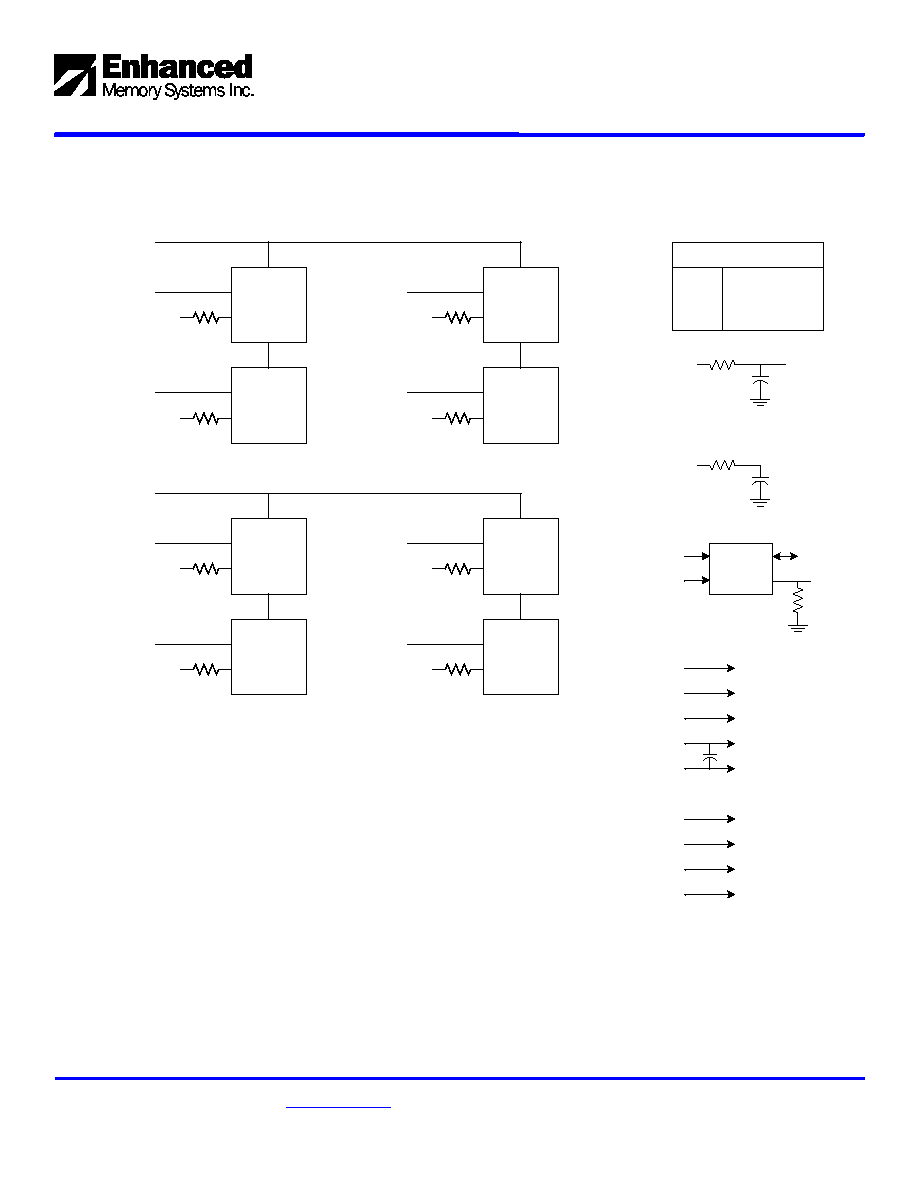

128MB DIMM Functional Block Diagram ≠ SM12808ALDT

U0

U1

DQ(7:0)

DQMB0

S0#

DQ(15:8)

DQMB1

U2

U3

DQ(23:16)

DQMB2

S2#

DQ(31:24)

DQMB3

U4

U5

DQ(39:32)

DQMB4

DQ(47:40)

DQMB5

U6

U7

DQ(55:48)

DQMB6

DQ(63:56)

DQMB7

Clock Wiring

4 SDRAM+3.3 pf

Termination

4 SDRAM+3.3 pf

Termination

CK0

CK1

CK2

CK3

10

CK0,2

SDRAMs

Clock Termination

10

CK1,3

Serial PD

SCL

SA0-2

SDA

10 pf

47K

WP

BA1 SDRAM U0-7

BA1

BA0 SDRAM U0-7

BA0

RAS# SDRAM U0-7

RAS#

A0-A11 SDRAM U0-7

A0-A11

Vdd SDRAM U0-7

Vdd

Vss SDRAM U0-7

Vss

CAS# SDRAM U0-7

CAS#

WE# SDRAM U0-7

WE#

CKE SDRAM U0-7

CKE0

Note:

All DQ resistor values are 10 ohms.

All CK resistor values are 10 ohms.

U0-U7 are HYB39S128800CT-7.

168-pin Low Latency, Low Profile SDRAM DIMMs

128MB, 256MB

Preliminary Data Sheet

Enhanced Memory Systems Inc., 1850 Ramtron Dr., Colo Spgs, CO 80921

2001 Enhanced Memory Systems. All rights reserved.

PHONE: (800) 545-DRAM; FAX: (719) 488-9095;

http://www.edram.com

The information contained herein is subject to change without notice.

Page 4 of 14

Revision 1.0

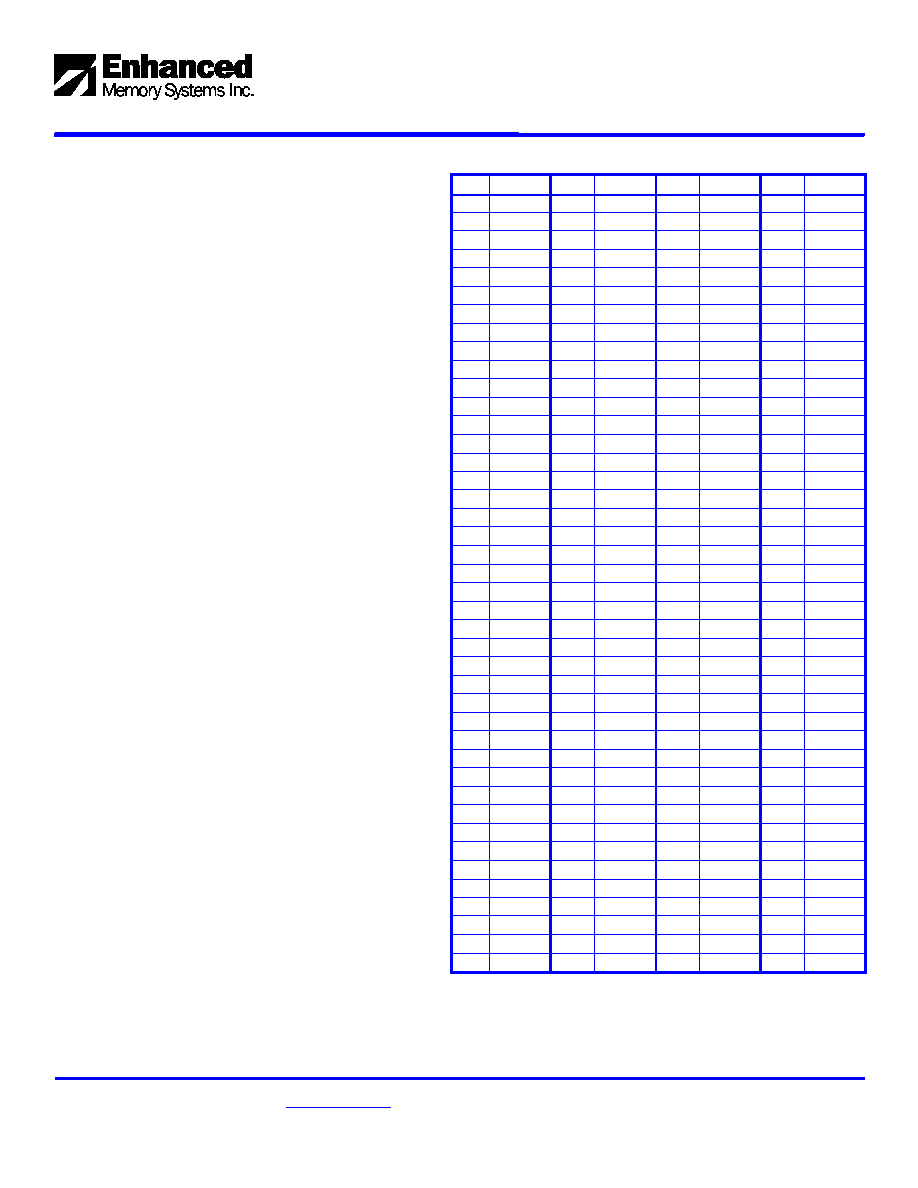

128MB ECC DIMM Functional Block Diagram ≠ SM12809ALDT

U0

U1

DQ(7:0)

DQMB0

S0#

DQ(15:8)

DQMB1

U3

U4

DQ(23:16)

DQMB2

S2#

DQ(31:24)

DQMB3

U5

U6

DQ(39:32)

DQMB4

DQ(47:40)

DQMB5

U7

U8

DQ(55:48)

DQMB6

DQ(63:56)

DQMB7

U2

CB(7:0)

Clock Wiring

5 SDRAM

Termination

4 SDRAM+3.3 pf

Termination

CK0

CK1

CK2

CK3

10

CK0,2

SDRAMs

Clock Termination

10

CK1,3

Serial PD

SCL

SA0-2

SDA

10 pf

47K

WP

BA1 SDRAM U0-8

BA1

BA0 SDRAM U0-8

BA0

RAS# SDRAM U0-8

RAS#

A0-A11 SDRAM U0-8

A0-A11

Vdd SDRAM U0-8

Vdd

Vss SDRAM U0-8

Vss

CAS# SDRAM U0-8

CAS#

WE# SDRAM U0-8

WE#

CKE SDRAM U0-8

CKE0

Note:

All DQ resistor values are 10 ohms.

All CK resistor values are 10 ohms.

U0-U8 are HYB39S128800CT-7.

168-pin Low Latency, Low Profile SDRAM DIMMs

Preliminary Data Sheet

128MB, 256MB

Enhanced Memory Systems Inc., 1850 Ramtron Dr., Colo Spgs, CO 80921

2001 Enhanced Memory Systems. All rights reserved.

PHONE: (800) 545-DRAM; FAX: (719) 488-9095;

http://www.edram.com

The information contained herein is subject to change without notice.

Revision 1.0

Page 5 of 14

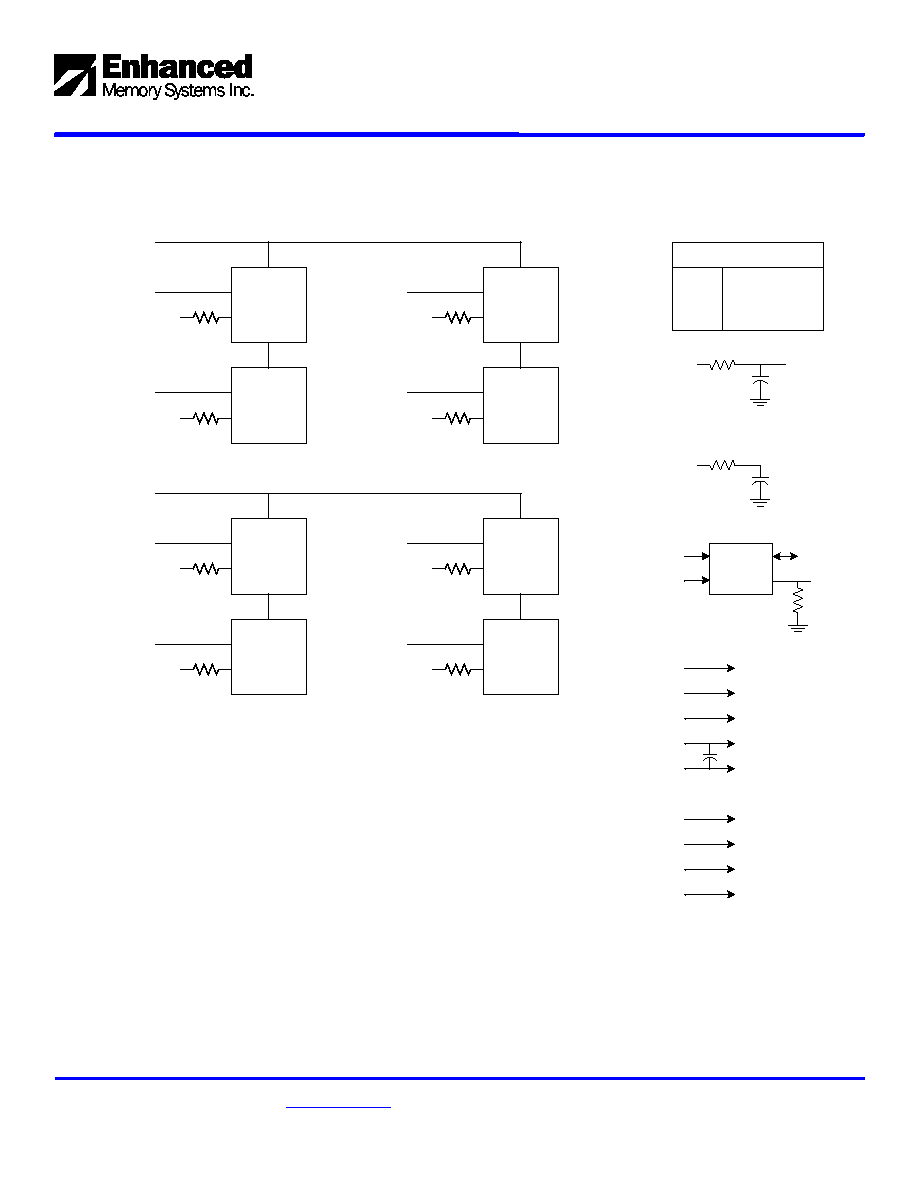

256MB DIMM Functional Block Diagram ≠ SM25608ALDT

DQ(7:0)

DQMB0

S0#

DQ(15:8)

DQMB1

DQ(23:16)

DQMB2

S2#

DQ(31:24)

DQMB3

DQ(39:32)

DQMB4

DQ(47:40)

DQMB5

DQ(55:48)

DQMB6

DQ(63:56)

DQMB7

U0

U1

U8

U9

U4

U12

U5

U13

U2

U10

U6

U3

U11

U14

U7

U15

S1#

S3#

SCL

SA0-2

BA1 SDRAM U0-15

BA1

BA0 SDRAM U0-15

BA0

RAS# SDRAM U0-15

RAS#

A0-A11 SDRAM U0-15

A0-A11

Vdd SDRAM U0-15

Vdd

Vss SDRAM U0-15

Vss

CAS# SDRAM U0-15

CAS#

WE# SDRAM U0-15

WE#

CKE SDRAM U0-7

CKE0

Clock Wiring

4 SDRAM+3.3 pf

4 SDRAM+3.3 pf

4 SDRAM+3.3 pf

4 SDRAM+3.3 pf

CK0

CK1

CK2

CK3

10

CK0-3

SDRAMs

Serial PD

SDA

47K

WP

Note:

All DQ resistor values are 10 ohms.

All CK resistor values are 10 ohms.

U0-U15 are HYB39S128800CT-7.

CKE SDRAM U8-15

CKE1