RTL8100B(L)

2001-11-9

Rev.1.41

1

REALTEK SINGLE CHIP

FAST ETHERNET CONTROLLER

WITH POWER MANAGEMENT

RTL8100B(L)

1. Features........................................................................ 2

2. General Description .................................................... 3

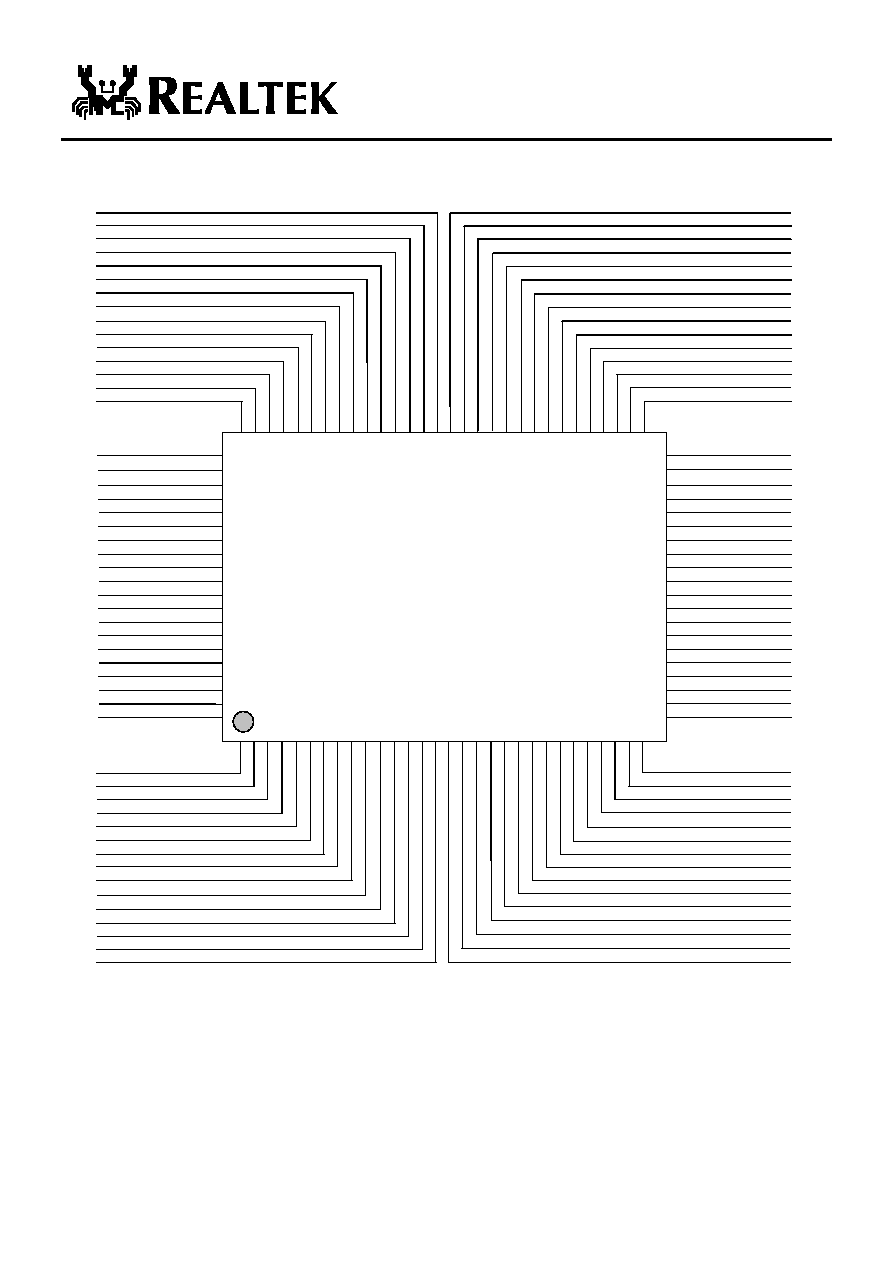

3. Pin Assignments .......................................................... 4

4. Pin Description ............................................................ 6

4.1 Power Management/Isolation Interface.................. 6

4.2 PCI Interface .......................................................... 6

4.3 EPROM/EEPROM Interface.................................. 8

4.4 Power Pins.............................................................. 8

4.5 LED Interface......................................................... 8

4.6 Attachment Unit Interface ...................................... 9

4.7 Test and Other Pins ................................................ 9

5. Register Descriptions ................................................ 10

5.1 Receive Status Register in Rx packet header ....... 12

5.2 Transmit Status Register....................................... 13

5.3 ERSR: Early Rx Status Register........................... 14

5.4 Command Register ............................................... 14

5.5 Interrupt Mask Register........................................ 15

5.6 Interrupt Status Register....................................... 15

5.7 Transmit Configuration Register.......................... 16

5.8 Receive Configuration Register ........................... 17

5.9 9346CR: 93C46 Command Register .................... 19

5.10 CONFIG 0: Configuration Register 0 ................ 20

5.11 CONFIG 1: Configuration Register 1 ................ 20

5.12 Media Status Register......................................... 21

5.13 CONFIG 3: Configuration Register3 ................. 22

5.14 CONFIG 4: Configuration Register4 ................. 23

5.15 Multiple Interrupt Select Register ...................... 24

5.16 PCI Revision ID ................................................. 24

5.17 Transmit Status of All Descriptors (TSAD) Register .. 25

5.18 Basic Mode Control Register ............................. 25

5.19 Basic Mode Status Register................................ 26

5.20 Auto-Negotiation Advertisement Register ......... 27

5.21 Auto-Negotiation Link Partner Ability Register 28

5.22 Auto-Negotiation Expansion Register................ 28

5.23 Disconnect Counter ............................................ 29

5.24 False Carrier Sense Counter ............................... 29

5.25 NWay Test Register ........................................... 29

5.26 RX_ER Counter ................................................. 29

5.27 CS Configuration Register ................................. 30

5.28 Config5: Configuration Register 5 ..................... 31

6. EEPROM (93C46) Contents .....................................32

6.1 Summary of the RTL8100B(L) EEPROM Registers...34

6.2 Summary of EEPROM Power Management Registers .34

7. PCI Configuration Space Registers..........................35

7.1 PCI Configuration Space Table ............................35

7.2 PCI Configuration Space Functions......................37

7.3 Default Values after Power-on (RSTB asserted) ..40

7.4 PCI Power Management Functions.......................41

7.5 VPD (Vital Product Data).....................................43

8. Block Diagram ...........................................................44

9. Functional Description ..............................................45

9.1 Transmit operation ................................................45

9.2 Receive operation..................................................45

9.3 Wander Compensation..........................................45

9.4 Signal Detect.........................................................45

9.5 Line Quality Monitor ............................................45

9.6 Clock Recovery Module .......................................45

9.7 Loopback Operation..............................................45

9.8 Tx Encapsulation ..................................................46

9.9 Collision................................................................46

9.10 Rx Decapsulation ................................................46

9.11 Flow Control .......................................................46

9.11.1. Control Frame Transmission .......................46

9.11.2. Control Frame Reception ............................46

9.12 LED Functions....................................................47

9.12.1 10/100 Mbps Link Monitor..........................47

9.12.2 LED_RX ......................................................47

9.12.3 LED_TX.......................................................47

9.12.4 LED_TX+LED_RX .....................................48

10. Application Diagram ...............................................48

11. Electrical Characteristics ........................................49

11.1 Temperature Limit Ratings .................................49

11.2 DC Characteristics ..............................................49

11.2.1 Supply voltage..............................................49

11.2.2 Supply voltage..............................................49

11.3 AC Characteristics ..............................................50

11.3.1 PCI Bus Operation Timing...........................50

12. Mechanical Dimensions...........................................56

12.1 QFP .....................................................................56

12.2 LQFP...................................................................57

RTL8100B(L)

2001-11-9

Rev.1.41

2

1. Features

100 pin QFP/LQFP

Integrated Fast Ethernet MAC, Physical chip and

transceiver in one chip

10 Mb/s and 100 Mb/s operation

Supports 10 Mb/s and 100 Mb/s N-way

Auto-negotiation operation

PCI local bus single-chip Fast Ethernet controller

Compliant to PCI Revision 2.2

Supports PCI clock 16.75MHz-40MHz

Supports PCI target fast back-to-back transaction

Provides PCI bus master data transfers and PCI

memory space or I/O space mapped data transfers

of RTL8100B(L)'s operational registers

Supports PCI VPD (Vital Product Data)

Supports ACPI, PCI power management

Supports 25MHz crystal or 25MHz OSC as the internal

clock source. The frequency deviation of either crystal or

OSC must be within 50 PPM.

Compliant to PC99/PC2001 standard

Supports Wake-On-LAN function and remote wake-up

(Magic Packet*, LinkChg and Microsoft

�

wake-up frame)

Supports 4 Wake-On-LAN (WOL) signals (active high,

active low, positive pulse, and negative pulse)

Supports auxiliary power-on internal reset, to be ready

for remote wake-up when main power still remains off

Supports auxiliary power auto-detect, and sets the

related capability of power management registers in PCI

configuration space.

Includes a programmable, PCI burst size and early

Tx/Rx threshold.

Supports a 32-bit general-purpose timer with the

external PCI clock as clock source, to generate

timer-interrupt

Contains two large (2Kbyte) independent receive and

transmit FIFOs

Advanced power saving mode when LAN function or

wakeup function is not used

Uses 93C46 (64*16-bit EEPROM) to store resource

configuration, ID parameter, and VPD data.

Supports LED pins for various network activity

indications

Supports loopback capability

Half/Full duplex capability

Supports Full Duplex Flow Control (IEEE 802.3x)

2.5/3.3V power supply with 5V tolerant I/Os.

0.25u CMOS process

* Third-party brands and names are the property of their

respective owners.

Note: The model number of the QFP package is RTL8100B. The LQFP package model number is RTL8100BL.

RTL8100B(L)

2001-11-9

Rev.1.41

3

2. General Description

The Realtek RTL8100B(L) is a highly integrated, cost-effective single-chip Fast Ethernet controller that provides 32-bit

performance, PCI bus master capability, and full compliance with IEEE 802.3u 100Base-T specifications and IEEE 802.3x Full

Duplex Flow Control. It also supports the Advanced Configuration Power management Interface (ACPI), PCI power management

for modern operating systems that are capable of Operating System Directed Power Management (OSPM) to achieve the most

efficient power management possible. The RTL8100B(L) does not support CardBus mode as the RTL8139C does.

In addition to the ACPI feature, the RTL8100B(L) also supports remote wake-up (including AMD Magic Packet, LinkChg, and

Microsoft

�

wake-up frame) in both ACPI and APM environments. The RTL8100B(L) is capable of performing an internal reset

through the application of auxiliary power. When auxiliary power is applied and the main power remains off, the RTL8100B(L)

is ready and waiting for the Magic Packet or Link Change to wake the system up. Also, the LWAKE pin provides 4 different

output signals including active high, active low, positive pulse, and negative pulse. The versatility of the RTL8100B(L) LWAKE

pin provides motherboards with Wake-On-LAN (WOL) functionality.

The RTL8100B(L) also supports Analog Auto-Power-down, that is, the analog part of the RTL8100B(L) can be shut down

temporarily according to user requirements or when the RTL8100B(L) is in a power down state with the wakeup function

disabled. In addition, when the analog part is shut down and the IsolateB pin is low (i.e. the main power is off), then both the

analog and digital parts stop functioning and the power consumption of the RTL8100B(L) will be negligible. The RTL8100B(L)

also supports an auxiliary power auto-detect function, and will auto-configure related bits of their own PCI power management

registers in PCI configuration space.

The PCI Vital Product Data(VPD) is also supported to provide the information that uniquely identifies hardware (i.e., the OEM

brand name of RTL8100B(L) LAN card). The information may consist of part number, serial number, and other detailed

information.

To provide cost down support, the RTL8100B(L) is capable of using a 25MHz crystal or OSC as its internal clock source.

The RTL8100B(L) keeps network maintenance costs low and eliminates usage barriers. It is the easiest way to upgrade a

network from 10 to 100Mbps. It also supports full-duplex operation, making 200Mbps bandwidth possible at no additional cost.

To improve compatibility with other brands' products, the RTL8100B(L) is also capable of receiving packets with

InterFrameGap no less than 40 Bit-Time. The RTL8100B(L) is highly integrated and requires no "glue" logic or external

memory.