DESCRIPTION

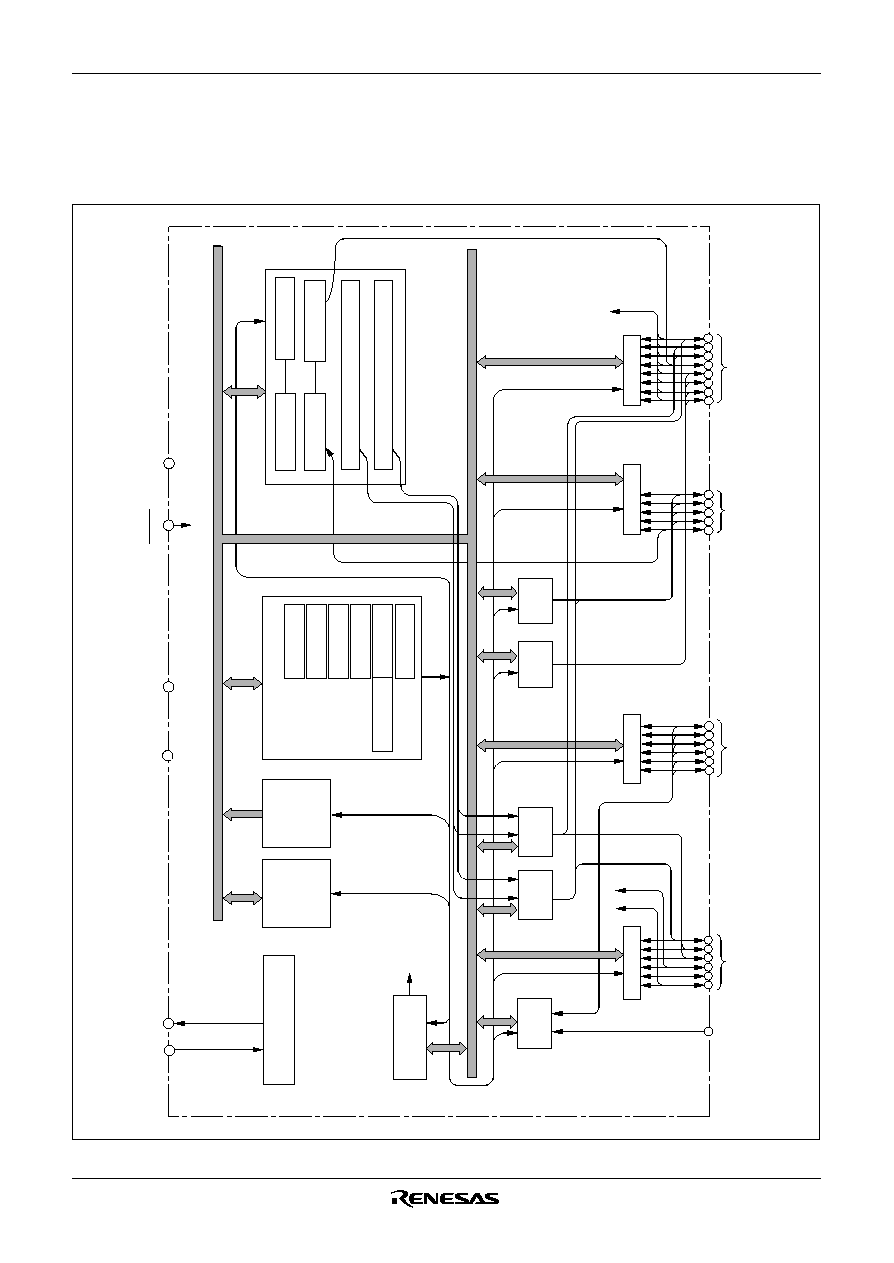

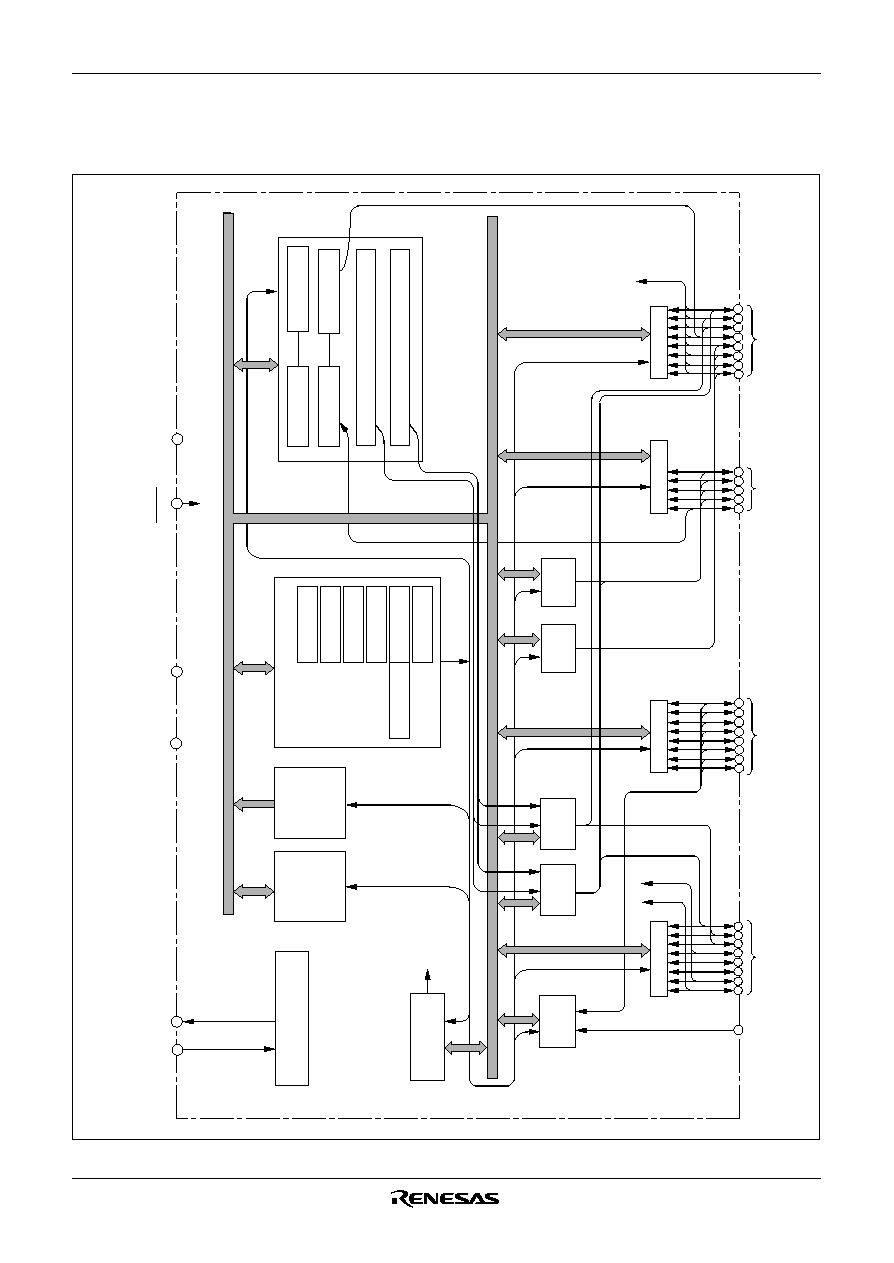

The 7542 Group is the 8-bit microcomputer based on the 740 fam-

ily core technology.

The 7542 Group has serial I/Os, 8-bit timers, 16-bit timers, and an

A-D converter, and is useful for control of home electric appliances

and office automation equipment.

FEATURES

∑

Basic machine-language instructions ...................................... 71

∑

The minimum instruction execution time ..

0.25

µ

µ

µ

µ

µ

s (Target Spec.)

(at 8 MHz oscillation frequency, double-speed mode for the

shortest instruction)

∑

Memory size

Flash memory version: ROM .............................. 32K + 4K bytes

RAM ..................................... 1024 bytes

Mask ROM version:

ROM ............................. 8K to 16K bytes

RAM ............................ 384 to 512 bytes

RSS version

RAM ..................................... 1024 bytes

∑

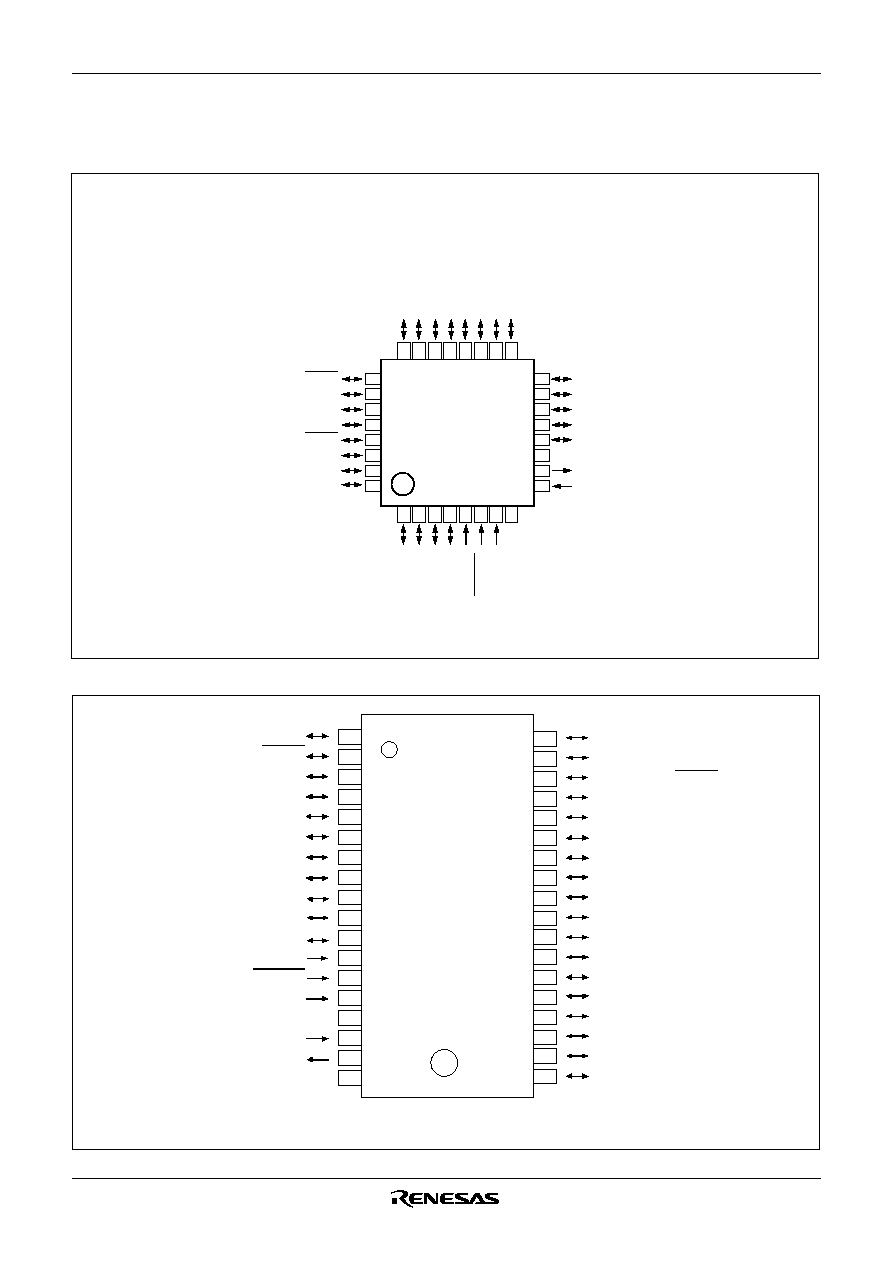

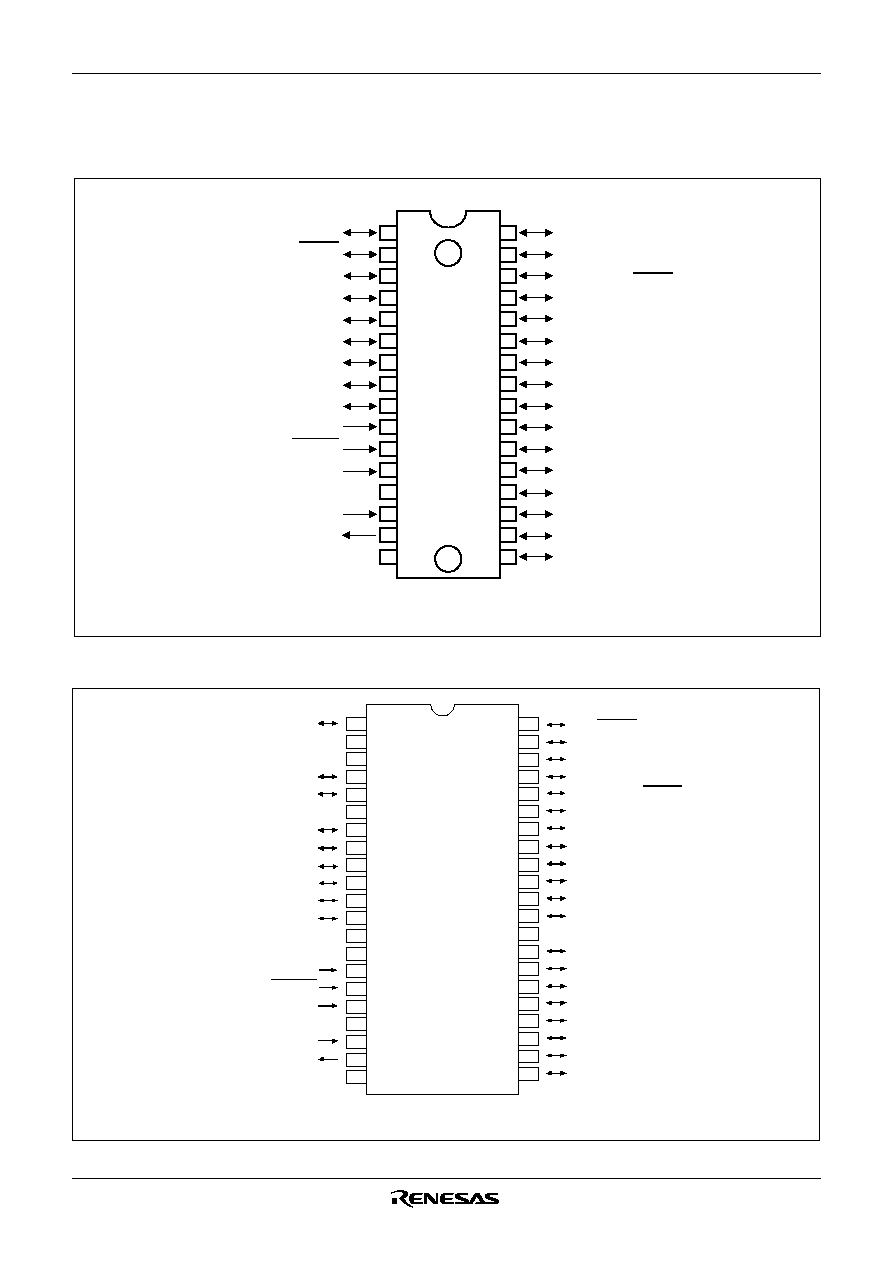

Programmable I/O ports ....................... 29 (25 in 32-pin version)

∑

Interrupts ................................................. 18 sources, 16 vectors

(14 sources, 14 vectors in 32-pin version)

∑

Timers ............................................................................. 8-bit

2

...................................................................................... 16-bit

2

∑ Output compare ............................................................ 4-channel

∑ Input capture ................................................................ 2-channel

∑

Serial I/O ...................... 8-bit

2 (UART or Clock-synchronized)

∑

A-D converter ............................................... 10-bit

8 channels

...................................................... (6 channels in 32-pin version)

∑

Clock generating circuit ............................................. Built-in type

(low-power dissipation by a ring oscillator)

(connected to external ceramic resonator or quartz-crystal

oscillator permitting RC oscillation)

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

∑

Watchdog timer ............................................................ 16-bit

1

∑

Power source voltage

X

IN

oscillation frequency at ceramic oscillation, in double-speed mode

At 8 MHz ................................................................................

TBD

X

IN

oscillation frequency at ceramic oscillation, in high-speed mode

At 8 MHz .................................................................... 4.0 to 5.5 V

At 4 MHz .................................................................... 2.4 to 5.5 V

At 2 MHz .................................................................... 2.2 to 5.5 V

X

IN

oscillation frequency at RC oscillation in high-speed mode or

middle-speed mode

At 4 MHz .................................................................... 4.0 to 5.5 V

At 2 MHz .................................................................... 2.4 to 5.5 V

At 1 MHz .................................................................... 2.2 to 5.5 V

∑

Power dissipation ..................................................................

TBD

∑

Operating temperature range ................................... ≠20 to 85 ∞C

(≠40 to 85 ∞C for extended operating temperature version)

(≠40 to 125 ∞C for extended operating temperature 125 ∞C ver-

sion (Note 1))

Notes 1: In this version, the operating temperature range and total time are

limited as follows;

55 ∞C to 85 ∞C: within total 6000 hours,

85 ∞C to 125 ∞C: within total 1000 hours.

2: This is not a final specification. Some parametric limits are subject

to change.Please contact Renesas or an authorized Renesas

product distributor in the case of examination of use.

APPLICATION

Office automation equipment, factory automation equipment, home

electric appliances, consumer electronics, car, etc.

Rev.2.00 2003.04.21 page 1 of 97

7542 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

REJ03B0006-0200Z

Rev.2.00

2003.04.21