K3P7C1000B-YC

CMOS MASK ROM

64M-Bit (8Mx8 /4Mx16) CMOS MASK ROM

The K3P7C1000B-YC is a fully static mask programmable

ROM fabricated using silicon gate CMOS process technology,

and is organized either as 8,388,608 x 8 bit(byte mode) or as

4,194,304 x 16 bit(word mode) depending on BHE voltage

level.(See mode selection table)

This device includes page read mode function, page read mode

allows 8 words (or 16 bytes) of data to read fast in the same

page, CE and A

3

~ A

21

should not be changed.

This device operates with a 5.0V single power supply, and all

inputs and outputs are TTL compatible.

Because of its asynchronous operation, it requires no external

clock assuring extremely easy operation.

It is suitable for use in program memory of microprocessor, and

data memory, character generator.

The K3P7C1000B-YC is packaged in a 48-TSOP1.

GENERAL DESCRIPTION

FEATURES

∑

Switchable organization

8,388,608 x 8(byte mode)

4,194,304 x 16(word mode)

∑

Fast access time

Random Access : 100ns(Max.)@C

L

=50pF,

120ns(Max.)@C

L

=100pF

Page Access : 30ns(Max.)@C

L

=50pF

40ns(Max.)@C

L

=100pF

8 Words / 16 Bytes page access

∑

Supply voltage : single +5.0V

∑

Current consumption

Operating : 150mA(Max.)

Standby : 100

µ

A(Max.)

∑

Fully static operation

∑

All inputs and outputs TTL compatible

∑

Three state outputs

∑

Package

K3P7C1000B-YC : 48-TSOP1-1218

A

21

X

A

0~

A

2

AND

DECODER

BUFFERS

A

3

Y

AND

DECODER

BUFFERS

MEMORY CELL

SENSE AMP.

CONTROL

LOGIC

MATRIX

(4,194,304x16/

8,388,608x8)

DATA OUT

BUFFERS

A

-1

CE

OE

BHE

.

.

.

.

.

.

.

.

Q

0

/Q

8

Q

7

/Q

15

. . .

FUNCTIONAL BLOCK DIAGRAM

Pin Name

Pin Function

A

0

- A

2

Page Address Inputs

A

3

- A

21

Address Inputs

Q

0

- Q

14

Data Outputs

Q

15

/A

-1

Output 15(Word mode)/

LSB Address(Byte mode)

BHE

Word/Byte selection

CE

Chip Enable

OE

Output Enable

V

CC

Power (+5V)

Vss

Ground

N.C

No Connection

K3P7C1000B-YC

CMOS MASK ROM

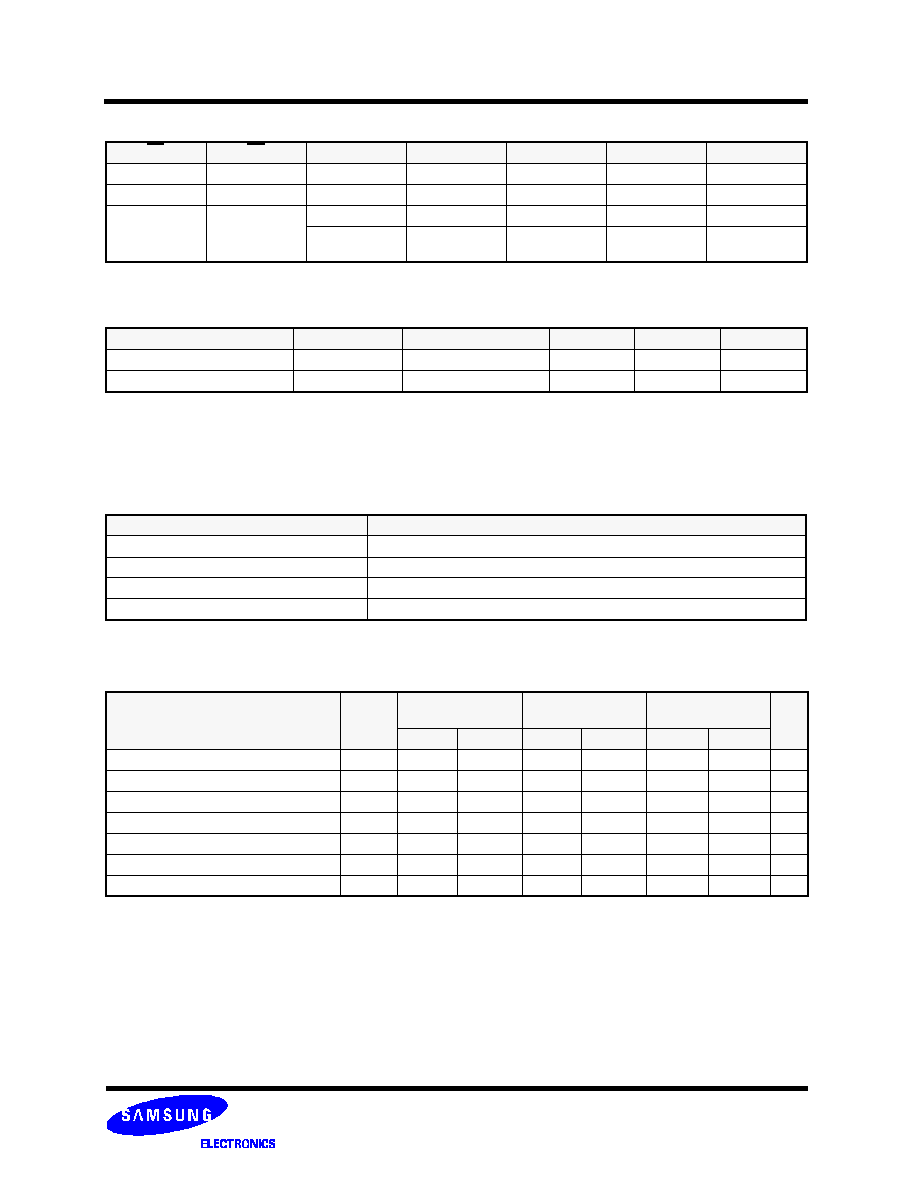

ABSOLUTE MAXIMUM RATINGS

NOTE : Permanent device damage may occur if "ABSOLUTE MAXIMUM RATINGS" are exceeded. Functional operation should be restricted to the

conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may

affect device reliability.

Item

Symbol

Rating

Unit

Voltage on Any Pin Relative to V

SS

V

IN

-0.3 to +7.0

V

Temperature Under Bias

T

BIAS

-10 to +85

∞

C

Storage Temperature

T

STG

-55 to +150

∞

C

RECOMMENDED OPERATING CONDITIONS

(Voltage reference to V

SS

, T

A

=0 to 70

∞

C)

Item

Symbol

Min

Typ

Max

Unit

Supply Voltage

V

CC

4.5

5.0

5.5

V

Supply Voltage

V

SS

0

0

0

V

PIN CONFIGURATION

BHE

A

16

A

15

A

14

A

13

A

12

A

11

A

9

A

8

A

10

A

20

A

18

A

17

A

7

A

6

A

5

A

4

K3P7C1000B-YC

1

2

48

47

3

4

5

6

7

8

9

10

39

11

12

37

13

14

15

16

17

18

19

20

21

22

TSOP1

A

3

A

1

Q

4

23

24

A

0

CE

V

SS

OE

Q

0

Q

8

Q

1

Q

3

Q

9

Q

2

Q

10

46

45

44

43

42

41

40

38

36

35

34

33

32

31

30

29

28

27

26

25

Q

15/

A-

1

Q

7

Q

14

Q

6

Q

13

Q

5

Q

12

Q

11

V

SS

A

2

A

19

V

SS

V

SS

N.C

V

SS

V

CC

V

CC

V

SS

V

SS

A

21

DC CHARACTERISTICS

NOTE : Minimum DC Voltage(V

IL

) is -0.3V an input pins. During transitions, this level may undershoot to -2.0V for periods <20ns.

Maximum DC voltage on input pins(V

IH

) is V

CC

+0.3V which, during transitions, may overshoot to V

CC

+2.0V for periods <20ns.

Parameter

Symbol

Test Conditions

Min

Max

Unit

Operating Current

I

CC

Cycle=5MHz, all outputs open

CE=OE=V

IL

, V

IN

=0.6V to 2.4V (AC Test Condition)

-

150

mA

Standby Current(TTL)

I

SB1

CE=V

IH

, all outputs open

1

mA

Standby Current(CMOS)

I

SB2

CE=V

CC

, all outputs open

100

µ

A

Input Leakage Current

I

LI

V

IN

=0 to V

CC

-

10

µ

A

Output Leakage Current

I

LO

V

OUT

=0 to V

CC

-

10

µ

A

Input High Voltage, All Inputs

V

IH

2.2

V

CC

+0.3

V

Input Low Voltage, All Inputs

V

IL

-0.3

0.8

V

Output High Voltage Level

V

OH

I

OH

=-400

µ

A

2.4

-

V

Output Low Voltage Level

V

OL

I

OL

=2.1mA

-

0.4

V

K3P7C1000B-YC

CMOS MASK ROM

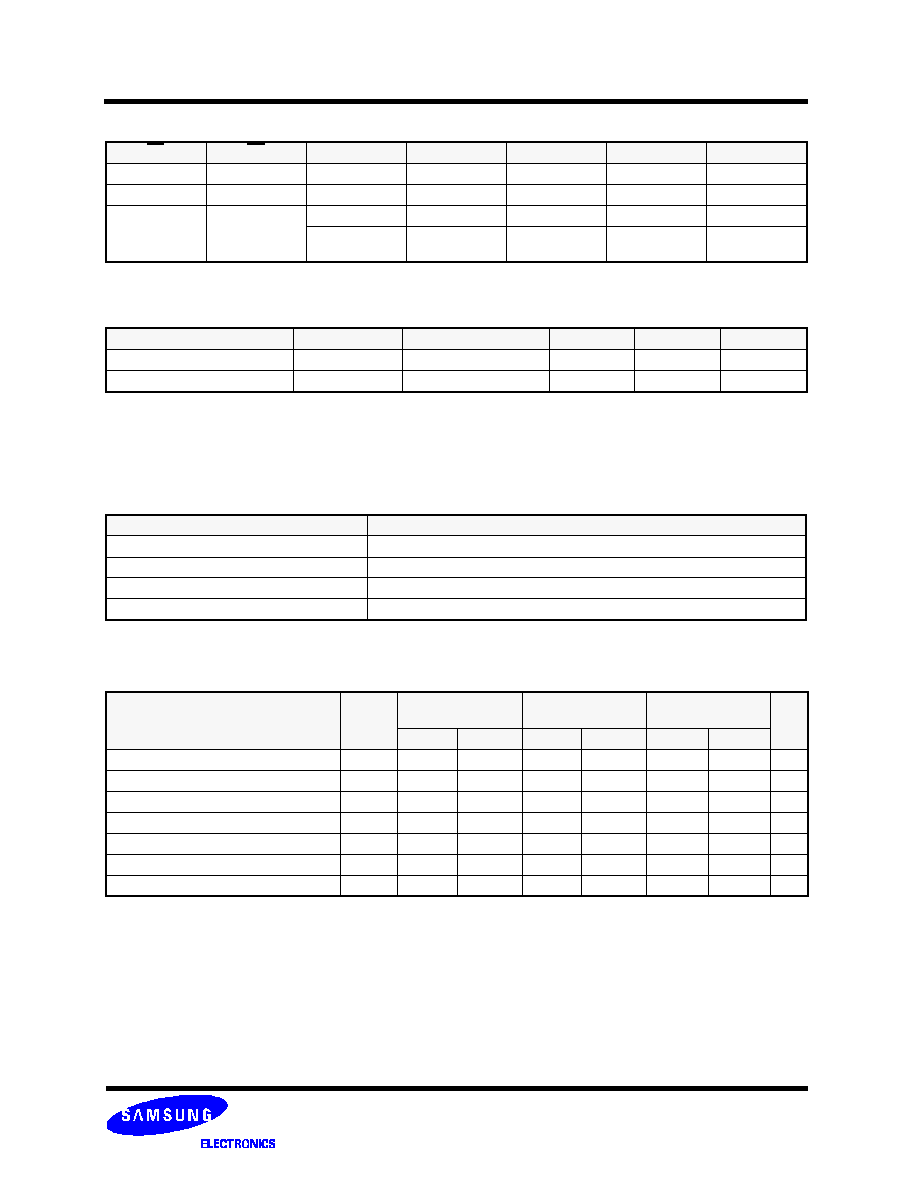

TEST CONDITIONS

Item

Value

Input Pulse Levels

0.6V to 2.4V

Input Rise and Fall Times

10ns

Input and Output timing Levels

0.8V and 2.0V

Output Loads

1 TTL Gate and C

L

=50pF or 100pF

AC CHARACTERISTICS

(T

A

=0

∞

C to +70

∞

C,V

CC

=5.0V

±

10%, unless otherwise noted.)

READ CYCLE

NOTE : Page Address is determined as below.

Word mode (BHE=V

IH

) : A

0

, A

1,

A

2

Byte mode (BHE=V

IL

) : A

-1

, A

0

, A

1,

A

2

Item

Symbol

K3P7C1000B-YC10

(C

L

=50pF)

K3P7C1000B-YC12

(C

L

=100pF)

K3P7C1000B-YC15

(C

L

=100pF)

Unit

Min

Max

Min

Max

Min

Max

Read Cycle Time

t

RC

100

120

150

ns

Chip Enable Access Time

t

ACE

100

120

150

ns

Address Access Time

t

AA

100

120

150

ns

Page Address Access Time

t

PA

30

40

50

ns

Output Enable Access Time

t

OE

30

40

50

ns

Output or Chip Disable to Output High-Z

t

DF

20

20

30

ns

Output Hold from Address Change

t

OH

0

0

0

ns

MODE SELECTION

CE

OE

BHE

Q

15

/A

-1

Mode

Data

Power

H

X

X

X

Standby

High-Z

Standby

L

H

X

X

Operating

High-Z

Active

L

L

H

Output

Operating

Q

0

~Q

15

: Dout

Active

L

Input

Operating

Q

0

~Q

7

: Dout

Q

8

~Q

14

: Hi-Z

Active

CAPACITANCE

(T

A

=25

∞

C, f=1.0MHz)

NOTE : Capacitance is periodically sampled and not 100% tested.

Item

Symbol

Test Conditions

Min

Max

Unit

Output Capacitance

C

OUT

V

OUT

=0V

-

12

pF

Input Capacitance

C

IN

V

IN

=0V

-

12

pF

K3P7C1000B-YC

CMOS MASK ROM

TIMING DIAGRAM

READ

ADD

CE

OE

D

OUT

A

0

~A

21

A

-1(*1)

D

0

~D

7

D

8

~D

15(*2)

PAGE READ

OE

ADD

D

OUT

CE

ADD

A

0,

A

1,

A

2

A

3

~A

21

VALID DATA

VALID DATA

VALID DATA

VALID DATA

1 st

2 nd

3 rd

t

DF(*3)

ADD1

ADD2

VALID DATA

VALID DATA

t

OH

t

DF(*3)

t

RC

t

ACE

t

OE

t

AA

NOTES :

*1. Byte Mode only. A

-1

is Least Significant Bit Address. (BHE = V

IL

)

*2. Word Mode only.(BHE = V

IH

)

*3. t

DF

is defined as the time at which the outputs achieve the open circuit condition and is not referenced to V

OH

or V

OL

level.

t

AA

t

PA

A

-1(*1)

D

0

~D

7

D

8

~D

15(*2)