DDR SDRAM

DDR SDRAM 256Mb E-die (x4, x8)

Rev. 1.3 April. 2005

256Mb E-die DDR SDRAM Specification

INFORMATION IN THIS DOCUMENT IS PROVIDED IN RELATION TO SAMSUNG PRODUCTS,

AND IS SUBJECT TO CHANGE WITHOUT NOTICE.

NOTHING IN THIS DOCUMENT SHALL BE CONSTRUED AS GRANTING ANY LICENSE,

EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE,

TO ANY INTELLECTUAL PROPERTY RIGHTS IN SAMSUNG PRODUCTS OR TECHNOLOGY. ALL

INFORMATION IN THIS DOCUMENT IS PROVIDED

ON AS "AS IS" BASIS WITHOUT GUARANTEE OR WARRANTY OF ANY KIND.

1. For updates or additional information about Samsung products, contact your nearest Samsung office.

2. Samsung products are not intended for use in life support, critical care, medical, safety equipment, or similar

applications where Product failure couldresult in loss of life or personal or physical harm, or any military or

defense application, or any governmental procurement to which special terms or provisions may apply.

Samsung Electronics reserves the right to change products or specification without notice.

66 TSOP-II

DDR SDRAM

DDR SDRAM 256Mb E-die (x4, x8)

Rev. 1.3 April. 2005

256Mb E-die Revision History

Revision 1.0 (April, 2003)

- First release.

Revision 1.1 (August, 2003)

- Corrected typo.

Revision1.2 (October, 2004)

- Corrected typo.

Revision1.3 (April, 2005)

- Added notice and corrected typo.

DDR SDRAM

DDR SDRAM 256Mb E-die (x4, x8)

Rev. 1.3 April. 2005

∑ Double-data-rate architecture; two data transfers per clock cycle

∑ Bidirectional data strobe(DQS)

∑ Four banks operation

∑ Differential clock inputs(CK and CK)

∑ DLL aligns DQ and DQS transition with CK transition

∑ MRS cycle with address key programs

-. Read latency 2, 2.5 (clock)

-. Burst length (2, 4, 8)

-. Burst type (sequential & interleave)

∑ All inputs except data & DM are sampled at the positive going edge of the system clock(CK)

∑ Data I/O transactions on both edges of data strobe

∑ Edge aligned data output, center aligned data input

∑ DM for write masking only (x4, x8)

∑ Auto & Self refresh

∑ 7.8us refresh interval(8K/64ms refresh)

∑ Maximum burst refresh cycle : 8

∑ 66pin TSOP II package

*CL : CAS Latency

Operating Frequencies

B3(DDR333@CL=2.5)

AA(DDR266@CL=2.0)

A2(DDR266@CL=2.0)

B0(DDR266@CL=2.5)

Speed @CL2

133MHz

133MHz

133MHz

100MHz

Speed @CL2.5

166MHz

133MHz

133MHz

133MHz

Ordering Information

Part No.

Org.

Max Freq.

Interface

Package

K4H560438E-TC/LB3

64M x 4

B3(DDR333@CL=2.5)

SSTL2

66pin TSOP II

K4H560438E-TC/LAA

AA(DDR266@CL=2)

K4H560438E-TC/LA2

A2(DDR266@CL=2)

K4H560438E-TC/LB0

B0(DDR266@CL=2.5)

K4H560838E-TC/LB3

32M x 8

B3(DDR333@CL=2.5)

SSTL2

66pin TSOP II

K4H560838E-TC/LAA

AA(DDR266@CL=2)

K4H560838E-TC/LA2

A2(DDR266@CL=2)

K4H560838E-TC/LB0

B0(DDR266@CL=2.5)

Key Features

DDR SDRAM

DDR SDRAM 256Mb E-die (x4, x8)

Rev. 1.3 April. 2005

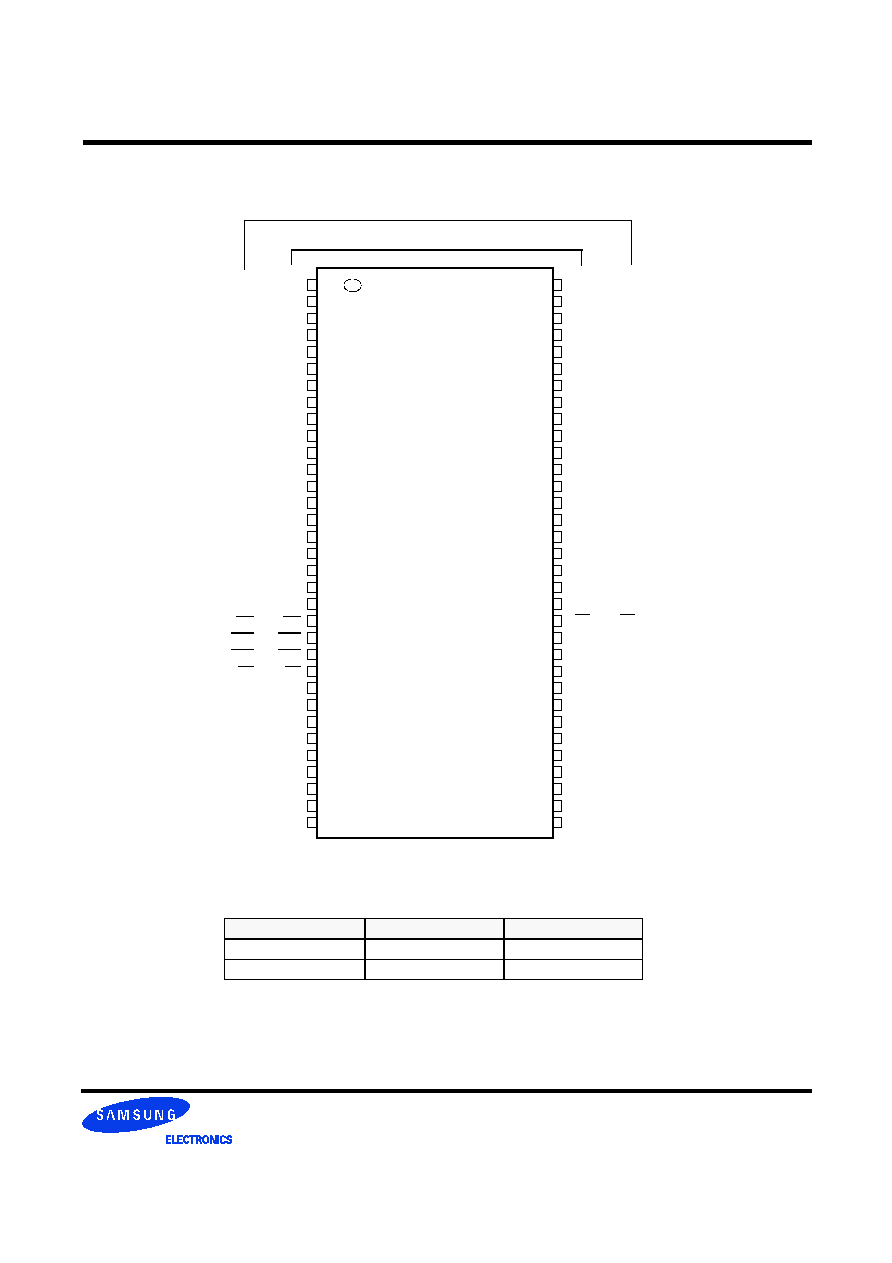

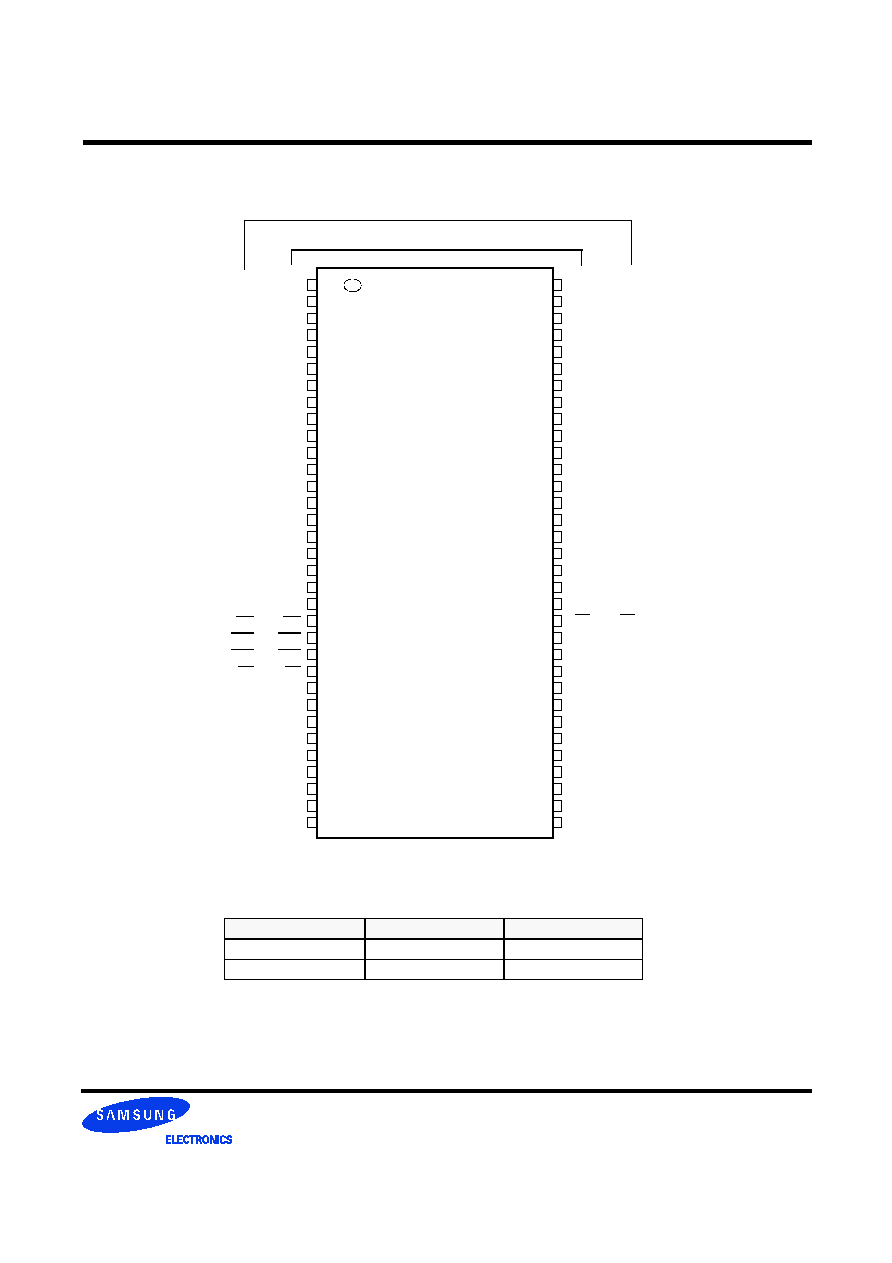

Pin Description

DM is internally loaded to match DQ and DQS identically.

256Mb TSOPII Package Pinout

Row & Column address configuration

V

DD

1

66Pin TSOPII

(400mil x 875mil)

DQ

0

2

V

DDQ

3

NC

4

DQ

1

5

V

SSQ

6

NC

7

DQ

2

8

V

DDQ

9

NC

10

DQ

3

11

V

SSQ

12

BA

0

20

CS

19

RAS

18

CAS

17

WE

16

NC

15

V

DDQ

14

NC

13

V

DD

27

A

3

26

A

2

25

A

1

24

A

0

23

AP/A

10

22

BA

1

21

V

SS

54

DQ

7

53

V

SSQ

52

NC

51

DQ

6

50

V

DDQ

49

NC

48

DQ

5

47

V

SSQ

46

NC

45

DQ

4

44

V

DDQ

43

A

11

35

36

CKE

37

CK

38

DM

39

V

REF

40

V

SSQ

41

NC

42

V

SS

55

A

4

56

A

5

57

A

6

58

A

7

59

A

8

60

A

9

34

(0.65mm Pin Pitch)

33

32

31

30

29

28

61

62

63

64

65

66

NC

NC

NC

NC

NC

V

DD

NC

DQS

NC

V

SS

CK

NC

A

12

V

SS

NC

V

SSQ

NC

DQ

3

V

DDQ

NC

NC

V

SSQ

NC

DQ

2

V

DDQ

A

11

CKE

CK

DM

V

REF

V

SSQ

NC

V

SS

A

4

A

5

A

6

A

7

A

8

A

9

NC

DQS

NC

V

SS

CK

NC

A

12

V

DD

NC

V

DDQ

NC

DQ

0

V

SSQ

NC

NC

V

DDQ

NC

DQ

1

V

SSQ

BA

0

CS

RAS

CAS

WE

NC

V

DDQ

NC

V

DD

A

3

A

2

A

1

A

0

AP/A

10

BA

1

NC

NC

NC

NC

NC

V

DD

Bank Address

BA0~BA1

Auto Precharge

A10

Organization

Row Address

Column Address

64Mx4

A0~A12

A0-A9, A11

32Mx8

A0~A12

A0-A9

64Mb x 4

32Mb x 8

DDR SDRAM

DDR SDRAM 256Mb E-die (x4, x8)

Rev. 1.3 April. 2005

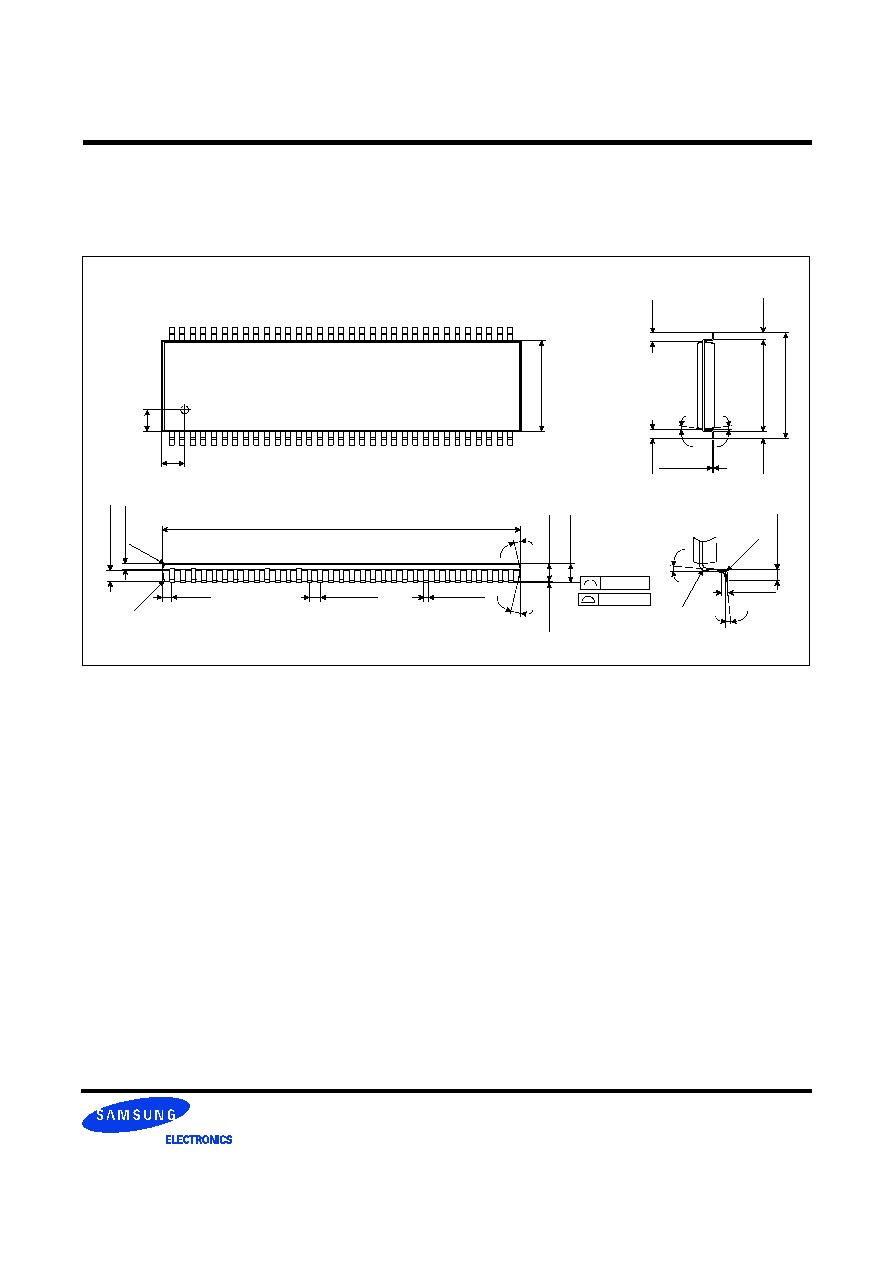

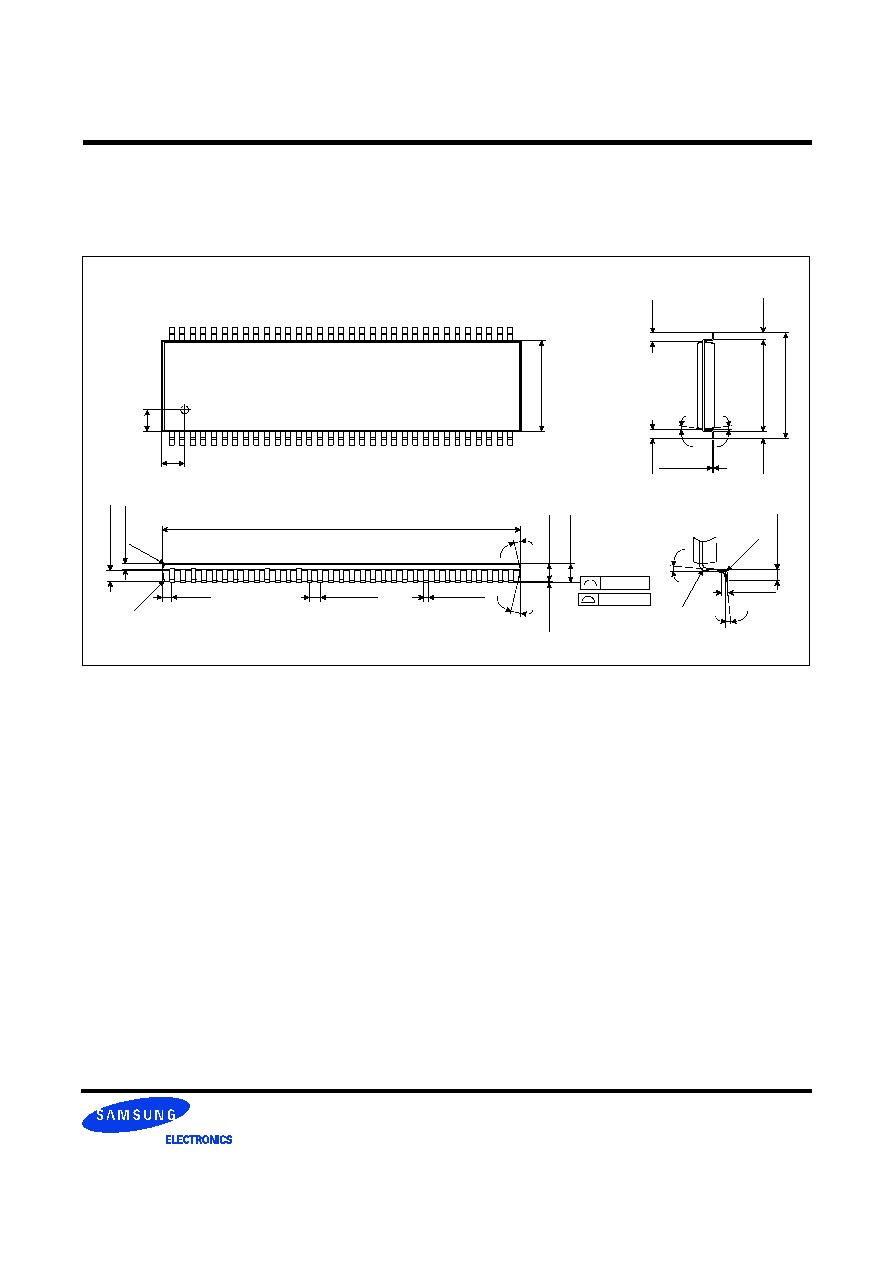

Units : Millimeters

0.30

±

0.08

0.65TYP

(0.71)

22.22

±

0.10

0.125

(0.80

)

10

.16

±

0.1

0

0

◊

~8

◊

#1

#33

#66

#34

(1.50)

(1.50

)

0.65

±

0.08

1.0

0

±

0.

1

0

1.2

0

MAX

(0

.50)

(0.

50)

(10.1

6

)

11

.

7

6

±

0.2

0

(10

◊

)

(10

◊

)

+0.075

-0.035

(0.8

0)

0.10 MAX

0.075 MAX

[

]

0

.

05 MIN

(10

◊

)

(10

◊

)

(R0.1

5)

0.

210

±

0.0

5

0.

665

±

0.0

5

(R

0.

15)

(4

◊

)

(R

0.

25

)

(R

0.

25)

0.45

~0.7

5

0.25TYP

NOTE

1. ( ) IS REFERENCE

2. [ ] IS ASS

'

Y OUT QUALITY

66pin TSOPII / Package dimension

Package Physical Dimension