FLASH MEMORY

1

K9W4G08U1M

K9W4G16U1M

K9K2G08U0M

K9K2G16Q0M

K9K2G08Q0M

K9K2G16U0M

Document Title

256M x 8 Bit / 128M x 16 Bit NAND Flash Memory

Revision History

The attached data sheets are prepared and approved by SAMSUNG Electronics. SAMSUNG Electronics CO., LTD. reserve the

right to change the specifications. SAMSUNG Electronics will evaluate and reply to your requests and questions about device. If you

have any questions, please contact the SAMSUNG branch office near your office.

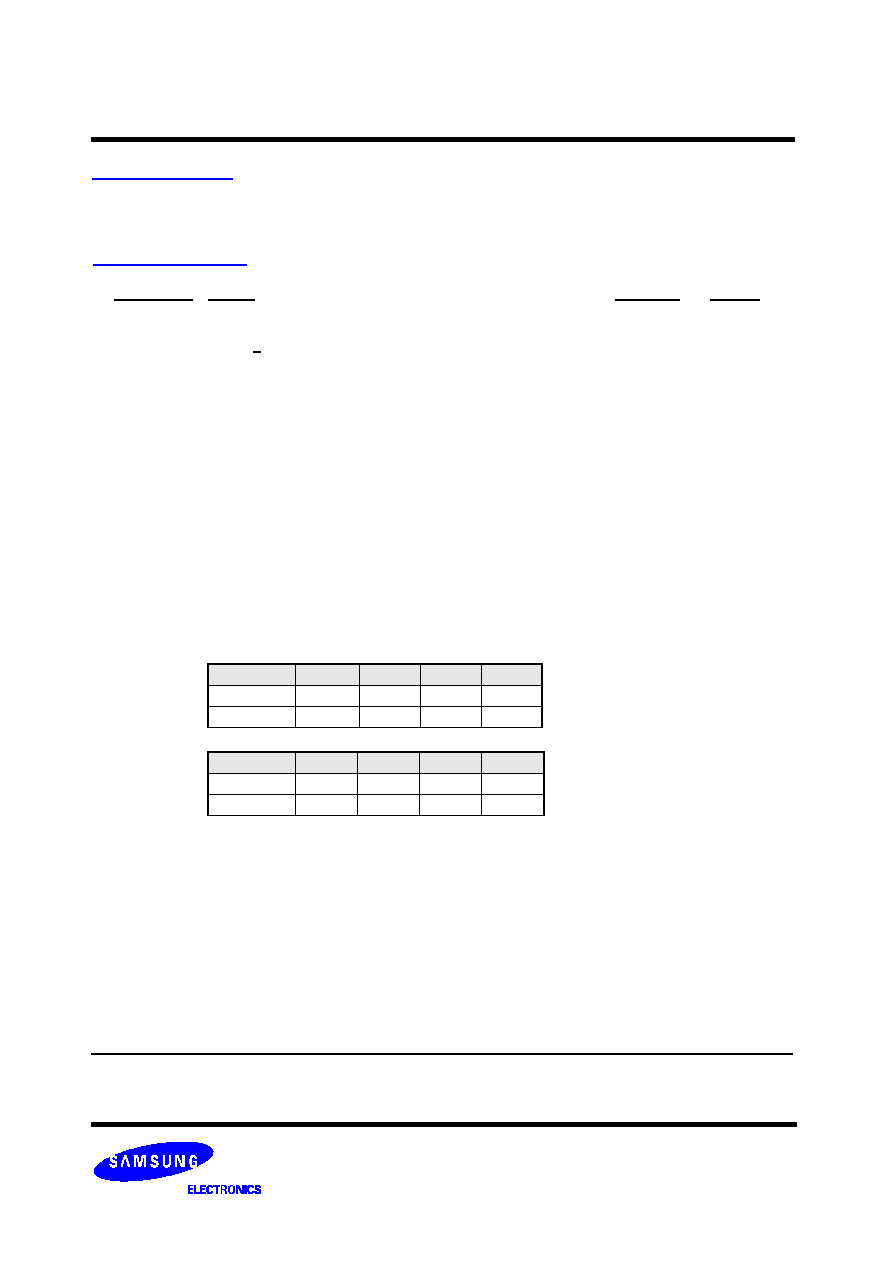

Revision No

0.0

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

Remark

Advance

Preliminary

Preliminary

Preliminary

Preliminary

Preliminary

Preliminary

Preliminary

Preliminary

History

1. Initial issue

1. I

OL

(R/B) of 1.8V device is changed.

-min. Value: 7mA -->3mA

-typ. Value: 8mA -->4mA

1. 5th cycle of ID is changed

: 40h --> 44h

1. Add WSOP Package Dimensions.

1. Add two-K9K2GXXU0M-YCB0/YIB0 Stacked Package

1. Min valid block of K9W4GXXU1M-YCB0/YIB0 is changed .

- min. 4016 --> 4036

1.

Each K9K2GXXX0M chip in the K9W4GXXU1M has Maximum 30

invalid blocks.

2. K9W4GXXU1M's ID is changed

(Before)

(After)

1. Add the Rp vs tr ,tf & Rp vs ibusy graph for 1.8V device (Page 36)

2. Add the data protection Vcc guidence for 1.8V device - below about

1.1V. (Page 37)

1. The min. Vcc value 1.8V devices is changed.

K9K2GXXQ0M : Vcc 1.65V~1.95V --> 1.70V~1.95V

Device

2nd Cycle 3rd cycle 4th Cycle 5th Cycle

K9W4G08U1M

DCh

C3

15h

4Ch

K9W4G16U1M

CCh

C3

55h

4Ch

Device

2nd Cycle 3rd cycle

4th Cycle 5th Cycle

K9W4G08U1M

DAh

C1

15h

44h

K9W4G16U1M

CAh

C1

55h

44h

Draft Date

Aug. 30.2001

Nov. 5. 2001

Jan. 23. 2002

May. 29. 2002

Aug. 13. 2 002

Aug. 22. 2002

Nov. 07. 2002

Nov. 22. 2002

Mar. 6. 2003

FLASH MEMORY

2

K9W4G08U1M

K9W4G16U1M

K9K2G08U0M

K9K2G16Q0M

K9K2G08Q0M

K9K2G16U0M

Document Title

256M x 8 Bit / 128M x 16 Bit

NAND Flash Memory

Revision History

The attached data sheets are prepared and approved by SAMSUNG Electronics. SAMSUNG Electronics CO., LTD. reserve the

right to change the specifications. SAMSUNG Electronics will evaluate and reply to your requests and questions about device. If you

have any questions, please contact the SAMSUNG branch office near your office.

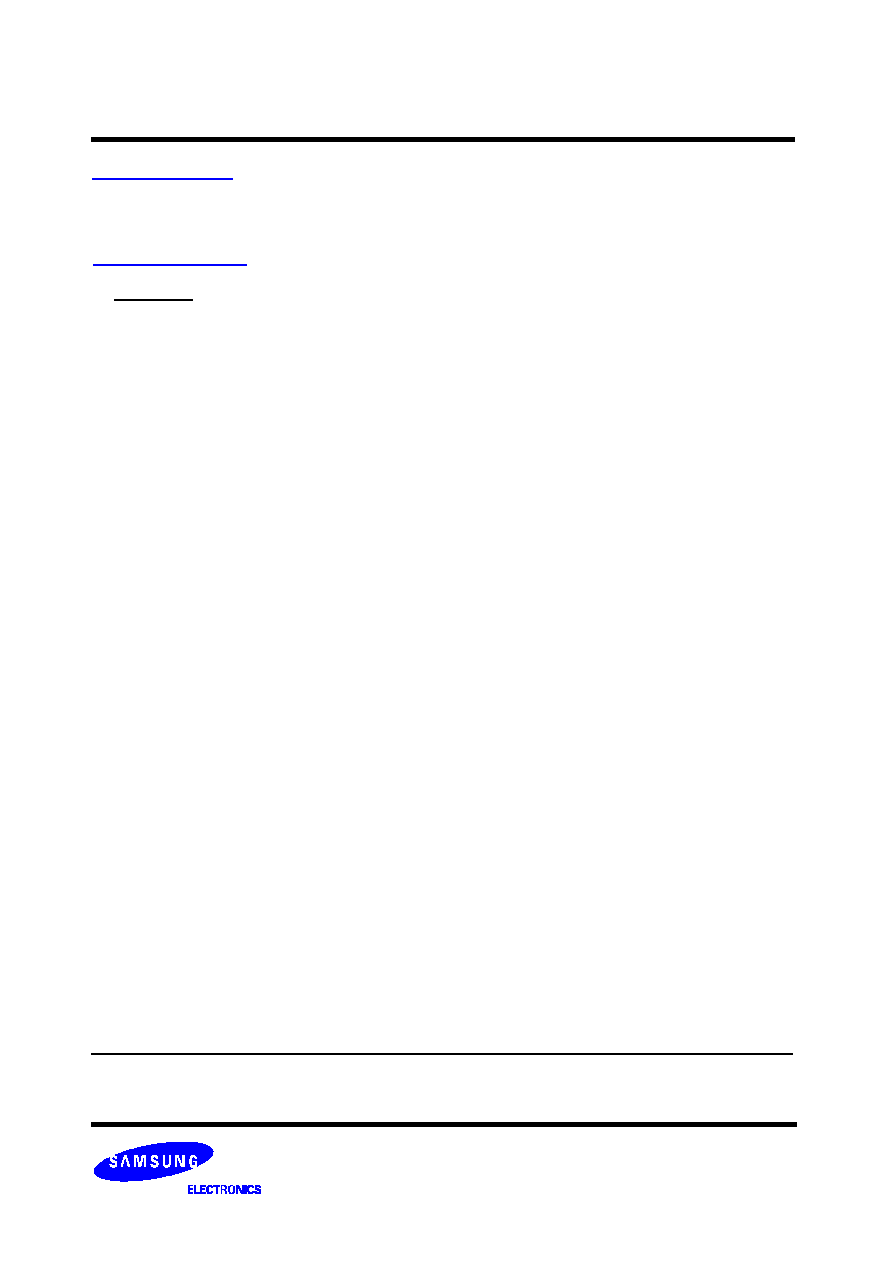

Revision No

0.9

1.0

1.1

1.2

1.3

1.4

1.5

1.6

1.7

Remark

Preliminary

Preliminary

Preliminary

Preliminary

Preliminary

Preliminary

History

Pb-free Package is added.

K9K2G08U0M-FCB0,FIB0

K9K2G08Q0M-PCB0,PIB0

K9K2G08U0M-PCB0,PIB0

K9K2G16U0M-PCB0,PIB0

K9K2G16Q0M-PCB0,PIB0

K9W4G08U1M-PCB0,PIB0,ECB0,EIB0

K9W4G16U1M-PCB0,PIB0,ECB0,EIB0

Errata is added.(Front Page)-K9K2GXXQ0M

tWC tWP tWH tRC tREH tRP tREA tCEA

Specification 45 25 15 50 15 25 30 45

Relaxed value 80 60 20 80 20 60 60 75

1. The 3rd Byte ID after 90h ID read command is don't cared.

The 5th Byte ID after 90h ID read command is deleted.

New package dimension is added.(K9W4GXXU1M-KXB0/EXB0)

1. Min valid block of K9W4GXXU1M-YCB0/YIB0 is changed .

- min. 4036 --> 4016

2. Note is added.

(VIL can undershoot to -0.4V and VIH can overshoot to VCC +0.4V for

durations of 20 ns or less.)

AC parameters are changed-K9K2GXXQ0M

tWC tWP tWH tRC tREH tRP tREA tCEA

Before 45 25 15 50 15 25 30 45

After 80 60 20 80 20 60 60 75

1. Added Addressing method for program operation

1. Add the Protrusion/Burr value in WSOP1

PKG Diagram

.

1. PKG(TSOP1, WSOP1) Dimension Change

Draft Date

Mar. 13.2003

Mar. 17.2003

Apr. 9. 2003

Apr. 15. 2003

Apr. 18. 2003

Aug. 5. 2003

Jan. 27. 2004

Apr. 24. 2004

May. 19. 2004

FLASH MEMORY

3

K9W4G08U1M

K9W4G16U1M

K9K2G08U0M

K9K2G16Q0M

K9K2G08Q0M

K9K2G16U0M

GENERAL DESCRIPTION

FEATURES

∑

Voltage Supply

-1.8V device(K9K2GXXQ0M): 1.7V~1.95V

-3.3V device(K9XXGXXUXM): 2.7 V ~3.6 V

∑

Organization

- Memory Cell Array

-X8 device(K9K2G08X0M) : (256M + 8,192K)bit x 8bit

-X16 device(K9K2G16X0M) : (128M + 4,096K)bit x 16bit

- Data Register

-X8 device(K9K2G08X0M): (2K + 64)bit x8bit

-X16 device(K9K2G16X0M): (1K + 32)bit x16bit

- Cache Register

-X8 device(K9K2G08X0M): (2K + 64)bit x8bit

-X16 device(K9K2G16X0M): (1K + 32)bit x16bit

∑

Automatic Program and Erase

- Page Program

-X8 device(K9K2G08X0M): (2K + 64)Byte

-X16 device(K9K2G16X0M): (1K + 32)Word

- Block Erase

-X8 device(K9K2G08X0M): (128K + 4K)Byte

-X16 device(K9K2G16X0M): (64K + 2K)Word

∑

Page Read Operation

- Page Size

- X8 device(K9K2G08X0M): 2K-Byte

- X16 device(K9K2G16X0M) : 1K-Word

- Random Read : 25

µ

s(Max.)

- Serial Access

1.8V device(K9K2GXXQ0M): 80ns(Min.)

3.3V device(K9XXGXXUXM): 50ns(Min.)

256M x 8 Bit / 128M x 16 Bit NAND Flash Memory

∑

Fast Write Cycle Time

- Program time : 300

µ

s(Typ.)

- Block Erase Time : 2ms(Typ.)

∑

Command/Address/Data Multiplexed I/O Port

∑

Hardware Data Protection

- Program/Erase Lockout During Power Transitions

∑

Reliable CMOS Floating-Gate Technology

- Endurance : 100K Program/Erase Cycles

- Data Retention : 10 Years

∑

Command Register Operation

∑

Cache Program Operation for High Performance Program

∑

Power-On Auto-Read Operation

∑

Intelligent Copy-Back Operation

∑

Unique ID for Copyright Protection

∑

Package :

- K9K2GXXX0M-YCB0/YIB0

48 - Pin TSOP I (12 x 20 / 0.5 mm pitch)

- K9K2G08U0M-VCB0/VIB0

48 - Pin WSOP I (12X17X0.7mm)

- K9K2GXXX0M-PCB0/PIB0

48 - Pin TSOP I (12 x 20 / 0.5 mm pitch)- Pb-free Package

- K9K2G08U0M-FCB0/FIB0

48 - Pin WSOP I (12X17X0.7mm)- Pb-free Package

* K9K2G08U0M-V,F(WSOPI ) is the same device as

K9K2G08U0M-Y,P(TSOP1) except package type.

- K9W4GXXU1M-YCB0,PCB0/YIB0,PIB0 : Two K9K2G08U0M

stacked.

48 - Pin TSOP I (12 x 20 / 0.5 mm pitch)

- K9W4GXXU1M-KCB0,ECB0/KIB0,EIB0 : Two K9K2G08U0M

stacked.

48 - Pin TSOP I (12 x 17 / 0.5 mm pitch)

Offered in 256Mx8bit or 128Mx16bit, the K9K2GXXX0M is 2G bit with spare 64M bit capacity. Its NAND cell provides the most cost-

effective solution for the solid state mass storage market. A program operation can be performed in typical 300

µ

s on the 2112-

byte(X8 device) or 1056-word(X16 device) page and an erase operation can be performed in typical 2ms on a 128K-byte(X8 device)

or 64K-word(X16 device) block. Data in the data page can be read out at 80ns(1.8V device) or 50ns(3.3V device) cycle time per

byte(X8 device) or word(X16 device). The I/O pins serve as the ports for address and data input/output as well as command input.

The on-chip write controller automates all program and erase functions including pulse repetition, where required, and internal verifi-

cation and margining of data. Even the write-intensive systems can take advantage of the K9K2GXXX0M

s extended reliability of

100K program/erase cycles by providing ECC(Error Correcting Code) with real time mapping-out algorithm. The K9K2GXXX0M is an

optimum solution for large nonvolatile storage applications such as solid state file storage and other portable applications requiring

non-volatility. An ultra high density solution having two 2Gb stacked with two chip selects is also available in standard TSOPI pack-

age.

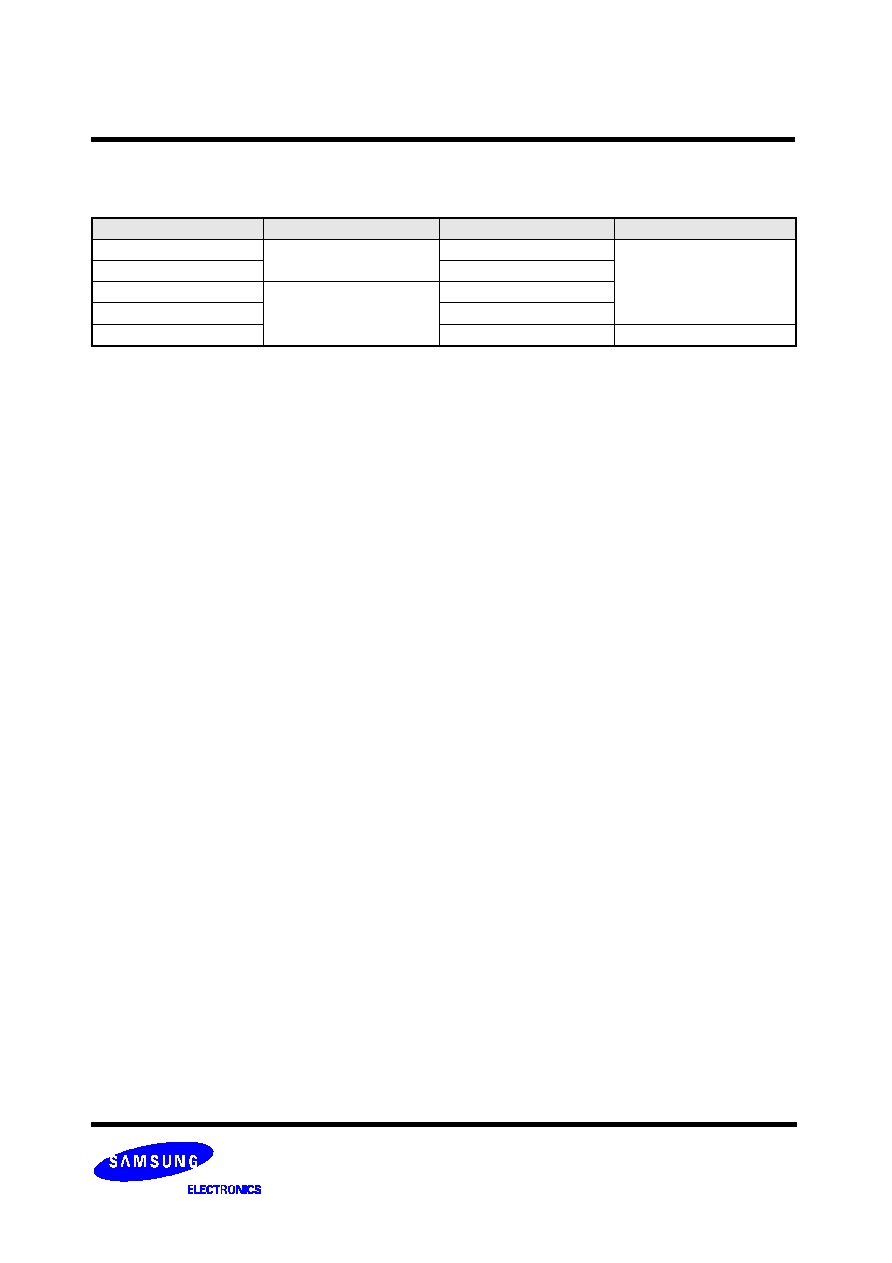

PRODUCT LIST

Part Number

Vcc Range

Organization

PKG Type

K9K2G08Q0M-Y,P

1.7 ~ 1.95V

X8

TSOP1

K9K2G16Q0M-Y,P

X16

K9XXG08UXM-Y,P,K,E

2.7 ~ 3.6V

X8

K9XXG16UXM-Y,P,K,E

X16

K9K2G08U0M-V,F

X8

WSOP1

FLASH MEMORY

4

K9W4G08U1M

K9W4G16U1M

K9K2G08U0M

K9K2G16Q0M

K9K2G08Q0M

K9K2G16U0M

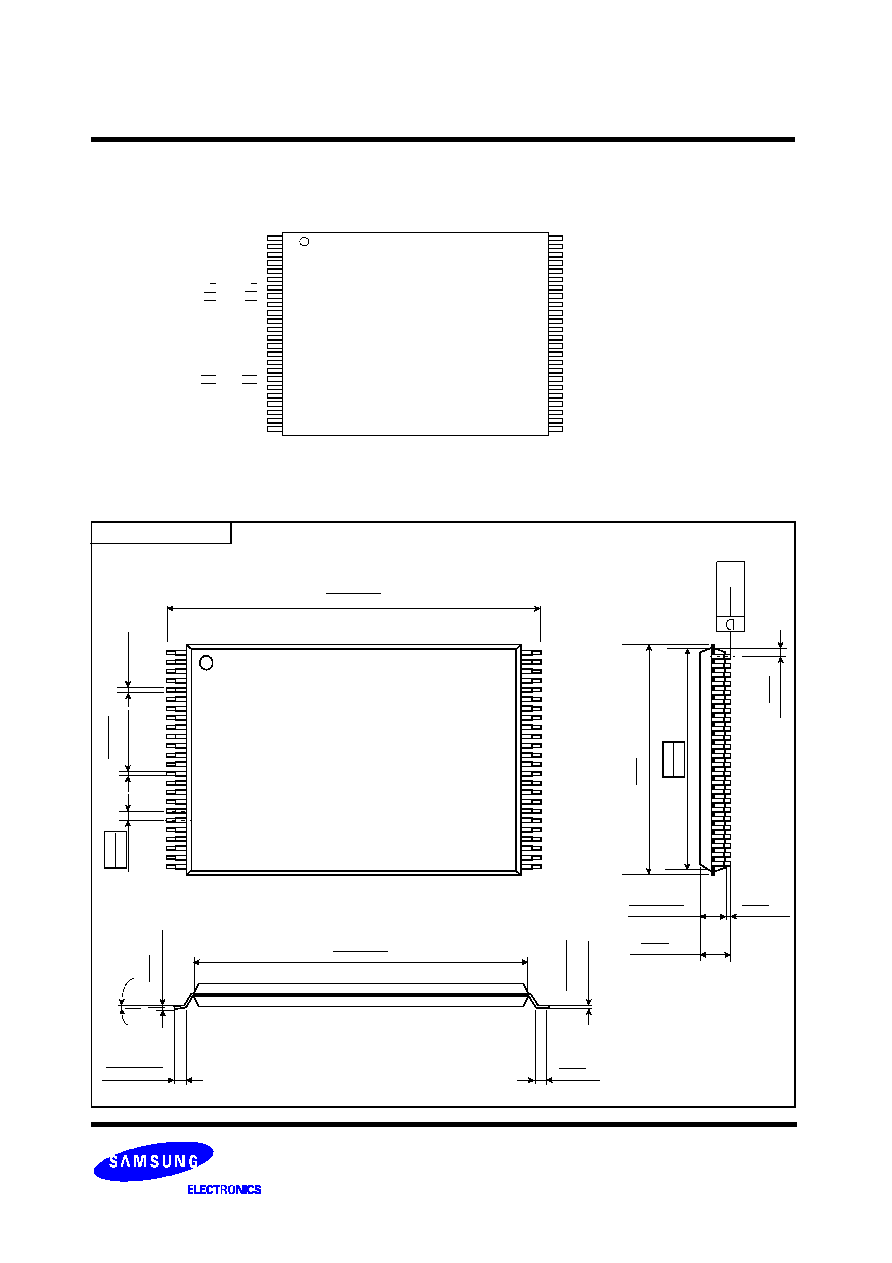

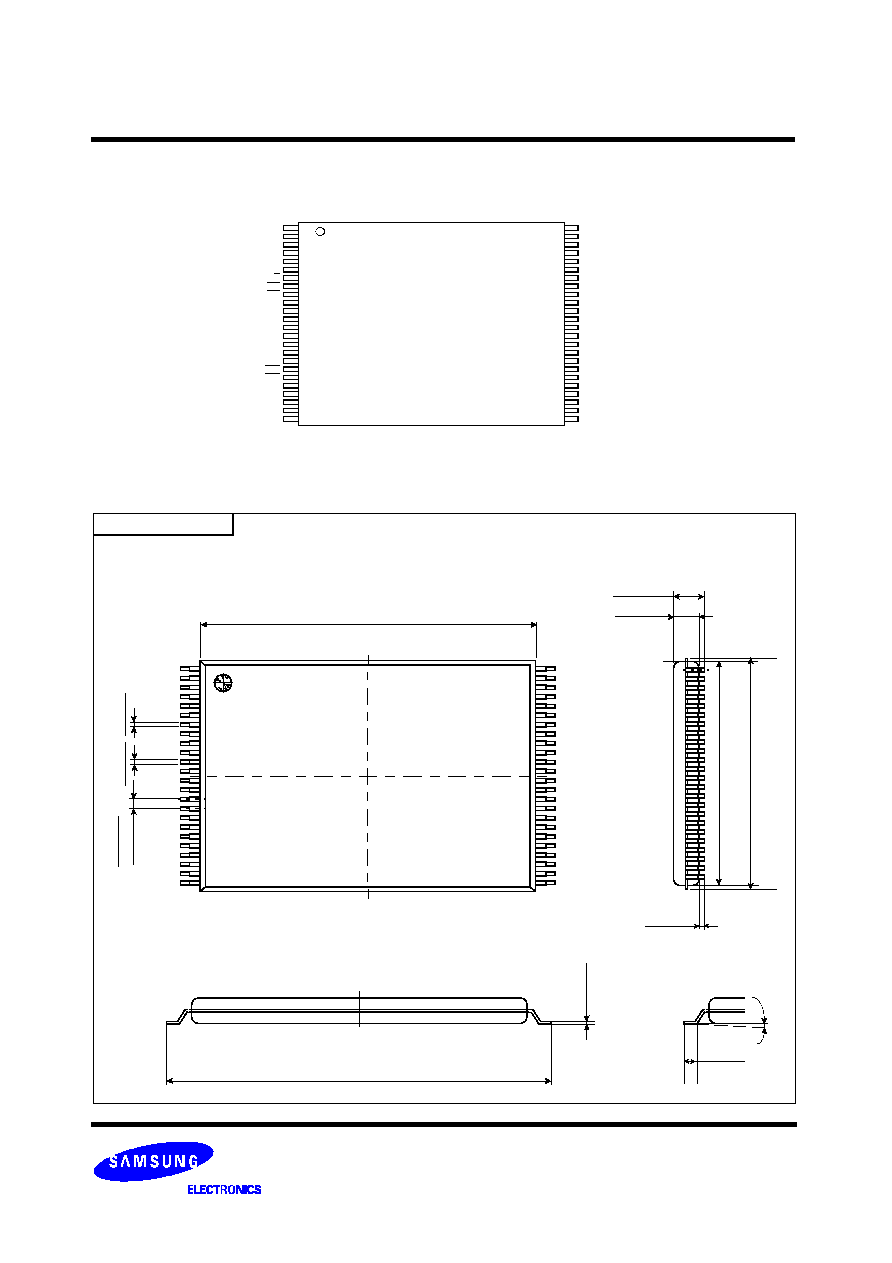

PIN CONFIGURATION (TSOP1)

K9K2GXXX0M-YCB0,PCB0/YIB0,PIB0

X8

X16

X16

X8

48-pin TSOP1

Standard Type

12mm x 20mm

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

N.C

N.C

N.C

N.C

N.C

N.C

R/B

RE

CE

N.C

N.C

Vcc

Vss

N.C

N.C

CLE

ALE

WE

WP

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

I/O7

I/O6

I/O5

I/O4

N.C

N.C

PRE

Vcc

Vss

N.C

N.C

N.C

I/O3

I/O2

I/O1

I/O0

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

R/B

RE

CE

N.C

N.C

Vcc

Vss

N.C

N.C

CLE

ALE

WE

WP

N.C

N.C

N.C

N.C

N.C

Vss

I/O15

I/O7

I/O14

I/O6

I/O13

I/O5

I/O12

I/O4

N.C

PRE

Vcc

N.C

N.C

N.C

I/O11

I/O3

I/O10

I/O2

I/O9

I/O1

I/O8

I/O0

Vss

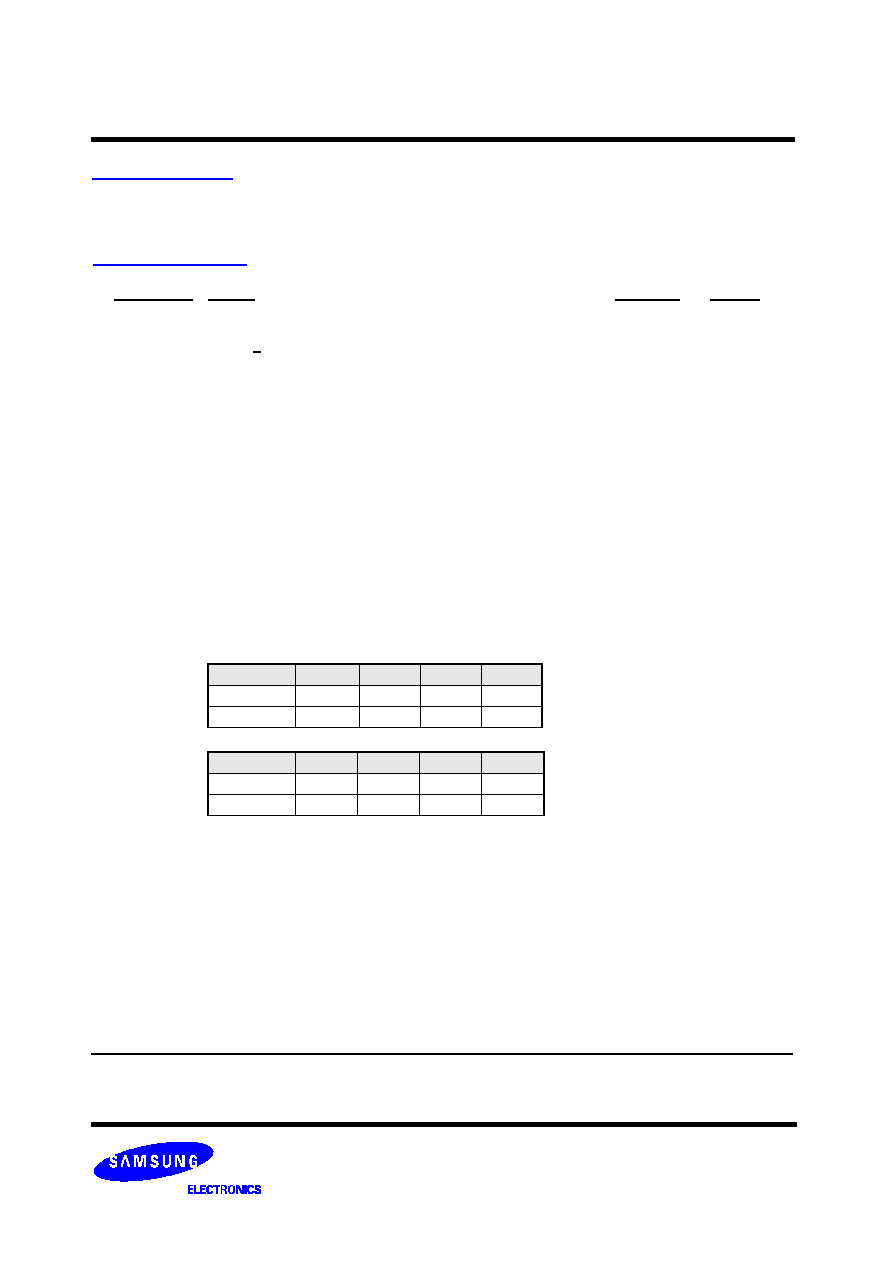

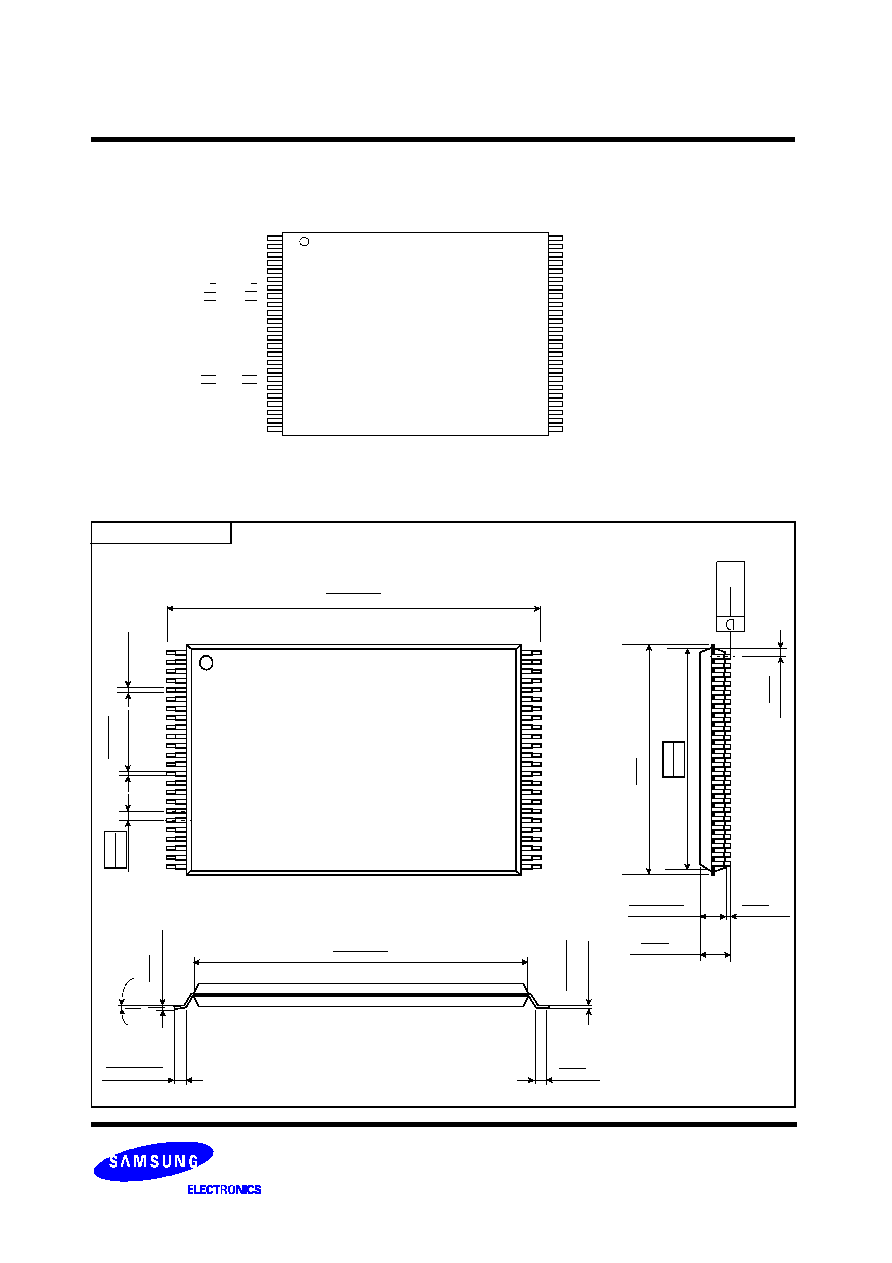

PACKAGE DIMENSIONS

48-PIN LEAD/LEAD FREE PLASTIC THIN SMALL OUT-LINE PACKAGE TYPE(I)

48 - TSOP1 - 1220AF

Unit :mm/Inch

0.787

±

0.008

20.00

±

0.20

#1

#24

0

.

1

6

+

0

.

0

7

-

0

.

0

3

0

.

0

0

8

+

0

.

0

0

3

-

0

.

0

0

1

0

.

5

0

0

.

0

1

9

7

#48

#25

0

.

4

8

8

1

2

.

4

0

M

A

X

1

2

.

0

0

0

.

4

7

2

0

.

1

0

0

.

0

0

4

M

A

X

0

.

2

5

0

.

0

1

0

(

)

0.039

±

0.002

1.00

±

0.05

0.002

0.05

MIN

0.047

1.20

MAX

0.45~0.75

0.018~0.030

0.724

±

0.004

18.40

±

0.10

0~8

∞

0

.

0

1

0

0

.

2

5

T

Y

P

0

.

1

2

5

+

0

.

0

7

5

0

.

0

3

5

0

.

0

0

5

+

0

.

0

0

3

-

0

.

0

0

1

0.50

0.020

(

)

0

.

2

0

+

0

.

0

7

-

0

.

0

3

FLASH MEMORY

5

K9W4G08U1M

K9W4G16U1M

K9K2G08U0M

K9K2G16Q0M

K9K2G08Q0M

K9K2G16U0M

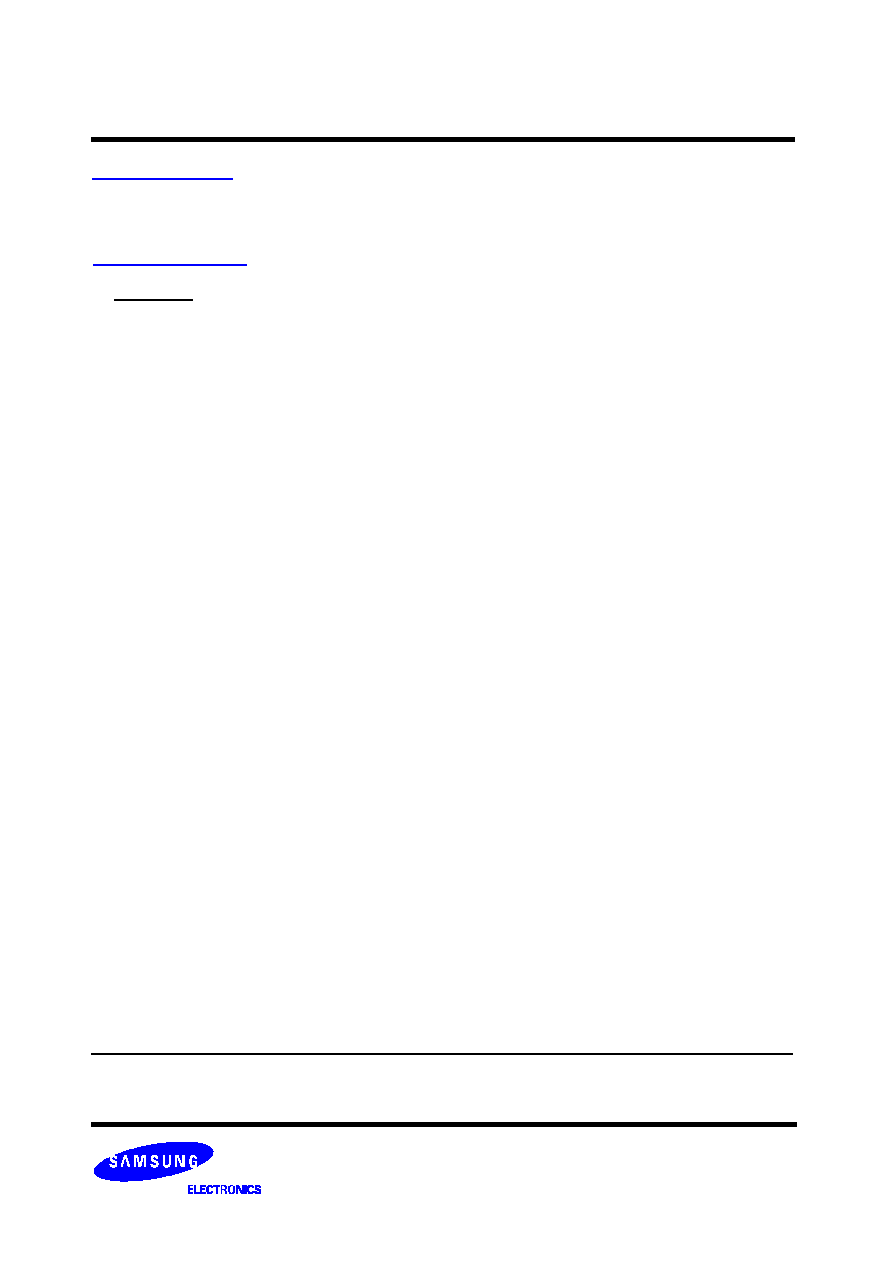

PIN CONFIGURATION (WSOP1)

K9K2G08U0M-VCB0,FCB0/VIB0,FIB0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

N.C

N.C

DNU

N.C

N.C

N.C

R/B

RE

CE

DNU

N.C

Vcc

Vss

N.C

DNU

CLE

ALE

WE

WP

N.C

N.C

DNU

N.C

N.C

N.C

N.C

DNU

N.C

I/O7

I/O6

I/O5

I/O4

N.C

DNU

N.C

Vcc

Vss

N.C

DNU

N.C

I/O3

I/O2

I/O1

I/O0

N.C

DNU

N.C

N.C

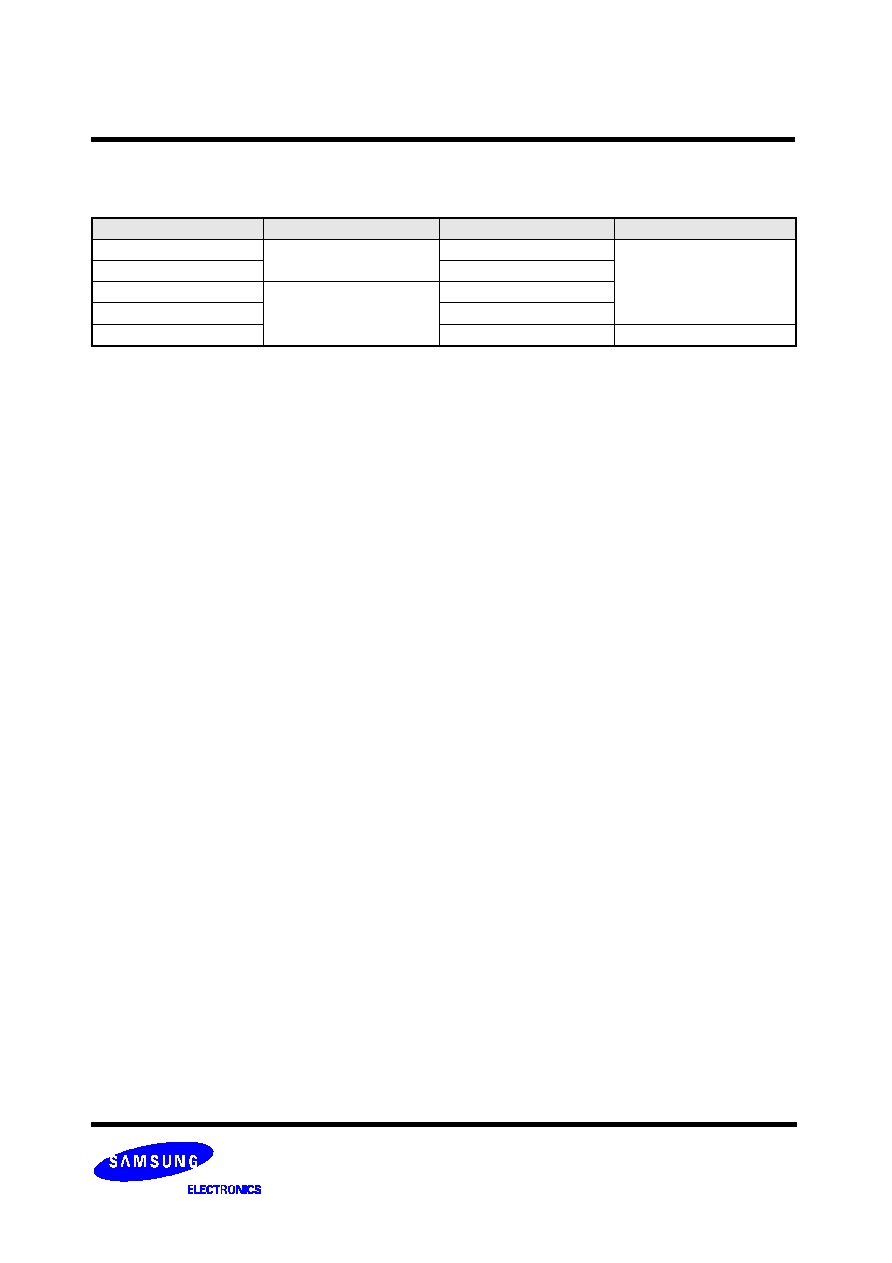

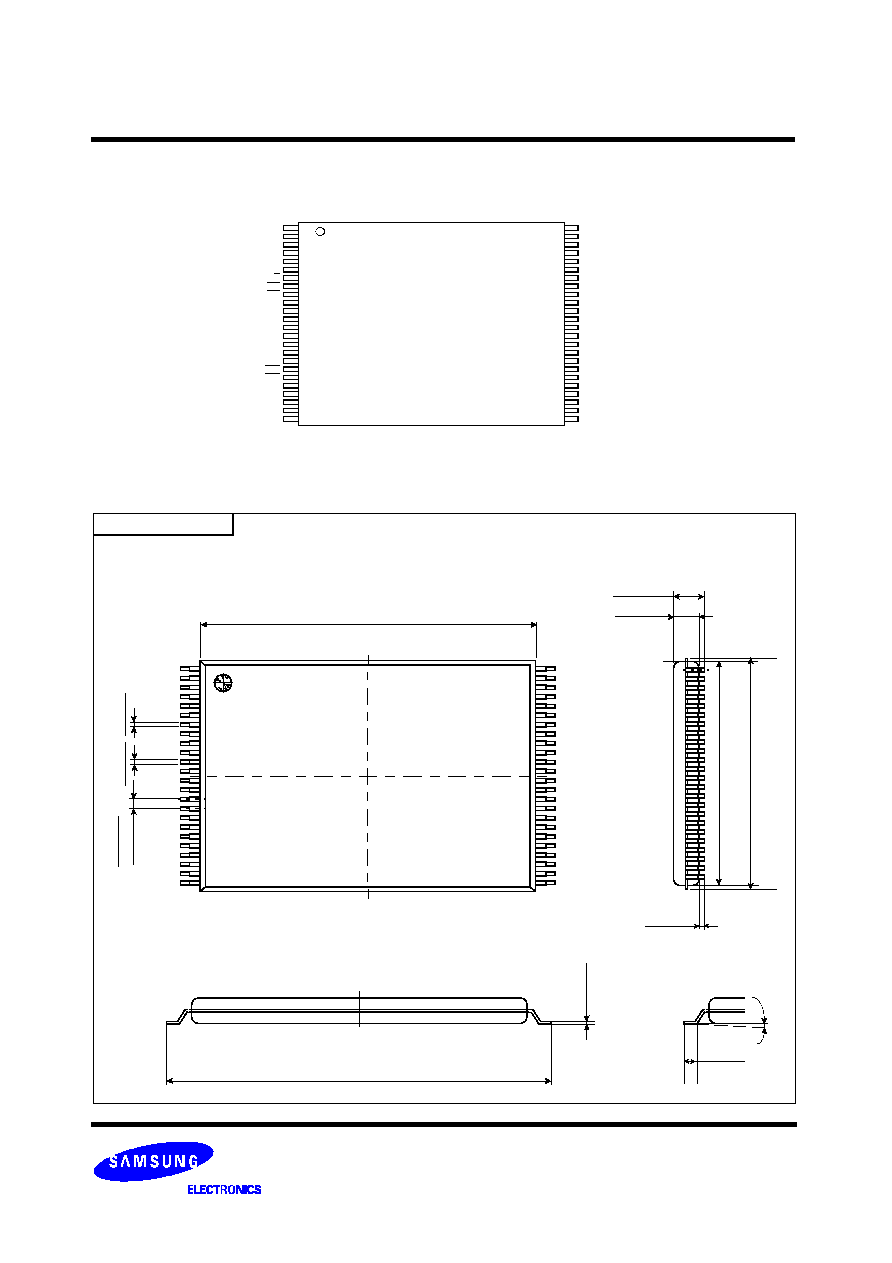

PACKAGE DIMENSIONS

48-PIN LEAD PLASTIC VERY VERY THIN SMALL OUT-LINE PACKAGE TYPE (I)

48 - WSOP1 - 1217F

Unit :mm

15.40

±

0.10

#1

#24

0

.

2

0

+

0

.

0

7

-

0

.

0

3

0

.

1

6

+

0

.

0

7

-

0

.

0

3

0

.

5

0

T

Y

P

(

0

.

5

0

±

0

.

0

6

)

#48

#25

0

.

1

0

+

0

.

0

7

5

-

0

.

0

3

5

17.00

±

0.20

0

∞

~8

∞

0.45~0.75

1

2

.

0

0

±

0

.

1

0

0.58

±

0.04

0.70 MAX

(0.01Min)

1

2

.

4

0

M

A

X