PRELIMINARY

Revision 3.0

KM62256C Family

CMOS SRAM

April 1996

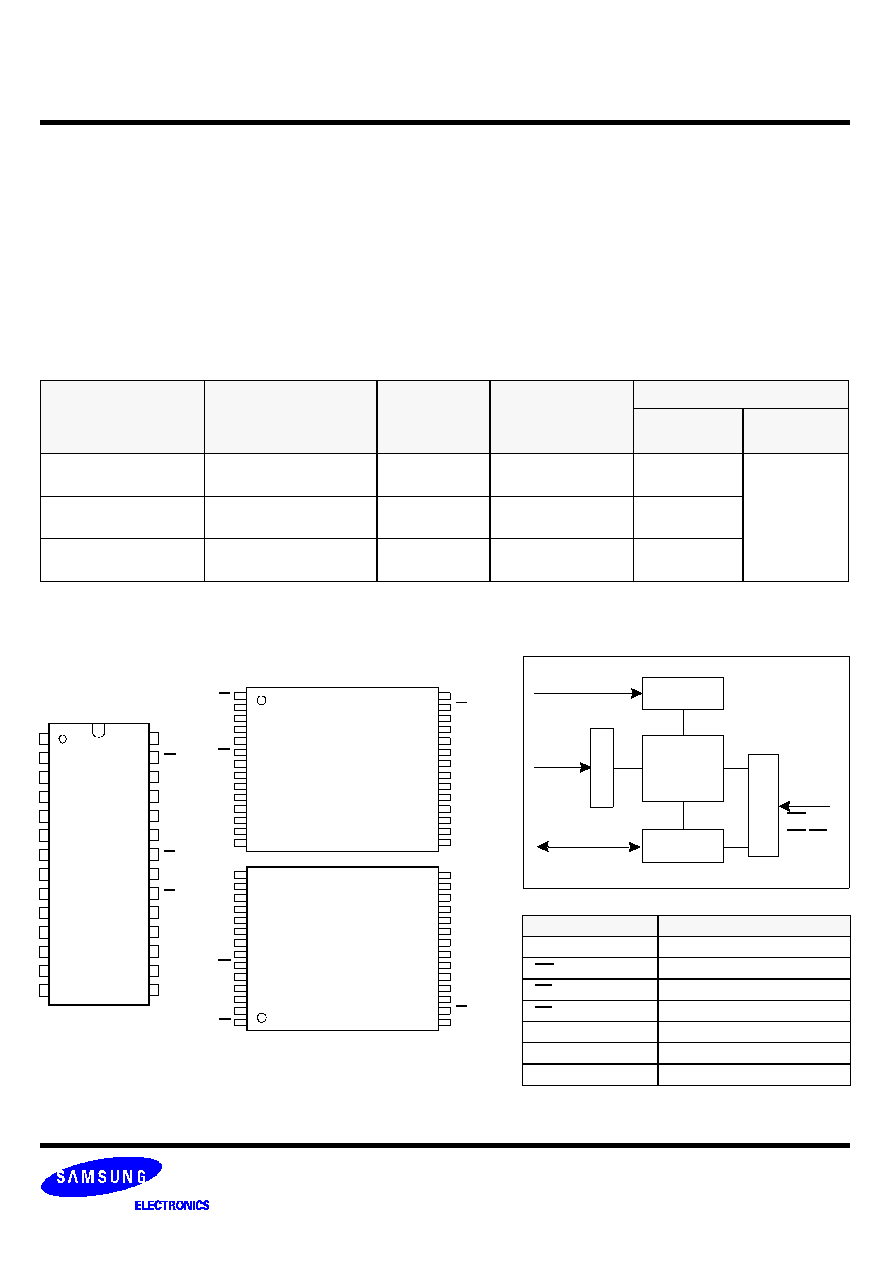

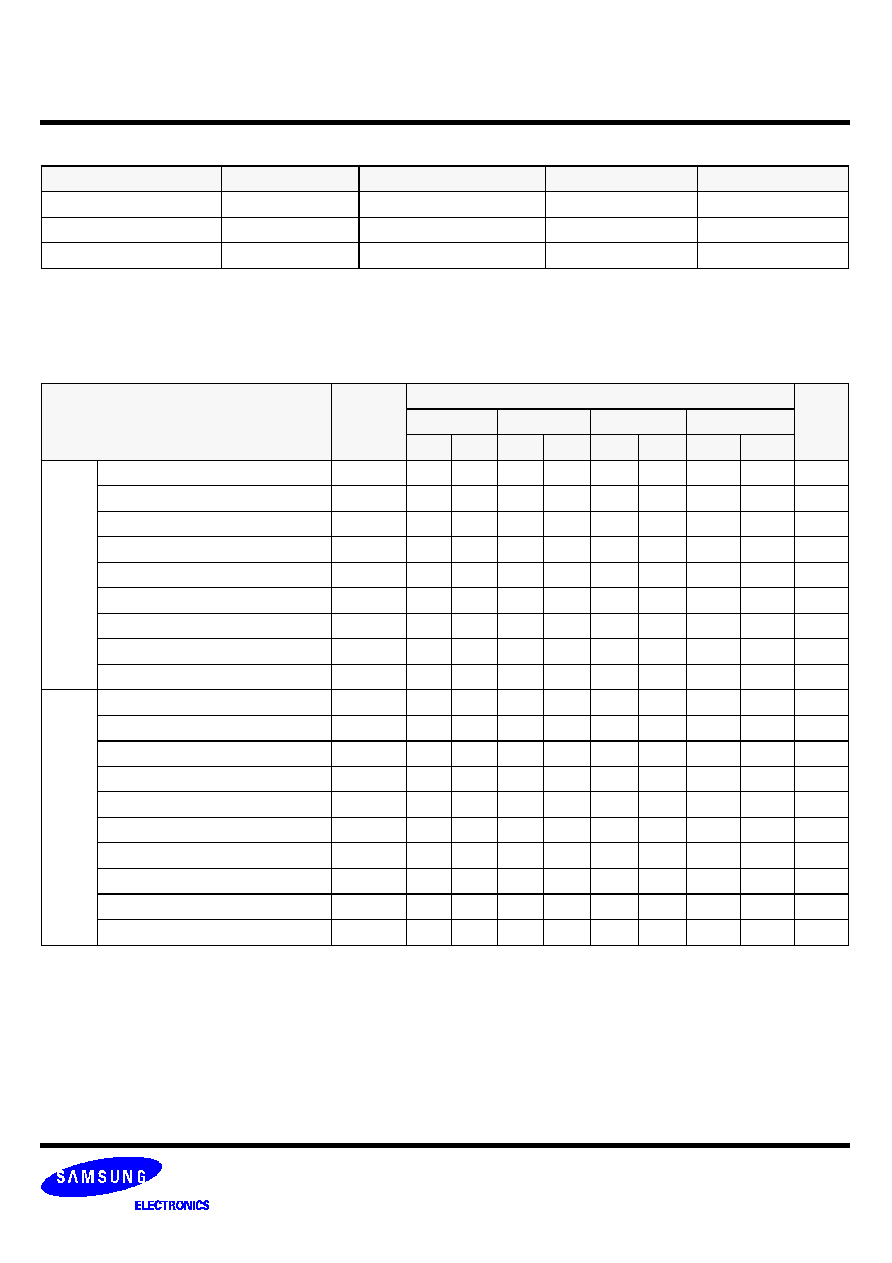

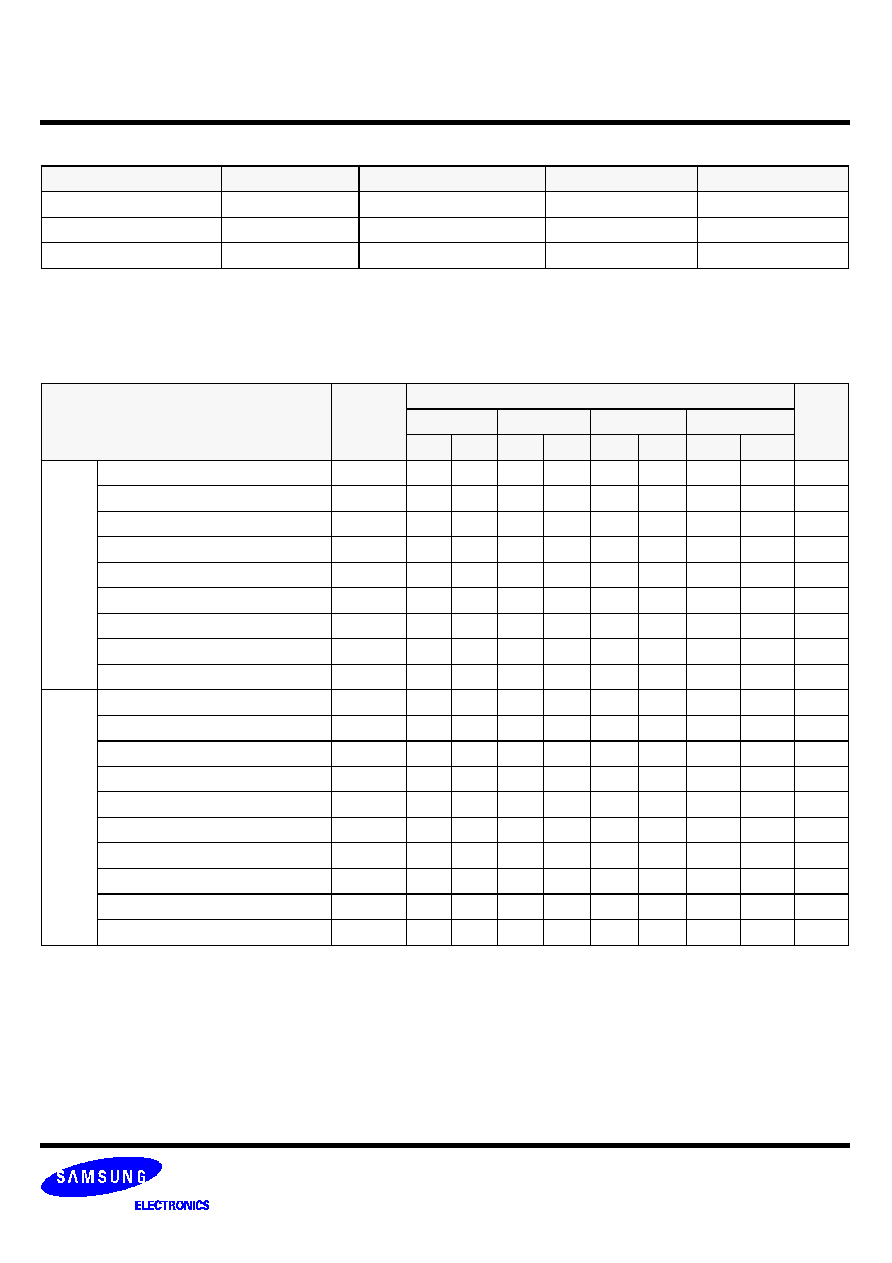

PRODUCT LIST & ORDERING INFORMATION

PRODUCT LIST

Commercial Temp Product

(0~70

°…

)

Extended Temp Products

(-25~85

°…

)

Industrial Temp Products

(-40~85

°…

)

Part Name

Function

Part Name

Function

Part Name

Function

KM62256CLP-4

KM62256CLP-4L

KM62256CLP-5

KM62256CLP-5L

KM62256CLP-7

KM62256CLP-7L

KM62256CLG-4

KM62256CLG-4L

KM62256CLG-5

KM62256CLG-5L

KM62256CLG-7

KM62256CLG-7L

KM62256CLTG-4

KM62256CLTG-4L

KM62256CLTG-5

KM62256CLTG-5L

KM62256CLTG-7

KM62256CLTG-7L

KM62256CLRG-4

KM62256CLRG-4L

KM62256CLRG-5

KM62256CLRG-5L

KM62256CLRG-7

KM62256CLRG-7L

28-DIP, 45ns, L-pwr

28-DIP, 45ns, LL-pwr

28-DIP, 55ns, L-pwr

28-DIP, 55ns, LL-pwr

28-DIP, 70ns, L-pwr

28-DIP, 70ns, LL-pwr

28-SOP, 45ns, L-pwr

28-SOP, 45ns, LL-pwr

28-SOP, 50ns, L-pwr

28-SOP, 50ns, LL-pwr

28-SOP, 70ns, L-pwr

28-SOP, 70ns, LL-pwr

28-TSOP F, 45ns, L-pwr

28-TSOP F, 45ns, LL-pwr

28-TSOP F, 55ns, L-pwr

28-TSOP F, 55ns, LL-pwr

28-TSOP F, 70ns, L-pwr

28-TSOP F, 70ns, LL-pwr

28-TSOP R, 45ns, L-pwr

28-TSOP R, 45ns, LL-pwr

28-TSOP R, 55ns, L-pwr

28-TSOP R, 55ns, LL-pwr

28-TSOP R, 70ns, L-pwr

28-TSOP R, 70ns, LL-pwr

KM62256CLGE-7

KM62256CLGE-7L

KM62256CLGE-10

KM62256CLGE-10L

KM62256CLTGE-7

KM62256CLTGE-7L

KM62256CLTGE-10

KM62256CLTGE-10L

KM62256CLRGE-7

KM62256CLRGE-7L

KM62256CLRGE-10

KM62256CLRGE-10L

28-SOP, 70ns, L-pwr

28-SOP, 70ns, LL-pwr

28-SOP, 100ns, L-pwr

28-SOP, 100ns, LL-pwr

28-TSOP F, 70ns, L-pwr

28-TSOP F, 70ns, LL-pwr

28-TSOP F, 100ns, L-pwr

28-TSOP F, 100ns, LL-pwr

28-TSOP R, 70ns, L-pwr

28-TSOP R, 70ns, LL-pwr

28-TSOP R, 100ns, L-pwr

28-TSOP R, 100ns, LL-pwr

KM62256CLGI-7

KM62256CLGI-7L

KM62256CLGI-10

KM62256CLGI-10L

KM62256CLTGI-7

KM62256CLTGI-7L

KM62256CLTGI-10

KM62256CLTGI-10L

KM62256CLRGI-7

KM62256CLRGI-7L

KM62256CLRGI-10

KM62256CLRGI-10L

28-SOP, 70ns, L-pwr

28-SOP, 70ns, LL-pwr

28-SOP, 100ns, L-pwr

28-SOP, 100ns, LL-pwr

28-TSOP F, 70ns, L-pwr

28-TSOP F, 70ns, LL-pwr

28-TSOP F, 100ns, L-pwr

28-TSOP F, 100ns, LL-pwr

28-TSOP R, 70ns, L-pwr

28-TSOP R, 70ns, LL-pwr

28-TSOP R, 100ns, L-pwr

28-TSOP R, 100ns, LL-pwr

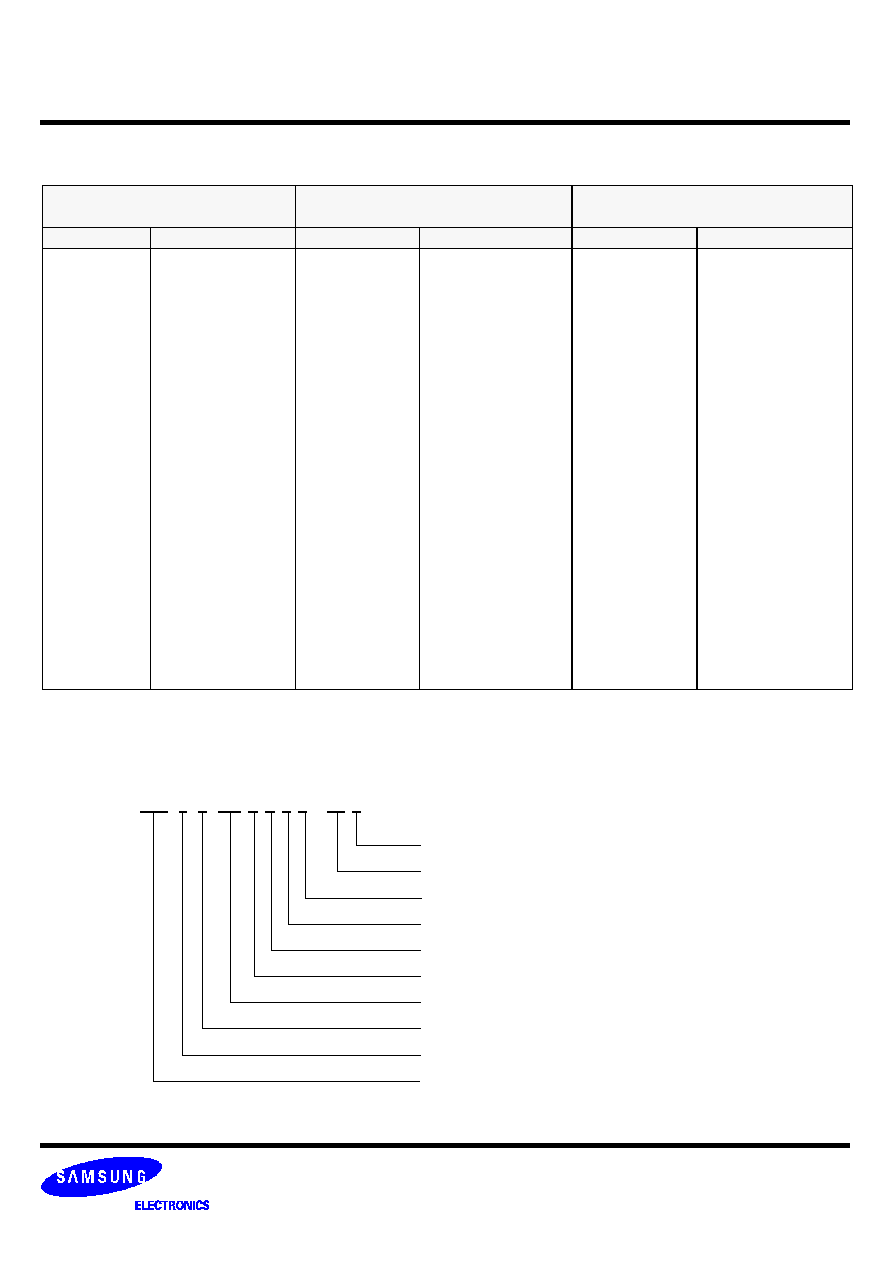

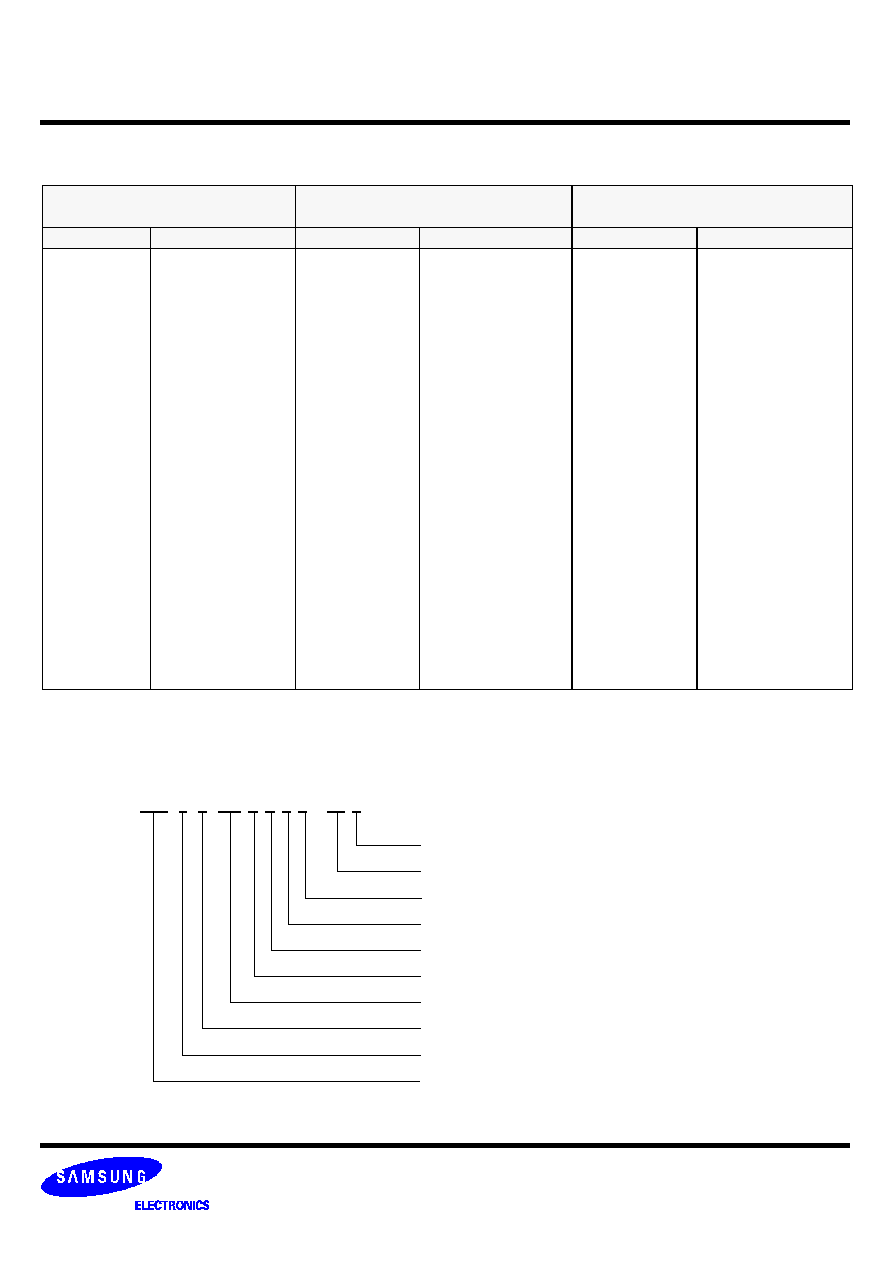

ORDERING INFORMATION

KM6 2 X 256 C X X X - XX X

L-Low Low Power, Blank-Low Power or High Power

Access Time : 4=45ns, 5=55ns, 7=70ns, 10=100ns

Operating temperature : Blank=Commercial, I=Industrial, E=Extended

Package Type : G=SOP, P=DIP, TG=TSOP Forward, RG=TSOP Reverse

L-Low Power or Low Low Power, Blank-High Power

Die Version : C=4th generation

Density : 256=256K bit

Blank=5V, V=3.0~3.6V, U=2.7~3.3V

Organization : 2=x8

SEC Standard SRAM

PRELIMINARY

Revision 3.0

KM62256C Family

CMOS SRAM

April 1996

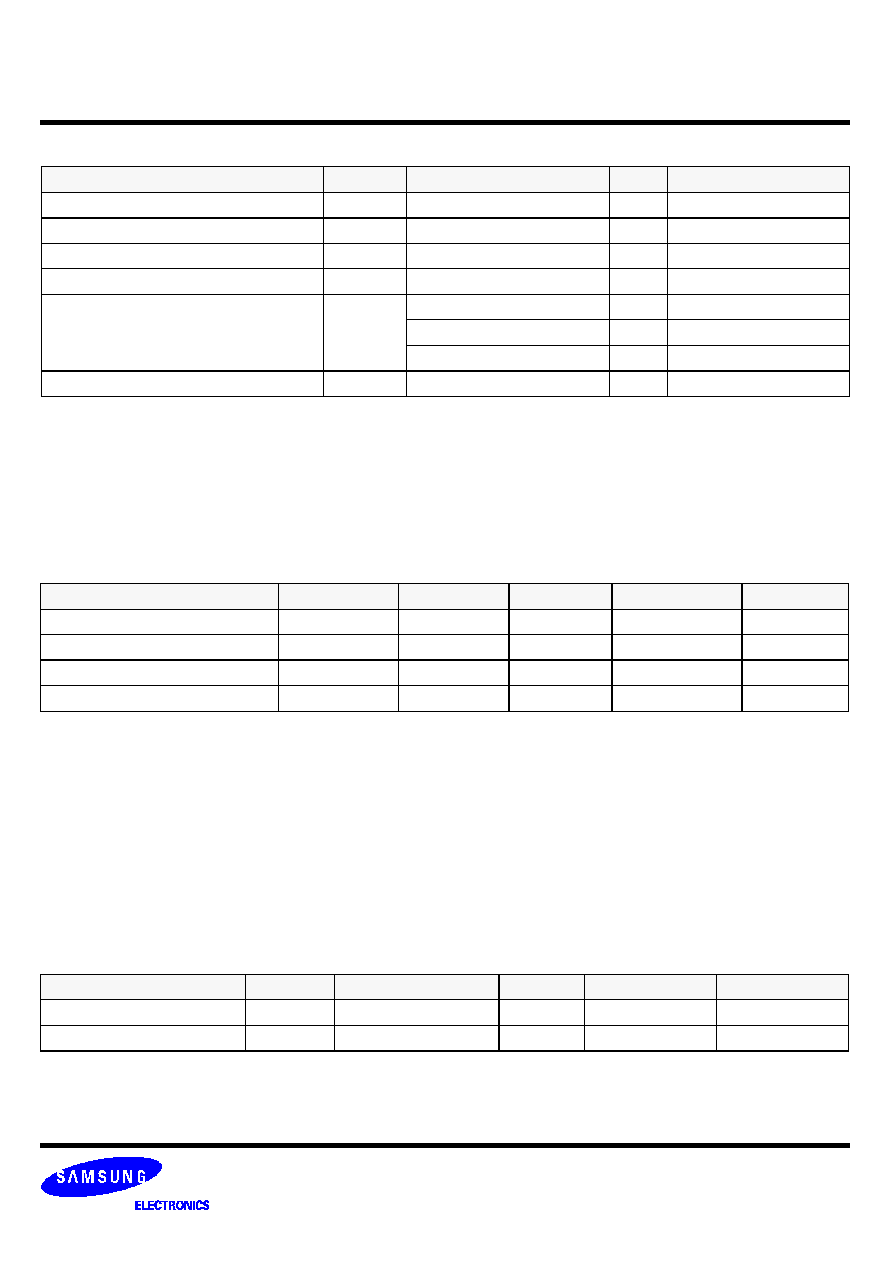

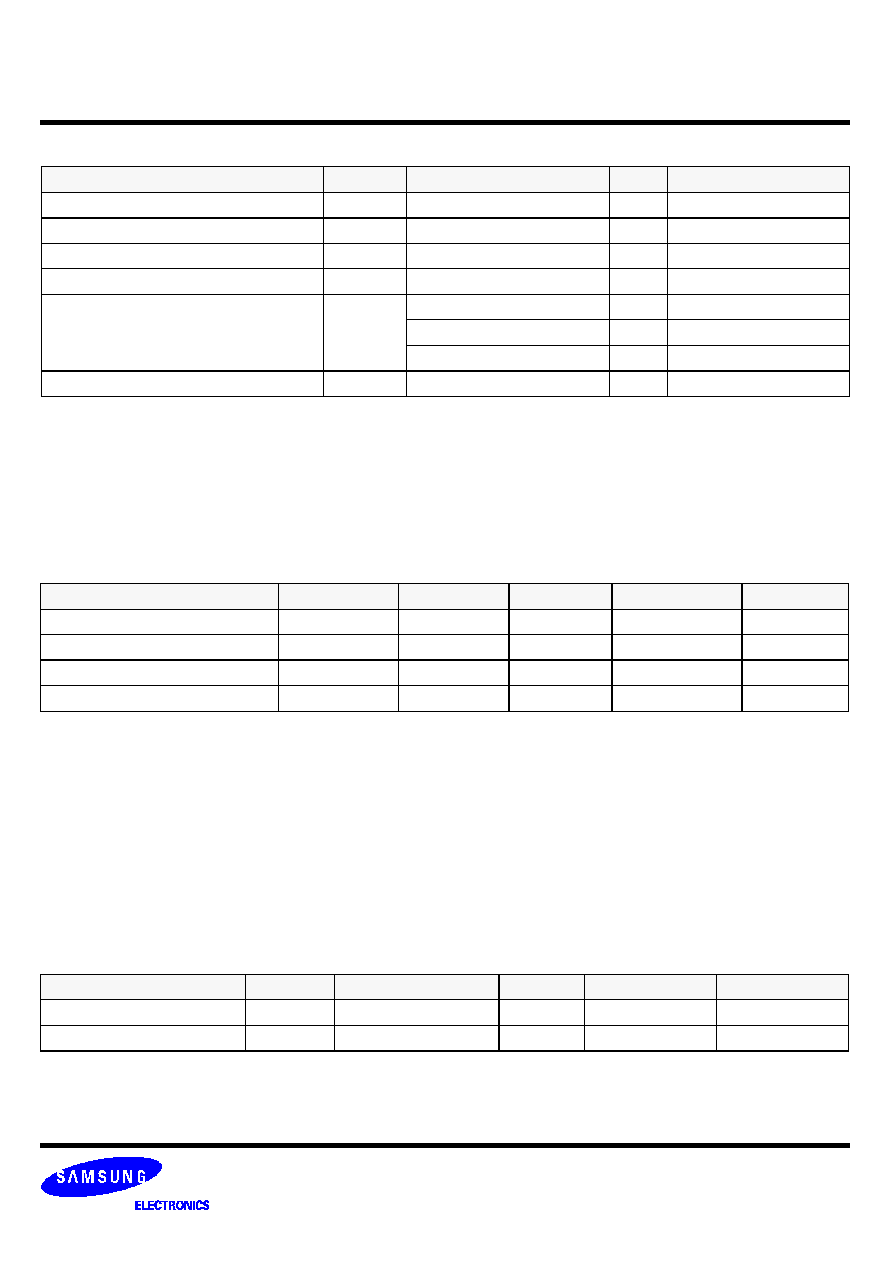

ABSOLUTE MAXIMUM RATINGS

*

* Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stres s rating only and functional operation of

the device at these or any other conditions above those indicated in the operating section of this specification is not impl ied. Exposure to absolute maximum rating conditions

for extended periods may affect reliability.

Item

Symbol

Ratings

Unit

Remark

Voltage on any pin relative to Vss

V

IN

,V

OUT

-0.5 to V

CC

+0.5

V

-

Voltage on Vcc supply relative to Vss

V

CC

-0.5 to 7.0

V

-

Power Dissipation

P

D

1.0

W

-

Storage temperature

T

STG

-65 to 150

°…

-

Operating Temperature

T

A

0 to 70

°…

KM62256CL/L-L

-25 to 85

°…

KM62256CLE/LE-L

-40 to 85

°…

KM62256CLI/LI-L

Soldering temperature and time

T

SOLDER

260

°…

, 10sec (Lead Only)

-

-

RECOMMENDED DC OPERATING CONDITIONS

*

* 1) Commercial Product : T

A

=0 to 70

°…

, unless otherwise specified

2) Extended Product : T

A

=-25 to 85

°…

, unless otherwise specified

3) Industrial Product : T

A

=-40 to 85

°…

, unless otherwise specified

** T

A

=25

°…

*** V

IL

(min)=-3.0V for

°¬

50ns pulse width

Item

Symbol

Min

Typ**

Max

Unit

Supply voltage

Vcc

4.5

5.0

5.5

V

Ground

Vss

0

0

0

V

Input high voltage

V

IH

2.2

-

Vcc+0.5V

V

Input low voltage

V

IL

-0.5***

-

0.8

V

CAPACITANCE*

(f=1MHz, T

A

=25

°…

)

* Capacitance is sampled not 100% tested

Item

Symbol

Test Condition

Min

Max

Unit

Input capacitance

C

IN

V

IN

=0V

-

6

pF

Input/Output capacitance

C

IO

V

IO

=0V

-

8

pF

PRELIMINARY

Revision 3.0

KM62256C Family

CMOS SRAM

April 1996

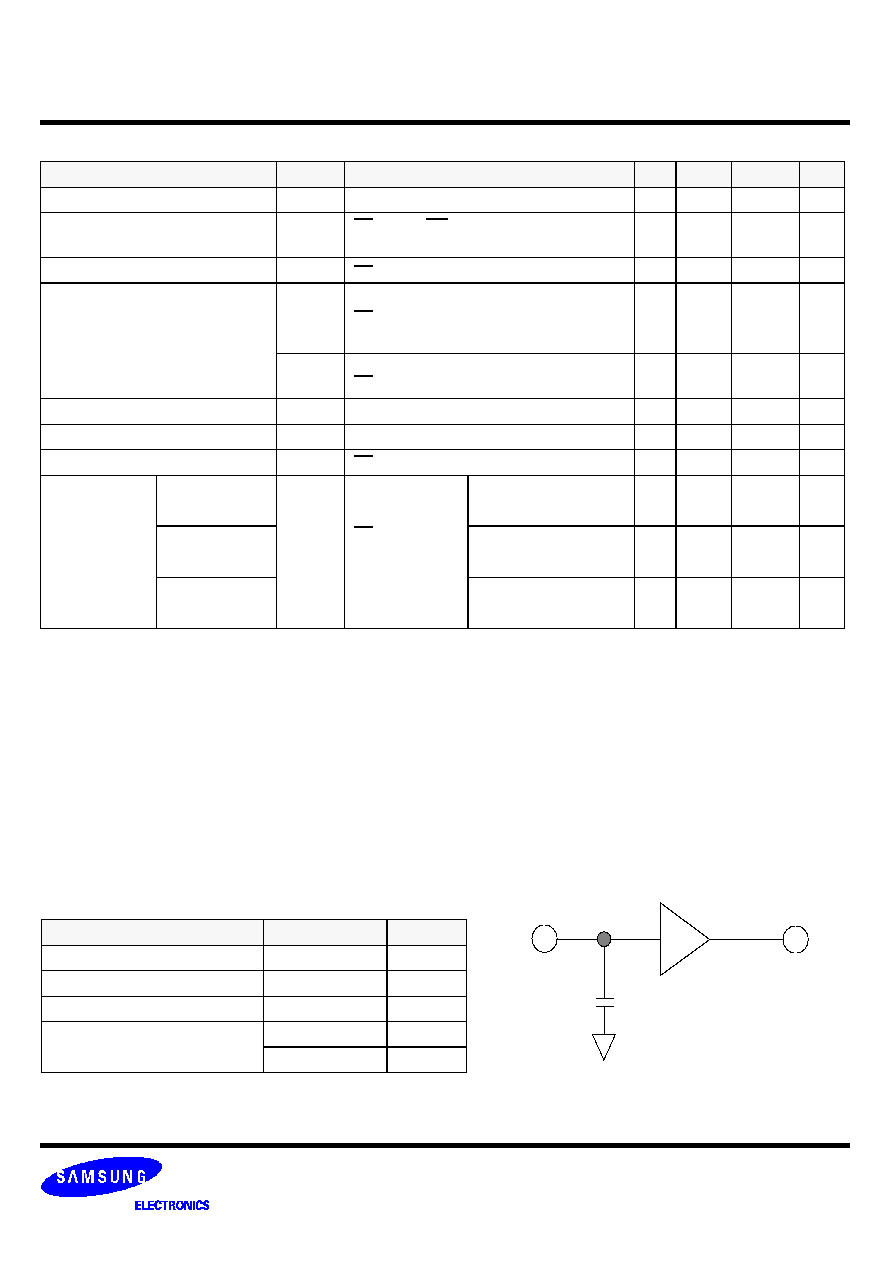

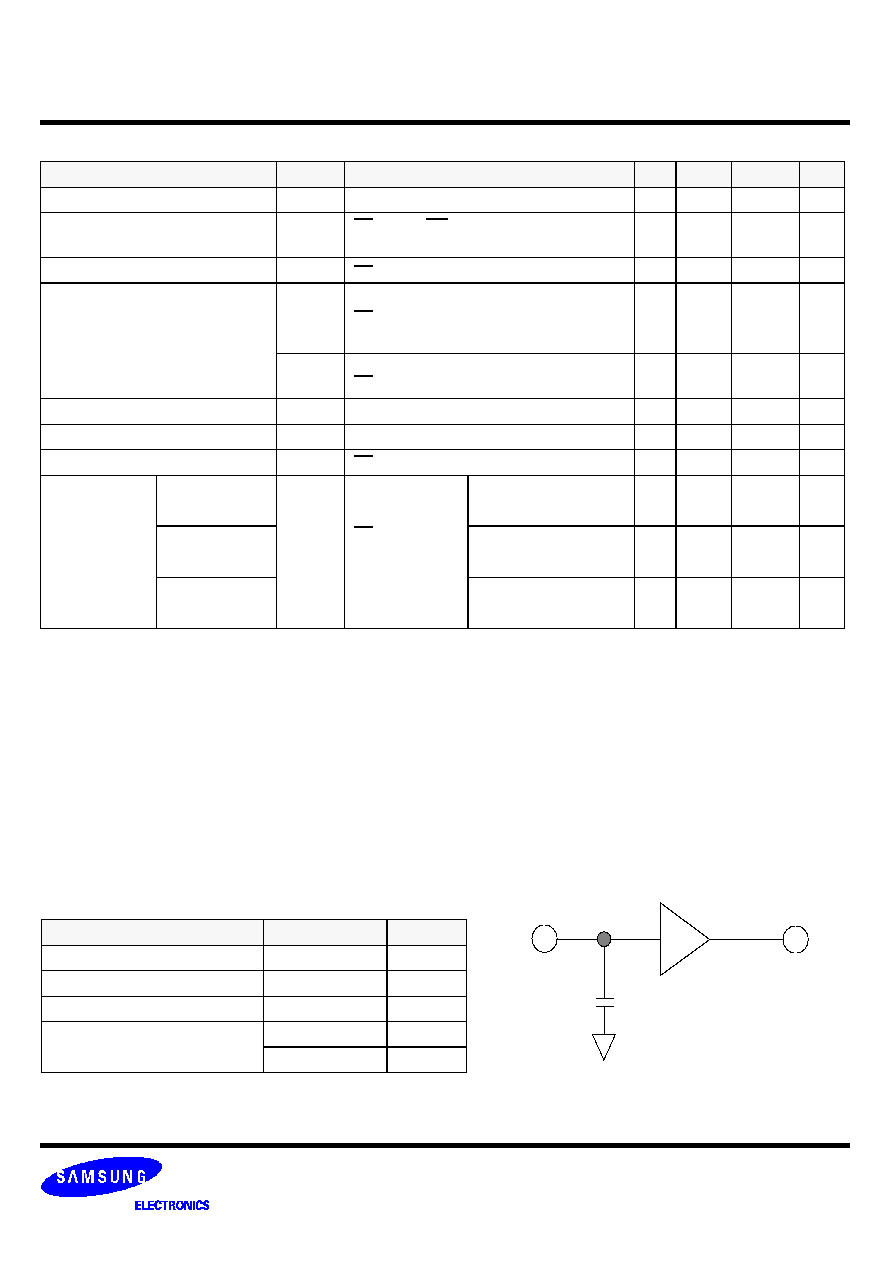

DC AND OPERATING CHARACTERISTICS

* 1) Commercial Product : T

A

=0 to 70

°…

, Vcc=5V

°æ

10% unless otherwise specified

2) Extended Product : T

A

=-25 to 85

°…

, Vcc=5V

°æ

10% nless otherwise specified

3) Industrial Product : T

A

=-40 to 85

°…

, Vcc=5V

°æ

10% unless otherwise specified

** T

A

=25

°…

*** 20mA for Extended and Industrial Products

****10mA for Extended and Industrial Products

*****2mA for Extended and Industrial Products

Item

Symbol

Test Conditions*

Min

Typ**

Max

Unit

Input leakage current

I

LI

V

IN

=Vss to Vcc

-1

-

1

ßÀ

Output leakage current

I

LO

CS=V

IH

or

WE=V

IL

V

IO

=Vss to Vcc

-1

-

1

ßÀ

Operating power supply current

I

CC

CS=V

IL

,

V

IN

=V

IH

or V

IL

, I

IO

=0mA

-

7

15***

mA

Average operating current

I

CC1

Cycle time=1

ß¡

100% duty

CS

°¬

0.2V,

V

IL

°¬

0.2V

V

IN

°√

Vcc -0.2V, I

IO

=0mA

-

-

7****

mA

I

CC2

Min cycle, 100% duty

CS=V

IL

, I

IO

=0mA

-

-

70

mA

Output low voltage

V

OL

I

OL

=2.1mA

-

-

0.4

V

Output high voltage

V

OH

I

OH

=-1.0mA

2.4

-

-

V

Standby Current(TTL)

I

SB

CS=V

IH

-

-

1*****

mA

Standby Current

(CMOS)

KM62256CL

KM62256CL-L

I

SB1

CS

°√

Vcc-0.2V

V

IN

°√

0.2V or

V

IN

°¬

V

CC

-0.2V

L(Low Power)

LL(L Low Power)

-

-

2

1

100

20

ßÀ

ßÀ

KM62256CLE

KM62256CLE-L

L(Low Power)

LL(L Low Power)

-

-

-

-

100

50

ßÀ

ßÀ

KM62256CLI

KM62256CLI-L

L(Low Power)

LL(L Low Power)

-

-

-

-

100

50

ßÀ

ßÀ

TEST CONDITIONS

(1.Test Load and Test Input/Output Reference)*

* See DC Operating conditions

** Test load for 45ns commercial products

Item

Value

Remark

Input pulse level

0.8 to 2.4V

-

Input rising & falling time

5ns

-

input and output reference voltage

1.5V

-

Output load (See right)

C

L

=100pF+1TTL

-

**C

L

=30pF+1TTL

-

A.C CHARACTERISTICS

C

L

*

* Including scope and jig capacitance

PRELIMINARY

Revision 3.0

KM62256C Family

CMOS SRAM

April 1996

TEST CONDITIONS

(2. Temperature and Vcc Conditions)

* The parameter is measured with 30pF test load

Product Family

Temperature

Power Supply(Vcc)

Speed Bin

Comments

KM62256CL/L-L

0~70

°…

5V

°æ

10%

45*/55/70ns

Commercial

KM62256CLE/LE-L

-25~85

°…

5V

°æ

10%

70/100ns

Extended

KM62256CLI/LI-L

-40~85

°…

5V

°æ

10%

70/100ns

Industrial

PARAMETER LIST FOR EACH SPEED BIN

* The parameter is measured with 30pF test load

Parameter List

Symbol

Speed Bins

Units

45ns*

55ns

70ns

100ns

Min

Max

Min

Max

Min

Max

Min

Max

Read

Read cycle time

t

RC

45

-

55

-

70

-

100

-

ns

Address access time

t

AA

-

45

-

55

-

70

-

100

ns

Chip select to output

t

CO

-

45

-

55

-

70

-

100

ns

Output enable to valid output

t

OE

-

25

-

25

-

35

-

50

ns

Chip select to low-Z output

t

LZ

10

-

10

-

10

-

10

-

ns

Output enable to low-Z output

t

OLZ

5

-

5

-

5

-

5

-

ns

Chip disable to high-Z output

t

HZ

0

20

0

20

0

30

0

35

ns

Output disable to high-Z output

t

OHZ

0

20

0

20

0

30

0

35

ns

Output hold from address change

t

OH

5

-

5

-

5

-

5

-

ns

Write

Write cycle time

t

WC

45

-

55

-

70

-

100

-

ns

Chip select to end of write

t

CW

45

-

45

-

60

-

80

-

ns

Address set-up time

t

AS

0

-

0

-

0

-

0

-

ns

Address valid to end of write

t

AW

45

-

45

-

60

-

80

-

ns

Write pulse width

t

WP

40

-

40

-

50

-

60

-

ns

Write recovery time

t

WR

0

-

0

-

0

-

0

-

ns

Write to output high-Z

t

WHZ

0

20

0

20

0

25

0

35

ns

Data to write time overlap

t

DW

25

-

25

-

30

-

50

-

ns

Data hold from write time

t

DH

0

-

0

-

0

-

0

-

ns

End write to output low-Z

t

OW

5

-

5

-

5

-

5

-

ns