AM/FM 1CHIP TUNER WITH PLL

S1A0903X01

1

INTRODUCTION

∑

AM: AM RF MIXER, AM OSC,

AM_IF AMP, AM Detector,

AGC, Tuning LED Driver,

OSC Buffer, IF Buffer

∑

FM: RF AMP, FM RF MIXER,

FM OSC, FM_IF AMP,

Quadrature Detector,

Tuning LED Driver,

OSC Buffer, IF Buffer

∑

MPX: PLL, Stereo Decoder, Stereo LED, MPX VCO Self-adjustment

∑

DTS : Prescaler, AM/FM Programmable Divider, AM/FM IF Counter, Lock Detector, LED Controller

∑

Microprocessor Interface

FEATURE

∑

Adopt New FCC

∑

AM/FM 1 Chip DTS with PLL

∑

MPX-VCO Self-adjustment

∑

Programmable Divider

FM: 10 to 160MHz <pulse swallow technique>

AM: 0.5 to 10MHz <direct division technique>

∑

IF COUNTER : 0.4 to 12MHz <AM/FM IF COUNTING>

∑

Reference Frequency

Twelve Selectable Frequency

1, 3, 5, 9, 10, 3.125, 6.25, 12.5, 15, 25, 50, and 100kHz

(Selectable Crystal 75kHz, 3.6MHz, 7.2MHz, 10.8MHz choice)

∑

Built-in Transistor for forming an active low-pass filter

∑

Package : 44 QFP/48 LQFP

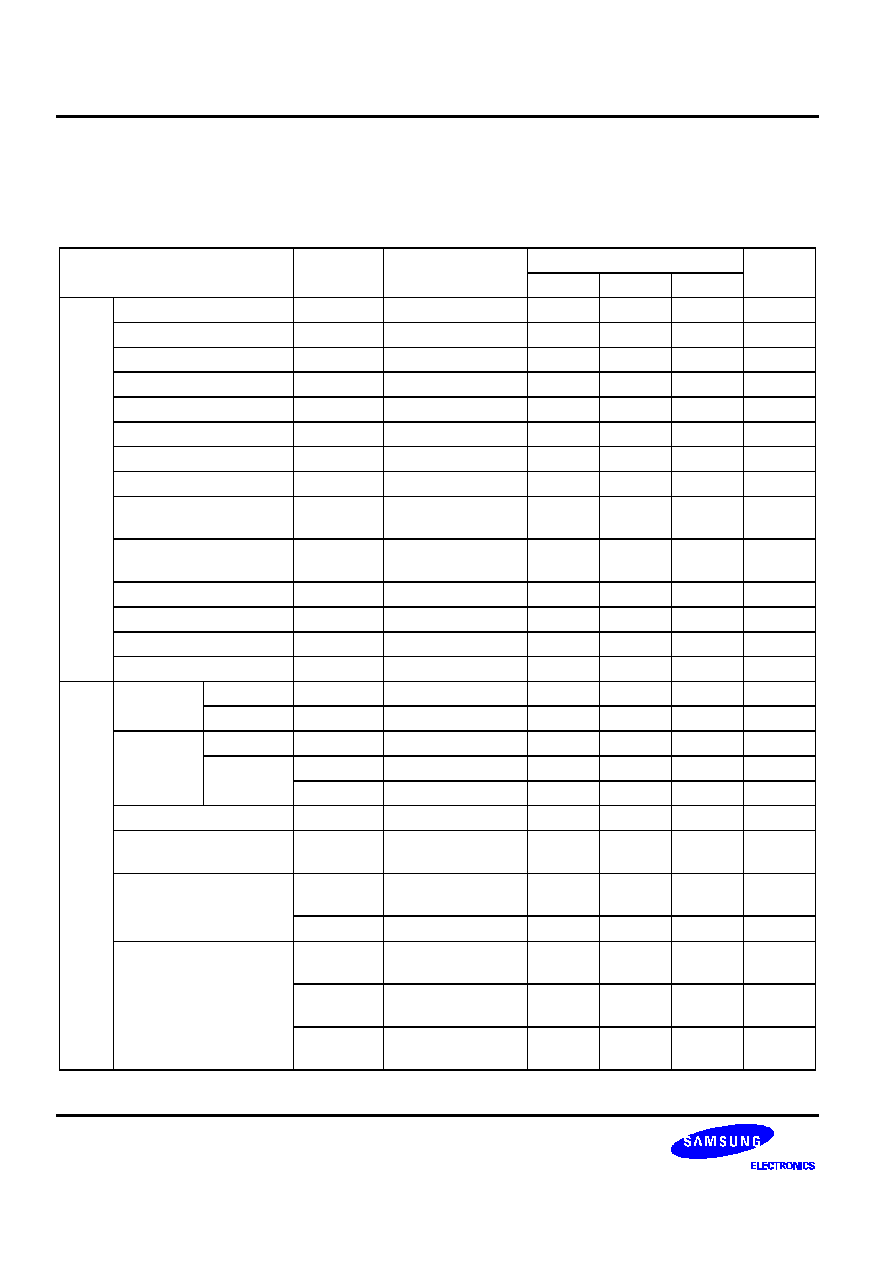

ORDERING INFORMATION

Device

Package

Supply voltage

Operating Temperature

S1A0903X01-Q0R0

44-QFP-1010B

2 to 7V

-20 to +75

∞

C

S1A0903X01-E0R0

48-LQFP-0707AN

44-QFP-1010B

S1A0903X01

AM/FM 1CHIP TUNER WITH PLL

2

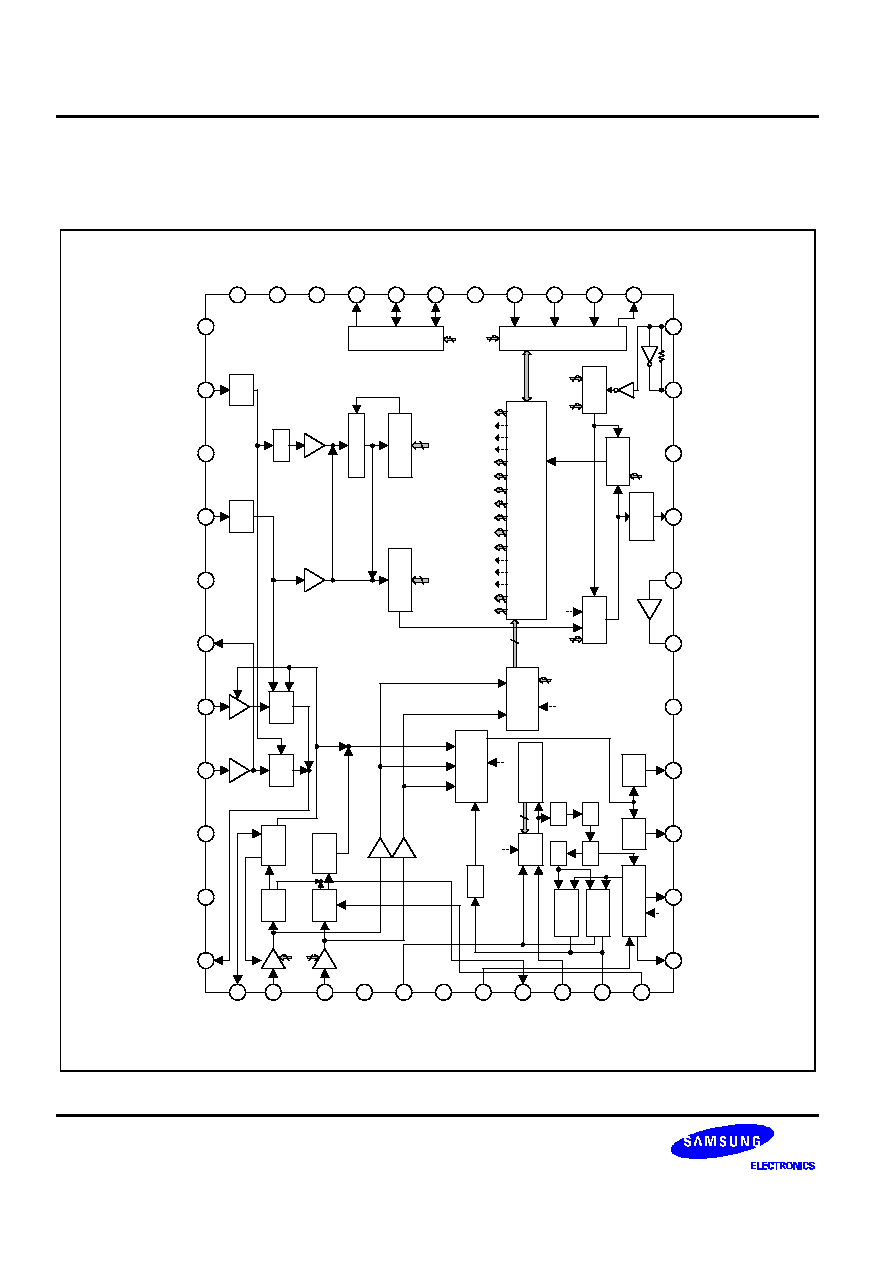

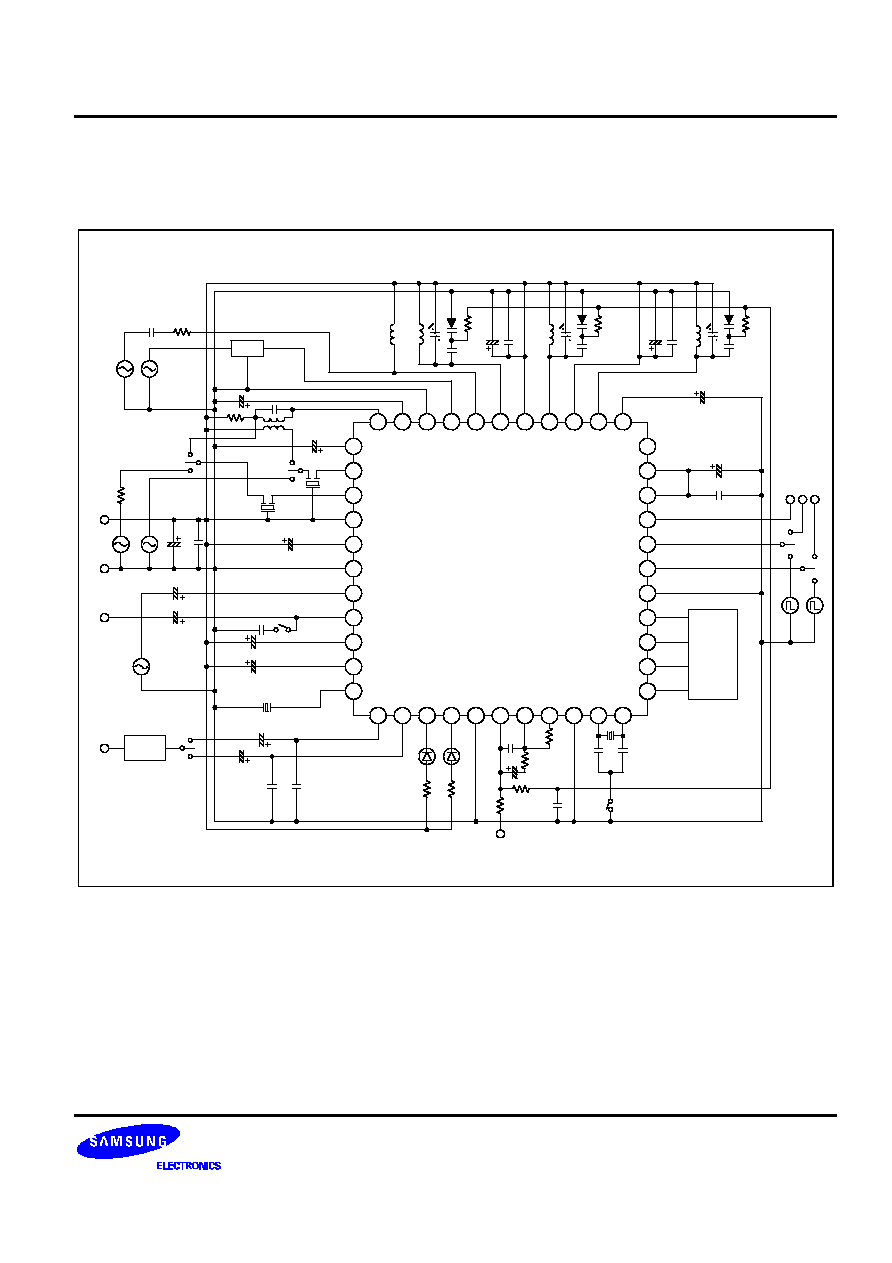

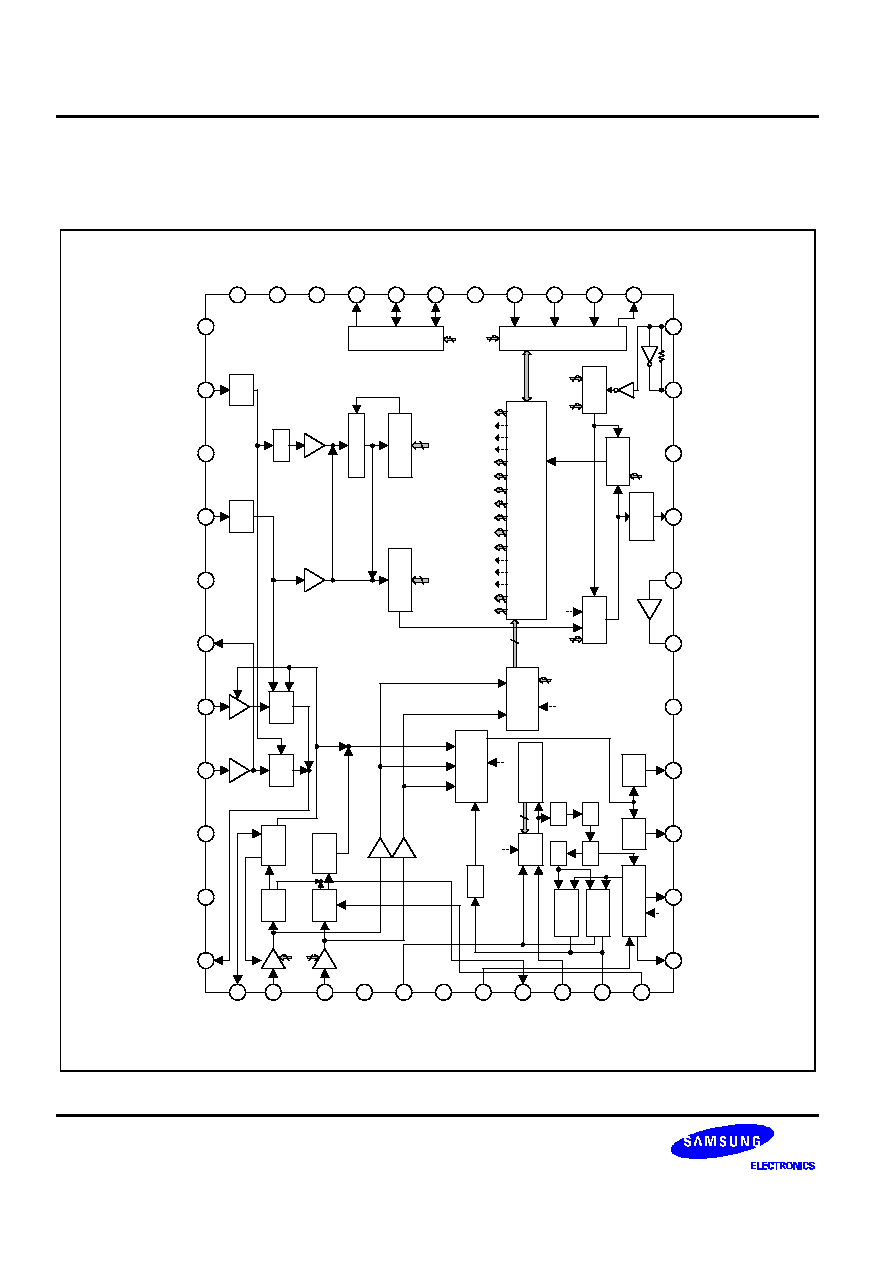

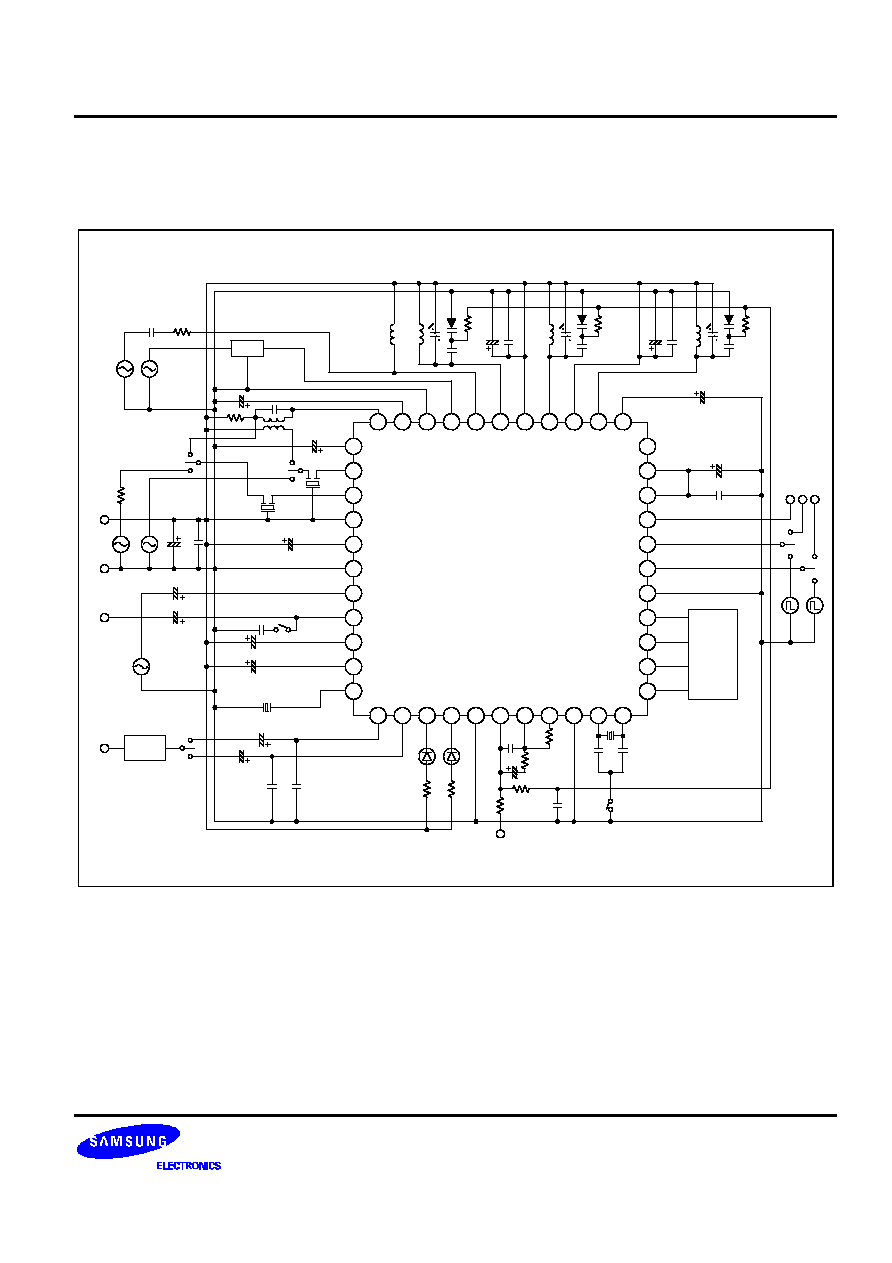

BLOCK DIAGRAM

44-QFP

LOUT

ROUT

TUNLED

STLED

VSSA

AOUT

AIN

PD

VSSX

XOUT

XIN

MIXOUT

AMLOWCUT

GND_RF

FMRFIN

AMRFIN

FMRFOUT

VCC_RF

AMOSC

VDDA

FMOSC

VCDC

IO[20:0]

IF[18:0]

R[3:0]

N[3:0]

N[16:4]

UL[1:0]

XS[1:0]

GT[1:0]

TEST[1:0]

DZ[1:0]

DLC

DOC[1:0]

IFCS

VREG

TEST3

NC

VDD

TEST2

TEST1

VSSD

CE

DI

CL

DO

PD[6:0]

MUTE

IFS[1:0]

MOST

TUNLEDC

AMIFIN

VCC

AGCCAP

FMIFIN

DETOUT

GND

MPXIN

LPF1

LPF2

LPF3

FMQUAD

34

35

36

37

38

39

40

41

42

43

44

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

A

A

AM

DET

AGC

FM

DET

LEVEL

DET

FM

MIX

AM

MIX

A

A

AM

OSC

B

FM

OSC

1/2

B

B

B

HYS

LED

CONTROL

IF

COUNTER

VCO

MPX VCO

CONTROL

PILOT

DET

PHASE

DET

F/F

F/F

F/F

F/F

DECODER

LED

DRV

LED

DRV

A

PRESCALER

MAIN

COUNTER

SWALLOW

COUNTER

PFD

DOC[1:0]

TEST[1:0]

DLC

TUNLEDC

MOST

OS[1:0]

XS[1:0]

R[3:0]

IFCS

MUTEC

MUTE

IFS[1:0]

GT[1:0]

DZ[1:0]

UL[1:0]

N[15:0]

DATA SHIFT REGISTER

CHARGE

PUMP

LOCK

DETECT

REF

DIVIDER

TEST CONTROL

SERIAL INTERFACE

AM/FM 1CHIP TUNER WITH PLL

S1A0903X01

3

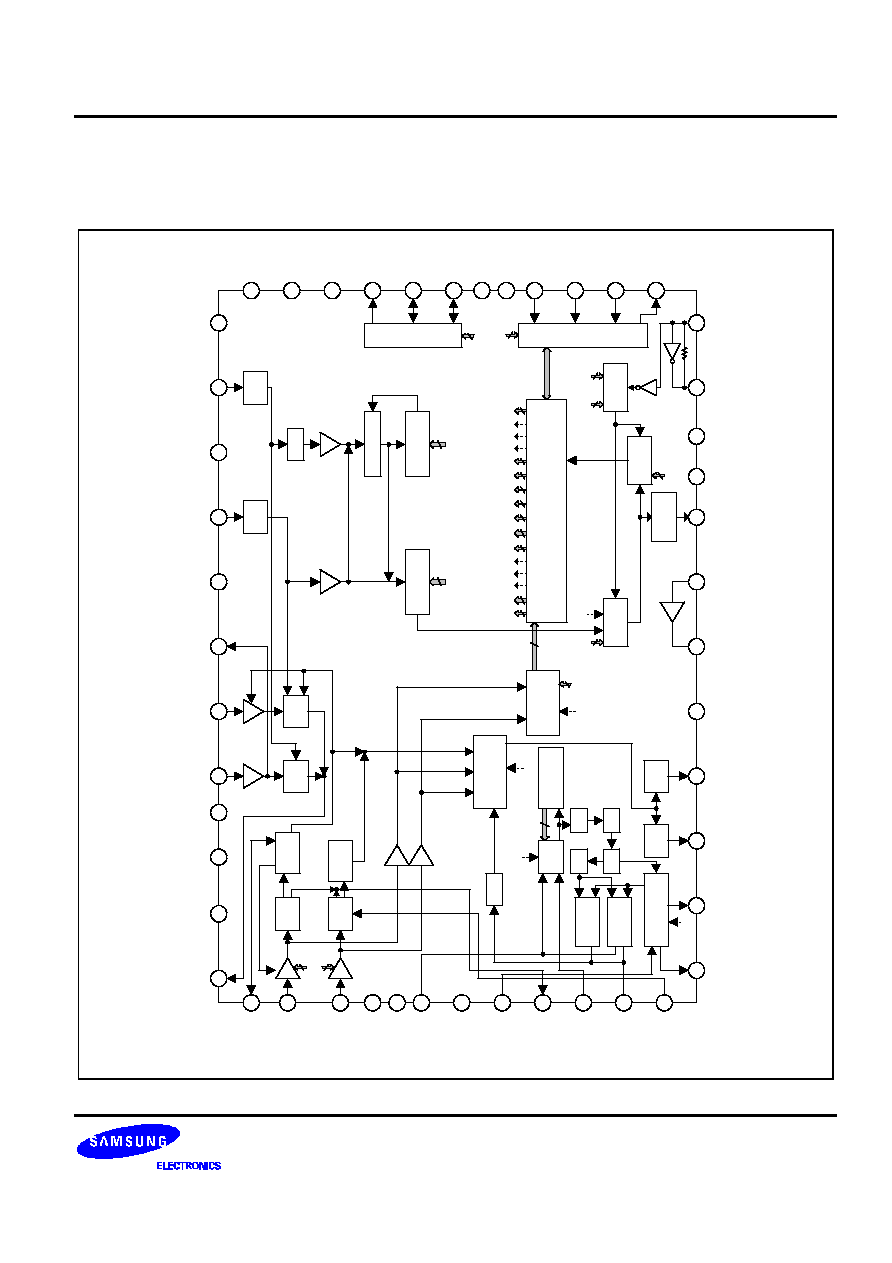

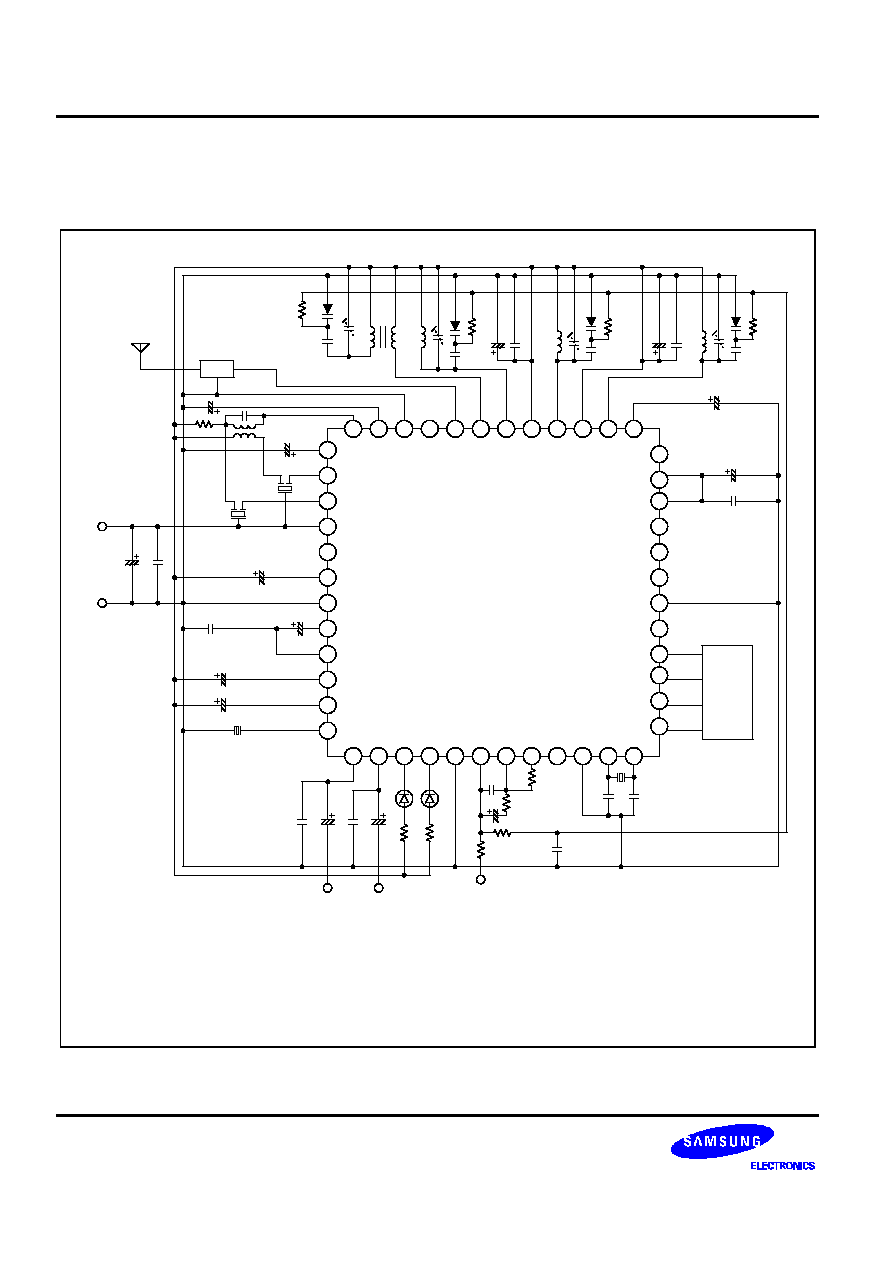

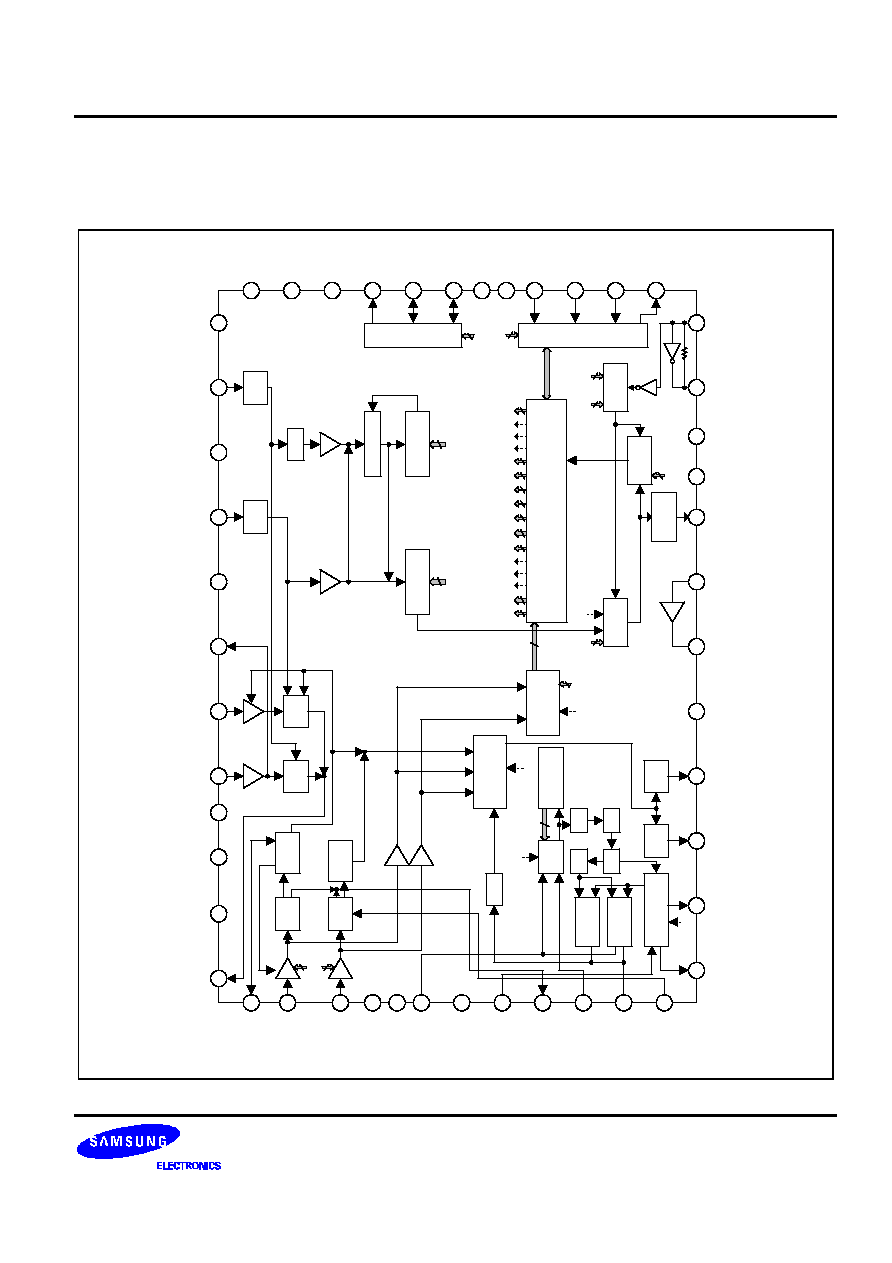

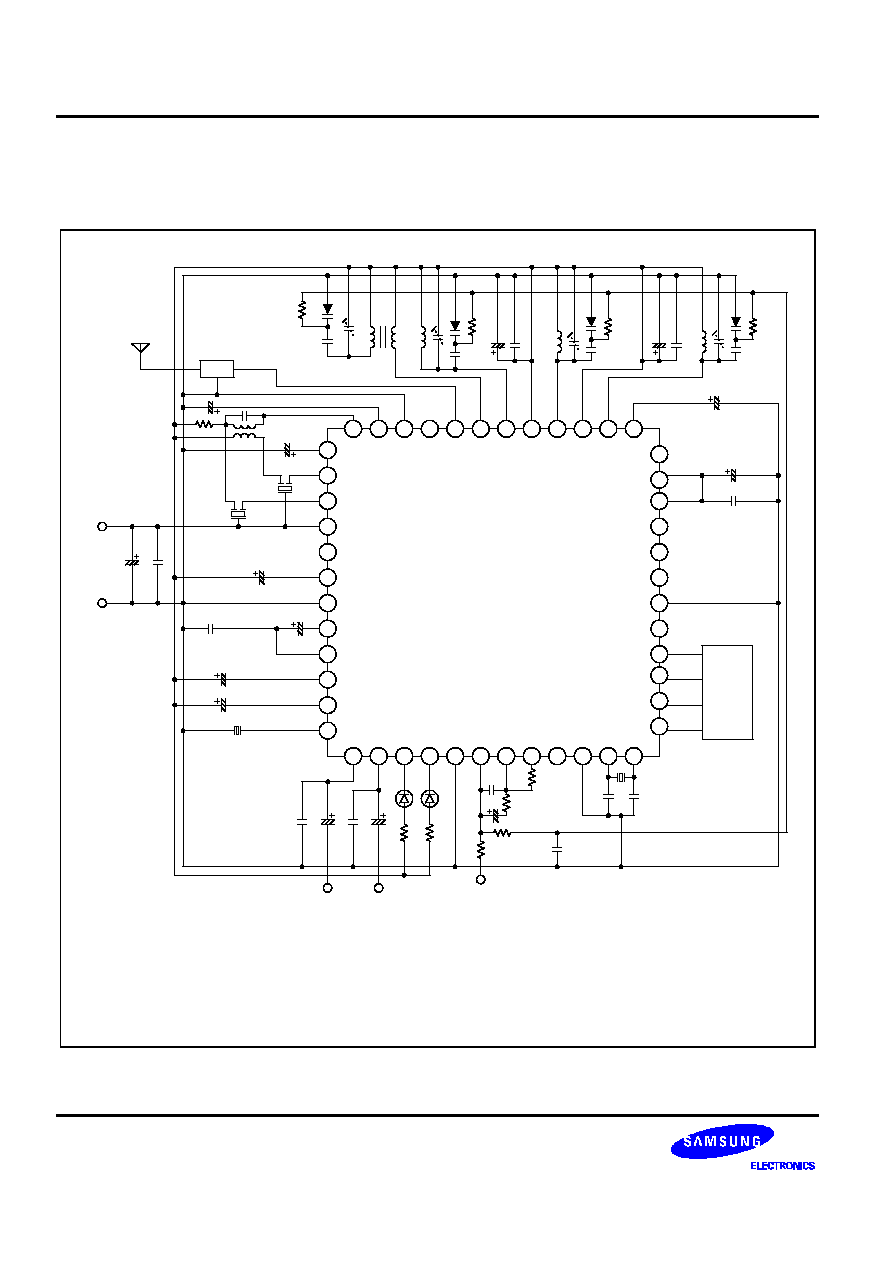

BLOCK DIAGRAM

48-LQFP

LOUT

ROUT

TUNLED

STLED

VSSA

AOUT

AIN

PD

VSSX

XOUT

XIN

MIXOUT

AMLOWCUT

GND_RF

FMRFIN

AMRFIN

FMRFOUT

VCC_RF

AMOSC

VDDA

FMOSC

VCDC

IO[20:0]

IF[18:0]

R[3:0]

N[3:0]

N[16:4]

UL[1:0]

XS[1:0]

GT[1:0]

TEST[1:0]

DZ[1:0]

DLC

DOC[1:0]

IFCS

VREG

TEST3

NC

VDD

TEST2

TEST1

VSSD

CE

DI

CL

DO

PD[6:0]

MUTE

IFS[1:0]

MOST

TUNLEDC

AMIFIN

VCC

AGCCAP

FMIFIN

DETOUT

GND

MPXIN

LPF1

LPF2

LPF3

FMQUAD

37

38

39

40

42

43

44

45

46

47

48

1

2

3

4

5

6

7

8

10

11

12

13

14

15

16

17

19

20

21

22

23

24

25

26

27

28

29

30

31

32

34

35

36

A

A

AM

DET

AGC

FM

DET

LEVEL

DET

FM

MIX

AM

MIX

A

A

AM

OSC

B

FM

OSC

1/2

B

B

B

HYS

LED

CONTROL

IF

COUNTER

VCO

MPX VCO

CONTROL

PILOT

DET

PHASE

DET

F/F

F/F

F/F

F/F

DECODER

LED

DRV

LED

DRV

A

PRESCALER

MAIN

COUNTER

SWALLOW

COUNTER

PFD

DOC[1:0]

TEST[1:0]

DLC

TUNLEDC

MOST

OS[1:0]

XS[1:0]

R[3:0]

IFCS

MUTEC

MUTE

IFS[1:0]

GT[1:0]

DZ[1:0]

UL[1:0]

N[15:0]

DATA SHIFT REGISTER

CHARGE

PUMP

LOCK

DETECT

REF

DIVIDER

TEST CONTROL

SERIAL INTERFACE

41

NC

9

NC

18

NC

33

NC

S1A0903X01

AM/FM 1CHIP TUNER WITH PLL

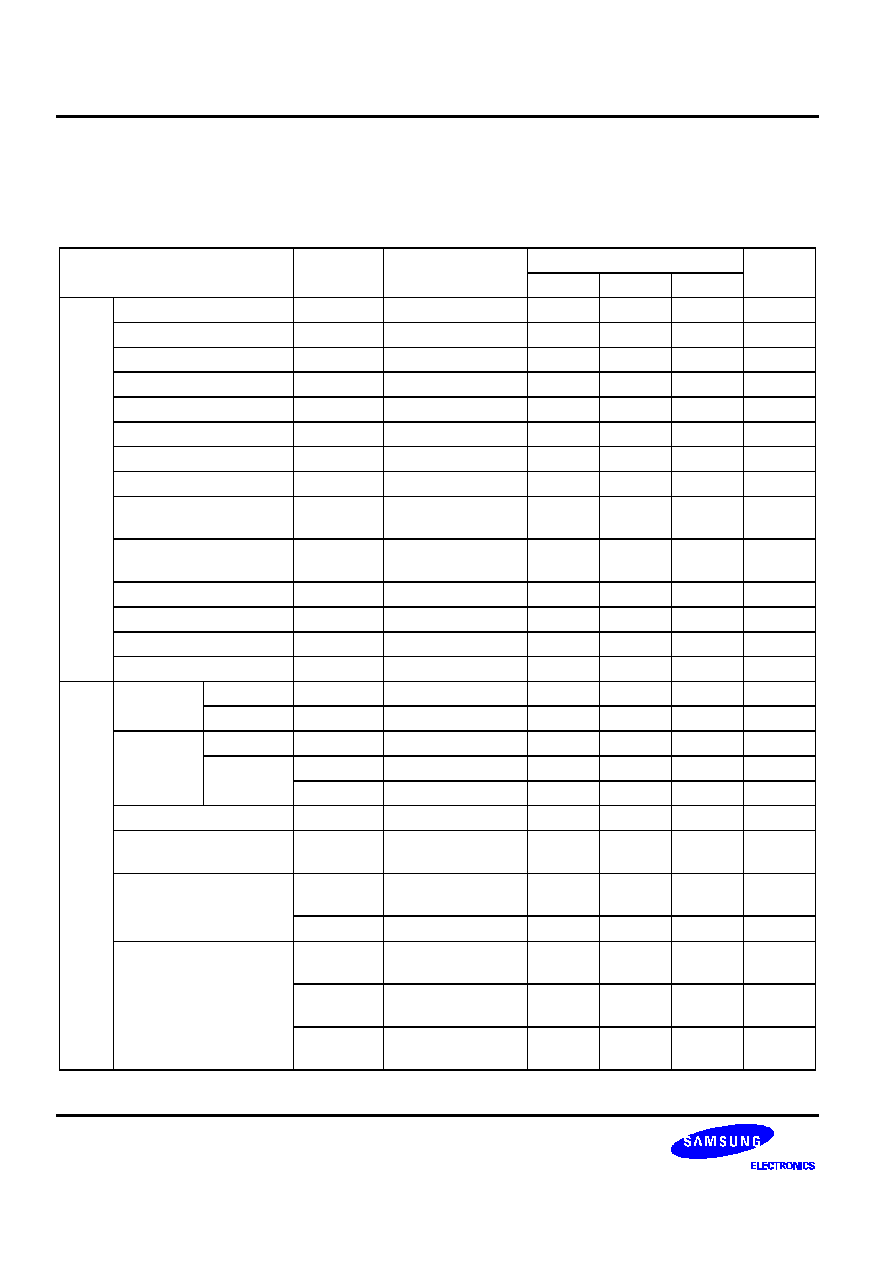

4

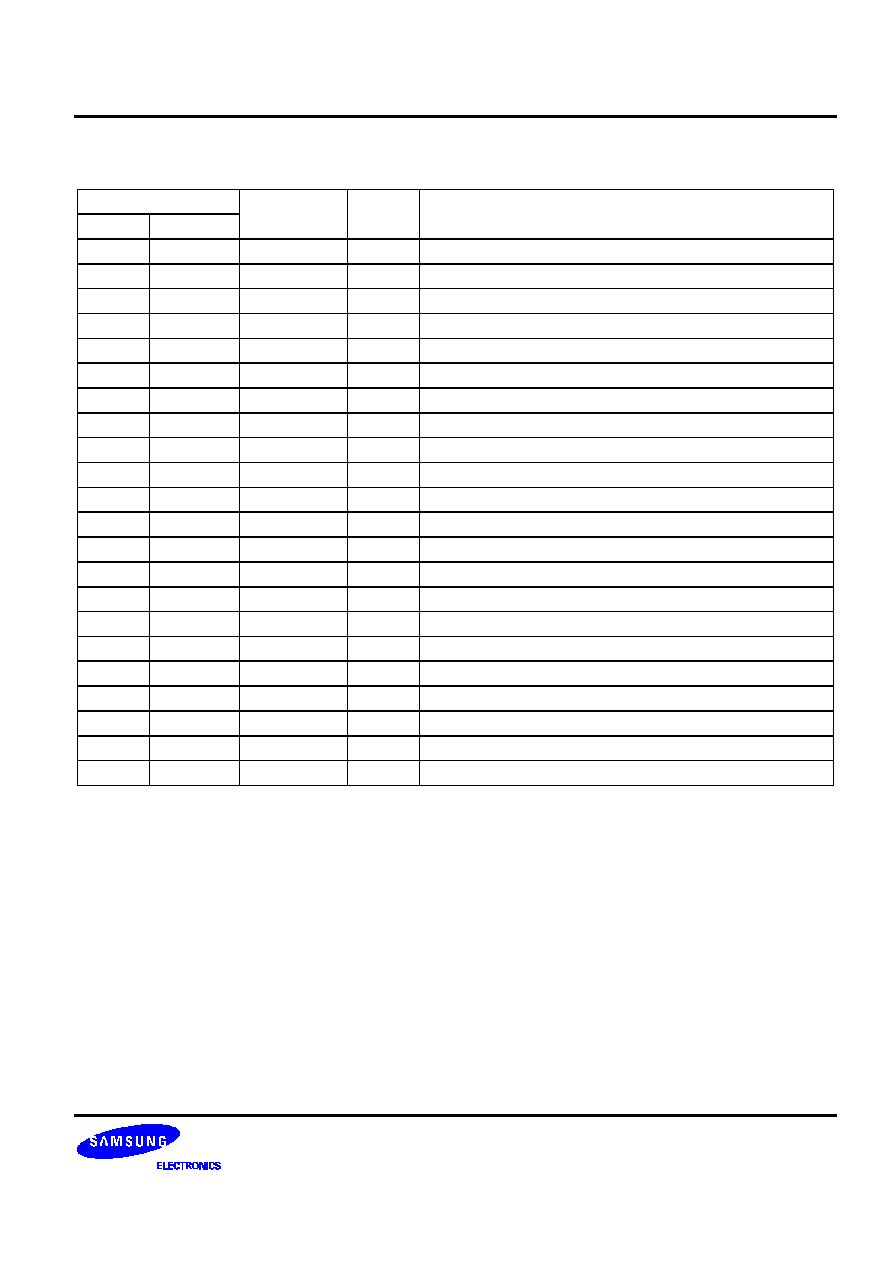

PIN CONFIGURATION

Pin No.

Symbol

In/Out

Function

44-QFP

48-LQFP

1

1

LOUT

O

Stereo left channel output

2

2

ROUT

O

Stereo right channel output

3

3

TUNLED

O

Tuning LED

4

4

STLED

O

Stereo LED

5

5

VSSA

-

Ground

6

6

AOUT

O

Connections for the Tr. used for the PLL active LPF.

7

7

AIN

I

8

8

PD

O

PLL charge pump output

9

10

VSSX

-

Crystal GND

10

11

XOUT

I

Crystal oscillator element connection

11

12

XIN

O

(75kHz, 3.6MHz, 7.2MHz, 10.8MHz)

12

13

DO

O

Serial data output to the microprocessor

13

14

CL

I

Clock used for data synchronization for serial data input(DI)

and serial data output(DO)

14

15

DI

I

Serial data input from the microprocessor

15

16

CE

I

Chip enable for serial I/O

16

18

VSSD

-

Ground

17

19

TEST1

I/O

Only for test

18

20

TEST2

I/O

19

21

TEST3

O

20

22

VDD

-

Regulator voltage input

21

23

VREG

-

Regulator voltage output

22

24

NC

-

No connection

* 48-LQFP: 9, 17 pin NC

AM/FM 1CHIP TUNER WITH PLL

S1A0903X01

5

PIN CONFIGURATION (Continued)

Pin No.

Symbol

In/Out

Function

44-QFP

48-LQFP

23

25

VCDC

-

VCC ripple rejection cap.

24

26

FMOSC

I

FM oscillator input

25

27

VDDA

-

Power

26

28

AMOSC

I

AM oscillator input

27

29

VCC_RF

-

RF-Power

28

30

FMRFOUT

O

FM RF output

29

31

AMRFIN

I

AM RF input

30

32

FMRFIN

I

FM RF input

31

34

GND_RF

-

RF-Ground

32

35

AMLOWCUT

-

AM lowcut cap.

33

36

MIXOUT

O

AM/FM MIX output

34

37

AGCCAP

-

AGC cap.

35

38

AMIFIN

I

AM IF input

36

39

FMIFIN

I

FM IF input

37

40

VCC

-

Power

38

42

LPF1

-

connection for the phase detector and the VCO LPF

39

43

GND

-

Ground

40

44

MPXIN

I

MPX input

41

45

DETOUT

O

AM/FM Detect Output

42

46

LPF2

-

connection for the VCO LPF

43

47

LPF3

-

connection for the pilot detector and the phase detector LPF

44

48

FMQUAD

-

connection for the FM QUAD detector resonator

* 48-LQFP: 33, 41 pin NC

S1A0903X01

AM/FM 1CHIP TUNER WITH PLL

6

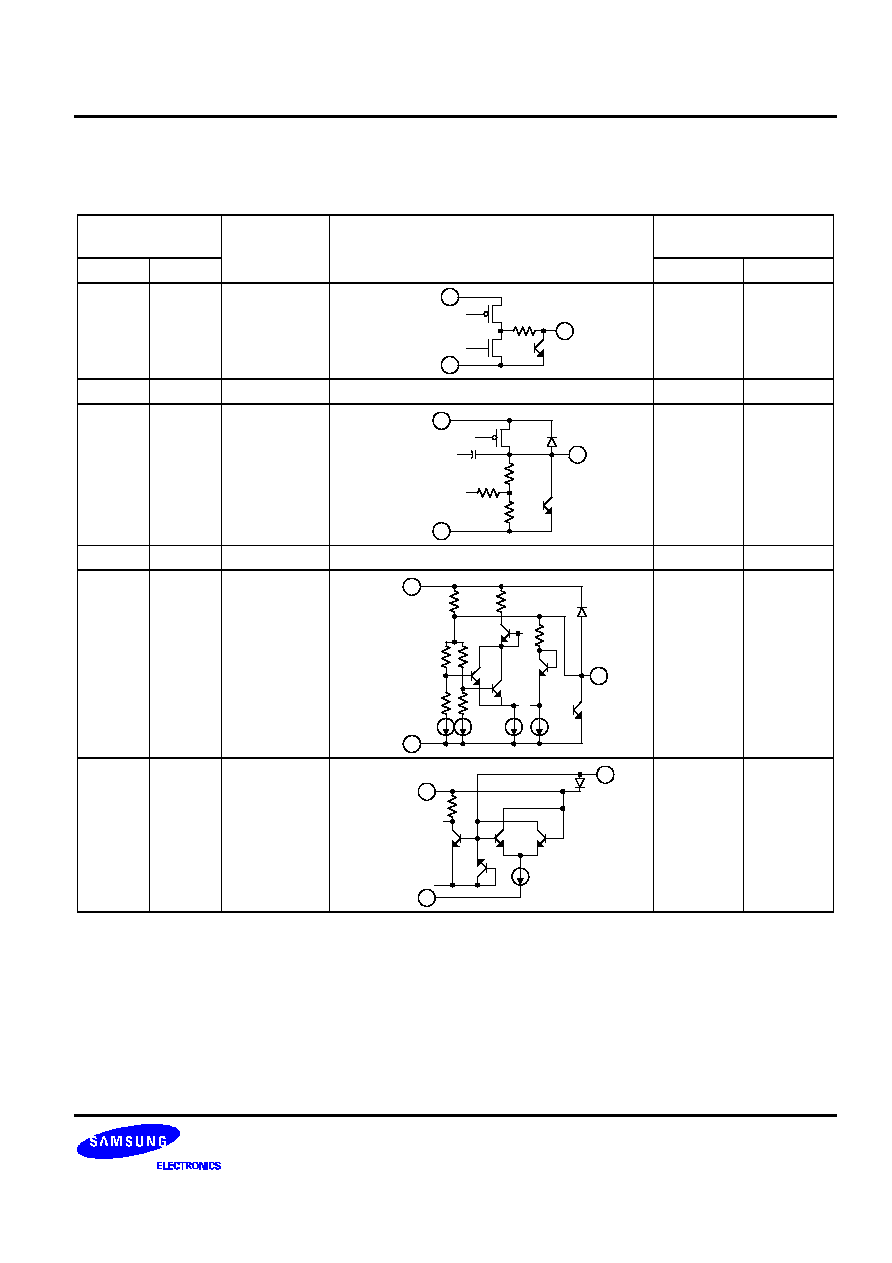

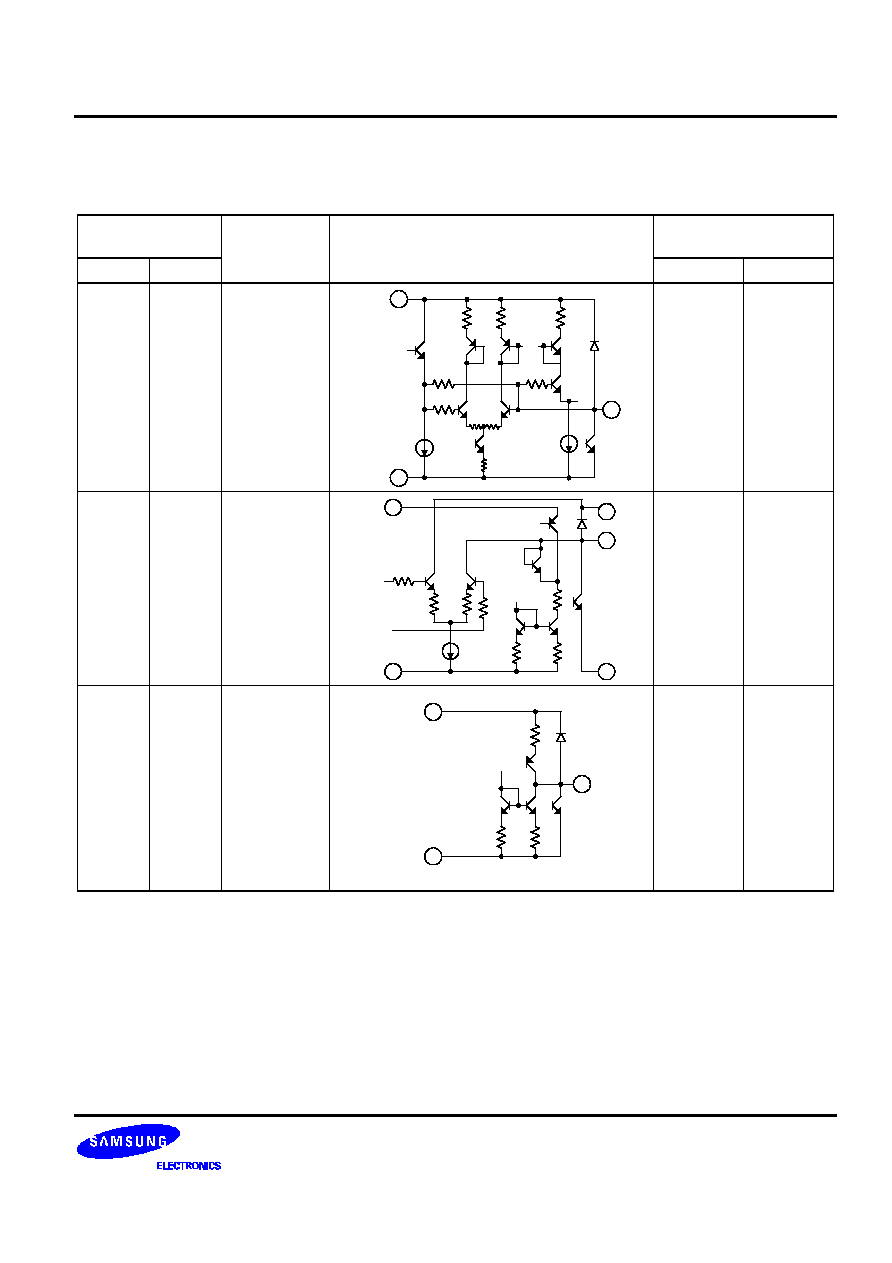

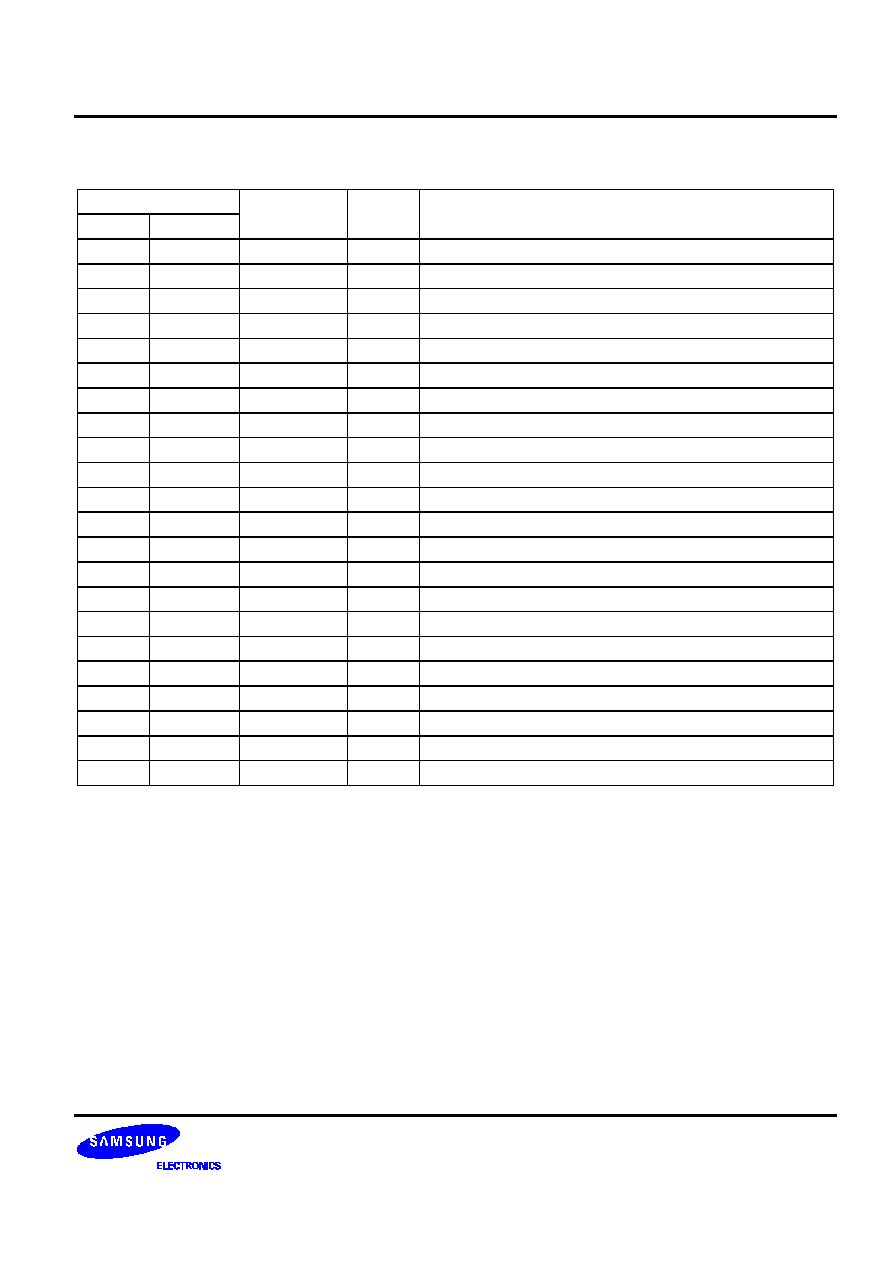

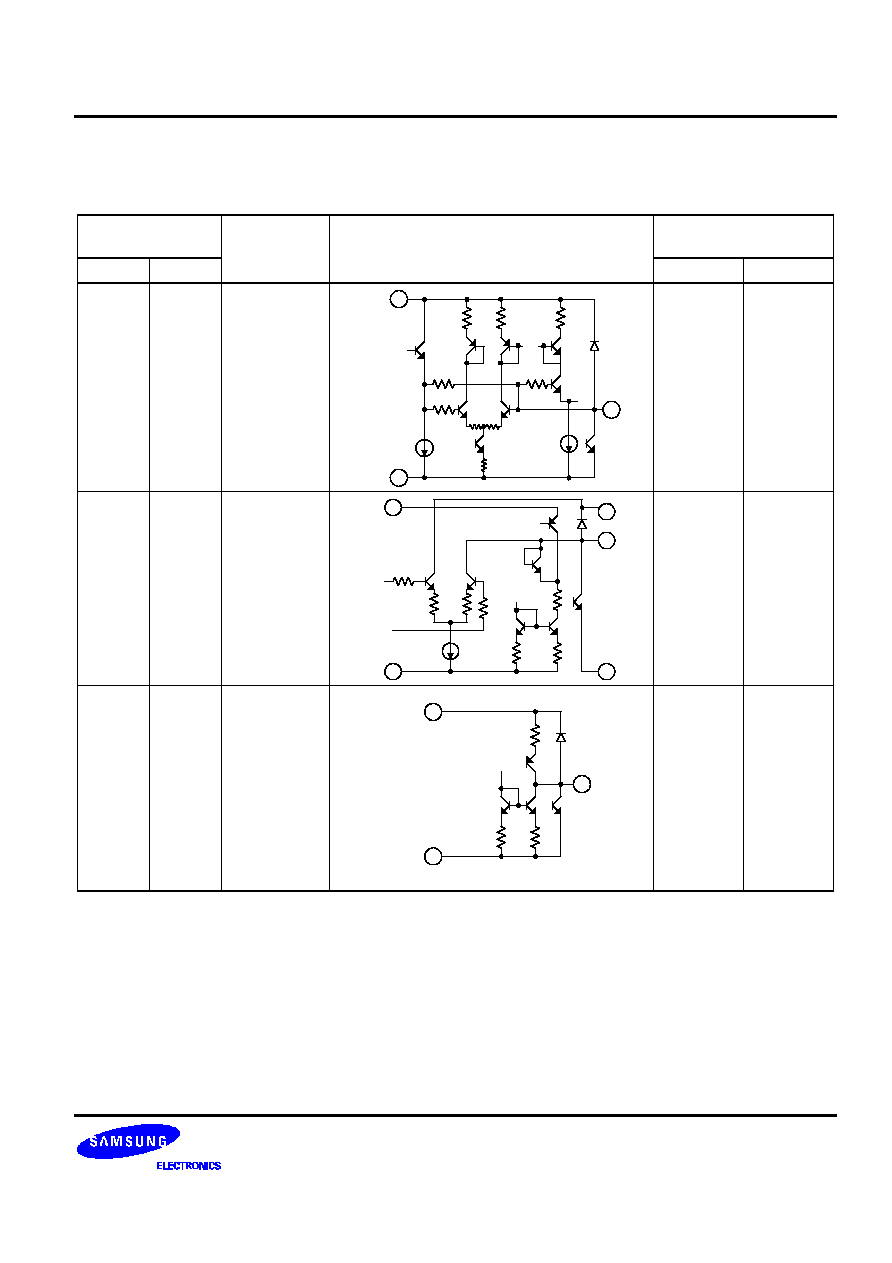

PIN DESCRIPTION

ANALOG BLOCK I/O PIN

(Terminal voltage: Typical terminal voltage at no signal with test circuit, V

CC

= 3V, Ta = 25

∞

C)

Pin No.

Pin Name

Internal Circuit

(Standard 44-QFP Device)

Terminal(Typ.)

Voltage (V)

44-QFP

48-LQFP

AM

FM

1

2

1

2

LOUT

ROUT

VCC

GND

37

39

1/2

1.1

1.1

3

4

3

4

TUNLED

STLED

GND

VCC 37

3/4

39

-

-

5

5

VSSA

6

7

6

7

AOUT

AIN

VSSA

VCC 37

7

5

6

-

-

-

-

AM/FM 1CHIP TUNER WITH PLL

S1A0903X01

7

ANALOG BLOCK I/O PIN (Continued)

(Terminal voltage: Typical terminal voltage at no signal with test circuit, V

CC

= 3V, Ta = 25

∞

C)

Pin No.

Pin Name

Internal Circuit

(Standard 44-QFP Device)

Terminal(Typ.)

Voltage (V)

44-QFP

48-LQFP

AM

FM

8

8

PD

VDD

VSSA

20

8

5

-

-

9

20

10

22

cf. Digital block I/O PIN

21

23

VREG

GND

VDDA 25

21

39

1.8

1.8

22

24

NC

-

-

23

25

VCCCAP

GND

VCC 37

23

39

2.85

3.0

24

26

FMOSC

VCC_RF

GND

27

24

39

3.0

3.0

S1A0903X01

AM/FM 1CHIP TUNER WITH PLL

8

ANALOG BLOCK I/O PIN (Continued)

(Terminal voltage: Typical terminal voltage at no signal with test circuit, V

CC

= 3V, Ta = 25

∞

C)

Pin No.

Pin Name

Internal Circuit

(Standard 44-QFP Device)

Terminal(Typ.)

Voltage (V)

44-QFP

48-LQFP

AM

FM

25

27

VDDA

-

3.0

3.0

26

28

AMOSC

VCC

GND

37

39

26

3.0

3.0

27

29

VCC_RF

-

3.0

3.0

28

30

30

32

FMRFOUT

FMRFIN

GND_RF

VCC_RF

VCC 37

27

28

30

31

3.0

0

3.0

0.8

29

31

AMRFIN

VCC_RF

GND_RF

27

29

31

3.0

3.0

30

32

FMRFIN

cf. PIN28

31

34

GND_RF

-

0

0

AM/FM 1CHIP TUNER WITH PLL

S1A0903X01

9

ANALOG BLOCK I/O PIN (Continued)

(Terminal voltage: Typical terminal voltage at no signal with test circuit, V

CC

= 3V, Ta = 25

∞

C)

Pin No.

Pin Name

Internal Circuit

(Standard 44-QFP Device)

Terminal(Typ.)

Voltage (V)

44-QFP

48-LQFP

AM

FM

32

35

AMLOWCUT

VCC

GND

37

39

32

1.7

-

33

36

MIXOUT

VCC_RF

FM MIX

GND

AM MIX

GND_RF

VCC

27

36

33

39

31

3.0

2.9

34

37

AGCCAP

VCC

GND

37

39

34

-

-

S1A0903X01

AM/FM 1CHIP TUNER WITH PLL

10

ANALOG BLOCK I/O PIN (Continued)

(Terminal voltage: Typical terminal voltage at no signal with test circuit, V

CC

= 3V, Ta = 25

∞

C)

Pin No.

Pin Name

Internal Circuit

(Standard 44-QFP Device)

Terminal(Typ.)

Voltage (V)

44-QFP

48-LQFP

AM

FM

35

38

AMIFIN

VCC

GND

37

35

39

3.0

3.0

36

39

FMIFIN

VCC

GND

37

36

39

3.0

3.0

37

40

VCC

-

3.0

3.0

38

42

LPF1

cf. PIN42

2.2

2.2

39

43

GND

-

0

0

40

44

MPXIN

GND

VCC 37

40

39

0.8

0.8

AM/FM 1CHIP TUNER WITH PLL

S1A0903X01

11

ANALOG BLOCK I/O PIN (Continued)

(Terminal voltage: Typical terminal voltage at no signal with test circuit, V

CC

= 3V, Ta = 25

∞

C)

Pin No.

Pin Name

Internal Circuit

(Standard 44-QFP Device)

Terminal(Typ.)

Voltage (V)

44-QFP

48-LQFP

AM

FM

41

45

DETOUT

VCC

GND

AM

FM

37

39

41

1.0

1.0

38

42

42

46

LPF1

LPF2

GND

VCC

GND

VCC

37

38

39

37

39

42

2.2

2.2

S1A0903X01

AM/FM 1CHIP TUNER WITH PLL

12

ANALOG BLOCK I/O PIN (Continued)

(Terminal voltage: Typical terminal voltage at no signal with test circuit, V

CC

= 3V, Ta = 25

∞

C)

Pin No.

Pin Name

Internal Circuit

(Standard 44-QFP Device)

Terminal(Typ.)

Voltage (V)

44-QFP

48-LQFP

AM

FM

43

47

LPF3

GND

VCC 37

43

39

2.2

2.2

44

48

FMQUAD

GND

VCC 37

44

40

2.2

2.2

AM/FM 1CHIP TUNER WITH PLL

S1A0903X01

13

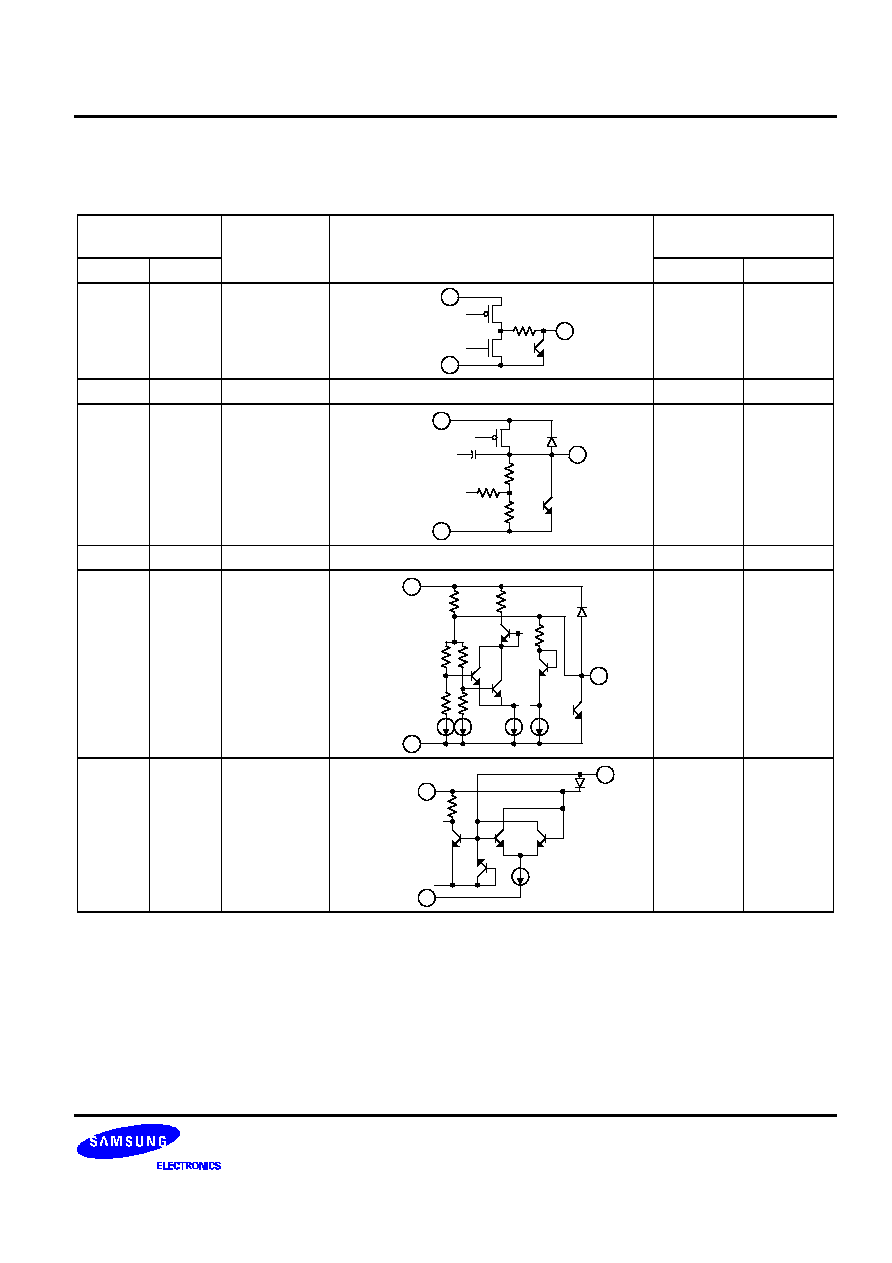

DIGITAL BLOCK I/O PIN

Pin No.

Pin Name

Internal Circuit

Remark

44-QFP

48-LQFP

(Standard 44-QFP device)

9

10

VSSX

10

11

11

12

XOUT

XIN

VDDA

VDD

VSSX

25

20

11

10

19

12

13

DO

VSSD

16

12

13

14

15

14

15

16

CL

DI

CE

13/14/15

VSSD

16

16

18

VSSD

17

18

19

20

TEST1

TEST2

17/18

VDD

VSSD

CDL

20

16

19

21

TEST3

VDD

VSSD

CDL

20

19

16

20

22

VDD

S1A0903X01

AM/FM 1CHIP TUNER WITH PLL

14

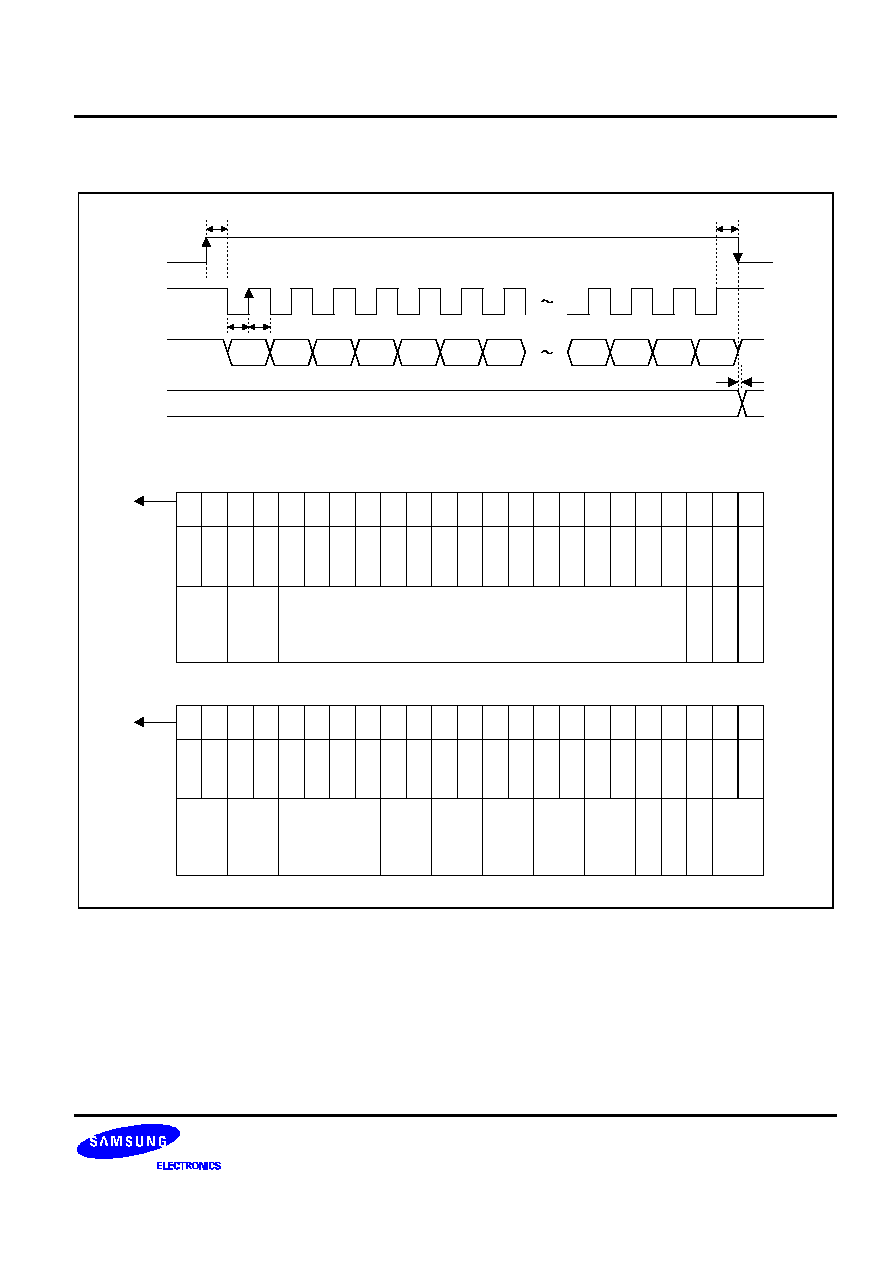

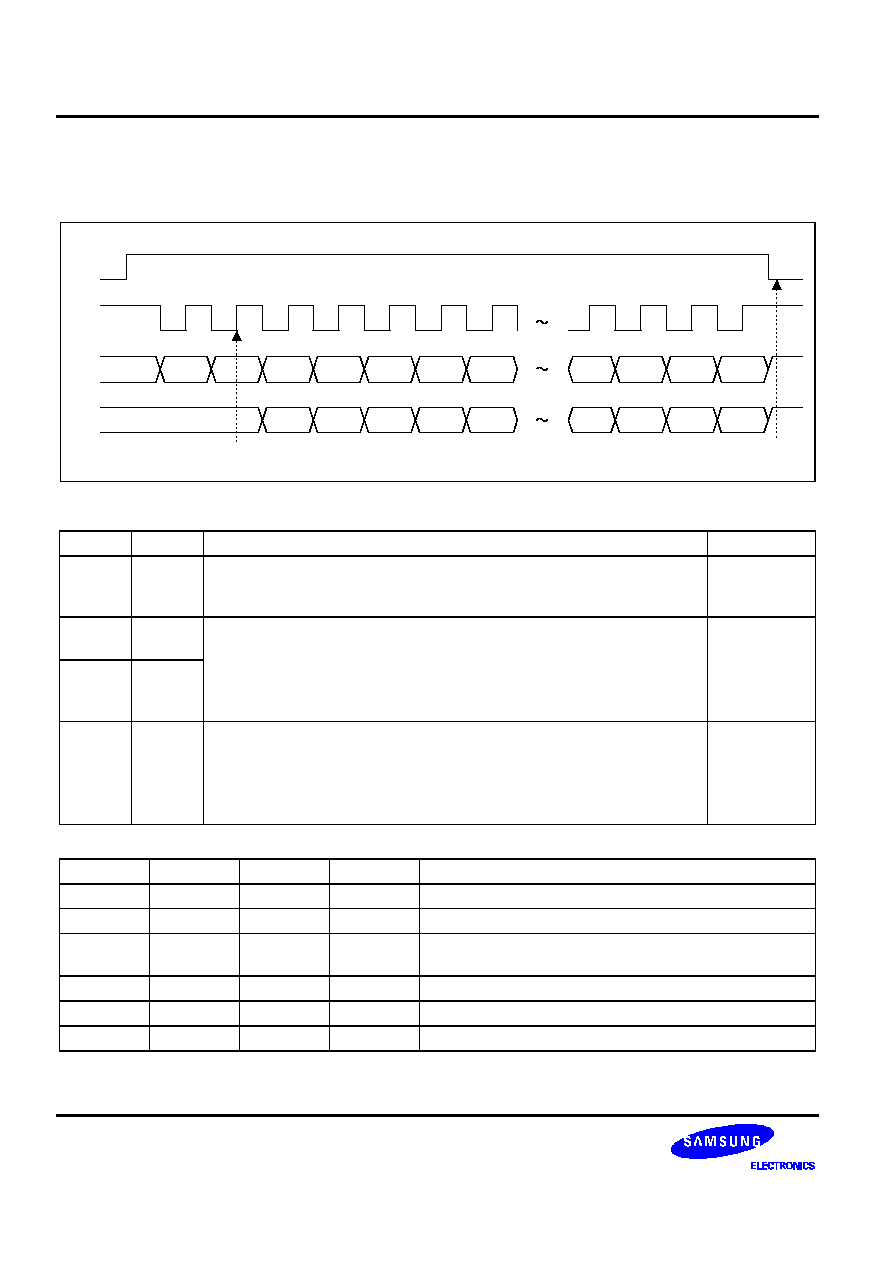

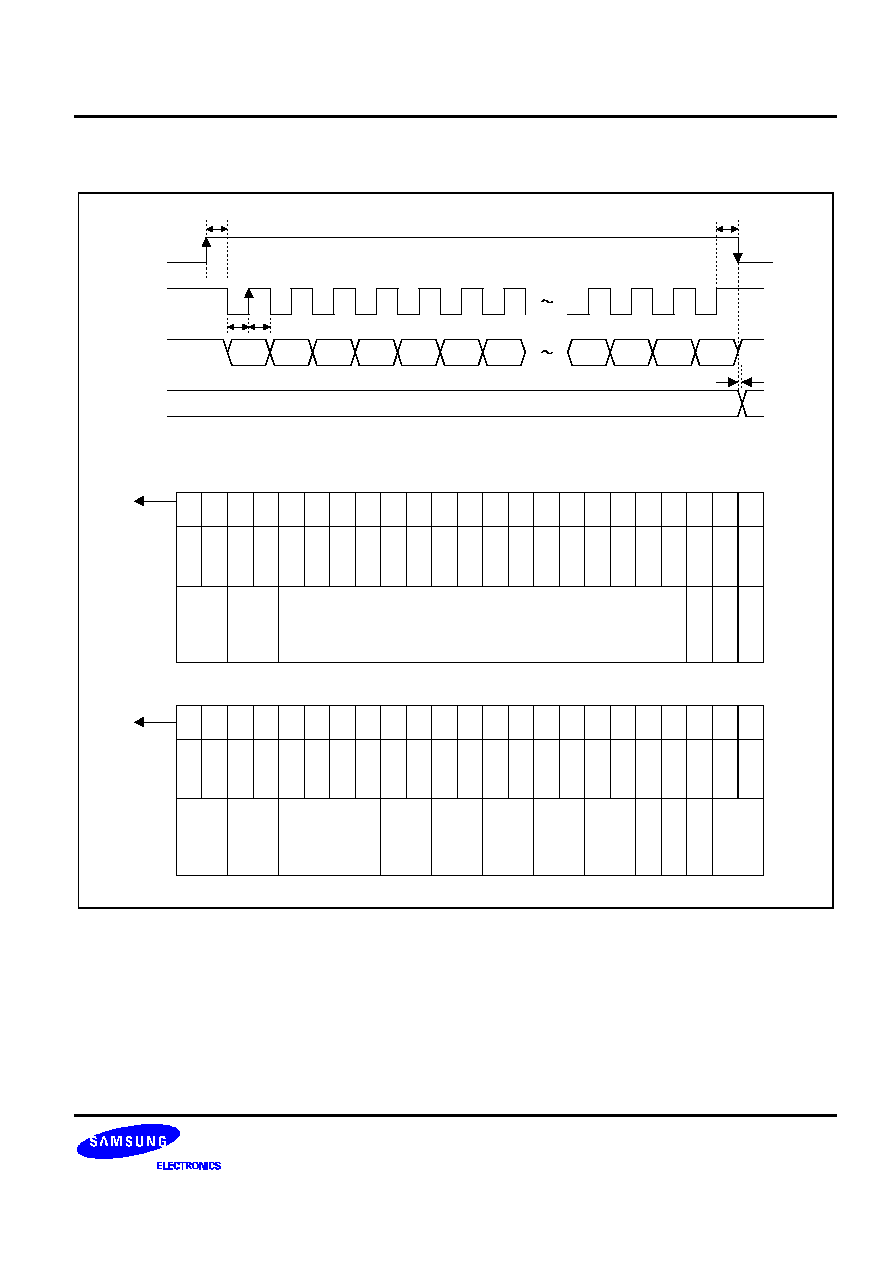

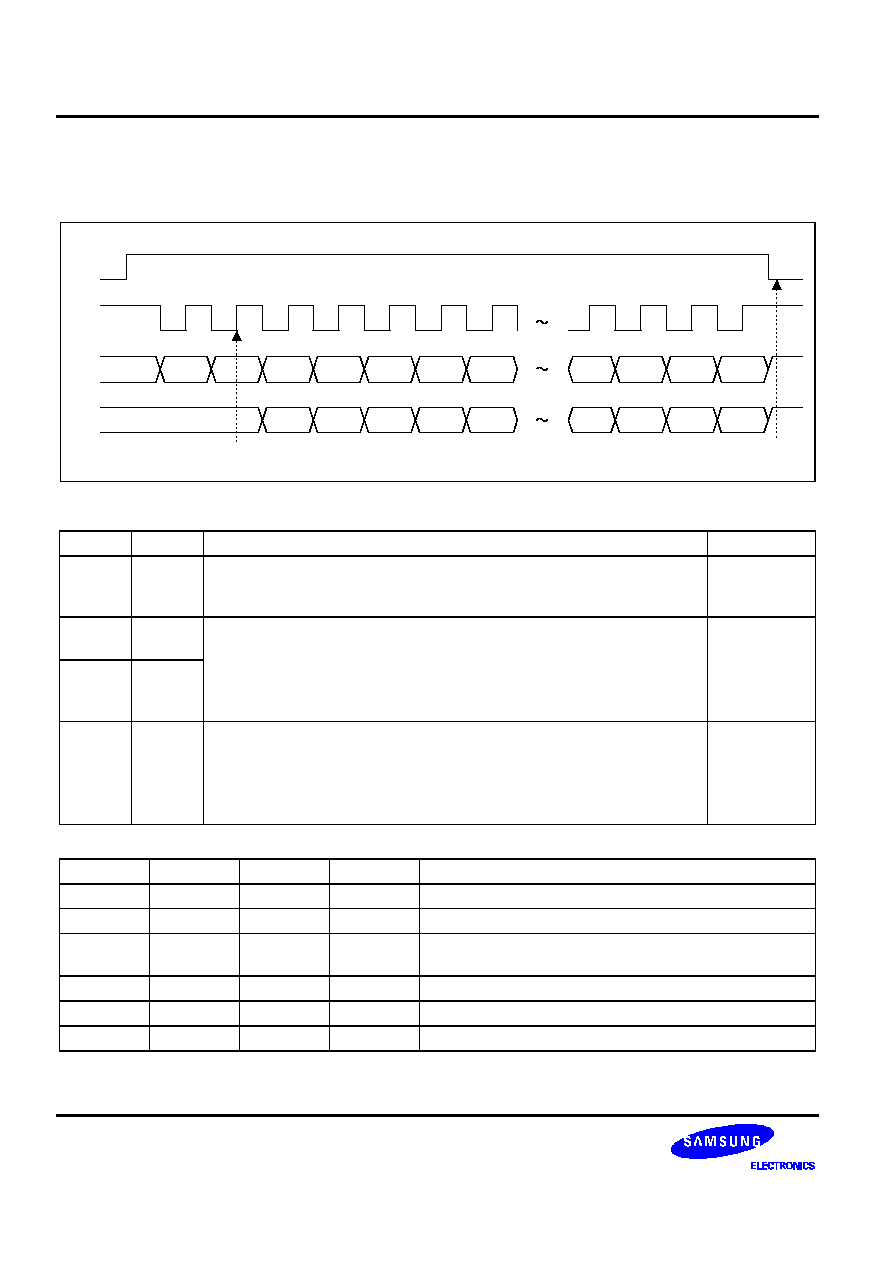

INPUT AND OUTPUT OF SERIAL DATA

SERIAL DATA FORMAT AND TIMING

CE

CL

DI

DO

Internal

data latching

Old

New

tLC

tDH

tEH

VIH

VIL

VIH

VIL

VIH

VIL

tCL

tCH

tSU

tHD

tES

tDC

Figure 1. Serial Data I/O Format and Timing

Parameter

Symbol

Conditions

Ratings

Unit

Min.

Typ.

Max.

Data setup time

t

SU

DI, CL

0.75

-

-

µ

s

Data hold time

t

HD

DI, CL

0.75

-

-

µ

s

Cock low level time

t

CL

CL

0.75

-

-

µ

s

Clock high level time

t

CH

CL

0.75

-

-

µ

s

CE setup time

t

ES

CE, CL

0.75

-

-

µ

s

CE hold time

t

EH

CE, CL

0.75

-

-

µ

s

Data latch change time

t

LC

-

-

0.75

µ

s

Data output time

t

DC

DO, CL

-

-

0.35

µ

s

t

DH

DO, CE

-

-

0.35

µ

s

AM/FM 1CHIP TUNER WITH PLL

S1A0903X01

15

STRUCTURE OF DI CONTROL DATA(SERIAL DATA INPUT)

DI

DI

[ IN1 MODE ]

[ IN2 MODE ]

A1

I20

I19

I18

I17

I16

I3

I2

I1

CE

CL

DI

DSR

Data

tEH

tLC

tES

tHD

tSU

A0

OLD

NEW

I0

A1

A0

I20

I19

I18

I17

I16

I15

I14

I13

I12

I11

I10

I9

I8

I7

I6

I5

I4

I3

I2

I1

I0

0

1

OS1

OS0

N15

N14

N13

N12

N11

N10

N9

N8

N7

N6

N5

N4

N3

N2

N1

N0

IFCS

MUTEC

MUTE

ADDRESS

OSC

SELECT

PROGRAMMABLE DIVISOR DATA

(N1[3:0] : 4 BIT , N2[15:4] : 12 BIT)

IF CNT. START

MUTE OFF

CONTROL

MUTE ON/OFF

A1

A0

I20

I19

I18

I17

I16

I15

I14

I13

I12

I11

I10

I9

I8

I7

I6

I5

I4

I3

I2

I1

I0

1

0

XS1

XS0

R3

R2

R1

R0

IFS1

IFS0

GT1

GT0

DZ1

DZ0

UL1

UL0

DOC1

DOC0

DLC

TUNLEDC

MOST

TEST1

TEST0

ADDRESS

X'TAL

SELECT

REFERENCE

DIVIDER DATA

IF

SENSITIVITY

CONTROL

IF

MEASURE

TIME

DEADZONE

CONTROL

UNLOCK

CONTROL

DO PIN

CONTROL

DEADLOCK

CLEAR

TUNLED

CONTROL

MO/ST

CONTROL

TEST

DATA

Figure 2. Serial Data Input Timing and Format

S1A0903X01

AM/FM 1CHIP TUNER WITH PLL

16

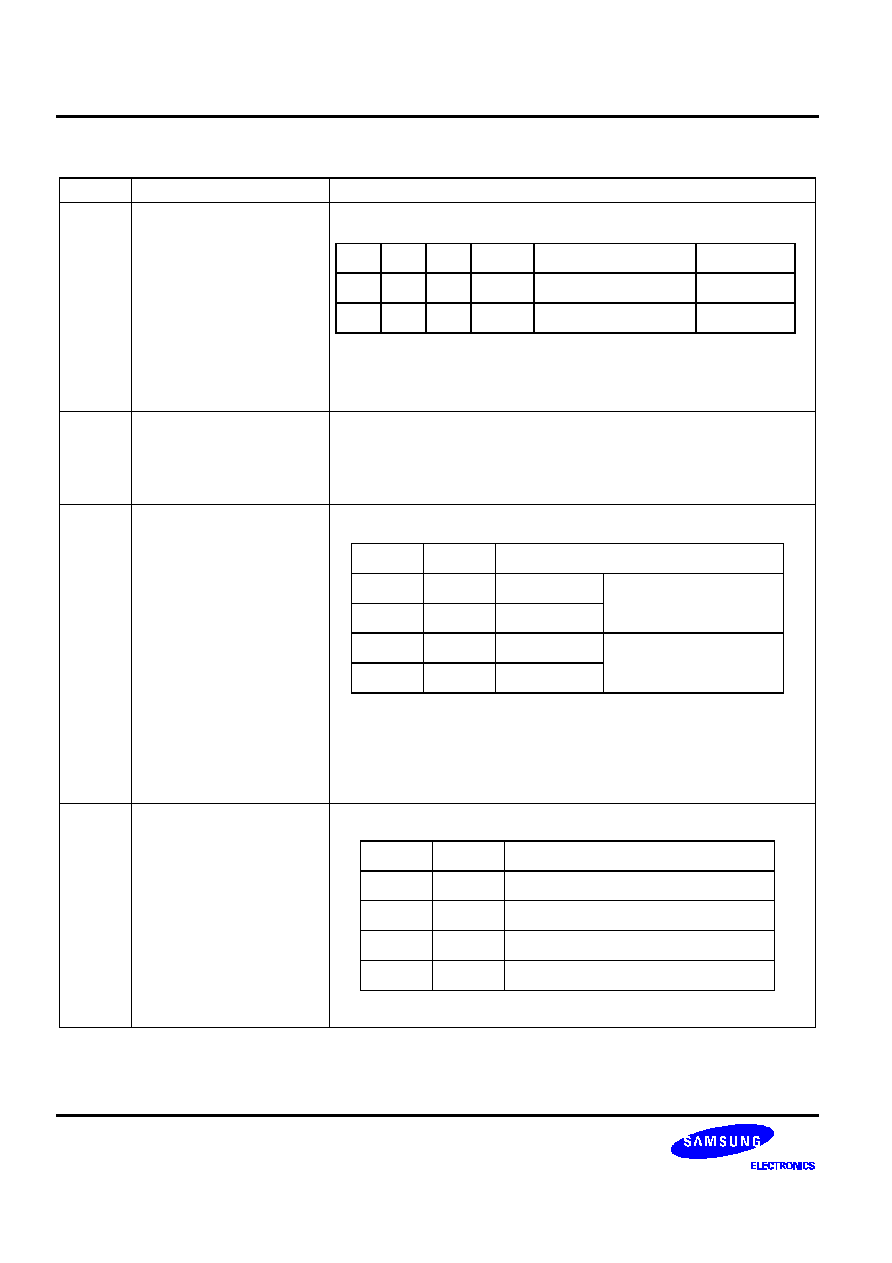

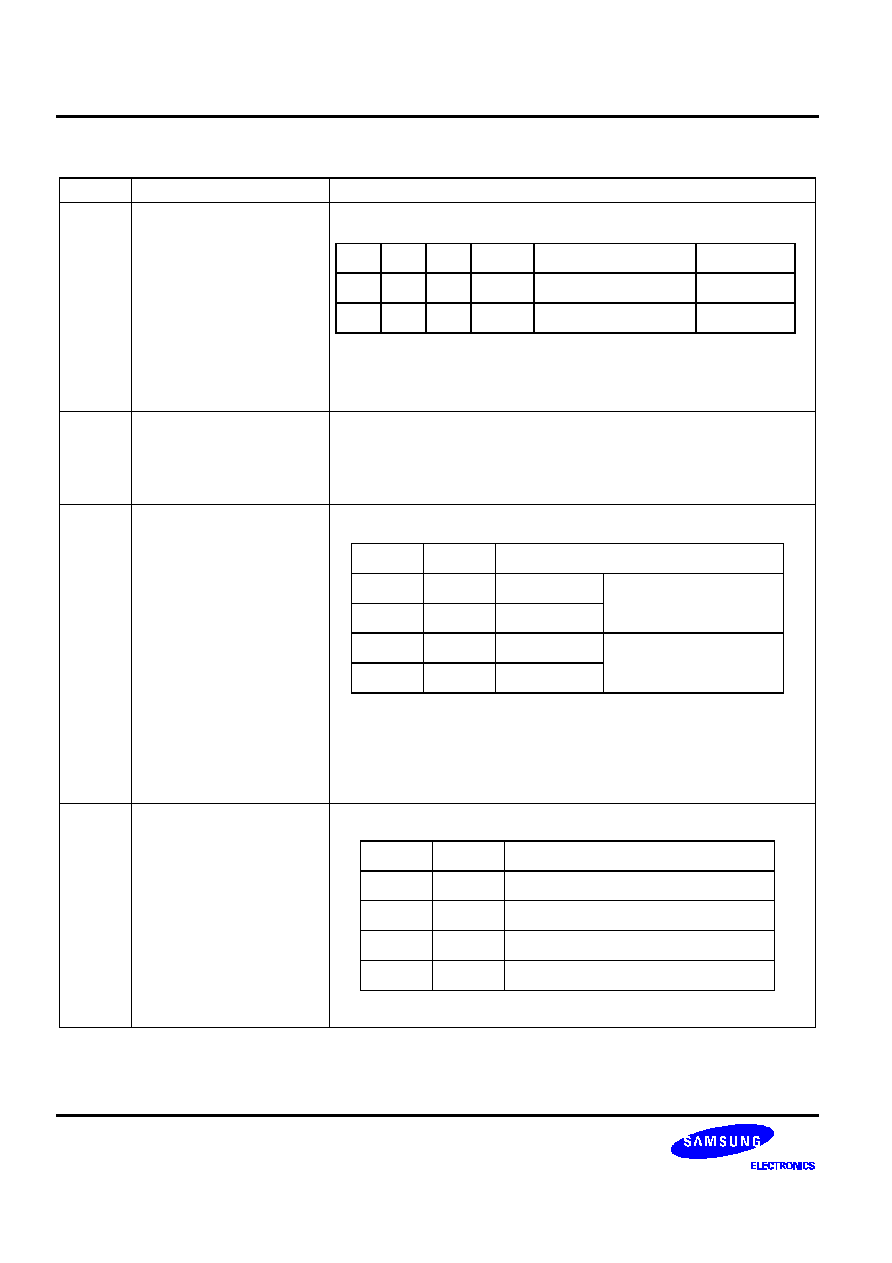

DI CONTROL DATA

No.

Control Block/Data

Function

1

Programmable Divider

Data

OS<1:0>

N<15:0>

∑

Select the input source

FM : Real divisor = 2

◊

N

AM : Real divisor = N

N[3:0] are "don't care" in the case of AMLF

2

If Counter

Start Data

IFCS

∑

IF counter start control data

IFCS = 1 : Start the IF counter

IFCS = 0 : Reset the IF counter

After OUTMODE SIO, IFCS is automatically reset to 0

3

Mute

Control Data

MUTEC, MUTE

∑

MUTE select/control data

MUTEC = 0 : Microprocessor set MUTE

MUTE is automatically reset when tuning LED is on

Whenever BAND is switched from AM to FM, MUTE is automatically

on until MPX VCO free-running frequency self_adjustment is end

4

Reference

Crystal Data

XS<1:0>

∑

Crystal selection data

OS1

OS0

LSB

AM/FM

Frequency Range

Divisor(N)

1

0

N0

FM

10

160MHz

256

65535

0

0

N4

AMLF

0.5

10MHz

4

4096

MUTEC

MUTE

Function

0

0

MUTE off

Self controlled

0

1

MUTE on

1

0

MUTE off

Microprocessor

1

1

MUTE on

controlled

XS1

XS0

CRYSTAL OSC.

0

0

3.6MHz

0

1

75kHz

1

0

7.2MHz

1

1

10.8MHz

AM/FM 1CHIP TUNER WITH PLL

S1A0903X01

17

DI CONTROL DATA (Continued)

No.

Control Block/Data

Function

5

Reference

Frequency

Select Data

R<3:0>

∑

Reference frequency selection

PLL stop mode

Programmable divider and IF counter are stopped.

Charge Pump's output is a high- impedance state.

All stop mode

All the frequency of DTS control block is stopped Control data are

holded the previous state

: No use

6

If

Sensitivity

Control Data

IFS<1:0>

∑

IF sensitivity control

R3

R2

R1

R0

Reference frequency

3.6,7.2,10.8MHz

75kHz

0

0

0

0

100 kHz

0

0

0

1

50 kHz

25 kHz

0

0

1

0

25 kHz

0

0

1

1

15 kHz

15 kHz

0

1

0

0

12.5 kHz

12.5 kHz

0

1

0

1

10 kHz

0

1

1

0

9 kHz

6.25 kHz

0

1

1

1

6.25 kHz

1

0

0

0

5 kHz

5 kHz

1

0

0

1

3.125 kHz

3.125 kHz

1

0

1

0

3 kHz

3 kHz

1

0

1

1

1 kHz

1 kHz

1

1

0

0

1

1

0

1

All stop

1

1

1

0

PLL stop + X'tal OSC. stop

1

1

1

1

PLL stop

IFS1

IFS0

Sensitivity (AM / FM)

0

0

0dB / 0dB

0

1

-4B / -5dB

1

0

-8B / -10dB

1

1

-12/ -16dB

S1A0903X01

AM/FM 1CHIP TUNER WITH PLL

18

DI CONTROL DATA (Continued)

No.

Control Block/Data

Function

7

If Counter

Control Data

GT<1:0>

∑

Select IF counter measurement time

8

Dead Zone

Control Data

DZ<1:0>

∑

Dead zone data

ON: Both of NMOS and PMOS in Charge pump turn on in the same

time and Dead zone is reduced

OFF: Each of NMOS and PMOS in Charge pump turn mutual

exclusively on

9

Unlock State

Control Data

UL<1:0>

∑

decide the LOCK state with the width of Phase error(

E)

DOC[1:0] = 2: DO pin is controlled with LOCK state

UL[1:0] = 1: Width of

E set DO pin low, else high

GT1

GT0

Measurement time (ms)

0

0

4

0

1

8

1

0

16

1

1

32

DZ1

DZ0

Charge Pump

DeadZone

0

0

ON

--0

0

1

ON

-0

1

0

OFF

+0

1

1

OFF

++0

UL1

UL0

E Detection Width

DO Pin State

0

0

stopped

hold the previous state

0

1

0

E is directly out

1

0

±

0.55us

E is extended by 2ms

1

1

±

1.11us

AM/FM 1CHIP TUNER WITH PLL

S1A0903X01

19

DI CONTROL DATA (Continued)

No.

Control Block/Data

Function

10

DO Pin

Control Data

DOC<1:0>

∑

DO pin control data

When CE is low, DOC[1:0] controls DO pin

11

Deadlock Clear

Control Data

DLC

∑

Deadlock clear data

DLC = 1 : The output of Charge pump is forcibly set to low, which

makes control voltage VCC and gets out of DEADLOCK condition

DLC = 0 : Normal operation

12

Tuning Led

Control Data

TUNLEDC

∑

LED control data

Abobe condition is IFS[1:0] = 0

The point of turning Tuning LED on depends on the value of IFS[1:0]

13

Mono, Stereo Control Data

MOST

∑

MONO/STEREO control

MOST = 1 : Set STEREO mode

MOST = 0 : Set forcibly MONO mode

14

Test

Control Data

TEST<1:0>

∑

Test data

DOC1 DOC0

Function

0

0

DO pin open

0

1

1

0

DTS PLL = lock, DO pin = open

1

1

IF counting = end, DO pin = low

TUNLEDC

AM

FM

0

IF

32dB

µ

=> LED On

IF

45dB

µ

=> LED On

1

IF

32dB

µ

and within

450kHz

±

5kHz

=> LED On

IF

45dB

µ

and within

10.7MHz

±

12.5kHz

=> LED On

TEST1

TEST0

Function

0

0

NORMAL OPERATION

0

1

TEST MODE1

1

0

TEST MODE2

1

1

TEST MODE3

S1A0903X01

AM/FM 1CHIP TUNER WITH PLL

20

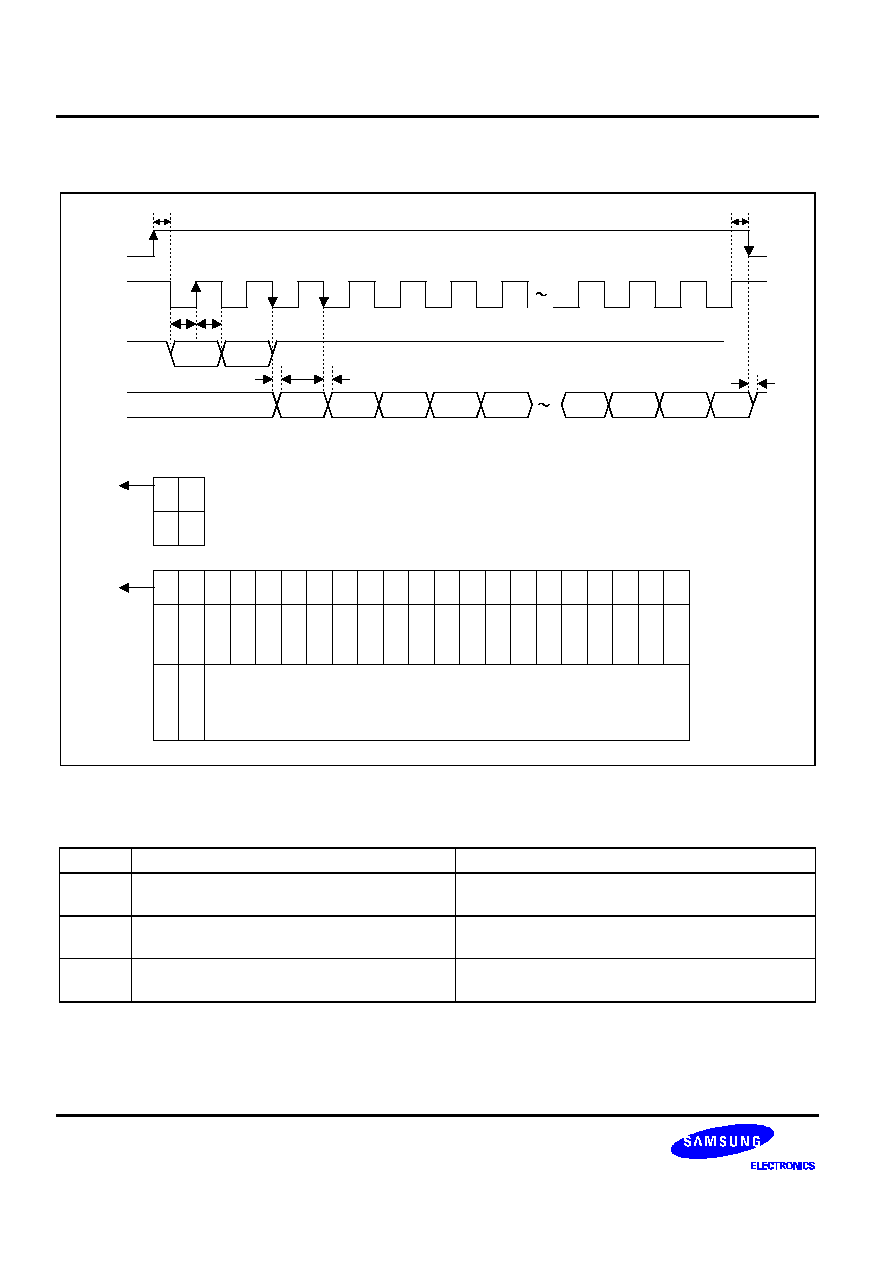

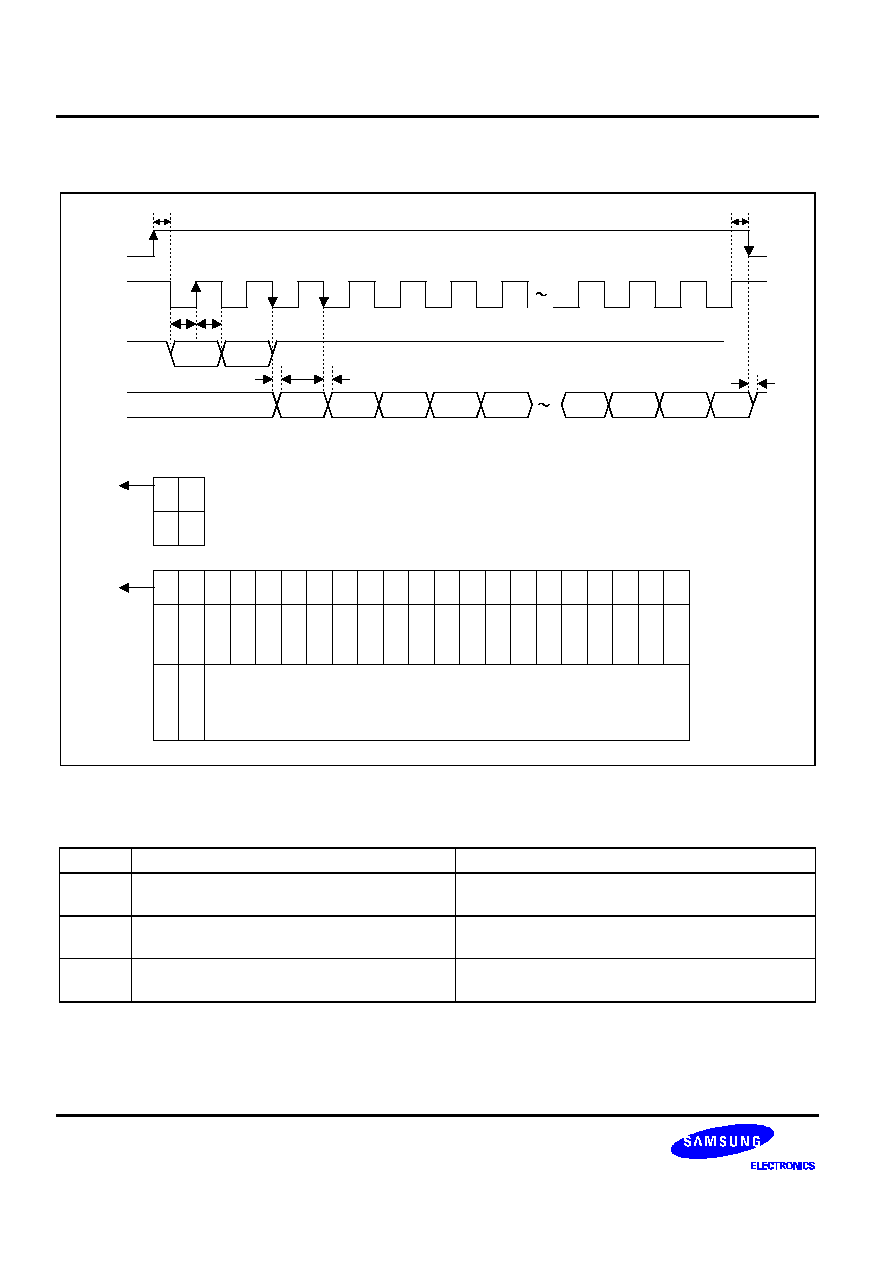

STRUCTURE OF DO OUTPUT DATA(SERIAL TEST DATA OUTPUT)

DO

[ OUT MODE ]

DI

A1

O20

O18

O17

O16

O3

O2

O1

O0

tHD

tSU

tDH

tDC

tDC

tEH

tES

O19

A0

CE

CL

DI

DO

A1

1

A0

1

O20

O19

O18

O17

O16

O15

O14

O13

O12

O11

O10

O9

O8

O7

O6

O5

O4

O3

O2

O1

O0

STID

LOCK

C18

C17

C16

C15

C14

C13

C12

C11

C10

C9

C8

C7

C6

C5

C4

C3

C2

C1

C0

STEREO

INDICATE

LOCK

STATE

IF COUNTER BINARY DATA

Figure 3. Serial Data Output Timing and Format

DI OUTPUT DATA

No.

Control Block/Data

Function

1

STEREO INDICATION DATA

STID

STID = 1 : detect STEREO

STID = 0 : detect MONO

2

PLL LOCKED STATE DATA

LOCK

LOCK = 1 : PLL is lock

LOCK = 0 : PLL isn't lock

3

IF COUNTER BINARY DATA

C18

C0

C18 : IF counter value (MSB)

C0 : IF counter value (LSB)

AM/FM 1CHIP TUNER WITH PLL

S1A0903X01

21

STRUCTURE OF TEST MODE DO OUTPUT DATA(SERIAL DATA OUTPUT)

DO

DI

[TEST MODE0 ]

[ TEST MODE1,2,3]

DO

DI

A1

O20

O18

O17

O16

O3

O2

O1

O0

tHD

tSU

tDH

tDC

tDC

tEH

tES

O19

A0

CE

CL

DI

DO

OS1

A1

A0

0

0

O20

O19

O18

O17

O16

O15

O14

O13

O12

O11

O10

O9

O8

O7

O6

O5

O4

O3

O2

O1

O0

OS0

N15

N14

N13

N12

N11

N10

N9

N8

N7

N6

N5

N4

N3

N2

N1

N0

IFCS

MUTEC

MUTE

A1

A0

0

0

O20

O19

O18

O17

O16

O15

O14

O13

O12

O11

O10

O9

O8

O7

O6

O5

O4

O3

O2

O1

O0

XS1

XS0

R3

R2

R1

R0

IFS1

IFS0

GT1

GT0

DZ1

DZ0

UL1

UL0

DOC1

DOC0

DLC

TUNLEDC

MOST

TEST1

TEST0

Figure 4. Serial Test Data Output Timing and Format

DO OUTPUT DATA

No.

Mode

Function

1

TEST MODE0

When TEST[1:0]=0 in MODE2 data,

IN1 data in Data Shift Register is sent from DO pin to Microprocessor

synchronously with the CL

2

TEST MODE1,2,3

When TEST[1:0]=1,2,3 in MODE2 data,

IN1 data in Data Shift Register is sent from DO pin to Microprocessor

synchronously with the CL

S1A0903X01

AM/FM 1CHIP TUNER WITH PLL

22

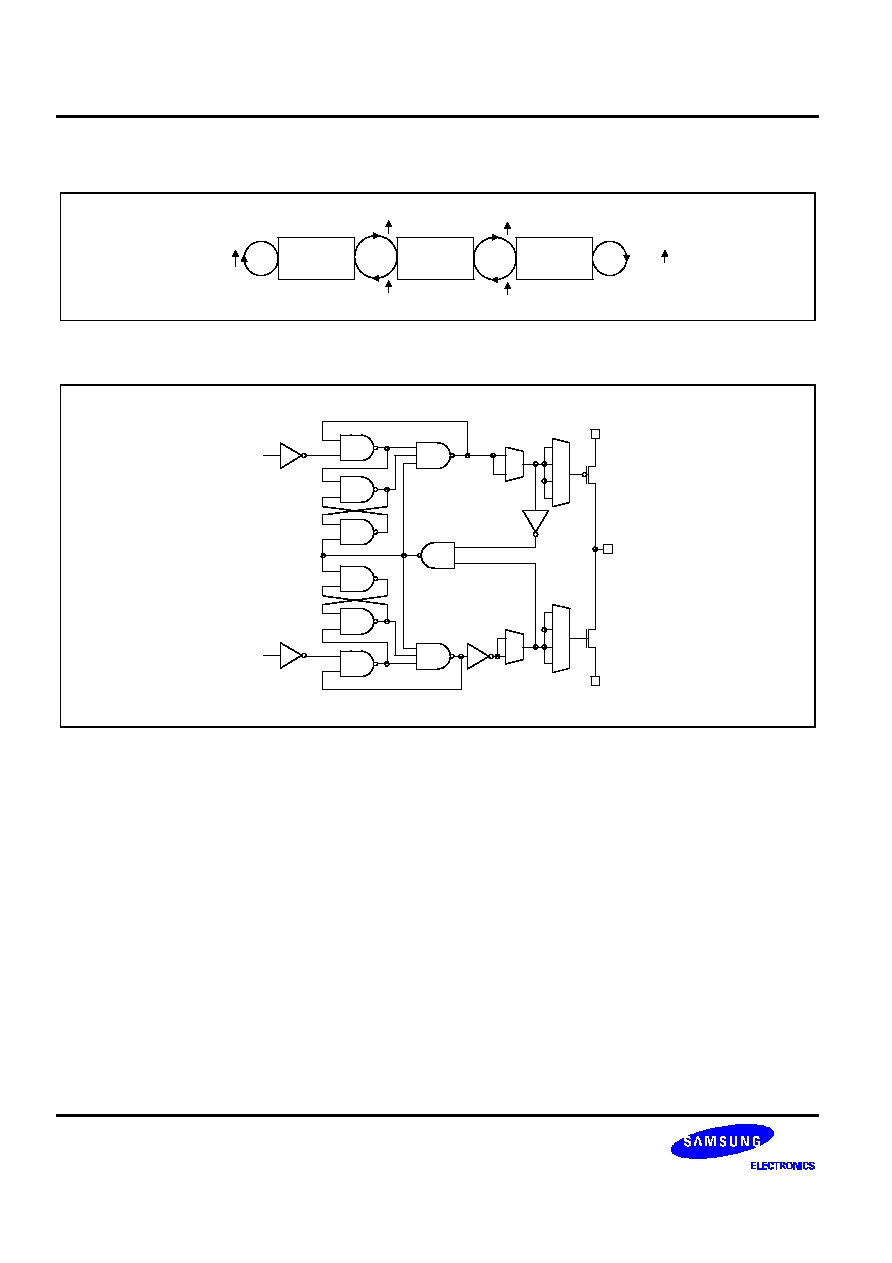

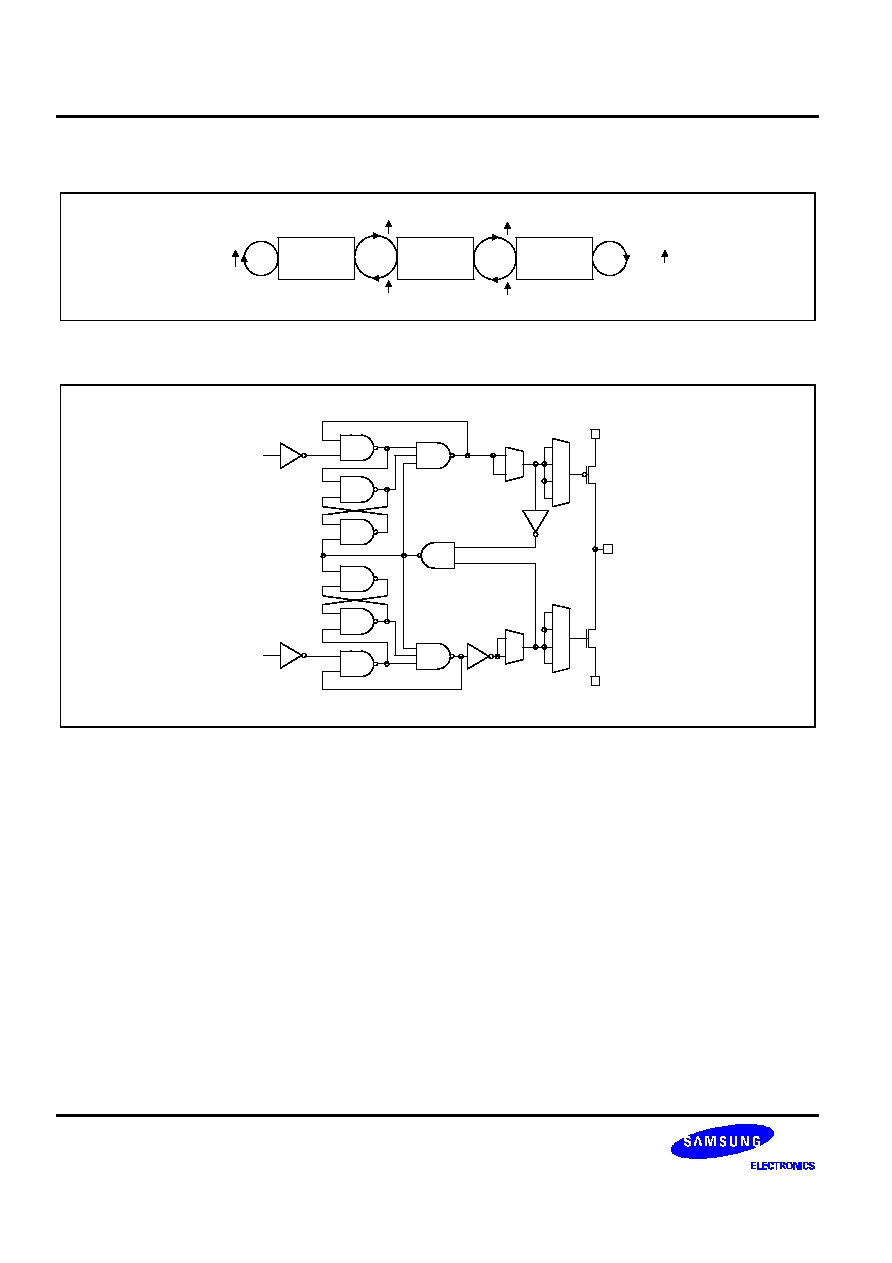

PROGRAMMABLE DIVIDER STRUCTURE

SERIAL INTERFACE

CE

CL

A1

DI

DO

O20

O18

O17

O16

O3

O2

O1

O0

O19

A0

I20

I18

I17

I16

I3

I2

I1

I0

I19

A

B

Figure 5. Serial I/O Timing

A[1:0]

Mode

DI / DO

Remarks

0

TEST

Data of IN1(TEST[1:0]=0) or IN2(TEST[1:0]=1,2,3) latched in DSR are

transferred to serial interface, which data are transferred to Micro-

processor through DO pin synchronized with the CL

1

IN1

Data I[20:0] from DI pin are latched in IN1 or IN2 Data shift register on

B point.

2

IN2

When OS[1:0] in IN1 MODE is changed, N[16:0] is changed and R[3:0]

is changed from PLL STOP MODE, Fr and Fc counter are reset which

make lock time of PLL fixed.

3

OUT

Data of OUT MODE latched in DSR are transferred on A point, which

data transferred to Microprocessor through DO pin synchronized with

the CL.

IFCS bit is reset on B point, which makes Micro-processor restart IF

counter

CE

DOC1

DOC0

OUTMODE

DO Pin State

0

0

0

X

Open

0

0

1

X

Open

0

1

0

X

When LOCK bit in OUT MODE is high, DO pin holds the

low state.

0

1

1

X

When IF counting is end, DO pin holds the low state.

1

X

X

0

Open

1

X

X

1

OUTMODE data are transferred through DO pin

X : don't care

AM/FM 1CHIP TUNER WITH PLL

S1A0903X01

23

1/N BLOCK

1/N block is used for frequency down-scaling from AM OSC. or FM OSC. to reference frequency Fr and

Prescaler, Swallow Counter, Main Counter is used for a natural number dividing.

FM OSC/2

AM OSC

XIN

[A]

Prescaler

1/16, 1/17

[B]

[C]

fp

Swallow

Counter

Main

Counter

N[3:0]

fc

N[15:0]

Phase

Frequency

Detector

E

R[3:0]

Reference

Divider

12

AM = fr=fc=AMOSC/N

FM = fr=fc=FMOSC/2N

N Divider

fr

Figure 6. 1/N block diagram

OS1

OS0

Input Frequency

Input Frequency Range

A

1

0

FM / 2

5

80 MHz

B

0

0

AMLF

0.5

10 MHz

∑

N = (16

◊

N2) + N1

= 17

◊

N1 + 16

◊

(N2 - N1)

∑

Fc is derived from OSC. divided by N, N2 is derived from N[16:4] and N1 is derived from N[3:0]

N2

N1

17

17XN1

16

16X(N2-N1)

counting number of M.C

counting number of S.C

divisor of Prescaler

counting number of M.C

Figure 7. 1/N counting method

∑

Prescaler : operates on FM MODE.

∑

Swallow Counter : counts down with N1 divisor and divides Fp by 17 on operation of swallow counter and

divide by 16 until S.C reloads N1 at the end of Fc 1 period.

∑

Main Counter : makes Fc divided by N2 divisor from Fp divided by 16 or 17

∑

Reference Divider : makes Fr divided by R[3:0] divisor from X'tal.

S1A0903X01

AM/FM 1CHIP TUNER WITH PLL

24

∑

For FM with a step size of 50kHz

FM RF = 89.3MHz (IF = 10.7MHz)

FM VCO = 100.0MHz

Reference clock(Fr) = 50kHz

100.0MHz(FM VCO)

˜

50kHz(fr)

˜

2 = 1000

03E8(hex)

O

S

1

O

S

0

N

1

5

N

1

4

N

1

3

N

1

2

N

1

1

N

1

0

N

9

N

8

N

7

N

6

N

5

N

4

N

3

N

2

N

1

N

0

I

F

C

S

M

U

T

E

C

M

U

T

E

1

0

0

0

0

0

0

0

1

1

1

1

1

0

1

0

0

0

X

X

X

0

3

E

8

X : don't care

∑

For AMLF with a step size of 9kHz

AMLF RF = 1161kHz (IF = 450kHz)

AM VCO = 1611kHz

Reference clock(fr) = 9kHz

1611kHz(AM VCO)

˜

9kHz(fr) = 179

OB3(hex)

O

S

1

O

S

0

N

1

5

N

1

4

N

1

3

N

1

2

N

1

1

N

1

0

N

9

N

8

N

7

N

6

N

5

N

4

N

3

N

2

N

1

N

0

I

F

C

S

M

U

T

E

C

M

U

T

E

0

0

0

0

0

0

1

0

1

1

0

0

1

1

X

X

X

X

X

X

X

0

B

3

X

X : don't care

AM/FM 1CHIP TUNER WITH PLL

S1A0903X01

25

∑

Fc generated by First example of setting 'N' divisor

N[15:0] = 03E8(hex) = 1000(dec)

N1 = N[3:0] = 8

N2 = N[15:4] = 3E(hex) = 62(dec)

Fc is divided by 17 with the amount of N1 and divided by 16 with the amount of N2 - N1 in Figure. 8.

1

2

3

4

5

6

8

7

9

10

11

12

13

14

15

16

17

OSC/2

Divided

by 16

Divided

by 17

62

61

60

59

58

57

55

56

54

53

52

51

50

7

6

5

4

3

2

1

62

Divided by 17 (N1)

Divided by 16 (N2 - N1)

Fp

Fc

0

61

60

N

Figure 8. Generated FC by First Example

S1A0903X01

AM/FM 1CHIP TUNER WITH PLL

26

PHASE FREQUENCY DETECTOR

FC

FC

FC

FR

FR

FR

STATE1

STATE2

STATE3

A=V

L

B=V

H

A=V

L

B=V

L

A=V

H

B=V

L

Figure 9. PFD state diagram

FC

FR

VDD

VSSA

PD

B

A

b

a

d

c

f

e

a

b

e

f

c

d

Figure 10. PFD scheme

States are changed on rising edges of Fr or Fc in Figure. 9(Fr moving to higher states and Fc moving to lower

states) Suppose the circuit is initially in state 1, Then alternate rising edges on Fr and Fc will cycle between

states 1 and 2. If Fc is constantly falling behind Fr in phase, as in the timing diagram(Figure. 11 A point), then

eventually there will be two Fr rising edges without an intervening Fc rising edge. This will take the circuit to state

3, and thereafter it will cycle between state 2 and state3.

For phase difference of Fc and Fr is almost zero, the rising edges of Fr and Fc are coincident, and the PD

remains in state 2 almost all the time

∑

Z-state Phase Frequency Detector is composed of 3-State PFD and two MOS gates

∑

State 1 : make the frequency of Fc slower.

∑

State 2 : hold the frequency of Fc.

∑

State 3 : make the frequency of Fc faster.

∑

State transition at rising edges of Fr and Fc

rising edge of Fr : cause current state to go high

rising edge of Fc : cause current state to go low

AM/FM 1CHIP TUNER WITH PLL

S1A0903X01

27

VFC

VFR

1

2

2

1

2

2

2

2

2

2

2

2

2

2

2

3

3

3

3

3

3

3

3

3

3

1

State

t

t

t

t

t

A

VA

VB

VPD

Figure 11. Timing Diagram (DZ[1:0]=0)

∑

differences of deadzone (in Figure. 10)

DZ[1]

DZ[0]

MX2 path

MX4 path

PMOS / NMOS

DeadZone

remarks

0

0

b

a

on/on

--0

(1)

0

1

a

b

on/on

-0

(2)

1

0

a

c

off/off

+0

(3)

1

1

a

d

off/off

++0

(4)

DZ[1:0] = 0 mode : Even though PLL loop is locked, generate phase error pulse and phase error

correction pulse which make Deadzone reduced.

DZ[1:0] = 1 mode : Same as Dz[1:0] = 0 mode, but a width of phase error correction pulse is relatively

narrower.

DZ[1:0] = 2 mode : Generate only phase error pulse but phase error correction pulse.

DZ[1:0] = 3 mode : Same as DZ[1:0] = 2 mode, but a width of phase error pulse is relatively narrower.

DZ[1:0] = 0 or 1

Excellent C/N characteristics

Sidebands may be created by reference frequency leakage

Sidebands may be created by low-frequency leakage due to the correction pulse envelope.

DZ[1:0] = 2 or 3

PLL loop stable

DEADZONE

PFD has to detect subtle phase error and makes phase error signal. There is a region that PFD doesn't make any

phase error pulse due to the propagation delay or other factors, which is called Deadzone.

(detailed in IX. Terminology)

S1A0903X01

AM/FM 1CHIP TUNER WITH PLL

28

Old data

New data ( OS[1:0] or N[15:0] is changed )

CE

DSR's

Data

Fc

Fr

VPD

A

B

z

z

z

z

z

Figure 12. PFD and PD Output Relationship

∑

Error pulse is made from rising edge of Fr and Fc.

∑

If rising edge of Fc is slower than that of Fr, set Vpd to low

make the frequency of Fc fast. (Figure. 9 state1)

∑

If rising edge of Fc is faster than that of Fr, set Vpd to high

make the frequency of Fc slow. (Figure. 9 state3)

∑

A region with no

Error makes Vpd high impedance and hold the frequency of Fc

∑

When data are changed in OS[1:0], N[15:0] or changed in R[3:0] from PLL stop mode.

reset Fc and Fr counter(Figure. 12 A) and change PFD in state 2

After new data is latched, accurate

Error can be reflected on the first phase error(Figure. 12 B)

Lock time can be estimated in advance depending on N[15:0] or OS[1:0] is changed

AM/FM 1CHIP TUNER WITH PLL

S1A0903X01

29

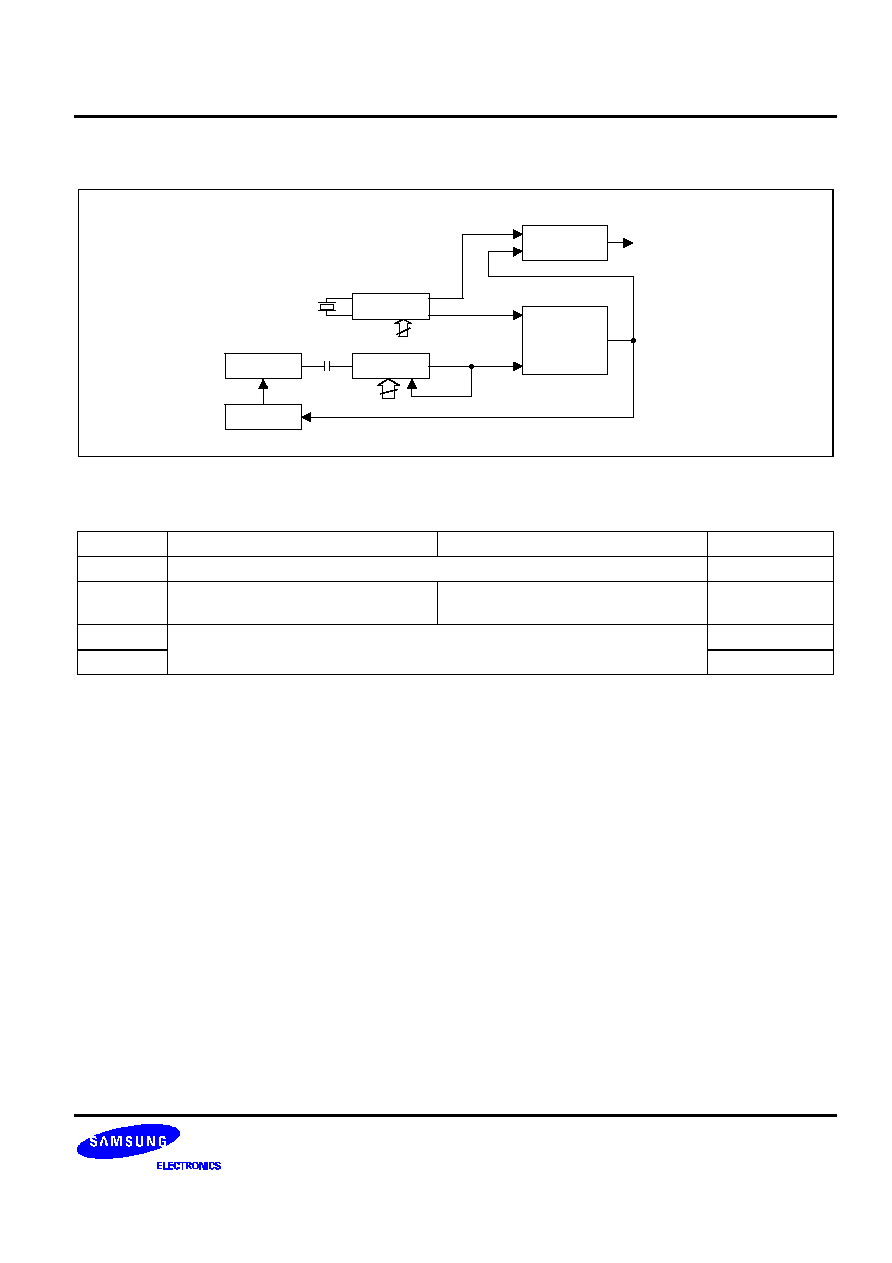

LOCKED STATE DETECTION TIMING

Fr

Fc

preset

Lock

Error

N(16)

R(4)

VCO

L.P.F

1/R

1/N

Lock

Detector

Phase

Frequency

Detector

Figure 13. Lock Detection Scheme

∑

Getting LOCK State

UL[1:0]

LOCK state in serial data

LOCK state on DO pin

Remarks

0

hold the previous state

1

E is out directly depending on SIO

timing

E is out directly

2

when

E is narrower than

E width more than 2ms, set LOCK

3

∑

LOCK bit in serial data reflects LOCK state regardless of DOC[1:0]

∑

DO pin reflects LOCK state only when DOC[1:0] is 2

LOCK : DO pin = open , UNLOCK : DO pin = low

S1A0903X01

AM/FM 1CHIP TUNER WITH PLL

30

Old data

New data ( OS[1:0] or N[15:0] is changed )

CE

DSR's

Data

VCO

frequency

Error

LOCK bit

DO pin

LOCK

UNLOCK

LOCK

data in

data out

data out

A

B

Figure 14. Lock detection timing diagram

∑

LOCK bit in serial data

LOCK bit in serial data shows UNLOCK because VCO frequency isn't stable (Figure. 14 A)

wait at least several cycle and check LOCK again(Figure. 14 B)

needs several LOCK check in order to get more reliable result.

∑

LOCK state on DO pin

Only when DOC[1:0]=1 and UL[1:0]

0, LOCK state can be checked on DO pin

needs several LOCK check in order to get more reliable result.

AM/FM 1CHIP TUNER WITH PLL

S1A0903X01

31

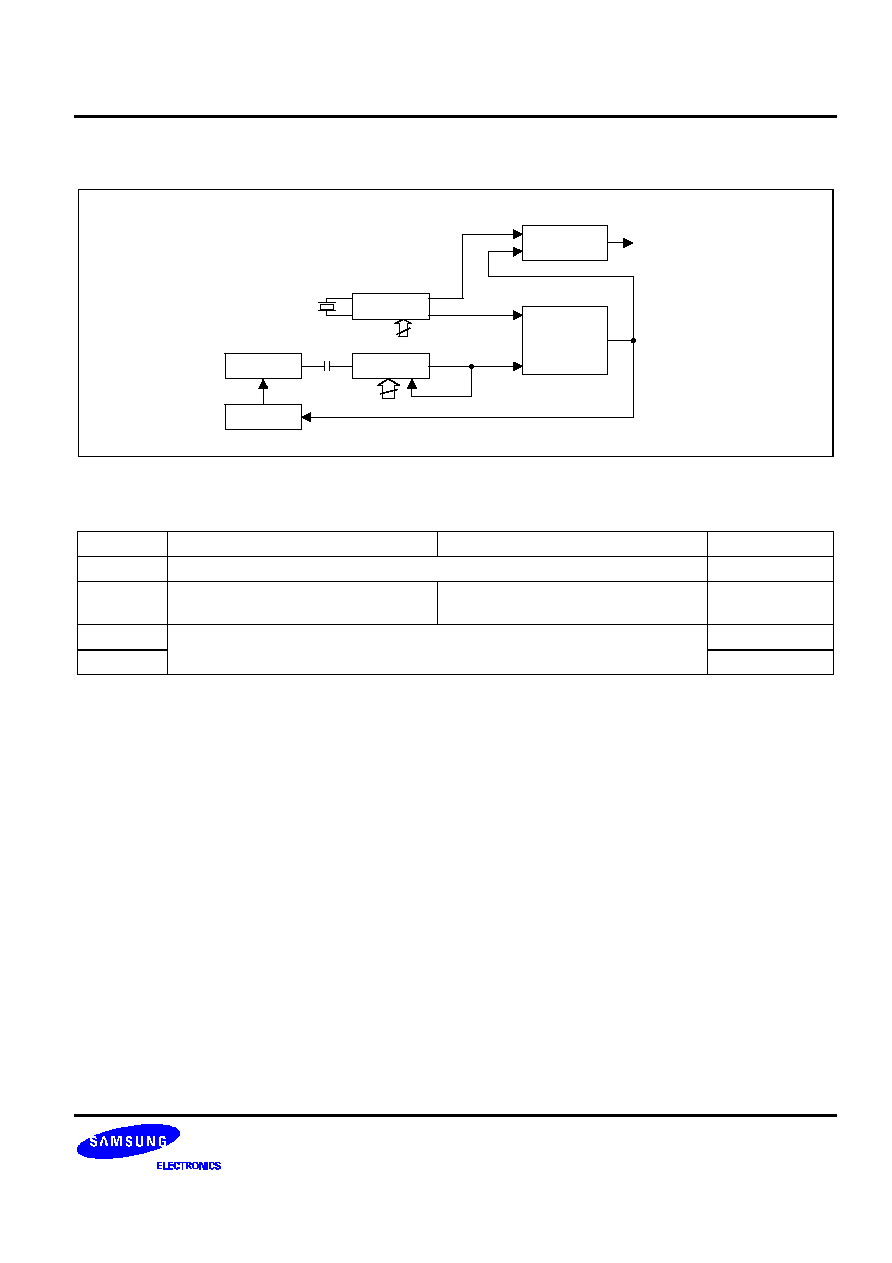

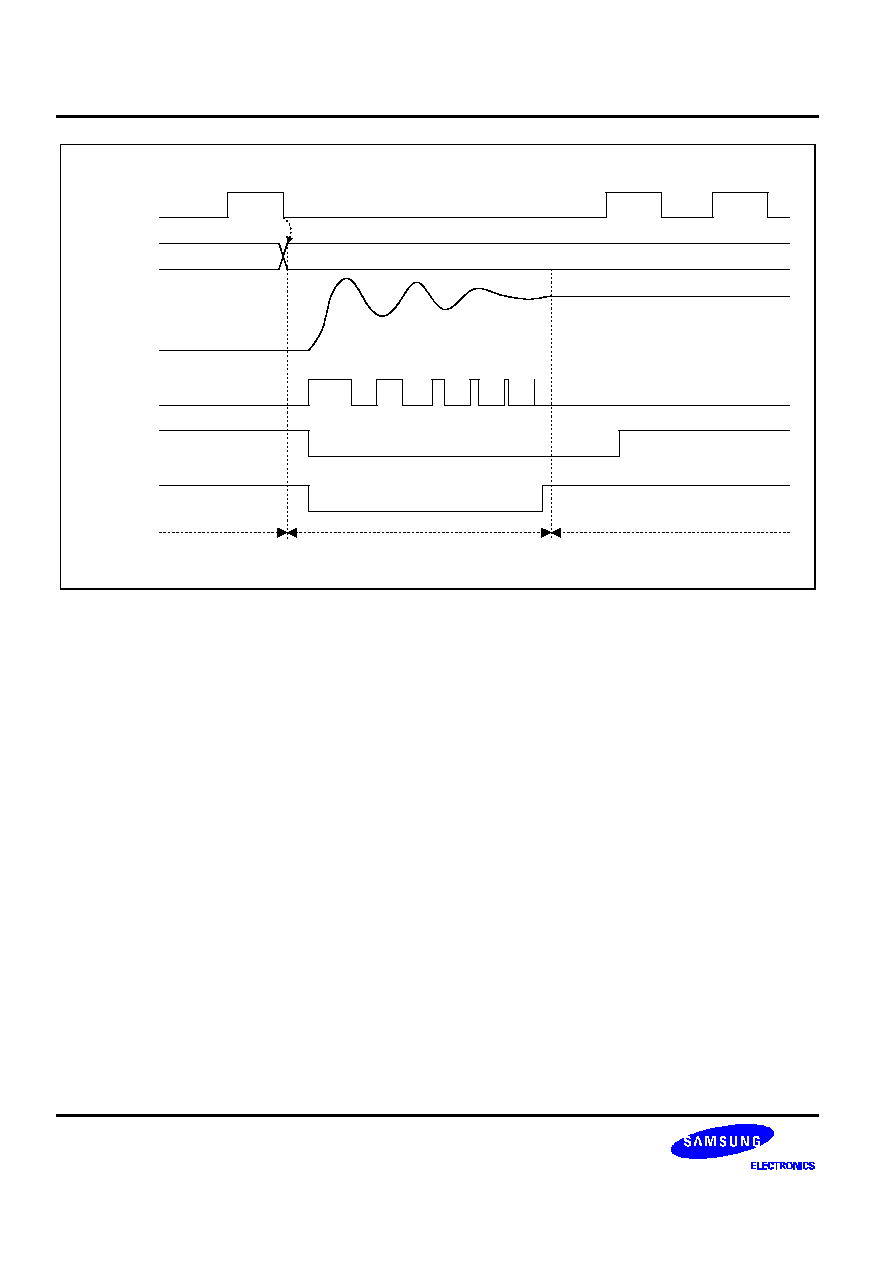

IF COUNTER

Count IF frequency during measurement time(GT[1:0]), start counting on IFCS setting high.

IF

GT

GT[1:0]

IF Counter

DSR

C[18:0]

IFCS

4/8/16/

32ms

LSB MSB

0 - 18

Figure 15. IF Counter Structure

∑

C[18:0] = F

IF

◊

GT : Counted value (the number of pulse)

GT1

GT0

Measurement time(GT)

GT1

GT0

Measurement time(GT)

0

0

4 ms

1

0

16 ms

0

1

8 ms

1

1

32 ms

GT

IFCS

Measurement

Time

IF

Frequency

Figure 16. IF counter operation

∑

In Figure. 16

When IFCS bit is zero, IF counter is reset. On IFCS bit is turning to one, IF counter starts to count IF

frequency during measurement time. Then IF counter holds the counted value. If DOC[1:0] is 3, inform

the micro- processor of the end of counting by means of setting DO pin to be low.

IF counter is automatically reset after sending serial data to Micro- processor and ready to count.

If IF frequency less than 45kHz(FM : 1.07MHz) comes into IF counter during first 100us of measurement

time(GT[1:0]), inform Micro-processor of the end of counting by means of setting DO pin to be low in the

case that DOC[1:0] is 3, even though measurement time isn't passed .

After measurement time(GT[1:0]) is passed, IFCS bit has to be held 1. Unless IFCS bit is held to be one,

counted IF value is all reset to be 0.

IFCS bit is automatically reset after Micro-processor reads the counted IF values.

S1A0903X01

AM/FM 1CHIP TUNER WITH PLL

32

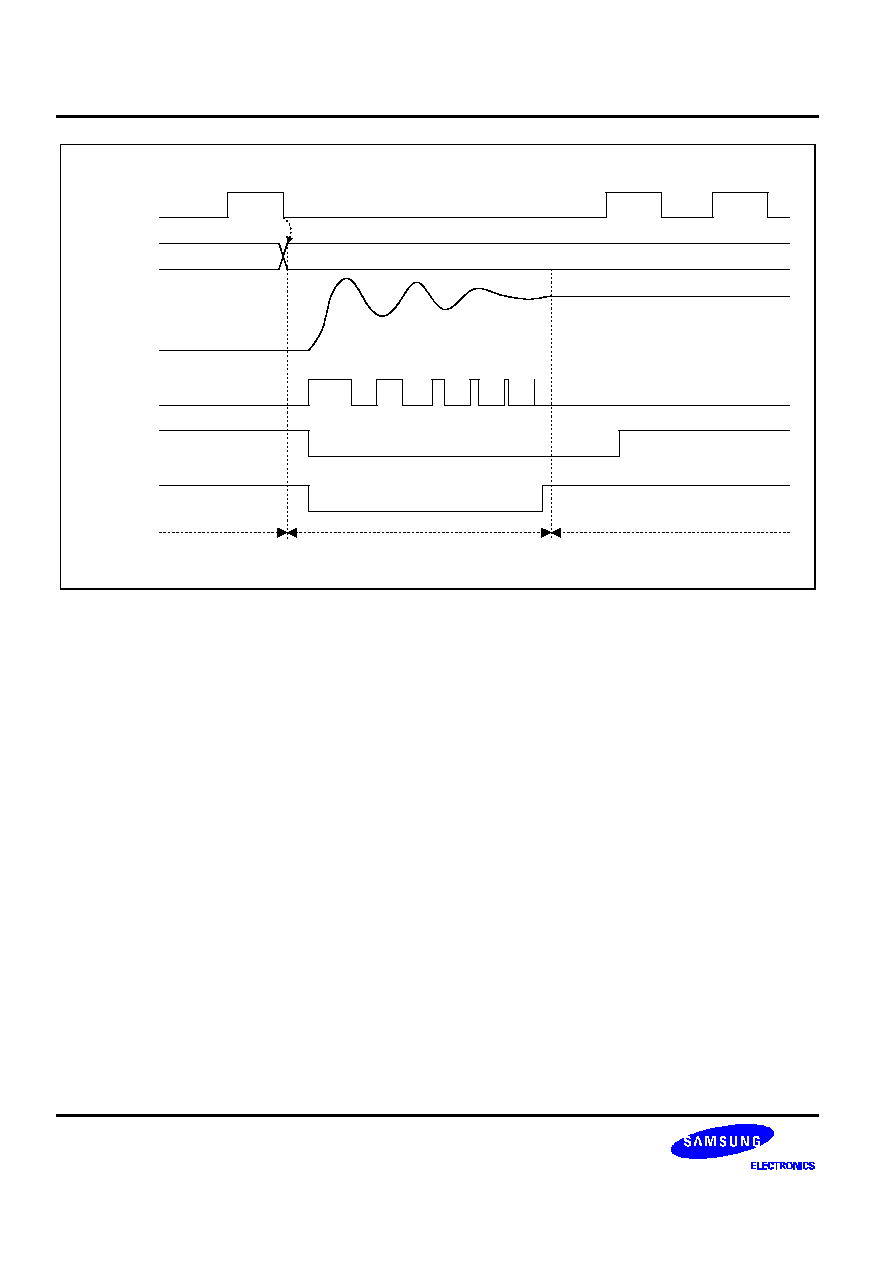

MPX VCO FREE-RUNNING-FREQUENCY SELF-ADJUSTING CONTROLLER

FMSW

PD[6:0]

1111110

TC

55.47ms

0.853ms

B

1111101

XXXXXXX

ADJUST

MODE

C

1111111

0.853ms

A

Figure 17. MPX VCO Free-Running Adjustment Timing Diagram

∑

Whenever band is switched to the FM mode, FM MPX VCO free-running frequency will be adjusted between

302.5kHz and 309.5kHz using control code PD[6:0]

∑

A region : wait time for MPX VCO to oscillate due to band switching.

∑

B region : measure MPX VCO free-running frequency and check whether free-running frequency is between

302.5kHz

309.5kHz or not. If MPX VCO free-running frequency is between 302.5kHz

309.5kHz, hold

the control code and end the adjusting.

∑

C region : reduce control code PD[6:0] into 1 step, make free-running frequency fast. If PD[6:0] is

1111111(bin), VCO frequency will be minimum frequency and If PD[6:0] is 0000000(bin), VCO frequency will

be maximum frequency.

∑

In adjusting MPX VCO free-running, MUTE will be set to one.

∑

The result of MPX VCO free-running adjust is out through TEST1 pin, when TEST[1:0] is zero.

TEST1 pin = 1 : operating VCO free-running adjustment

TEST1 pin = 0 : success adjusting VCO free-running between 302.5kHz

309.5kHz

TEST1 pin = 1.172kHz/2 : 1.172kHz/2 frequency is out when first adjustment cycle

(maximum adjustment time : 164.7ms / 1 cycle) is failed. Try to adjust VCO free-running on and on,

TEST1 pin is set to be zero when VCO free-running frequency is between 302.5kHz

309.5kHz

AM/FM 1CHIP TUNER WITH PLL

S1A0903X01

33

TEST FUNCTION

TEST[1:0]

TEST1 Pin

TEST2 Pin

TEST3 Pin

Remarks

IN

OUT

IN

OUT

OUT

0

-

ADJRESULT

-

-

-

(1)

1

-

TFCOUT

-

TFROUT

TMPXVCO

(2)

2

TIF

-

TLEDRSTB

-

TIFMINMAX

(2)

3

TFCIN

-

TFRIN

-

-

(2)

∑

ADJRESULT : out MPX VCO adjustment result

1 : on adjusting

0 : success in adjustment

1.172kHz : 1st. adjustment cycle is failed, but adjusting 2nd, 3rd adjustment cycle.

∑

TFCOUT : Fc Frequency divided by N[16:0]

∑

TIF : IF frequency comes in through external source for test

∑

TFCIN : Fc frequency comes in through external source for test

∑

TLEDRSTB : counter reset signal of tuning LED control block comes in through external source for test

∑

TFRIN : Fr frequency comes in through external source for test

∑

TFROUT : Fr frequency divided by R[4:0]

∑

TMPXVCO : MPX VCO free-running frequency which is end of adjusting

∑

TIFMINMAX : Minimum and maximum of IF frequency which is used to check tuning LED operation

TEST[1:0]=0 :inform the state of MPX VCO free-running adjustment

TEST[1:0]=1 : Fc frequency for testing N divider block, Fr frequency for testing X'tal divider block, MPX

VCO free-running frequency for testing MPX VCO self adjusting block

TEST[1:0]=2 : IF frequency, reset signal of LED control counter and IF Min. Max value for testing LED

control block

TEST[1:0]=3 : Fc and Fr frequency for testing PFD and LOCK detector

(1) : If A[1:0] is zero, send the IN1 MODE data latched in DSR to Micro- processor through DO pin

synchronized with falling edge of CL

(2) : If A[1:0] is zero, send the IN2 MODE data latched in DSR to Micro- processor through DO pin

synchronized with falling edge of CL

S1A0903X01

AM/FM 1CHIP TUNER WITH PLL

34

CHARACTERISTICS

ABSOLUTE MAXIMUM RATINGS

Parameter

Symbol

Ratings

Unit

Remarks

Supply Voltage

Vs

10

V

Operating Temperature

Top

-20

+75

∞

C

Storage Temperature

Tstg

-55

+150

∞

C

Power Dissipation

Pdmax

1800

mW

TEMPERATURE CHARACTERISTICS

Parameter

Symbol

Condition

Ratings

Unit

Remarks

Quiescent circuit current1(FM)

Icc1

-20

+75

∞

C

20

uA/

∞

C

Quiescent circuit current2(AM)

Icc2

-20

+75

∞

C

20

uA/

∞

C

ELECTRO_STATIC DISCHARGE CHARACTERISTICS

Parameter

Condition

Pin No.

Ratings

Unit

Remarks

Human Body Model

C = 100pF, R = 1.5k

ALL PINS

±

2000

V

Machine Model

C = 200pF, R = 0 k

ALL PINS

±

200

V

CDM

-

ALL PINS

±

500

V

AM/FM 1CHIP TUNER WITH PLL

S1A0903X01

35

ELECTRICAL CHARACTERISTICS

(Ta = 25

∞

C, Vcc = 3V. unless otherwise specified)

FM F/E : f = 98MHZ, fm = 1kHz,

f = 22.5kHz, AM : f = 1MHz, fm = 1kHz, 30% Mod

FM IF : f = 10.7MHZ, fm = 1kHz,

f = 22.5kHz, MPX : f = 1kHz, L+R = 90%, P = 10%, Vi = 150mV)

Parameter

Symbol

Condition

Ratings

Unit

Min.

Typ.

Max.

Supply Voltage Range

Vcc

2.0

-

7.0

V

Supply Current

Iccq1

FM, Vi = 0

6

13

18

mA

Iccq2

AM, Vi = 0

2.5

5

8

mA

F/E

Input Limiting

Voltage

Vi lim1

Vo = -3dB

-

12

18

dBu

Local Oscillation

Voltage

Vosc

fosc = 108.7MHz

40

70

110

mV

Input Limiting

Voltage

Vi lim2

Vo = -3dB

30

36

42

dBu

Detection Output

Voltage

Vo det1

Vi = 80dBu

60

80

110

mV

S/N Ratio

S/N1

Vi = 80dBu

55

65

-

dB

FM IF

AM Depression

Ratio

AMR

Vi = 80dBu

40

50

-

dB

THD

THD1

Vi = 80dBu

-

0.2

1.0

%

LED Turning On

Vl11

IFS[1:0] = 0

40

45

50

dB

µ

sensitivity

VI12

IFS[1:0] = 1

46

51

56

dB

µ

VI13

IFS[1:0] = 2

52

57

62

dB

µ

VI14

IFS[1:0] = 3

58

63

68

dB

µ

Voltage Gain

Gv1

Vi = 26dBu

30

55

-

mV

AM

RF

Detection Output

Voltage

Vo det2

Vi = 60dBu

60

85

110

mV

LED Turning On

Vl21

IFS[1:0] = 0

22

27

32

dB

µ

VI22

IFS[1:0] = 1

28

33

38

dB

µ

VI23

IFS[1:0] = 2

32

37

42

dB

µ

VI24

IFS[1:0] = 3

36

41

46

dB

µ

AM IF

S/N Ratio

S/N2

Vi = 60dBu

32

42

-

dB

THD

THD2

Vi = 60dBu

-

1

2

%

S1A0903X01

AM/FM 1CHIP TUNER WITH PLL

36

ELECTRICAL CHARACTERISTICS (Continued)

(Ta = 25

∞

C, Vcc = 3V. unless otherwise specified)

FM F/E : f = 98MHZ, fm = 1kHz,

f = 22.5kHz, AM : f = 1MHz, fm = 1kHz, 30% Mod

FM IF : f = 10.7MHZ, fm = 1kHz,

f = 22.5kHz, MPX : f = 1kHz, L+R = 90%, P = 10%, Vi = 150mV)

Parameter

Symbol

Condition

Ratings

Unit

Min.

Typ.

Max.

Maximum Input Voltage

Vimax

Stereo, THD = 3%

300

450

-

mV

Voltage Gain

Gv2

-5

-1

0.5

dB

Channel Balance

CB

Mono

-1.5

0

1.5

dB

THD1

THD3

Mono

-

0.2

1.0

%

MPX

THD2

THD4

Stereo

-

0.2

1.0

%

Separation 1

CS1

Stereo, f=100Hz

25

35

-

dB

Separation 2

CS2

Stereo, f=1kHz

25

35

-

dB

Separation 3

CS3

Stereo, f=10kHz

25

35

-

dB

LED Turning On

Sensitivity

Vlon

TUNLED=ON,

Pilot only

-

8

16

mV

LED Turning Off

Sensitivity

Vloff

TUNLED = OFF,

Pilot only

1

6

-

mV

Lamp Hysteresis

HY

-

2

-

mV

Capture Range

CR

Pilot only

-

4

-

%

S/N Ratio

S/N3

Mono

60

70

-

dB

Mute Attenuation

Amute

65

75

-

dB

Input

High Level

Vih

CE, DI, CL

0.7Vreg

-

-

V

Voltage

Low Level

Vil

CE, DI, CL

0

-

0.3Vreg

V

Output

High Level

Voh1

PD : lo=-1mA

0.7Vreg

-

-

V

Voltage

Low Level

Vol1

PD : lo=1mA

-

-

0.3Vreg

V

Vol2

DO : lo=5mA

0

-

0.3Vreg

V

DTS

Output Voltage Range

Vo

Aout

0

-

9

V

Internal Feedback

Registance

Rf

XIN

-

0.4

-

M

Input Current

Iin1

CE, DI, CL=VDD or

GND

-

-

5

µ

A

Iin2

XIN=VDD or GND

1.3

-

8

µ

A

Idd1

X'tal=10.8MHz,

FM=130MHz

-

2.5

6

mA

Supply Current

Idd2

PLL stop mode,

X'tal=10.8MHz

-

0.3

-

mA

Idd3

PLL stop mode,

X'tal stop mode

-

-

10

µ

A

AM/FM 1CHIP TUNER WITH PLL

S1A0903X01

37

TEST CIRCUIT

44-QFP

34

35

36

37

38

39

40

41

42

43

44

1

2

3

4

5

6

7

8

9

10

11

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

CE

DI

CL

DO

micro-

processor

TEST IN

B.P.F

19kHz

BRF

0.022uF 2k

AMRFIN

FMRFIN

330

0.47uF

IFT1

1uF

450k

10.7M

F2

330

VCC1

FMIFIN

AMIFIN

220uF

0.1uF

0.1

µ

F

GND

4.7uF

4.7uF

DETOUT

MPXIN

0..1uF

3.3uF

0.33

µ

F

10.7M

F3

OUT

4.7uF

4.7uF

0.015uF

560

560

VCC2

10K

0.047

µ

F

1uF

2.2K

0.022

µ

F

10K

X_SW

20pF

20pF

TEST1

TEST2

TEST3

TEST OUT

0.1uF

10uF

2.2uF

68pF

4.7K

VD1

L1

0.1uF

220uF

33K

VD4

470pF

T1

220uF

0.1uF

4.7K

68pF

VD2

L2

2.7mH

10K

S1A0903X01

F1

0.015uF

S1A0903X01

AM/FM 1CHIP TUNER WITH PLL

38

TEST CIRCUIT

48-LQFP

34

37

38

39

40

41

42

43

44

1

2

3

4

5

6

7

8

9

10

11

33

32

31

30

29

28

27

26

24

23

21

20

19

18

16

15

14

13

CE

DI

CL

DO

micro-

processor

TEST IN

B.P.F

19kHz

BRF

0.022uF 2k

AMRFIN

FMRFIN

330

0.47uF

IFT1

1uF

450k

10.7M

F2

330

VCC1

FMIFIN

AMIFIN

220uF

0.1uF

0.1

µ

F

GND

4.7uF

4.7uF

DETOUT

MPXIN

0..1uF

3.3uF

0.33

µ

F

10.7M

F3

OUT

4.7uF

4.7uF

0.015uF

560

560

VCC2

10K

0.047

µ

F

1uF

2.2K

0.022

µ

F

10K

X_SW

20pF

20pF

TEST1

TEST2

TEST3

TEST OUT

0.1uF

10uF

2.2uF

68pF

4.7K

VD1

L1

0.1uF

220uF

33K

VD4

470pF

T1

220uF

0.1uF

4.7K

68pF

VD2

L2

2.7mH

10K

S1A0903X01

F1

0.015uF

12

17

22

25

35

36

45

46

47

48

NC

AM/FM 1CHIP TUNER WITH PLL

S1A0903X01

39

APPLICATION CIRCUIT

44-QFP

34

35

36

37

38

39

40

41

42

43

44

1

2

3

4

5

6

7

8

9

10

11

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

CE

DI

CL

DO

micro-

processor

B.P.F

FM

Antenna

330

0.47uF

IFT1

1uF

450k

10.7M

F2

VCC1

220uF

0.1uF

0.1uF

GND

3.3uF

0.33uF

10.7M

F3

560

560

VCC2

10K

0.047

µ

F

1uF

2.2K

0.022

µ

F

10K

20pF

20pF

NC

0.1uF

10uF

2.2uF

68pF

4.7K

VD1

L1

0.1uF

220uF

33K

VD4

470pF

T1

220uF

0.1uF

4.7K

68pF

VD2

L2

10K

S1A0903X01

F1

1000p

4.7u

LOUT

0.015

µ

F

4.7uF

ROUT

4.7uF

7.2M

NC

NC

NC

20pF

10pF

12pF

33K

AM

Antenna

VD3

22nF

0.015

µ

F

B.P.F

: GFMG7 (KOREA SANGSHIN ELECTRIC Co.Ltd)

F1 (450kHz)

: 450 BL(Toko co.Ltd)

F2 (10.7MHz)

: SFE 10.7MA5 (MURATA Co.Ltd)

F3 (10.7MHz)

: CDALA10M7GA115A-B0 (MURATA Co.Ltd)

VD1, VD2

: KV1471 (Toko co.Ltd)

VD3, VD4

: KV1236 (Toko co.Ltd)

S1A0903X01

AM/FM 1CHIP TUNER WITH PLL

40

APPLICATION CIRCUIT

48-LQFP

34

35

36

41

42

43

44

45

46

47

48

1

2

3

4

5

6

7

8

9

10

11

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

CE

DI

CL

DO

micro-

processor

B.P.F

FM

Antenna

330

0.47uF

IFT1

1uF

450k

10.7M

F2

VCC1

220uF

0.1uF

0.1uF

GND

3.3uF

0.33uF

10.7M

F3

560

560

VCC2

10K

0.047

µ

F

1uF

2.2K

0.022

µ

F

10K

20pF

20pF

NC

0.1uF

10uF

2.2uF

68pF

4.7K

VD1

L1

0.1uF

220uF

33K

VD4

470pF

T1

220uF

0.1uF

4.7K

68pF

VD2

L2

10K

S1A0903X01

F1

1000p

4.7u

LOUT

0.015

µ

F

4.7uF

ROUT

4.7uF

7.2M

NC

NC

NC

20pF

10pF

12pF

33K

AM

Antenna

VD3

22nF

0.015

µ

F

12

NC

NC

NC

39

40

37

38

NC

B.P.F

: GFMG7 (KOREA SANGSHIN ELECTRIC Co.Ltd)

F1 (450kHz)

: 450 BL(Toko co.Ltd)

F2 (10.7MHz)

: SFE 10.7MA5 (MURATA Co.Ltd)

F3 (10.7MHz)

: CDALA10M7GA115A-B0 (MURATA Co.Ltd)

VD1, VD2

: KV1471 (Toko co.Ltd)

VD3, VD4

: KV1236 (Toko co.Ltd)

AM/FM 1CHIP TUNER WITH PLL

S1A0903X01

41

0.5

1.0

2.0

4.0

8.0

16.0

40

50

60

70

80

90

100

THD

(%)

RF Input Level

(dBu)

AM RF THD -RF Level

Vcc=3V

fin=1MHz

fm=1kHz,MOD=30%

0

0.5

1

1.5

2

2.5

3

3.5

4

4.5

5

5.5

6

2

3

4

5

6

7

8

9

Iccq2

(mA)

Vcc (V)

AM Iccq - Vcc

Vcc=3V

fin=1MHz

0

25

50

75

100

125

150

175

200

225

250

0

10

20

30

40

50

60

70

80

90

Voa1,

Voa2

(dB)

AM Modulation

(%)

AM RF Voa1,Voa2 - Modulation Level

Vcc=3V

fin=1MHz

fm=1kHz

Voa1 = RF IN 26dBu

Voa2 = RF IN 60dBu

Voa2

Voa1

-60

-50

-40

-30

-20

-10

0

10

20

0

10 20

30 40

50 60 70

80 90 100

RF Input Level (dBu)

AM RF Voa2,S/Na -RF Level

Vcc=3V

fin=1MHz

fm=1kHz,MOD=30%

Voa2,

S/Na

(dB)

Voa2

S/Na

AM Modulation

(%)

0.0

0.2

0.4

0.6

0.8

1.0

1.2

1.4

1.6

1.8

0

10

20 30 40 50 60 70 80

90

THD

(%)

AM RF THD - Modulation Level

Vcc=3V

fin=1MHz

fm=1kHz

RF IN 60 dBu

-5

-4

-3

-2

-1

0

1

2

3

4

5

3

4

5

6

7

8

9

Voa2

(dB)

Vcc (V)

AM Voa2 - Vcc

Vcc=3V

fin=1MHz

fm=1kHz,MOD=30%

Voa2=RF IN 60dBu

S1A0903X01

AM/FM 1CHIP TUNER WITH PLL

42

0.0

0.2

0.4

0.6

0.8

1.0

1.2

1.4

1.6

THDf

(%)

RF Input Level (dBu)

FM RF+IF THDf-RF Level

Vcc=3V

fin=98MHz

fm=1kHz

f=22.5kHz

-20

0

20

30

40

50

60

70

80

90

100

-60

-50

-40

-30

-20

-10

0

10

Vof,S/Nf

(dB)

RF Input Level (dBu)

FM RF+IF Vof,S/Nf - RF Level

Vof

S/Nf

Vcc=3V

fin=98MHz

fm=1kHz

f=22.5kHz

-20

-10

0

10

20

30

40

50

60

70

80

90

100

0.0

0.5

1.0

1.5

2.0

2.5

THDf

(%)

IF Input Level (dBu)

FM IF THD - IF Level

Vcc=3V

fin=10.7MHz

fm=1kHz

f=22.5kHz

-20

45

65

85

110

-60

-50

-40

-30

-20

-10

0

10

Vof,

S/Nf

(dB)

FM IF Vof,S/Nf - IF Level

Vcc=3V

fin=10.7MHz

fm=1kHz

f=22.5kHz

IF Input Level (dBu)

Vof

S/Nf

-20

20

40

60

80

100

FM Icc - Vcc

0

2

4

6

8

10

12

0

2

4

6

8

10

Icc

(mA)

Vcc (V)

AM/FM 1CHIP TUNER WITH PLL

S1A0903X01

43

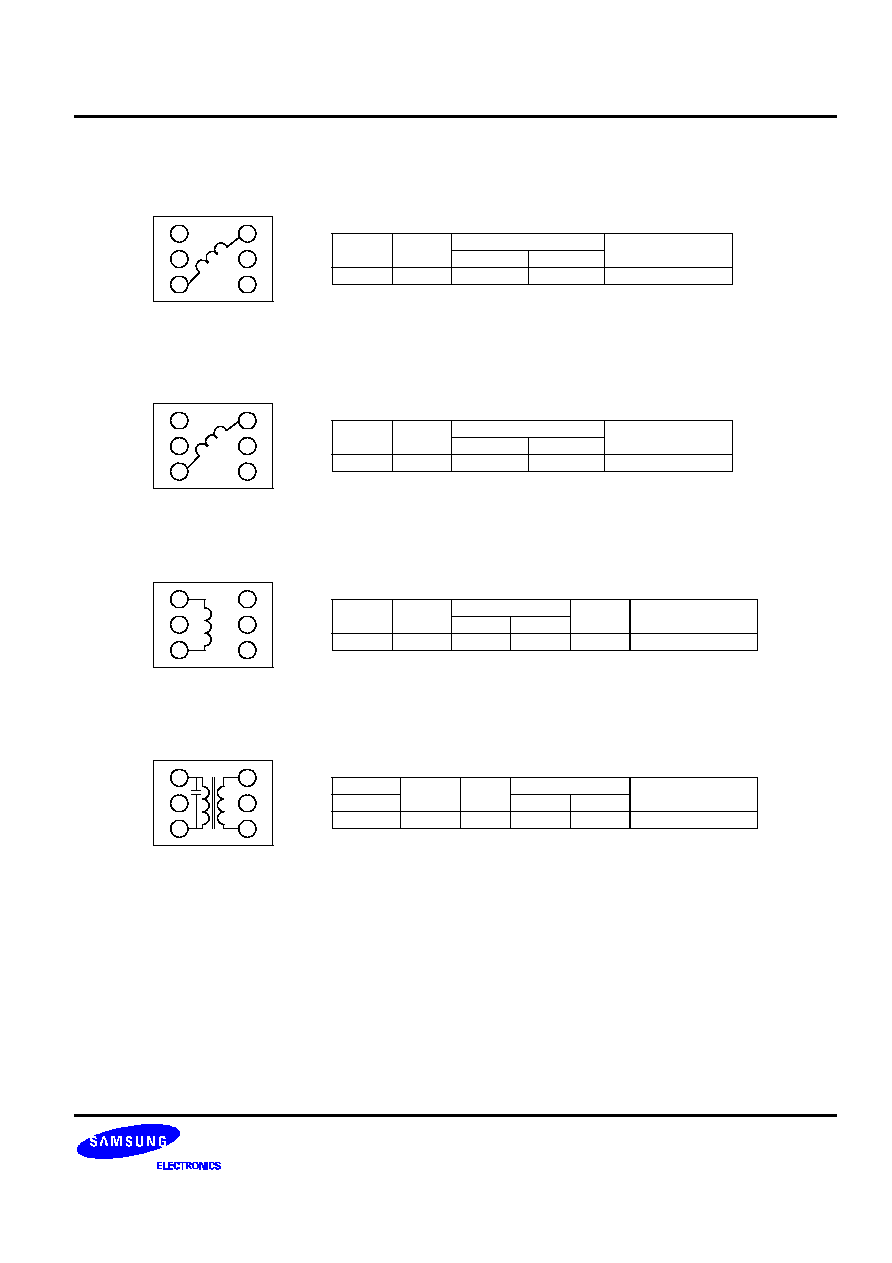

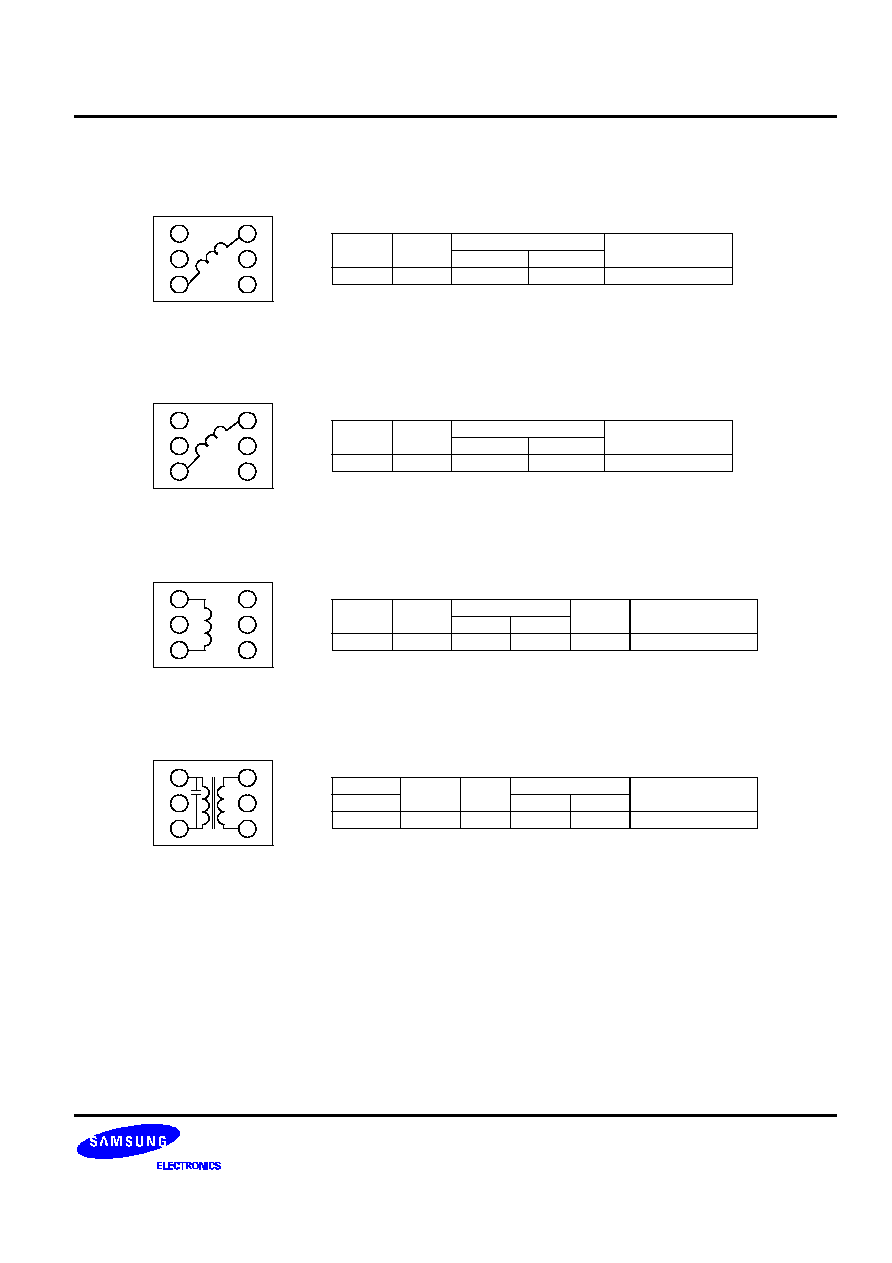

3

2

1

4

5

6

f

(MHz)

100

Qo

80

TURNS

1-4

WIRE

7*(1/2)

0.45m/m

KWANG SUNG

PART NO

SP-2065

FM RF

3

2

1

4

5

6

f

(MHz)

100

Qo

80

TURNS

1-4

WIRE

6*(1/2)

0.45m/m

KWANG SUNG

PART NO

SP-2066

FM OSC

SP-2065

SP-2066

3

2

1

4

5

6

f

(MHz)

796

Qo

50

TURNS

1-3

WIRE

84

KWANG SUNG

PART NO

KS50N-354

AM OSC

KS50N-354

L

(uH)

110

3

2

1

4

5

6

Co (pF)

470

Qo

40

TURNS

1-3

4-6

115

5

KWANG SUNG

PART NO

KS50N-SAA

AM IFT (MIX OUT)

KS50-SAA

1-3

f

(MHz)

455

S1A0903X01

AM/FM 1CHIP TUNER WITH PLL

44

PACKAGE DIMENSIONS

44-QFP

44-QFP-1010B

#44

NOTE: Dimensions are in millimeters.

10.00

+ 0.20

13.20

+ 0.30

10.00

+

0.20

13.20

+

0.30

#1

0.35

+ 0.10

- 0.05

0.80

0.10 MAX

0.80

+

0.20

0.05 MIN

2.05

+ 0.10

2.30 MAX

0.15

+ 0.10

- 0.05

0-8

0.15 MAX

(1.00)

AM/FM 1CHIP TUNER WITH PLL

S1A0903X01

45

PACKAGE DIMENSIONS

48-LQFP

#48

7.00 BSC

9.00 BSC

7.00 BSC

9.00 BSC

0.08 MAX

0.09 - 2.20

0-7

NOTE: Dimensions are in millimeters.

#1

0.20

+ 0.07

- 0.03

0.50 BSC

0.08 MAX

0.60

+

0.15

0.10

+ 0.05

1.40

+ 0.05

1.60 MAX

M

S1A0903X01

AM/FM 1CHIP TUNER WITH PLL

46

TERMONOLOGY

DeadZone

PFD has to detect subtle phase error and makes phase error signal. There is a region that PFD doesn't make any

phase error pulse due to the propagation delay or other factors, which is called Deadzone.

Performance of PLL frequency synthesizer depends on the width of DeadZone

The characteristic of PFD is not ideal A(Figure. 18) but curved B(Fig. 18) because PLL frequency synthesizer

operates on reference signal just like a LPF(low pass filter)

The cause of Deadzone is that PFD doesn't generate phase error signal even though there is a phase error

between reference frequency and VCO divided by N. In general deadzone has several nano seconds width.

To implement a high S/N ratio system, the width of Deadzone is as narrow as possible. But, RF leakage in

MIXER block comes into VCO, which causes be a noise.

(ns)

V

A

B

DeadZone

Figure 18. PFD Characteristic

AM/FM 1CHIP TUNER WITH PLL

S1A0903X01

47

Application Note

1. Recommend using filter with 330

I/O impedance as 10.7MHz IF filter

2. Output gain of RF mixer is fixed by both of 330

register on PIN33 and parallel register of input impedance on

10.7MHz IF filter. Thereafter to control output gain of mixer depends on changing load register on PIN 34, which

case both of input impedance of IF filter and load register are recommended to have same impedance.

3. Application of a input pin CE, DI, CL depends on the output of Micro-processor(Figure. 19). Input pin of CE,

CL, DI must be set to be VDD using R1 and R2 In the case of Figure.19 <B>.

VREG

100K

VREG

R2

VDD

R1

S1A0903X01

MICOM

CL,DI,CE

(13,14,15)

MICOM

CL,DI,CE

(13,14,15)

< A >

< B >

S1A0903X01

21

Figure 19. Connection between SIO and Microprocessor

4. Crystal can be selectable among 75kHz, 3.6MHz, 7.2MHz, 10.8MHz. The connection must be the same as

Figure. 20 to share crystal for Micro-processor

XIN

MICOM

S1A0903X01

11

Figure 20. Connection X'tal for Micro-processor

S1A0903X01

AM/FM 1CHIP TUNER WITH PLL

48

NOTES