| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: S3C9688 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Document Outline

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

S3C9688/P9688

PRODUCT OVERVIEW

1-1

1

PRODUCT OVERVIEW

SAM88RCRI PRODUCT FAMILY

Samsung's SAM88RCRI family of 8-bit single-chip CMOS microcontrollers offers a fast and efficient CPU, a wide range of integrated

peripherals, and various mask-programmable ROM sizes.

A dual address/data bus architecture and a large number of bit- or nibble-configurable I/O ports provide a flexible programming environment for

applications with varied memory and I/O requirements. Timer/counters with selectable operating modes are included to support real-time

operations. Many SAM88RCRI microcontrollers have an external interface that provides access to external memory and other peripheral

devices.

S3C9688/P9688 MICROCONTROLLER

The S3C9688/P9688 single-chip 8-bit microcontroller is fabricated using an advanced CMOS process. It is built around the powerful

SAM88RCRI CPU core.

Stop and Idle power-down modes were implemented to reduce power consumption. To increase on-chip register space, the size of the internal

register file was logically expanded. The S3C9688 has 8 K bytes of program memory on-chip.

Using the SAM88RCRI design approach, the following peripherals were integrated with the SAM88RCRI core:

-- Five configurable I/O ports (32 pins)

-- 20 bit-programmable pins for external interrupts

-- 8-bit timer/counter with three operating modes

-- Low speed USB function

The S3C9688/P9688 is a versatile microcontroller that can be used in a wide range of low speed USB support general purpose applications. It

is especially suitable for use as a keyboard controller and is available in a 42-pin SDIP and a 44-pin QFP package.

OTP

The S3C9688/P9688 microcontroller is also available in OTP (One Time Programmable) version, S3P9688. S3P9688 microcontroller has an

on-chip 8-Kbyte one-time-programmable EPROM instead of masked ROM. The S3P9688 is comparable to S3C9688/P9688, both in function

and in pin configuration.

PRODUCT OVERVIEW

S3C9688/P9688

1-2

FEATURES

CPU

∑

SAM88RCRI CPU core

Memory

∑

8 K byte internal program memory (ROM)

∑

208 byte RAM

Instruction Set

∑

41 instructions

∑

IDLE and STOP instructions added for power-down modes

Instruction Execution Time

∑

0.66

µ

s at 6 MHz f

OSC

Interrupts

∑

29 interrupt sources with one vector, each source has its

pending bit

∑

One level, one vector interrupt structure

Oscillation Circuit

∑

6 MHz crystal/ceramic oscillator

∑

External clock source (6 MHz)

∑

Embedded oscillation capacitor (XI, XO, 33pF)

General I/O

∑

Bit programmable five I/O ports (34 pins total)

-- (D+/PS2, D-/PS2 Included)

Timer/Counter

∑

One 8-bit basic timer for watchdog function and

programmable oscillation stabilization interval generation

function

∑

One 8-bit timer/counter with Compare/Overflow

USB Serial Bus

∑

Compatible to USB low speed (1.5 Mbps) device 2.0

specification.

∑

1 Control endpoint and 2 Interrupt endpoint

∑

Serial bus interface engine (SIE)

-- Packet decoding/generation

-- CRC generation and checking

-- NRZI encoding/decoding and bit-stuffing

∑

8 bytes each receive/transmit USB buffer

Low Voltage Reset

∑

Low voltage detect for RESET

∑

Power on Reset

Operating Temperature Range

∑

≠ 40

∞

C to + 85

∞

C

Operating Voltage Range

∑

4.0 V to 5.25 V

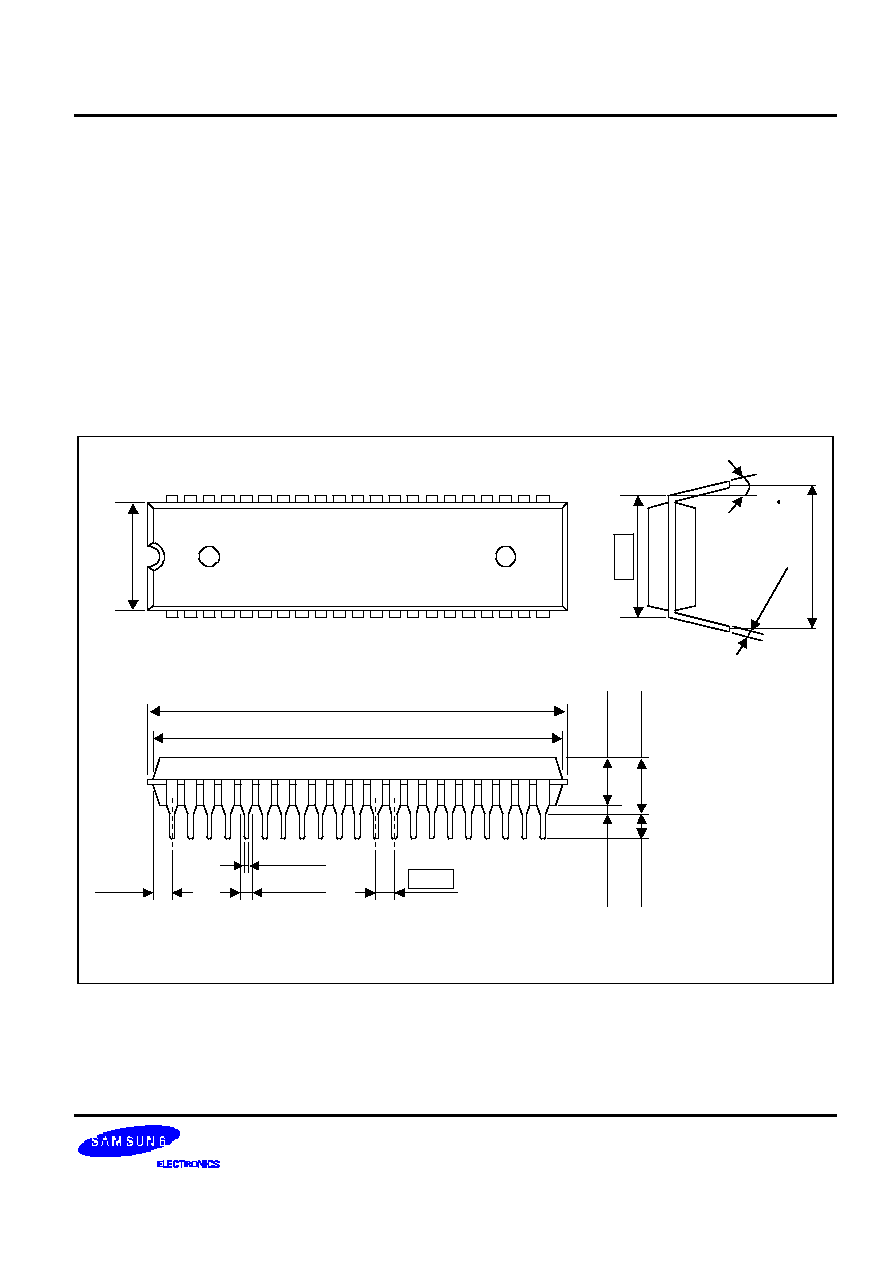

Package Types

∑

42-pin SDIP

∑

44-pin QFP

S3C9688/P9688

PRODUCT OVERVIEW

1-3

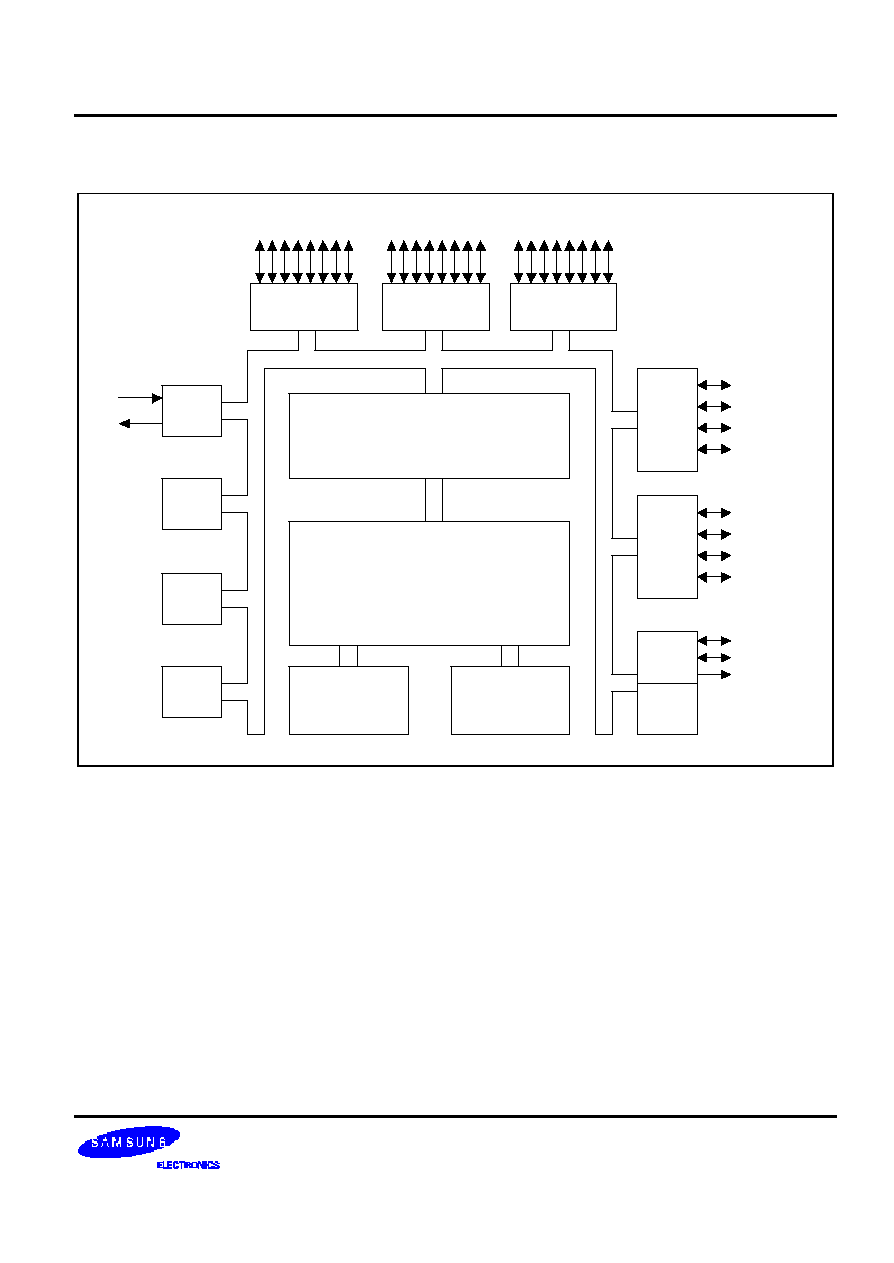

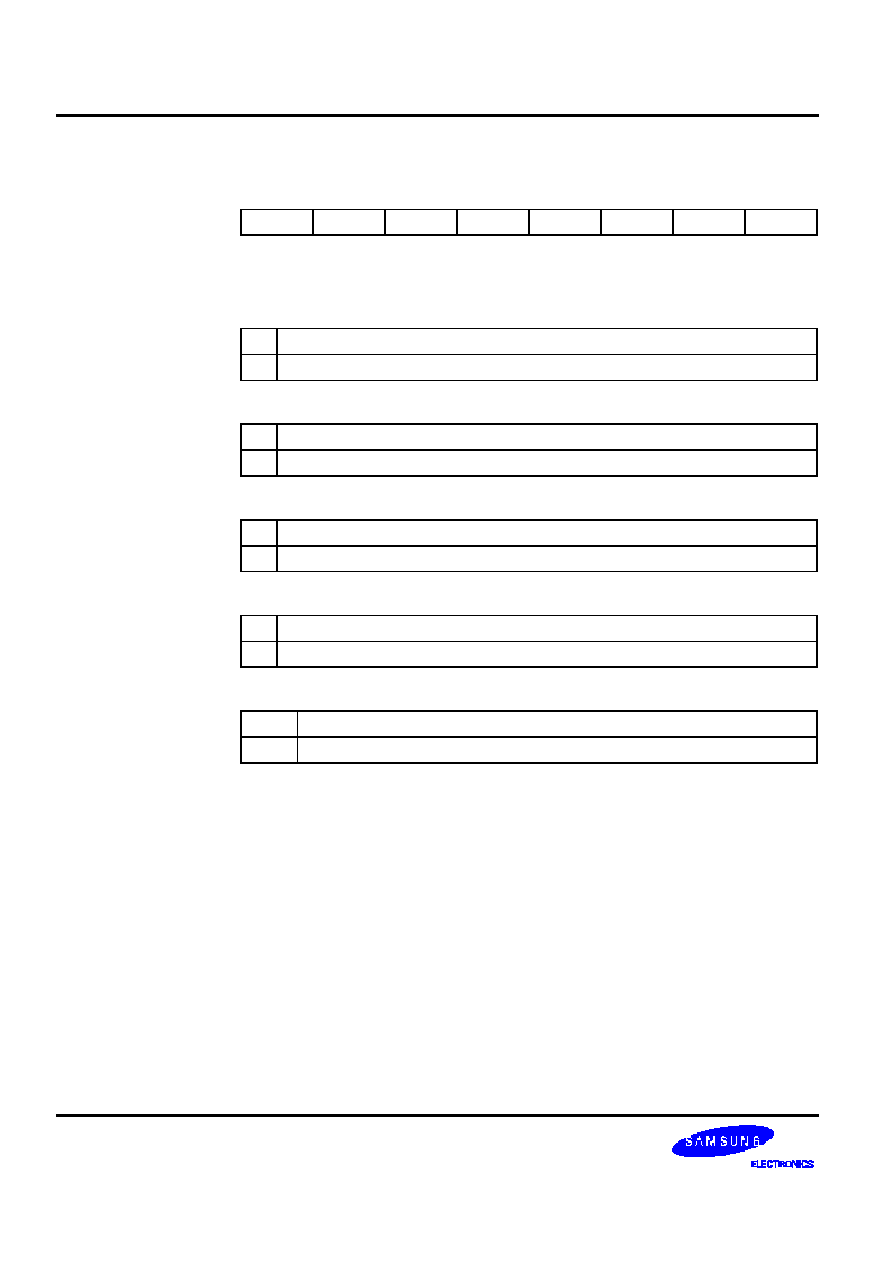

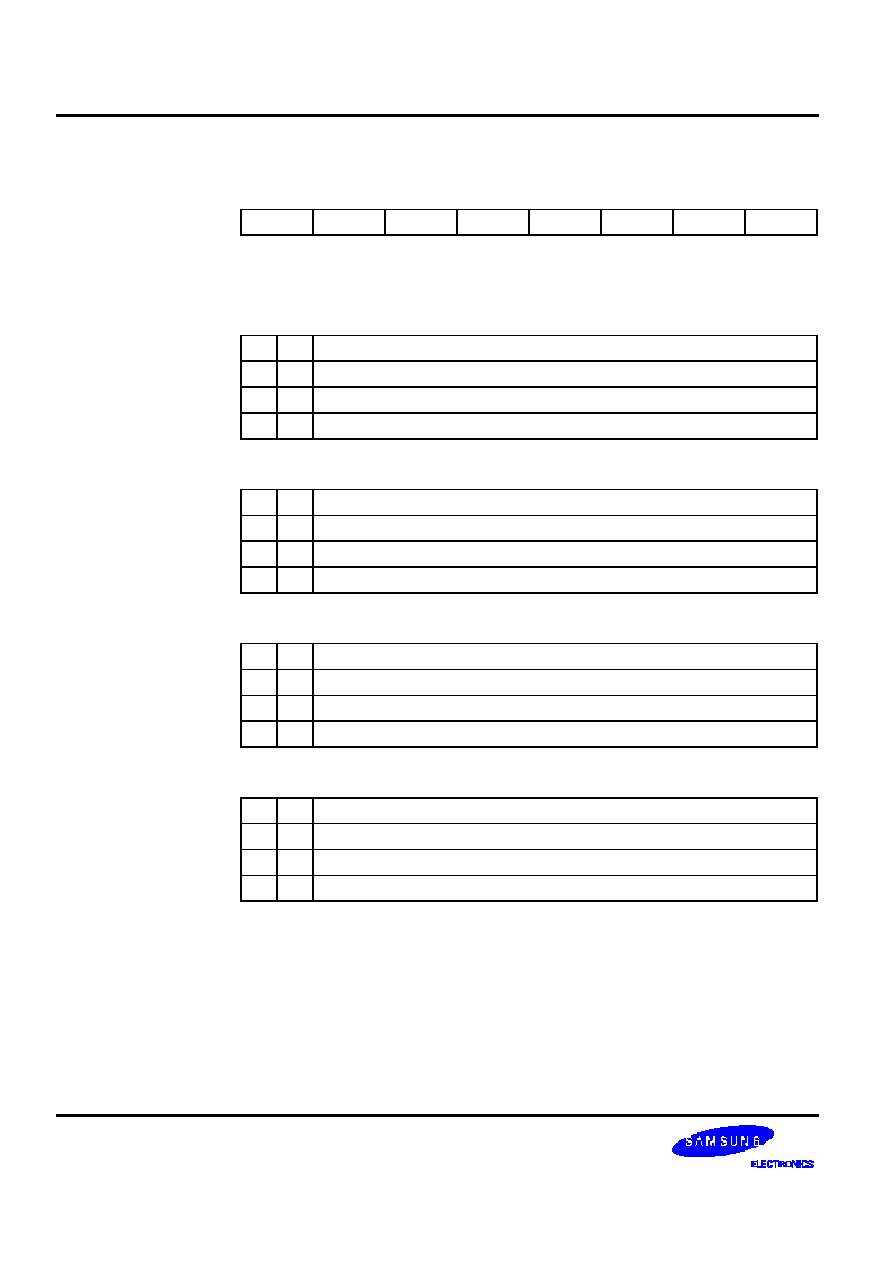

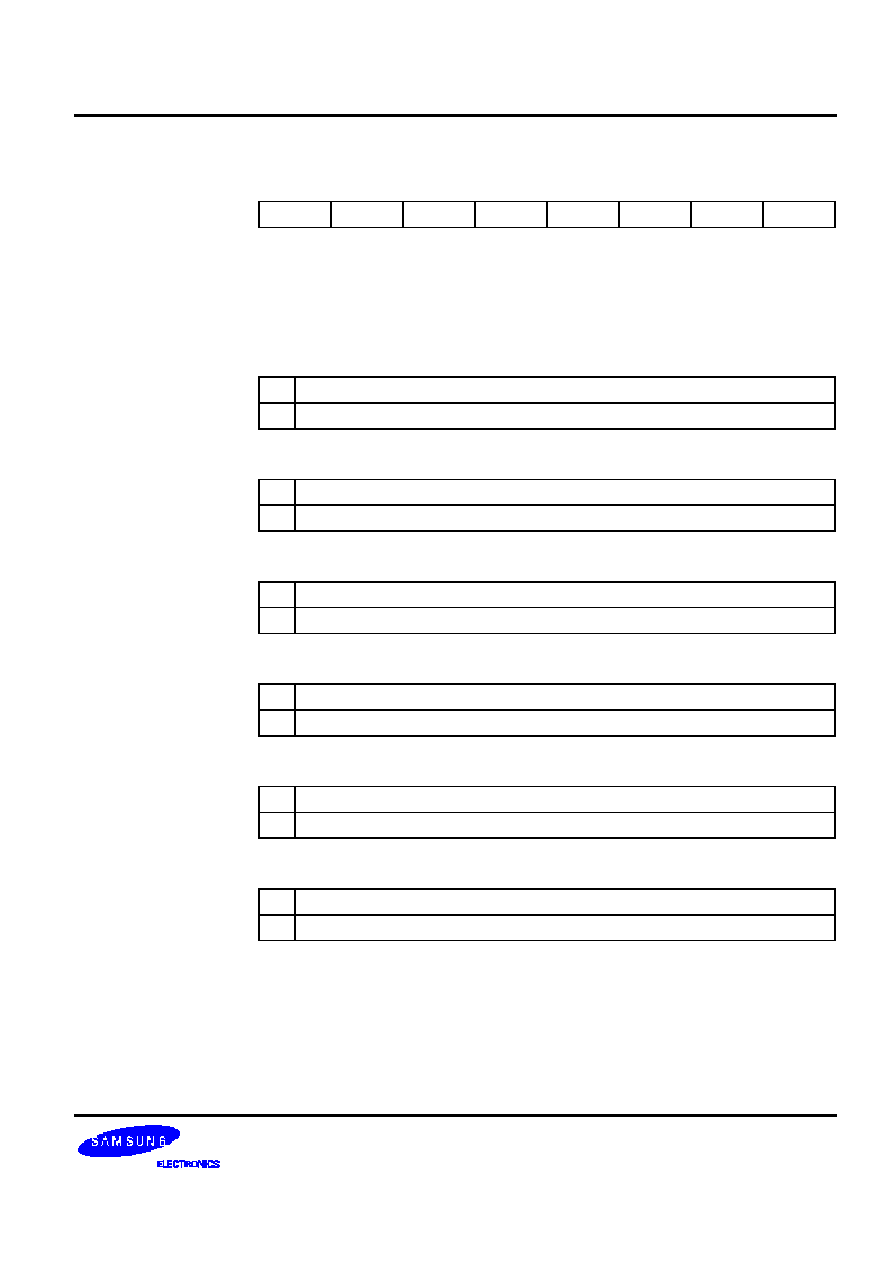

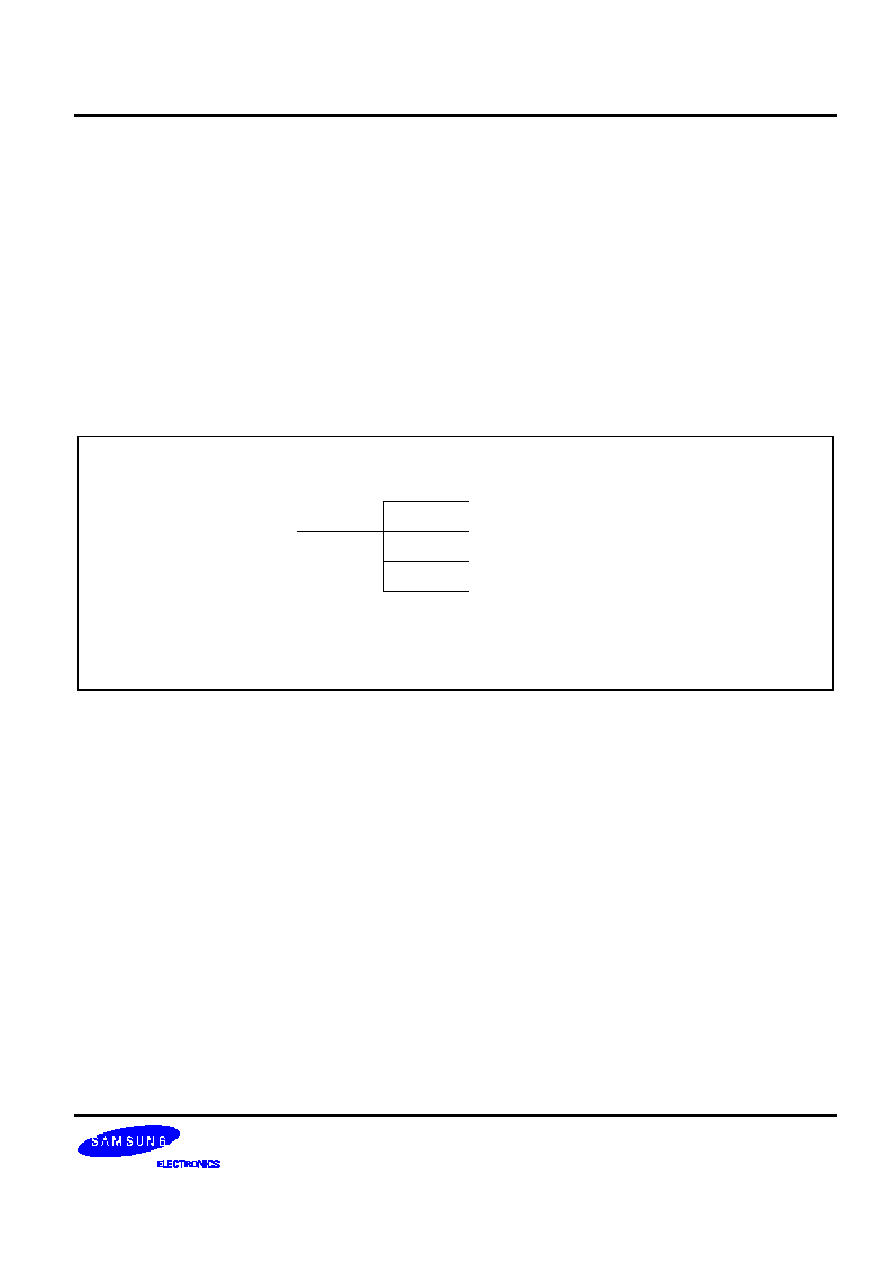

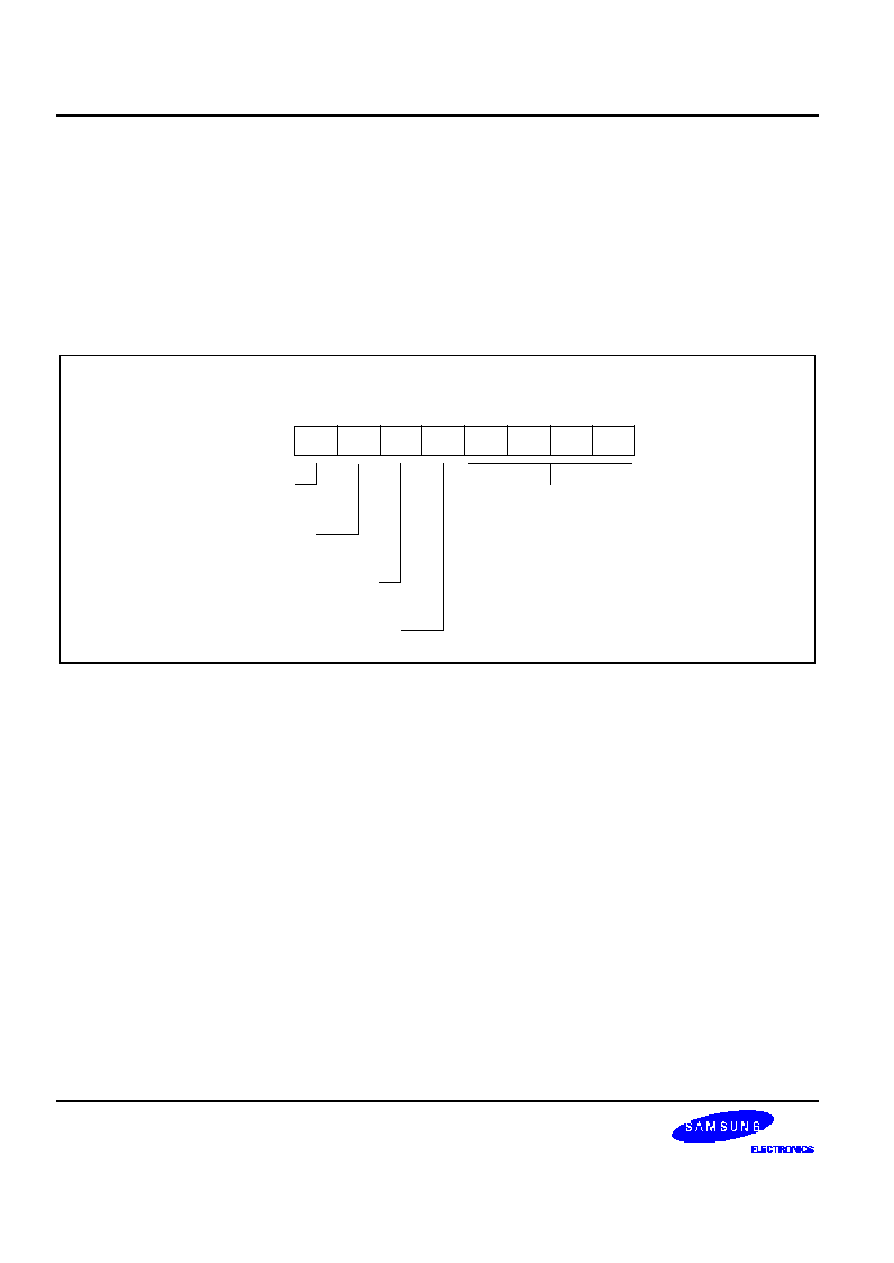

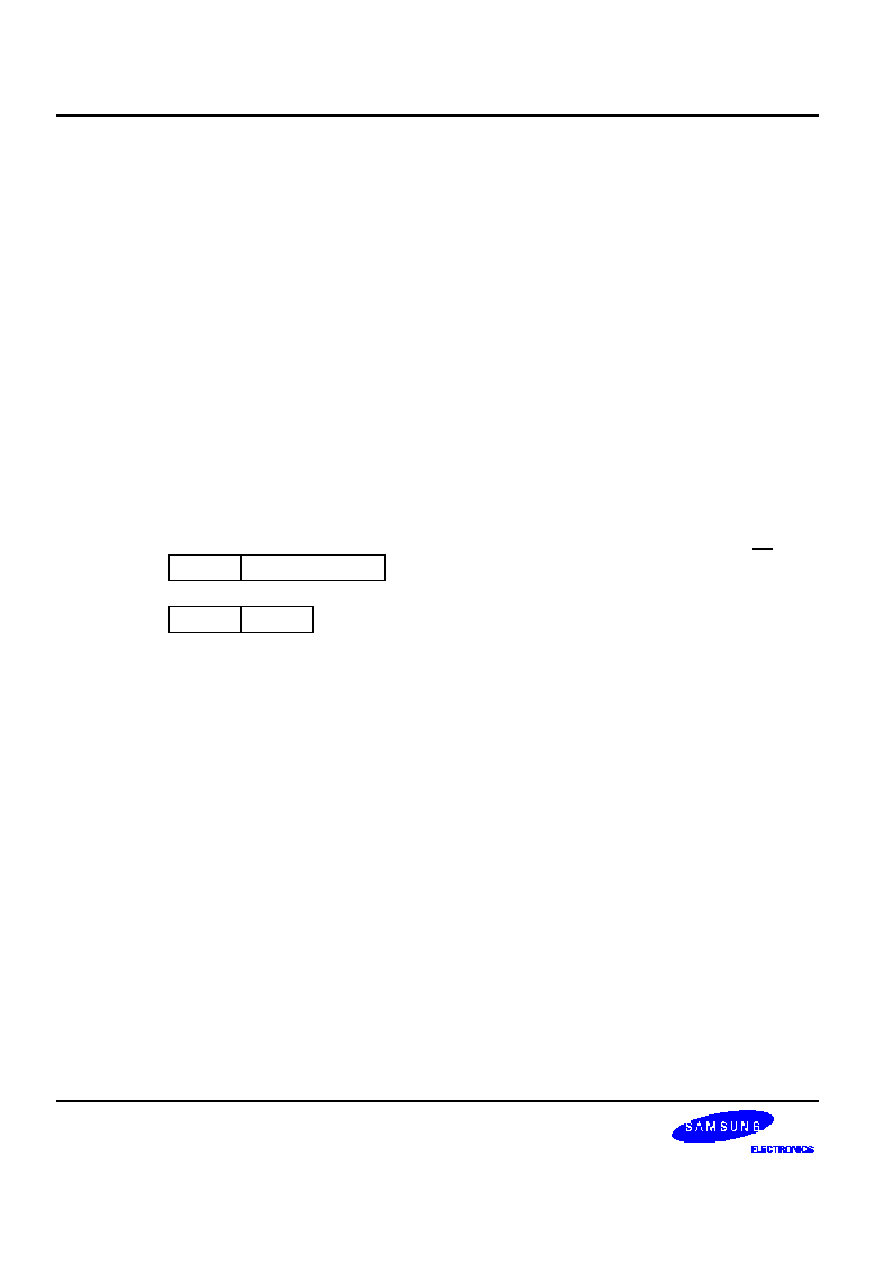

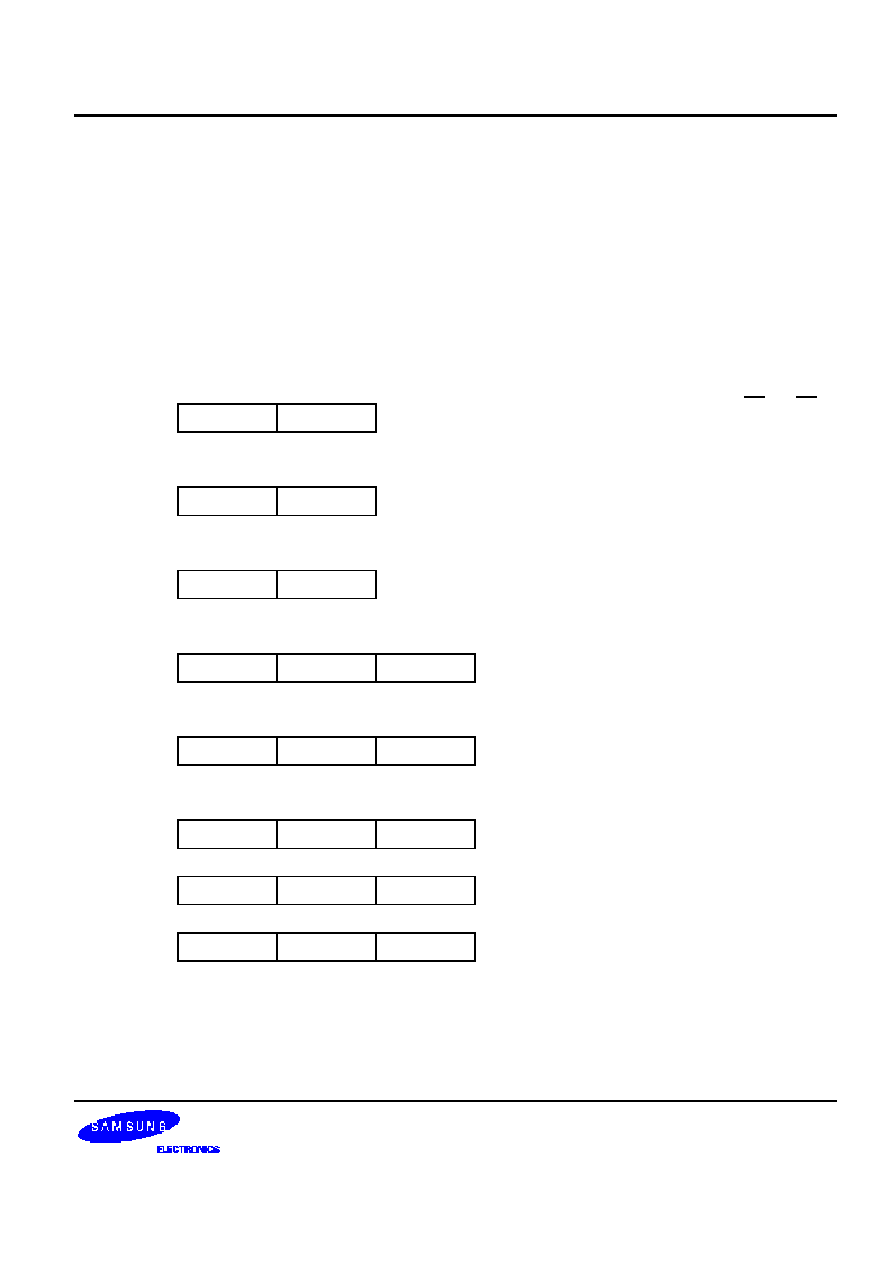

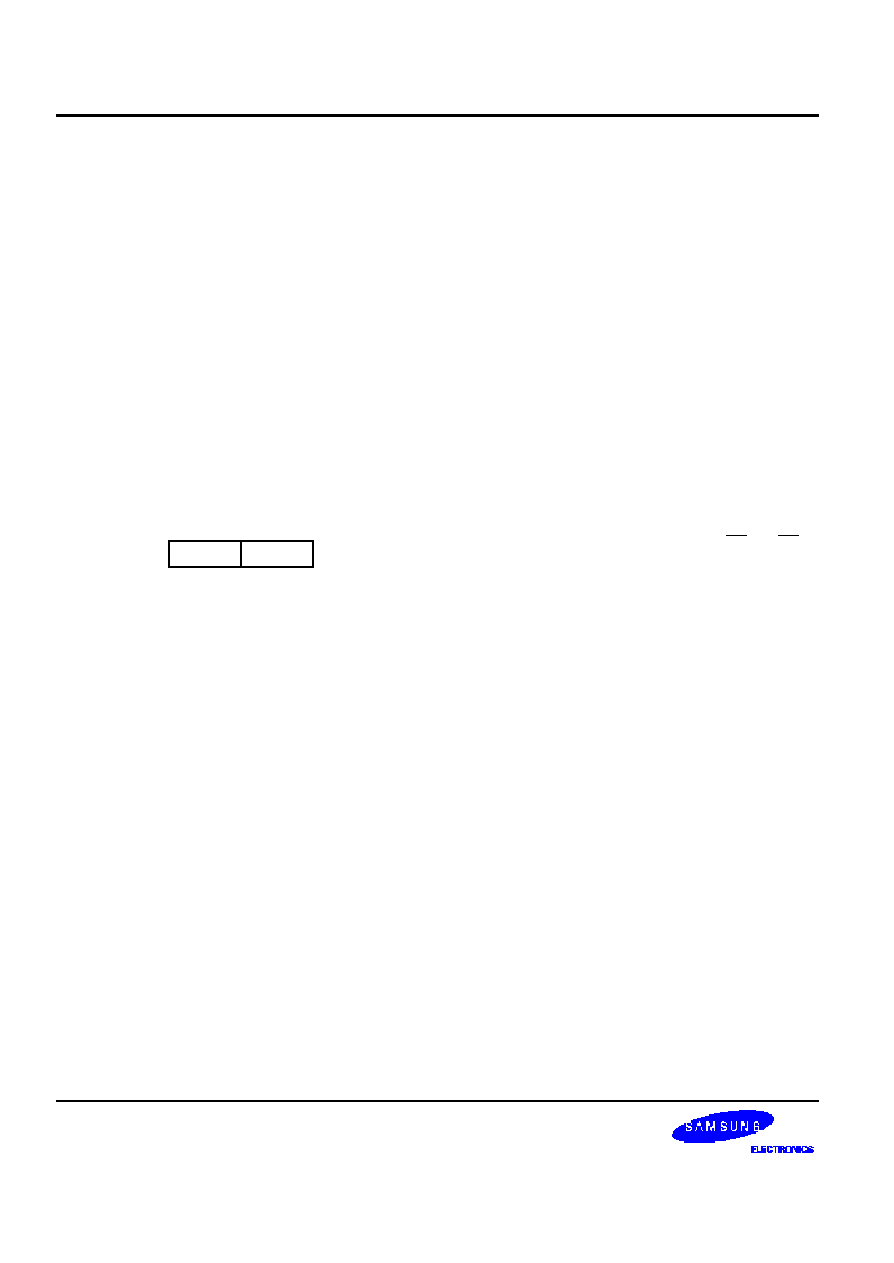

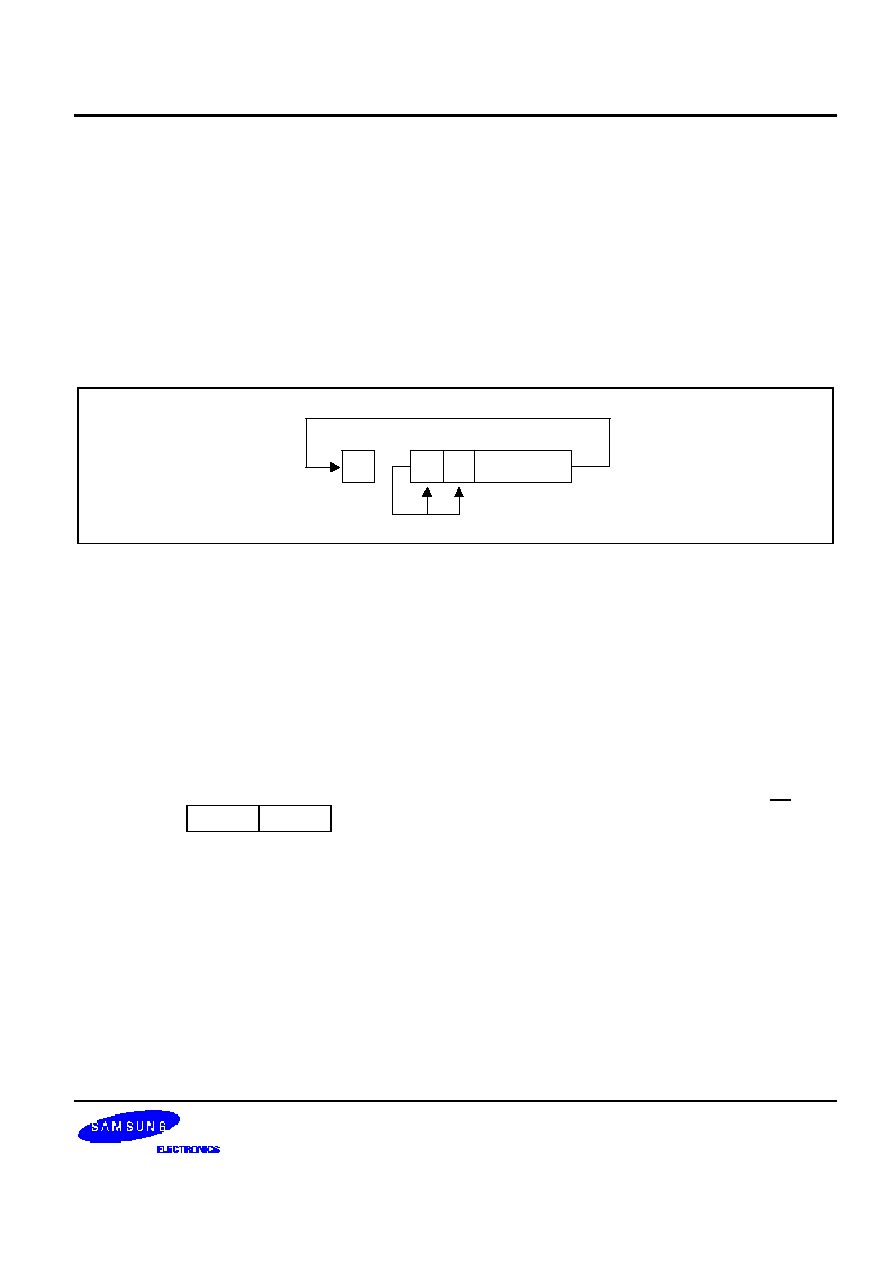

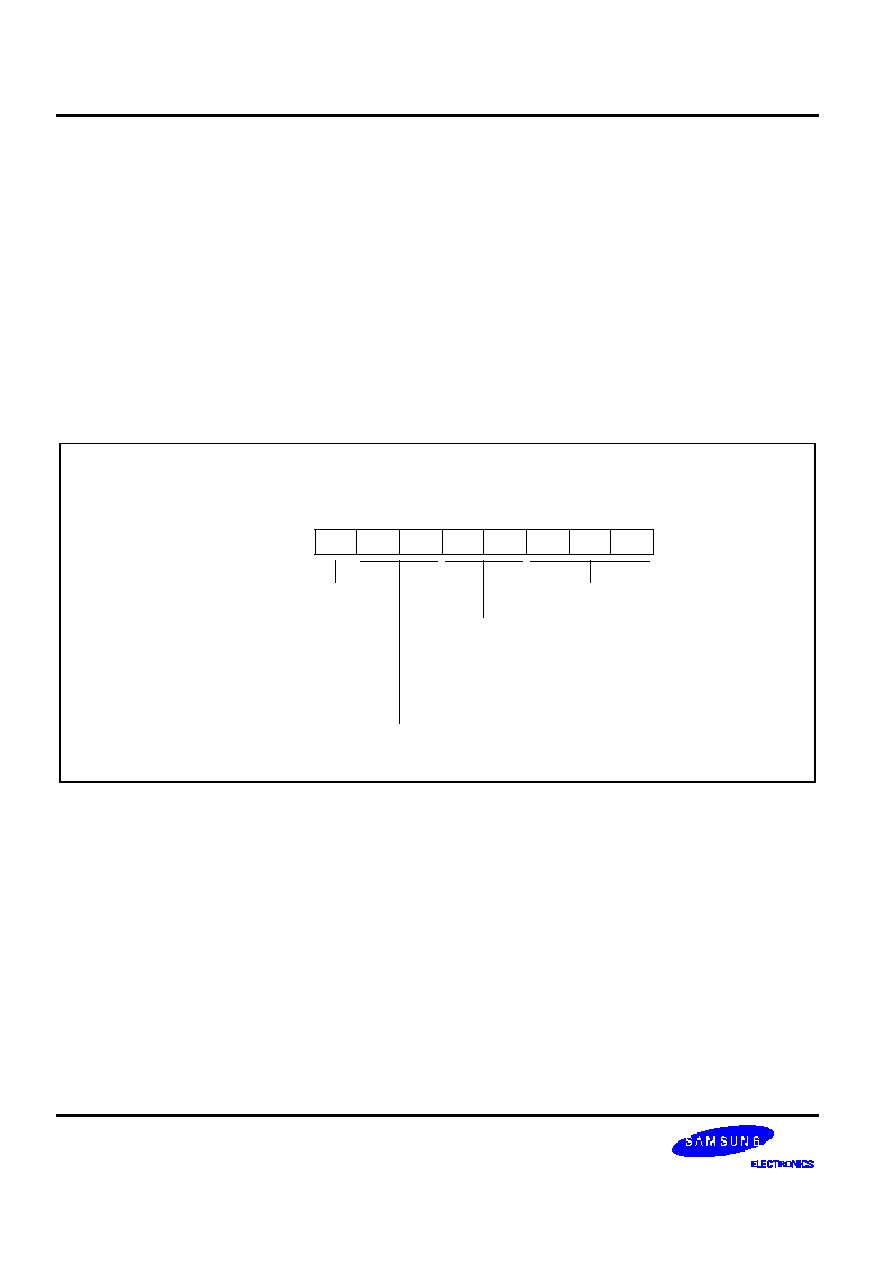

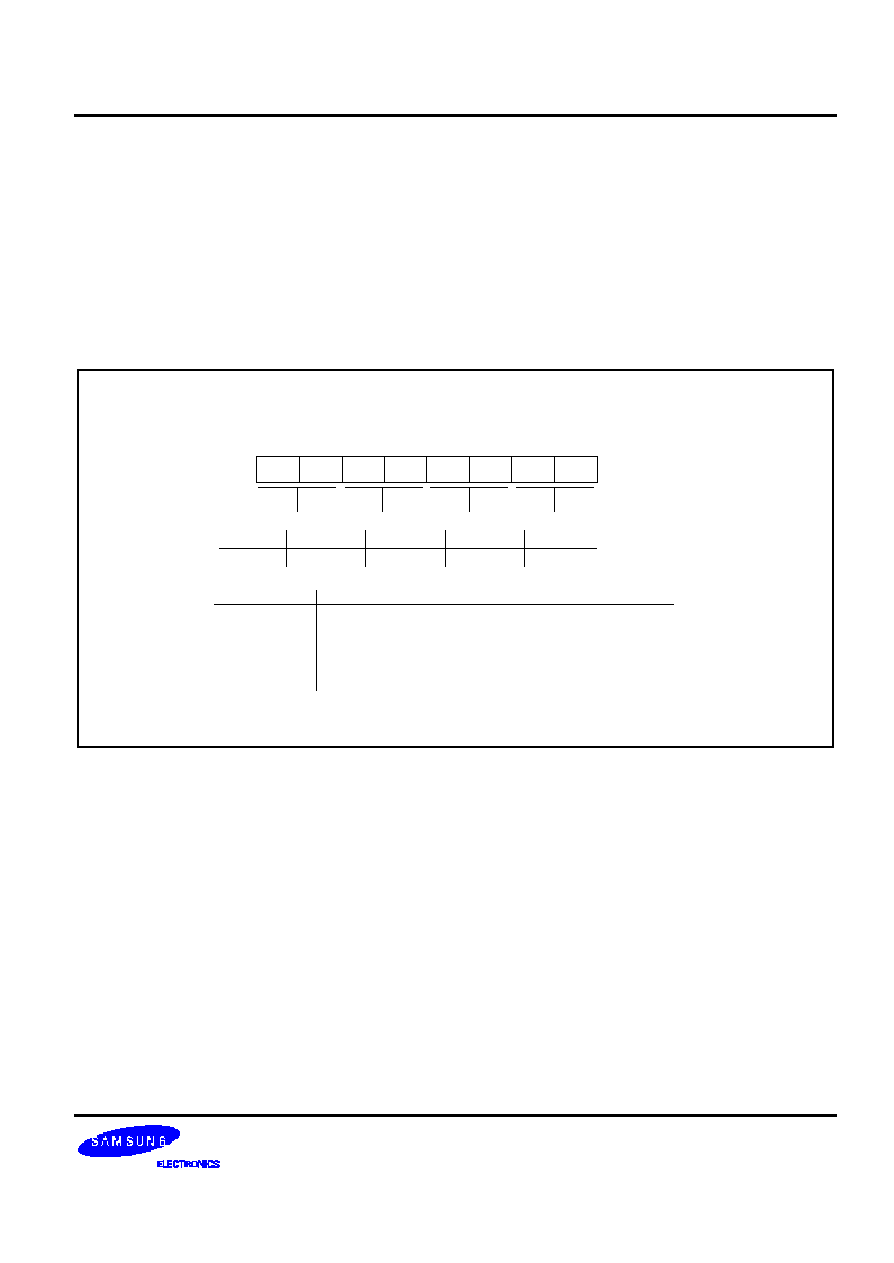

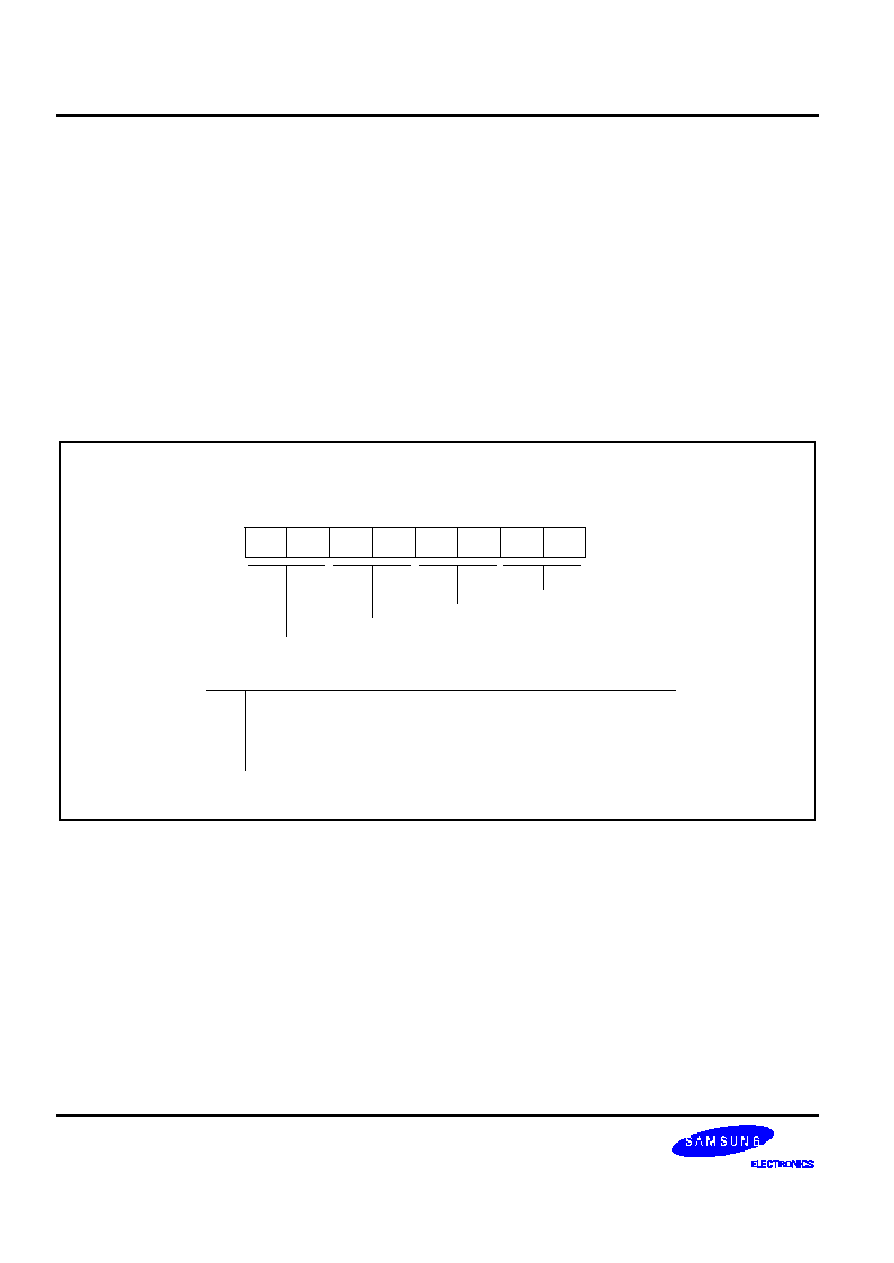

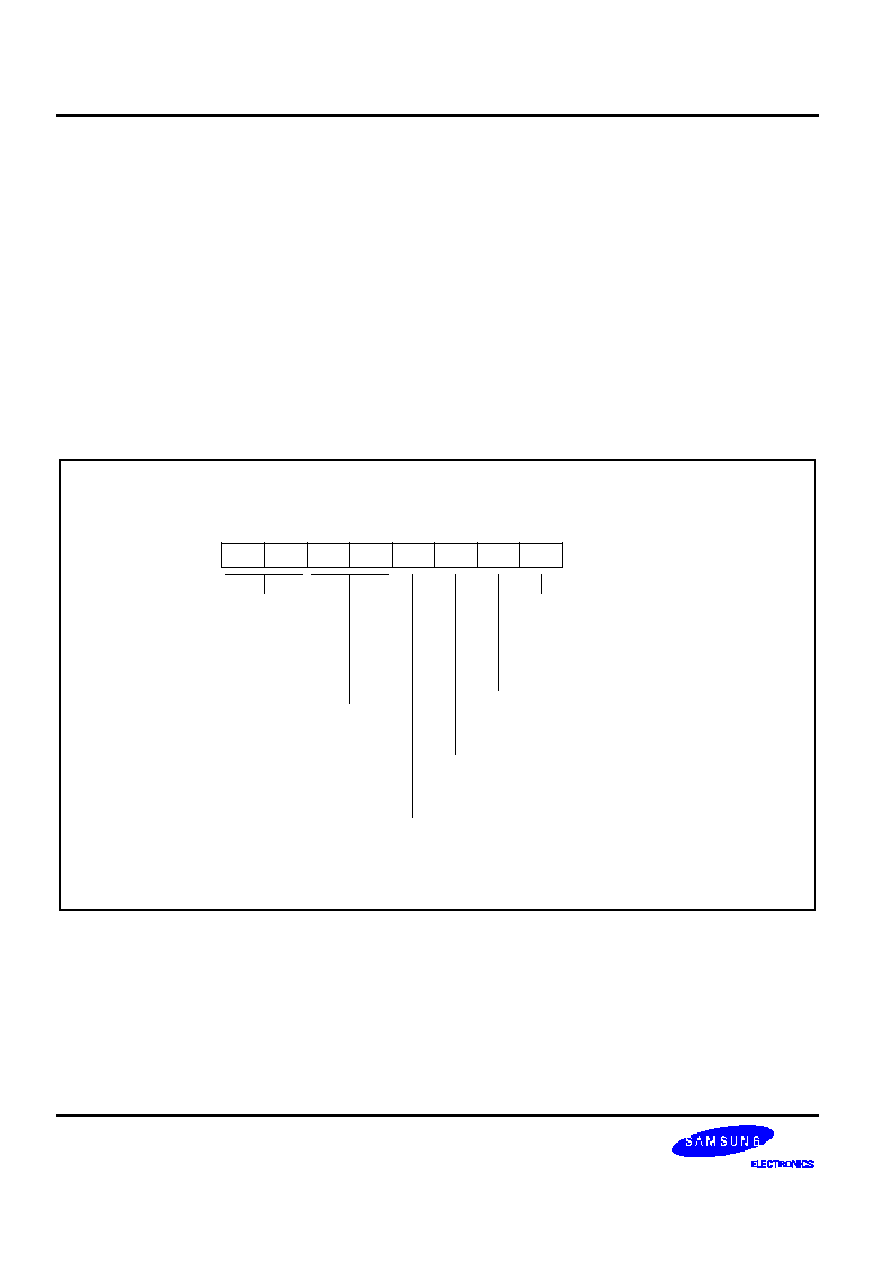

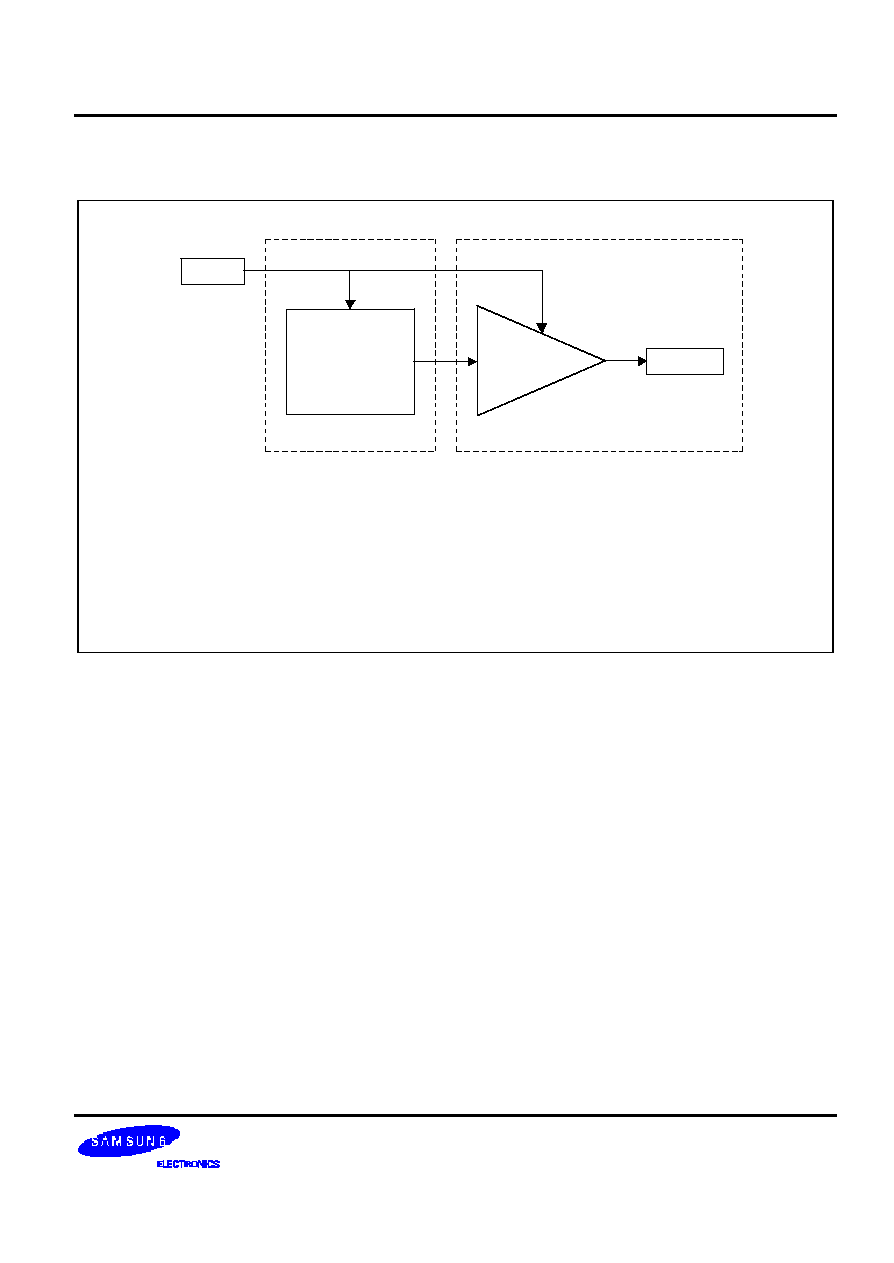

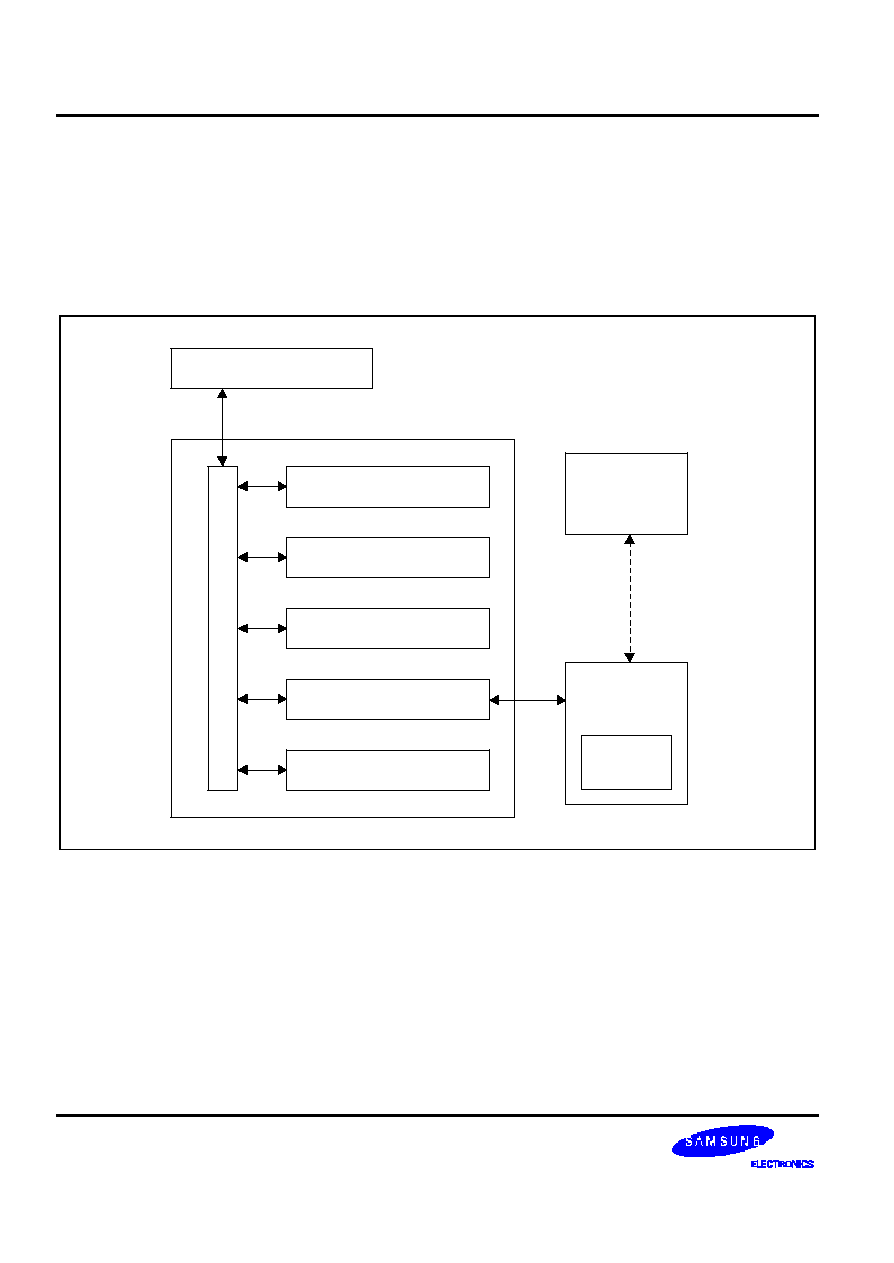

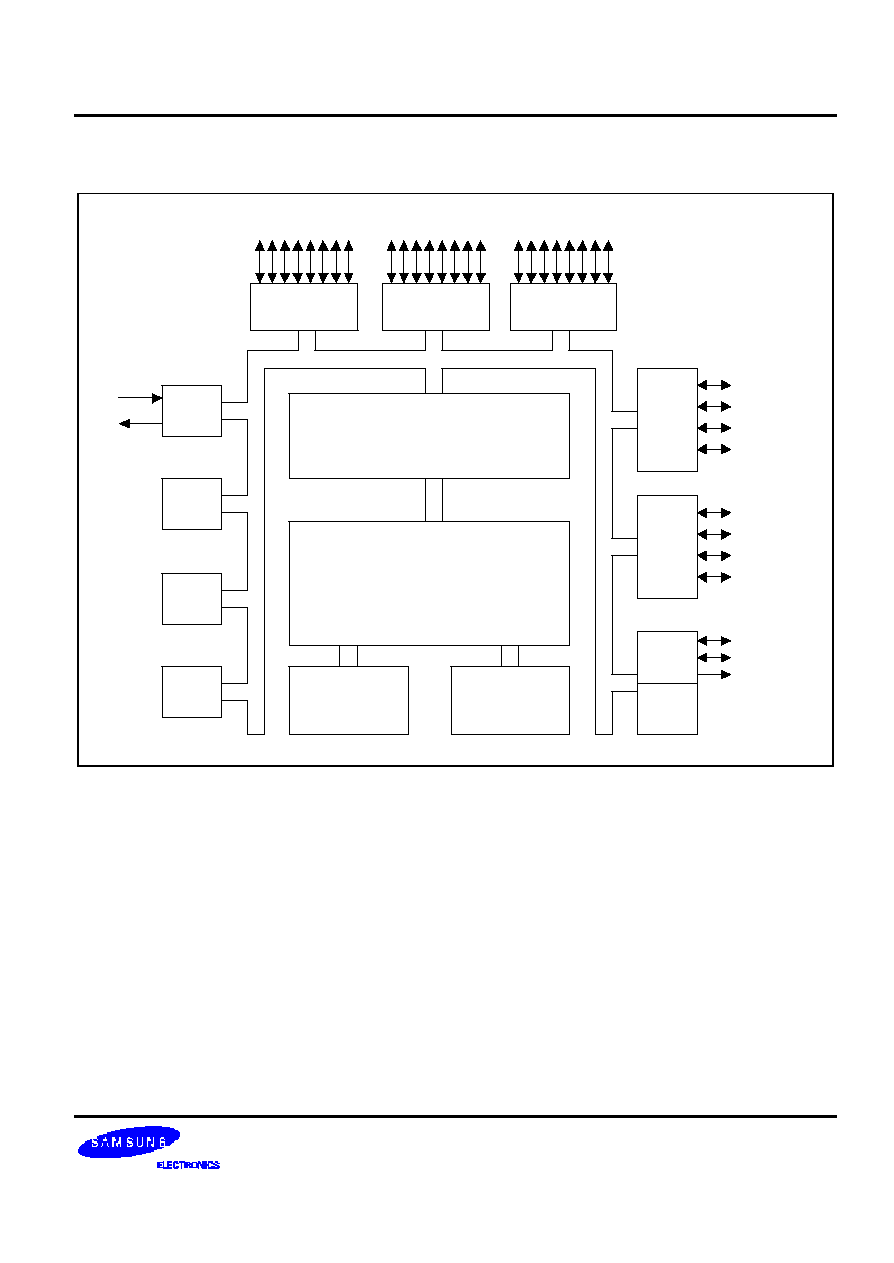

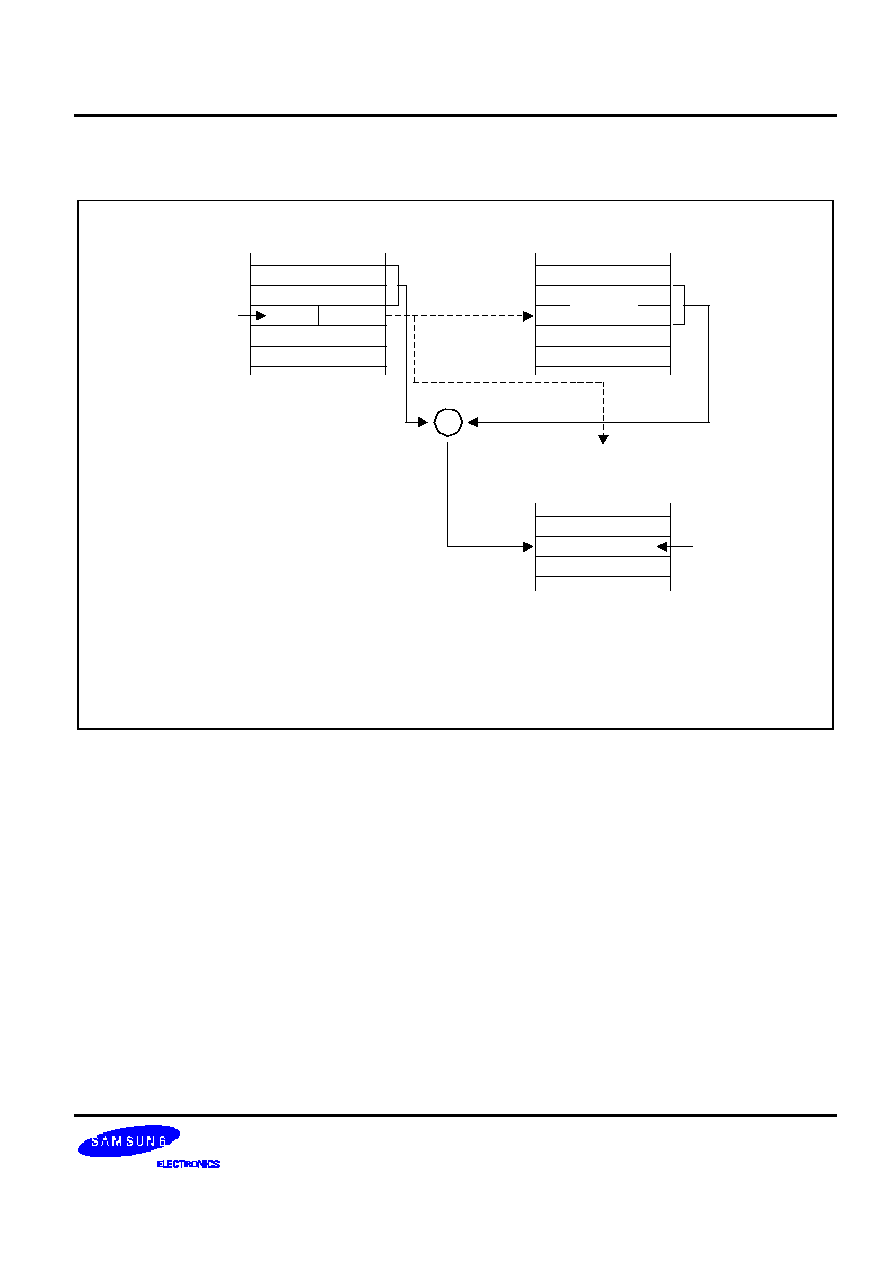

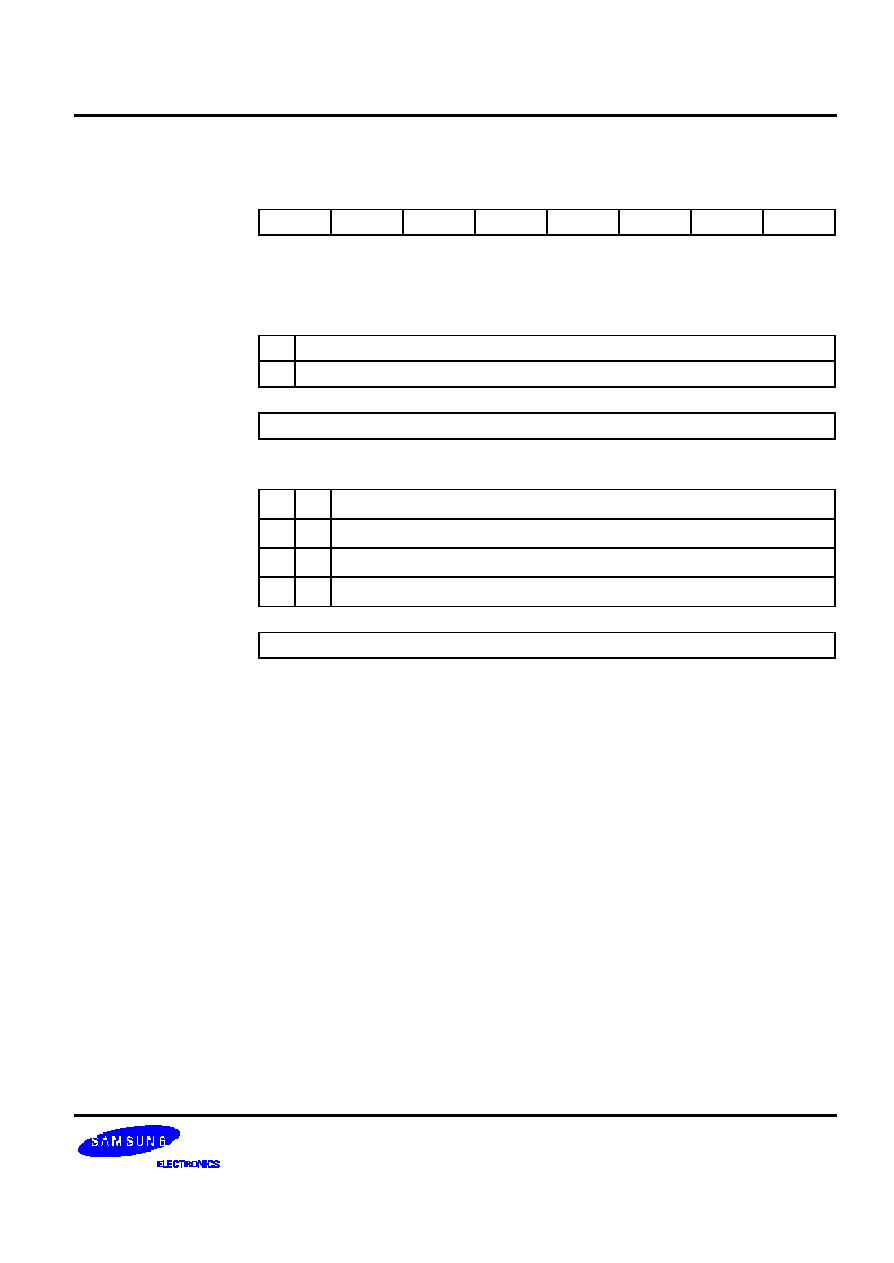

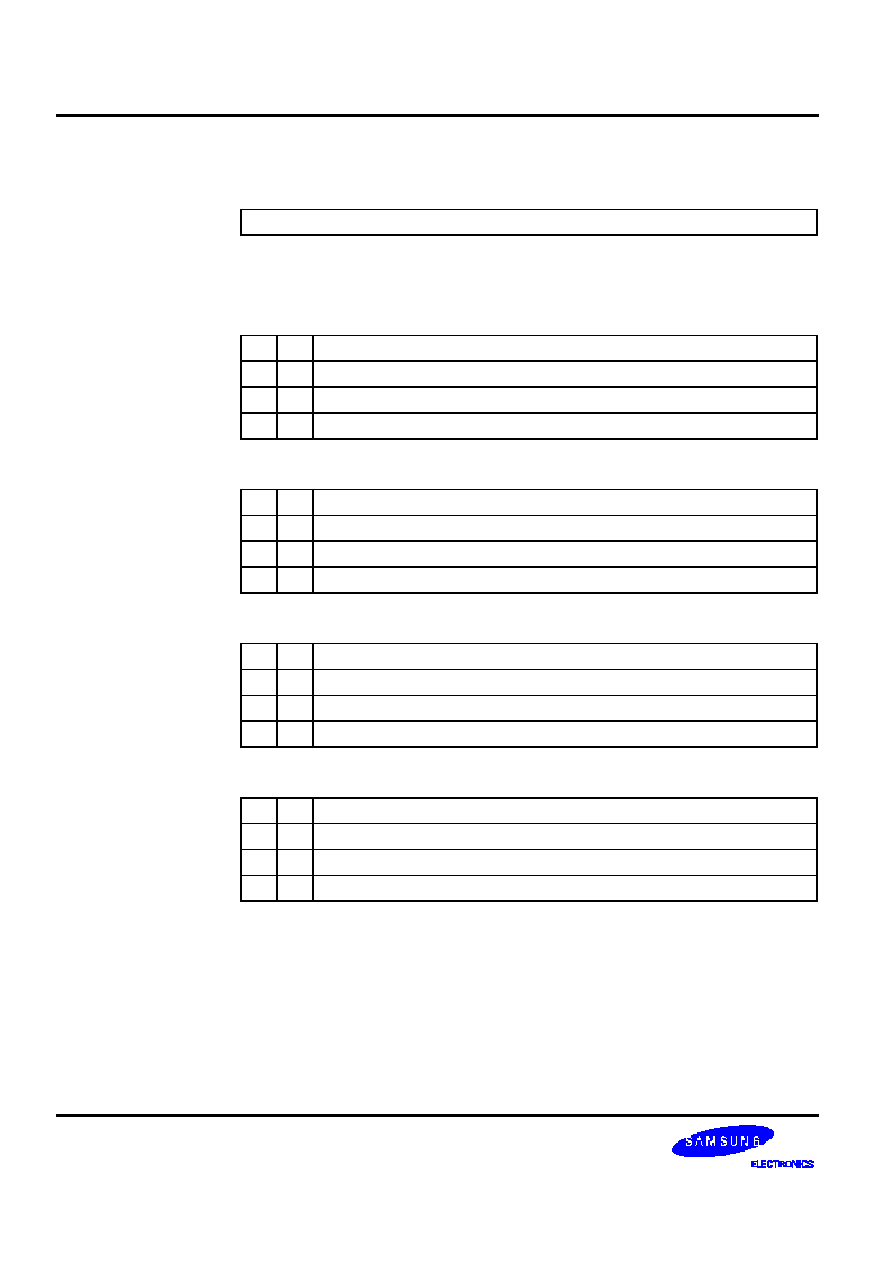

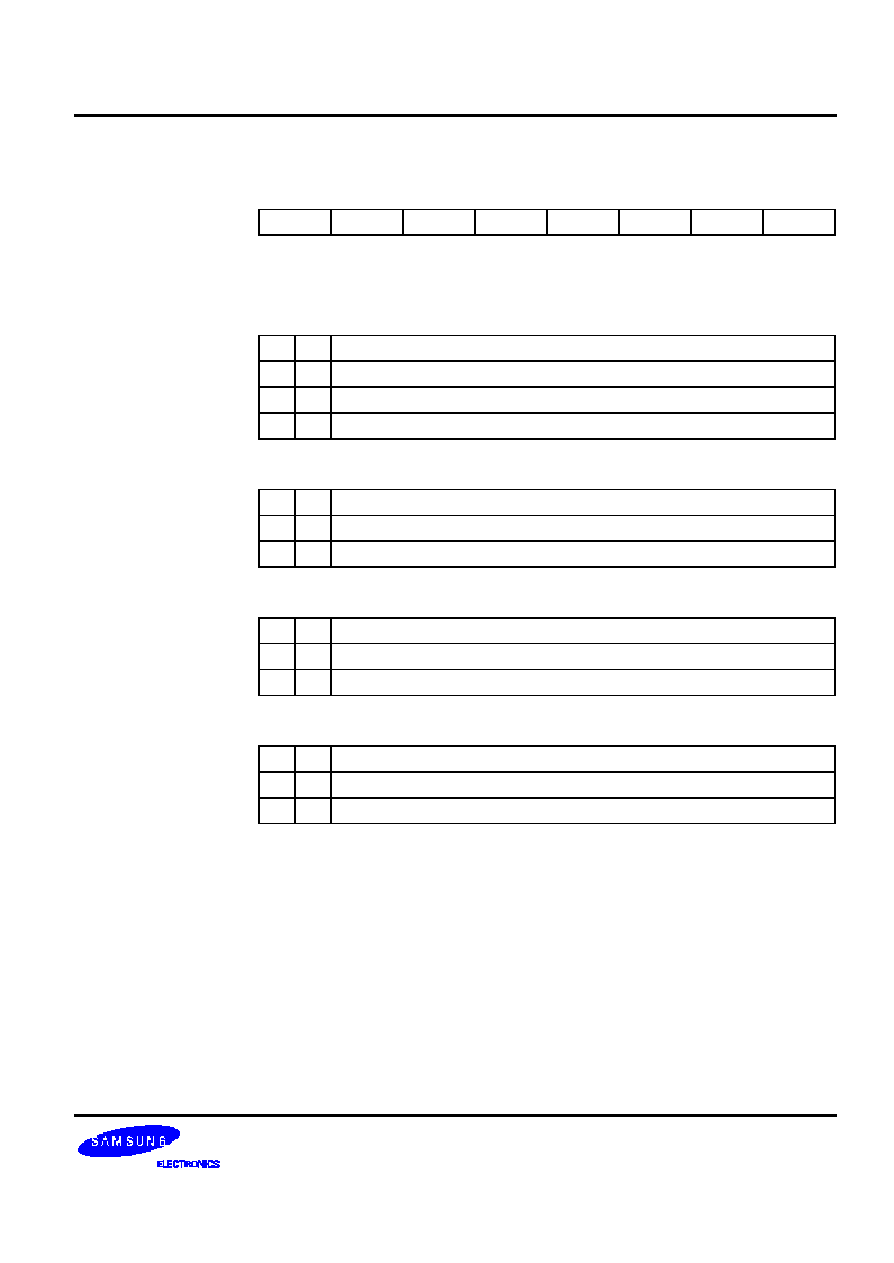

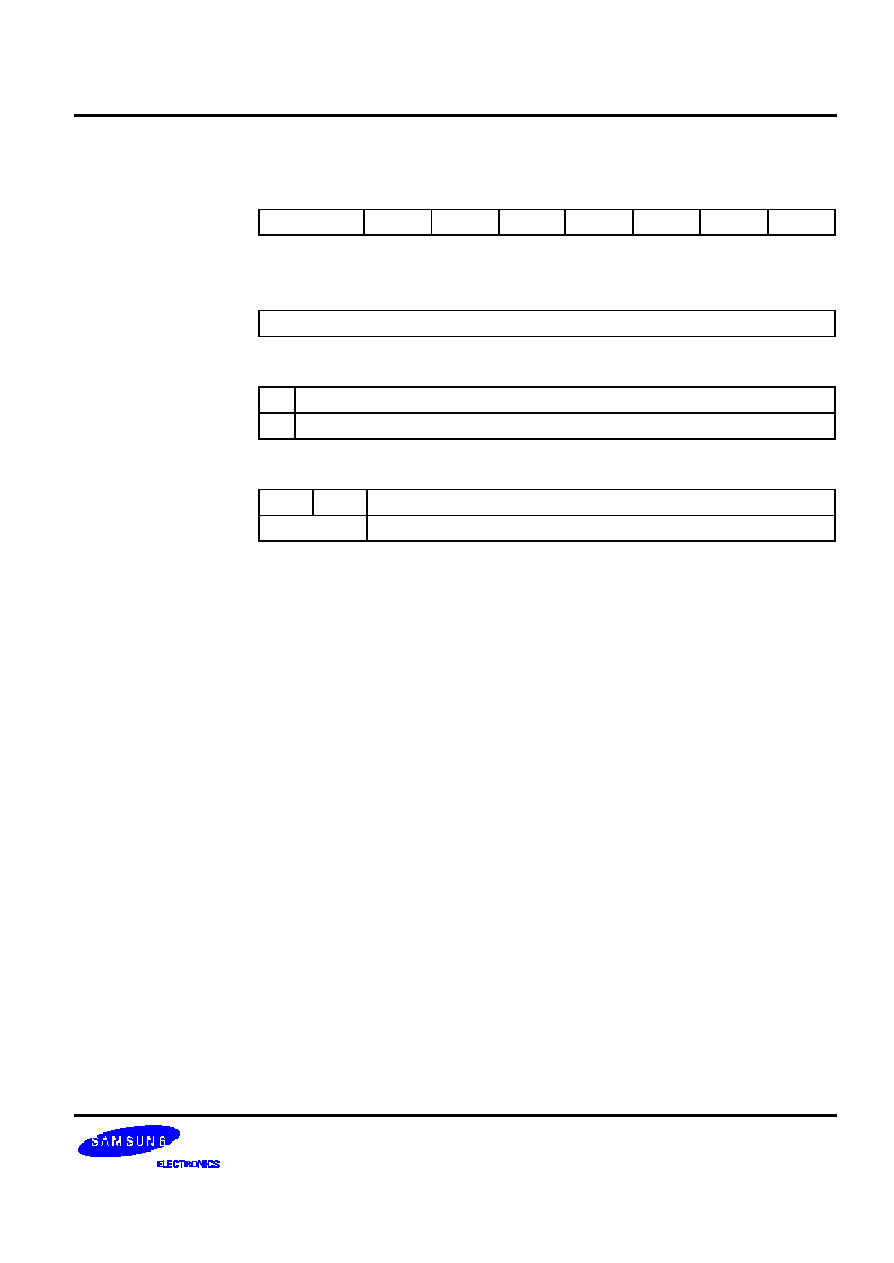

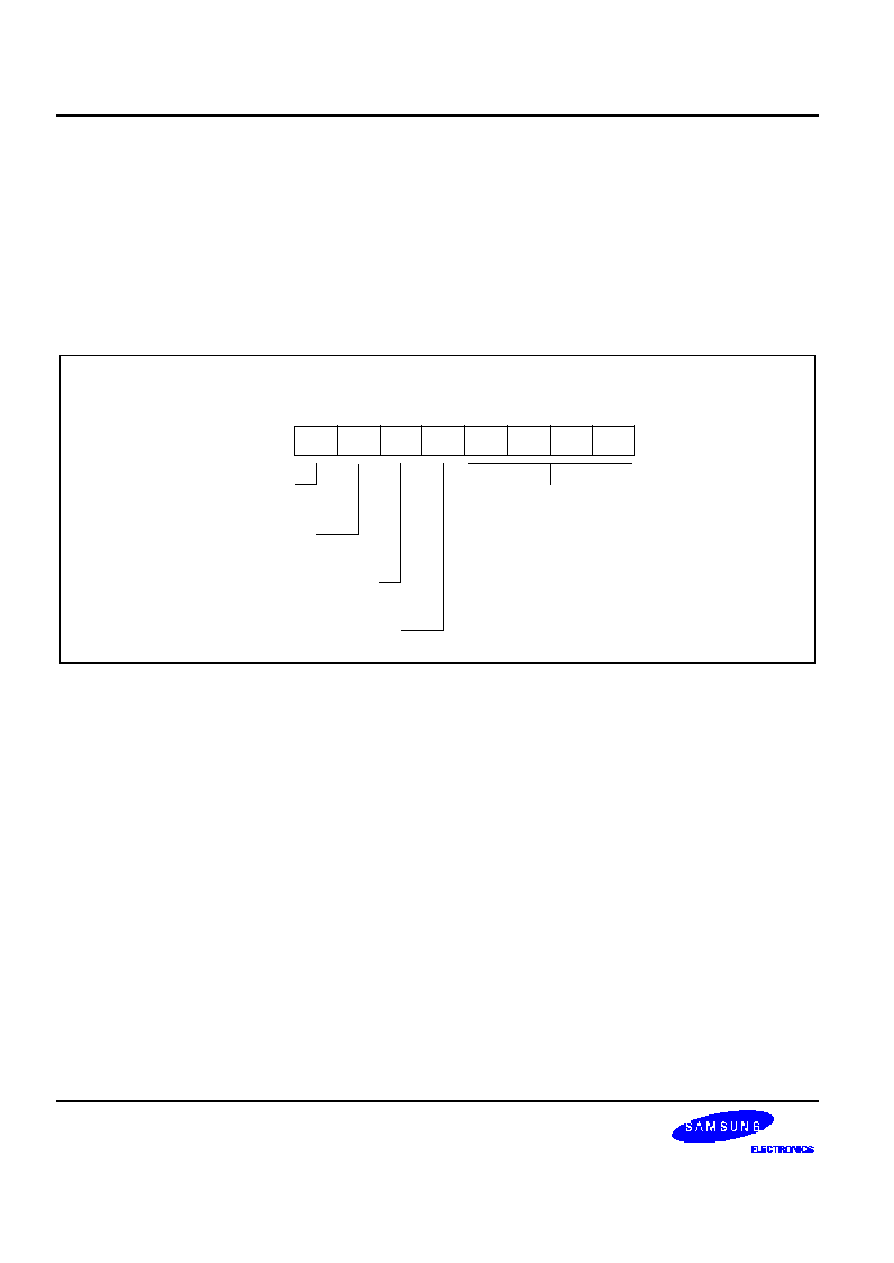

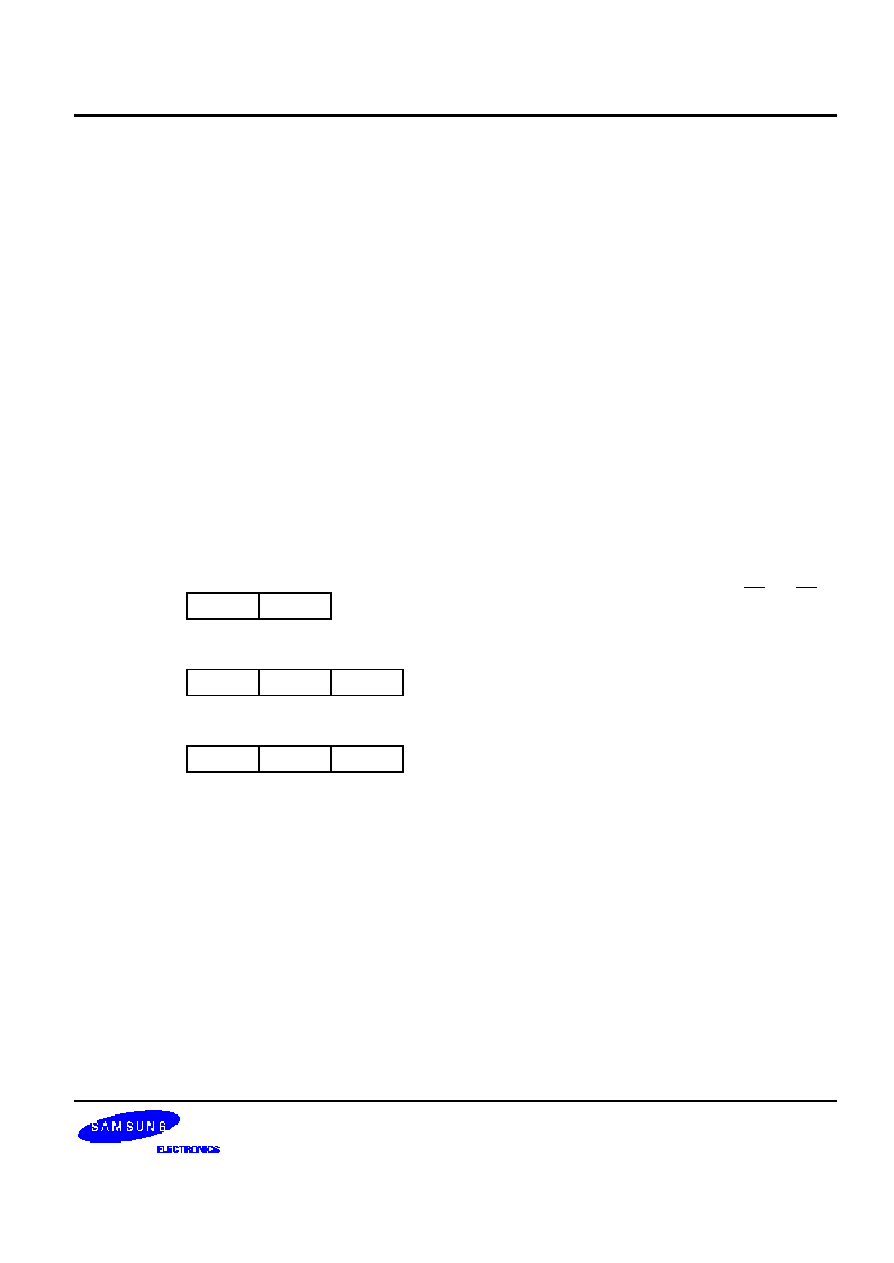

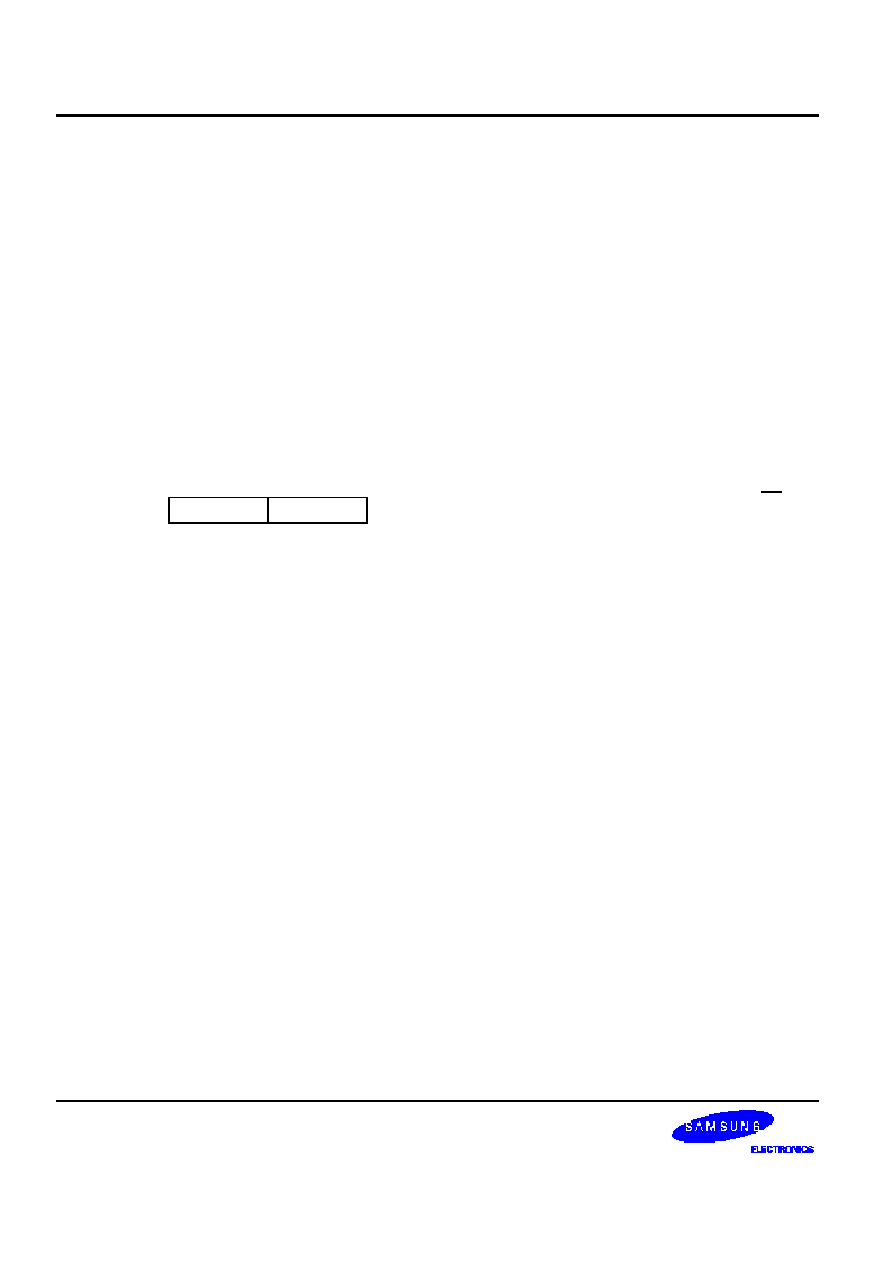

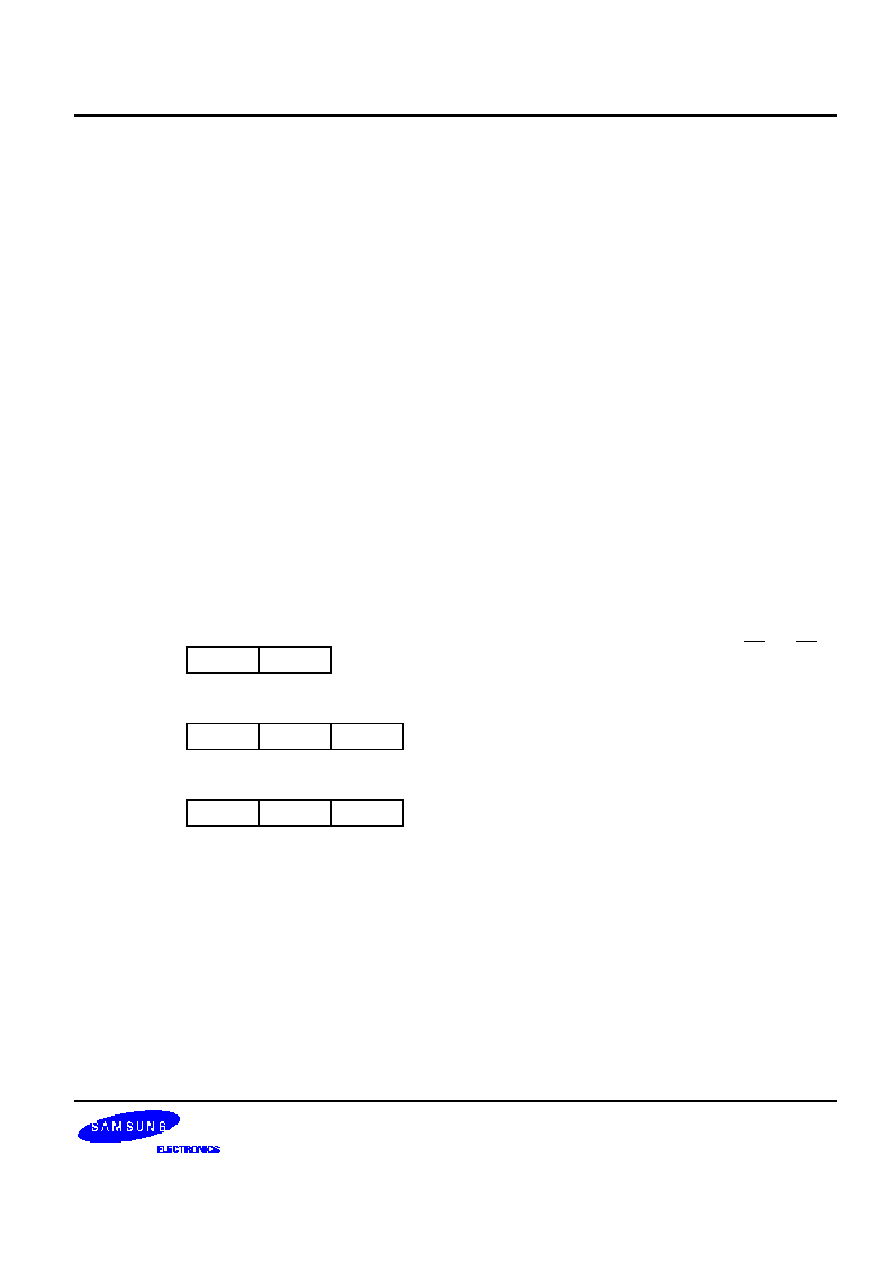

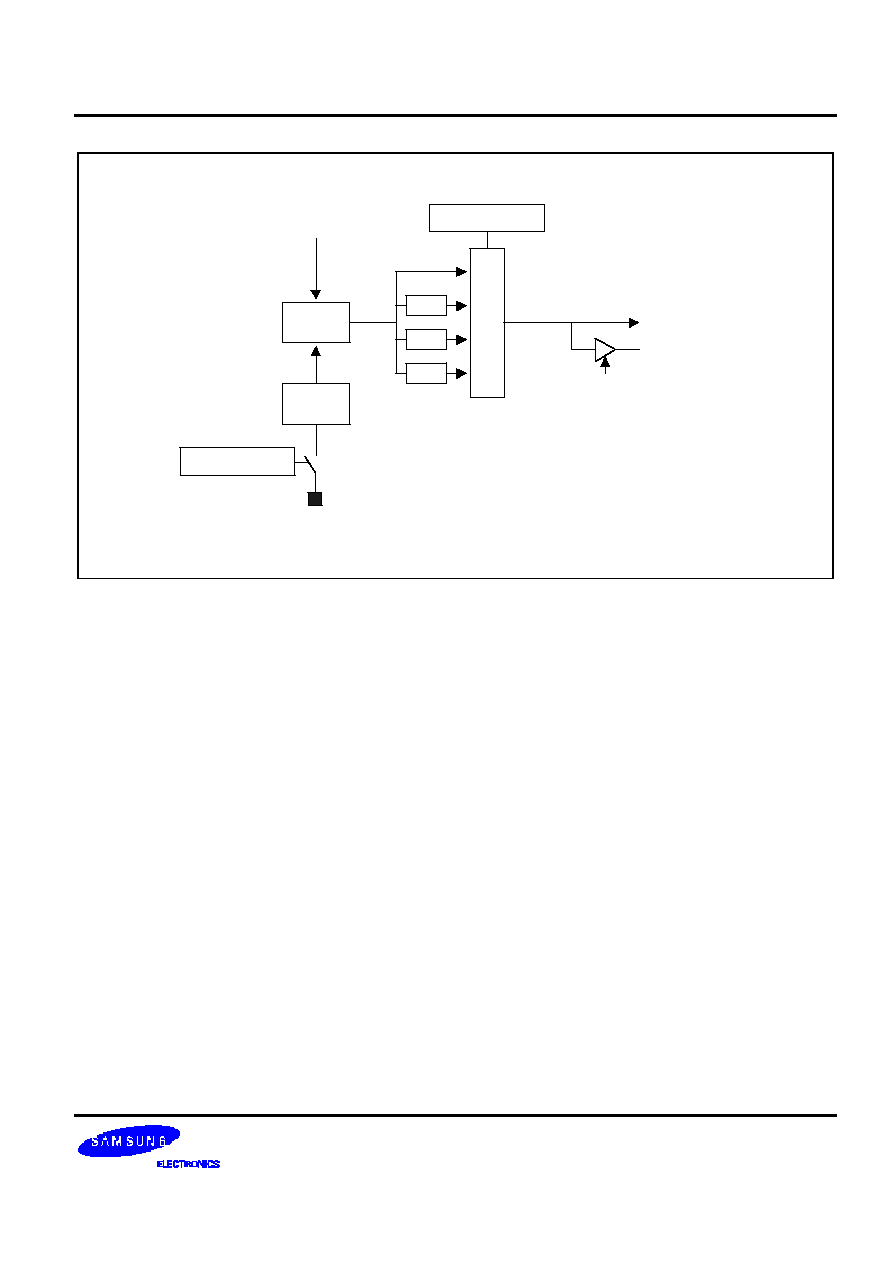

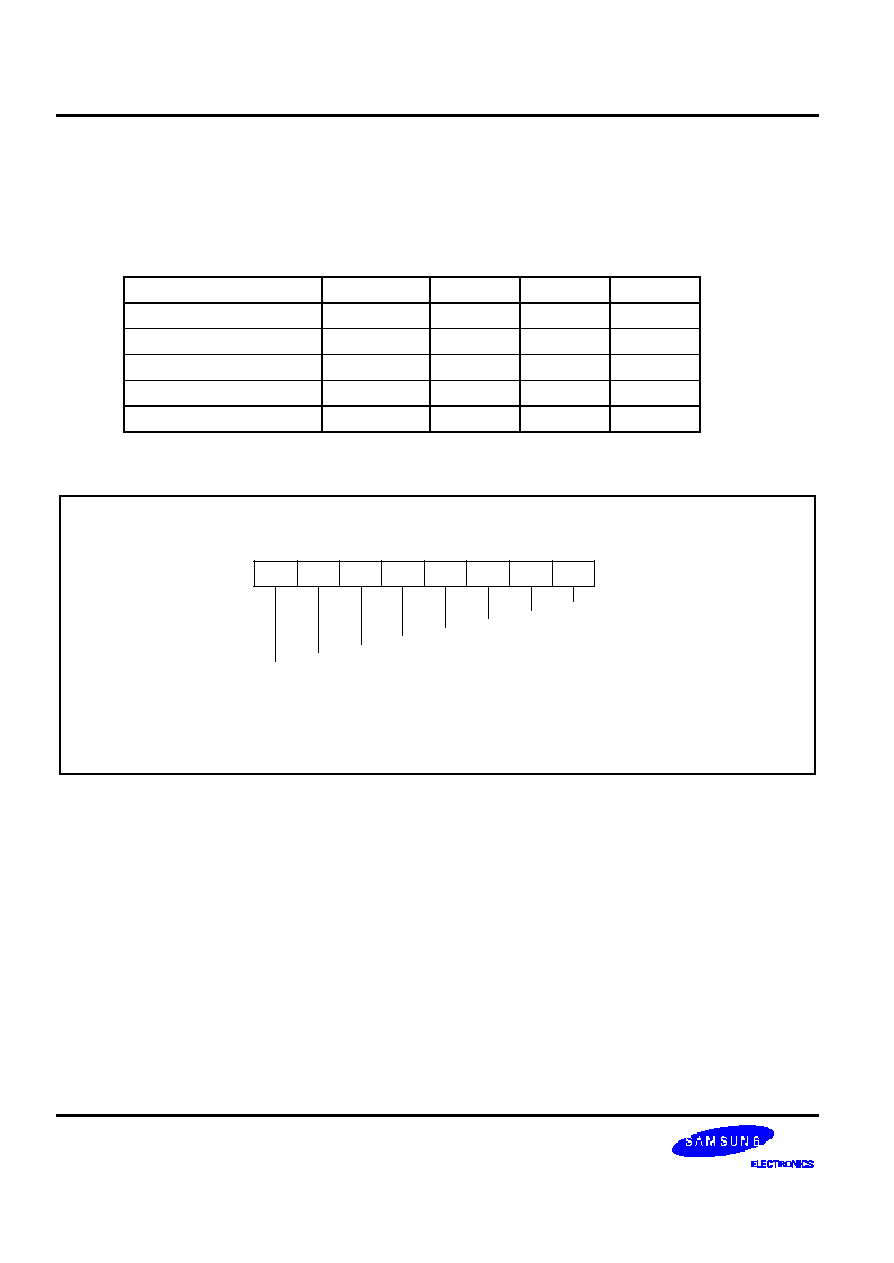

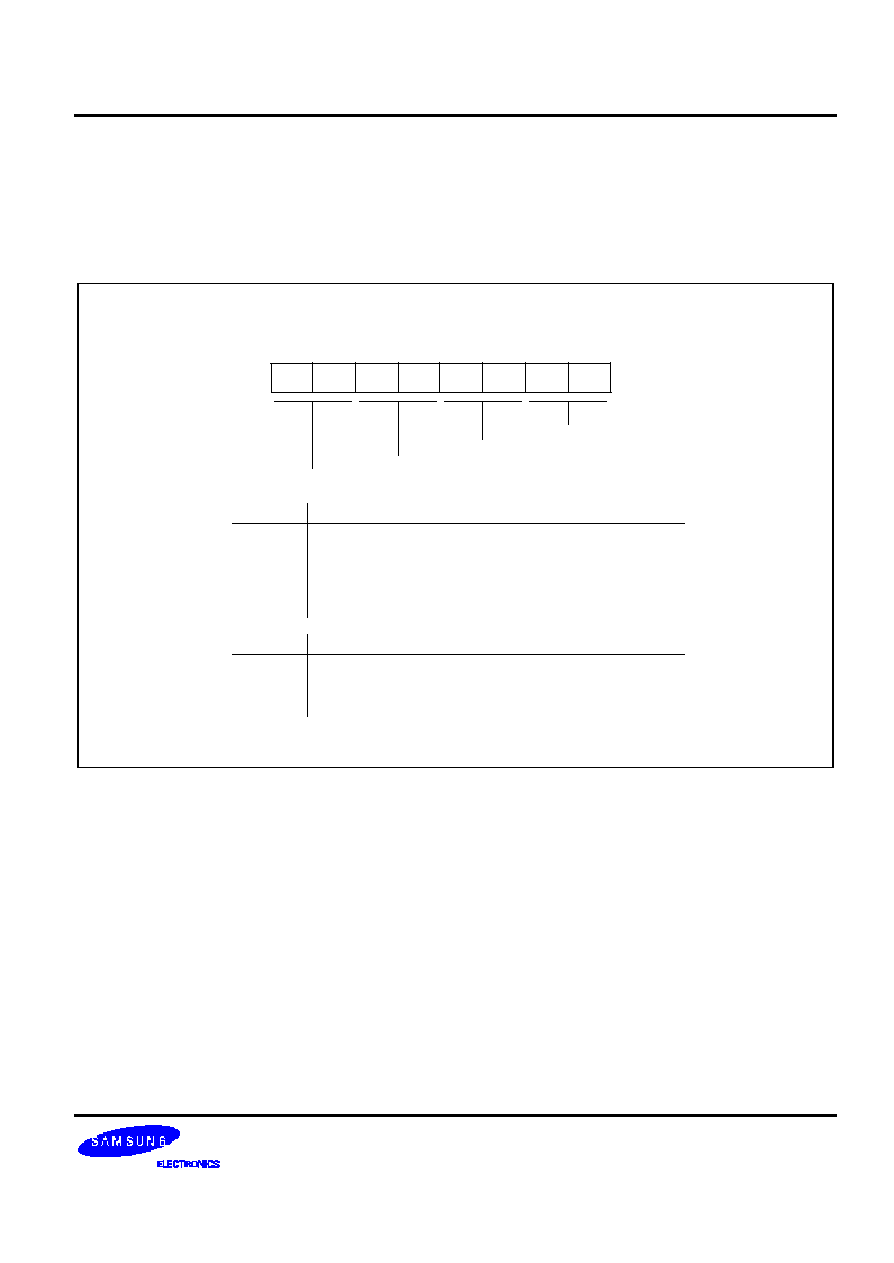

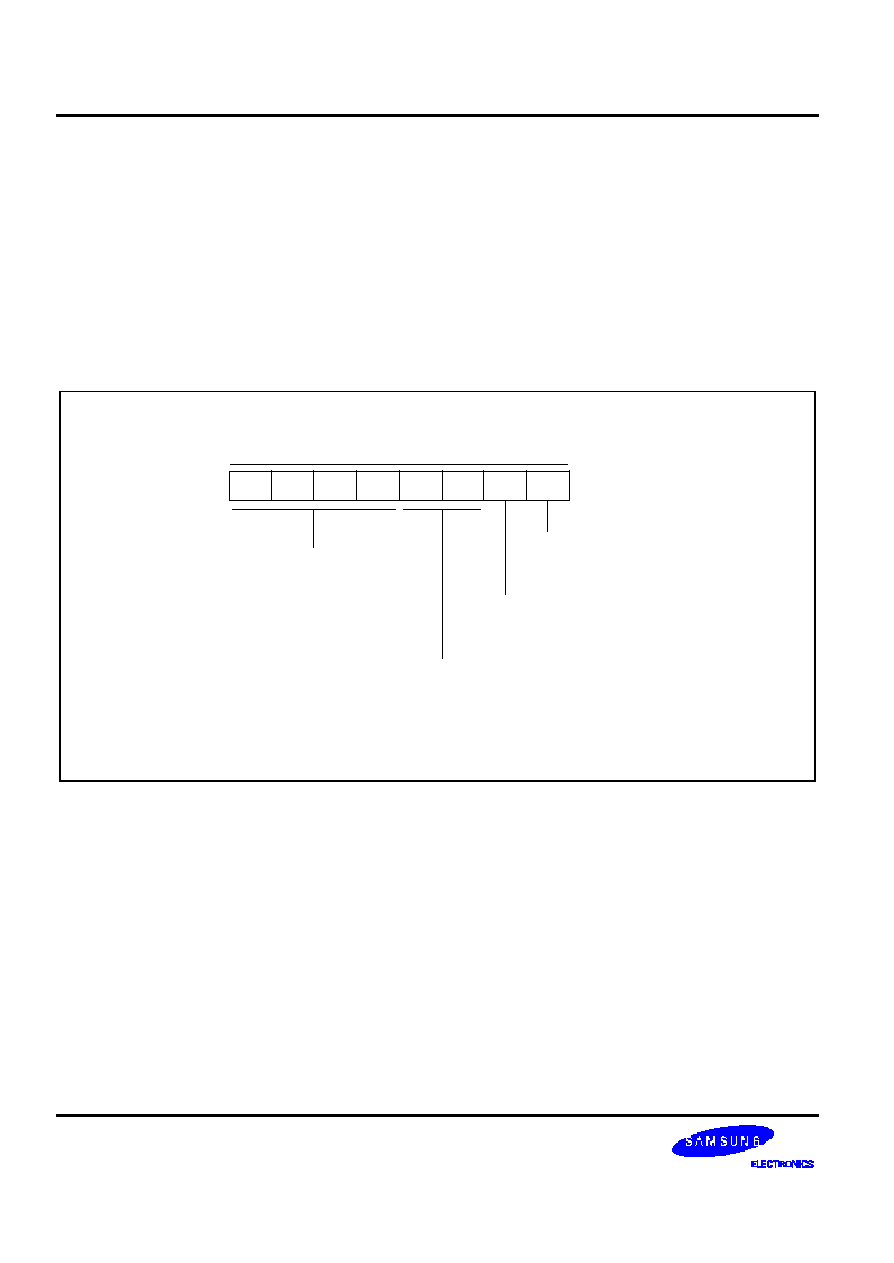

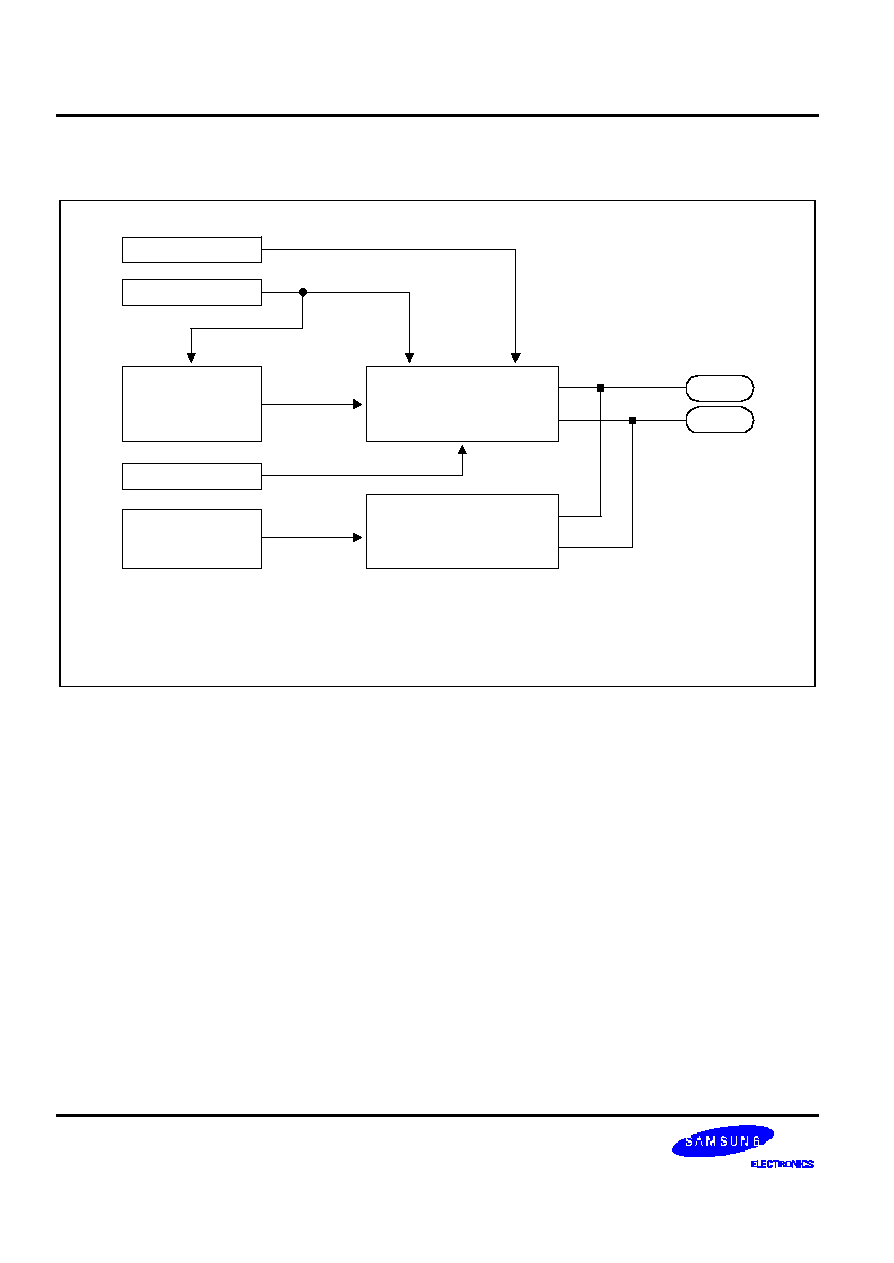

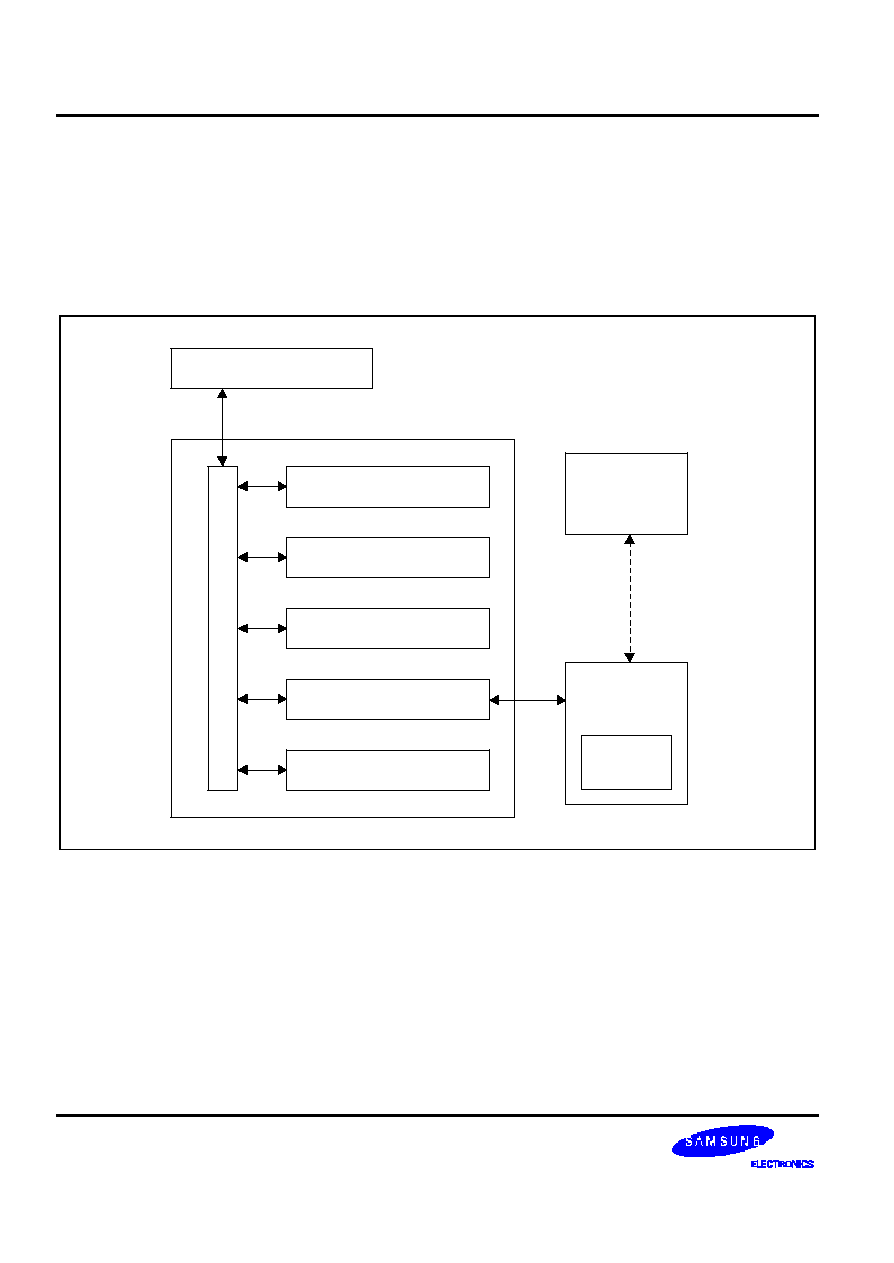

BLOCK DIAGRAM

P0.0-P0.7/INT2

SAM88RCRI Bus

X

IN

X

OUT

P2.0-P2.7/INT0

P1.0-P1.7

P3.0

P3.1

P3.2

P3.3/CLO

P4.0/INT1

P4.1/INT1

P4.2/INT1

P4.3/INT1

D+/PS2

D-/PS2

3.3 V OUT

I/O Port and Interrupt Control

SAM88RCRI CPU

Port 0

Port 1

Port 2

Main

OSC

Basic

Timer

LVR

Timer

Port 3

Port 4

USB

40 bytes

USB

Buffer

4 K/8KB ROM

208-Byte

Register File

Figure 1-1. Block Diagram

PRODUCT OVERVIEW

S3C9688/P9688

1-4

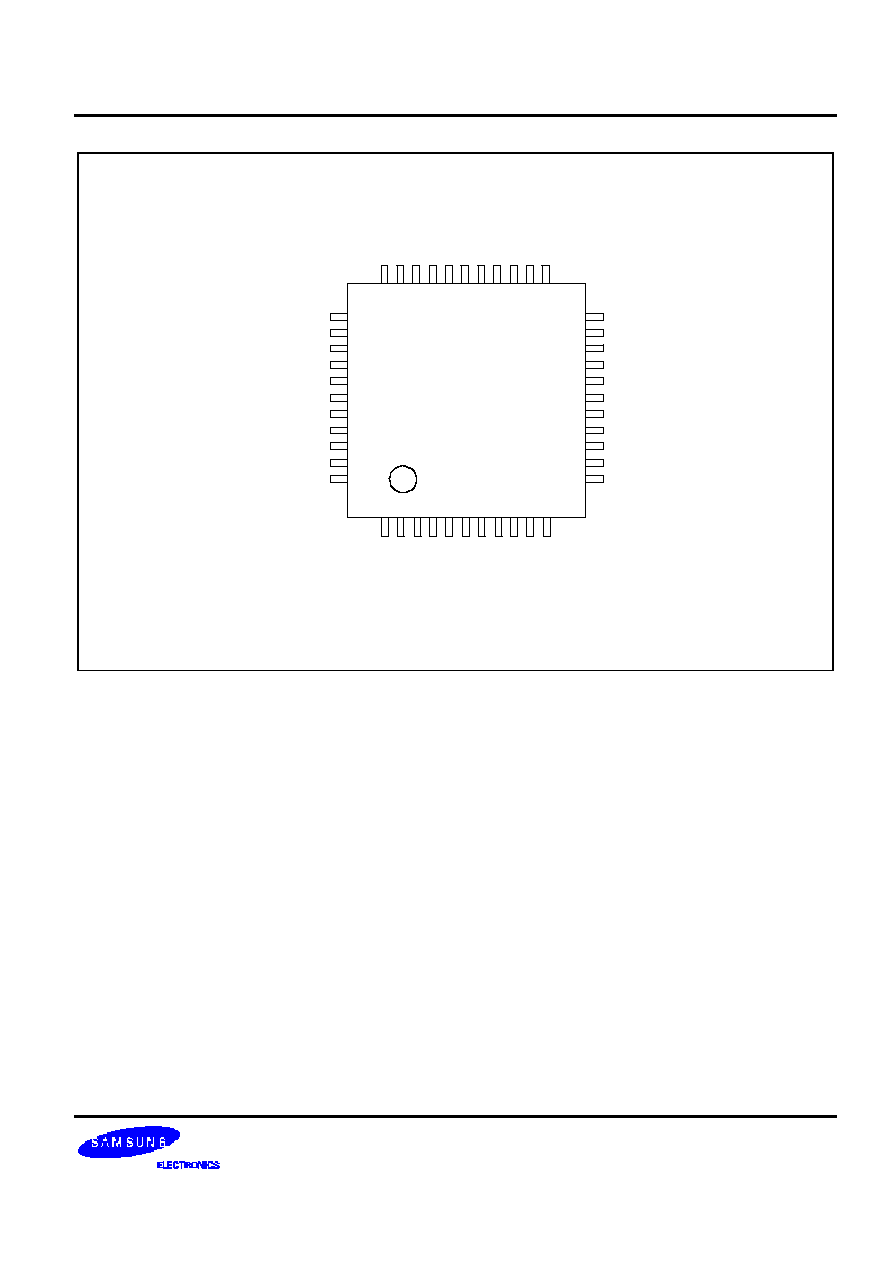

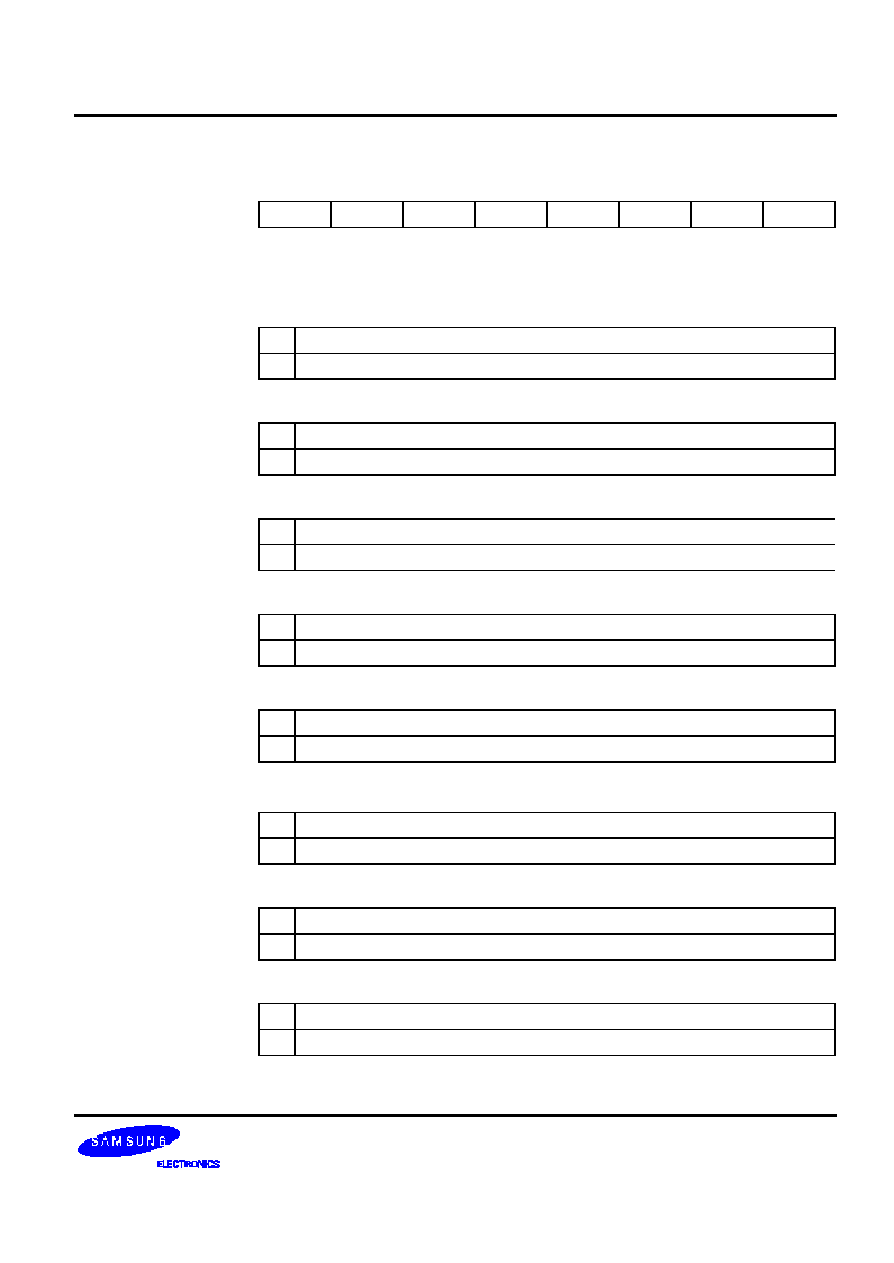

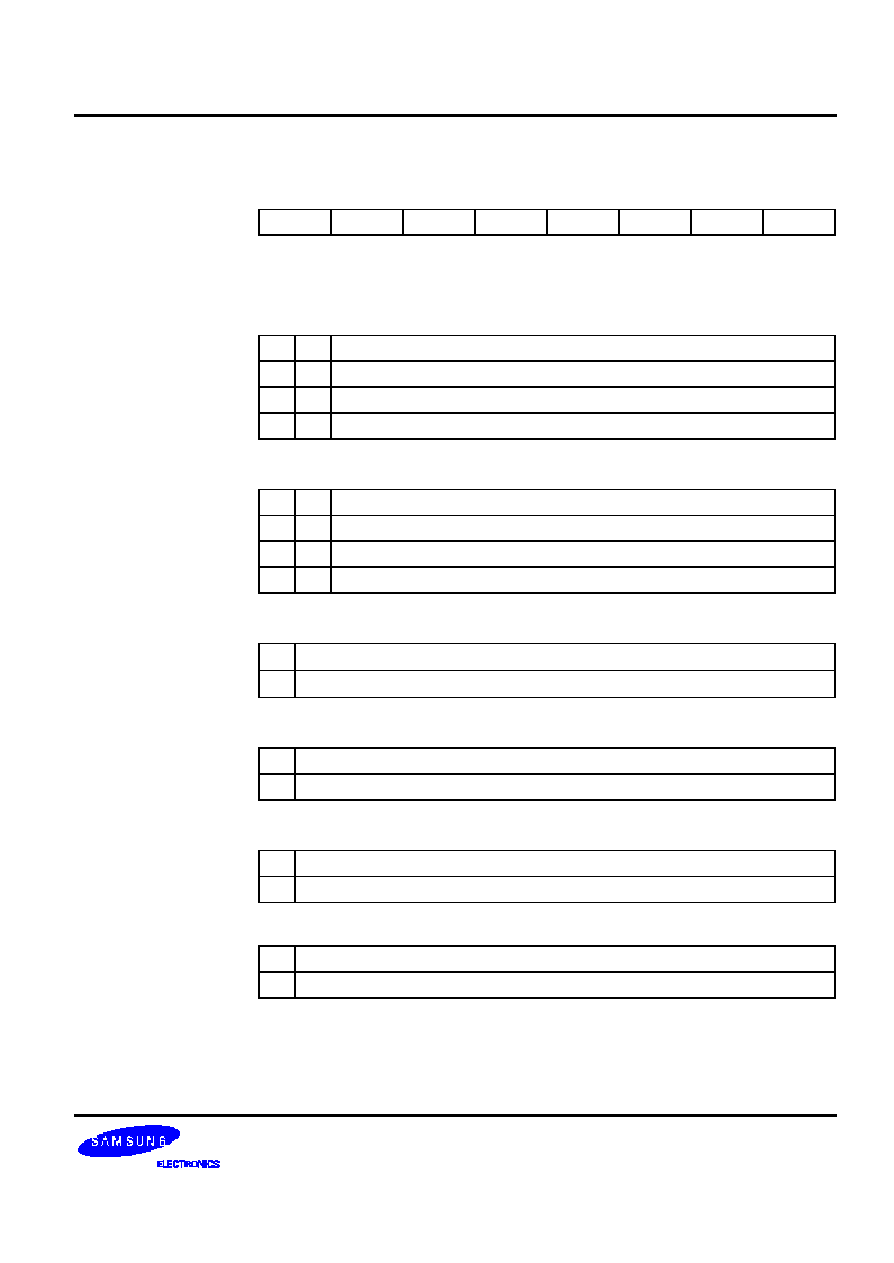

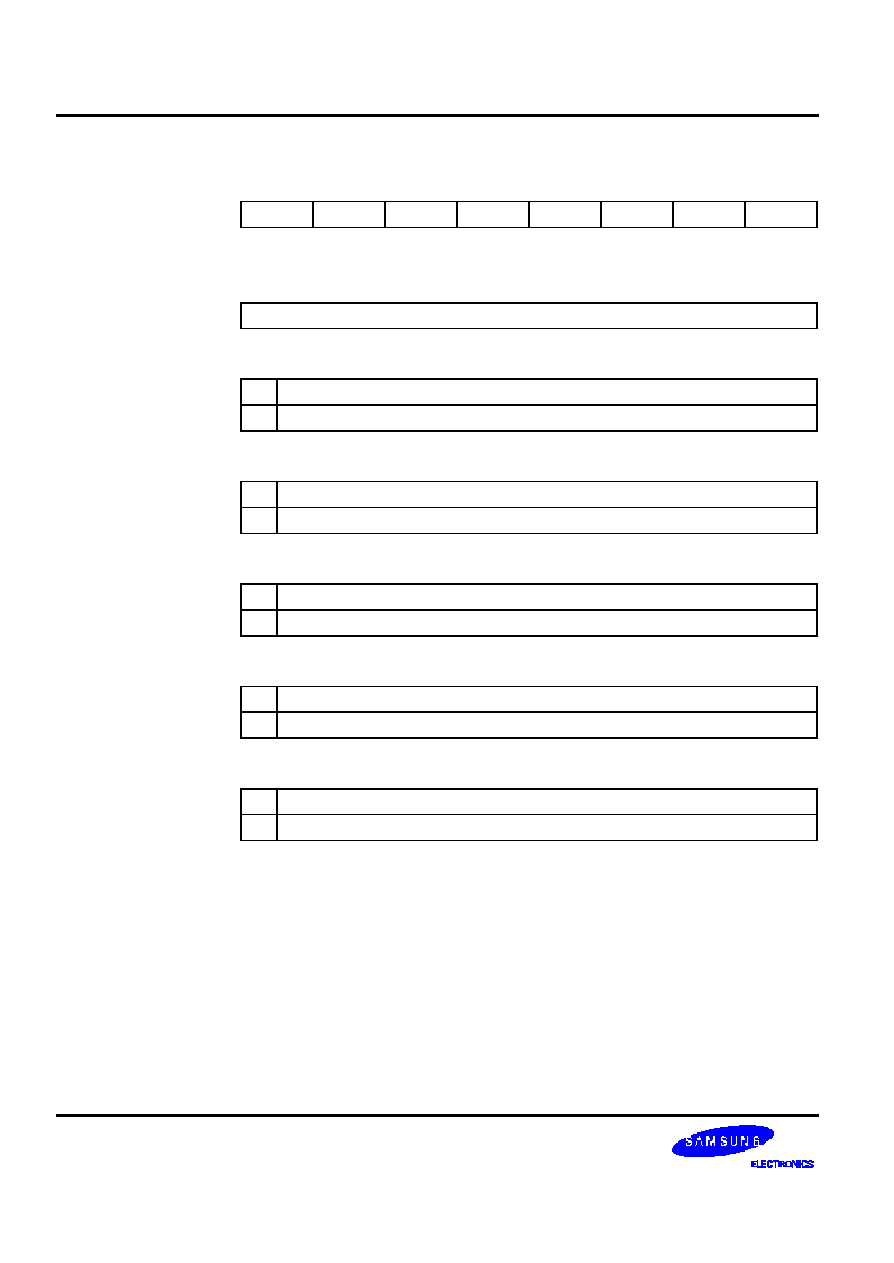

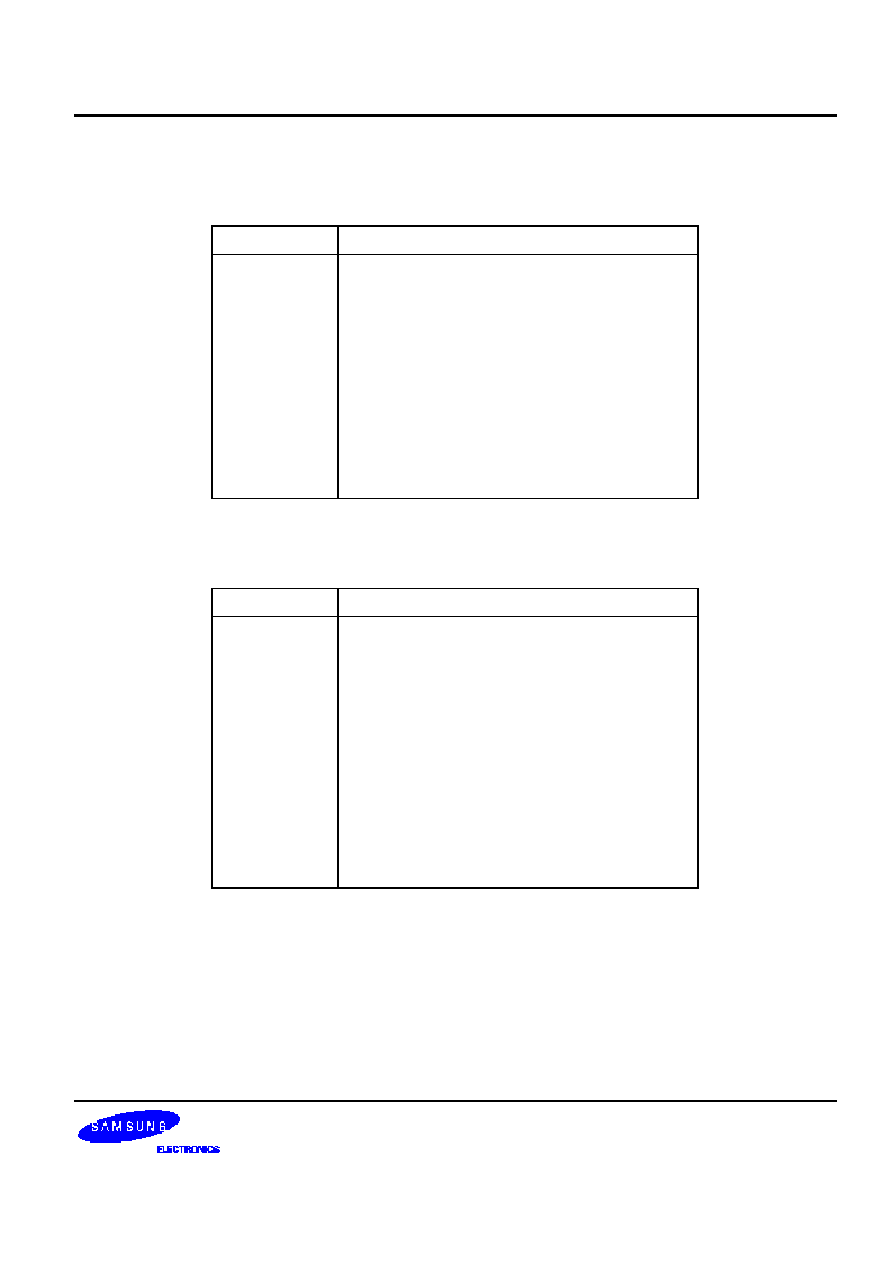

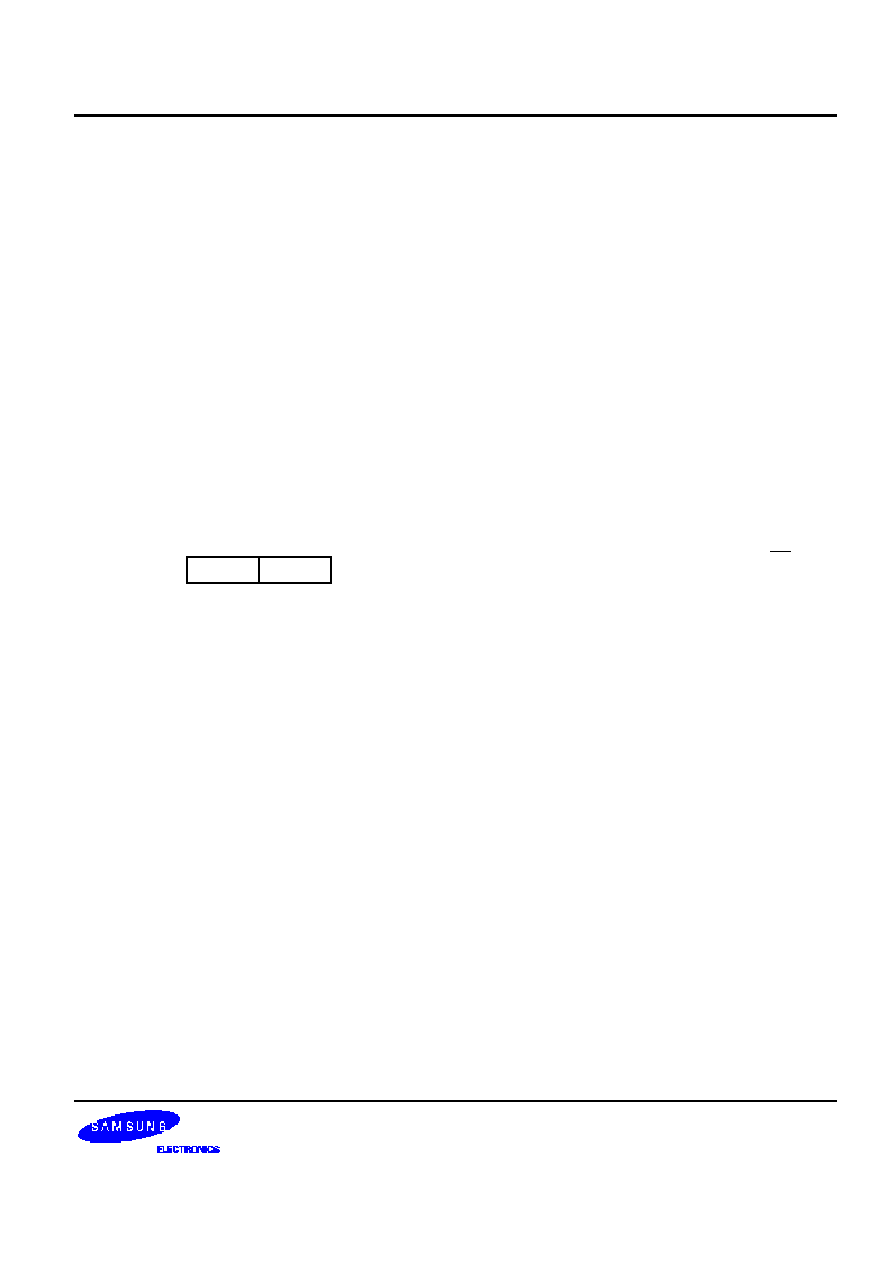

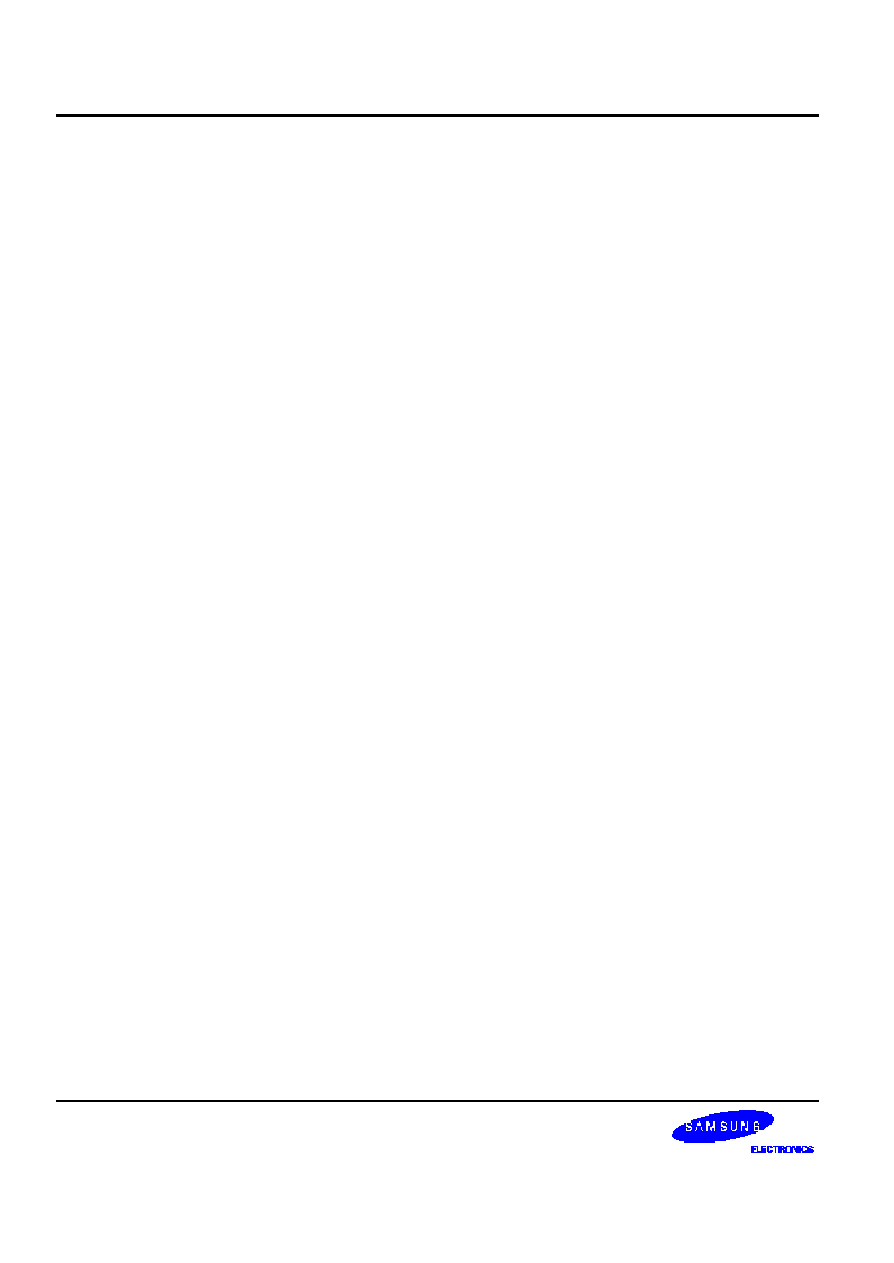

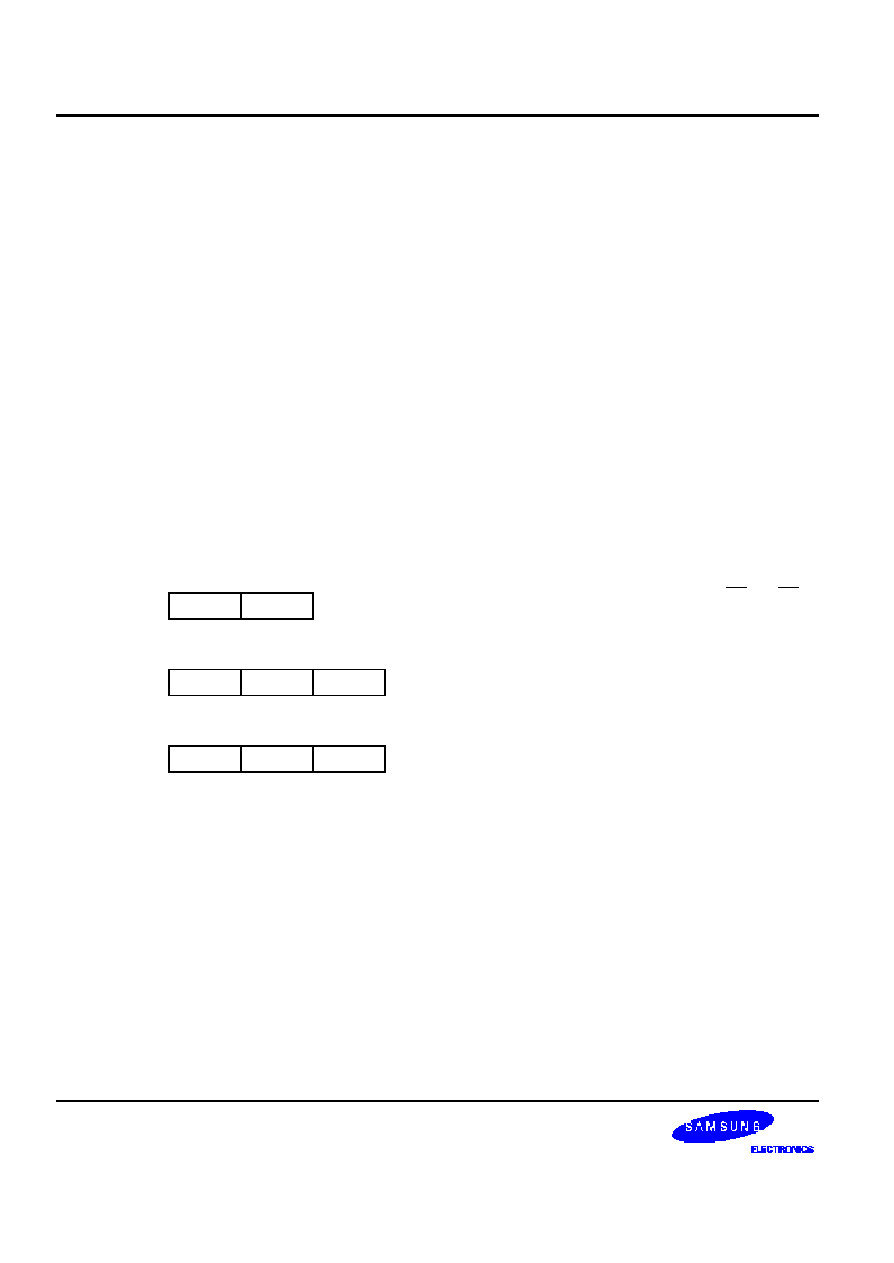

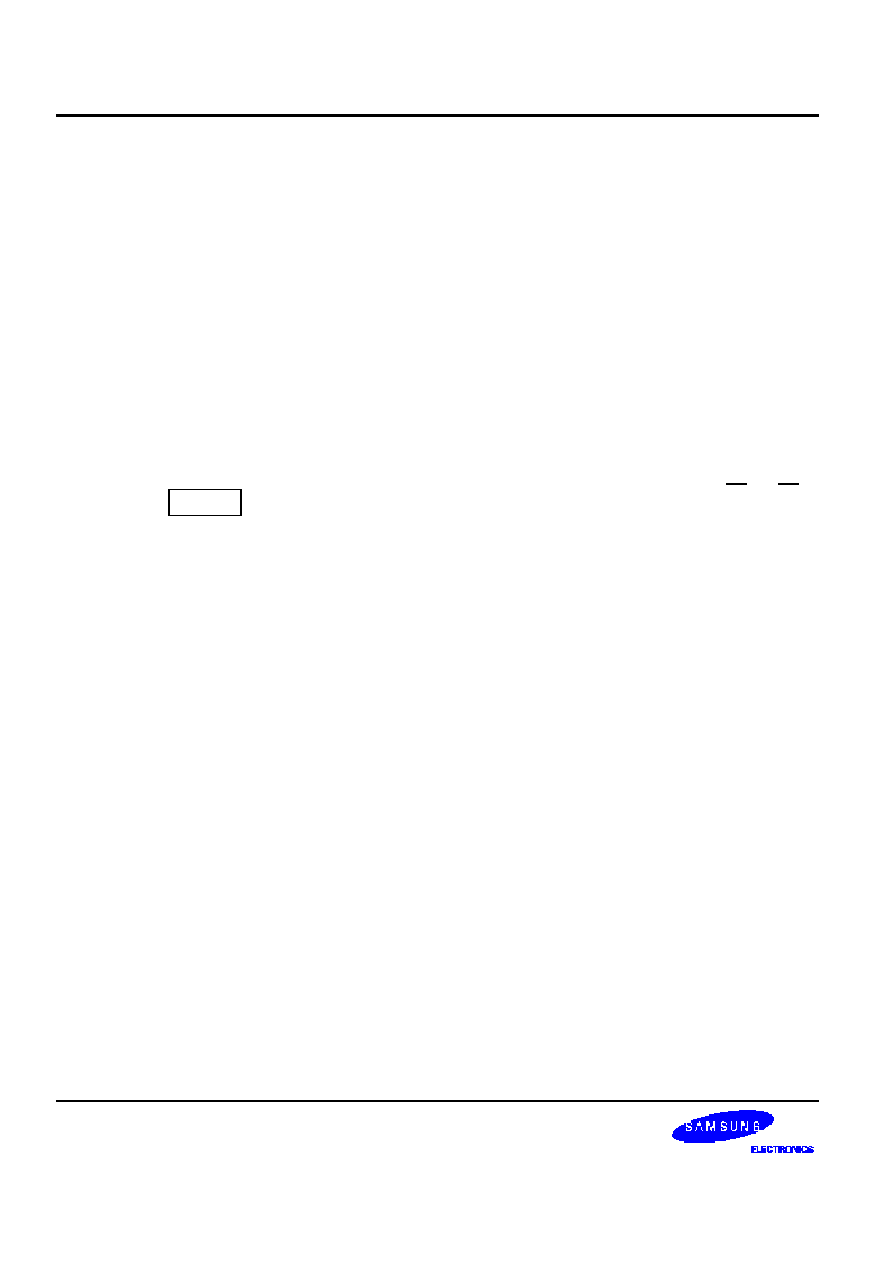

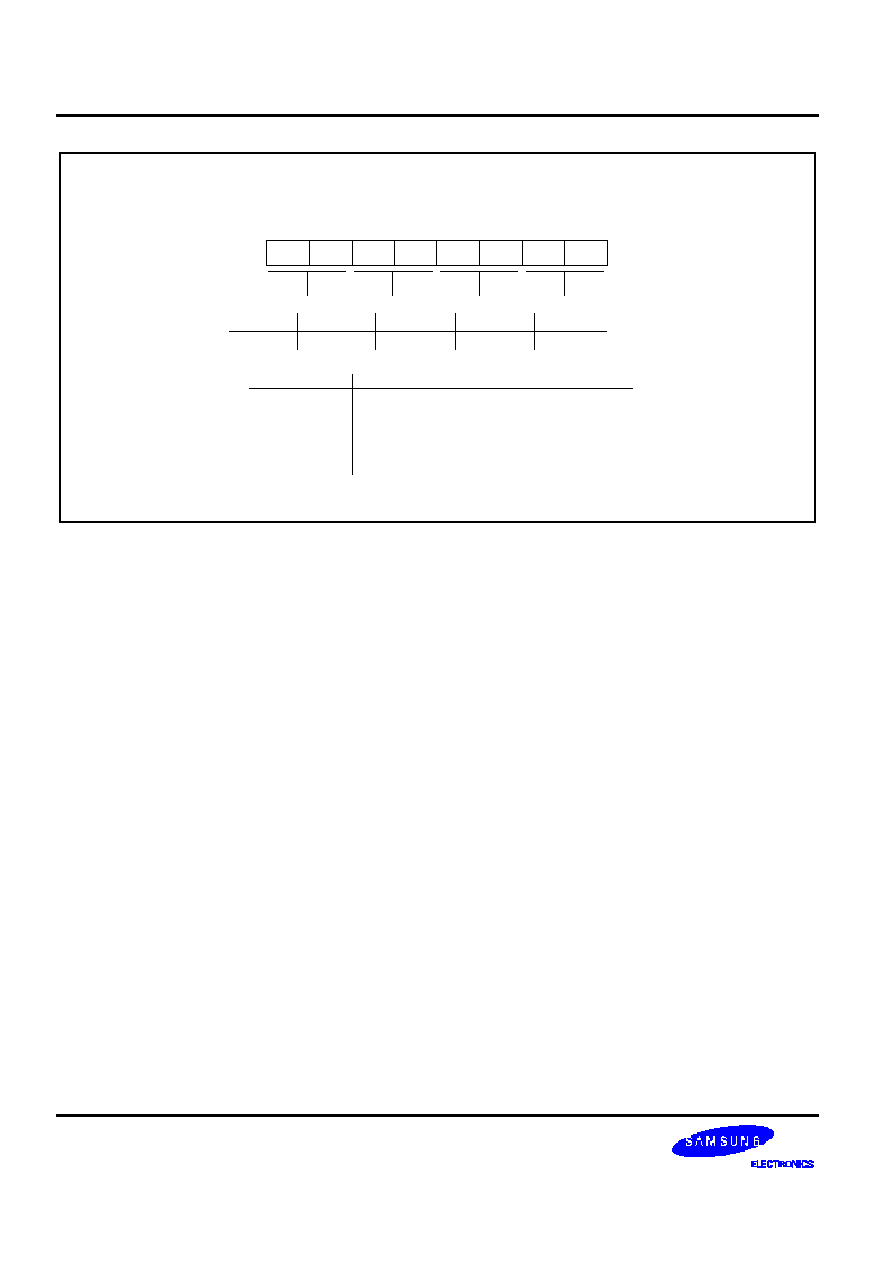

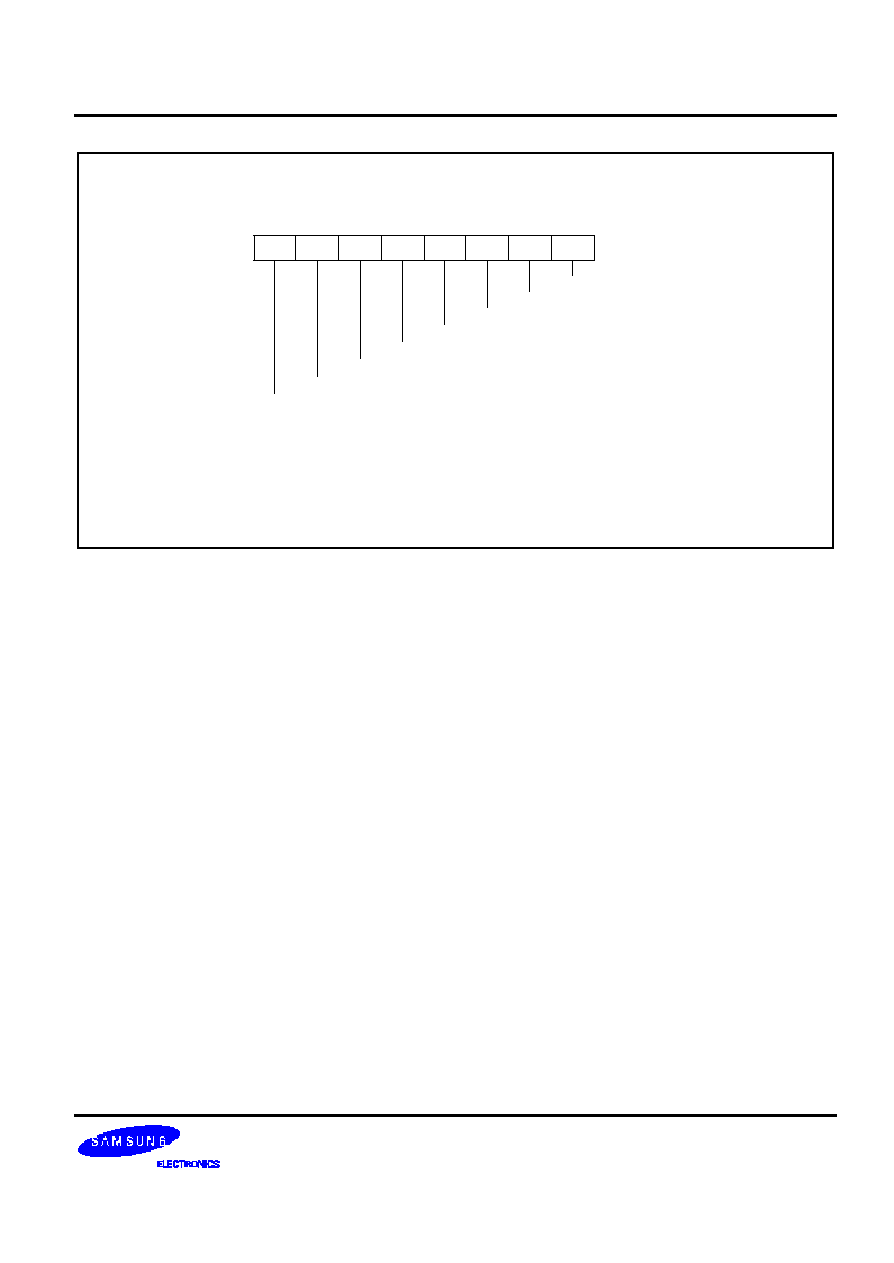

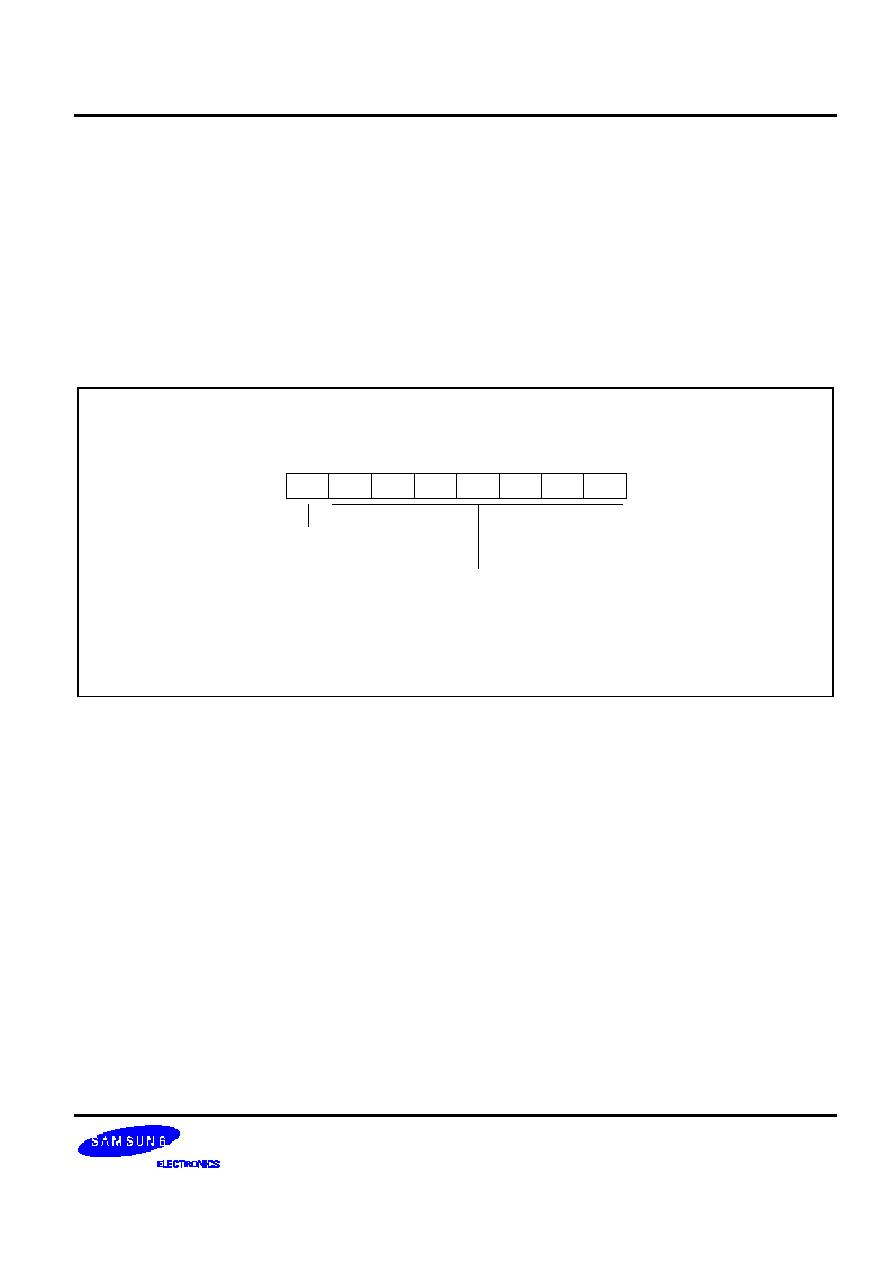

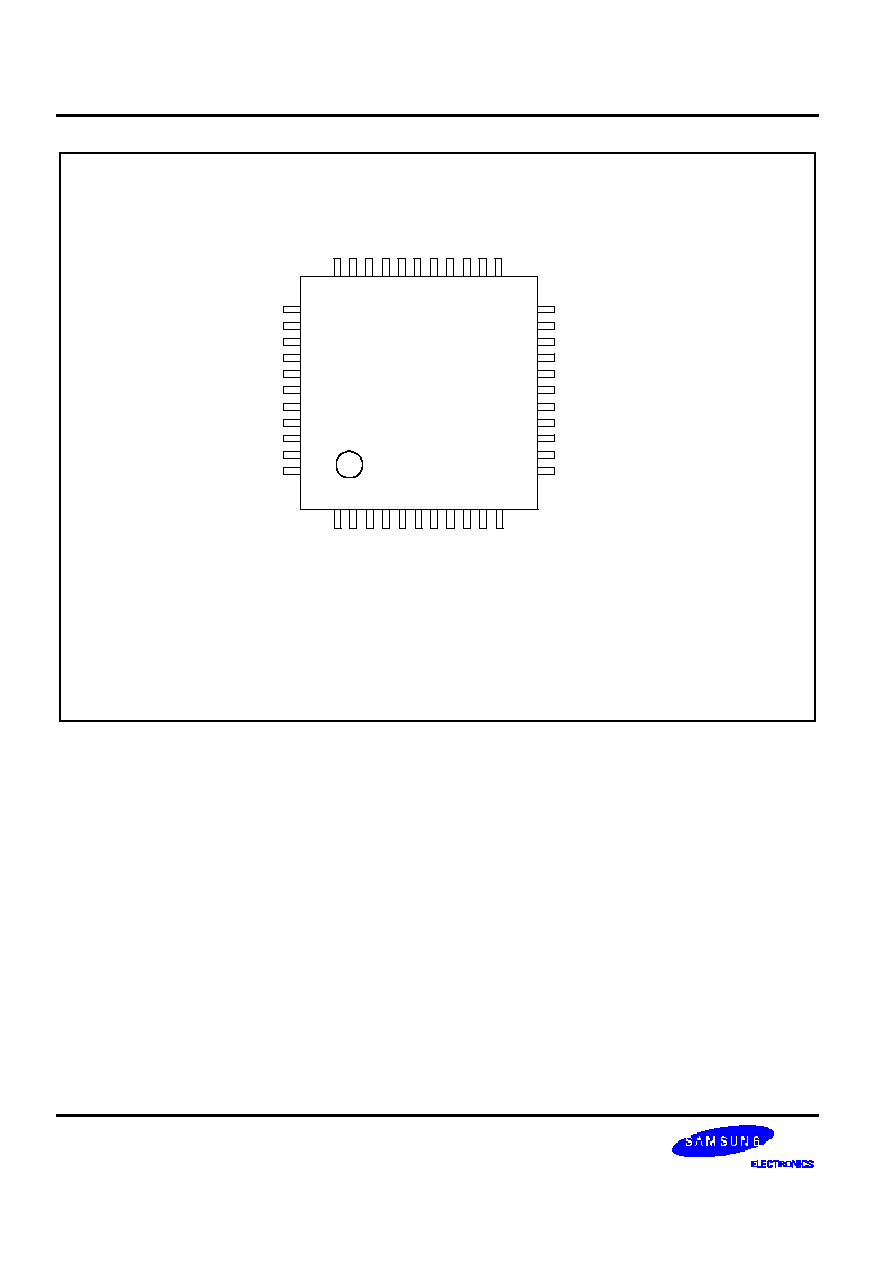

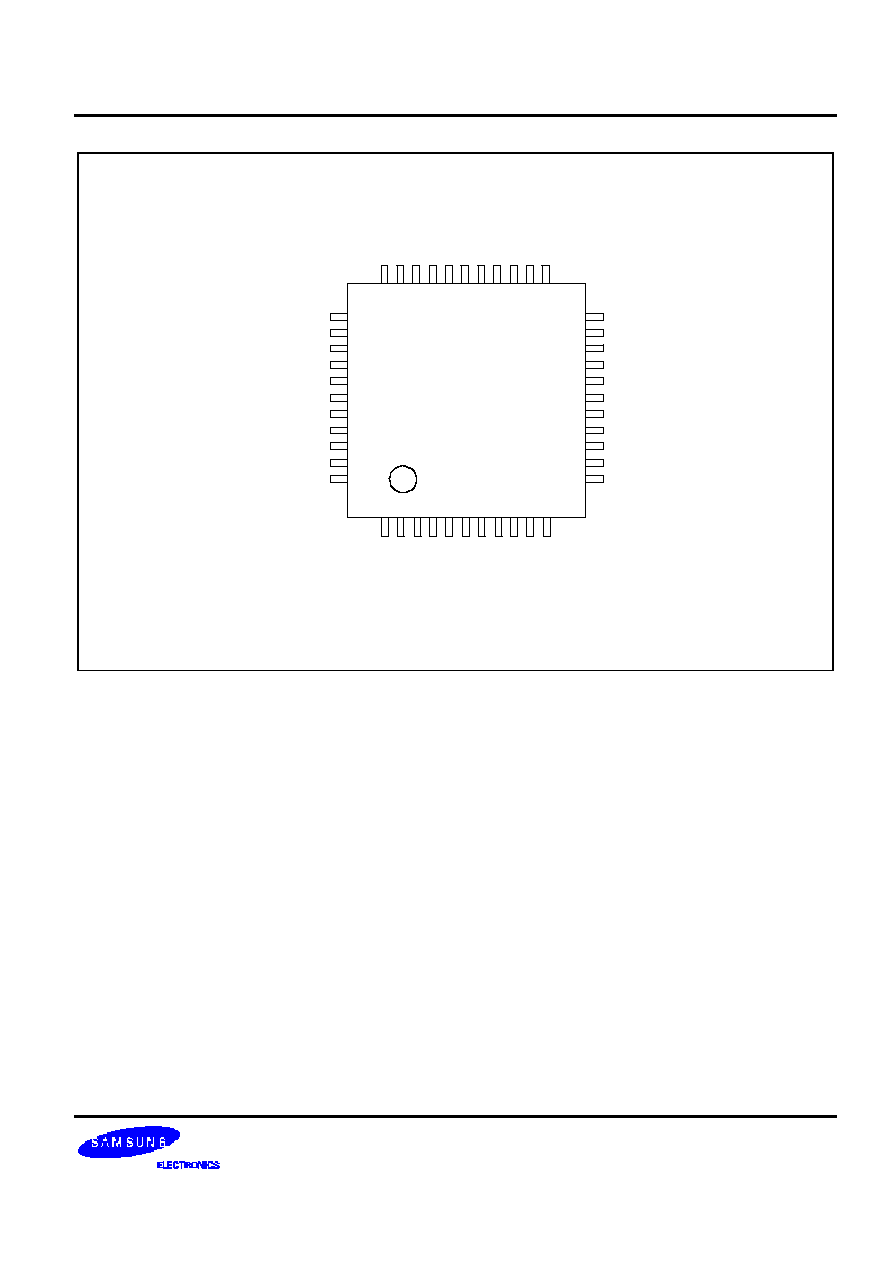

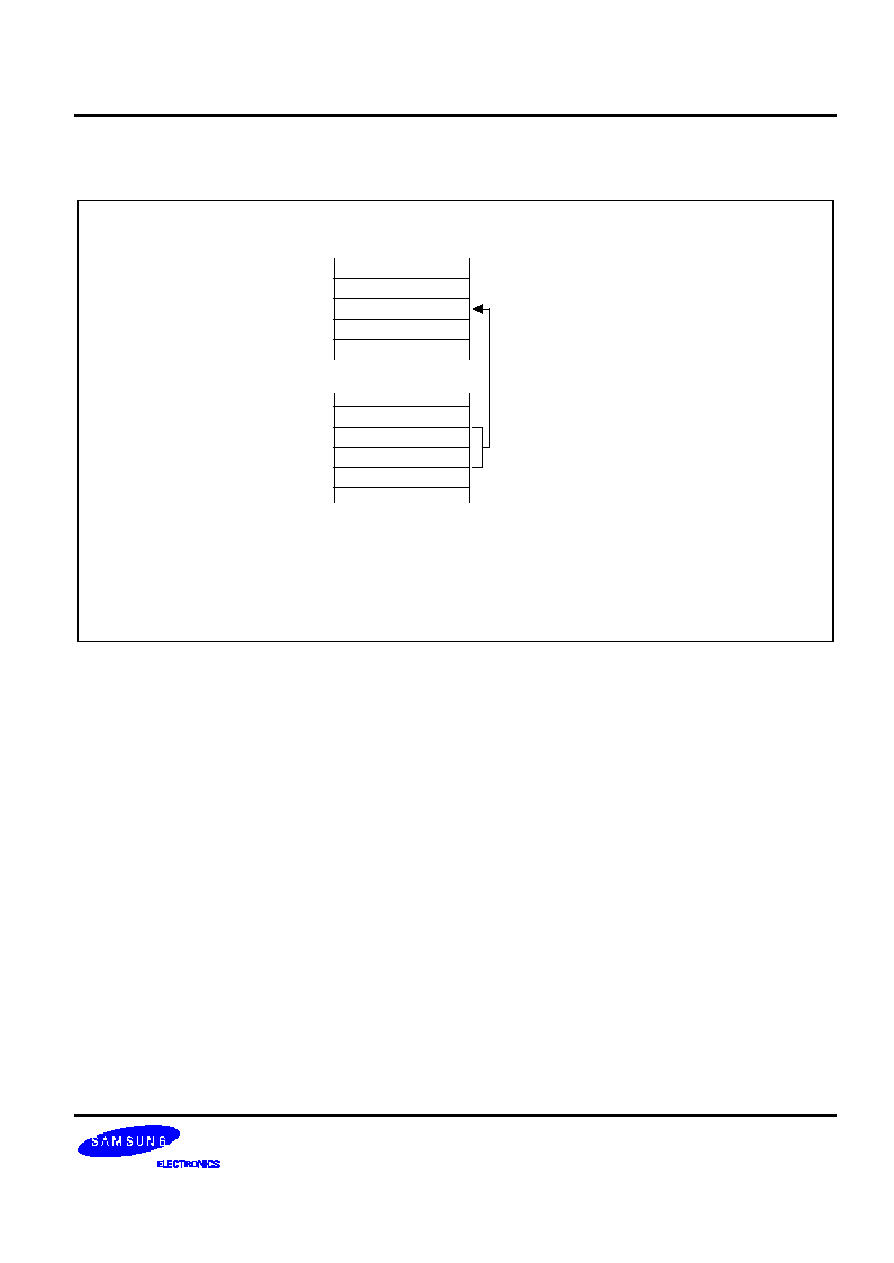

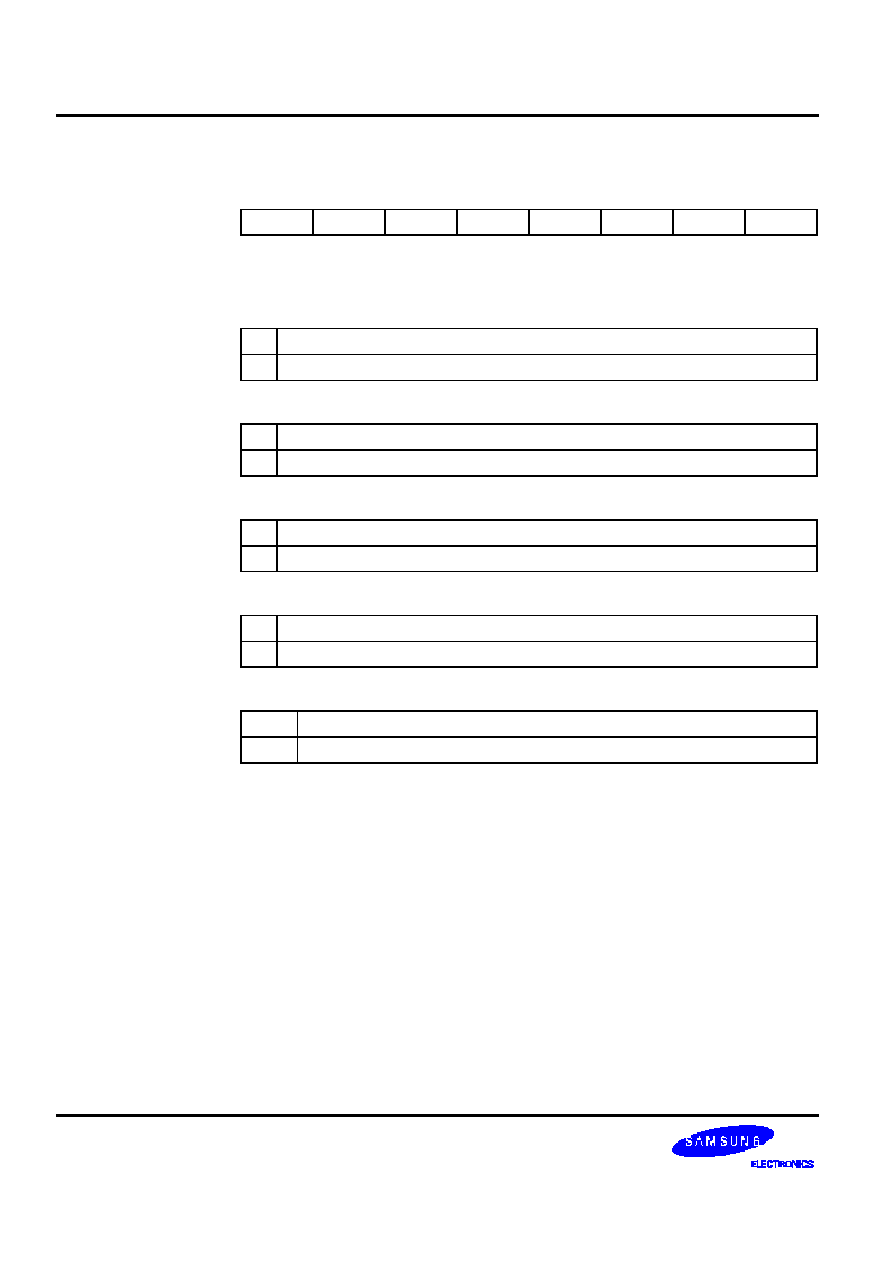

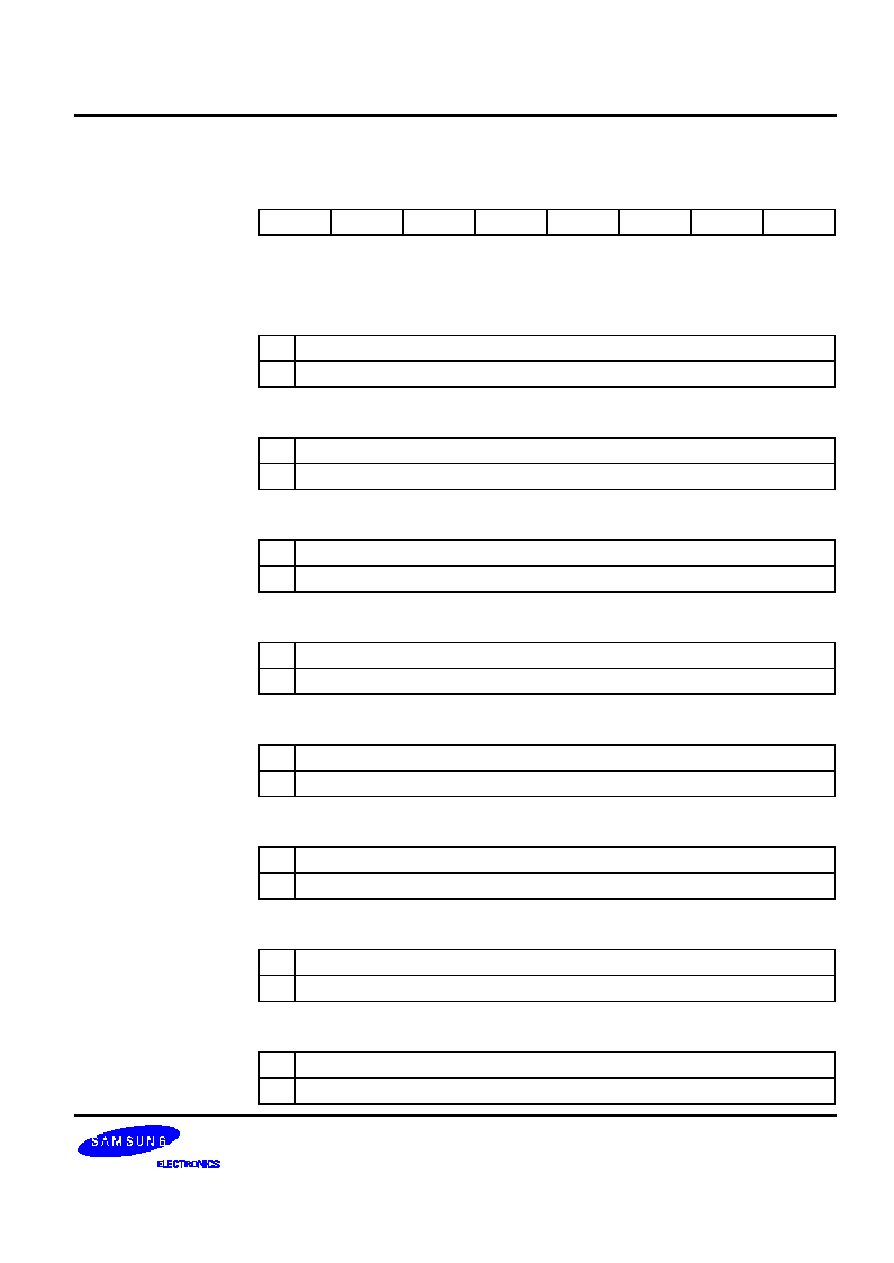

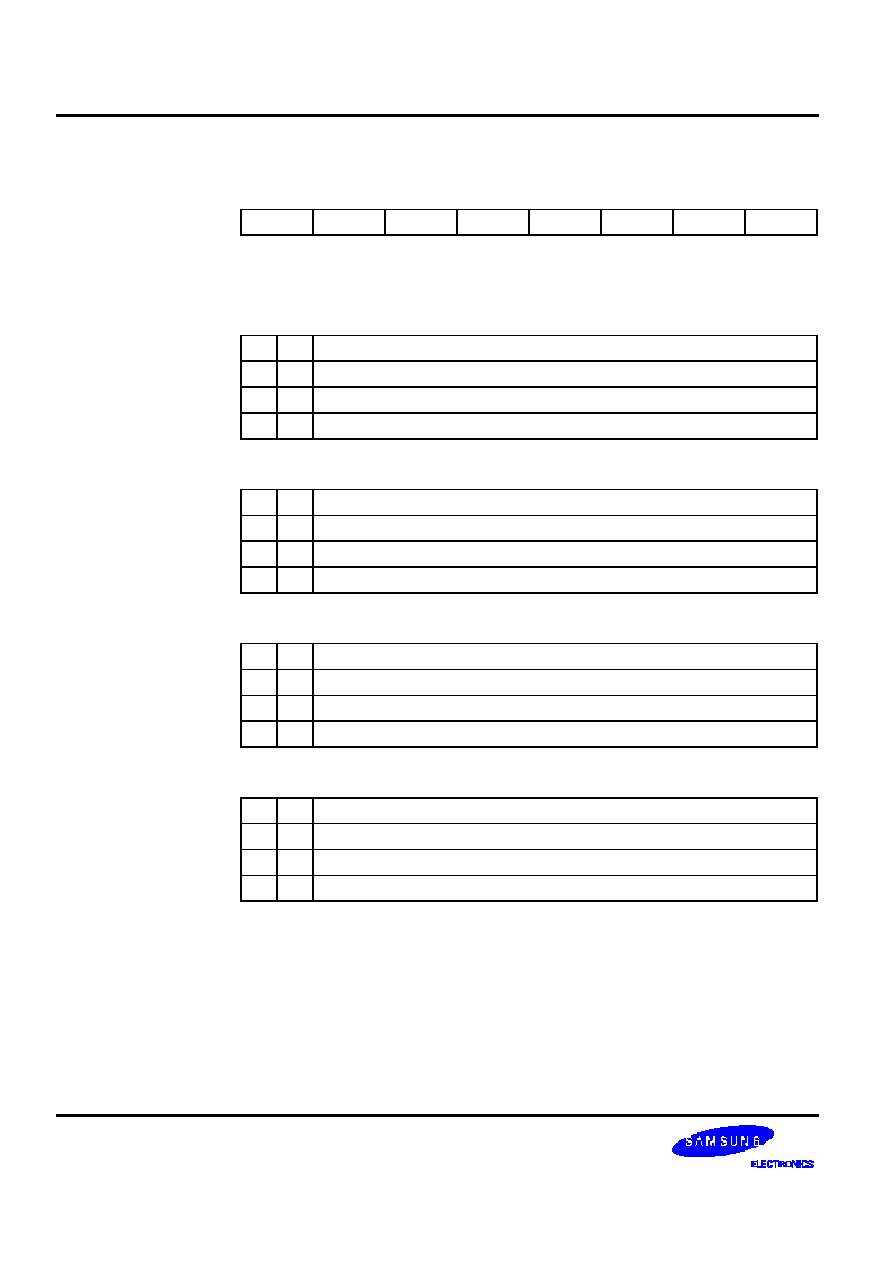

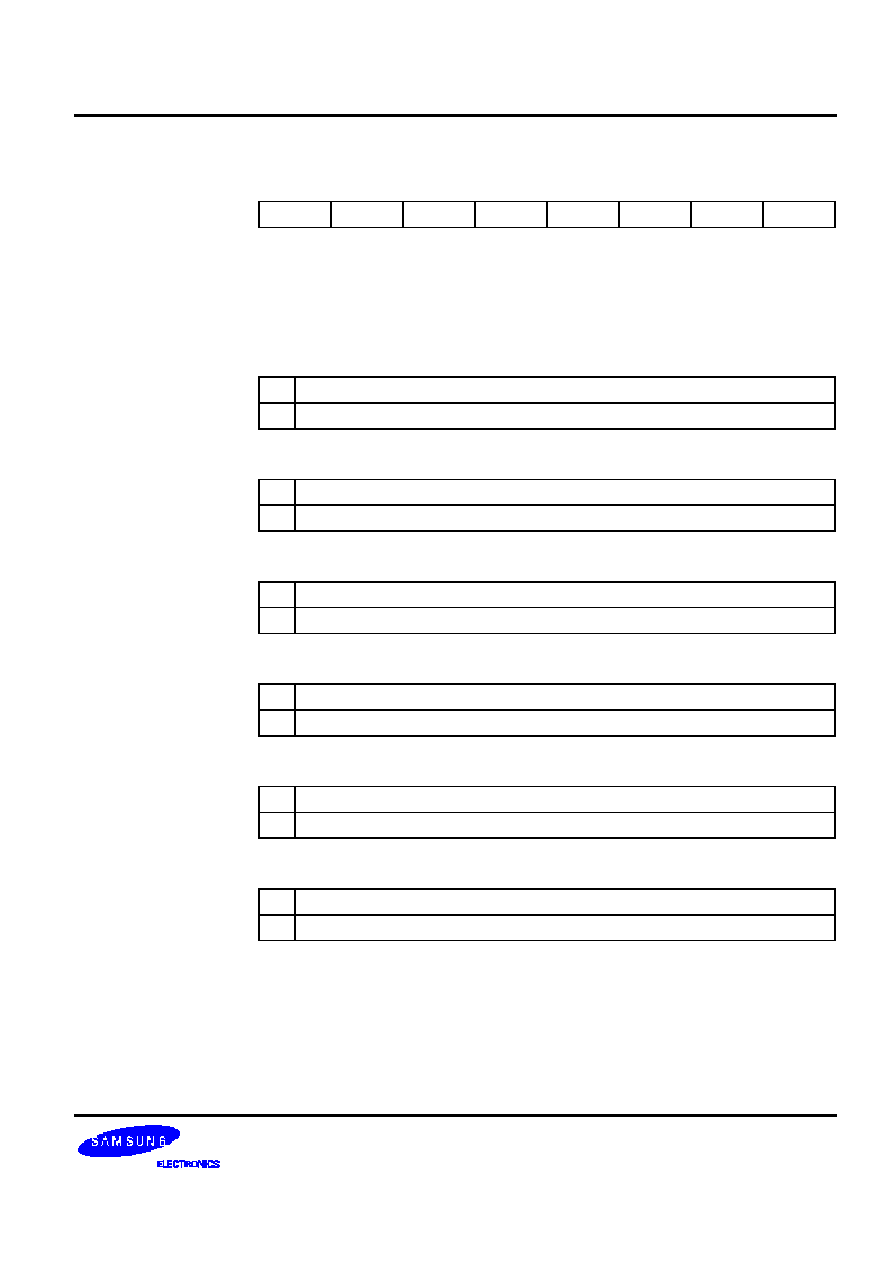

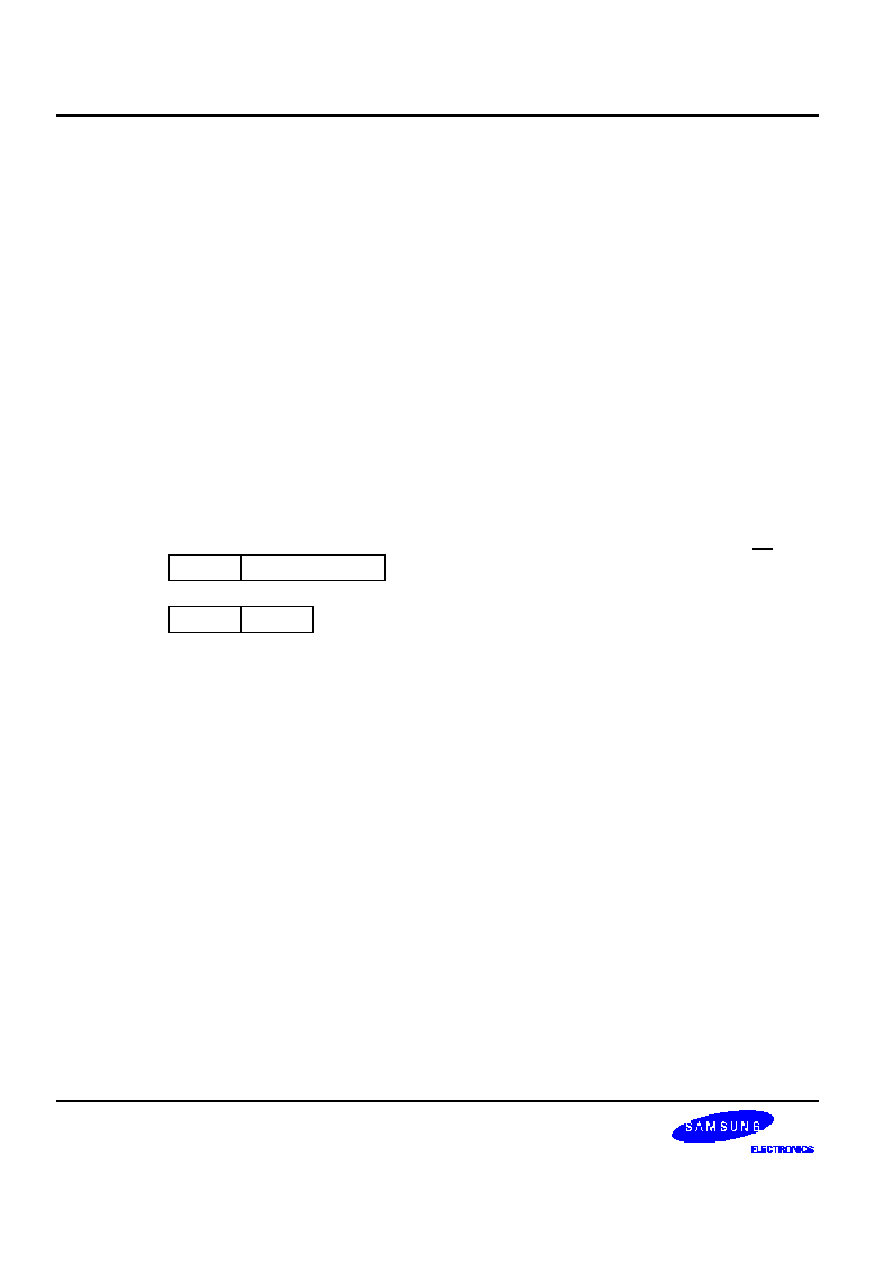

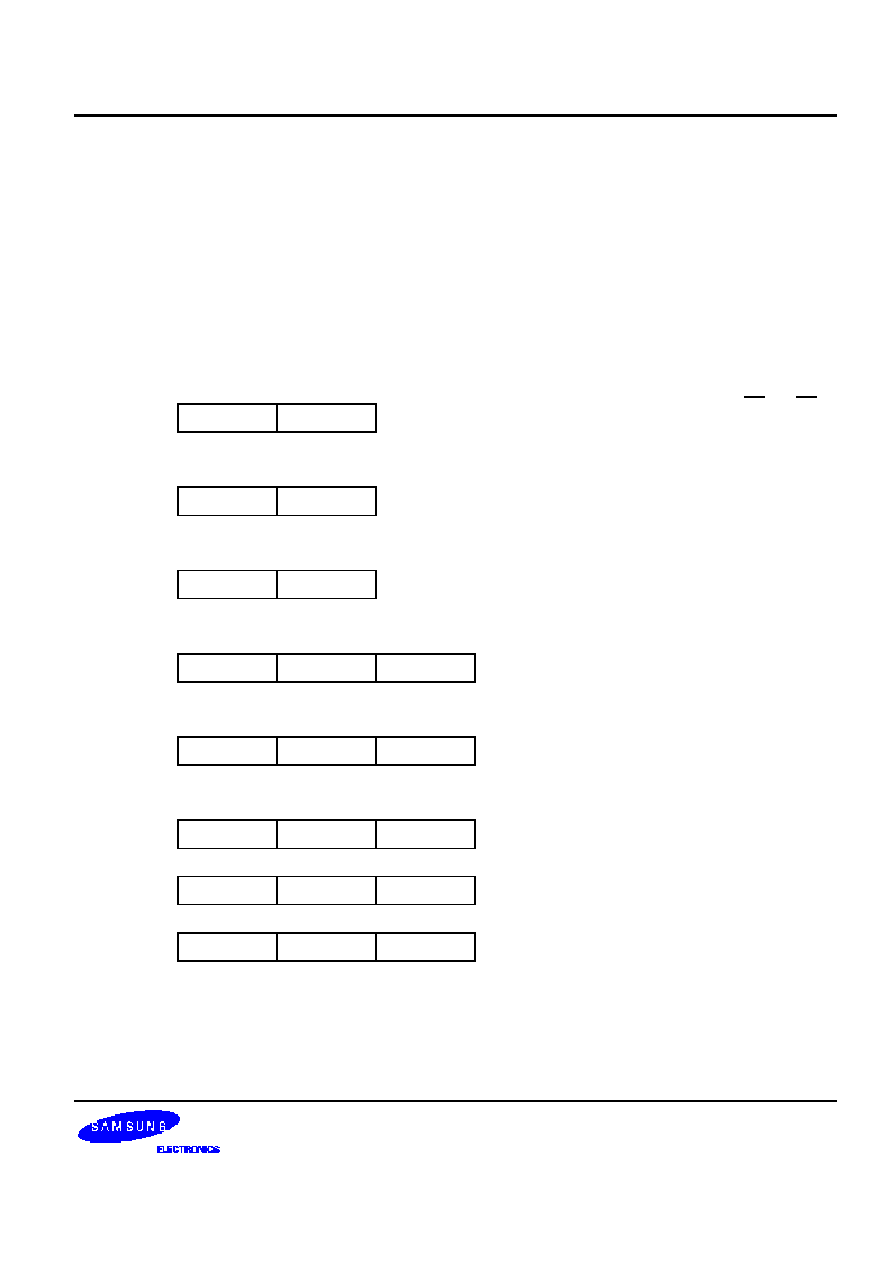

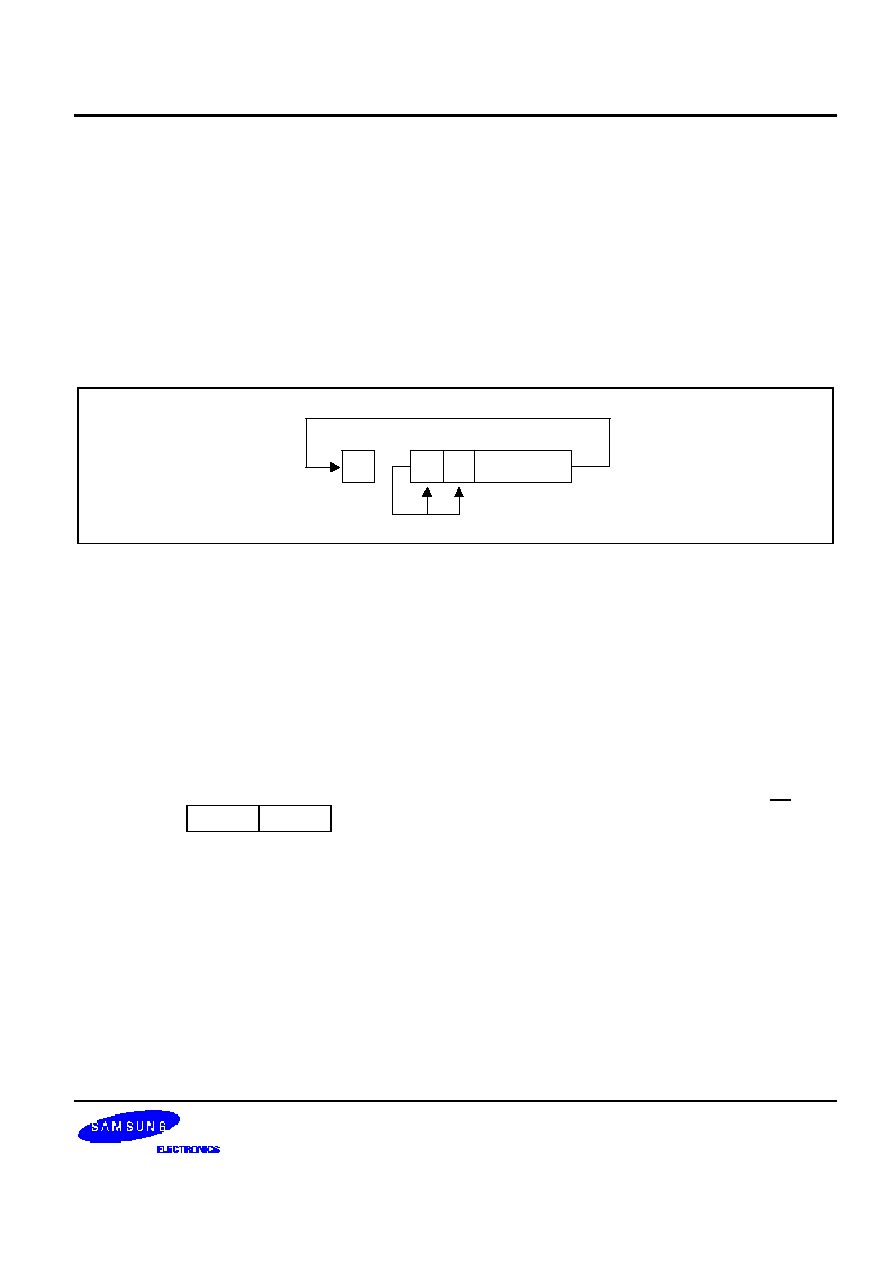

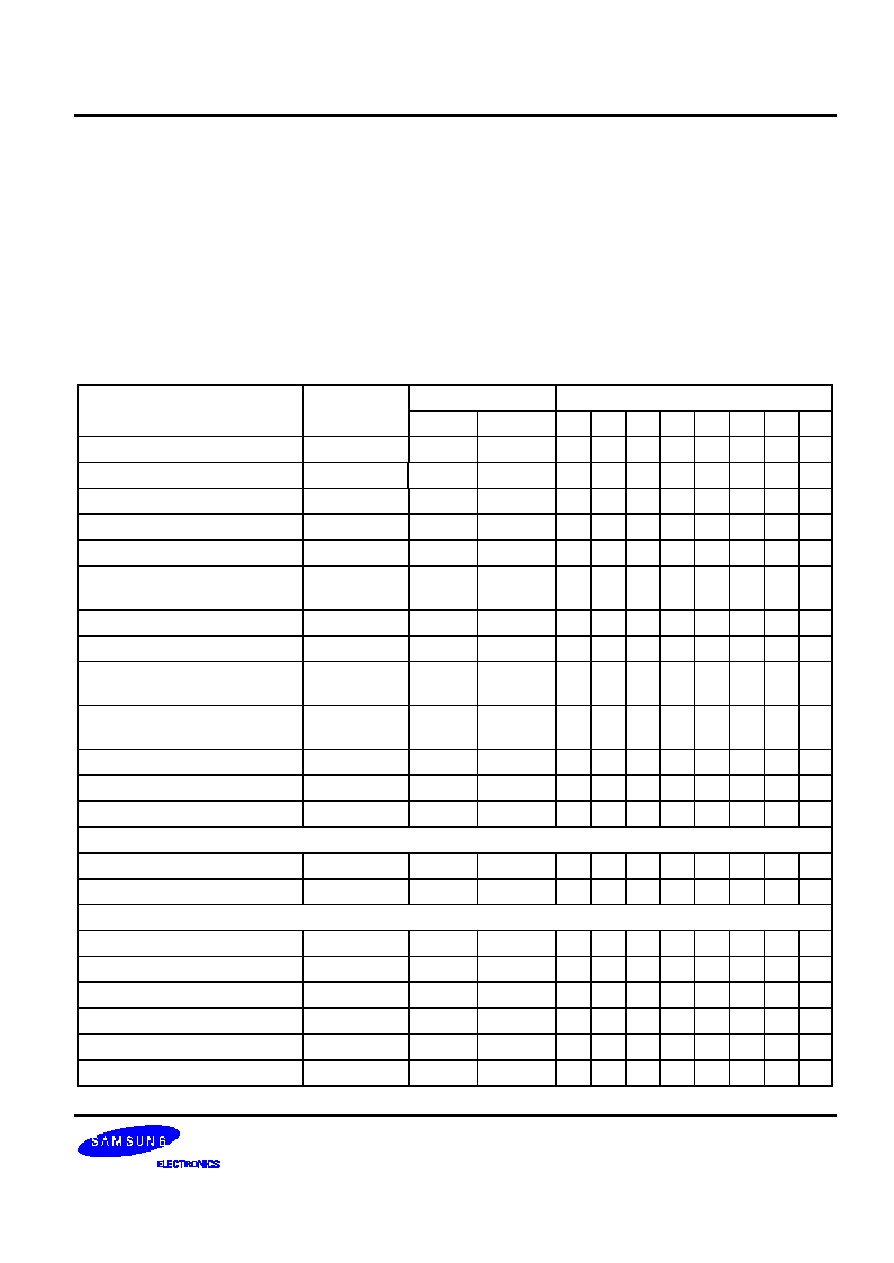

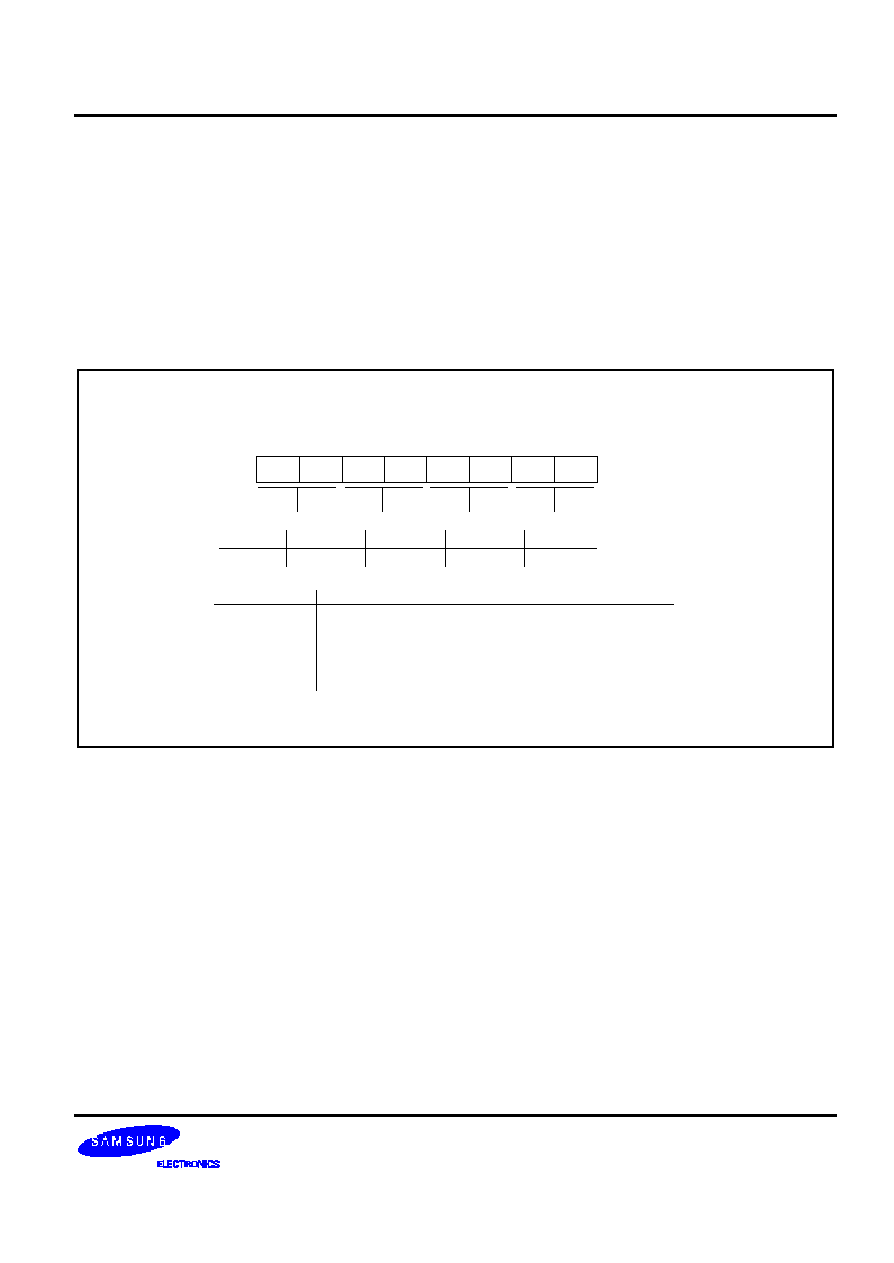

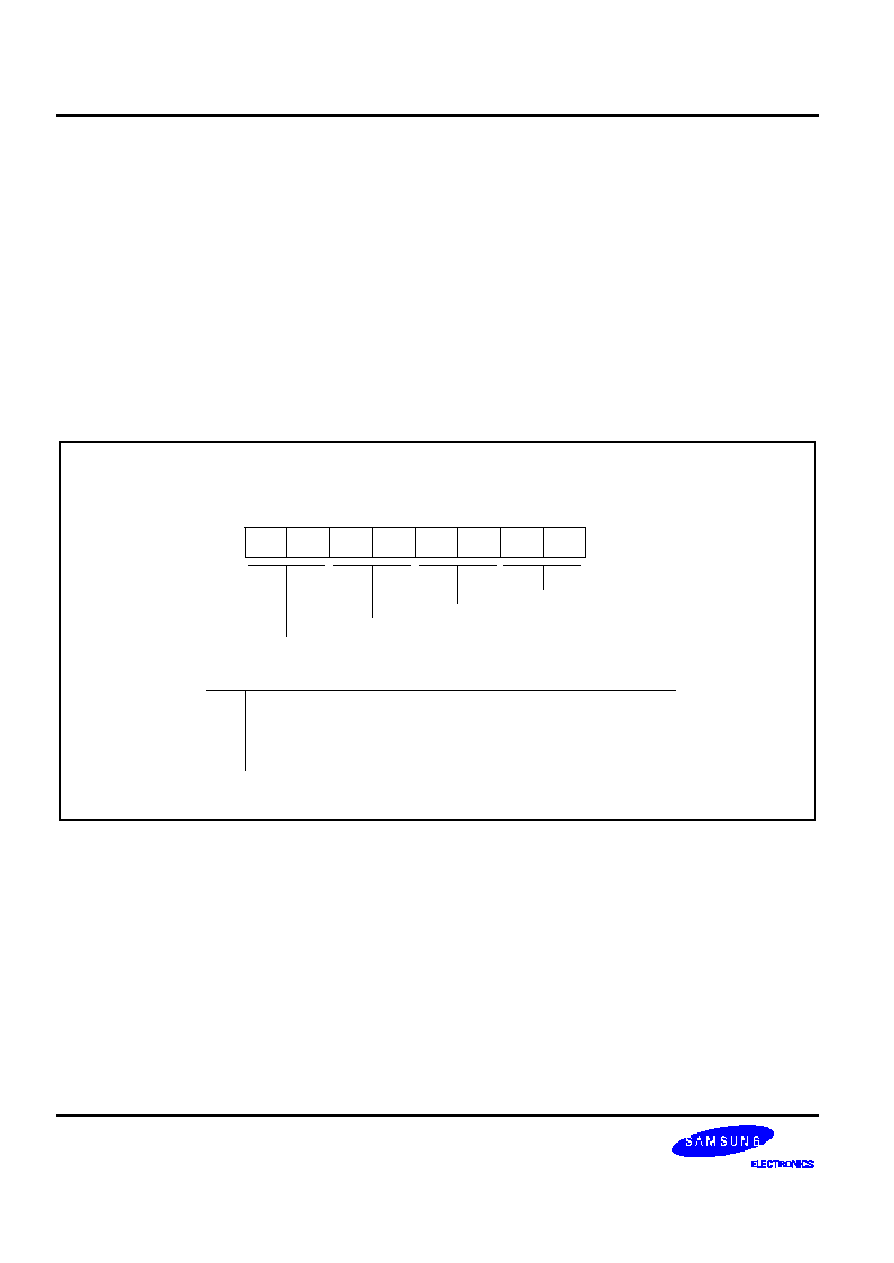

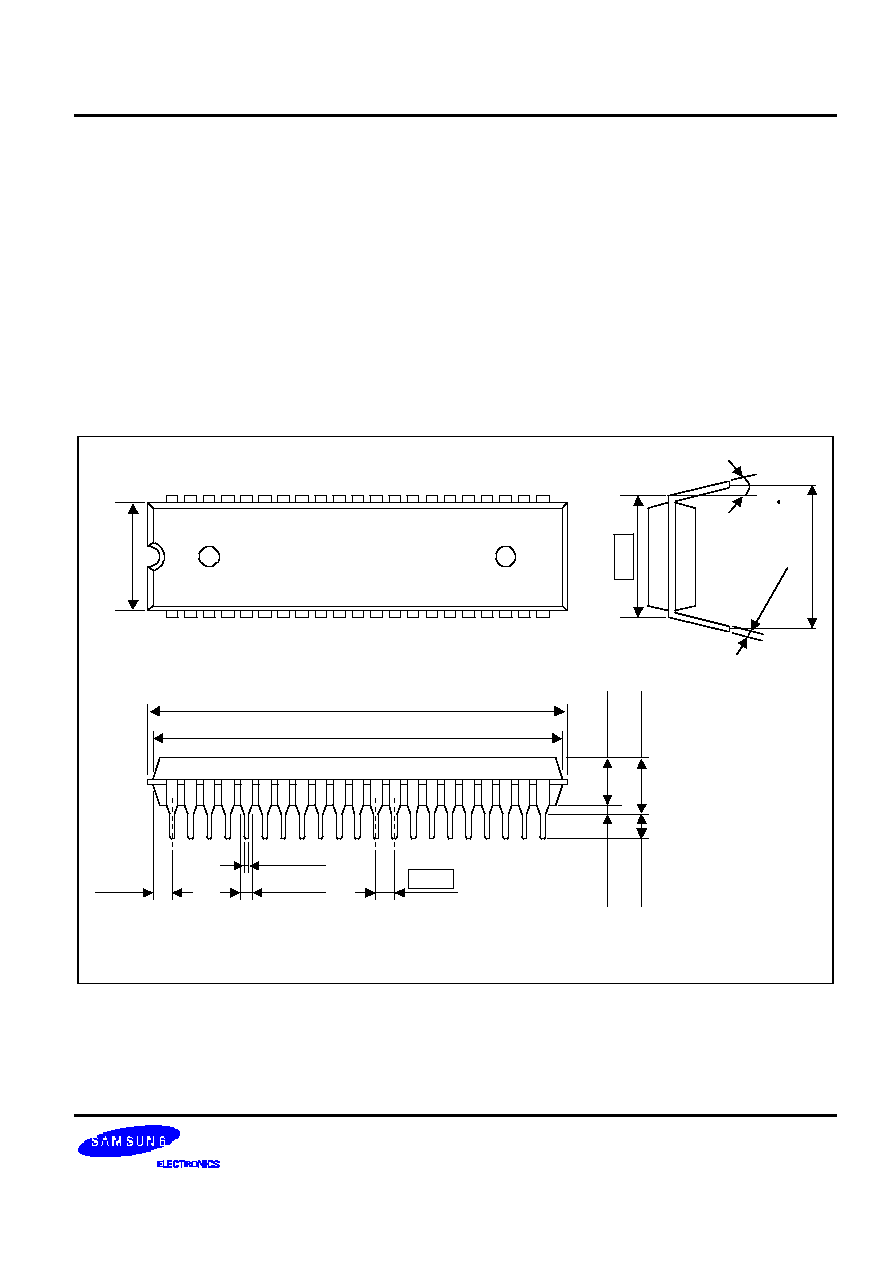

PIN ASSIGNMENTS

S3C9688/P9688

(42-SDIP)

P3.1

P3.0

INT0/P2.0

INT0/P2.1

INT0/P2.2

INT0/P2.3

INT0/P2.4

INT0/P2.5

INT0/P2.6

INT0/P2.7

V

DD

V

SS

X

OUT

X

IN

TEST

INT1/P4.0

INT1/P4.1

RESET

INT1/P4.2

INT1/P4.3

P1.7

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

P3.2

P3.3/CLO

D+/PS2

D-/PS2

3.3V

OUT

NC

P0.0/INT2

P0.1/INT2

P0.2/INT2

P0.3/INT2

P0.4/INT2

P0.5/INT2

P0.6/INT2

P0.7/INT2

P1.0

P1.1

P1.2

P1.3

P1.4

P1.5

P1.6

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

Figure 1-2. Pin Assignment Diagram (42-Pin SDIP Package)

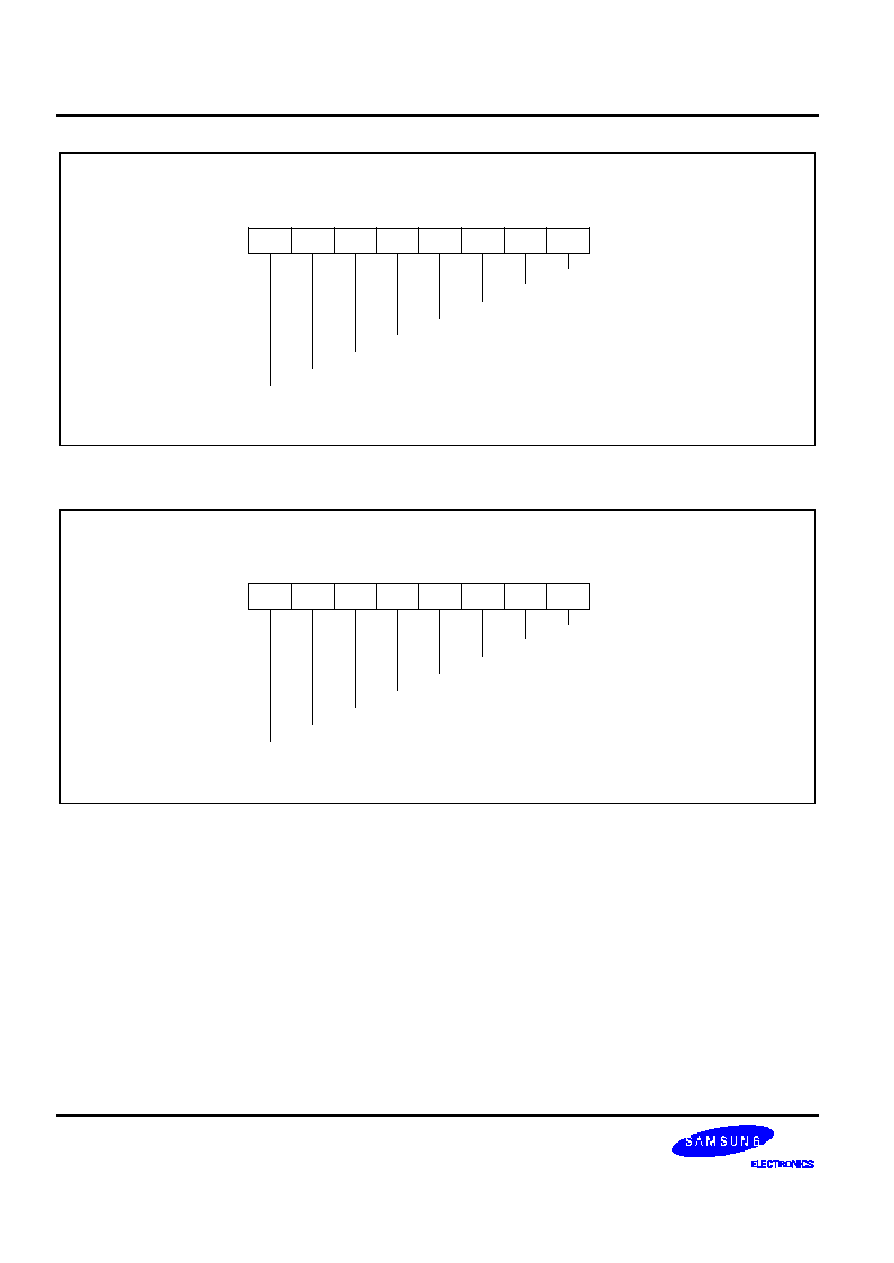

S3C9688/P9688

PRODUCT OVERVIEW

1-5

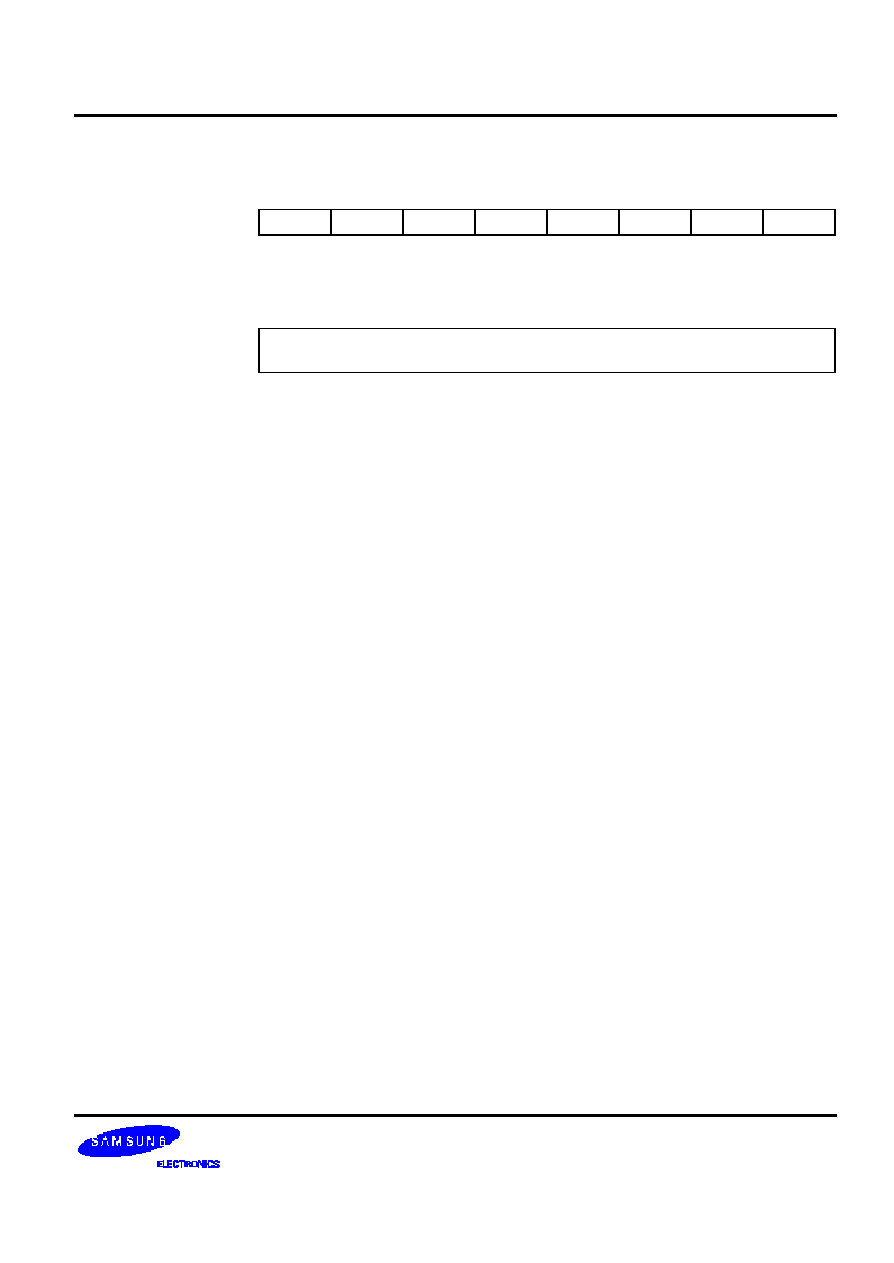

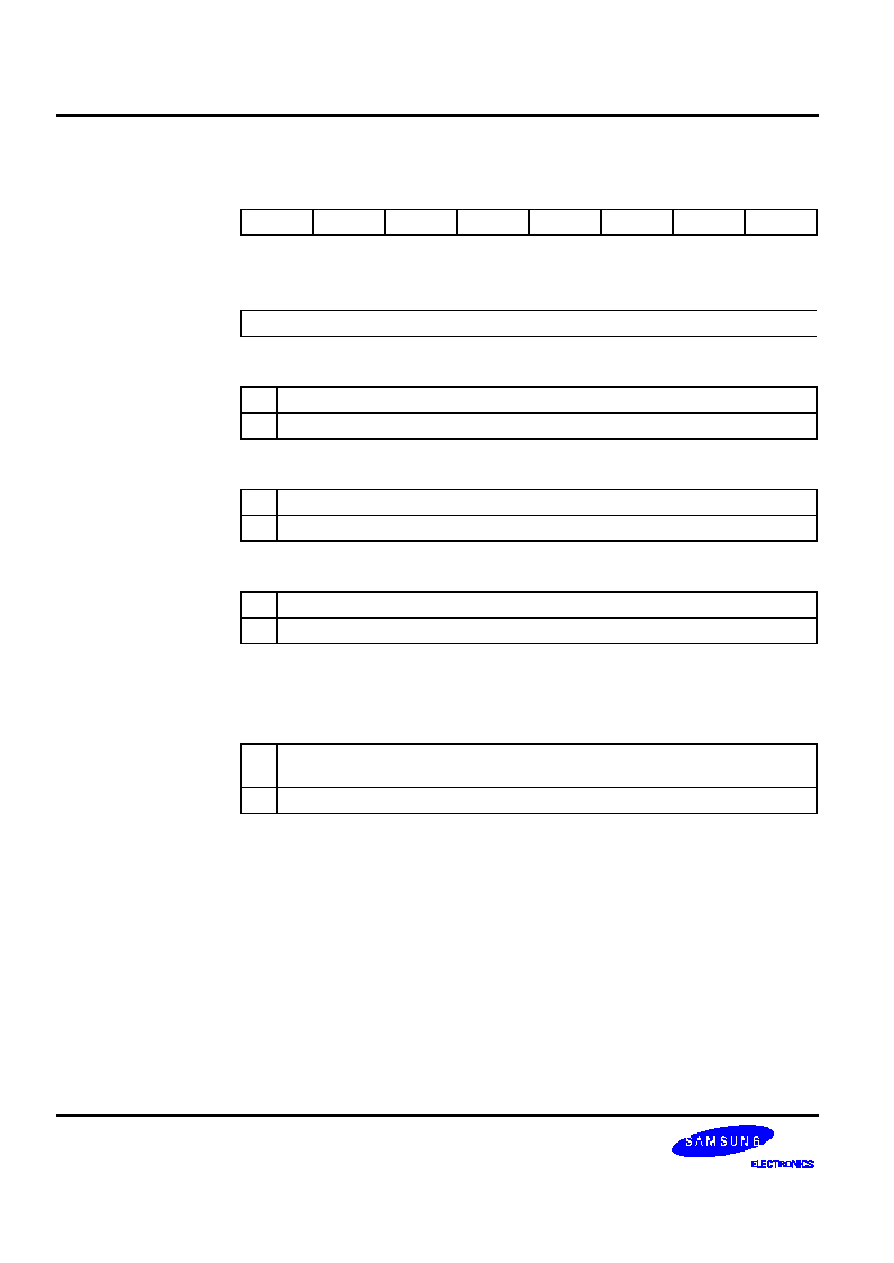

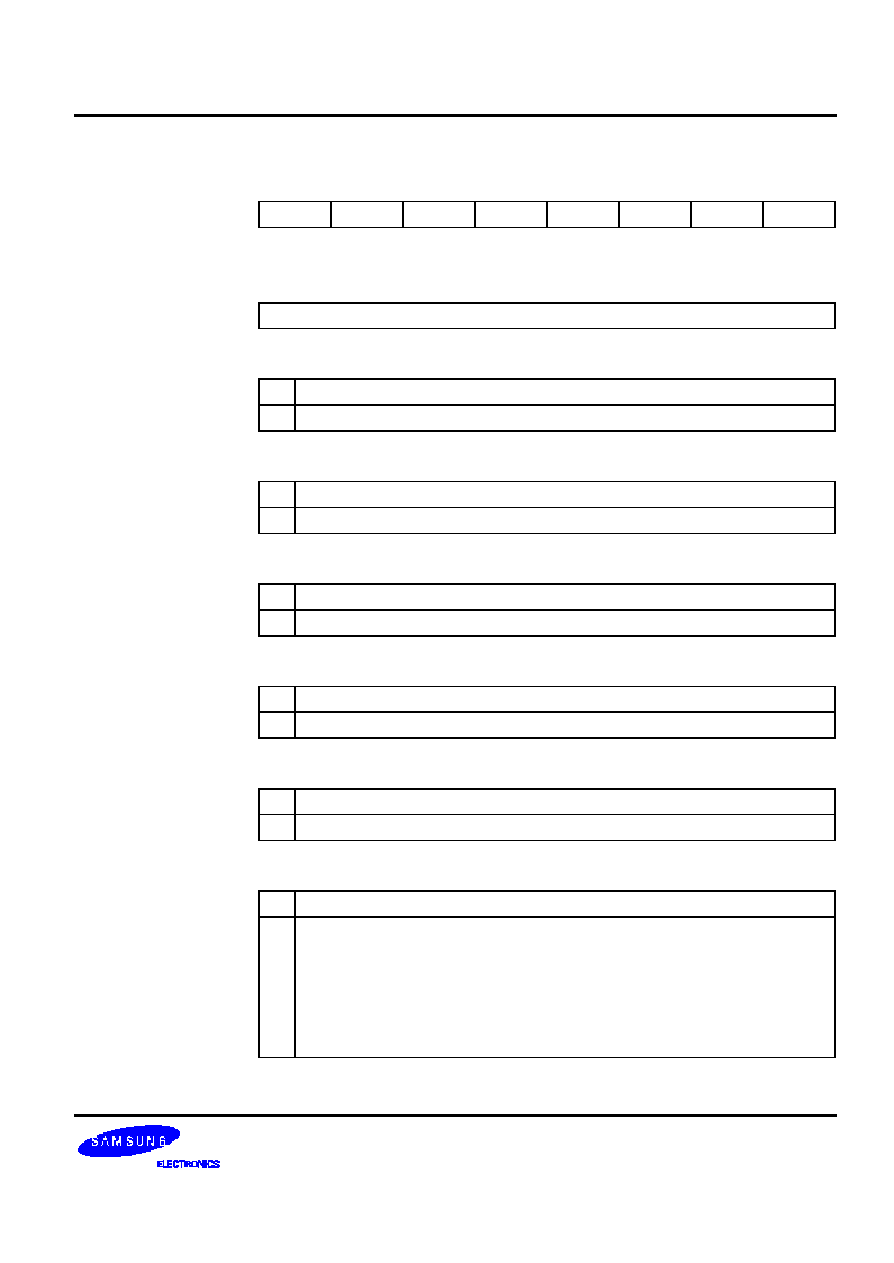

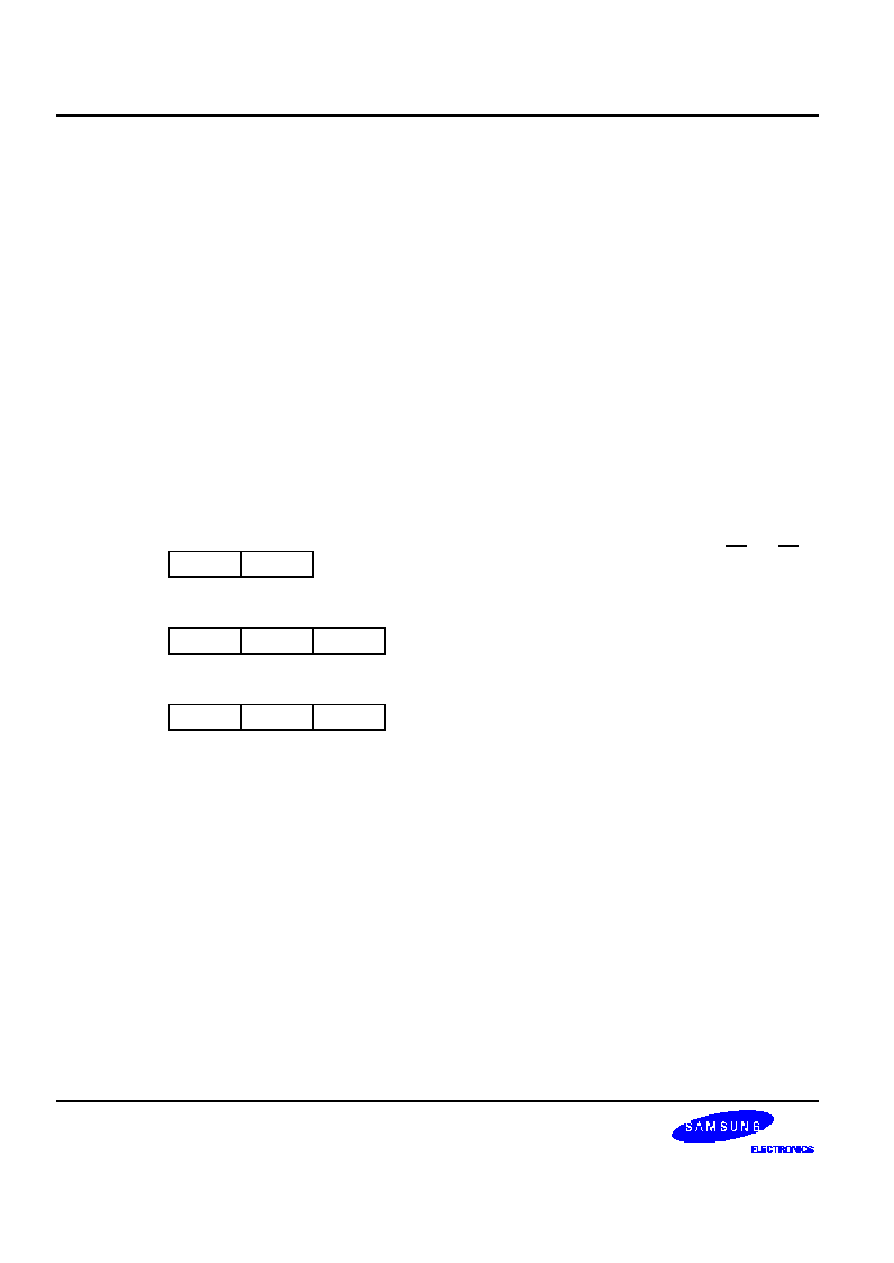

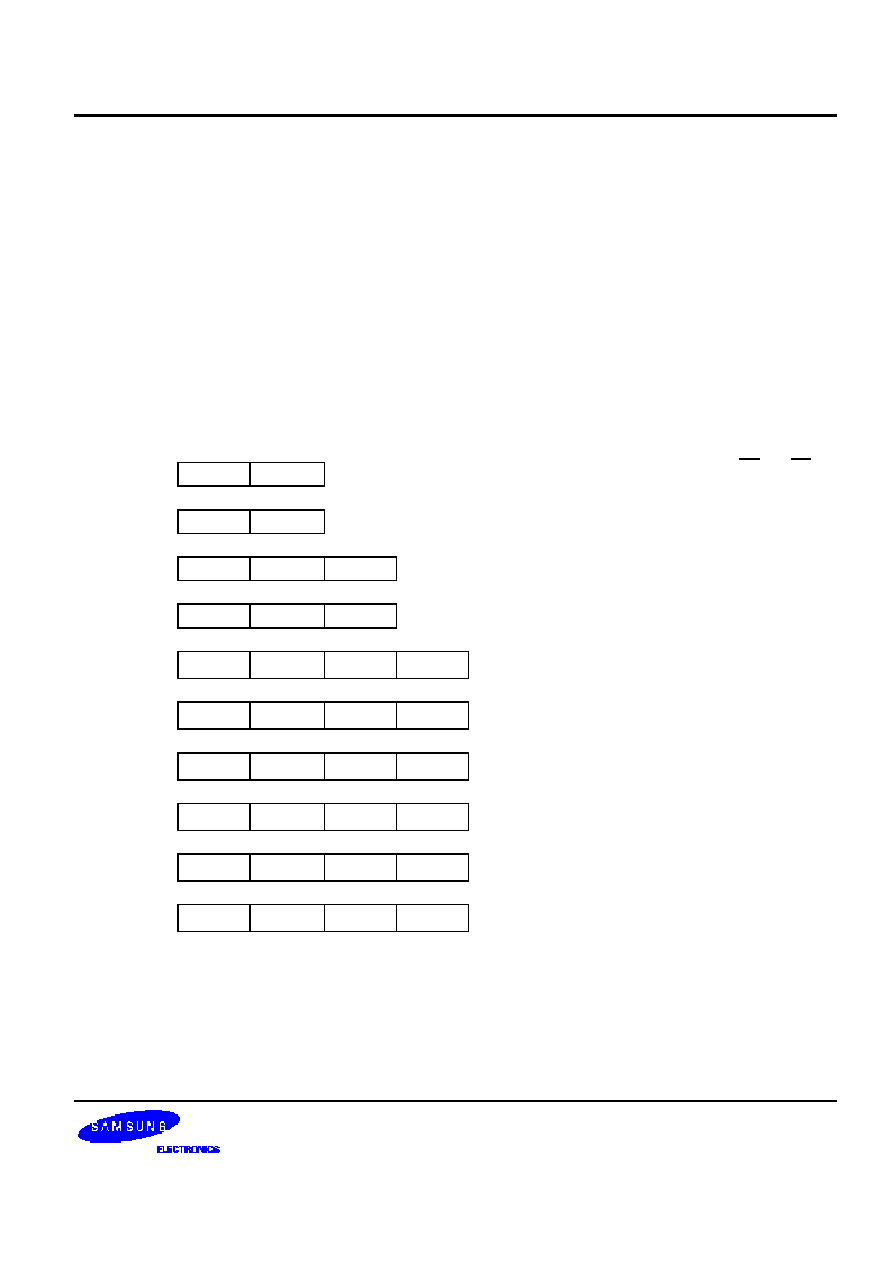

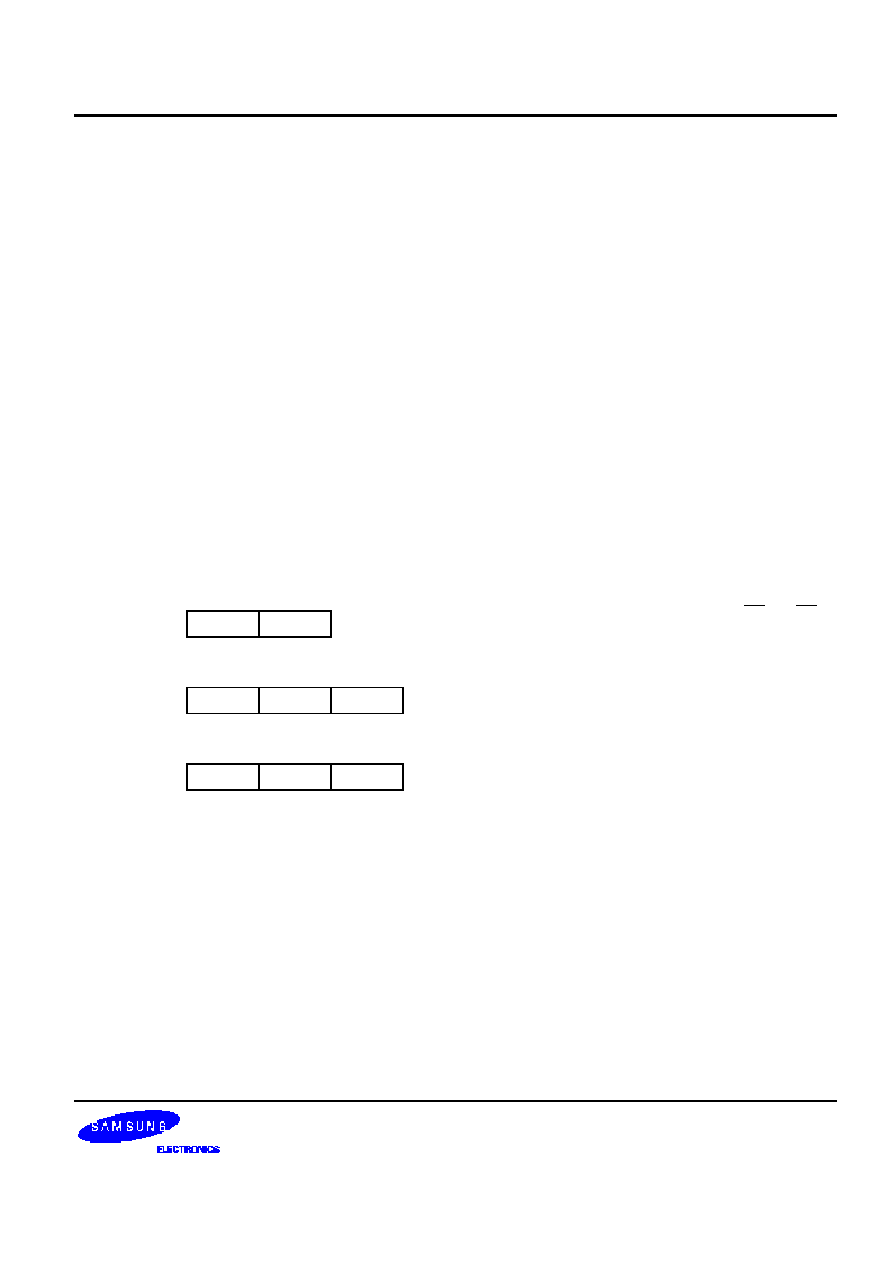

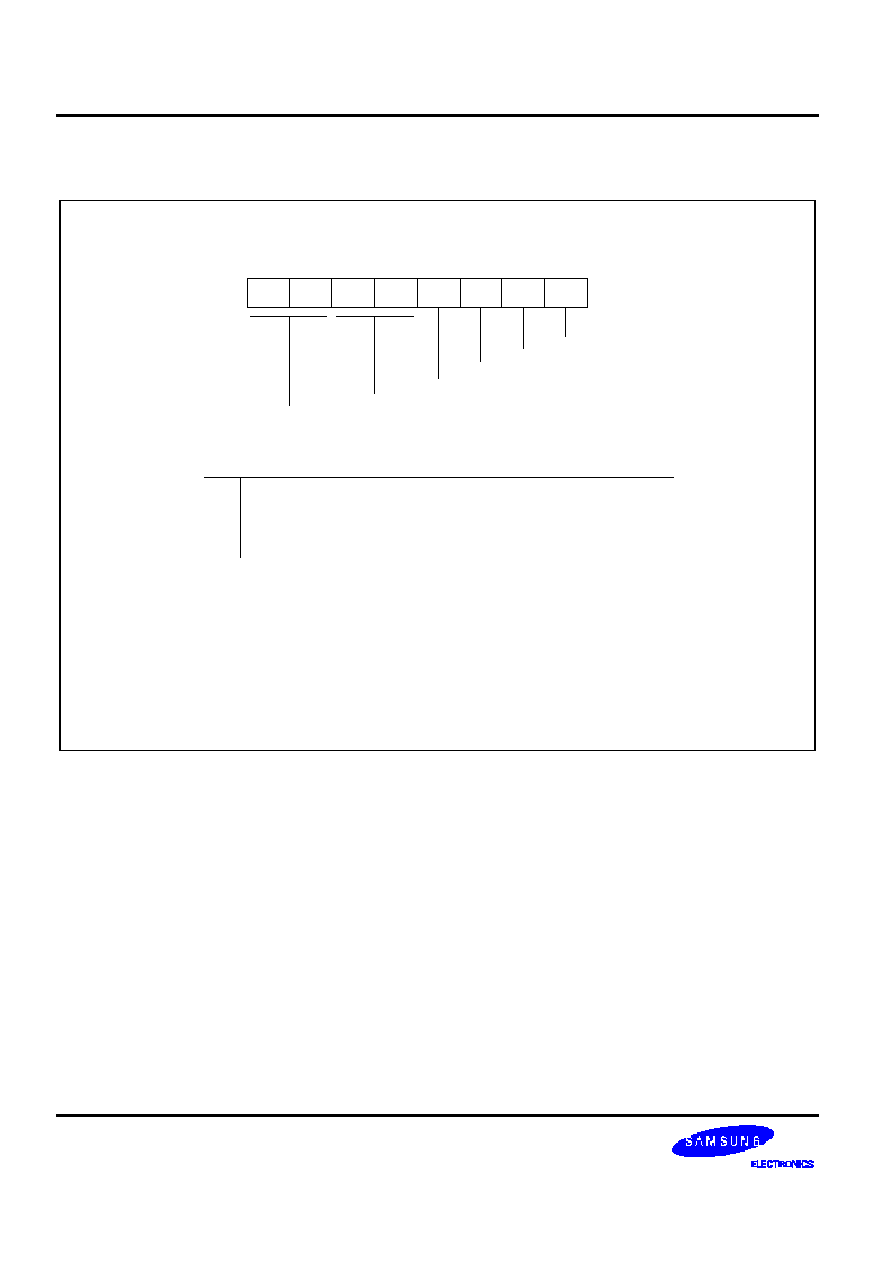

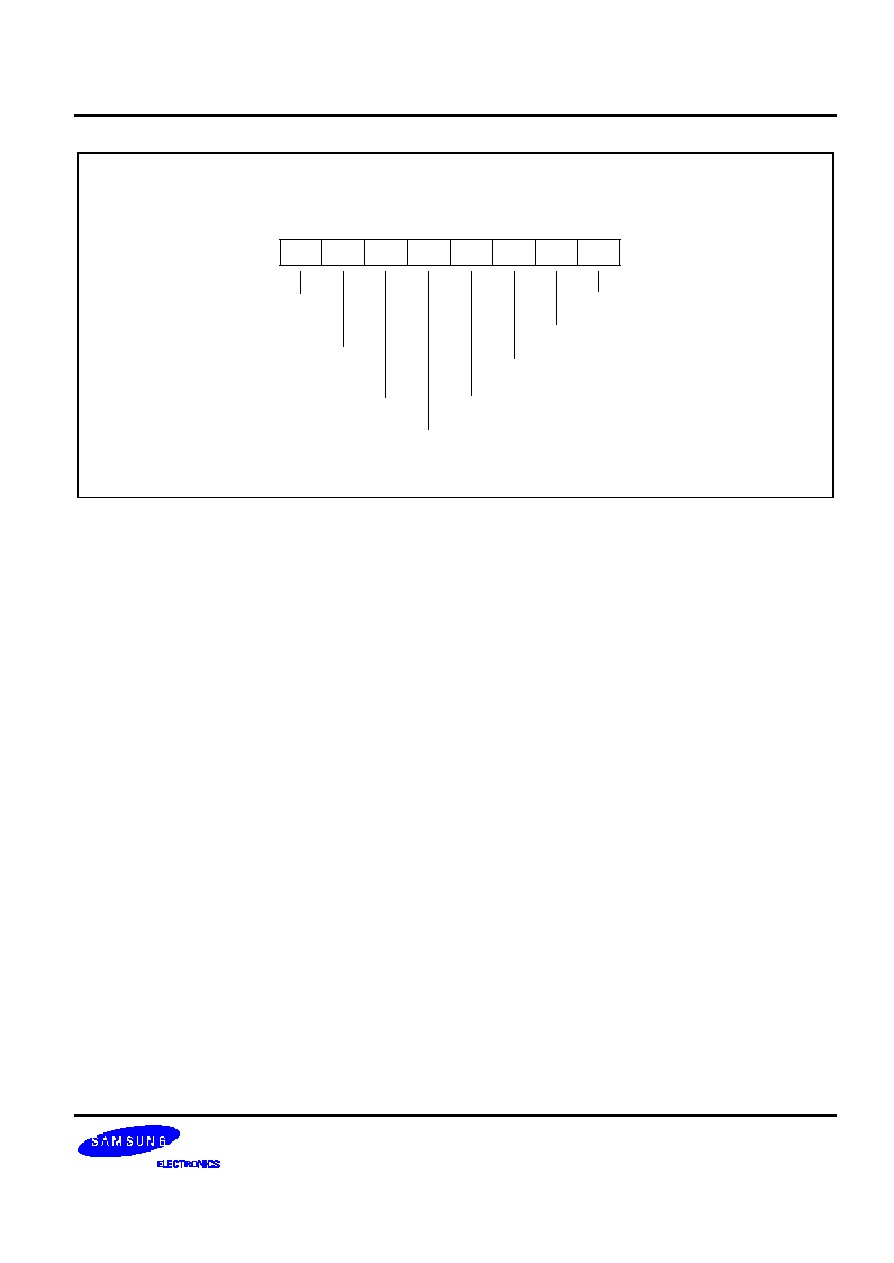

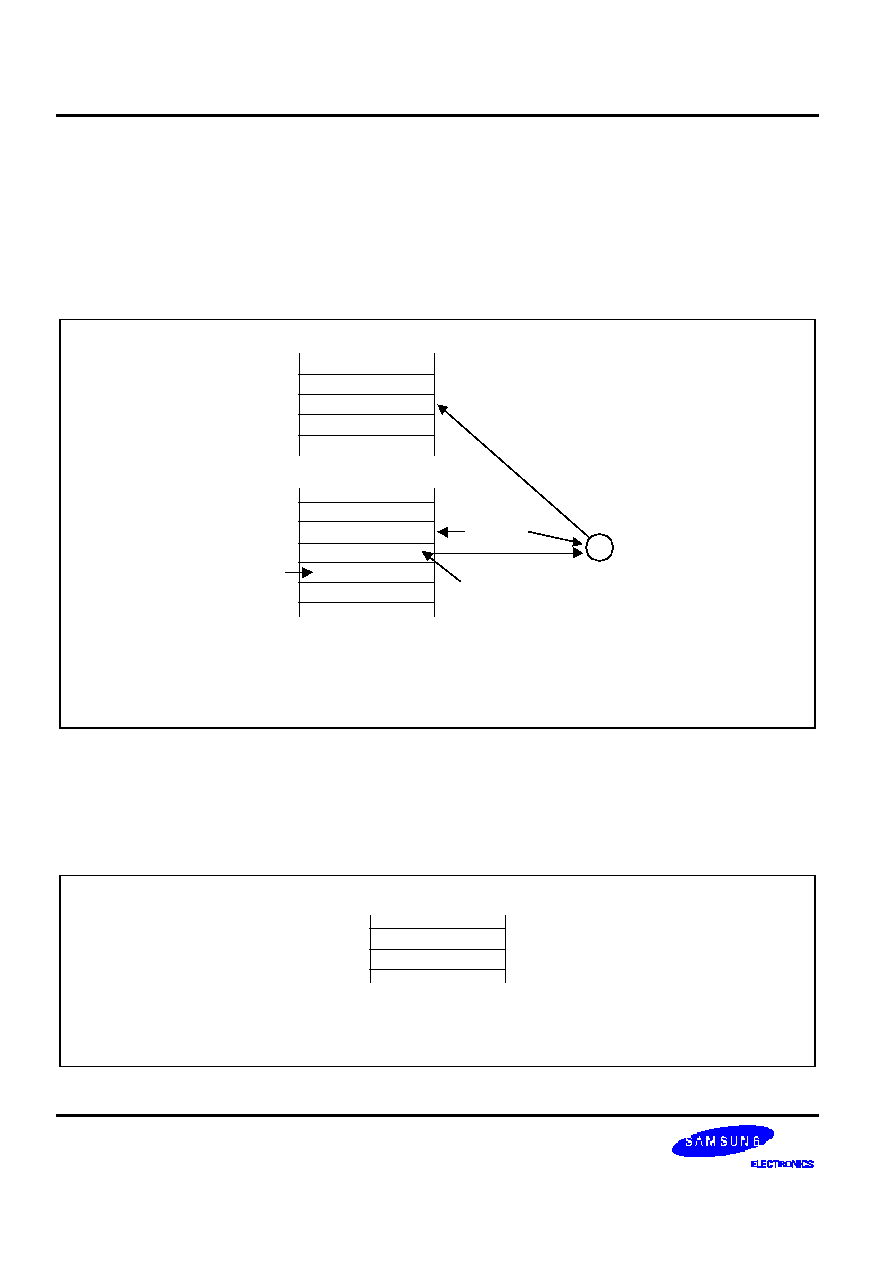

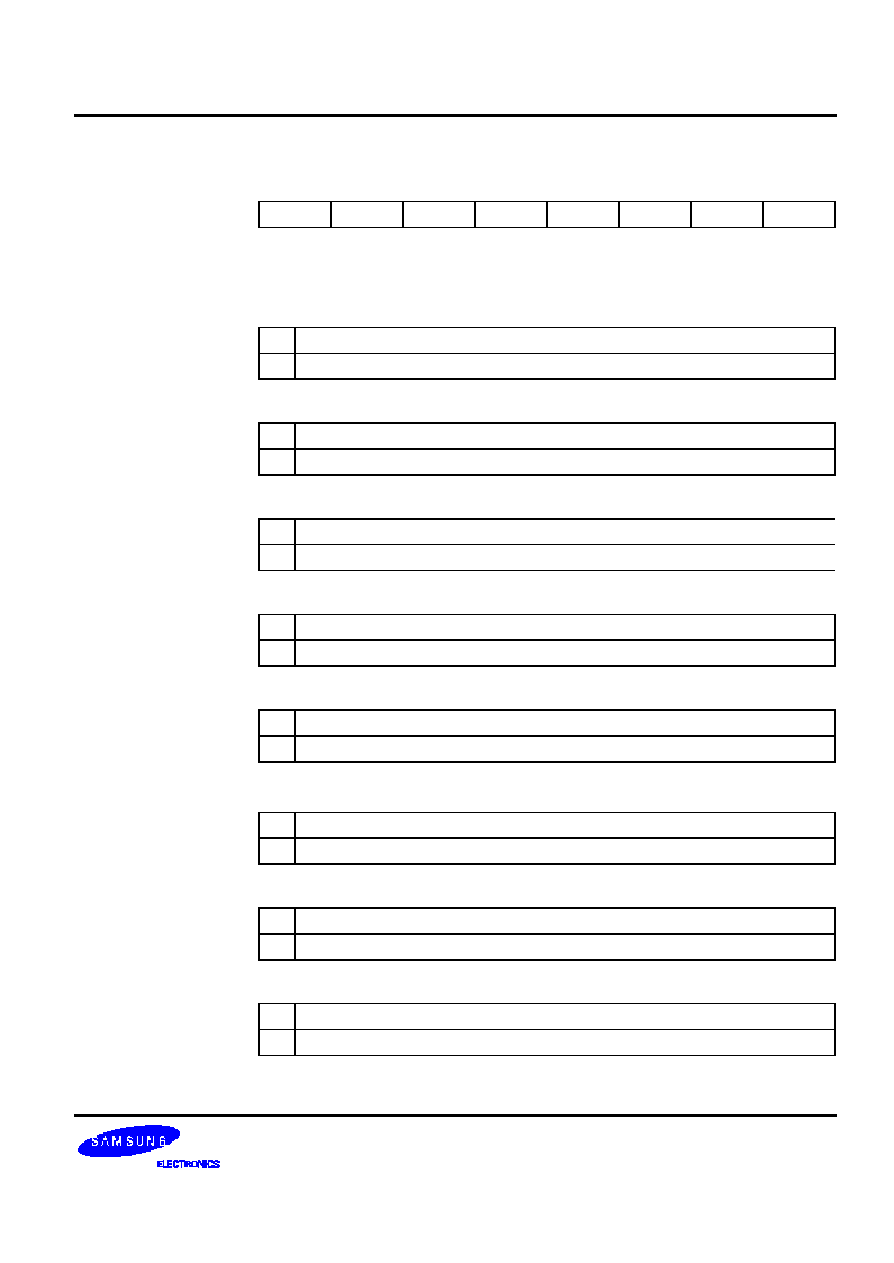

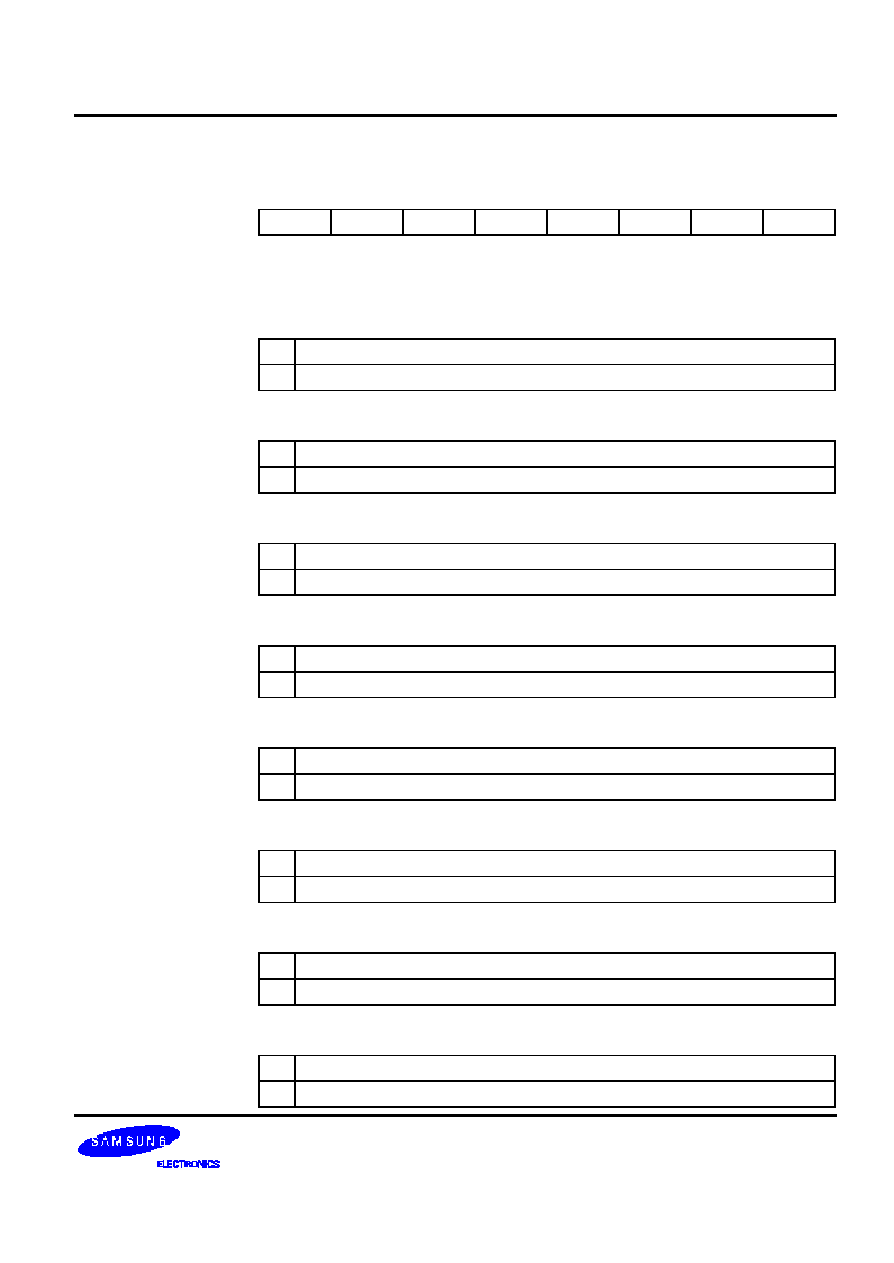

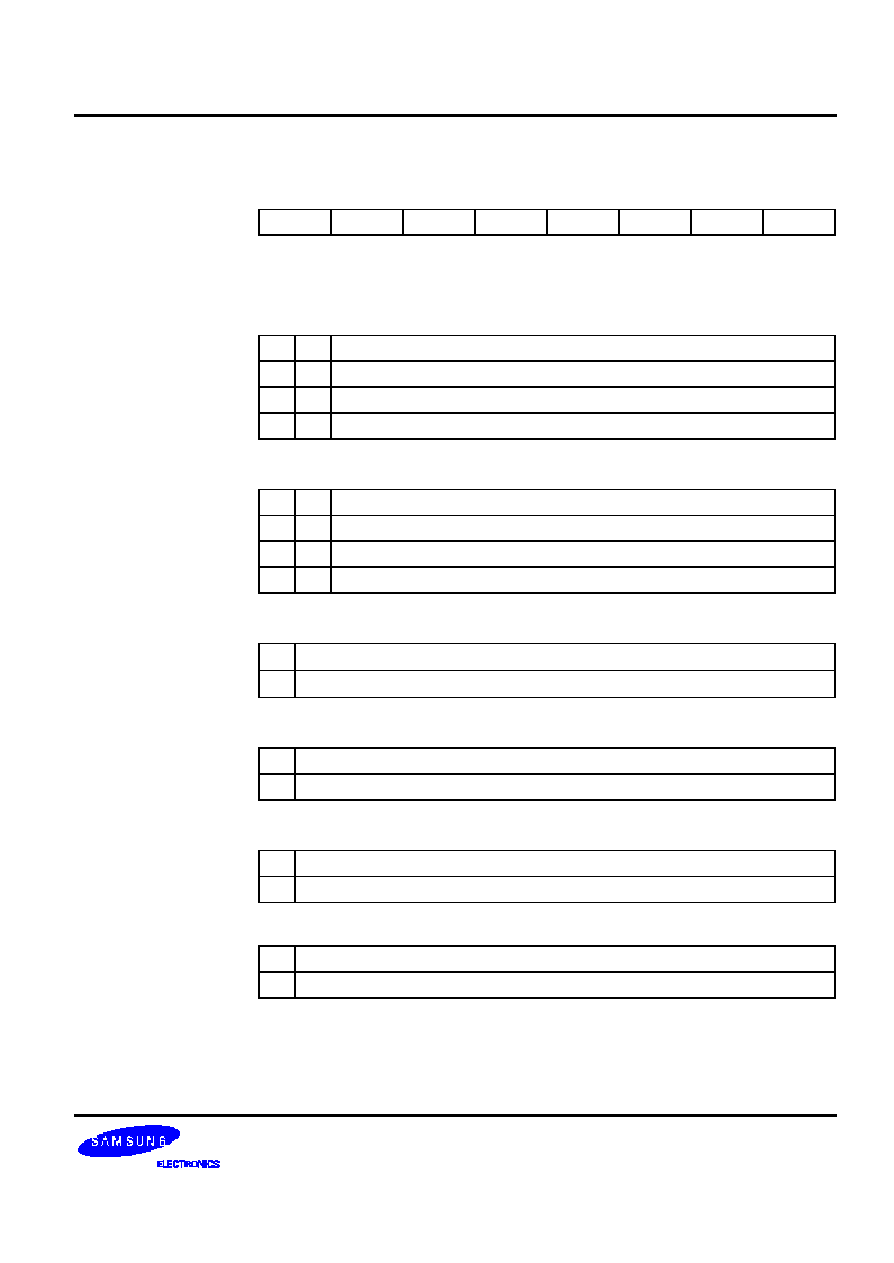

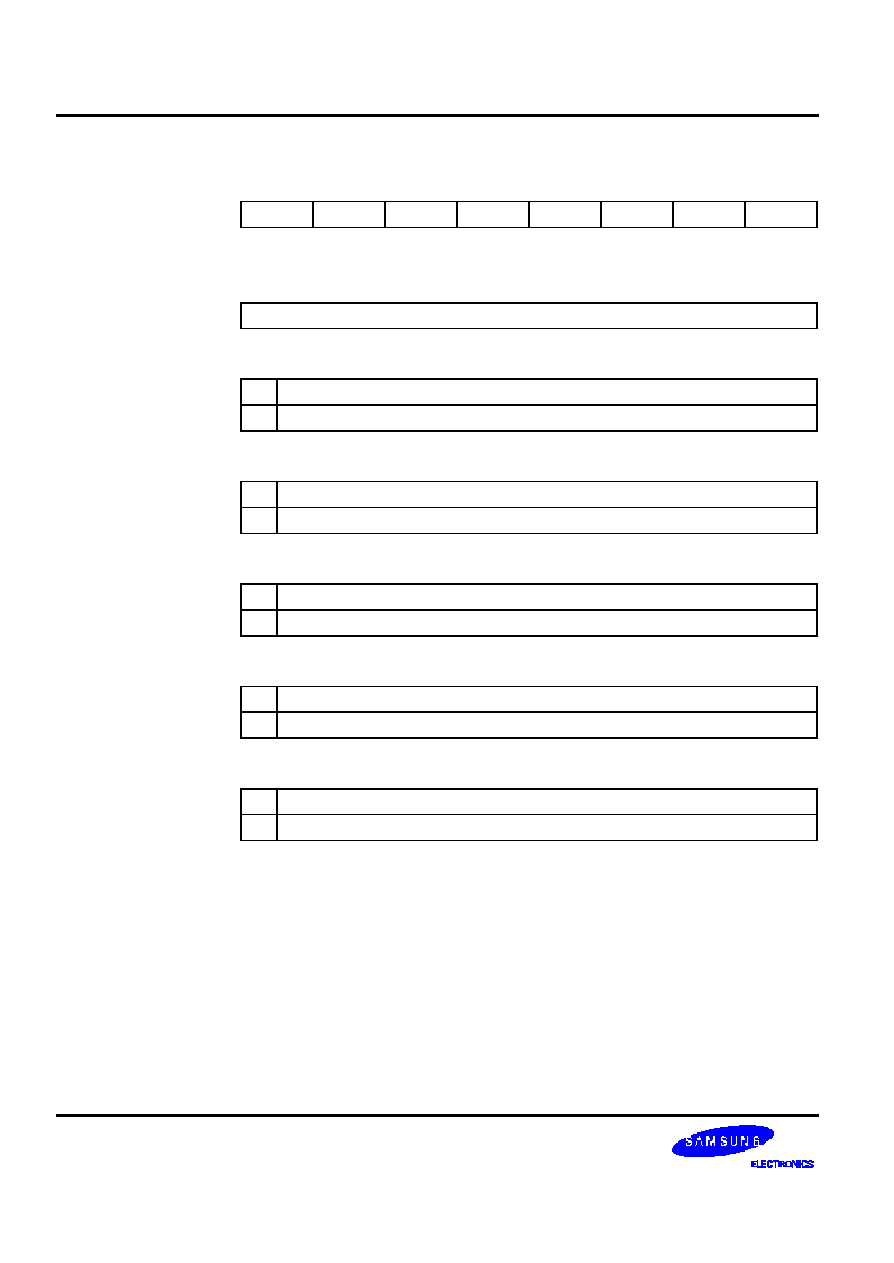

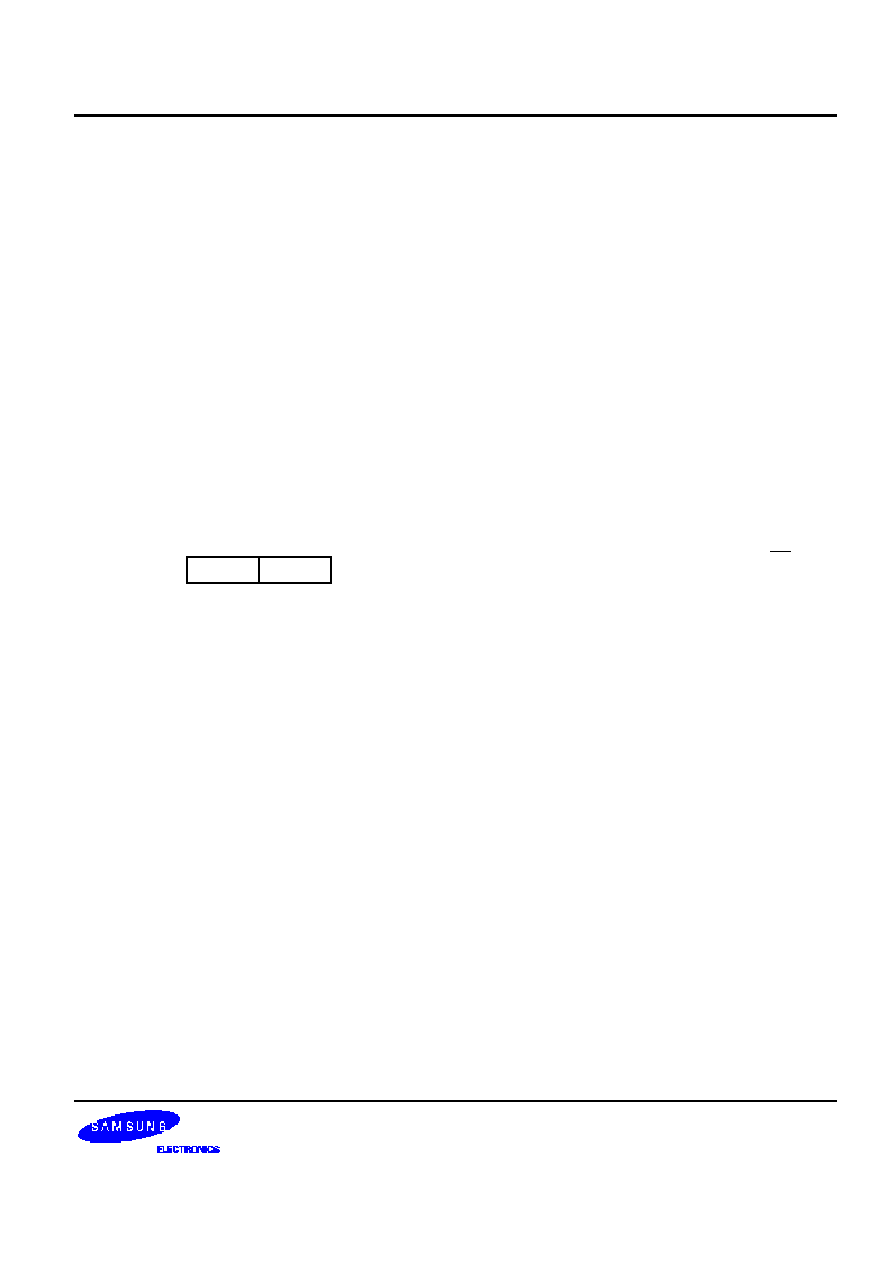

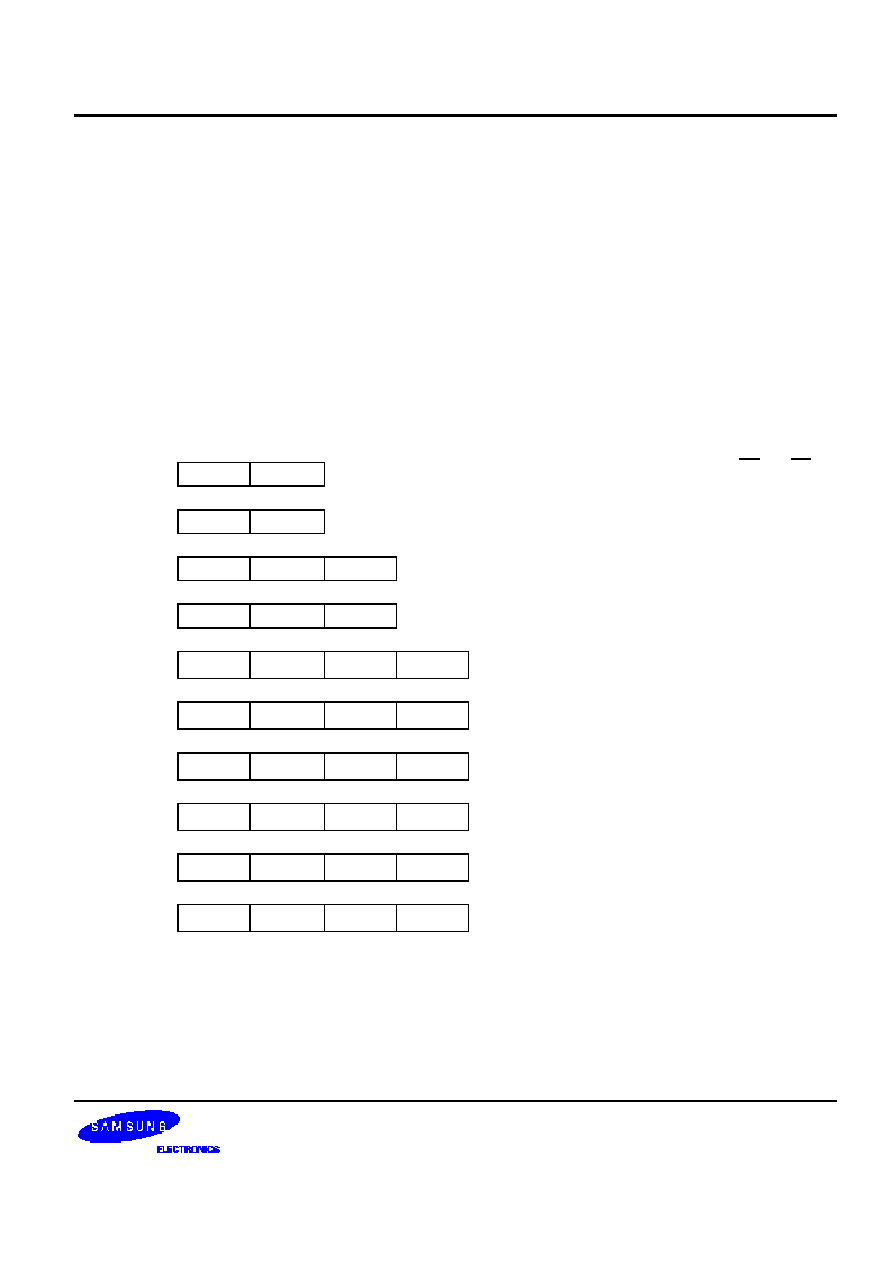

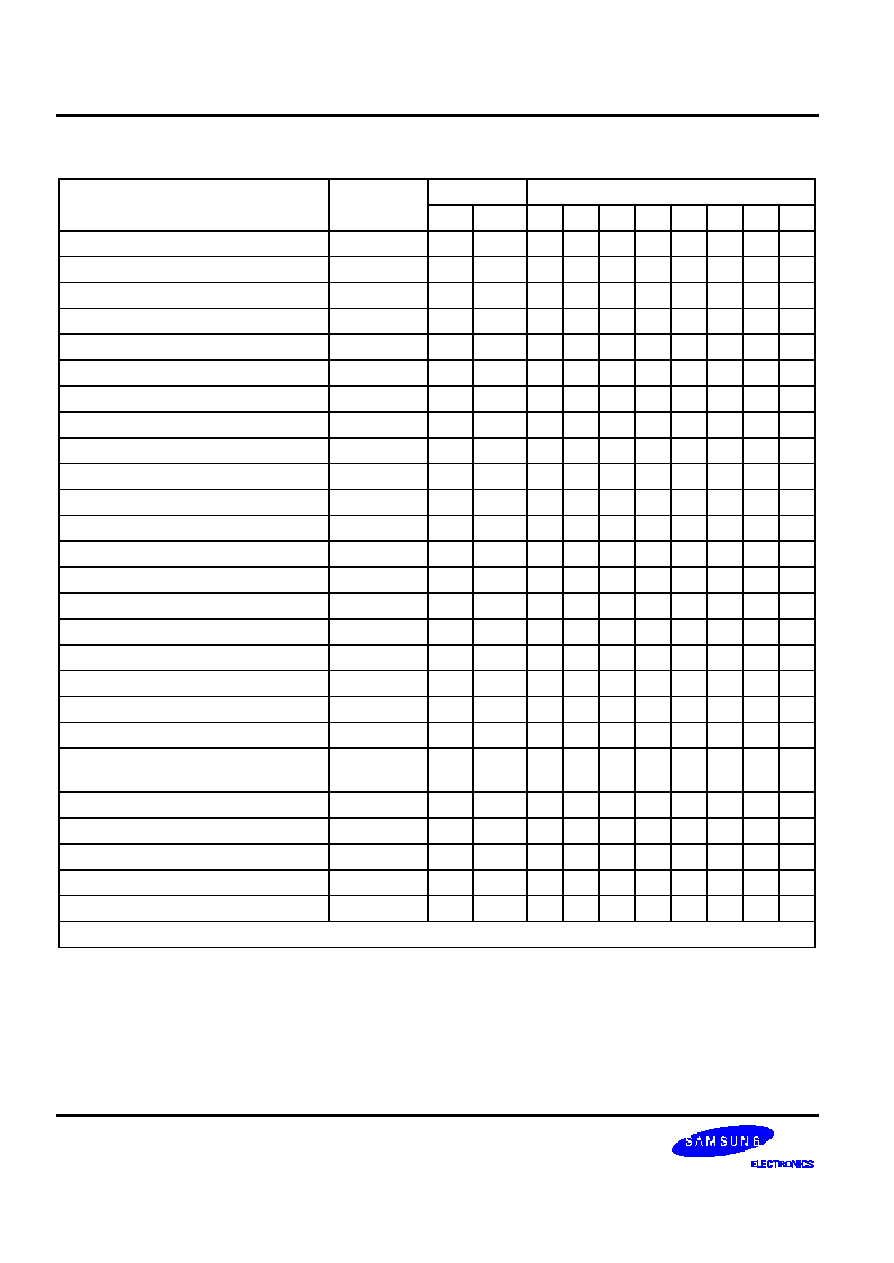

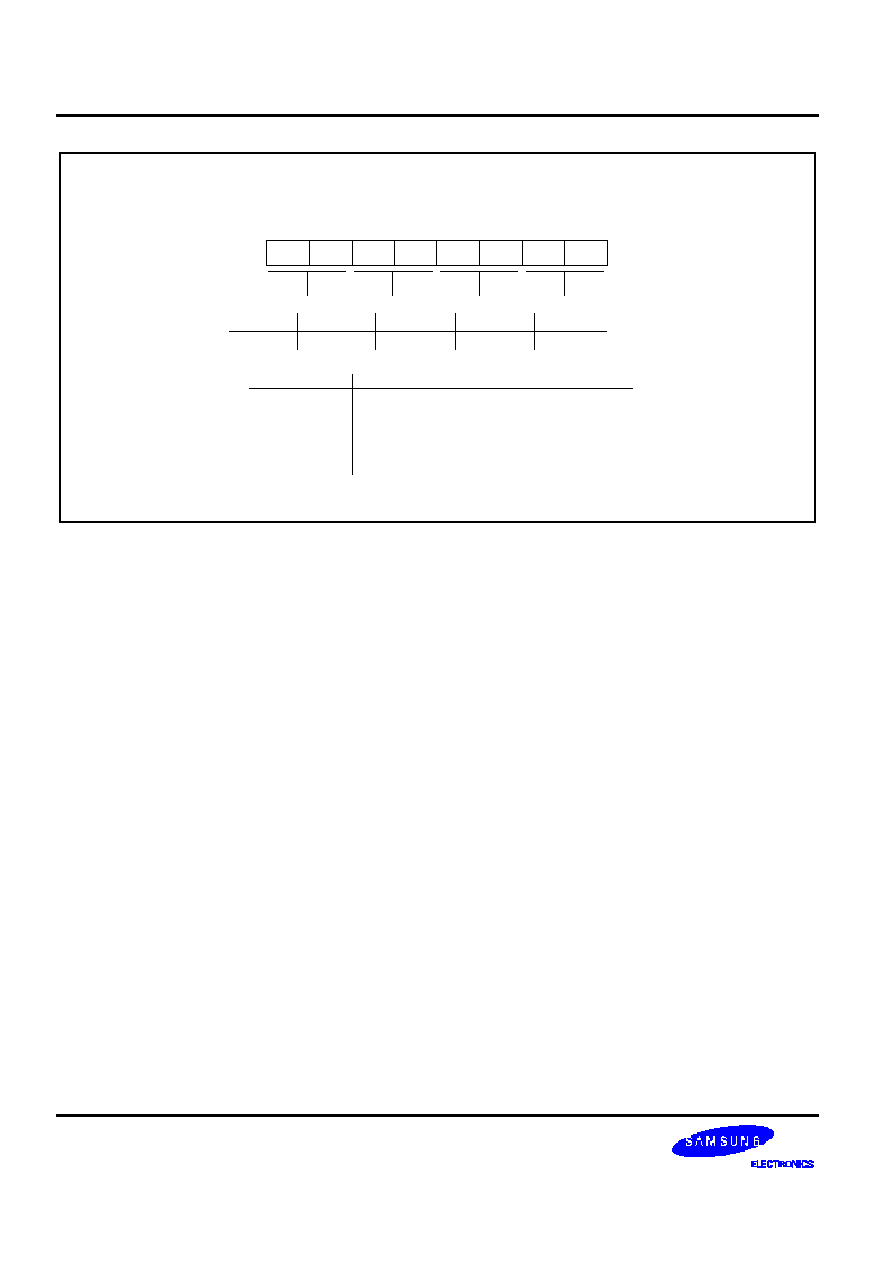

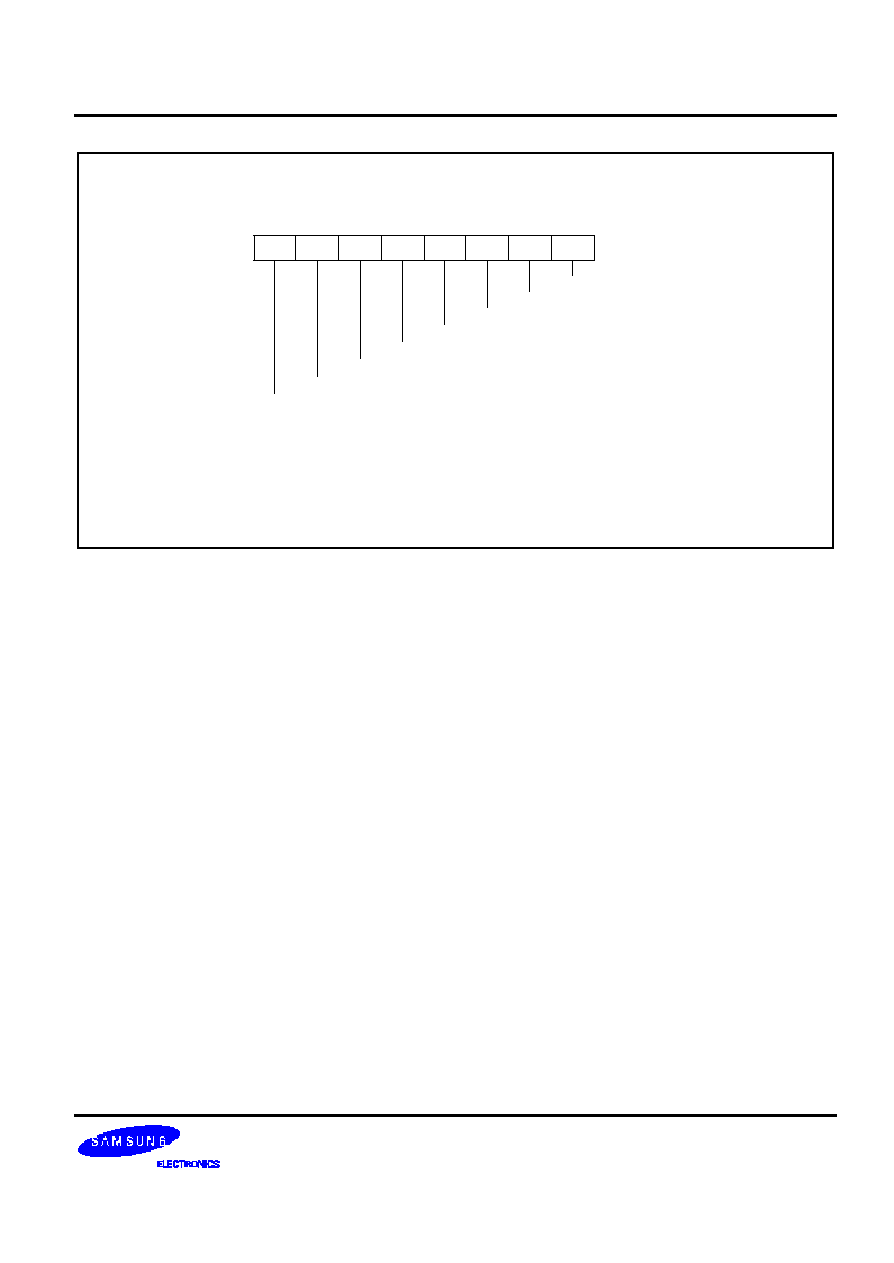

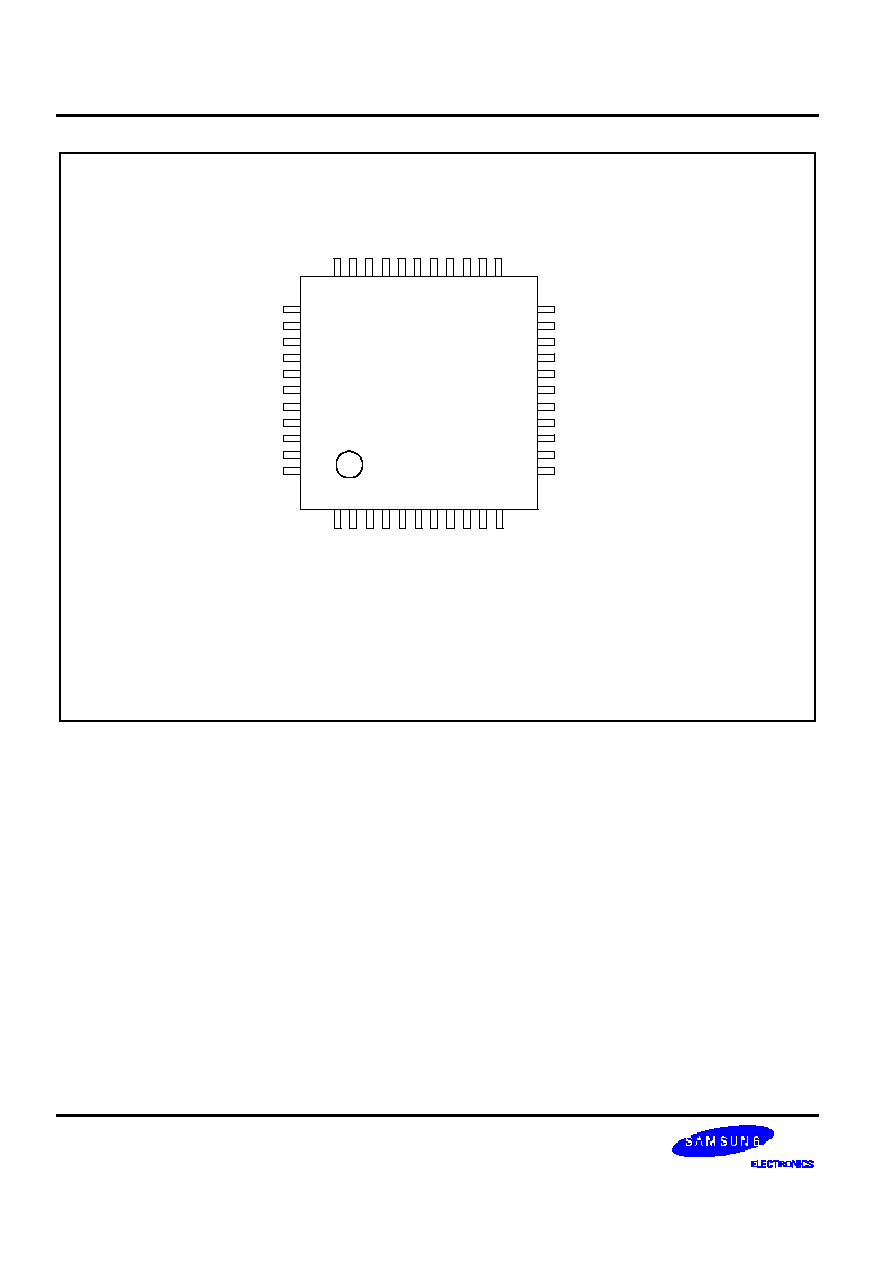

INT0/P2.4

INT0/P2.5

INT0/P2.6 INT0/P2.7

V

DD

V

SS

X

OUT

X

IN

TEST

INT1/P4.0 INT1/P4.1

P1.0

P1.1

P1.2

P1.3

P1.4

P1.5

P1.6

P1.7

P4.3/INT1

P4.2/INT1

RESET

NC NC

NC P0.0/INT2 P0.1/INT2

P0.2/INT2 P0.3/INT2

P0.4/INT2

P0.5/INT2 P0.6/INT2 P0.7/INT2

3.3V

OUT

D- /PS2

D+/PS2

CLO/P3.3

P3.2

P3.1

P3.0

P2.0/INT0

P2.1/INT0

P2.2/INT0

P2.3/INT0

S3C9688/P9688

44-QFP

(Top View)

NOTE:

The TEST pin must connect to V

SS

(GND) in the normal operation mode.

1 2

3 4 5

6 7

8 9 10

11

34

35

36

37

38

39

40

41

42

43

44

33 32

31 30

29 28 27

26 25 24

23

22

21

20

19

18

17

16

15

14

13

12

Figure 1-3. Pin Assignment Diagram (44-Pin QFP Package)

PRODUCT OVERVIEW

S3C9688/P9688

1-6

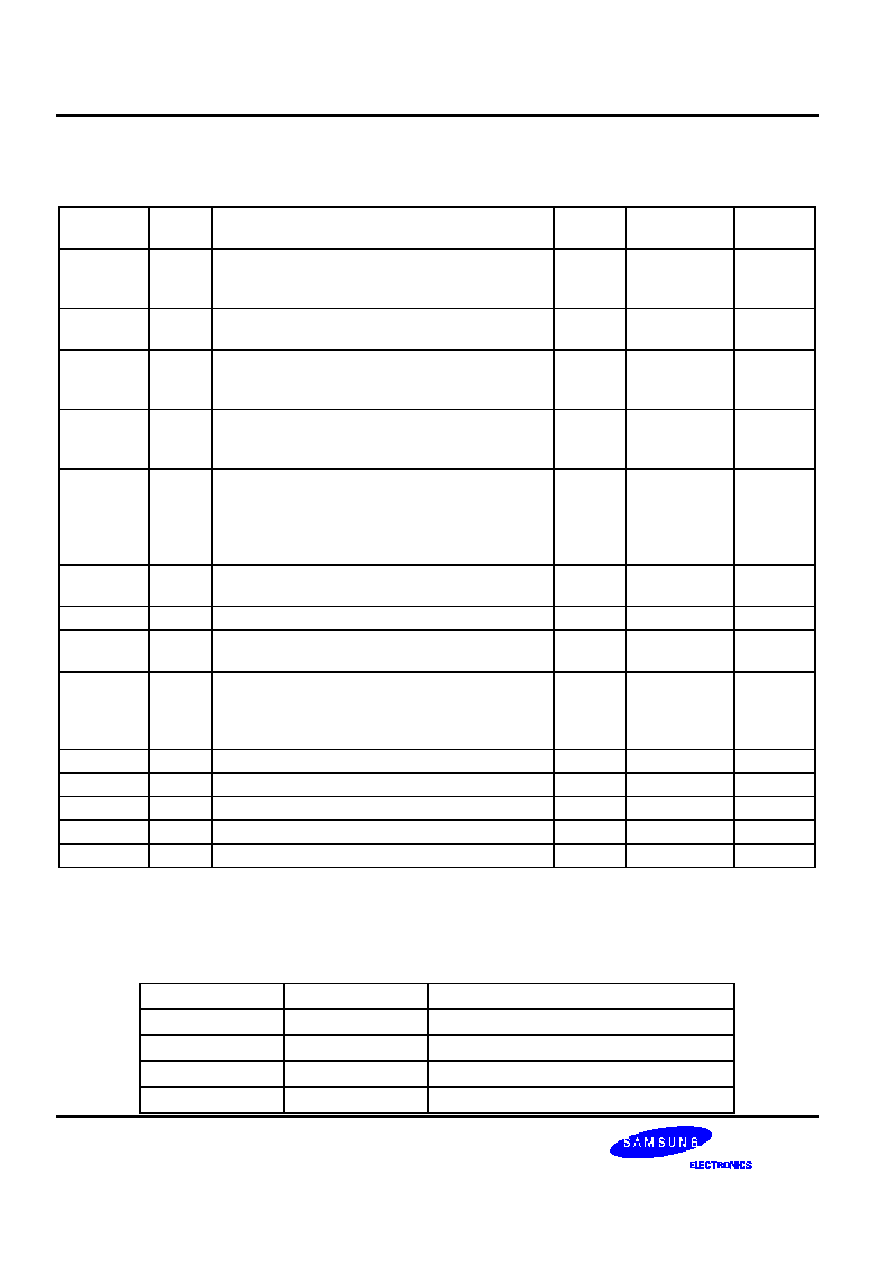

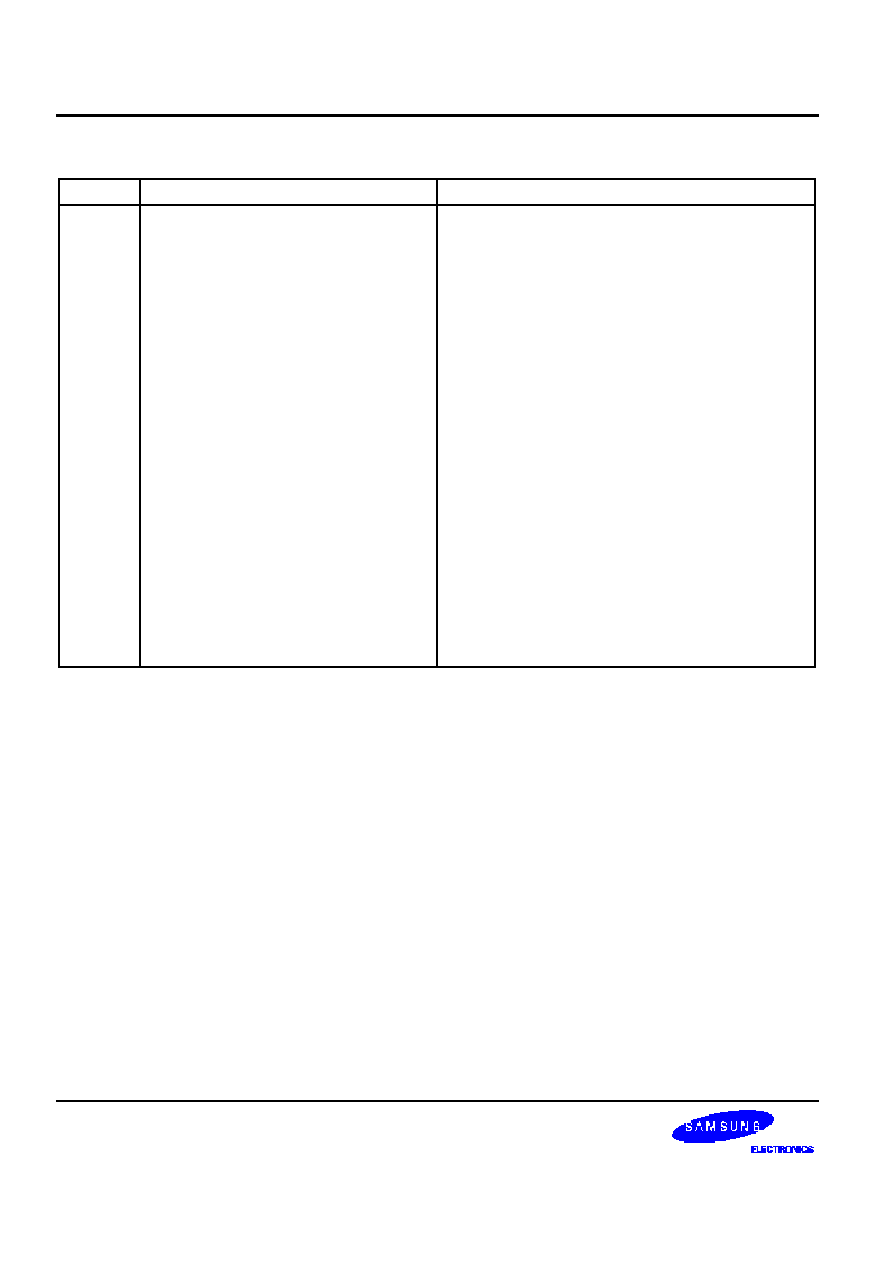

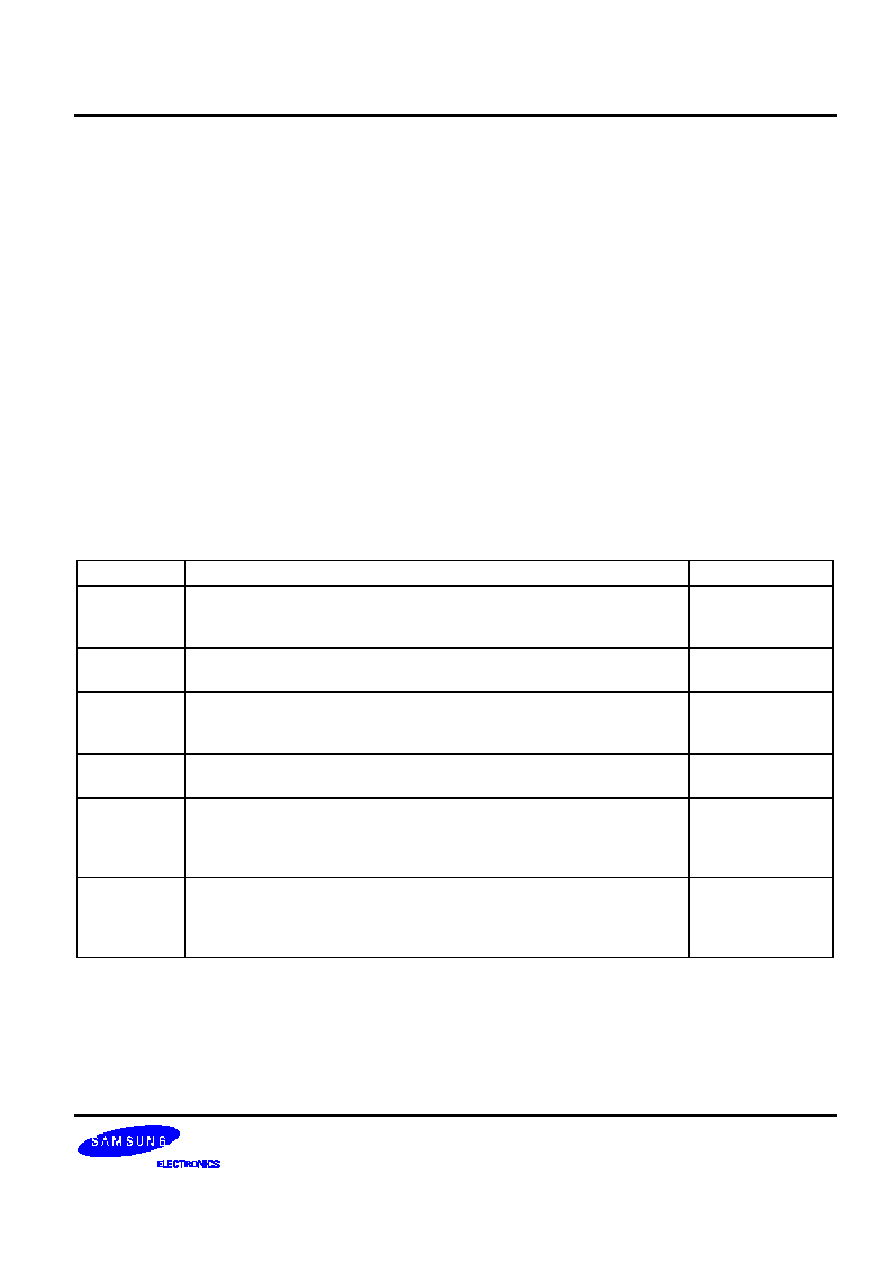

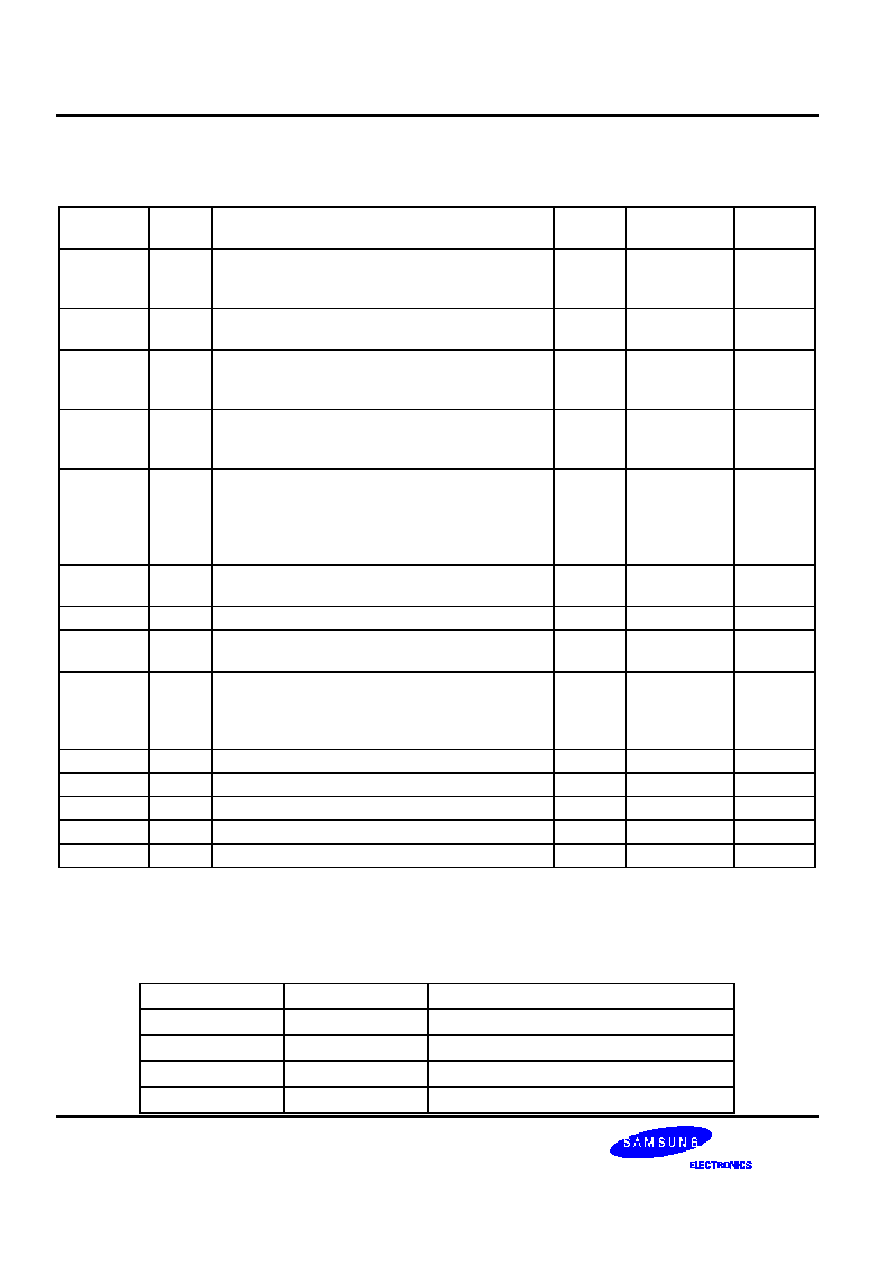

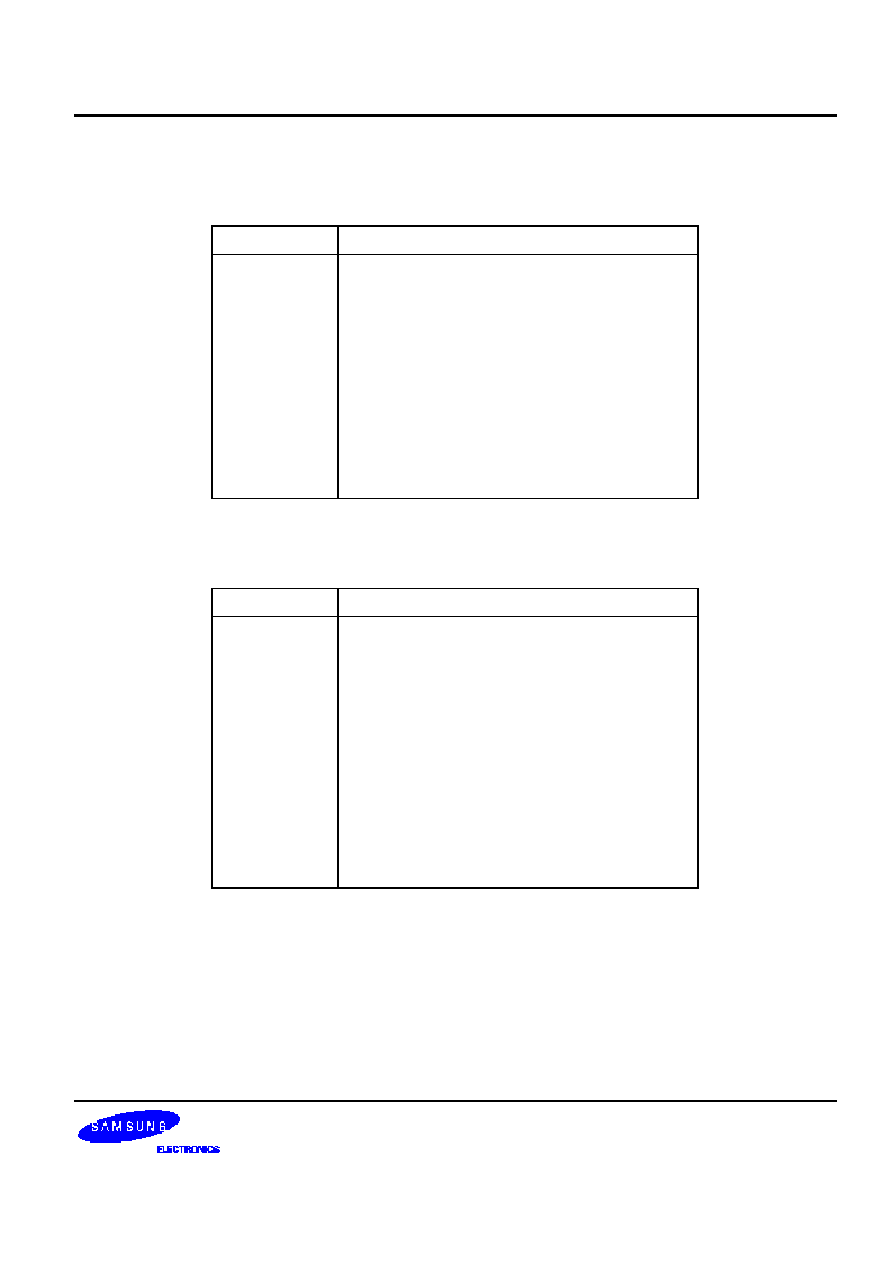

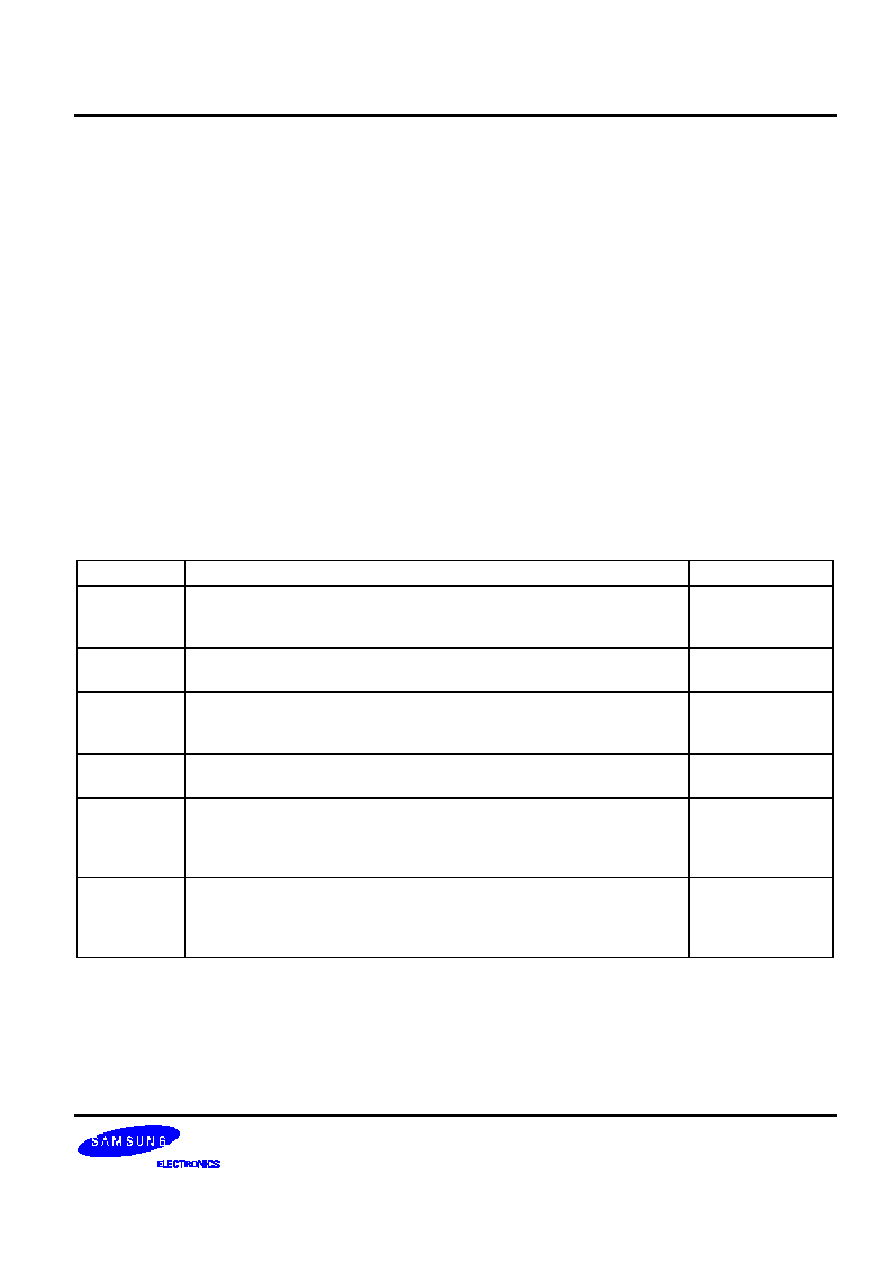

PIN DESCRIPTIONS

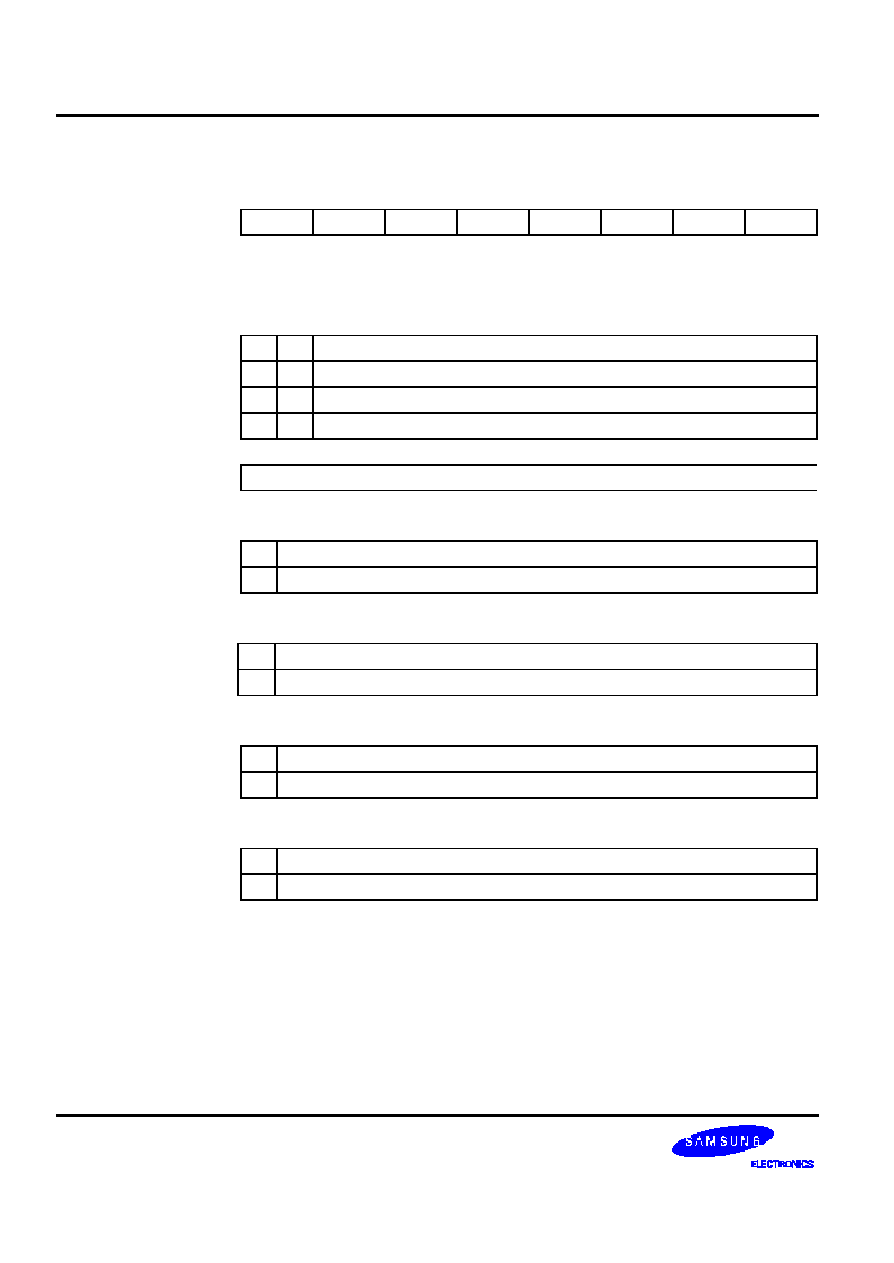

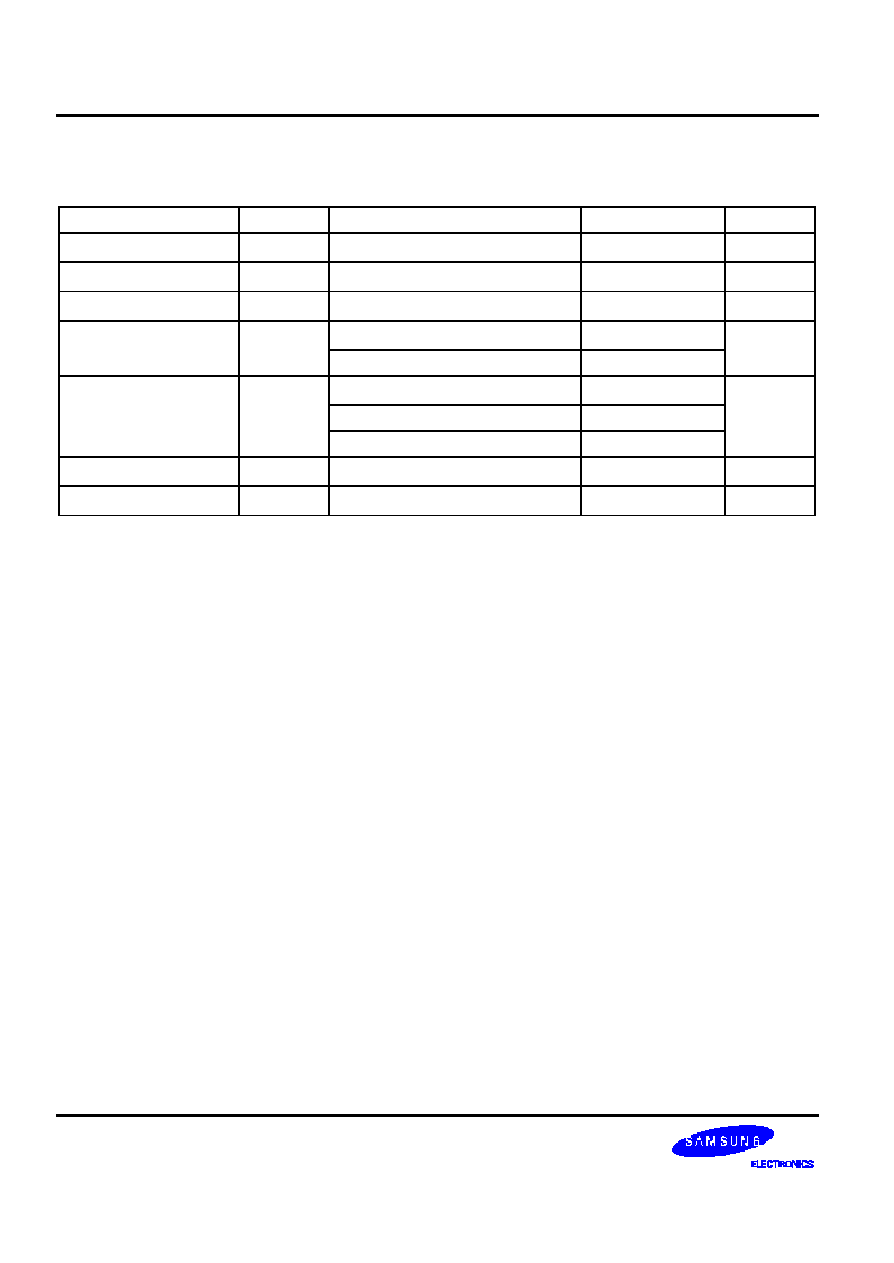

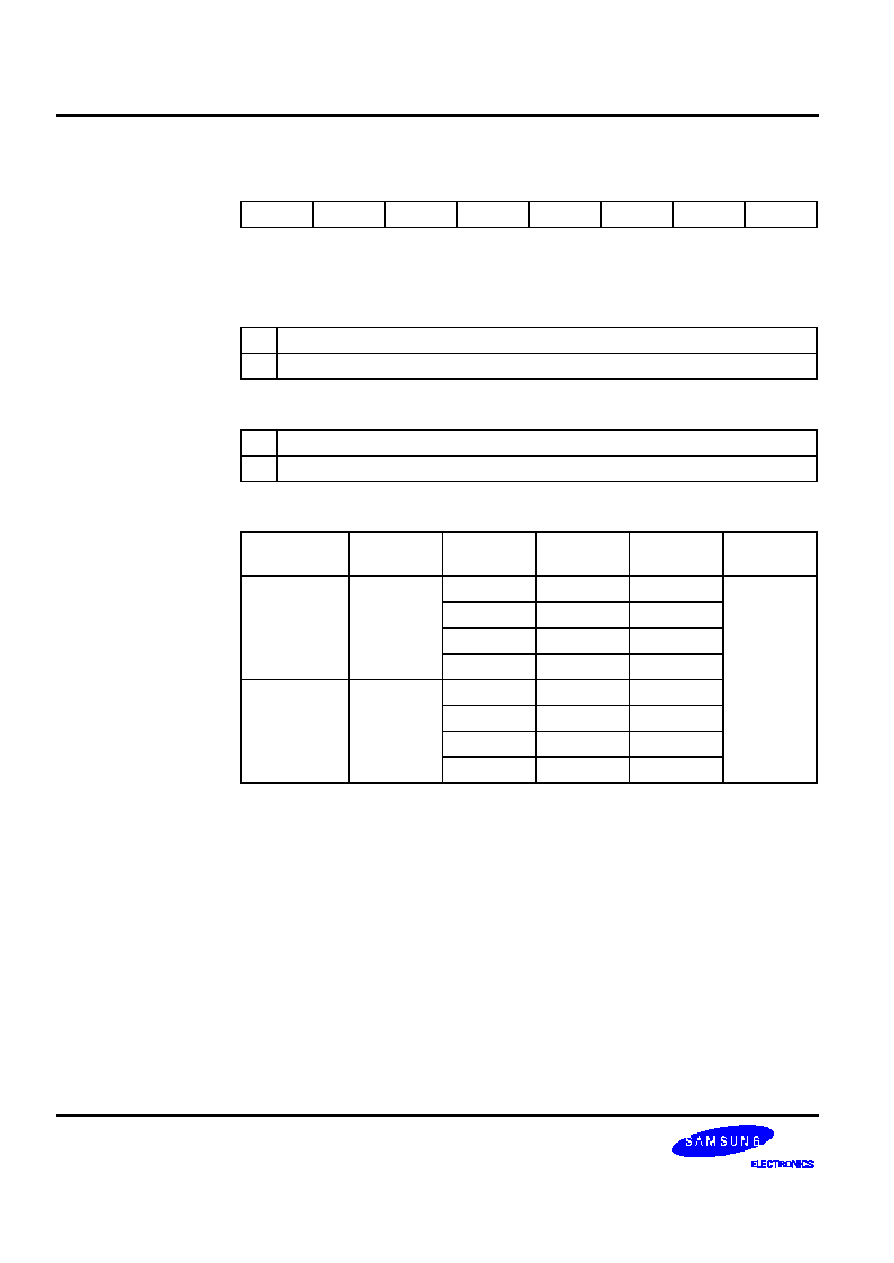

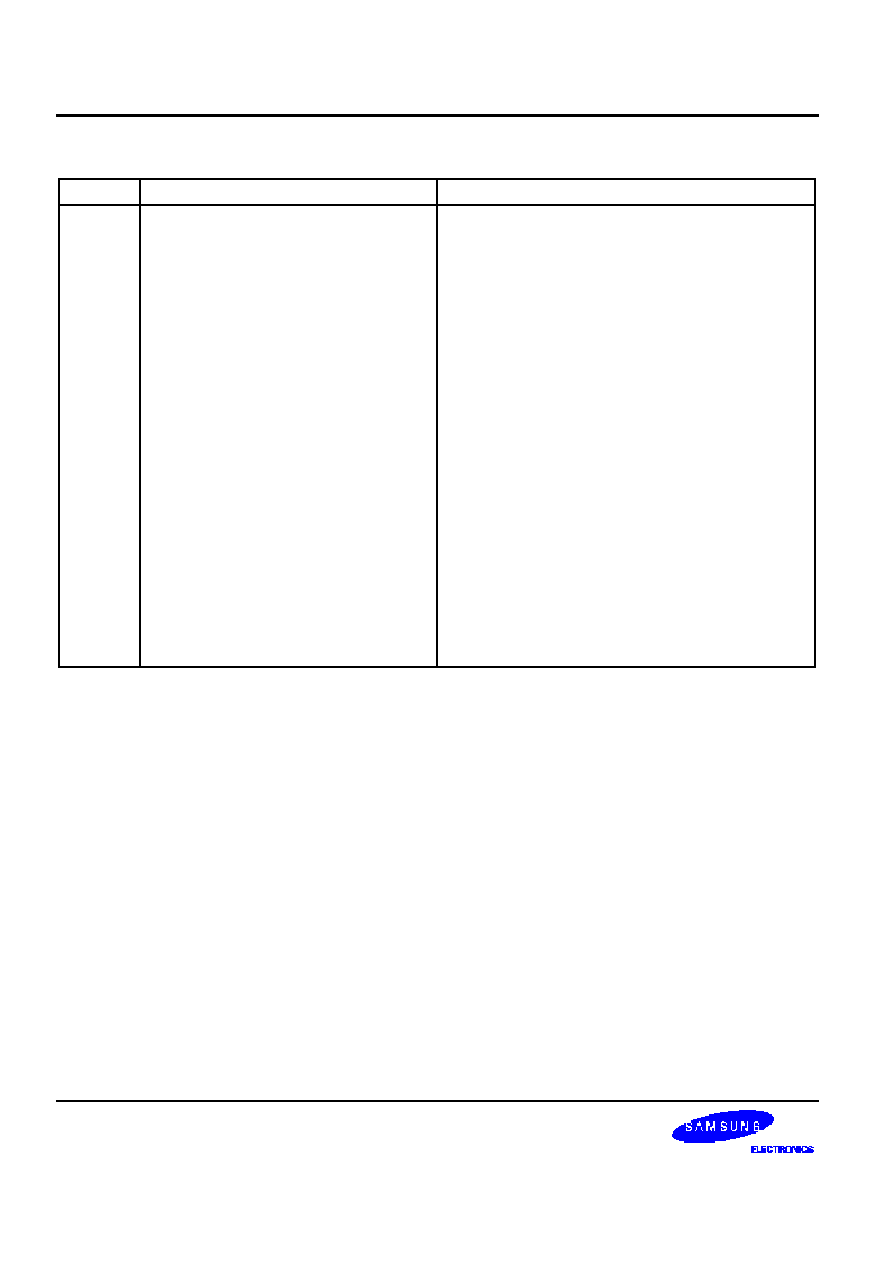

Table 1-1. S3C9688/P9688 Pin Descriptions

Pin Names

Pin

Type

Pin

Description

Circuit

Number

Pin

Numbers

Share

Pins

P0.0≠P0.7

I/O

Bit-programmable I/O port for Schmitt trigger input or open-

drain output. Port0 can be individually configured as external

interrupt inputs. Pull-up resistors are assignable by software.

B

36≠29

(30≠23)

INT2

P1.0≠P1.7

I/O

Bit-programmable I/O port for Schmitt trigger input or open-

drain output. Pull-up resistors are assignable by software.

B

28≠21

(22≠15)

≠

P2.0≠P2.7

I/O

Bit-programmable I/O port for Schmitt trigger input or open-

drain output. Port2 can be individually configured as external

interrupt inputs. Pull-up resistors are assignable by software.

B

3≠10

(41≠44, 1≠4)

INT0

P3.0≠P3.3

I/O

Bit-programmable I/O port for Schmitt trigger input, open-

drain or push-pull output. P3.3 can be used to system clock

output (CLO) pin.

C

2, 1, 42, 41

(40≠37)

P3.3/CLO

P4.0≠P4.3

I/O

Bit-programmable I/O port for Schmitt trigger input or open-

drain output or push-pull output. Port4 can be individually

configured as external interrupt inputs. In output mode, pull-

up resistors are assignable by software. But in input mode,

pull-up resistors are fixed.

D

16, 17, 19, 20

(10, 11, 13, 14)

INT1

D+/PS2 D-

/PS2

I/O

Programmable port for USB interface

or PS2 interface.

≠

40≠39

(36≠35)

≠

3.3 V

OUT

≠

3.3 V output from internal voltage regulator

≠

38 (34)

≠

X

IN

, X

OUT

≠

System clock input and output pin (crystal/ceramic oscillator,

or external clock source)

≠

14, 13

(8, 7)

≠

INT0

INT1

INT2

I

External interrupt for bit-programmable port0, port2 and port4

pins when set to input mode.

≠

3-10, 16,17, 19,

20, 29-36

(30-23, 41-44, 1-

4, 10, 11, 13, 14)

PORT2/

PORT4/

PORT0

RESET

I

RESET signal input pin. Input with internal pull-up resistor.

A

18 (12)

≠

TEST

I

Test signal input pin (for factory use only; connected to V

SS

)

≠

15 (9)

≠

V

DD

≠

Power input pin

≠

11 (5)

≠

V

SS

≠

Ground input pin

≠

12, (6)

≠

NC

≠

No connection

≠

37 (31,32, 33)

≠

NOTE

:

Pin numbers shown in parenthesis '( )' are for the 44-QFP package; others are for the 42-SDIP package.

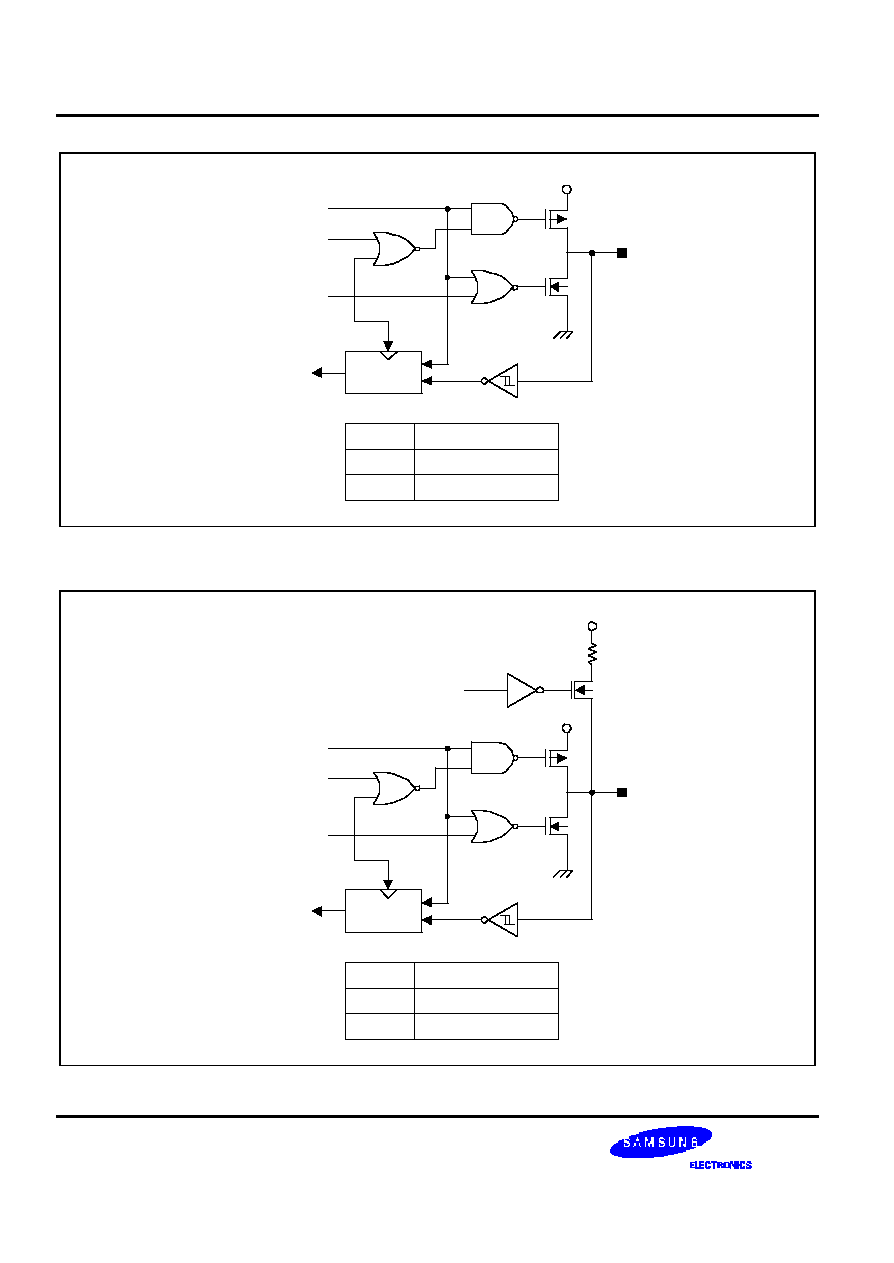

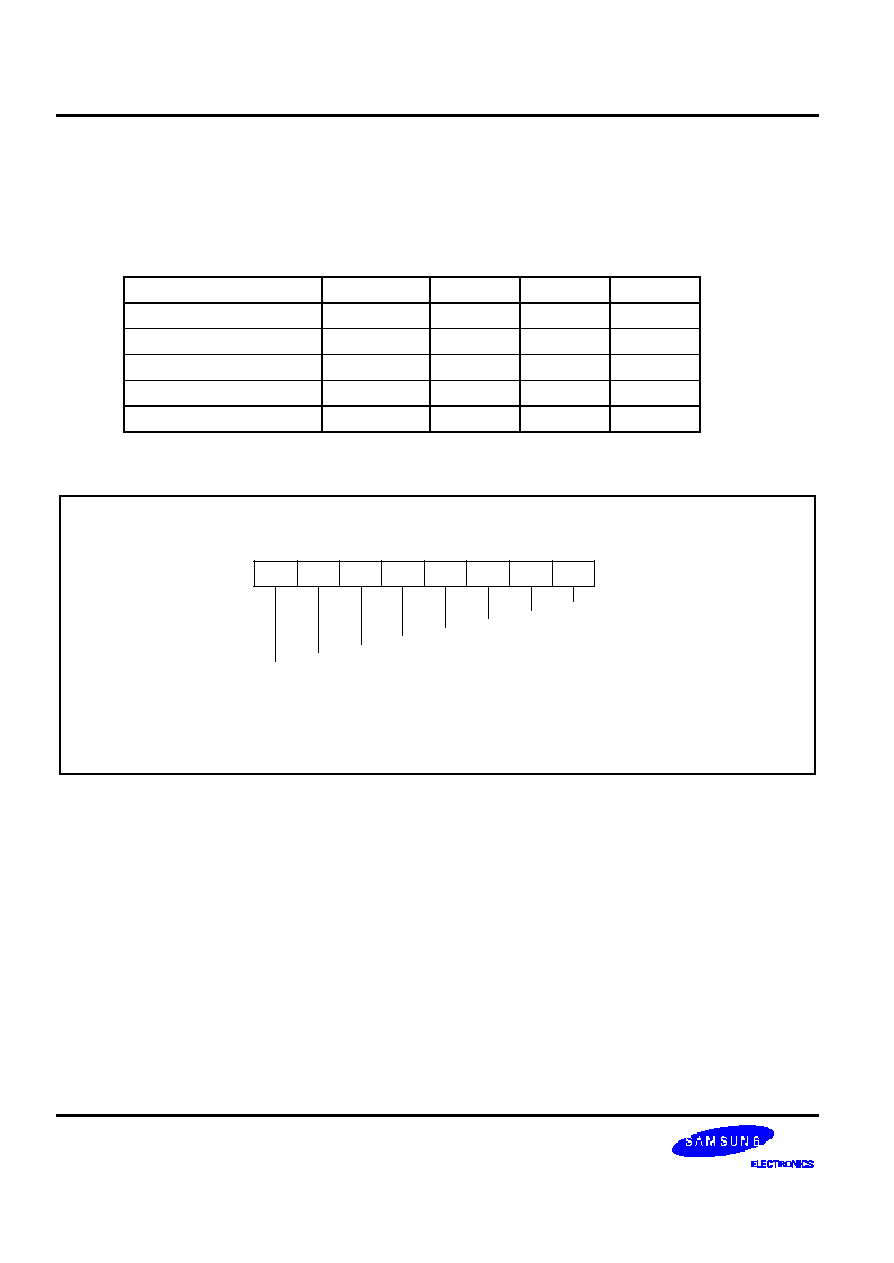

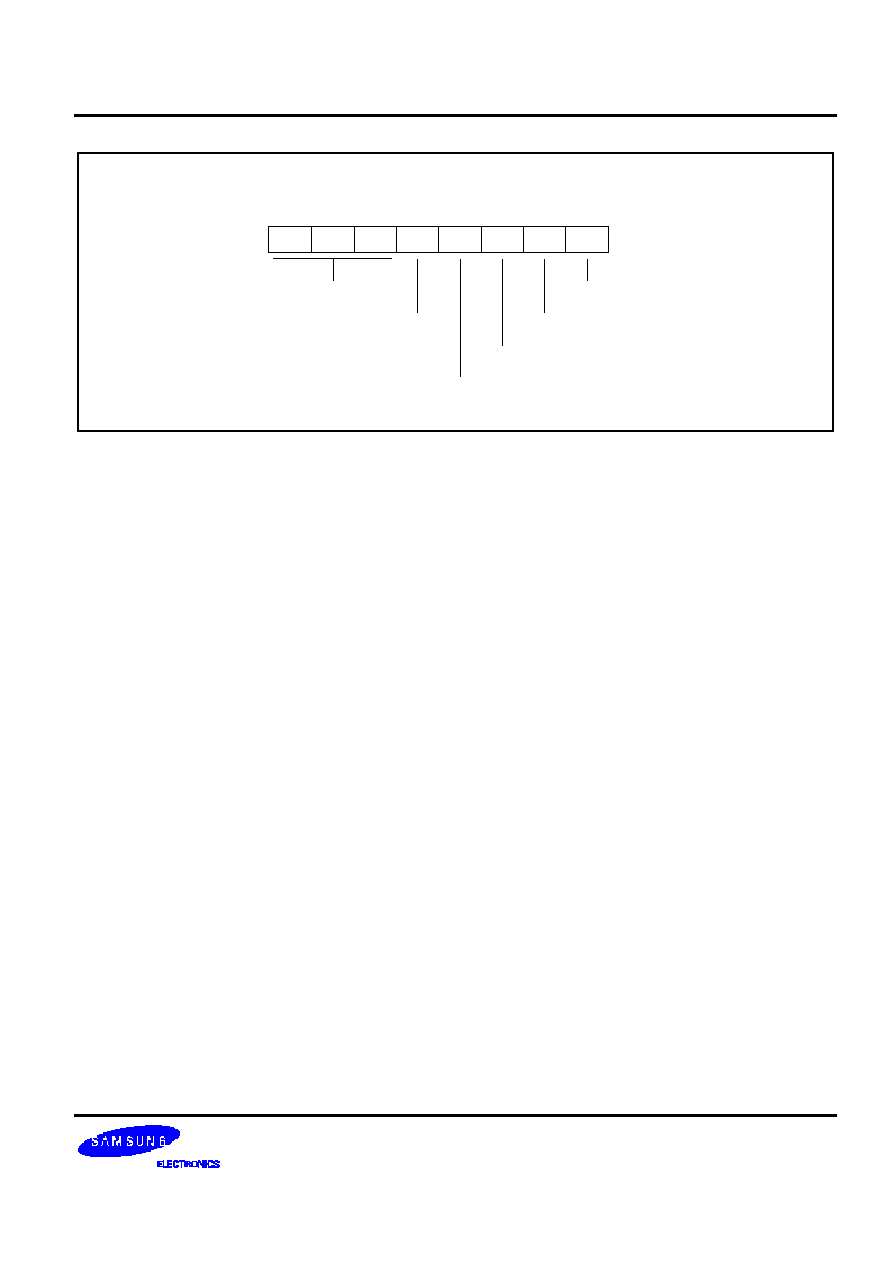

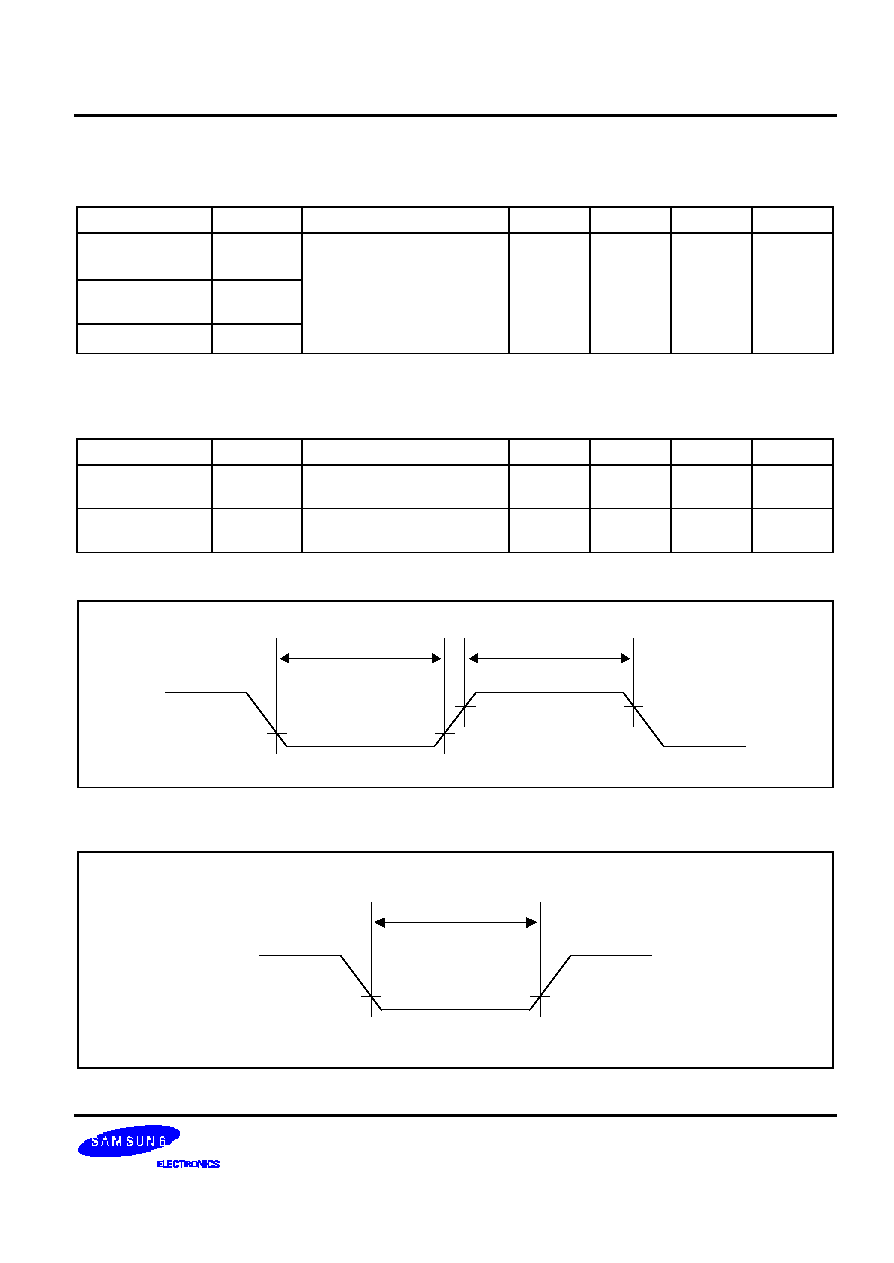

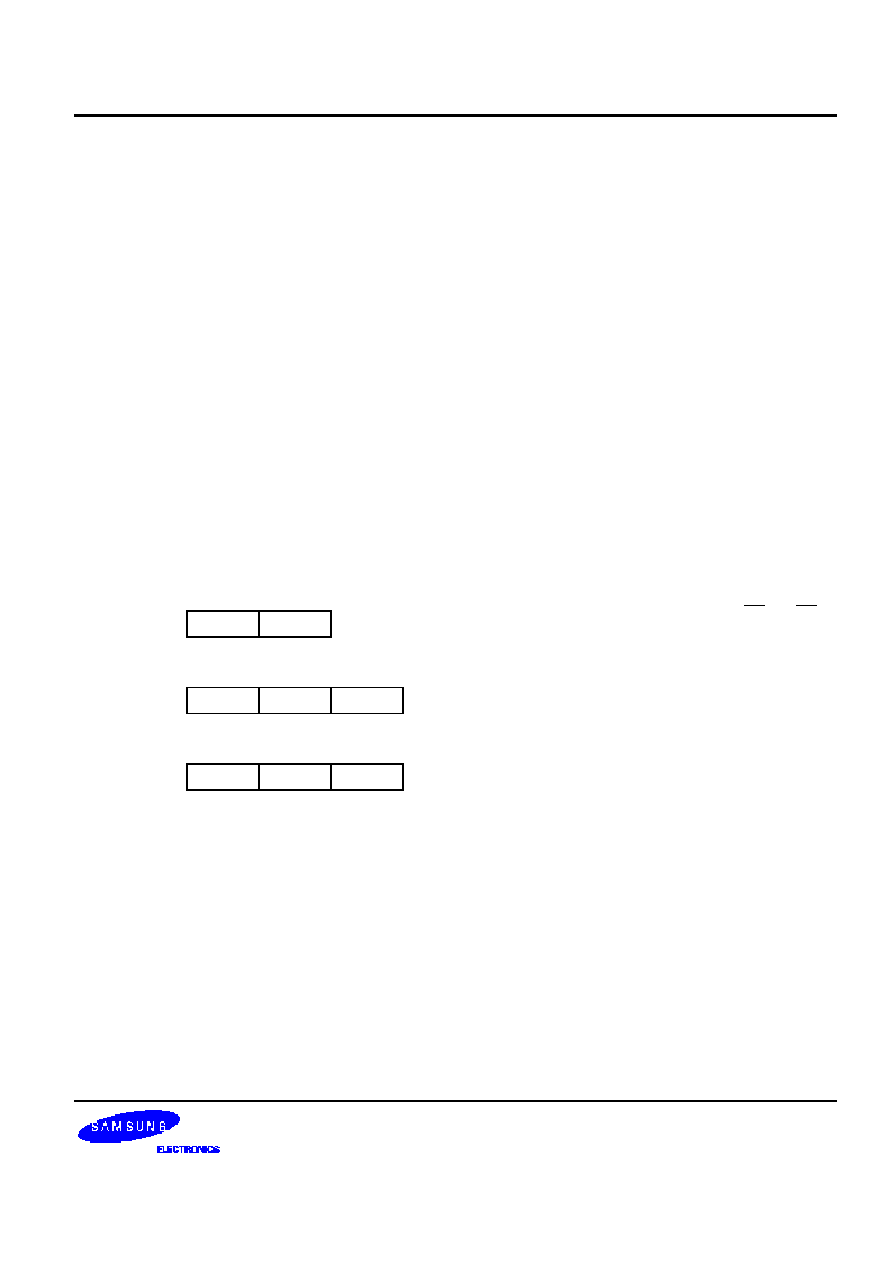

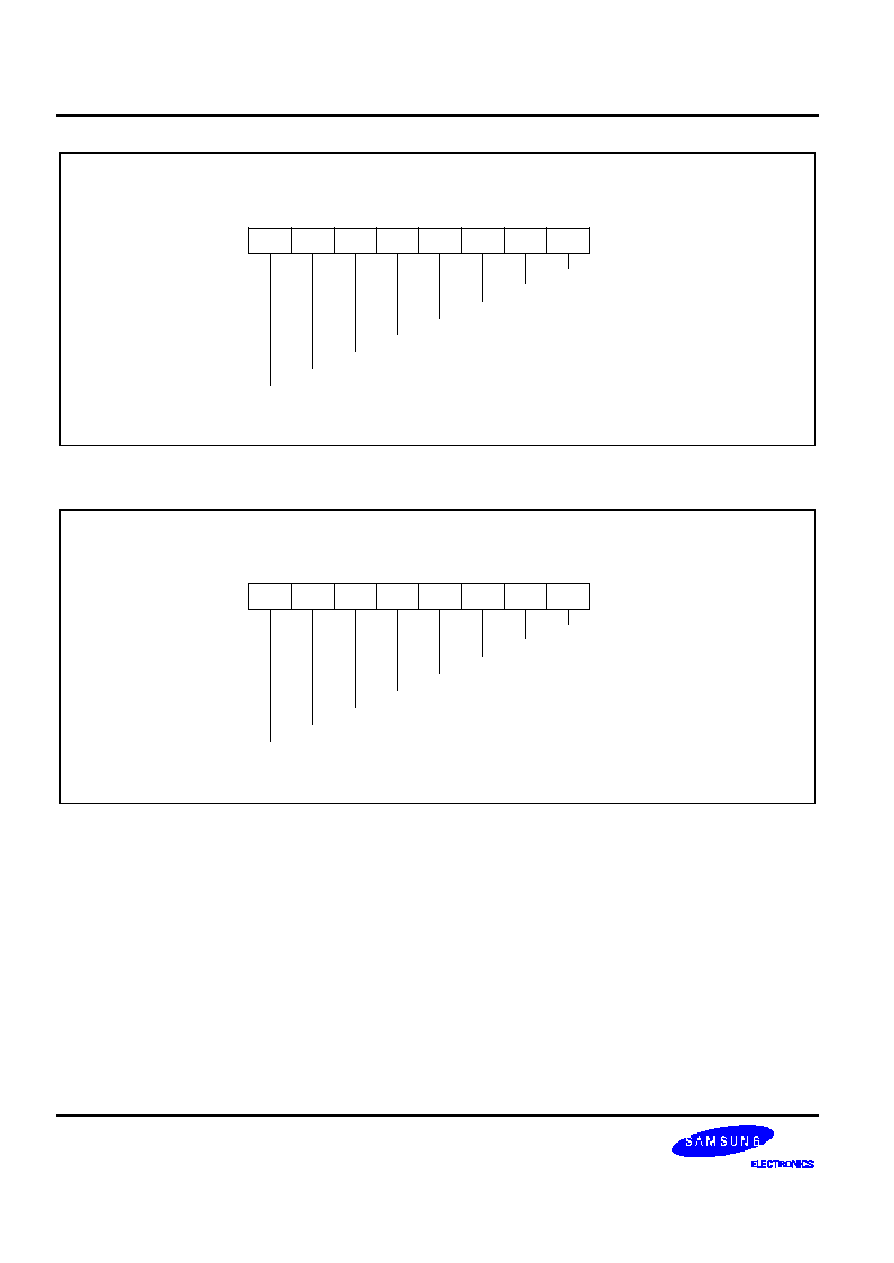

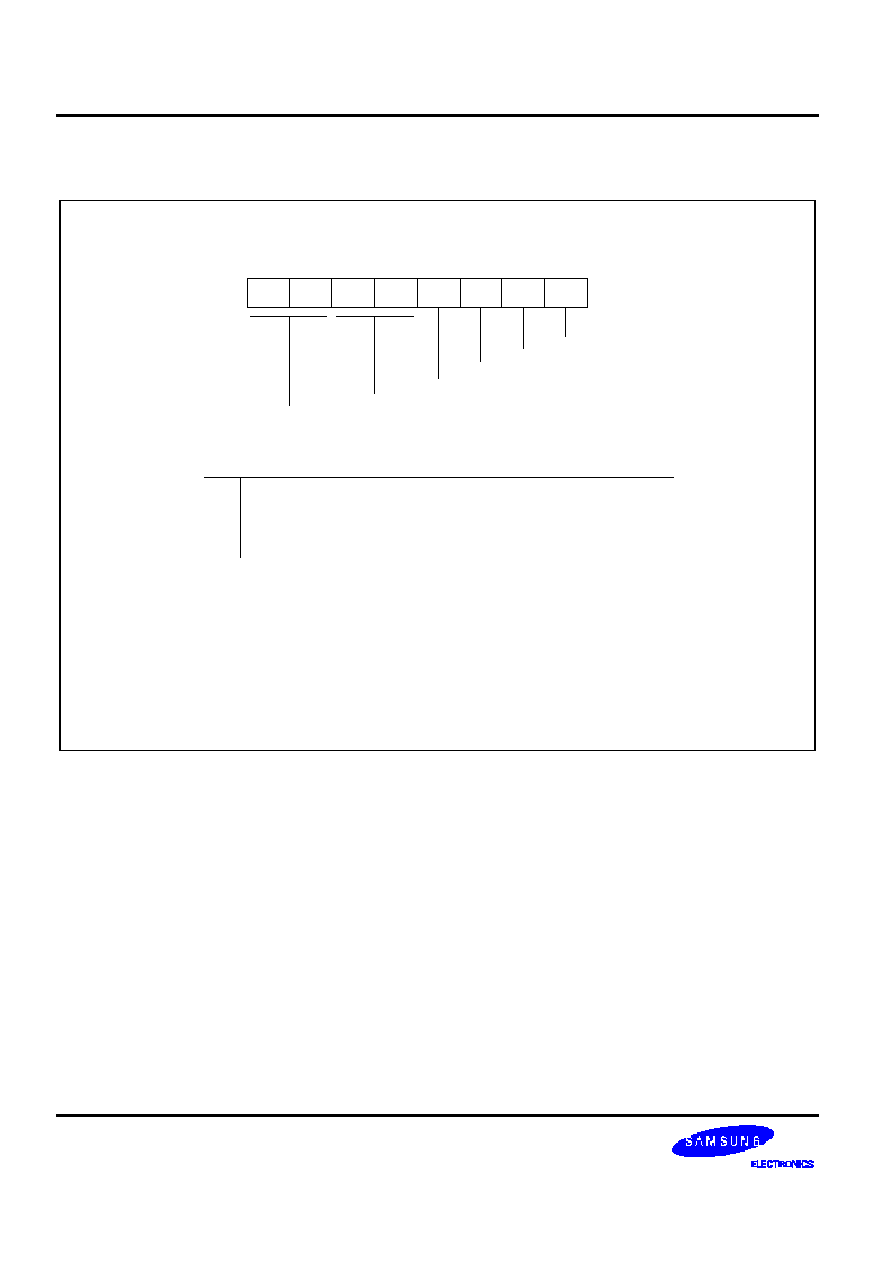

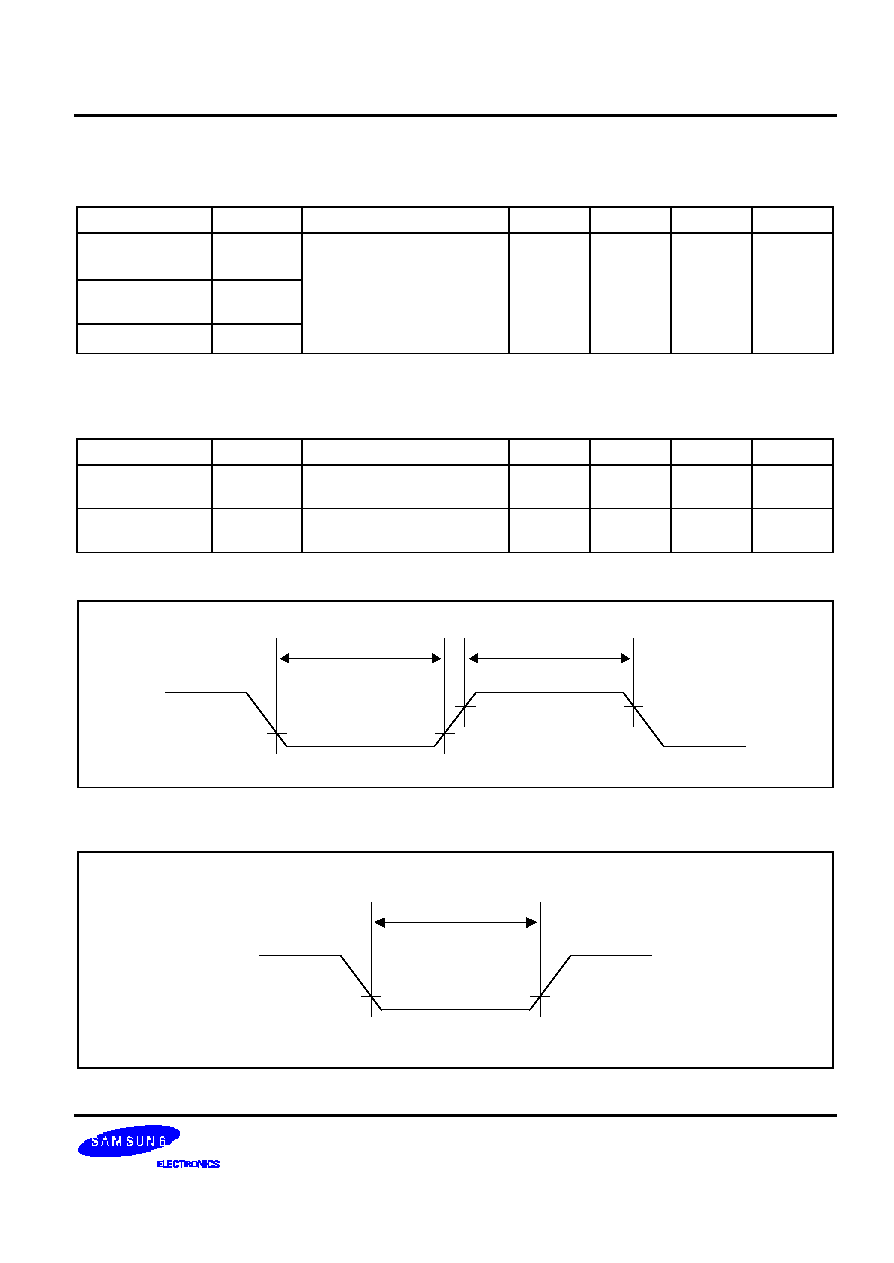

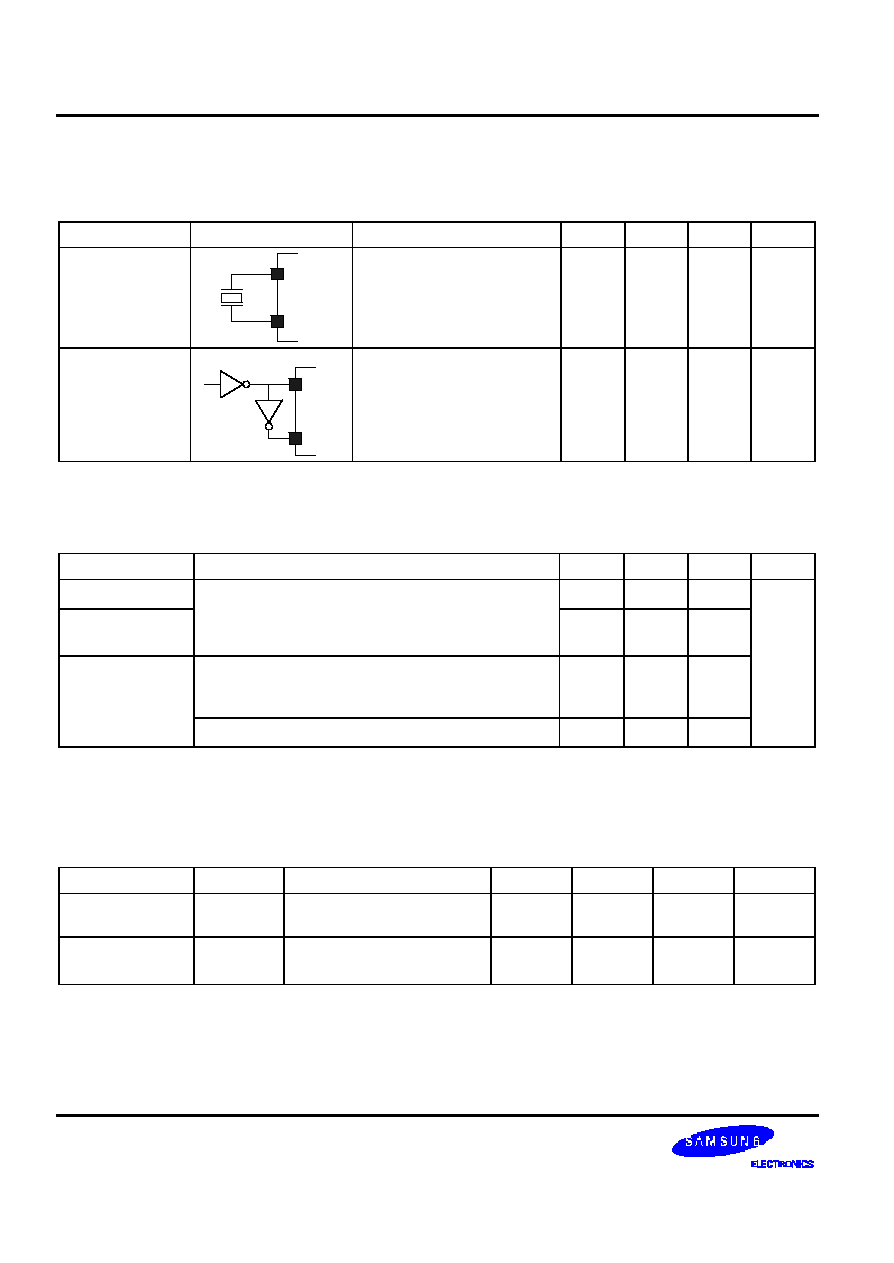

PIN CIRCUITS DIAGRAMS

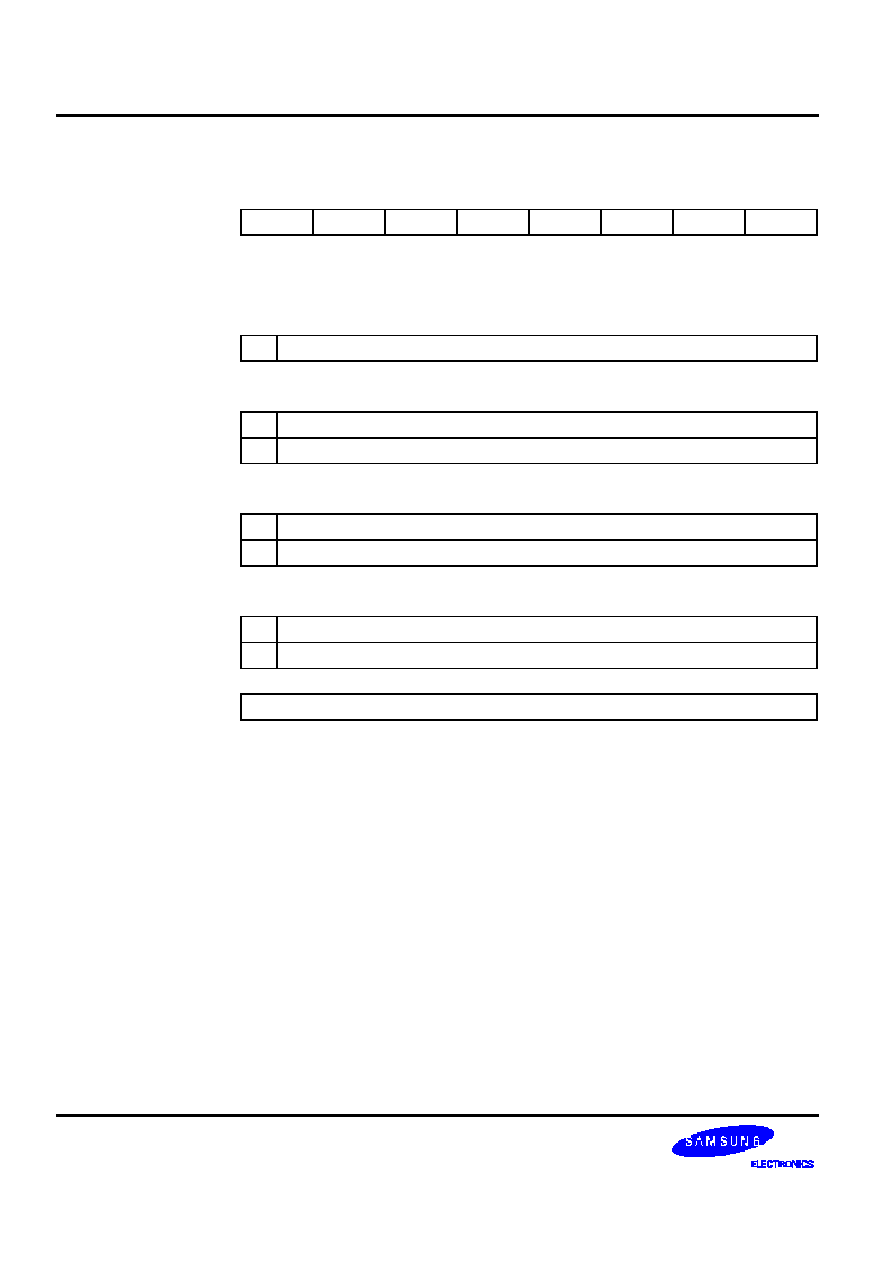

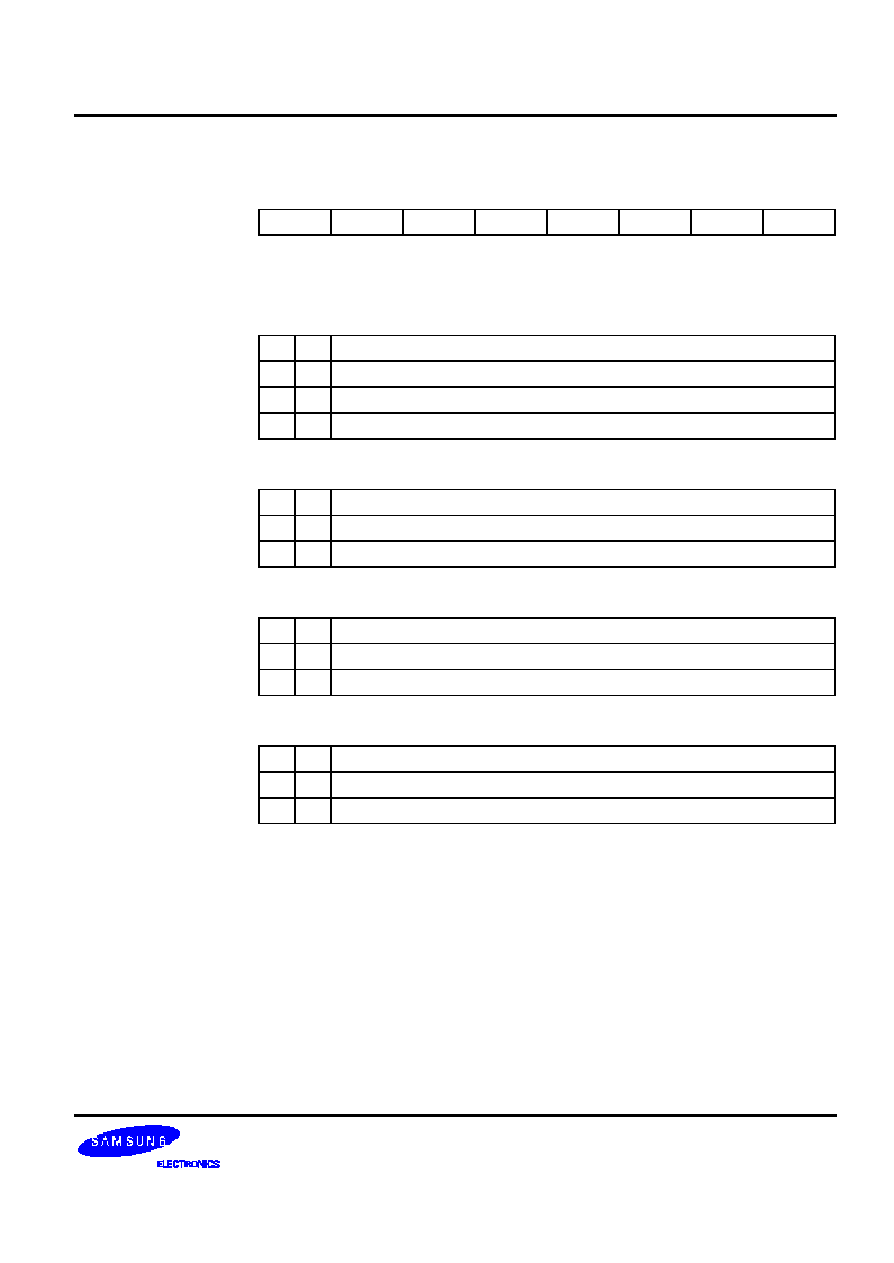

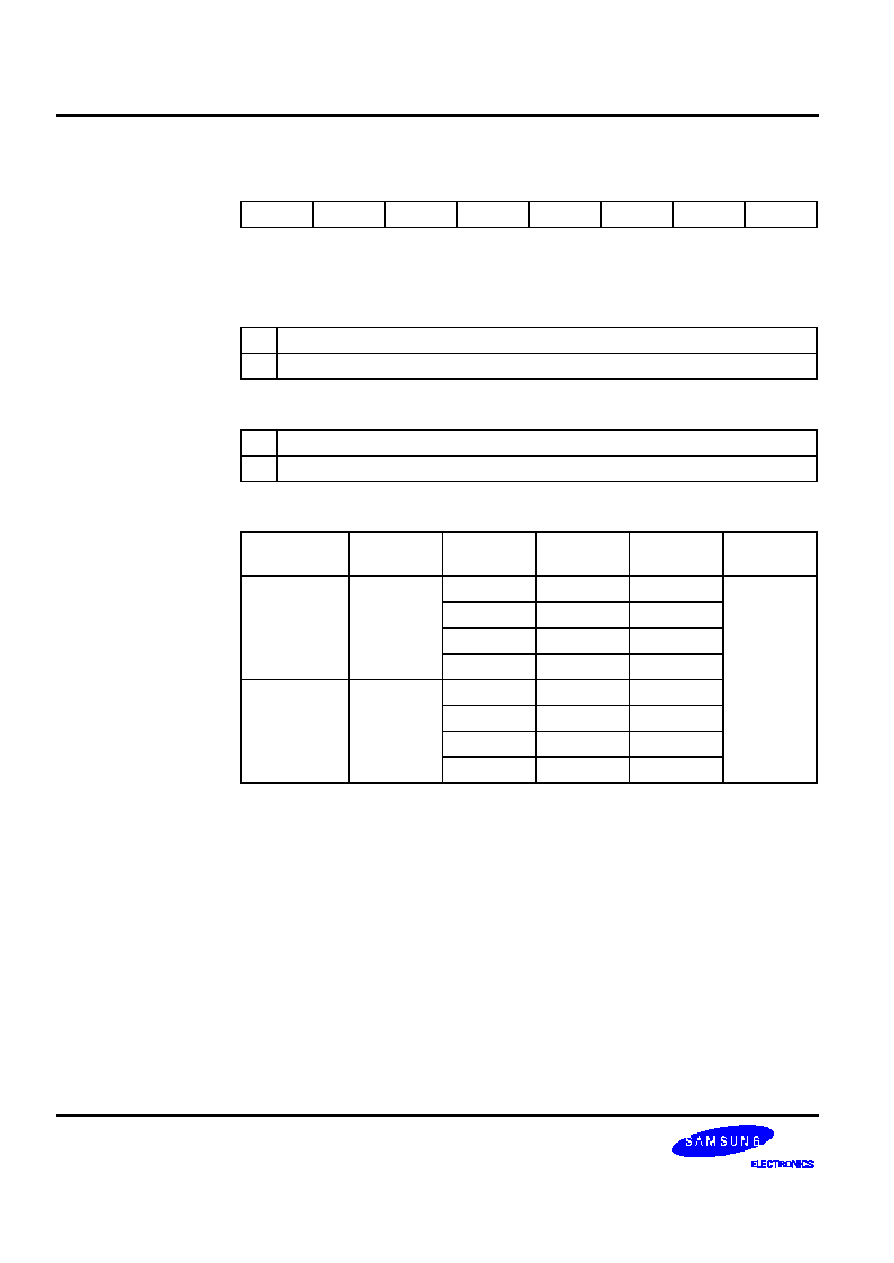

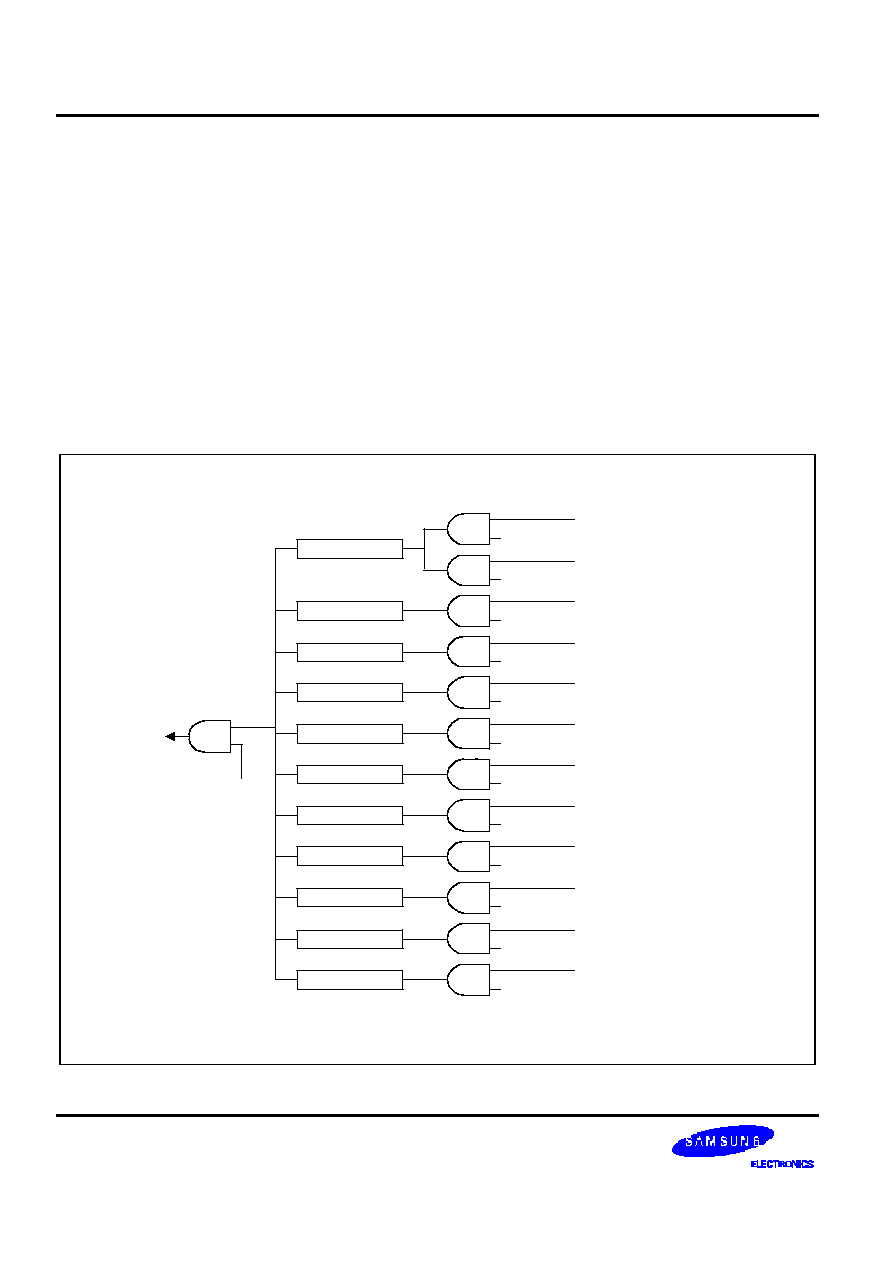

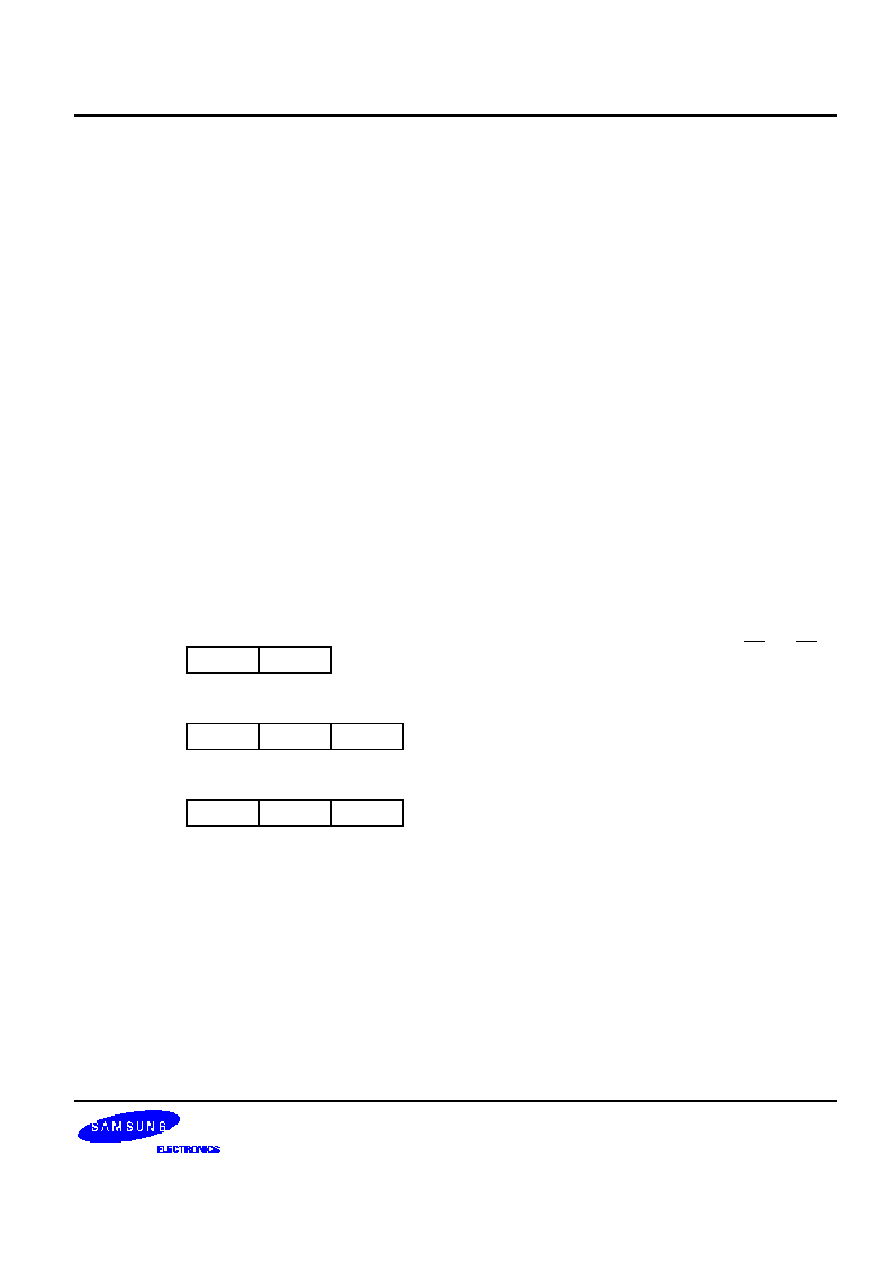

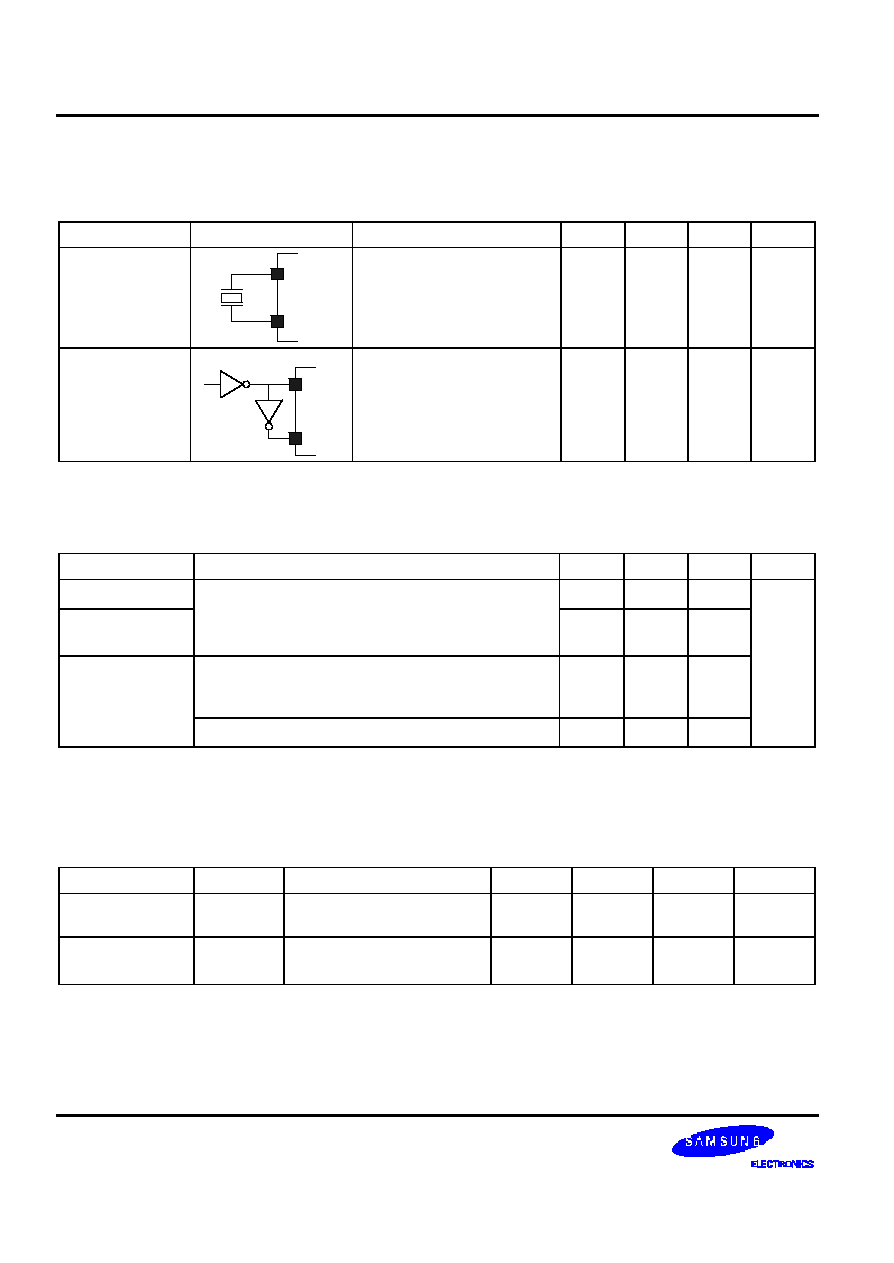

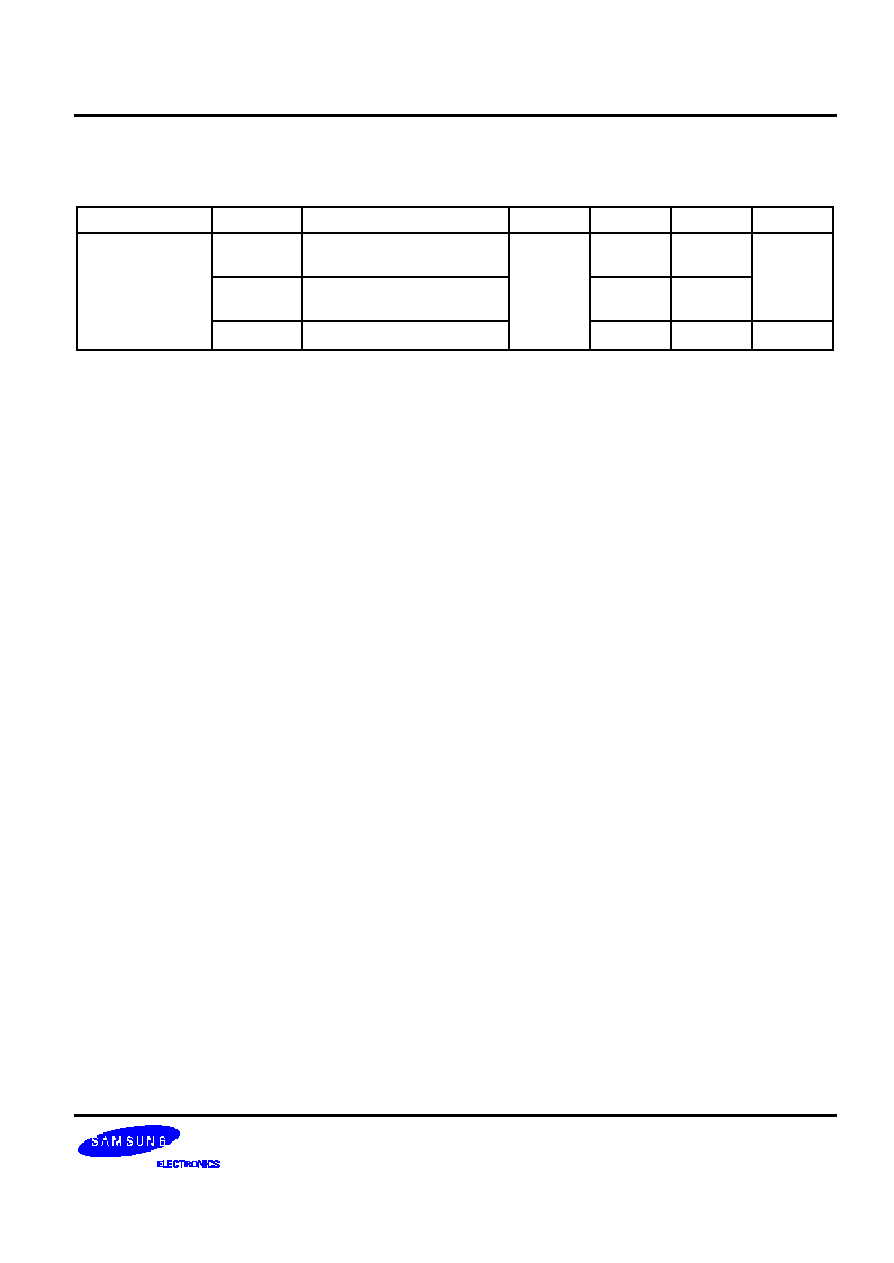

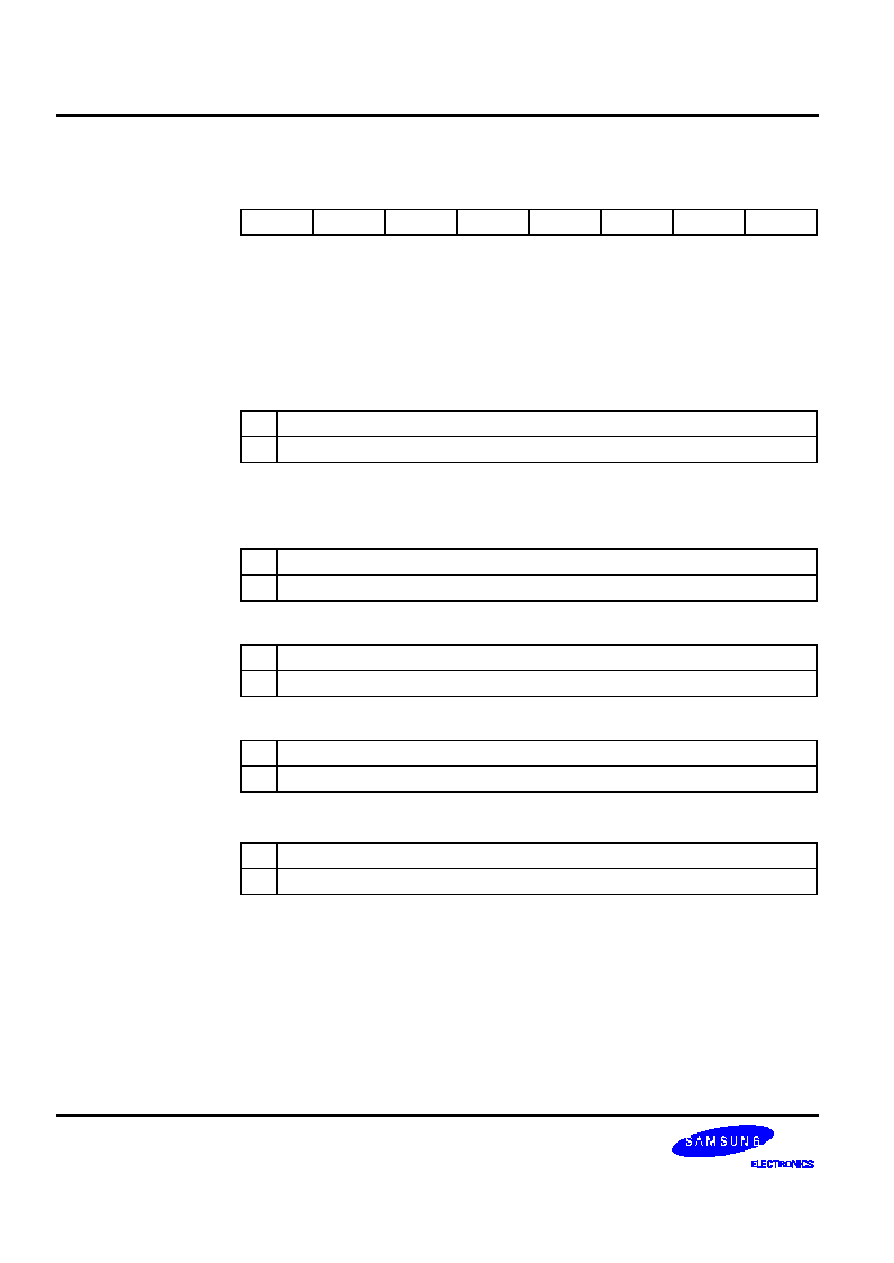

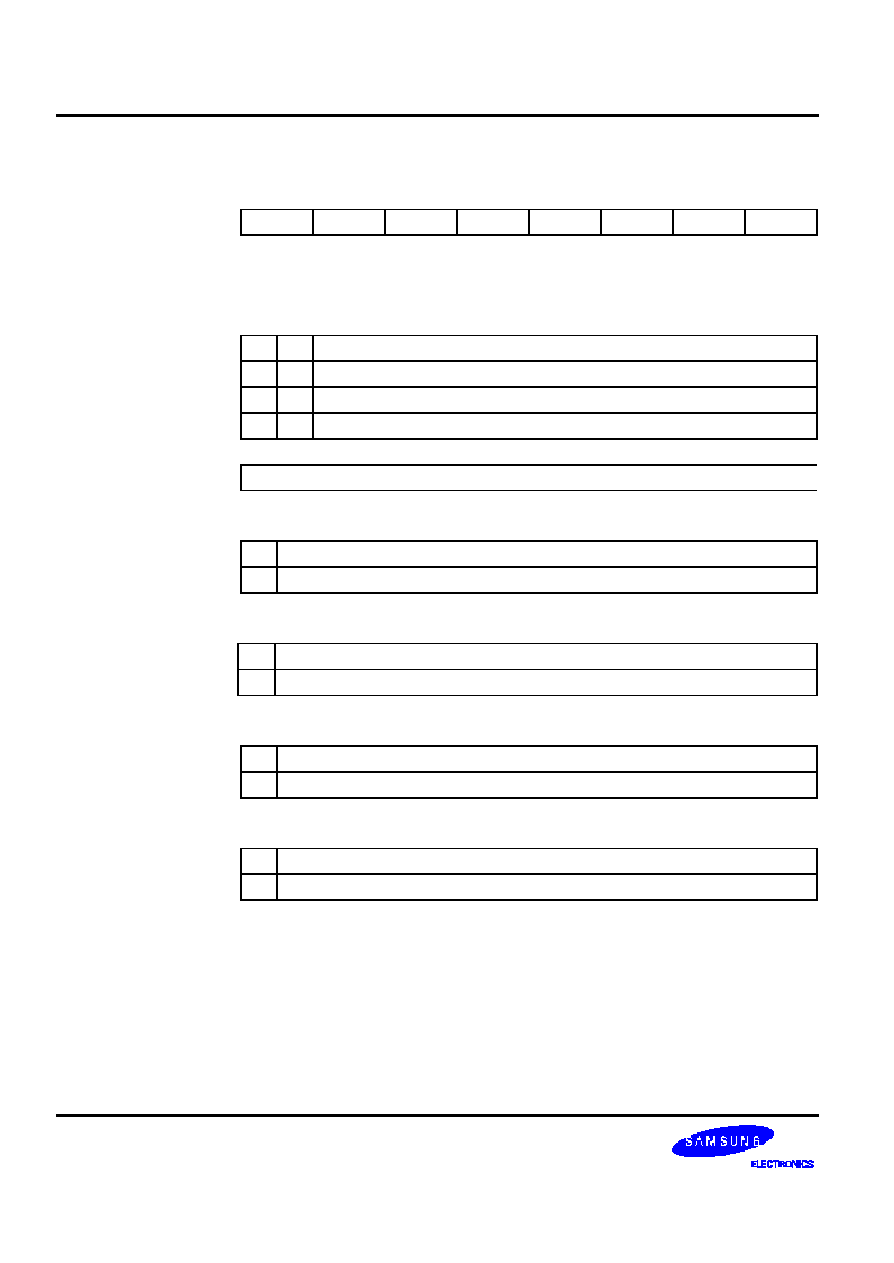

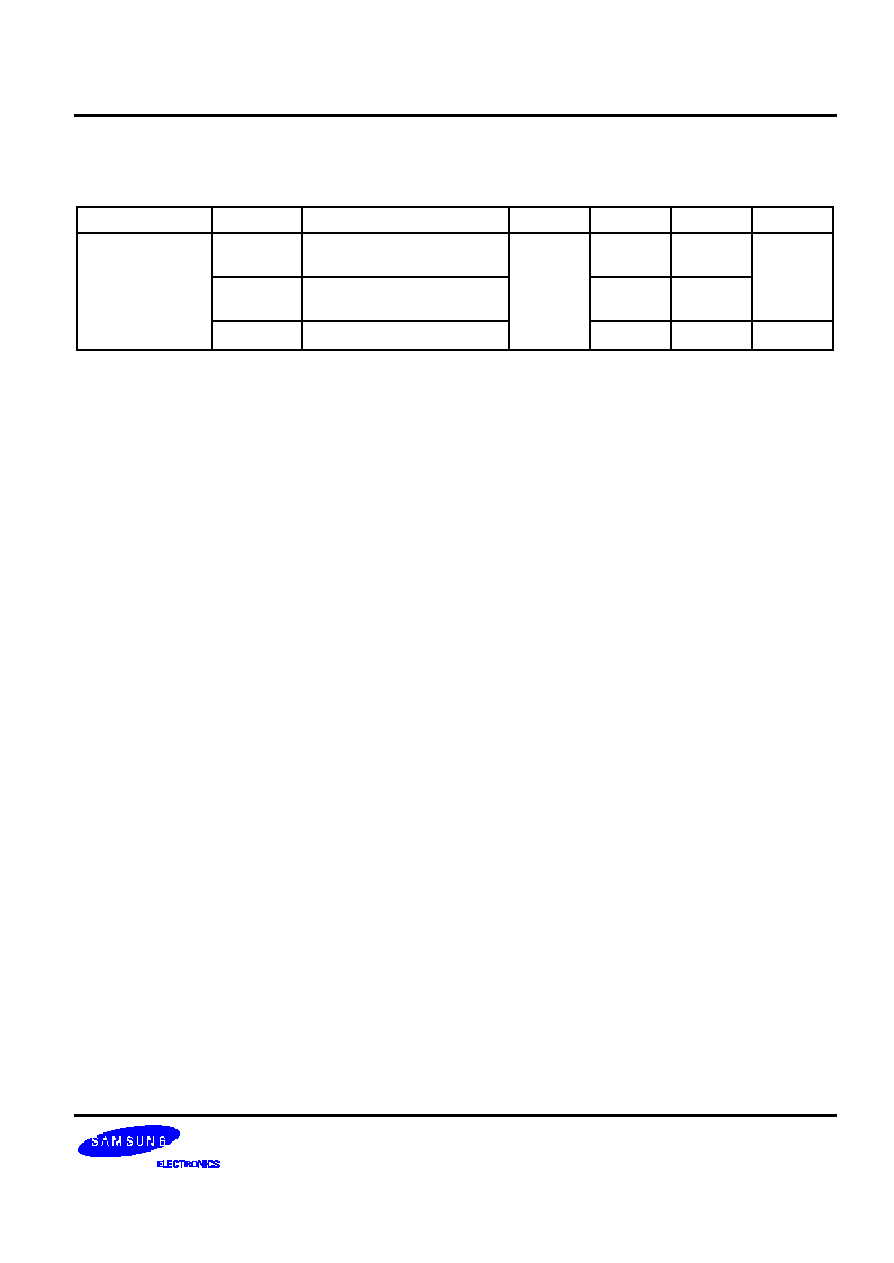

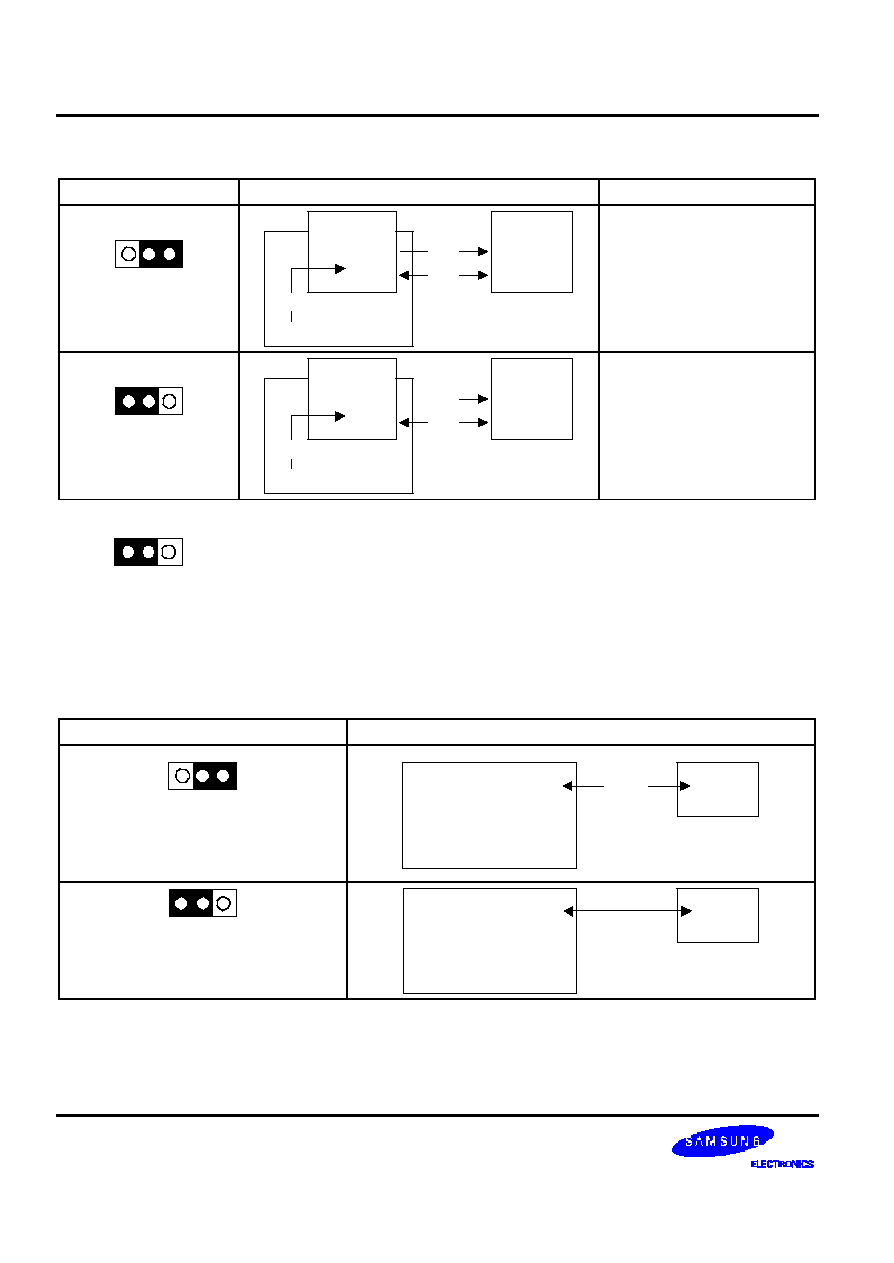

Table 1-2. Pin Circuit Assignments for the S3C9688/P9688

Circuit Number

Circuit Type

S3C9688/P9688 Assignments

A

I

RESET

signal input

B

I/O

Ports 0, 1, and 2

C

I/O

Port 3

D

I/O

Port 4

S3C9688/P9688

PRODUCT OVERVIEW

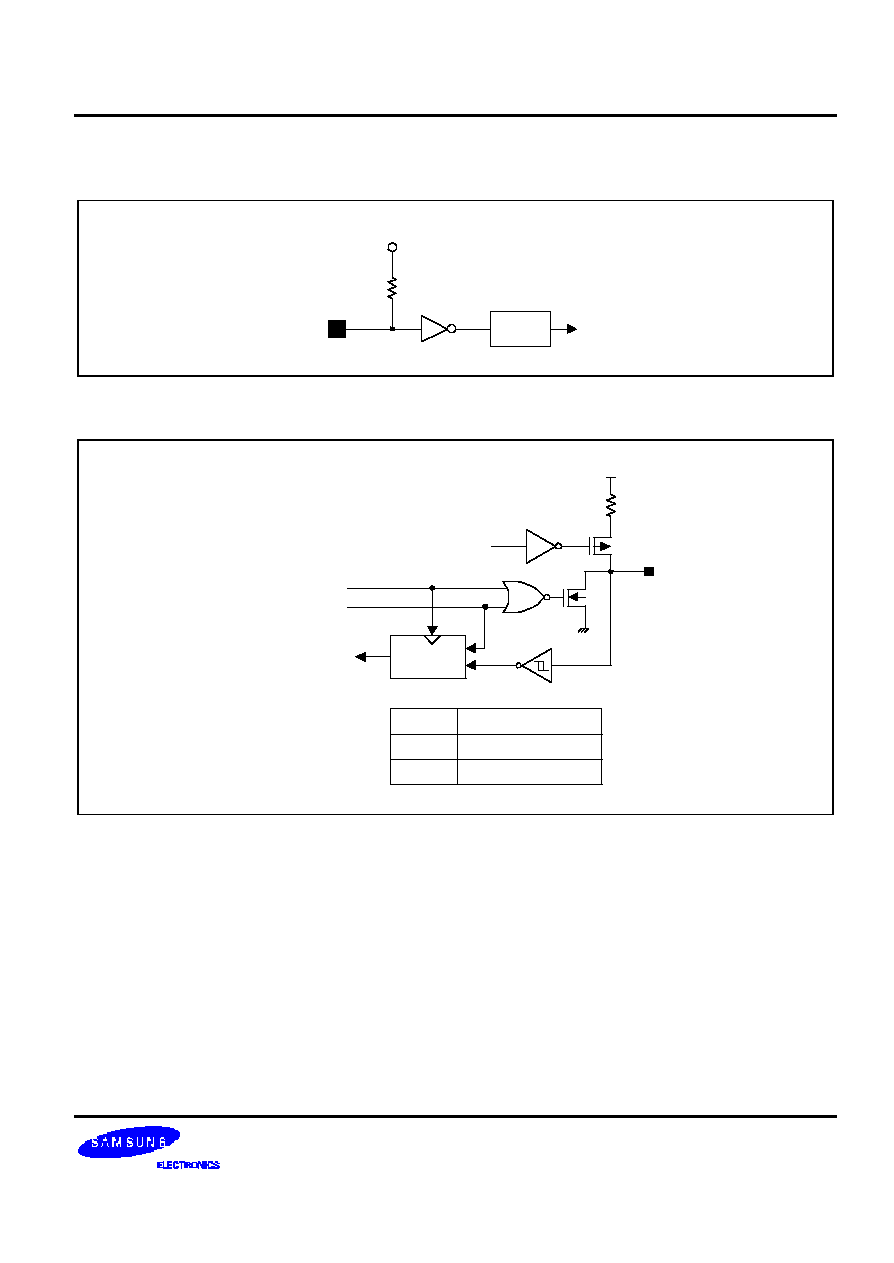

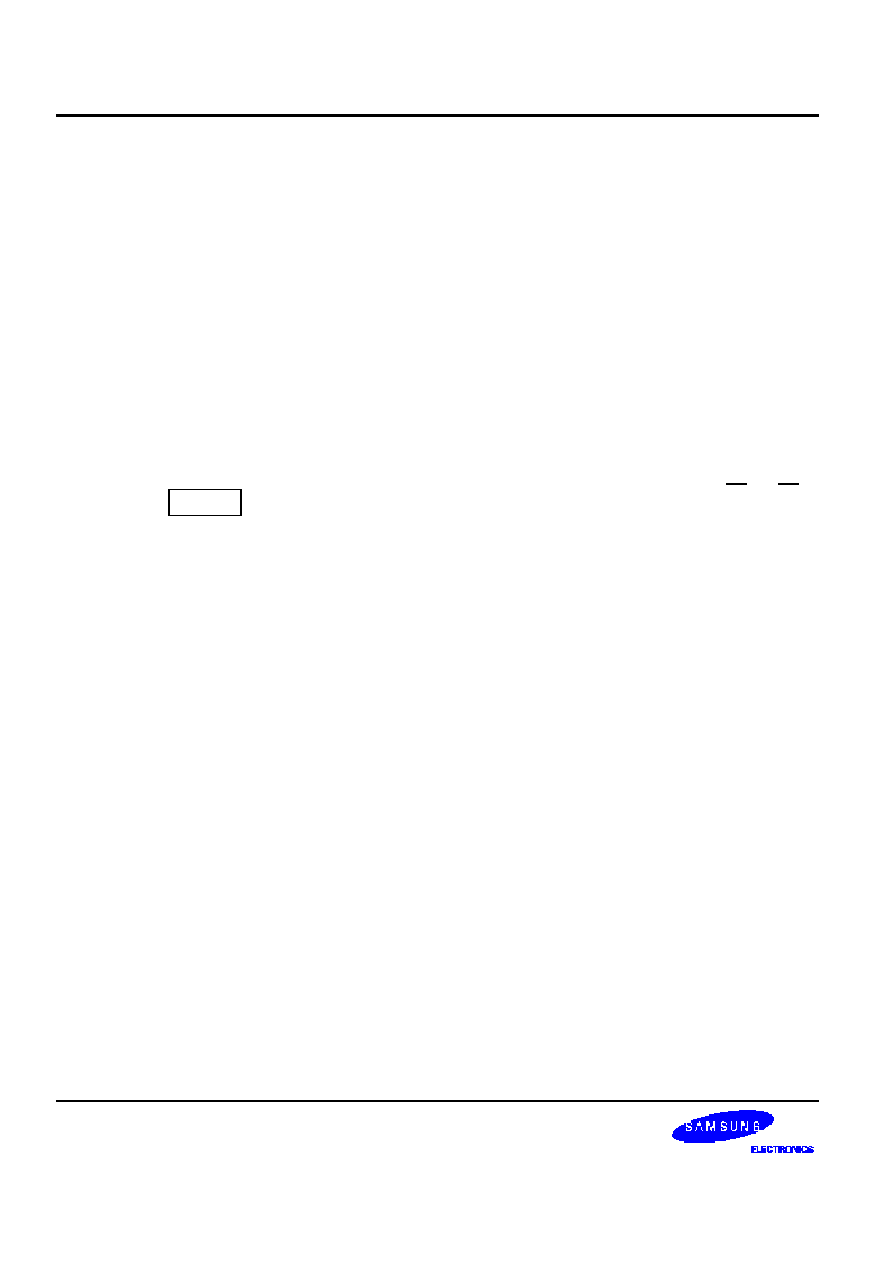

1-7

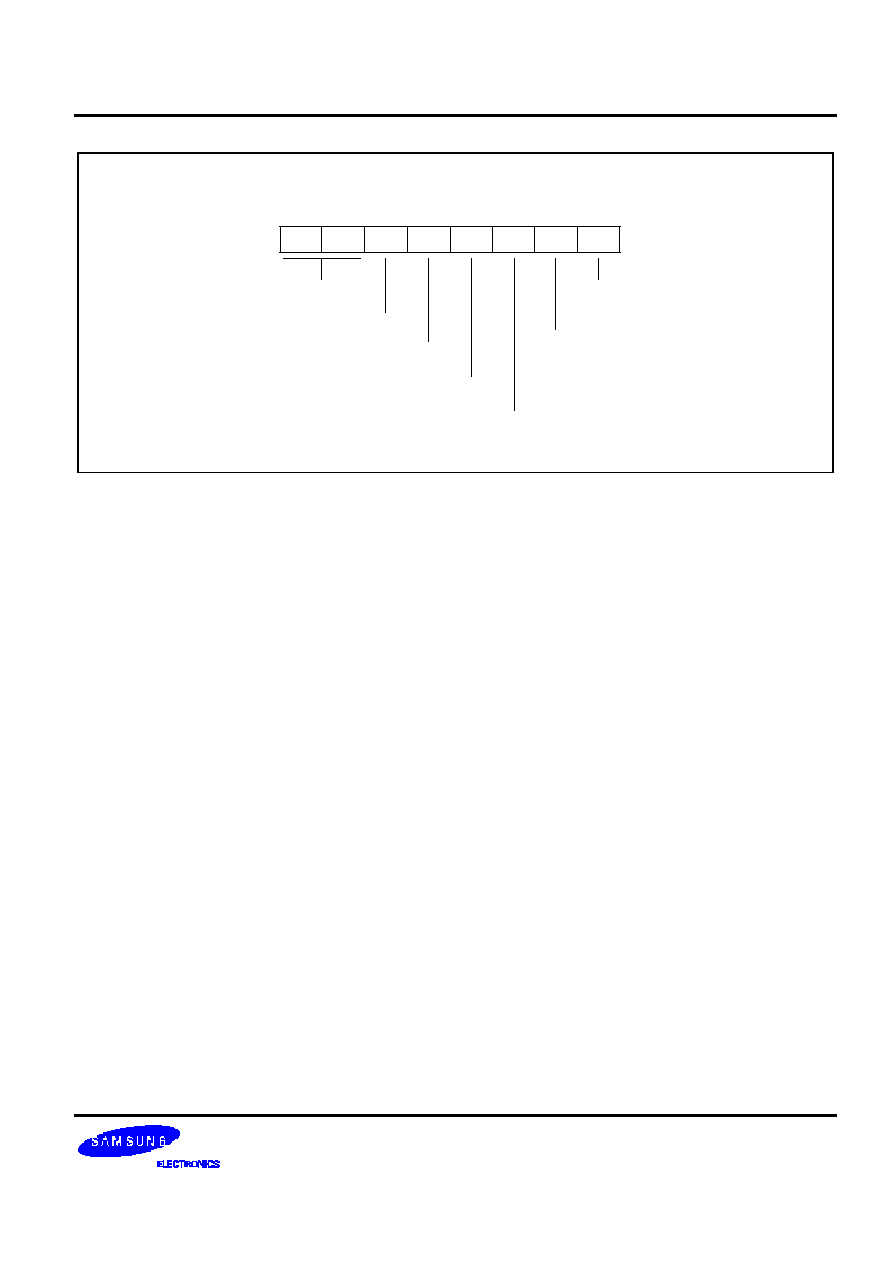

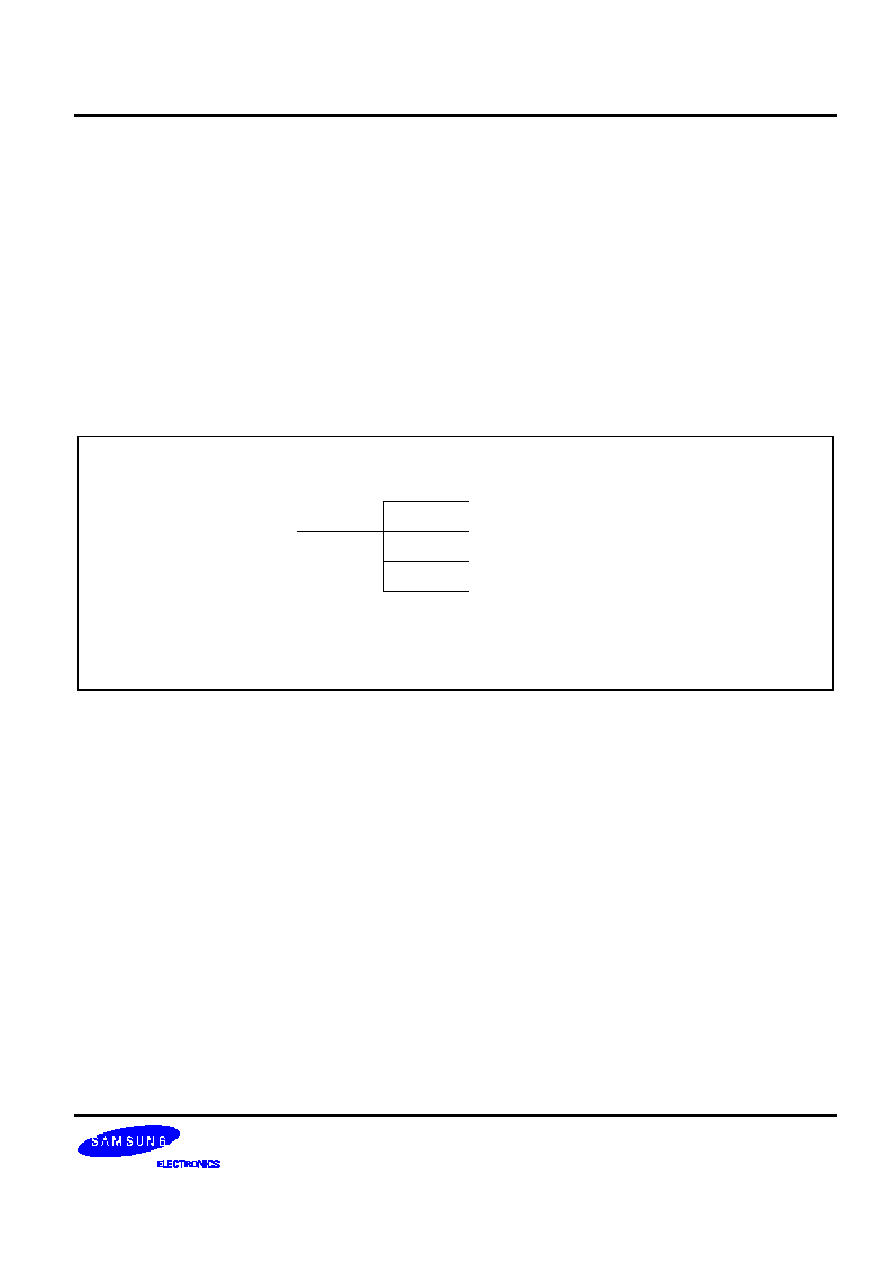

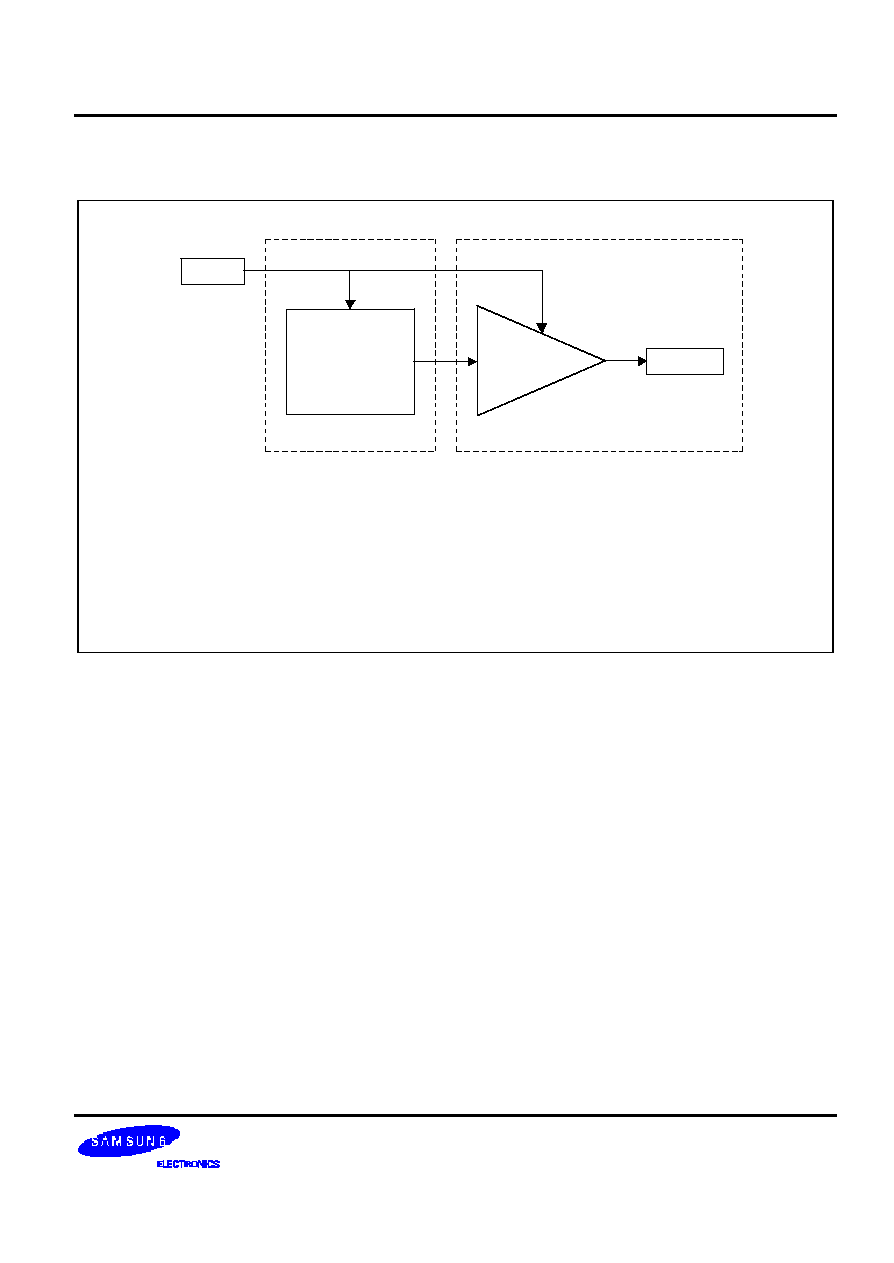

V

DD

Pull-up

Resistor

Noise

Filter

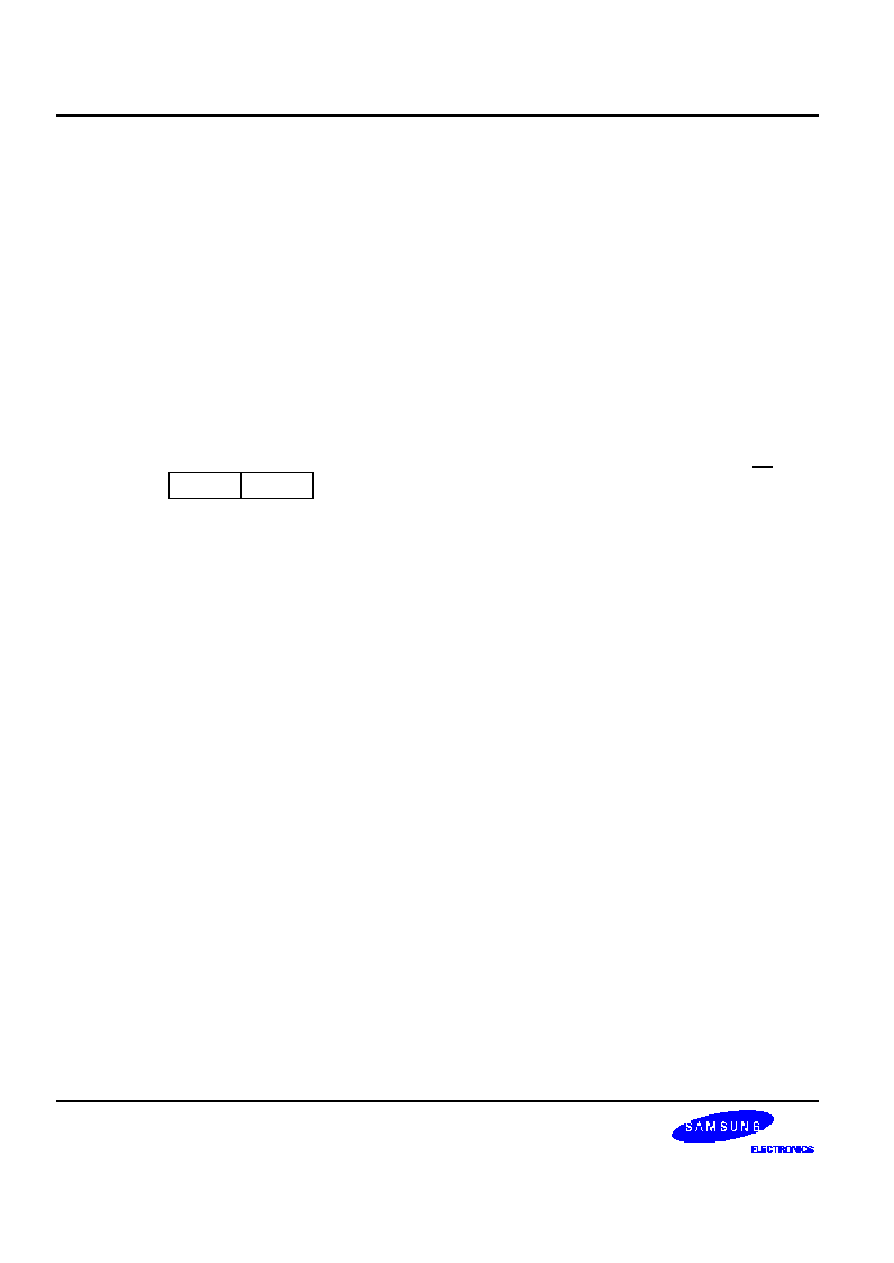

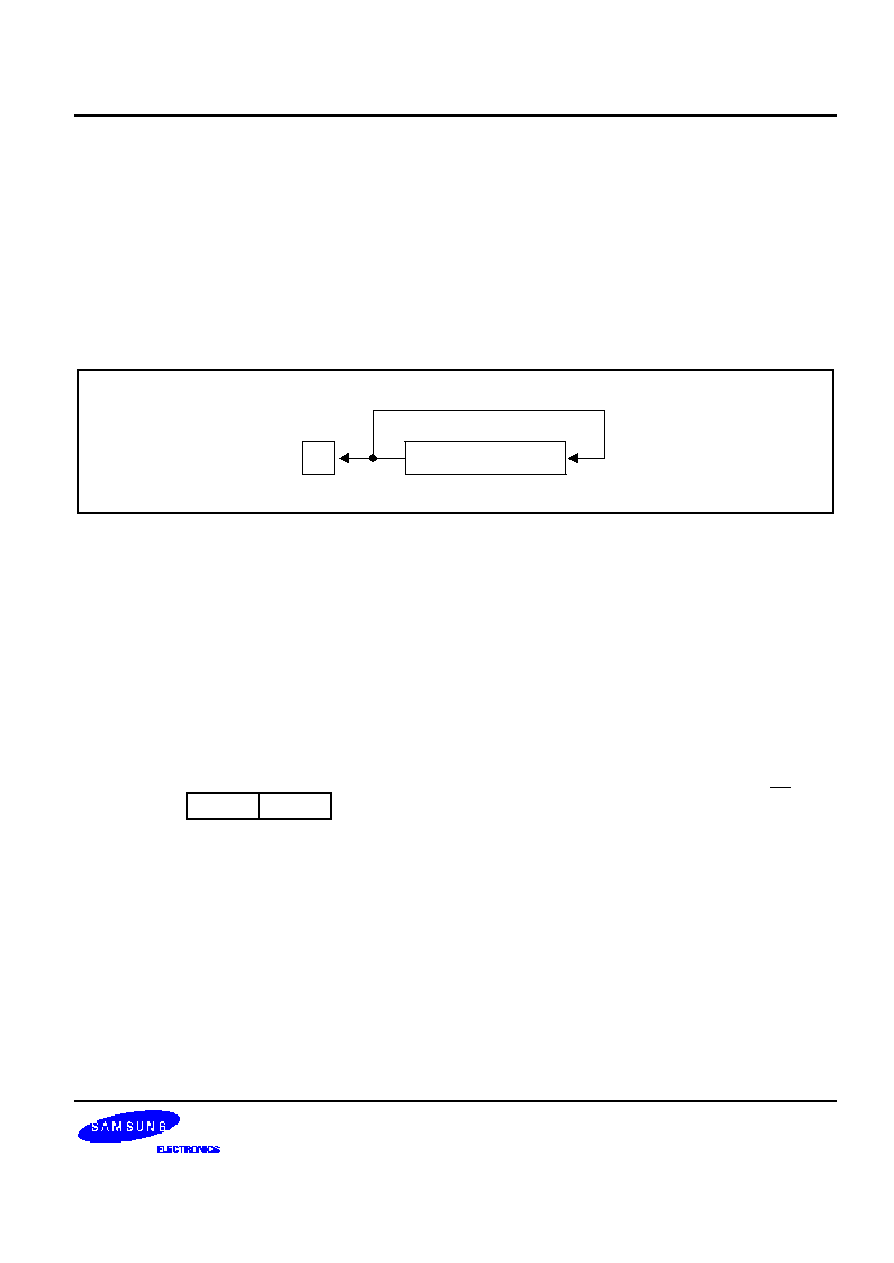

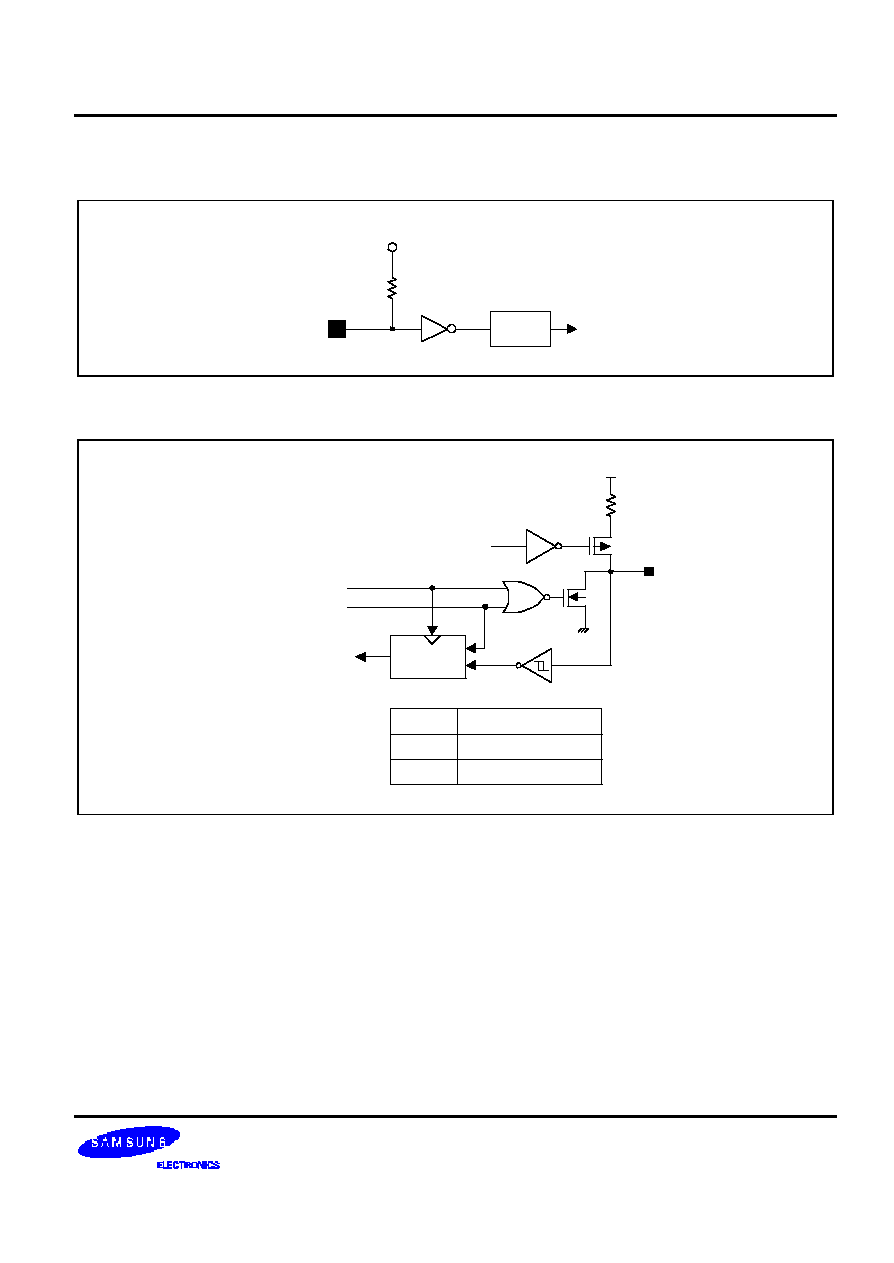

Figure 1-4. Pin Circuit Type A (RESET)

V

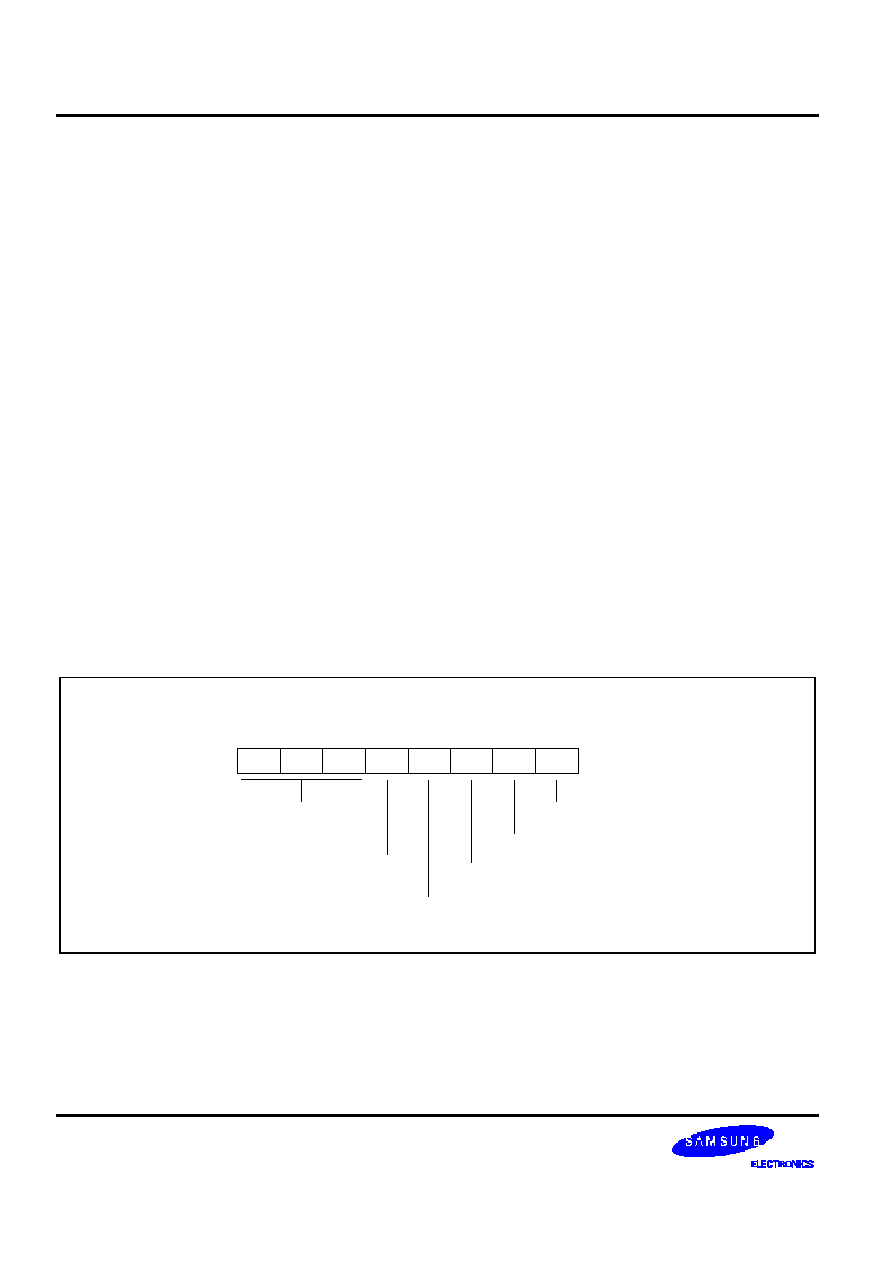

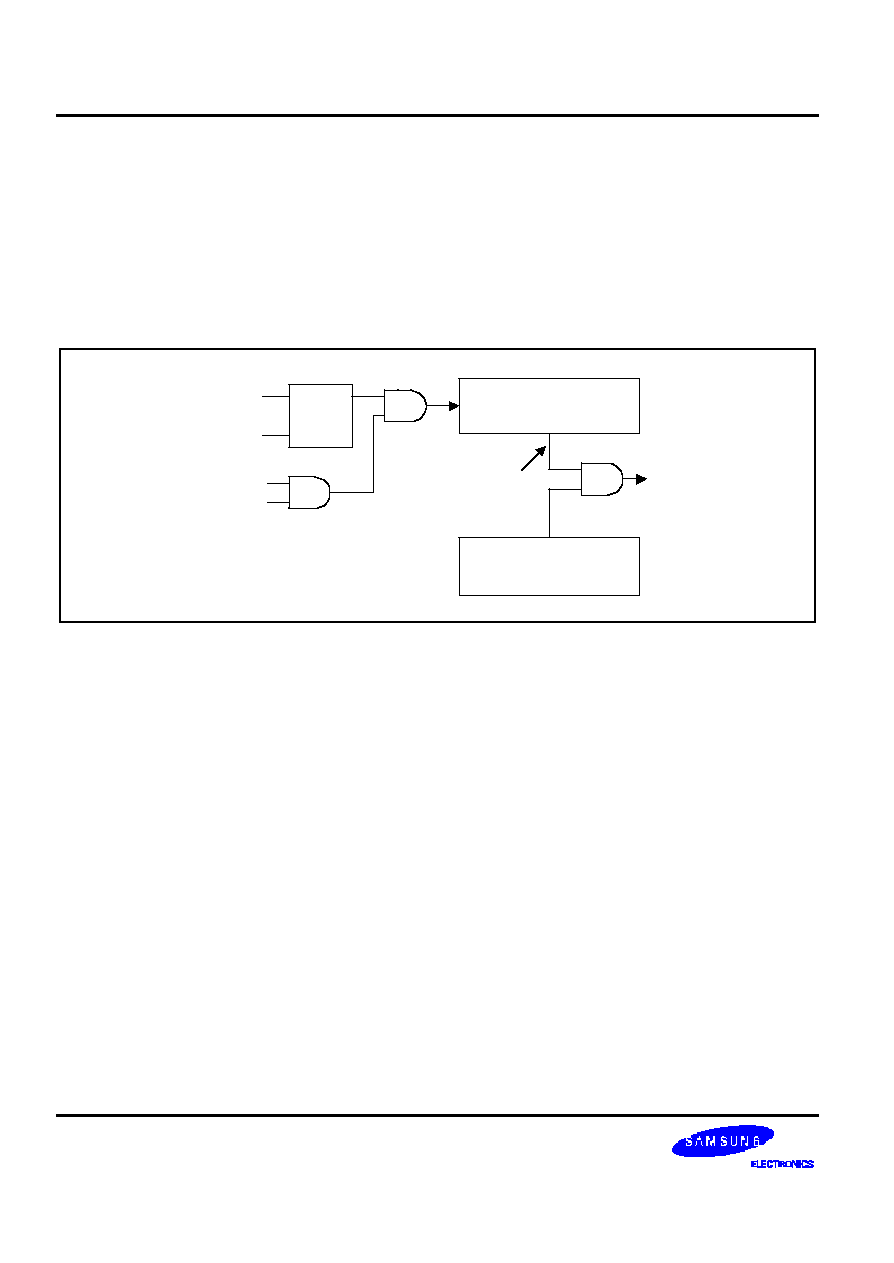

DD

Pull-up

Resistor

V

SS

Pull-up Enable

Output Disable

Open Data

D0

D1

MUX

Input Data

I/O

Mode

Input Data

Output

D0

Input

D1

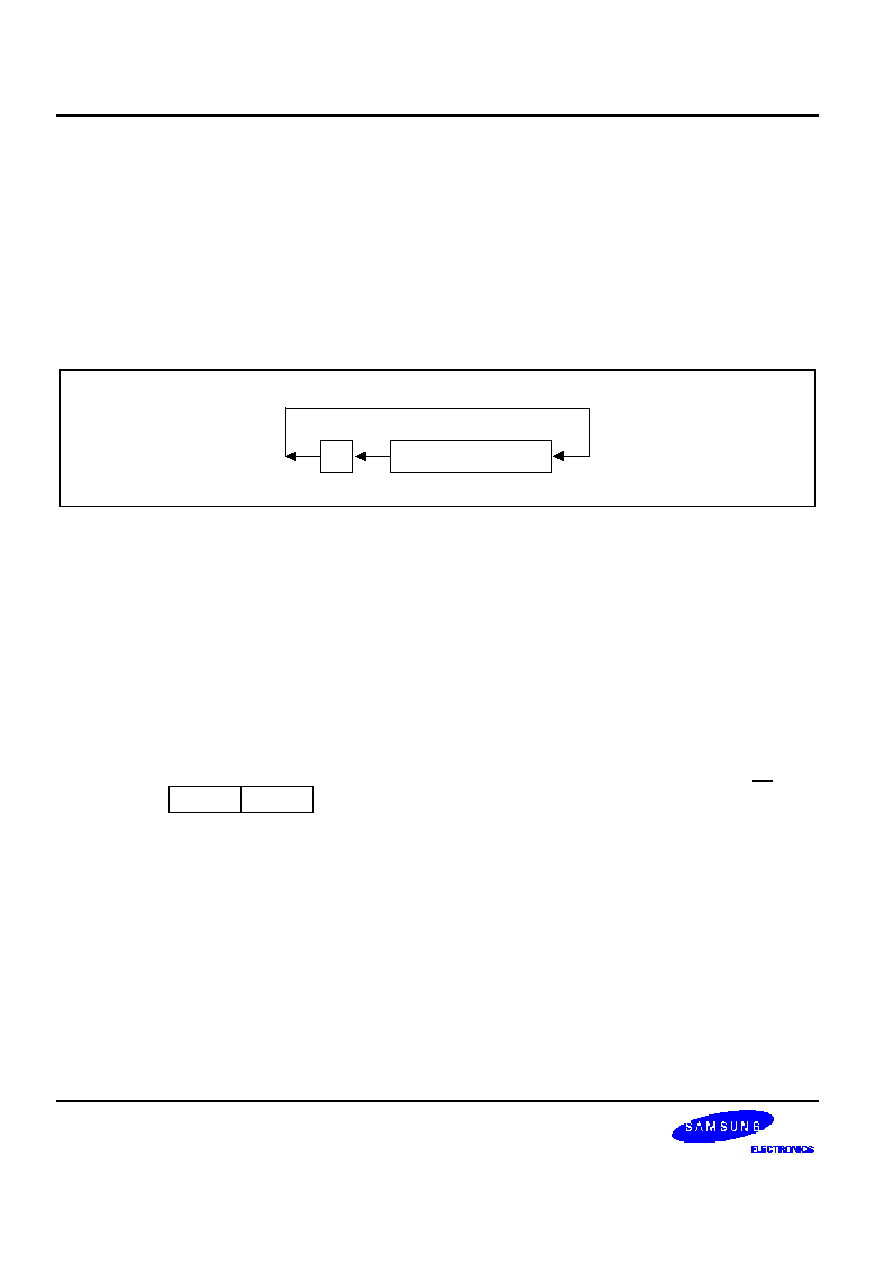

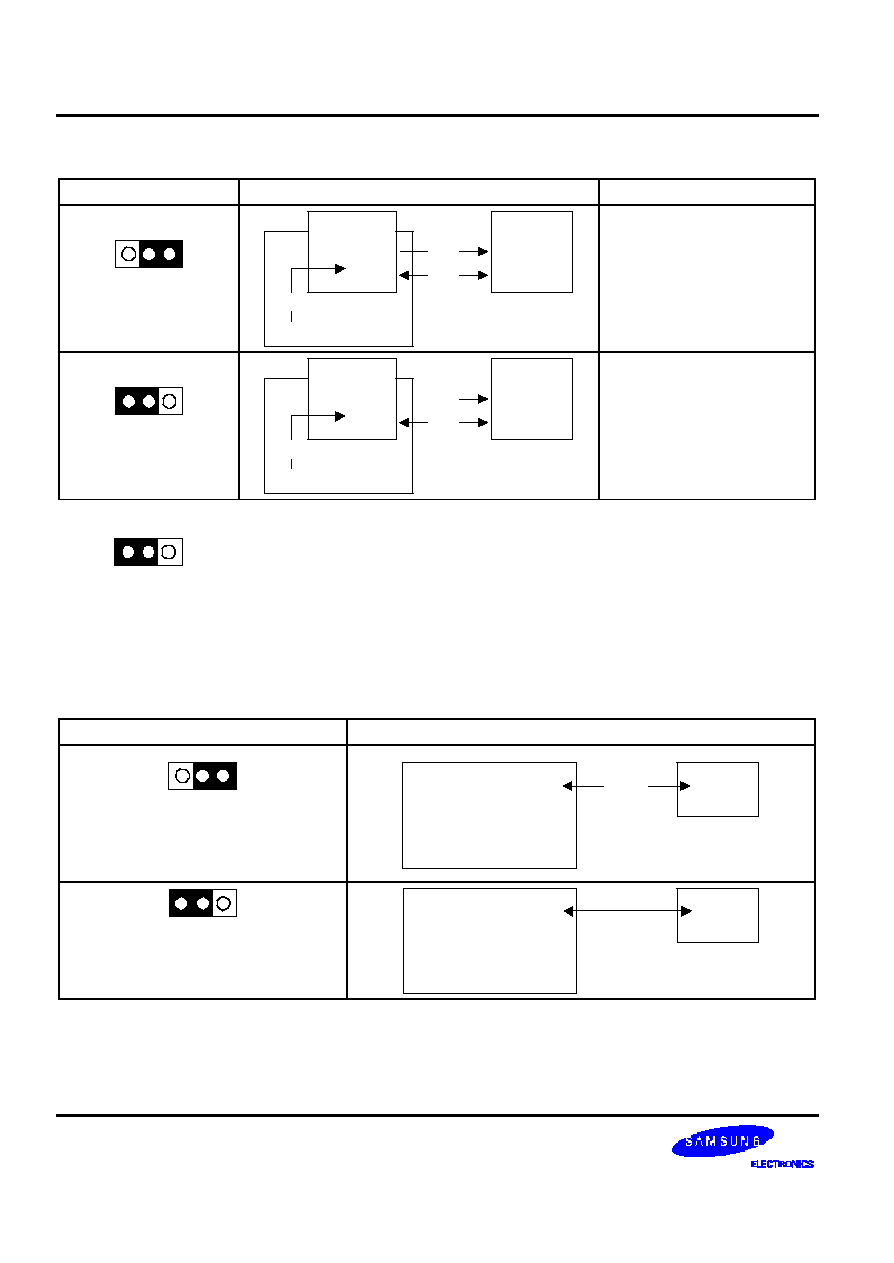

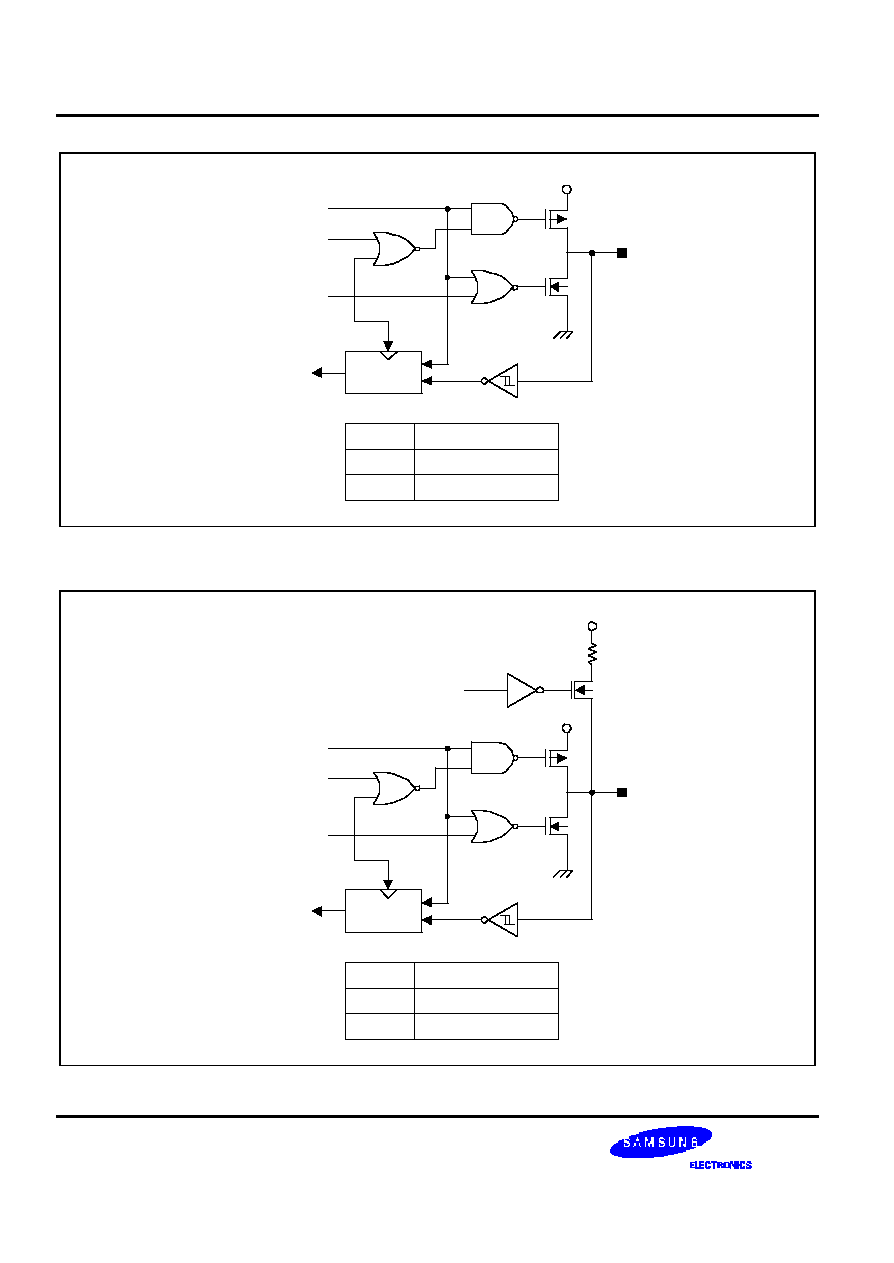

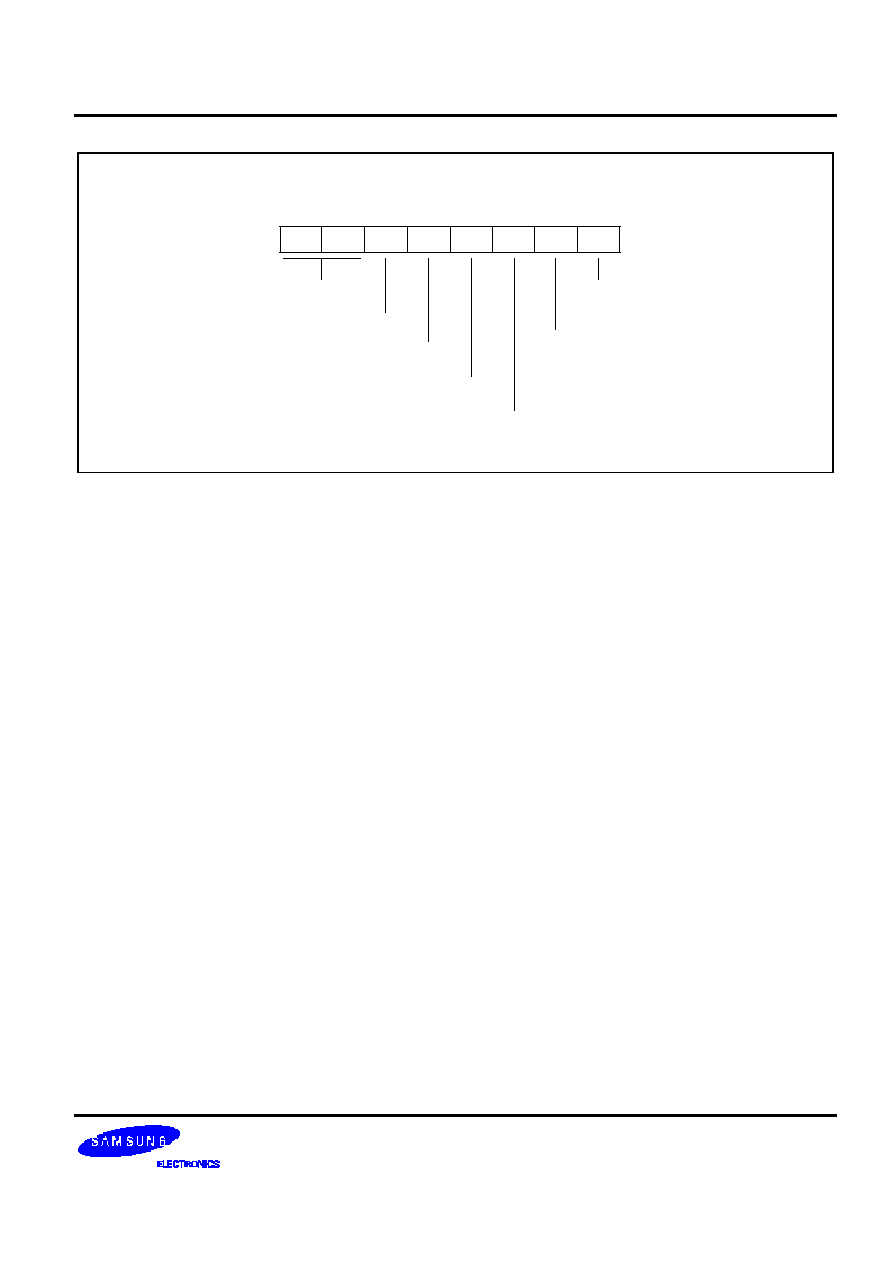

Figure 1-5. Pin Circuit Type B (Ports 0, 1 and 2)

PRODUCT OVERVIEW

S3C9688/P9688

1-8

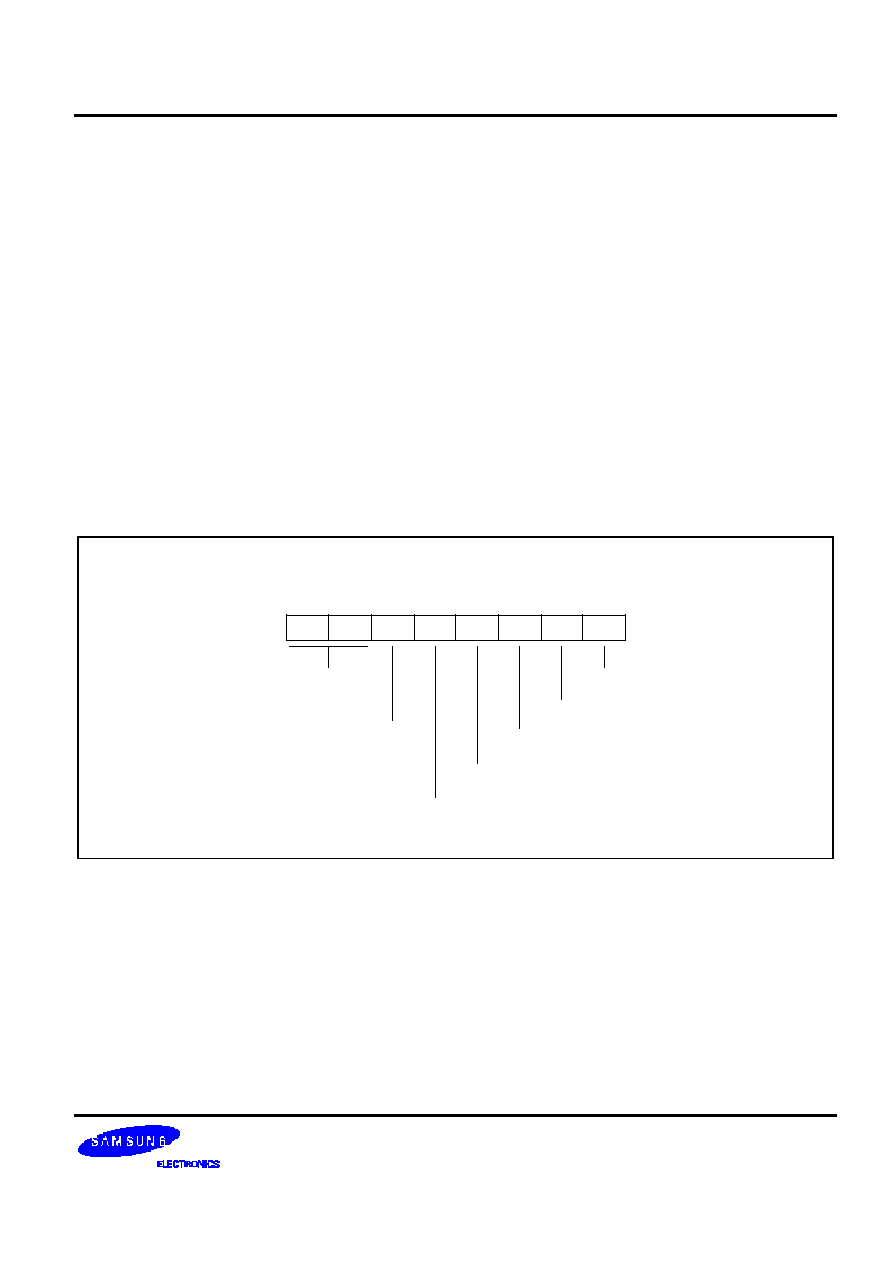

V

DD

V

SS

Output Data

Open Drain

D0

D1

MUX

Input Data

I/O

Mode

Input Data

Output

D0

Input

D1

Output

Disable

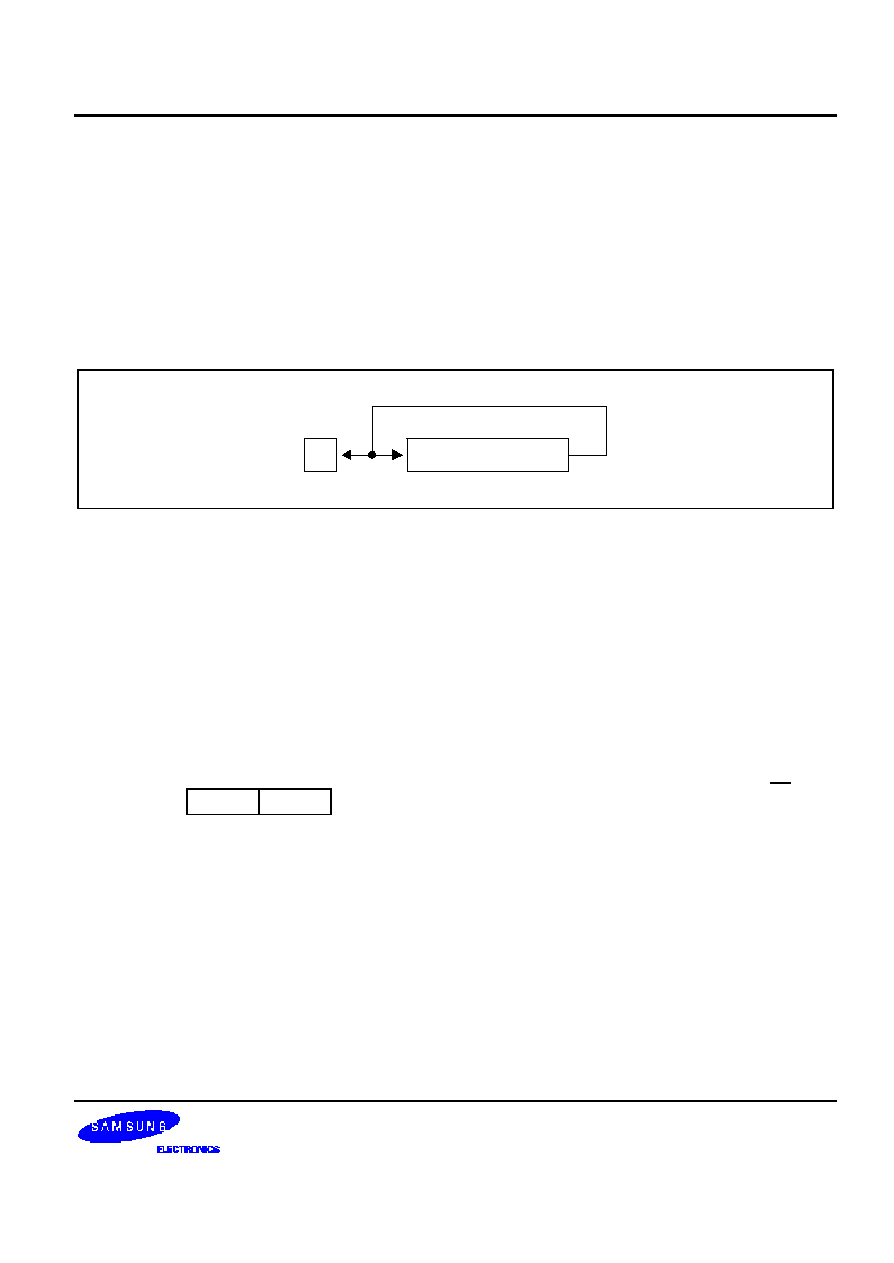

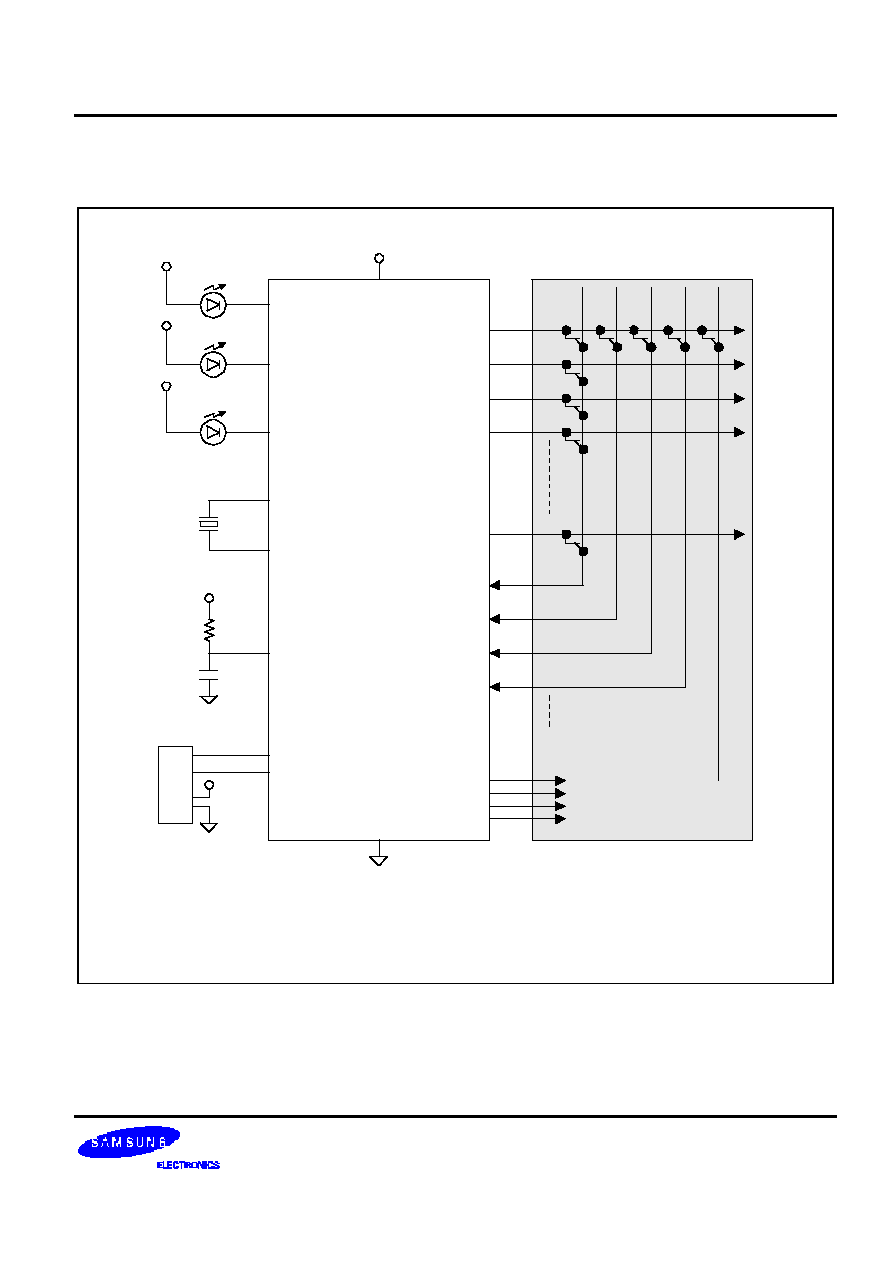

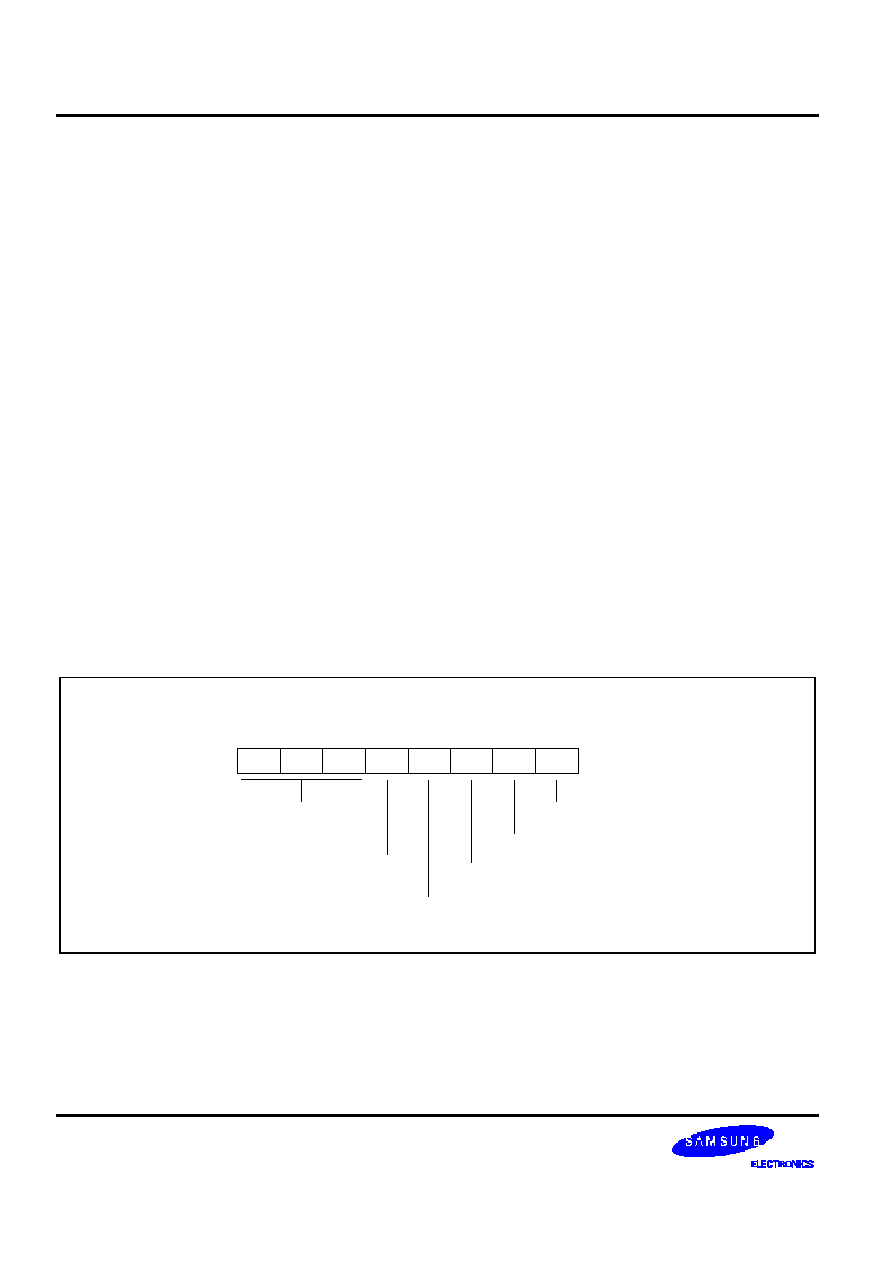

Figure 1-6. Pin Circuit Type C (Port 3)

V

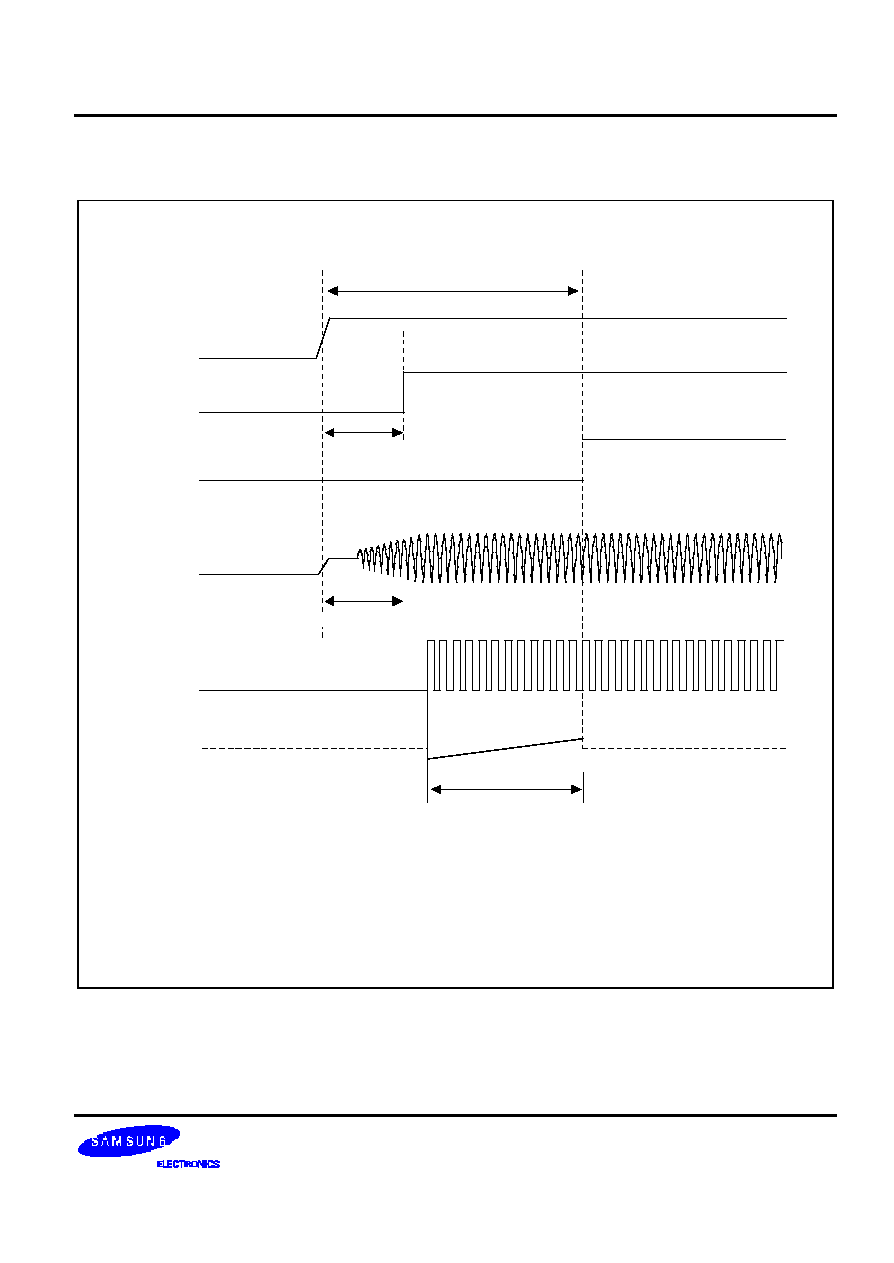

DD

V

SS

Output Data

Open Drain

D0

D1

MUX

Input Data

I/O

Mode

Input Data

Output

D0

Input

D1

Output

Disable

Pull-up

Resistor

Pull-up Enable

V

DD

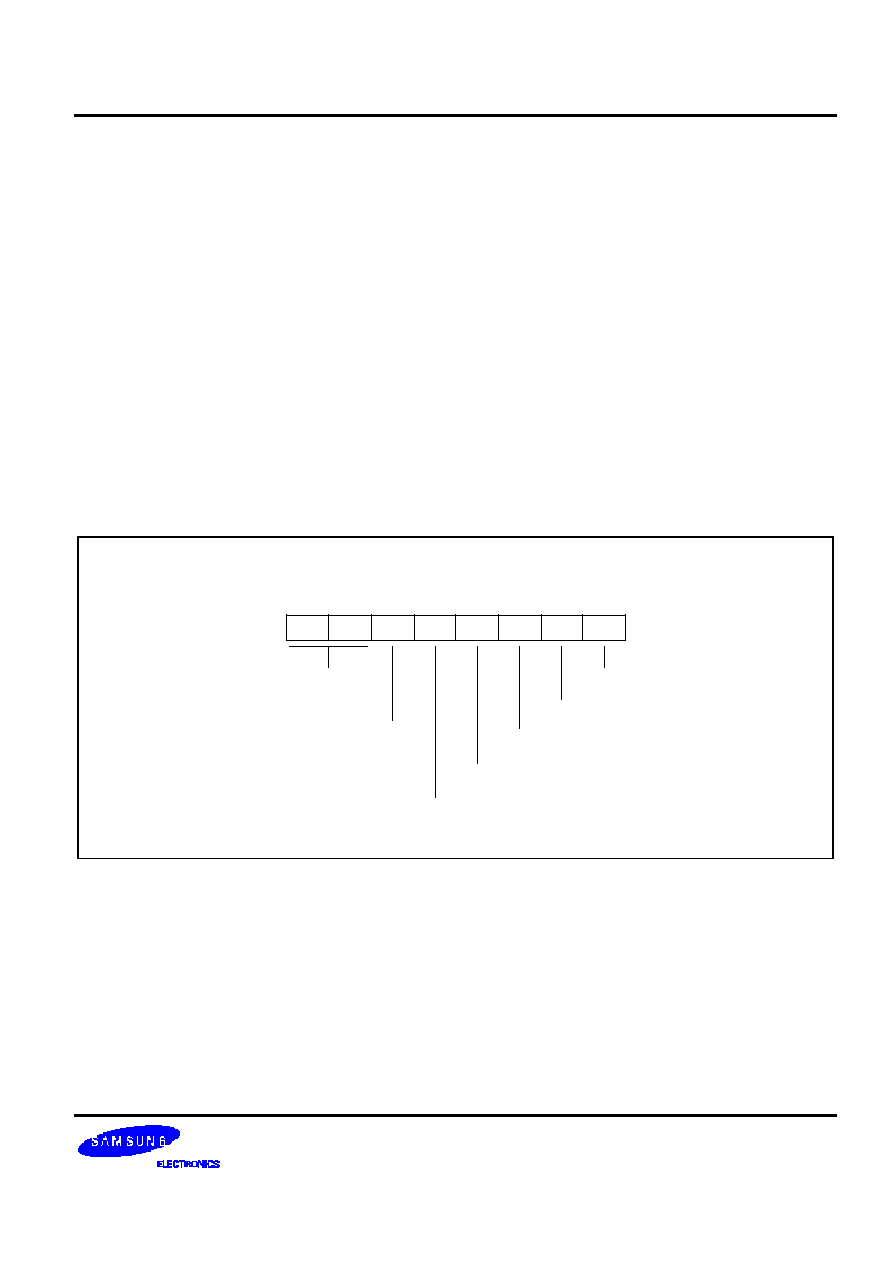

Figure 1-7. Pin Circuit Type D (Port 4)

S3C9688/P9688

PRODUCT OVERVIEW

1-9

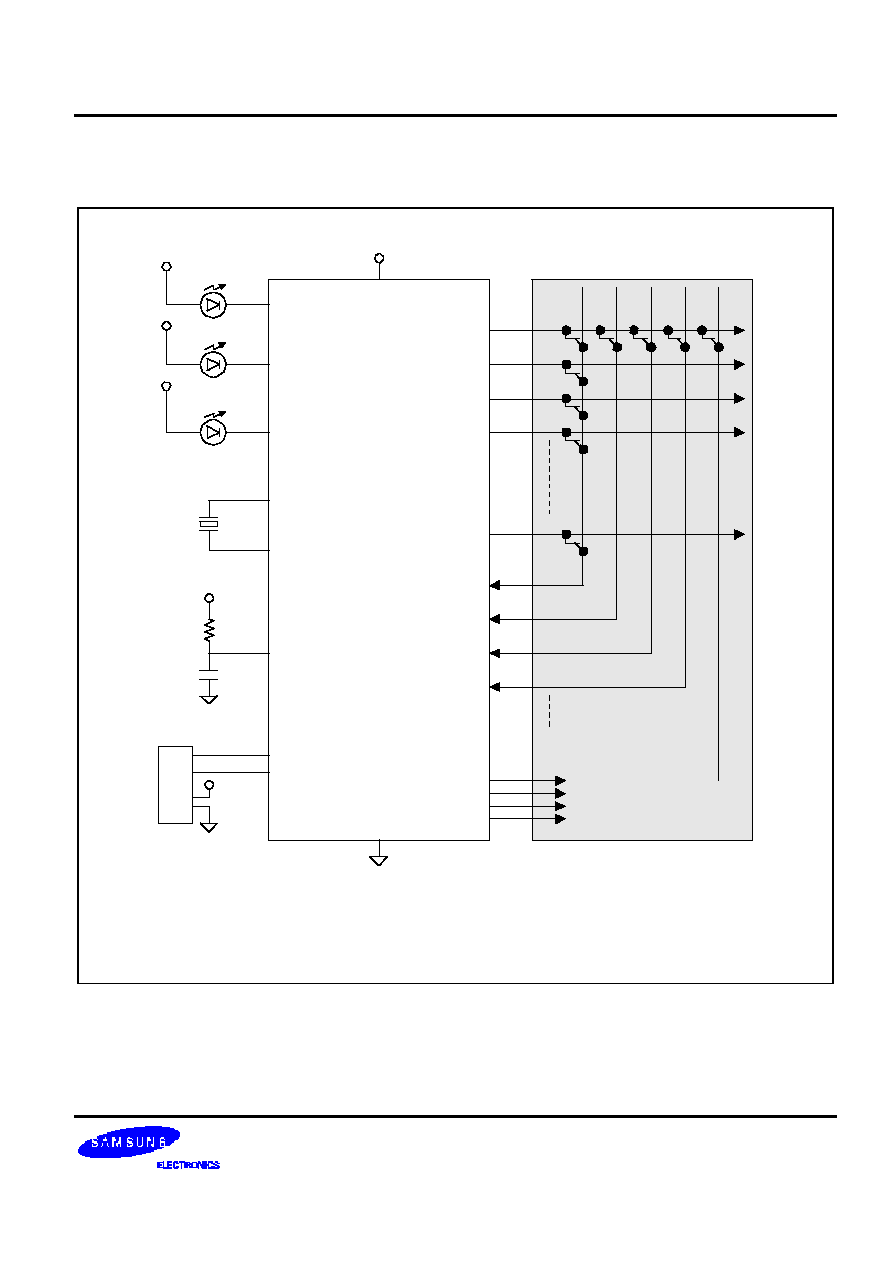

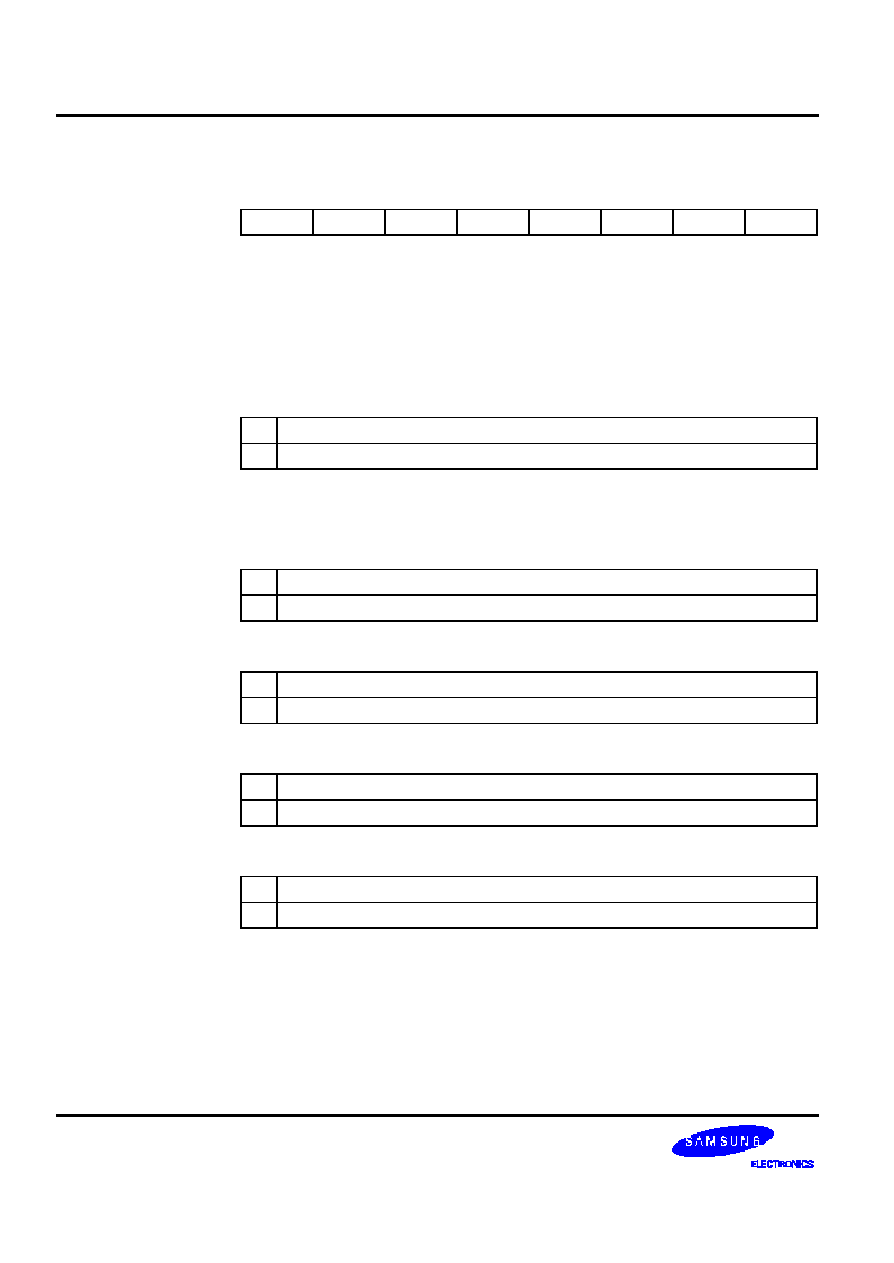

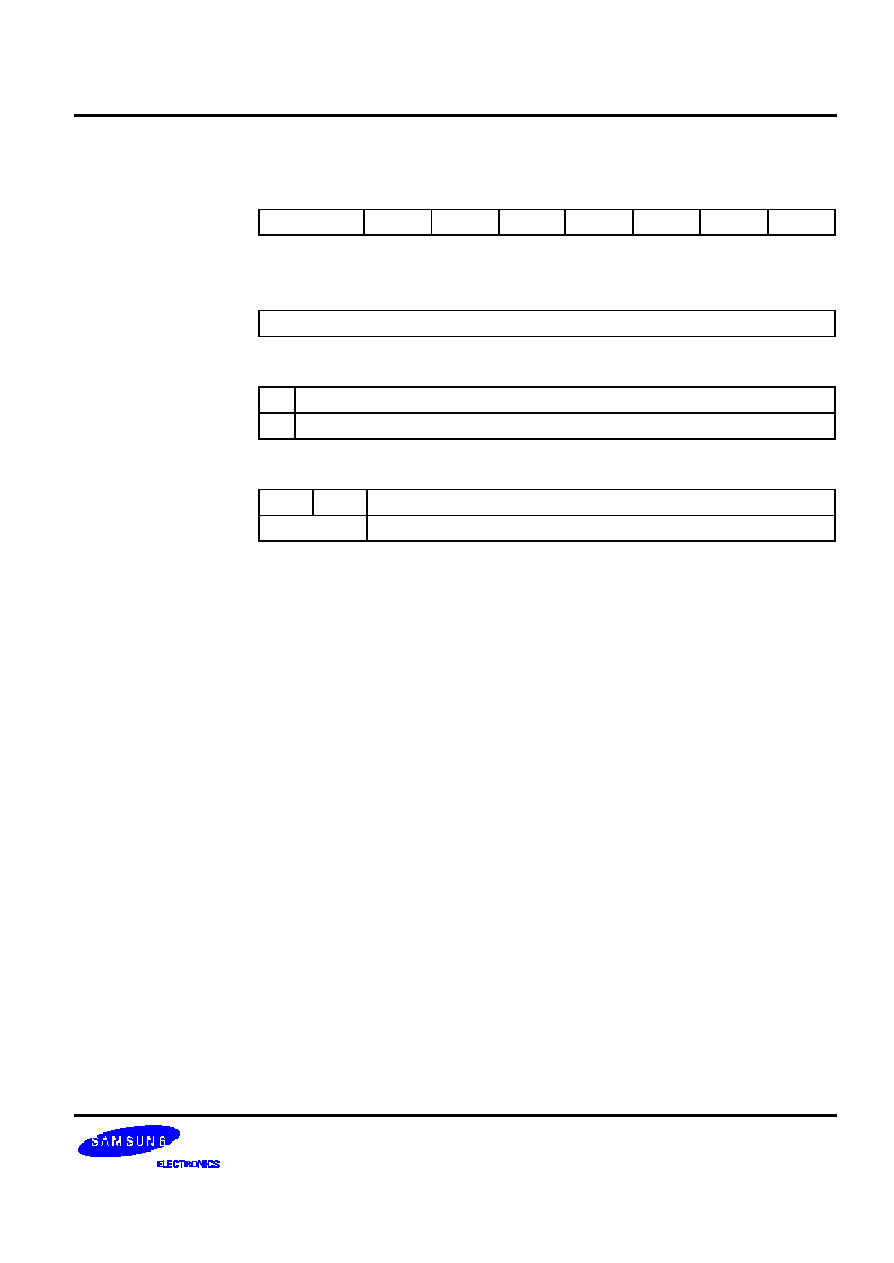

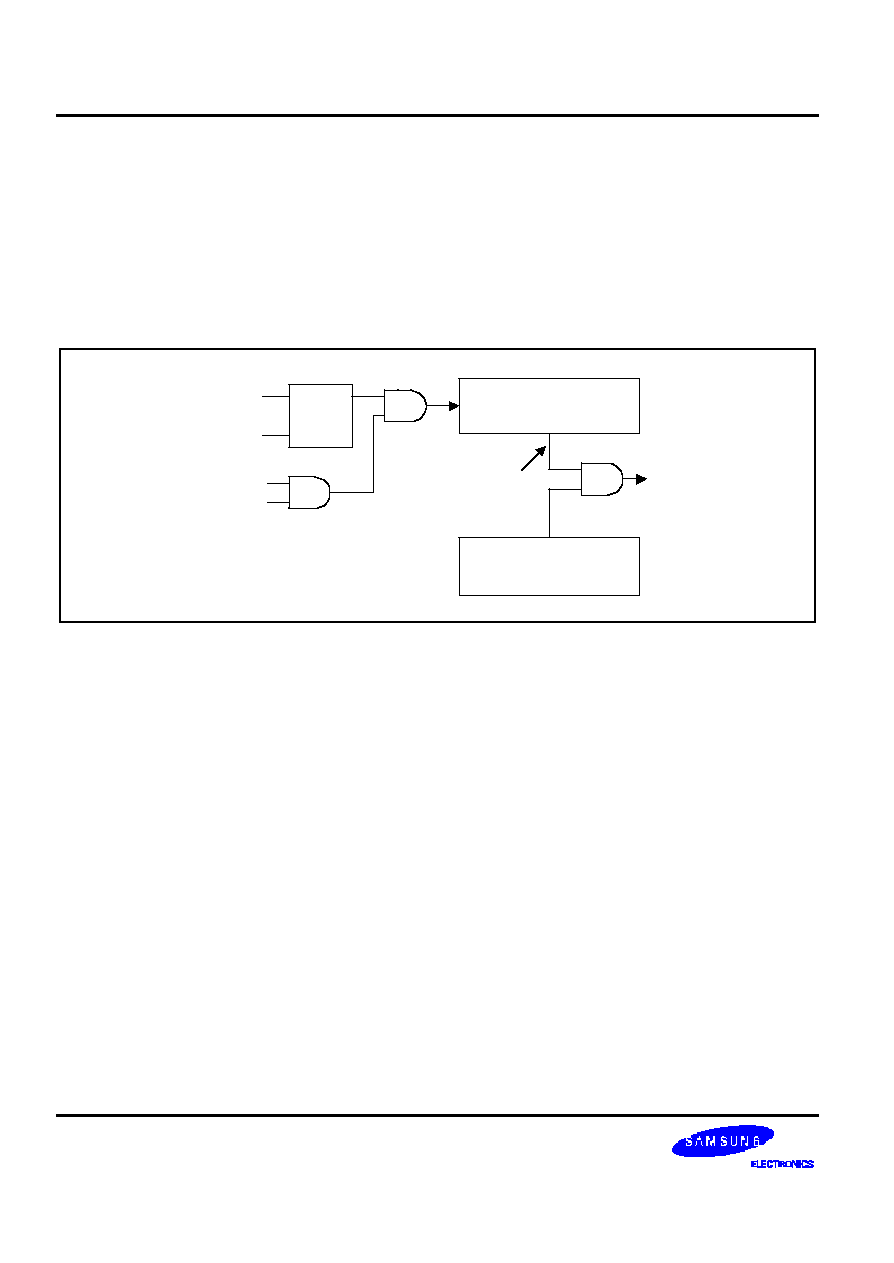

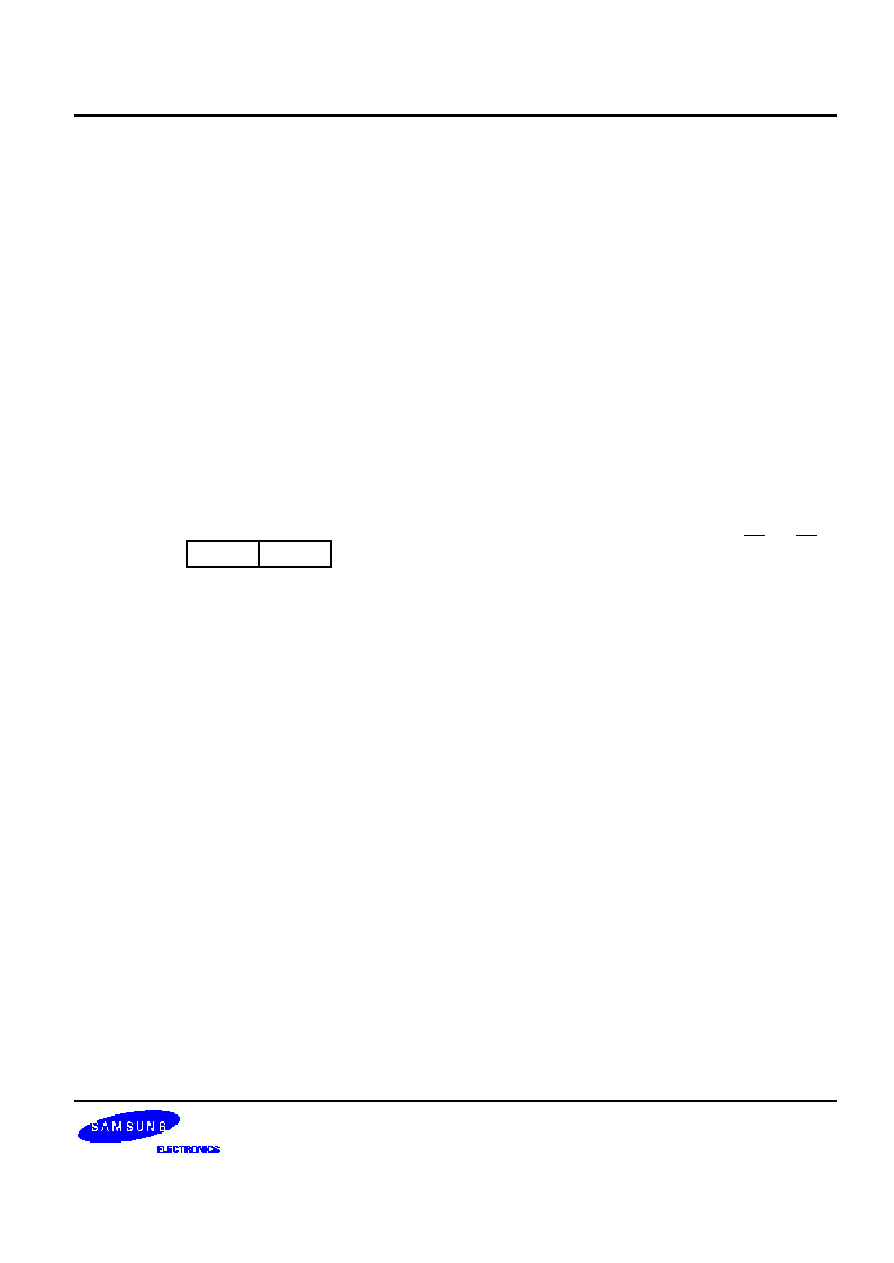

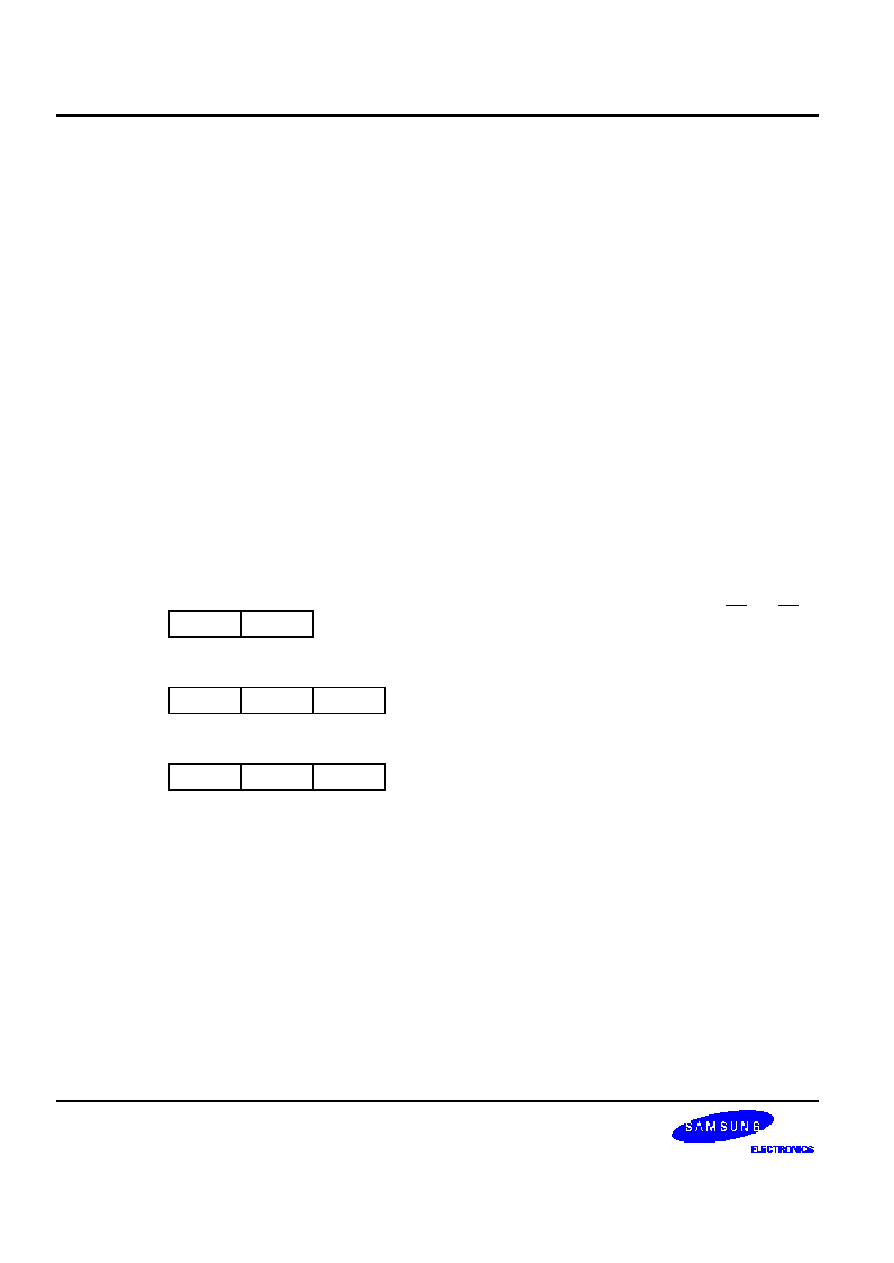

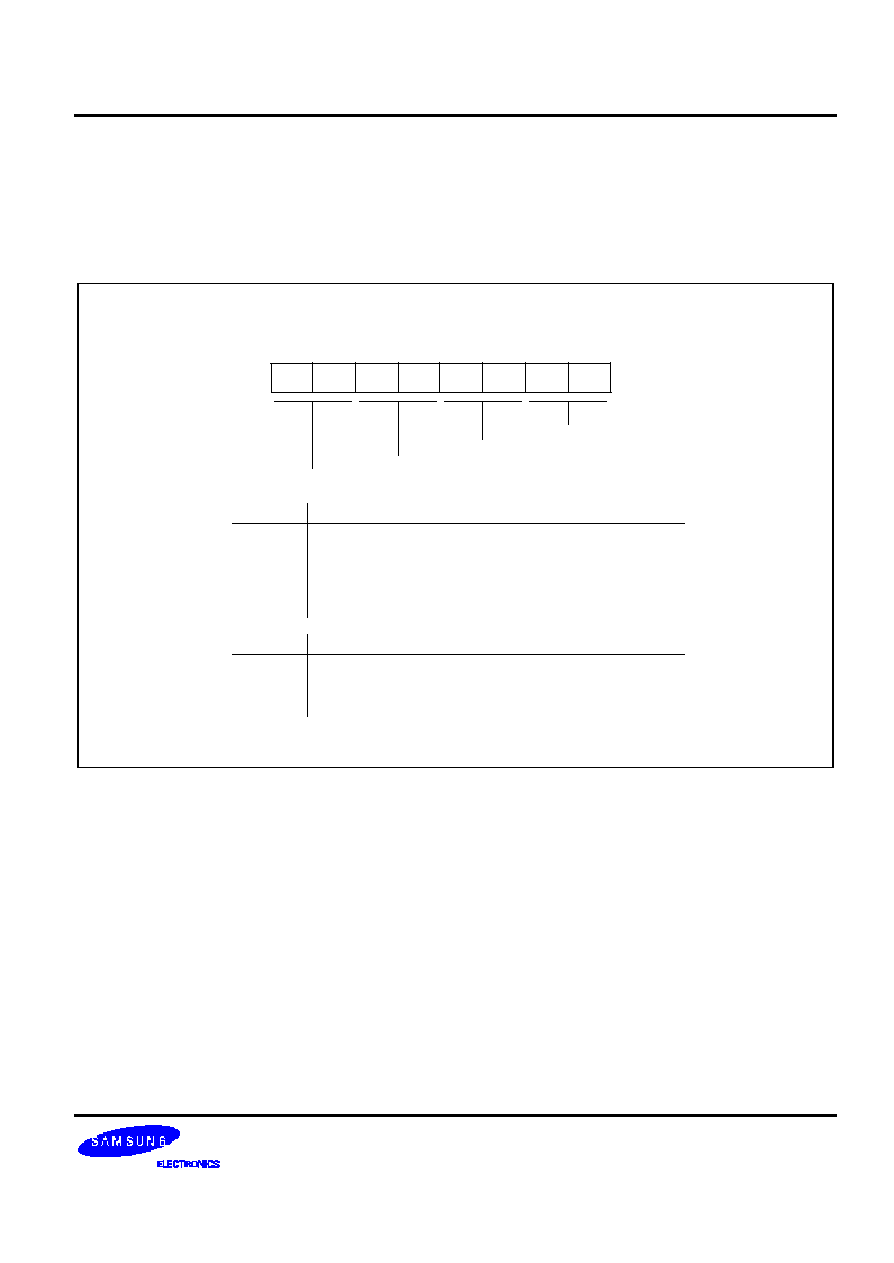

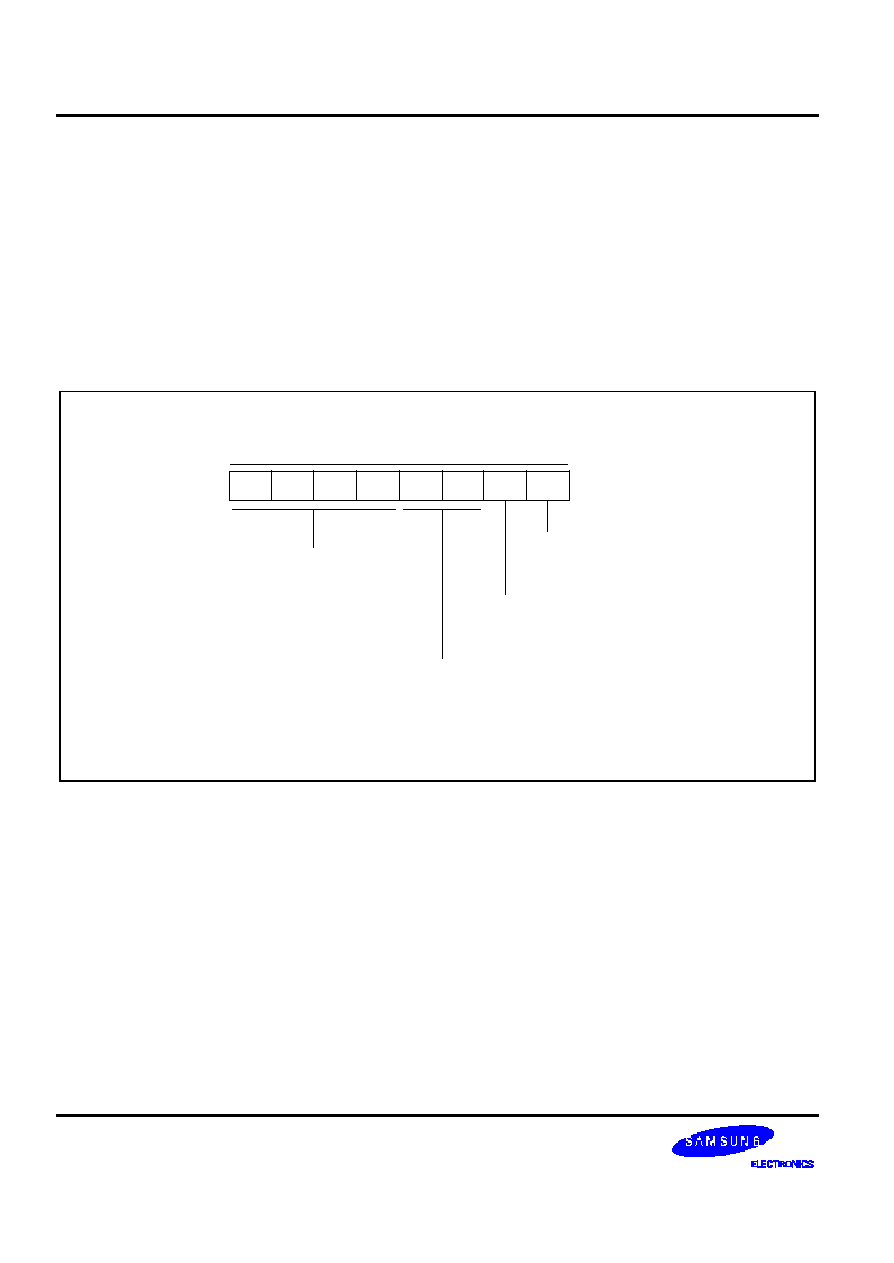

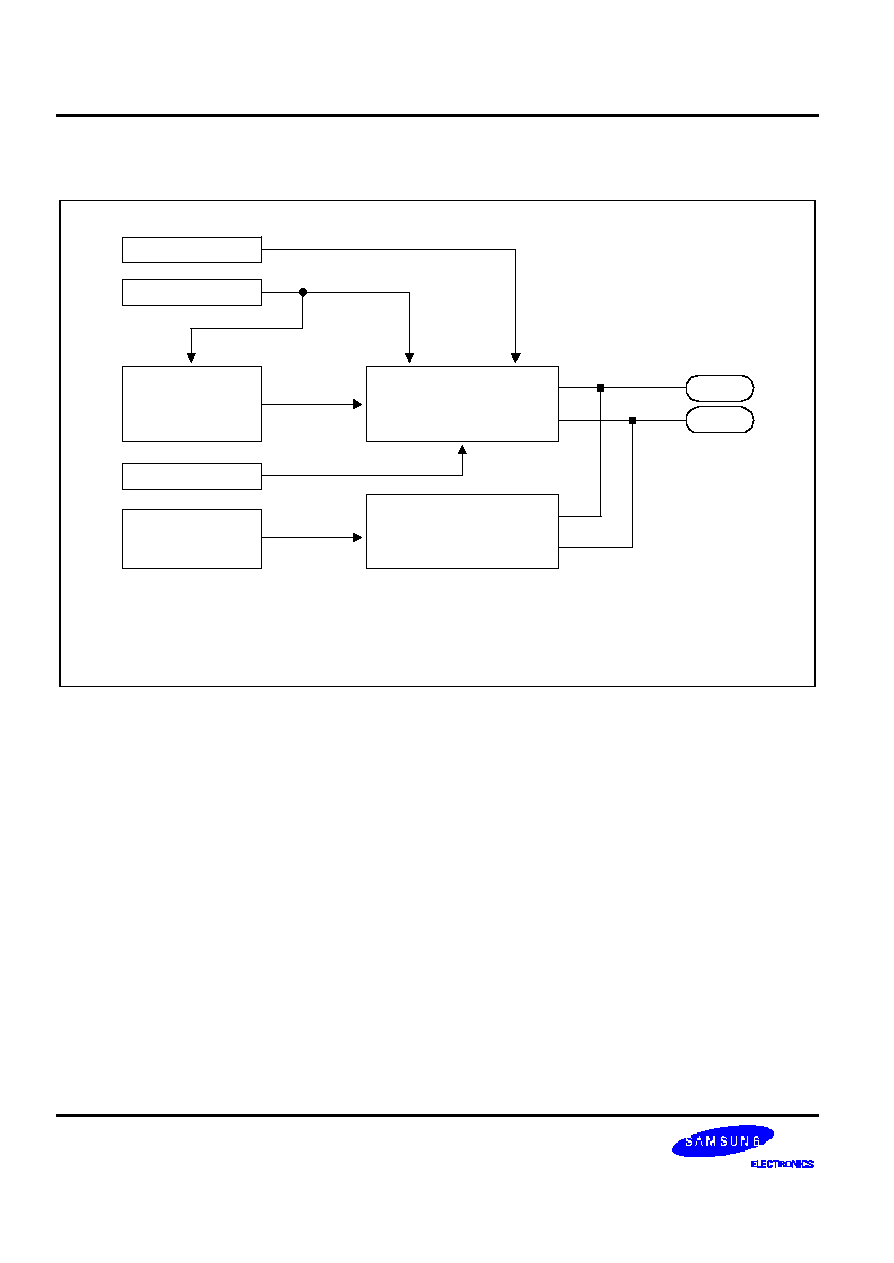

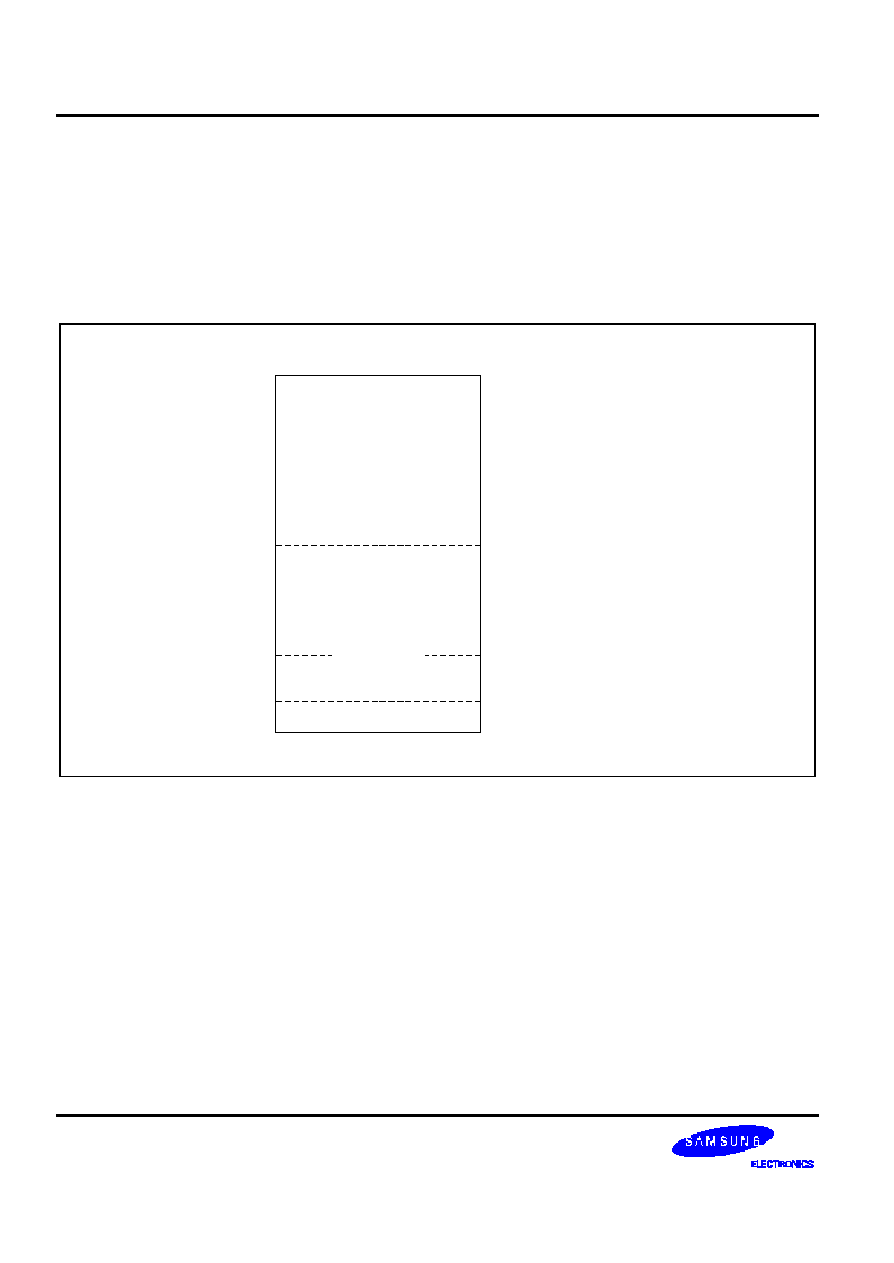

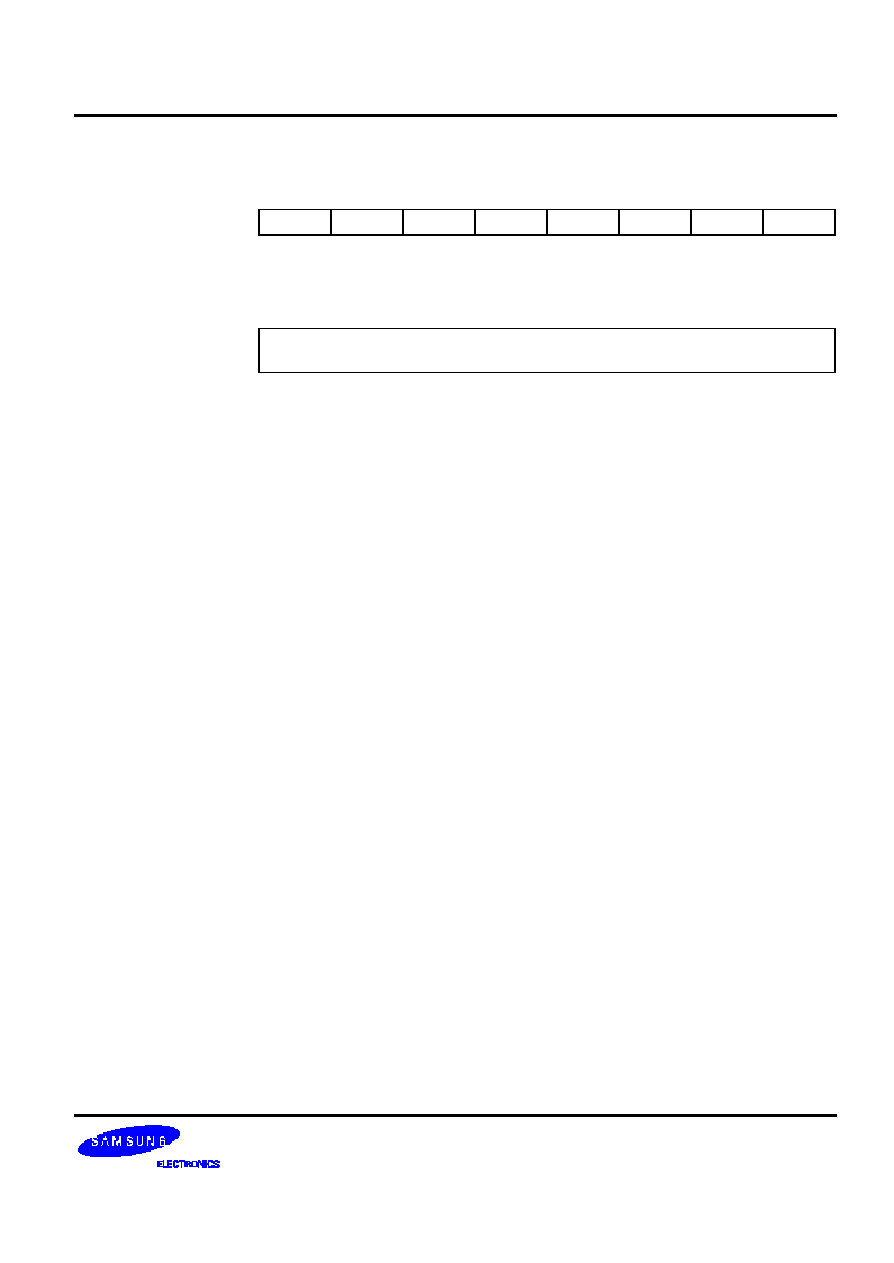

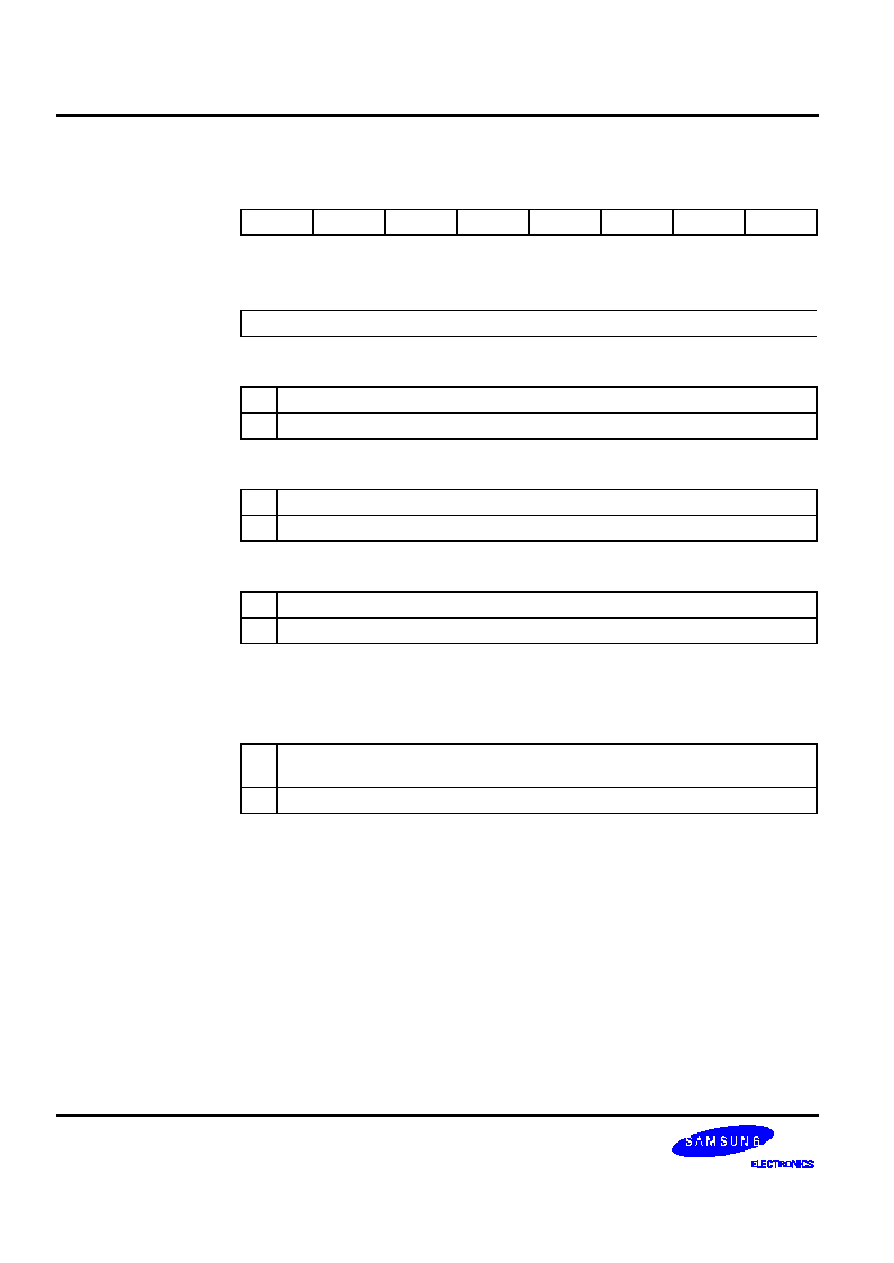

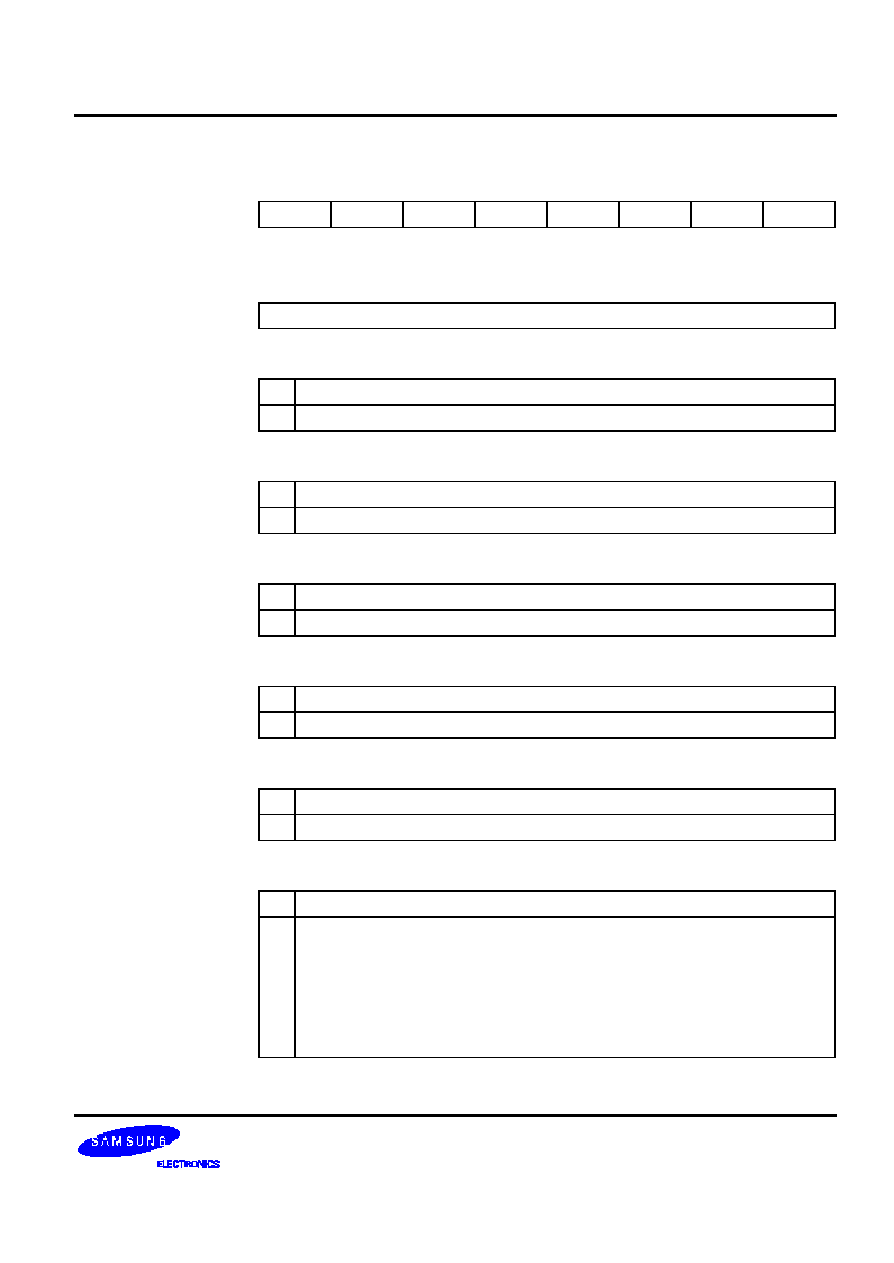

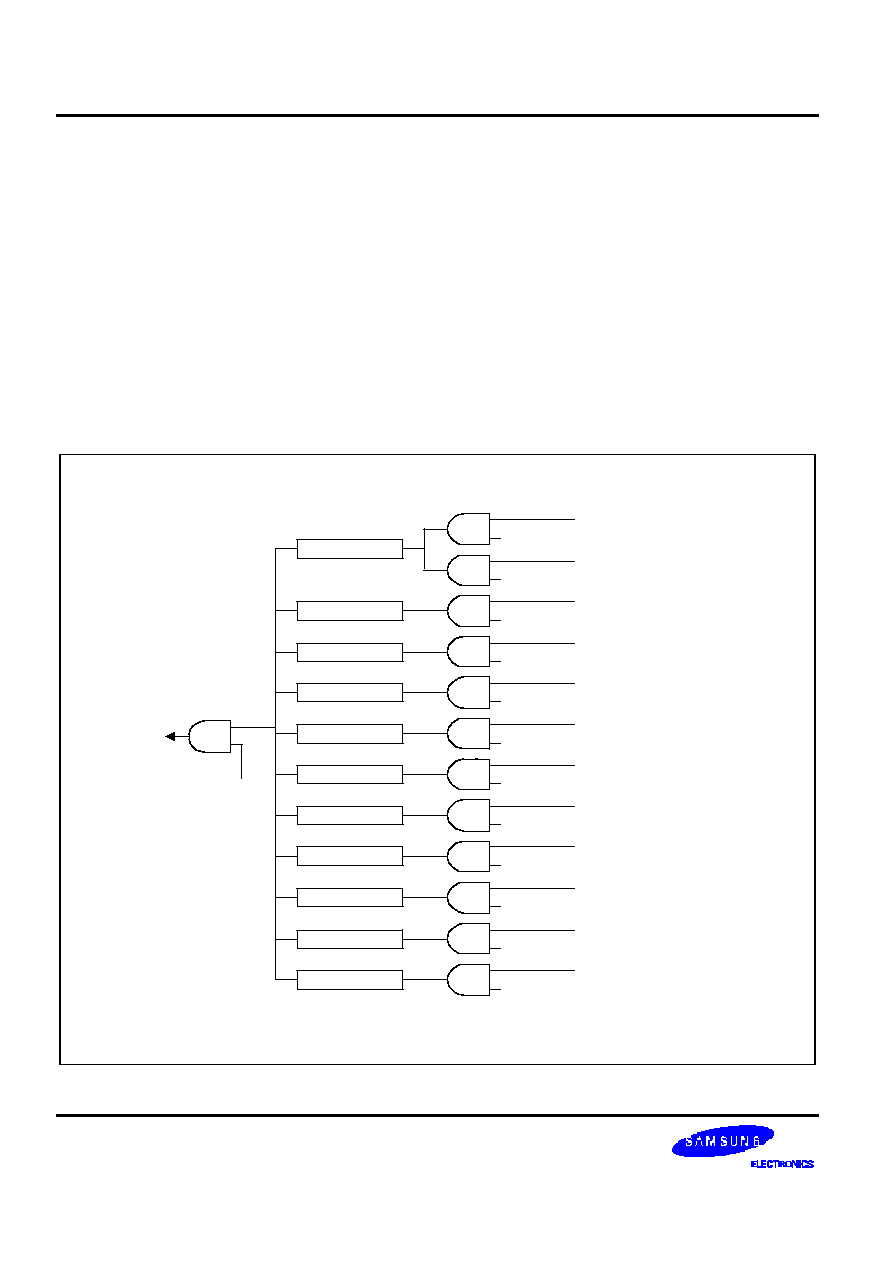

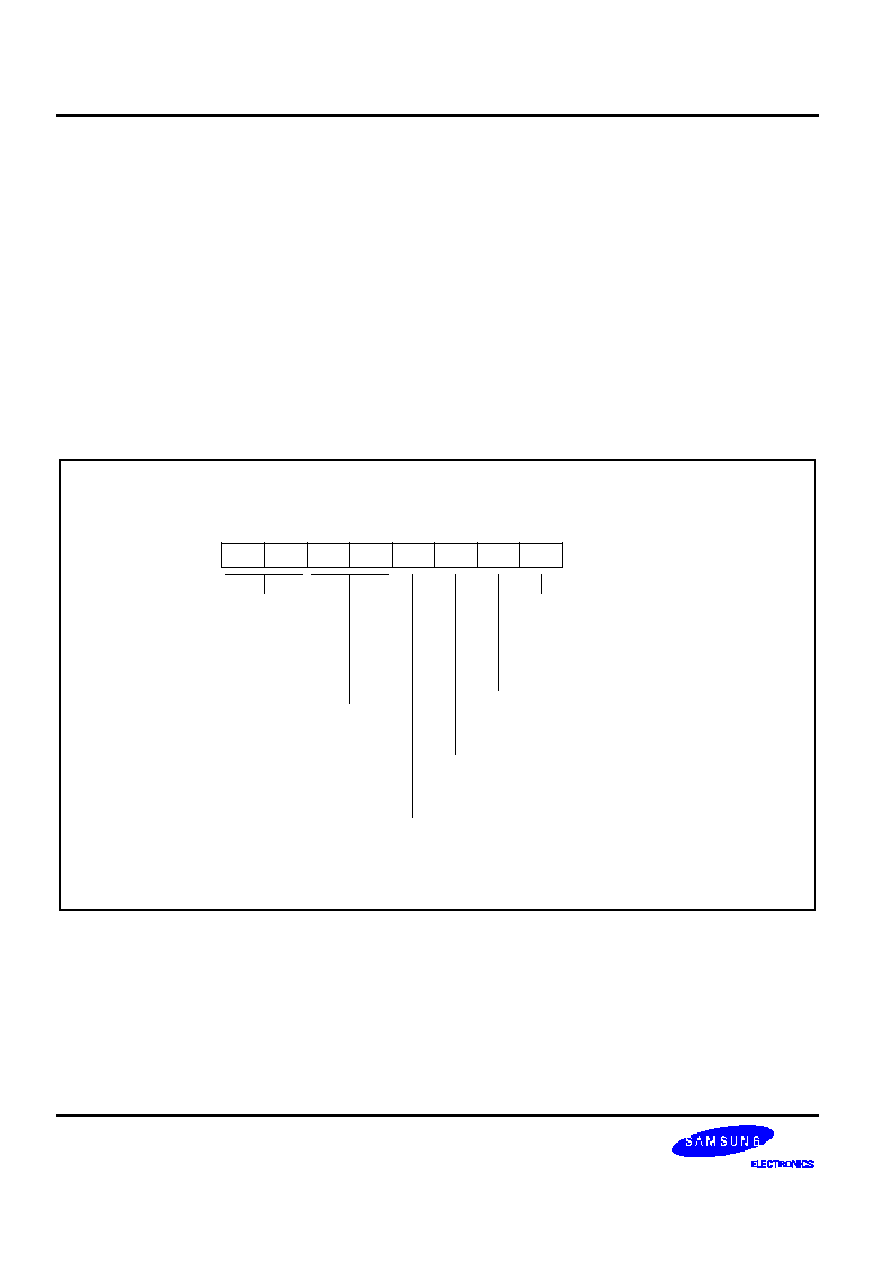

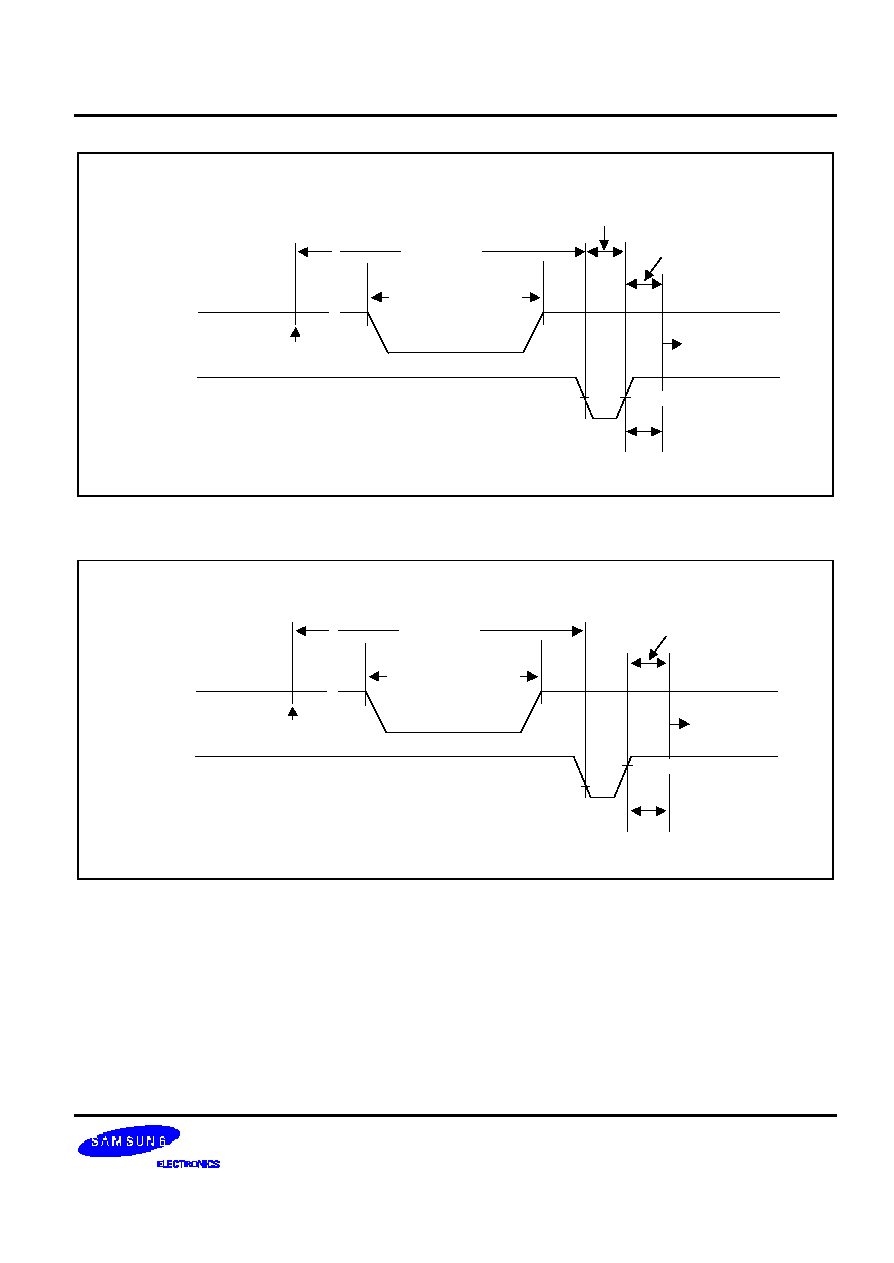

APPLICATION CIRCUIT

5V

Port 0

Port 1

Port 2

RESET

DP

DM

Port 4

D+/PS2

D-/PS2

NOTE:

Port4 can use expend keyboard MATRIX.

D+/PS2, D-/PS2 can use PS2 keyboard interface (see PS2CONINT, page 4-34).

Port 4.2, 4.3 can use PS2 mouse interface.

Port 3 can use LED direct drive.

S3C9688/P9688

Port 3

V

DD

5V

X

IN

X

OUT

V

SS1

H

O

S

T

15

0

1

2

3

0

1

2

3

7

KEYBOARD

MATRIX

Figure 1-8. Keyboard Application Circuit Diagram

PRODUCT OVERVIEW

S3C9688/P9688

1-10

NOTES

S 3 C 9 6 8 8 / P 9 6 8 8

ADDRESS SPACES

2 -1

2

A D D R E S S S P A C E S

O V E R V I E W

T h e S 3 C 9 6 8 8 / P 9 6 8 8 m i c r o c o n t r o l l e r h a s t w o k i n d s o f a d d r e s s s p a c e :

--

P r o g r a m m e m o r y ( R O M ) , i n t e r n a l

--

Internal register file

A 1 3 -b i t a d d r e s s b u s s u p p o r t s b o t h p r o g r a m m e m o r y . A s e p a r a t e 8 -b i t r e g i s t e r b u s c a r r i e s a d d r e s s e s a n d d a t a

between the CPU and the internal register file.

T h e S 3 C 9 6 8 8 h a s 8 K b y t e s o f m a s k -p r o g r a m m a b l e p r o g r a m m e m o r y o n -c h i p . T h e r e i s o n e p r o g r a m m e m o r y

configuration option:

--

I n t e r n a l R O M m o d e , i n w h i c h o n l y t h e 8 K b y t e i n t e r n a l p r o g r a m m e m o r y i s u s e d .

T h e S 3 C 9 6 8 8 / P 9 6 8 8 m i c r o c o n t r o l l e r h a s 2 0 8 g e n e r a l-purpose registers in its internal register file. Twenty -seven

b y t e s i n t h e r e g i s t e r f i l e a r e m a p p e d f o r s y s t e m a n d p e r i p h e r a l c o n t r o l f u n c t i o n s .

ADDRESS SAPCES

S3C9 6 8 8 / P 9 6 8 8

2 -2

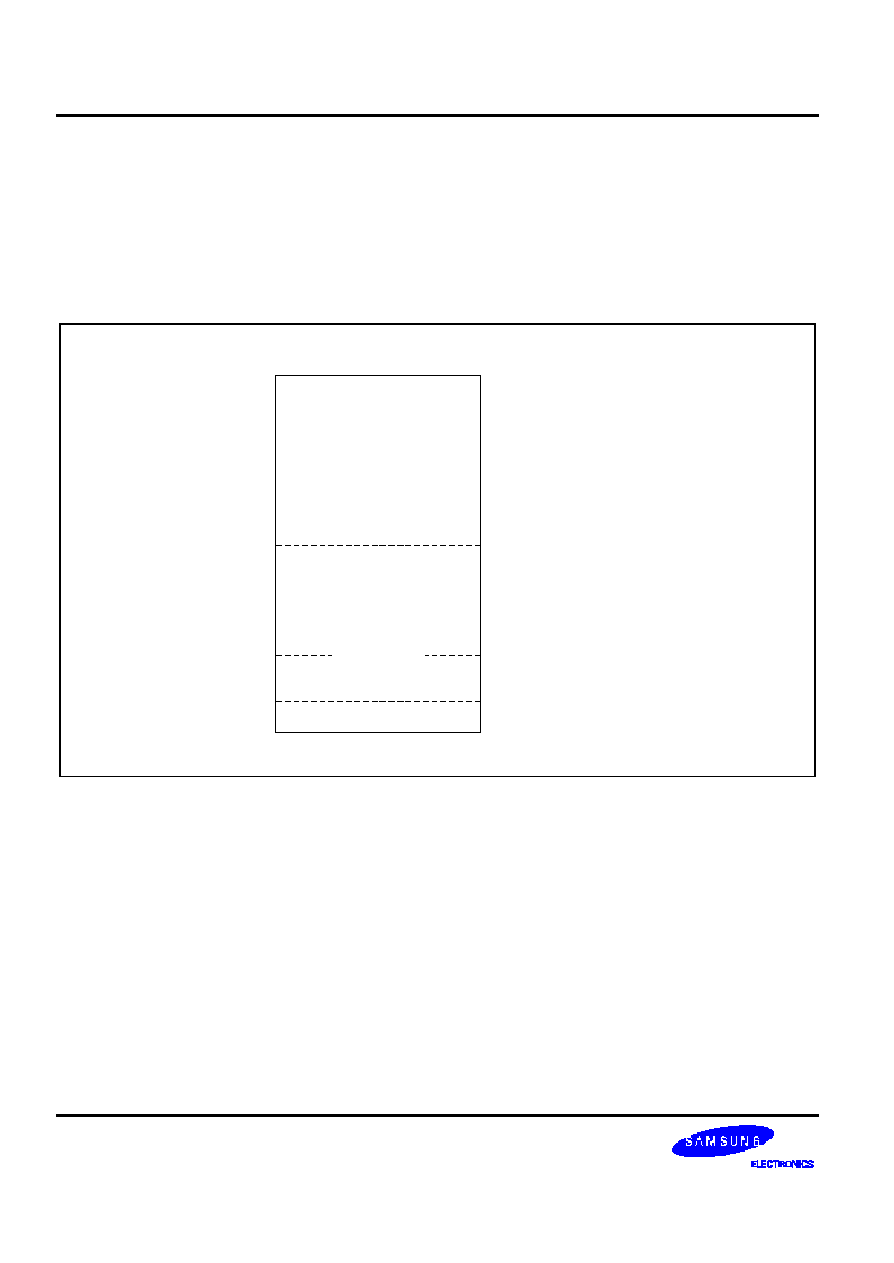

P R O G R A M M E M O R Y ( R O M )

N o r m a l O p e r a t i n g M o d e ( I n t e r n a l R O M )

T h e S 3 C 9 6 8 8 / P 9 6 8 8 h a s 8 K b y t e s ( l o c a t i o n s 0 H ≠ 1 F F F H ) o f i n t e r n a l m a s k -p r o g r a m m a b l e p r o g r a m m e m o r y .

T h e f i r s t 2 b y t e s o f t h e R O M ( 0 0 0 0 H ≠ 0 0 0 1 H ) a r e a n i n t e r r u p t v e c t o r a d d r e s s .

T h e p r o g r a m r e s e t a d d r e s s i n t h e R O M i s 0 1 0 0 H .

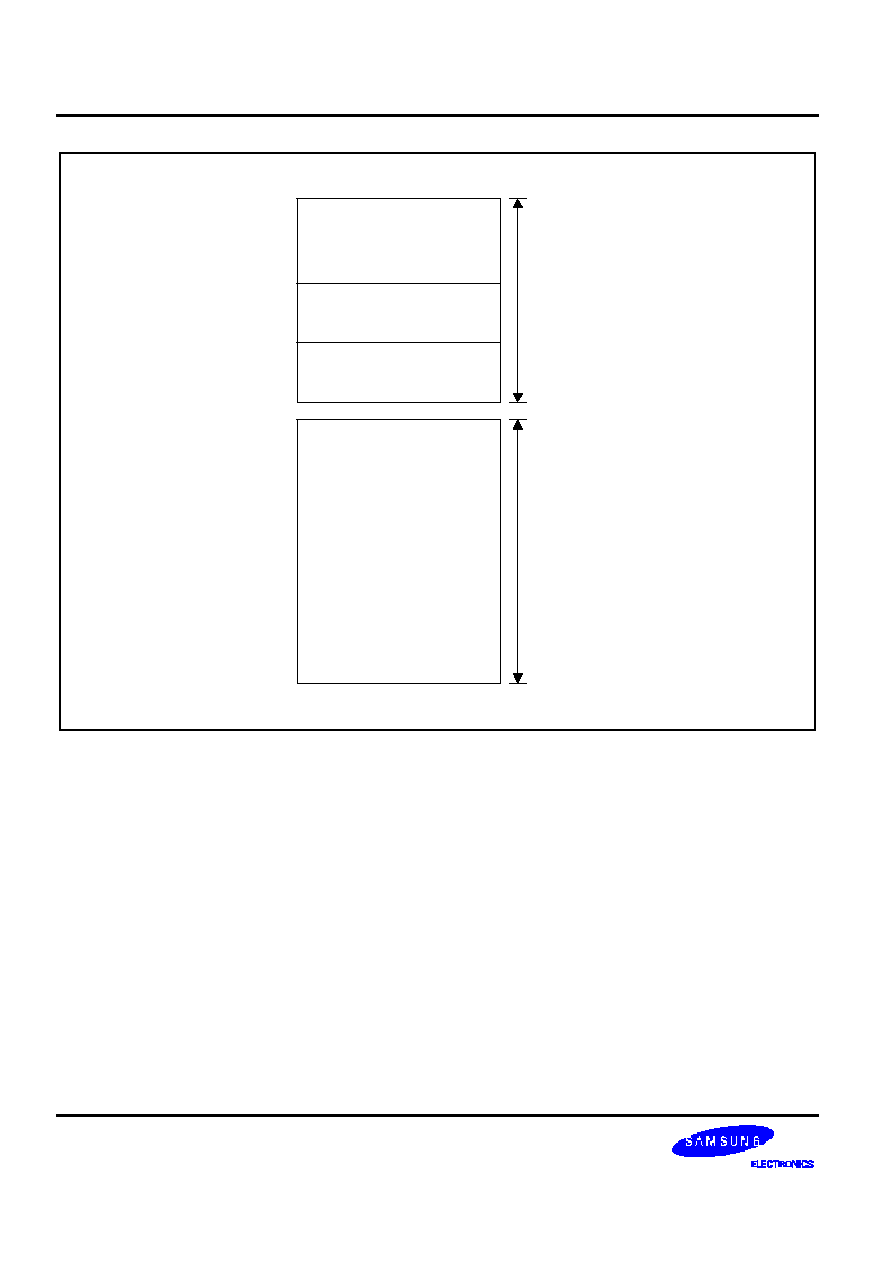

8 K byte Internal

Program Memory

Area

8,191

(DECIMAL)

(HEX)

1FFFH (S3C9688/P9688)

256

2

1

0

0100H

0002H

0001H

0000H

Interrupt Vector

4-Kbyte Internal

Program Memory

Area

4,095

0FFFH

Program Start

F i g u r e 2 -1 . P r o g r a m M e m o r y A d d r e s s S p a c e

S 3 C 9 6 8 8 / P 9 6 8 8

ADDRESS SPACES

2 -3

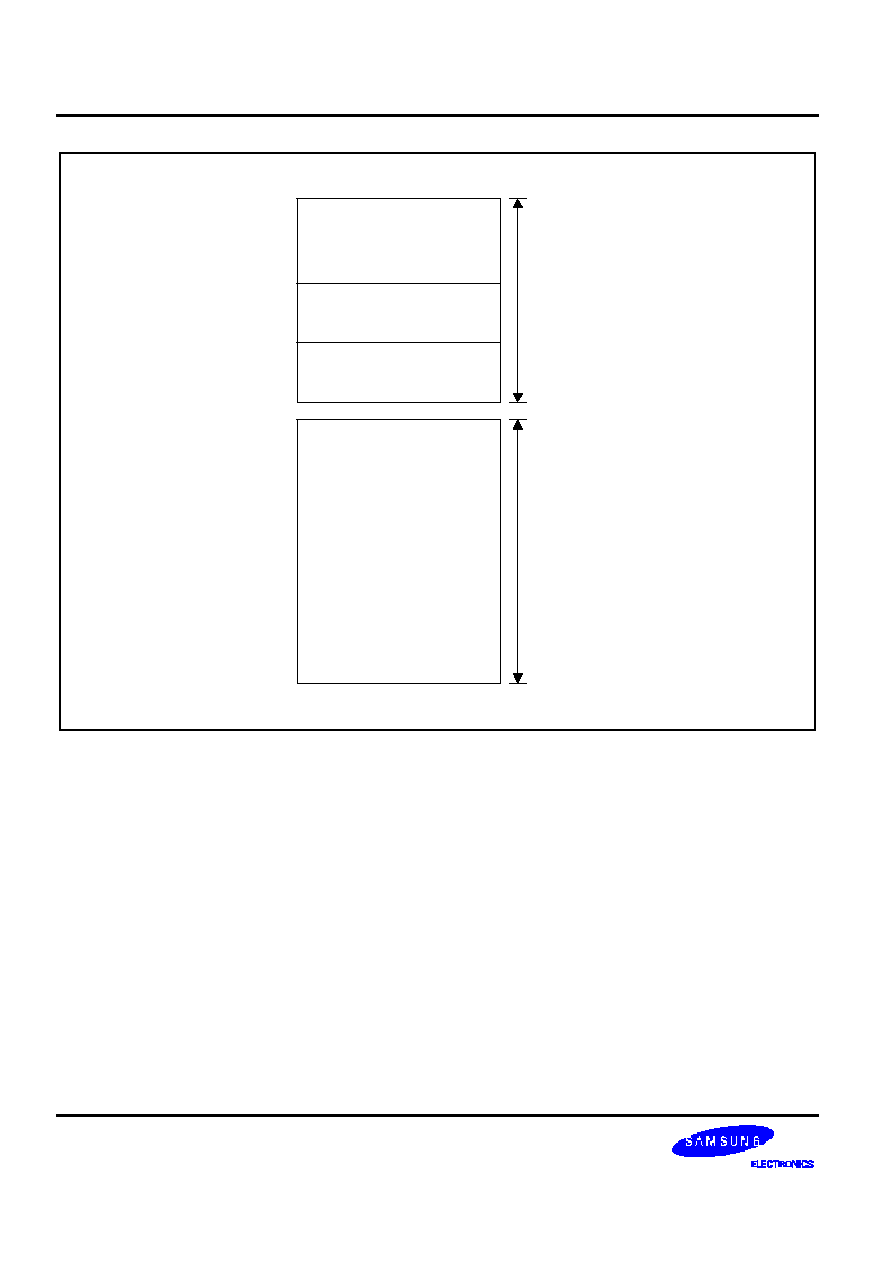

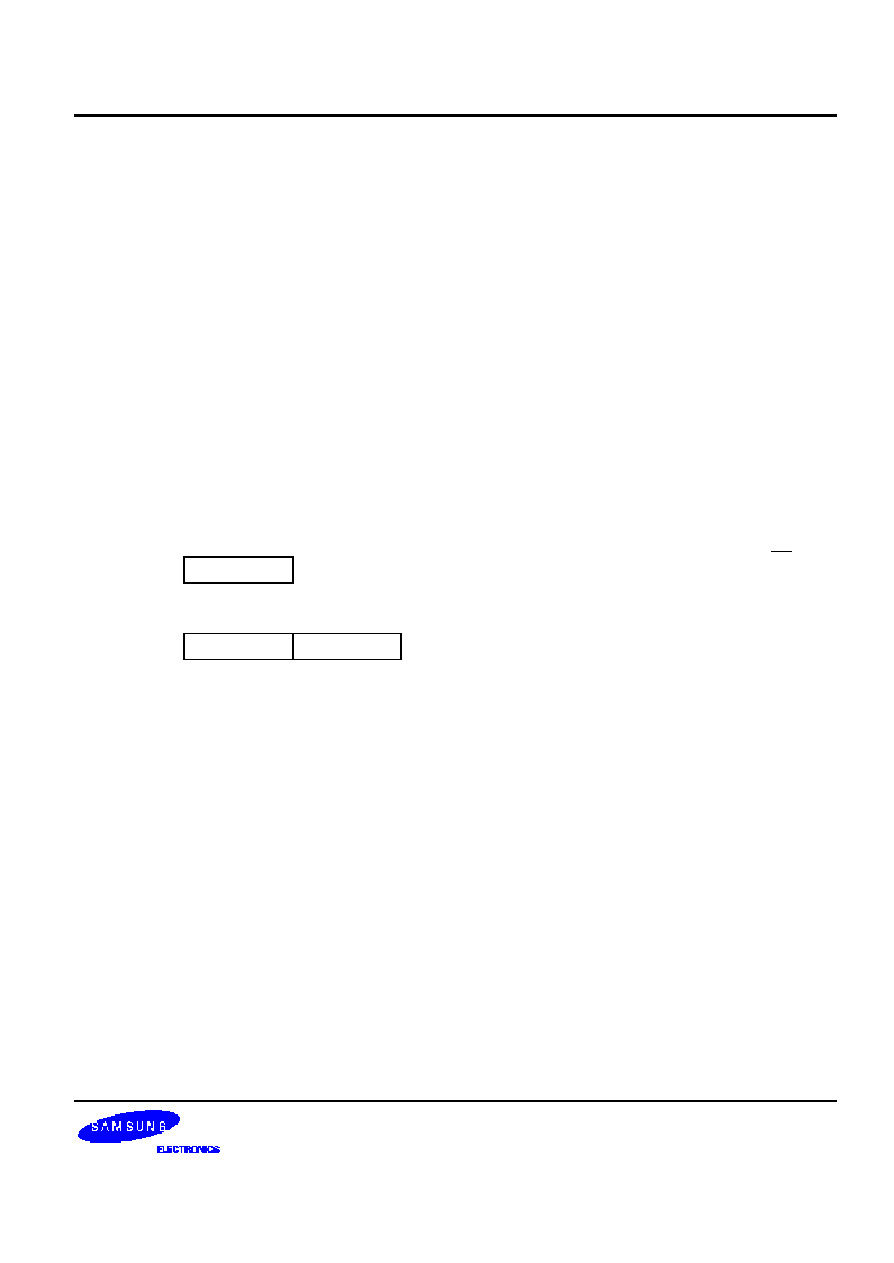

R E G I S T E R A R C H I T E C T U R E

The upper 64 by t e s o f t h e S 3 C 9 6 8 8 / P 9 6 8 8 ' s i n t e r n a l r e g i s t e r f i l e a r e a d d r e s s e d a s w o r k i n g r e g i s t e r s , s y s t e m c o n t r o l

registers and peripheral control registers. The lower 192 bytes of internal register file (00H≠ B F H ) i s c a l l e d t h e g e n e r a l

p u r p o s e r e g i s t e r s p a c e . T h e t o t a l a d d r e s s a b l e r e g i s t e r s p a c e i s t h e r e b y 2 5 6 b y t e s . 2 3 3 r e g i s t e r s i n t h i s s p a c e c a n

b e a c c e s s e d . ; 2 0 8 a r e a v a i l a b l e f o r g e n e r a l-p u r p o s e u s e .

F o r m a n y S A M 8 8 R C R I m i c r o c o n t r o l l e r s , t h e a d d r e s s a b l e a r e a o f t h e i n t e r n a l r e g i s t e r f i l e i s f u r t h e r e x p a n d e d b y t h e

a d d i t i o n a l o f o n e o r m o r e r e g i s t e r p a g e s a t g e n e r a l p u r p o s e r e g i s t e r s p a c e ( 0 0 H ≠ B F H ) . T h i s r e g i s t e r f i l e e x p a n s i o n i s

n o t i m p l e m e n t e d i n t h e S 3 C 9 6 8 8 / P 9 6 8 8 , h o w e v e r . P a g e a d d r e s s i n g i s c o n t r o l l e d b y t h e S y s t e m M o d e R e g i s t e r

( S Y M . 1 ≠ S Y M . 0 ) .

T h e s p e c i f i c r e g i s t e r t y p e s a n d t h e a r e a ( i n b y t e s ) t h a t t h e y o c c u p y i n t h e i n t e r n a l r e g i s t e r f i l e a r e s u m m a r i z e d i n

Table 2-1 .

T a b l e 2 -1 . R e g i s t e r T y p e S u m m a r y

R e g i s t e r T y p e

N u m b e r o f B y t e s

C P U a n d s y s t e m c o n t r o l r e g i s t e r s

1 1

P eripheral, I/O, and clock control and data registers

3 4

G e n e r a l-p u r p o s e r e g i s t e r s ( i n c l u d i n g t h e 1 6 -b i t c o m m o n w o r k i n g r e g i s t e r a r e a )

2 0 8

T o t a l A d d r e s s a b l e B y t e s

2 5 3

ADDRESS SAPCES

S3C9 6 8 8 / P 9 6 8 8

2 -4

Peripheral Control

Register

System Control

Registers

Working Register

General Purpose

Register File

and Stack Area

FFH

E0H

DFH

D0H

CFH

C0H

BFH

00H

64 Bytes of

Common Area

192 Bytes

F i g u r e 2 -2 . I n t e r n a l R e g i s t e r F i l e O r g a n i z a t i o n

S 3 C 9 6 8 8 / P 9 6 8 8

ADDRESS SPACES

2 -5

C O M M O N W O R K I N G R E G I S T E R A R E A ( C 0 H ≠C F H )

T h e S A M 8 8 R C R I r e g i s t e r a r c h i t e c t u r e p r o v i d e s a n e f f i c i e n t m e t h o d o f w o r k i n g r e g i s t e r a d d r e s s i n g t h a t t a k e s f u l l

advantage of shorter instruction form a t s t o r e d u c e e x e c u t i o n t i m e .

T h i s 1 6 -b y t e a d d r e s s r a n g e i s c a l l e d c o m m o n a r e a . T h a t i s , l o c a t i o n s i n t h i s a r e a c a n b e u s e d a s w o r k i n g r e g i s t e r s

b y o p e r a t i o n s t h a t a d d r e s s a n y l o c a t i o n o n a n y p a g e i n t h e r e g i s t e r f i l e . T y p i c a l l y , t h e s e w o r k i n g r e g i s t e r s s e r v e a s

t e m p o r a r y b u f f e r s f o r d a t a o p e r a t i o n s b e t w e e n d i f f e r e n t p a g e s . H o w e v e r , b e c a u s e t h e S 3 C 9 6 8 8 / P 9 6 8 8 u s e s o n l y

p a g e 0 , y o u c a n u s e t h e c o m m o n a r e a f o r a n y i n t e r n a l d a t a o p e r a t i o n .

T h e R e g i s t e r ( R ) a d d r e s s i n g m o d e c a n b e u s e d t o a c c e s s t h i s a r e a

R e g i s te r s a r e a d d r e s s e d e i t h e r a s a s i n g l e 8 -bit register or as a paired 16-bit register. In 16-bit register pairs, the

address of the first 8-b i t r e g i s t e r i s a l w a y s a n e v e n n u m b e r a n d t h e a d d r e s s o f t h e n e x t r e g i s t e r i s a n o d d n u m b e r .

T h e m o s t s i g n i f i c a n t b y t e o f t h e 1 6 -b i t d a t a i s a l w a y s s t o r e d i n t h e e v e n -n u m b e r e d r e g i s t e r ; t h e l e a s t s i g n i f i c a n t b y t e

i s a l w a y s s t o r e d i n t h e n e x t ( + 1 ) o d d -n u m b e r e d r e g i s t e r .

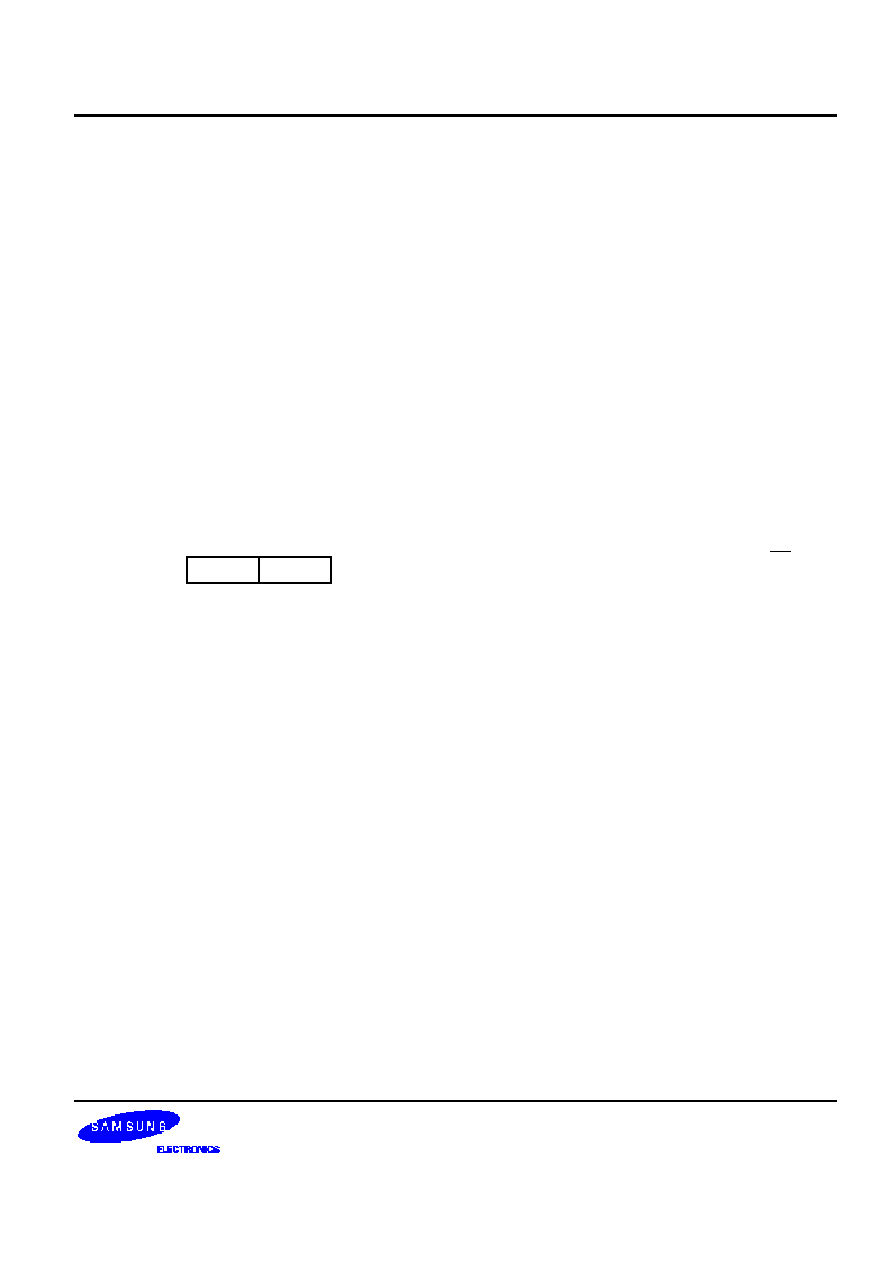

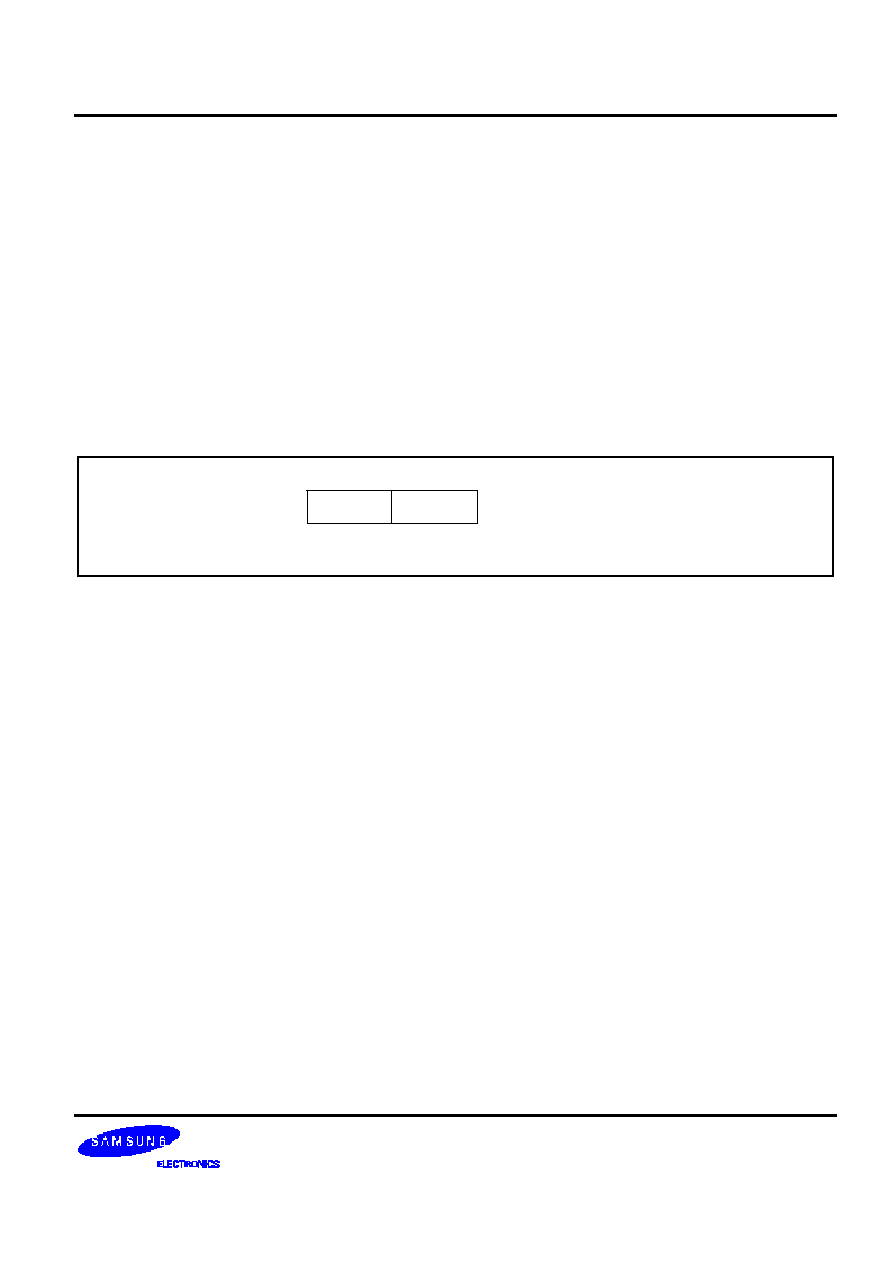

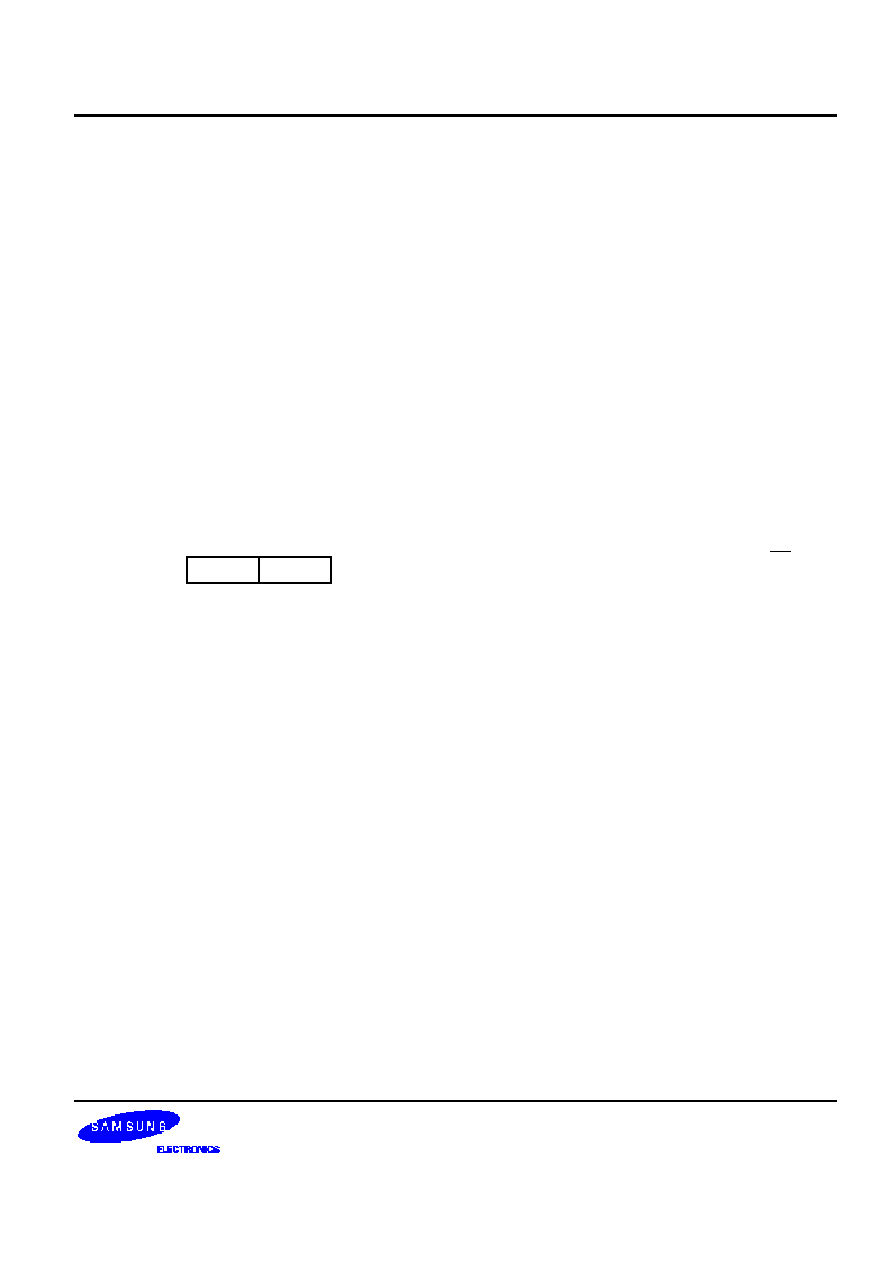

MSB

LSB

Rn

Rn+1

n = Even Address

F i g u r e 2 -3 . 1 6 -B i t R e g i s t e r P a i r s

F

P R O G R A M M I N G T I P -- A d d r e s s i n g t h e C o m m o n W o r k i n g R e g i s t e r A r e a

A s t h e f o l l o w i n g e x a m p l e s s h o w , y o u s h o u l d a c c e s s w o r k i n g r e g i s t e r s i n t h e c o m m o n a r e a , l o c a t i o n s C 0 H ≠ C F H ,

u s i n g w o r k i n g r e g i s t e r a d d r e s s i n g m o d e o n l y .

E x a m p l e s :

1 . L D

0 C 2 H , 4 0 H

; Invalid addressing mode!

U s e w o r k i n g r e g i s t e r a d d r e s s i n g i n s t e a d :

L D

R 2 , 4 0 H

; R 2 ( C 2 H ) ® t h e v a l u e i n l o c a t i o n 4 0 H

2 . A D D

0 C 3 H , # 4 5 H

; Invalid addressing mode!

U s e w o r k i n g r e g is t e r a d d r e s s i n g i n s t e a d :

A D D

R 3 , # 4 5 H

; R 3 ( C 3 H ) ® R 3 + 4 5 H

ADDRESS SAPCES

S3C9 6 8 8 / P 9 6 8 8

2 -6

S Y S T E M S T A C K

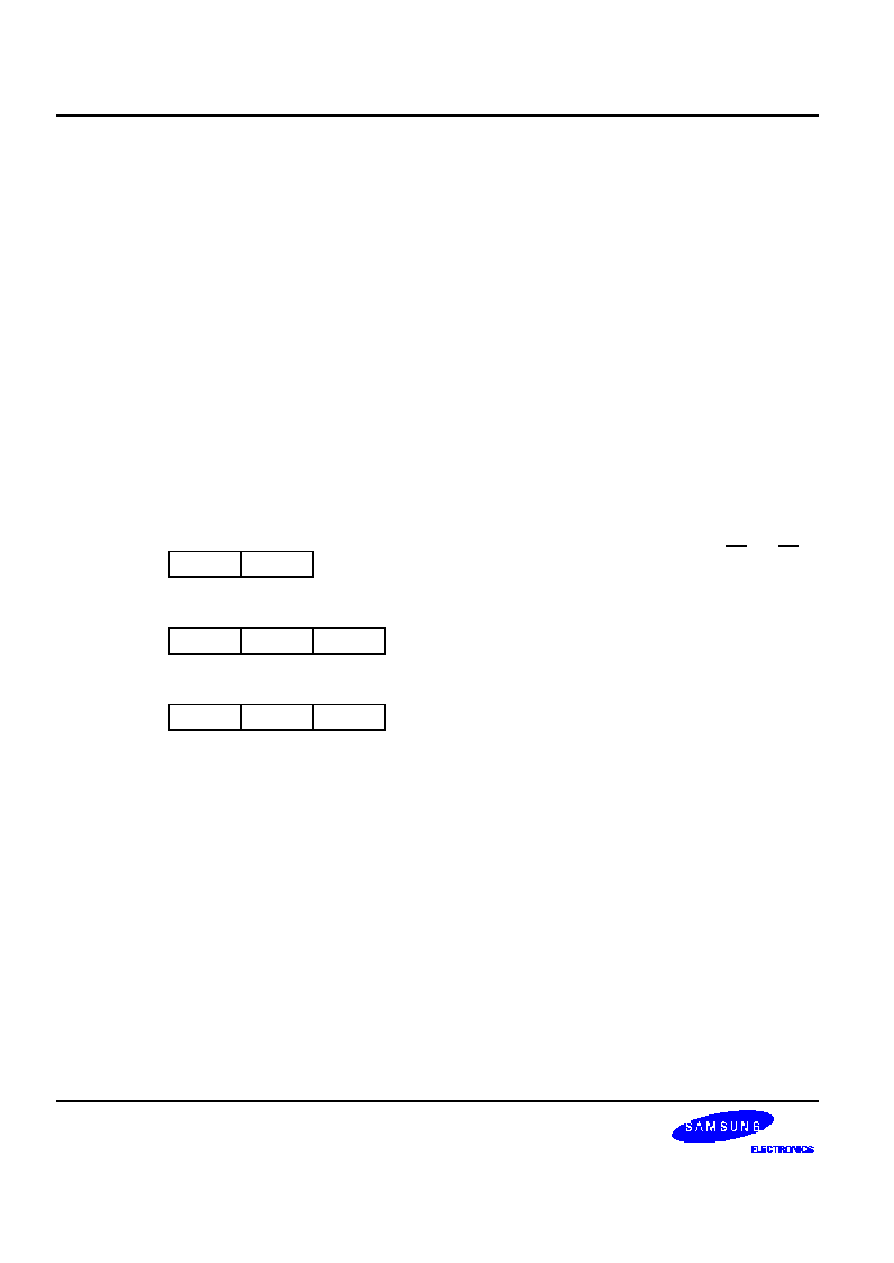

S 3 C 9 -s e r i e s m i c r o c o n t r o l l e r s u s e t h e s y s t e m s t a c k f o r s t o r i n g d a t a i n s u b r o u t i n e c a l l a n d r e t u r n . T h e P U S H a n d

P O P i n s t r u c t i o n s a r e u s e d t o c o n t r o l s y s t e m s t a c k o p e r a t i o n s . T h e S 3 C 9 6 8 8 / P 9 6 8 8 a r c h i t e c t u r e s u p p o r t s s t a c k

operations in the internal register file.

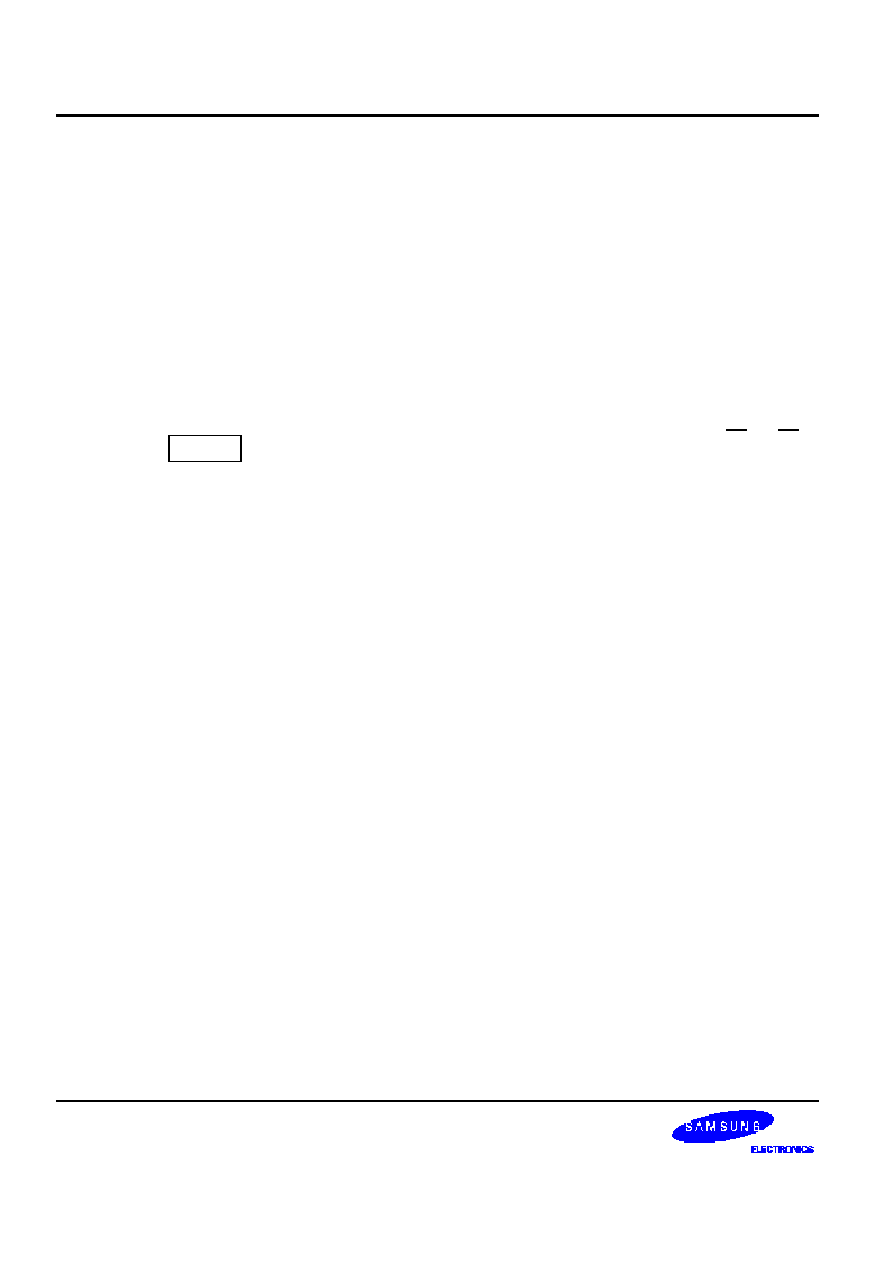

S t a c k O p e r a t i o n s

R e t u r n a d d r e s s e s f o r p r o c e d u r e c a l l s a n d i n t e r r u p t s a n d d a t a a r e s t o r e d o n t h e s t a c k . T h e c o n t e n t s o f t h e P C a r e

s a v e d t o s t a c k b y a C A L L i n s t r u c t i o n a n d r e s t o r e d b y t h e R E T i n s t r u c t i o n . W h e n a n i n t e r r u p t o c c u r s , t h e c o n t e n t s o f

t h e P C a n d t h e F L A G S r e g i s t e r a r e p u s h e d t o t h e s t a c k . T h e I R E T i n s t r u c t i o n t h e n p o p s t h e s e v a l u e s b a c k t o t h e i r

o r i g i n a l l o c a t i o n s . T h e s t a c k a d d r e s s i s a l w a y s d e c r e m e n t e d b e f o r e a p u s h o p e r a t i o n a n d i n c r e m e n t e d a f t e r a p o p

o p e r a t i o n . T h e s t a c k p o i n t e r ( S P ) a l w a y s p o i n t s t o t h e s t a c k f r a m e s t o r e d o n t h e t o p o f t h e s t a c k , a s s h o w n i n F i g u r e

2 -4 .

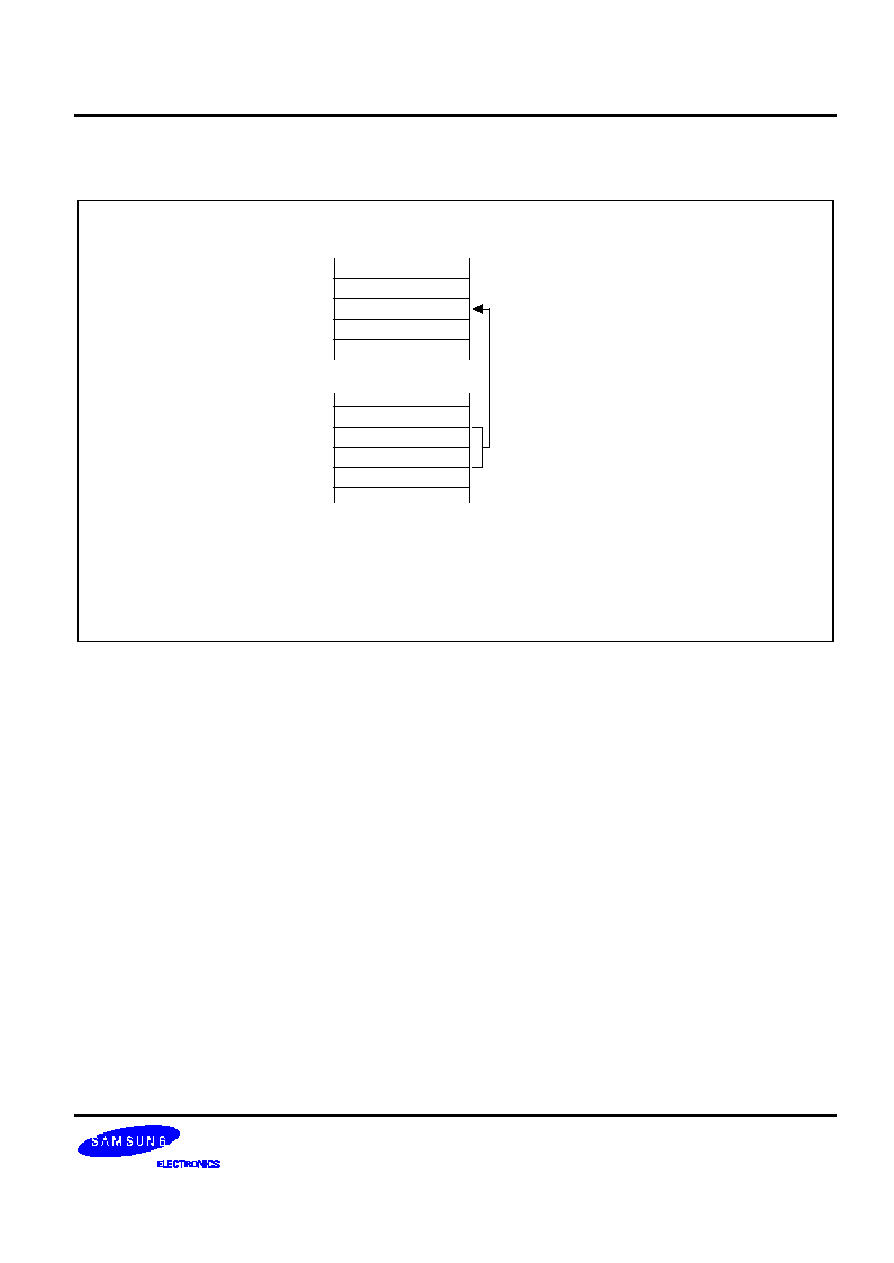

PCL

PCH

Top of

Stack

Stack Contents

After a Call

Instruction

PCL

PCH

FLAGS

Top of

Stack

High Address

Low Address

Stack Contents

After an

Interrupt

F i g u r e 2 -4 . S t a c k O p e r a t i o n s

S t a c k P o i n t e r ( S P )

R e g i s t e r l o c a t i o n D 9 H c o n t a i n s t h e 8 -b i t s t a c k p o i n t e r ( S P ) t h a t i s u s e d f o r s y s t e m s t a c k o p e r a t i o n s . A f t e r a r e s e t ,

t h e S P v a l u e i s u n d e t e r m i n e d .

B e c a u s e o n l y i n t e r n a l m e m o r y s p a c e i s i m p l e m e n t e d i n t h e S 3 C 9 6 8 8 / P 9 6 8 8 , t h e S P m u s t b e i n i t i a l i z e d t o a n 8 -bit

value in the range 00H≠ B F H .

N O T E

I n c a s e a S t a c k P o i n t e r i s i n i t i a l i z e d t o 0 0 H , i t i s d e c r e a s e d t o F F H w h e n s t a c k o p e r a t i o n s t a r t s . T h i s m e a n s

t h a t a S t a c k P o i n t e r a c c e s s i n v a l i d s t a c k a r e a .

S 3 C 9 6 8 8 / P 9 6 8 8

ADDRESS SPACES

2 -7

F

P R O G R A M M I N G T I P -- S t a n d a r d S t a c k O p e r a t i o n s U s i n g P U S H a n d P O P

T h e f o l l o w i n g e x a m p l e s h o w s y o u h o w t o p e r f o r m s t a c k o p e r a t i o n s i n t h e i n t e r n a l r e g i s t e r f i l e u s i n g P U S H a n d P O P

i n s t r u c t i o n s :

L D

S P , # 0 C 0 H

; S P ® C 0 H ( N o r m a l l y , t h e S P i s s e t t o 0 C 0 H b y t h e

; initialization routine)

∑

∑

∑

P U S H

S Y M

; S t a c k a d d r e s s 0 B F H ® S Y M

P U S H

C L K C O N

; S t a c k a d d r e s s 0 B E H ® C L K CO N

P U S H

2 0 H

; S t a c k a d d r e s s 0 B D H ® 2 0 H

P U S H

R 3

; S t a c k a d d r e s s 0 B C H ® R 3

∑

∑

∑

P O P

R 3

; R 3 ® S t a c k a d d r e s s 0 B C H

P O P

2 0 H

; 2 0 H ® S t a c k a d d r e s s 0 B D H

P O P

C L K C O N

; C L K C O N ® S t a c k a d d r e s s 0 B E H

P O P

S Y M

; S Y M ® S t a c k a d d r e s s 0 B F H

ADDRESS SAPCES

S3C9 6 8 8 / P 9 6 8 8

2 -8

N O T E S

S 3 C 9 6 8 8 / P 9 6 8 8

ADDRESSING MODES

3 -1

3

A D D R E S S I N G M O D E S

O V E R V I E W

I n s t r u c t i o n s t h a t a r e s t o r e d i n p r o g r a m m e m o r y a r e f e t c h e d f o r e x e c u t i o n u s i n g t h e p r o g r a m c o u n t e r . I n s t r u c t i o n s

i n d i c a t e t h e o p e r a t i o n t o b e p e r f o r m e d a n d t h e d a t a t o b e o p e r a t e d o n . A d d r e s s i n g m o d e i s t h e m e t h o d u s e d t o

d e t e r m i n e t h e l o c a t i o n o f t h e d a t a o p e r a n d . T h e o p e r a n d s s p e c i f i e d i n S A M 8 8 R C R I i n s t r u c t i o n s m a y b e c o n d i t i o n

c o d e s , i m m e d i a t e d a t a , o r a l o c a t i o n i n t h e r e g i s t e r f i l e , p r o g r a m m e m o r y , o r d a t a m e m o r y .

T h e S A M 8 8 R C R I i n s t r u c t i o n s e t s u p p o r t s s i x e x p l i c i t a d d r e s s i n g m o d e s . N o t a l l o f t h e s e a d d r e s s i n g m o d e s a r e

a v a i l a b l e f o r e a c h i n s t r u c t i o n . T h e a d d r e s s i n g m o d e s a n d t h e i r s y m b o l s a r e a s f o l l o w s :

--

R e g i s t e r ( R )

--

Indirect Register (IR)

--

Indexed (X)

--

D i r e c t A d d r e s s ( D A )

--

R e l a t i v e A d d r e s s ( R A )

--

I m m e d i a t e ( I M )

ADDRESSING MODES

S 3 C 9 6 8 8 / P 9 6 8 8

3 -2

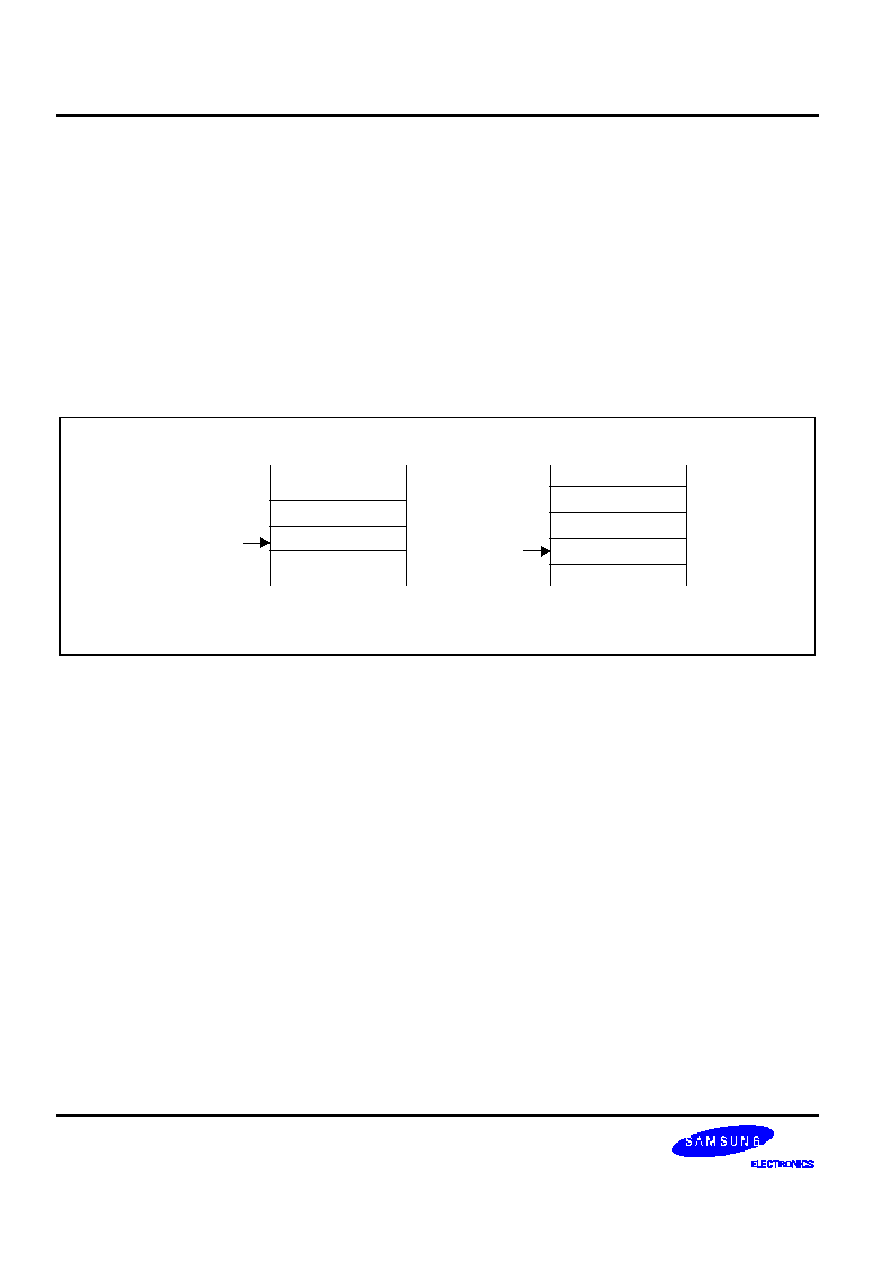

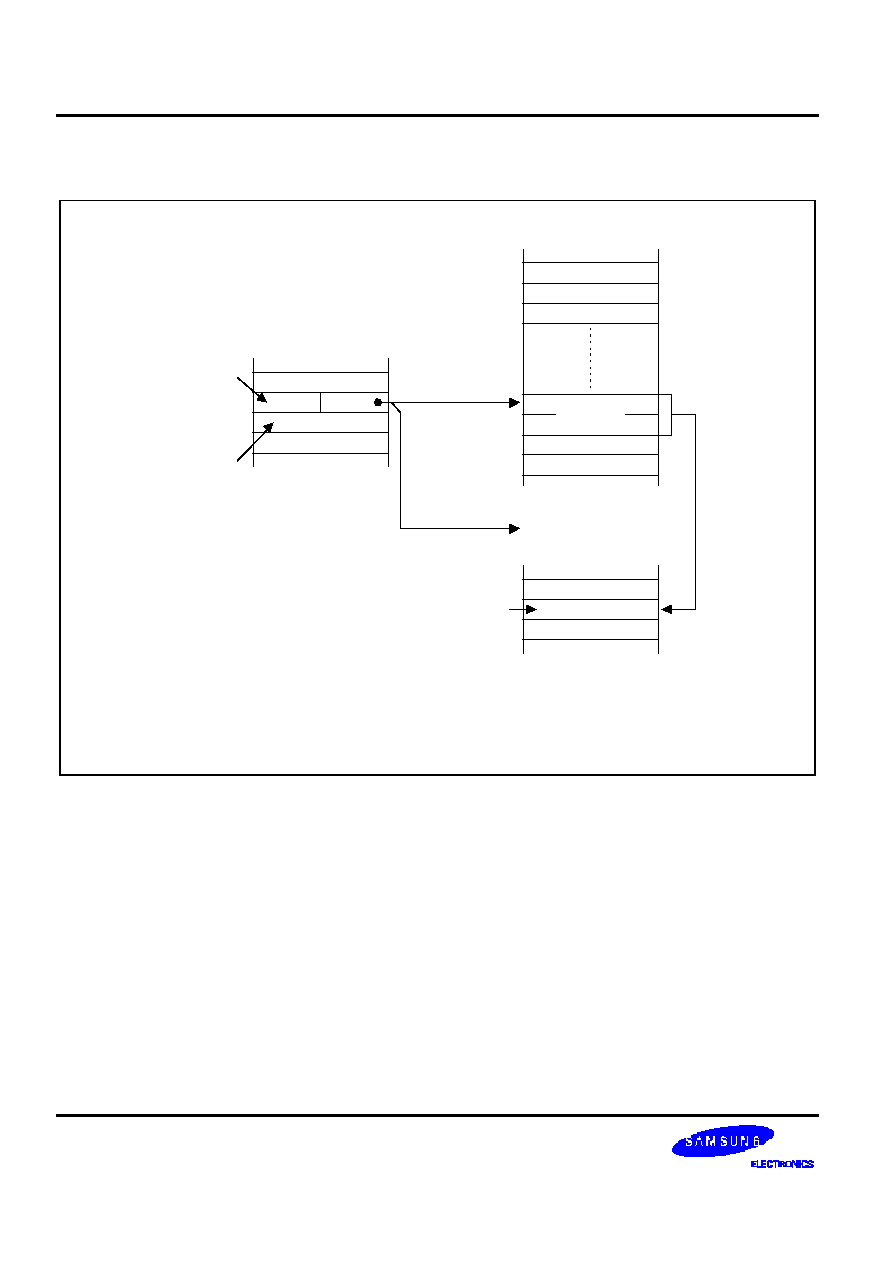

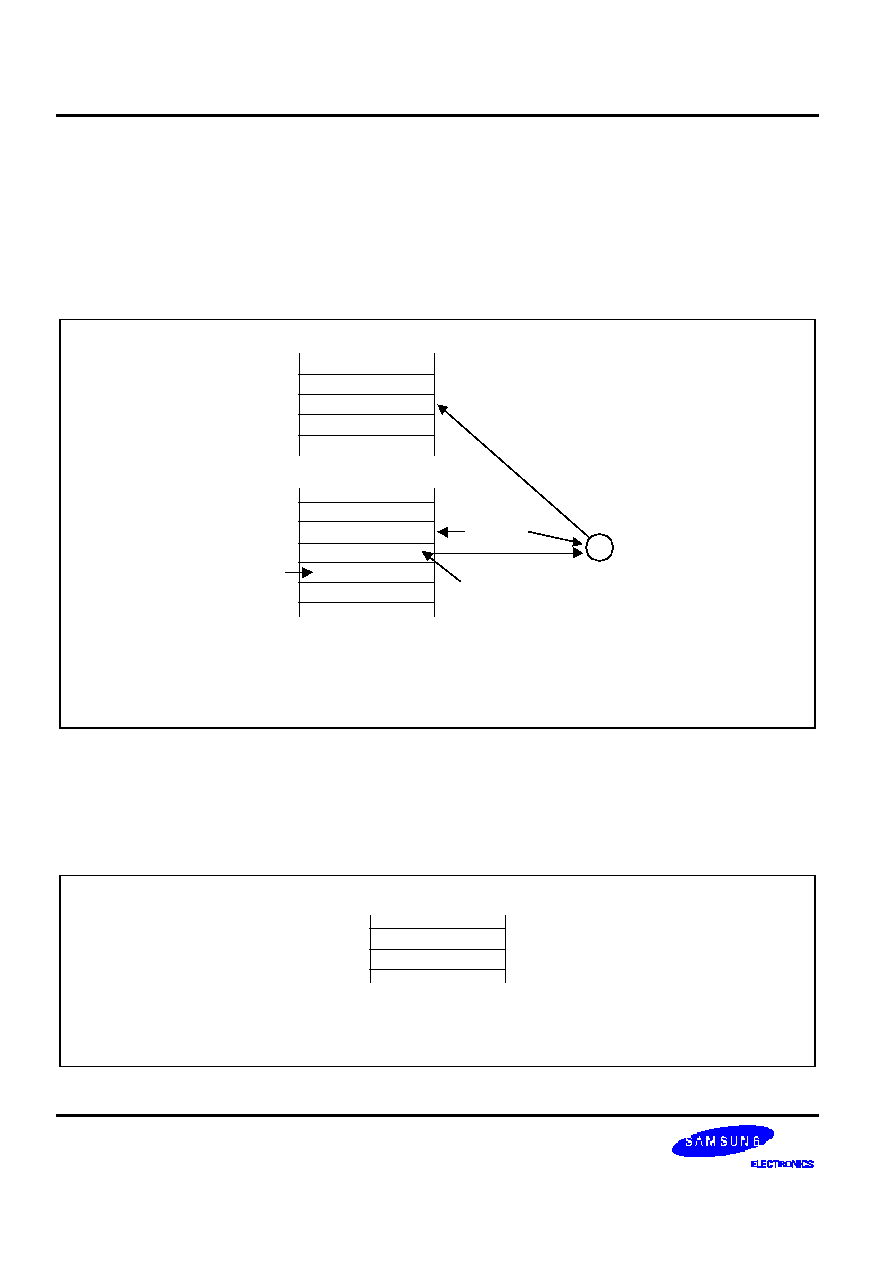

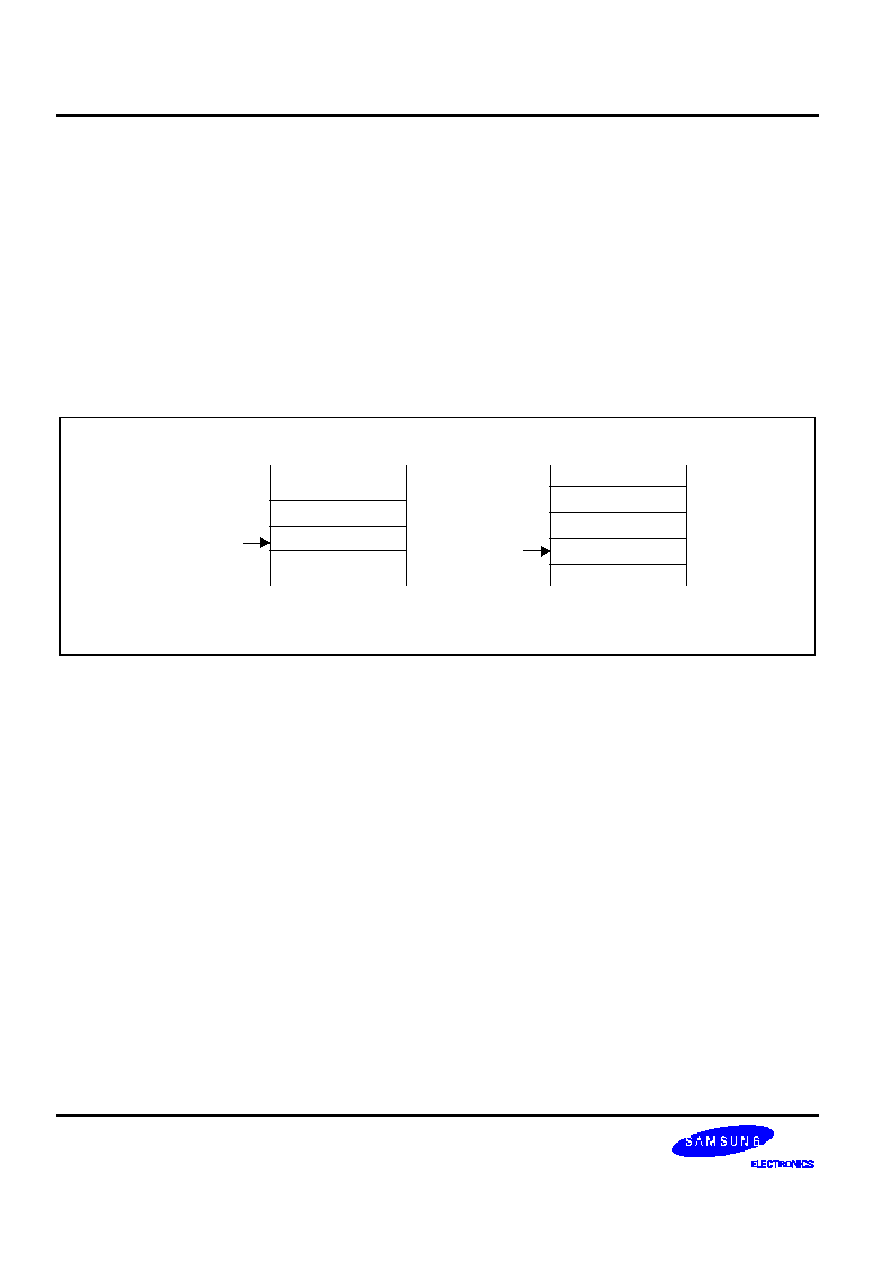

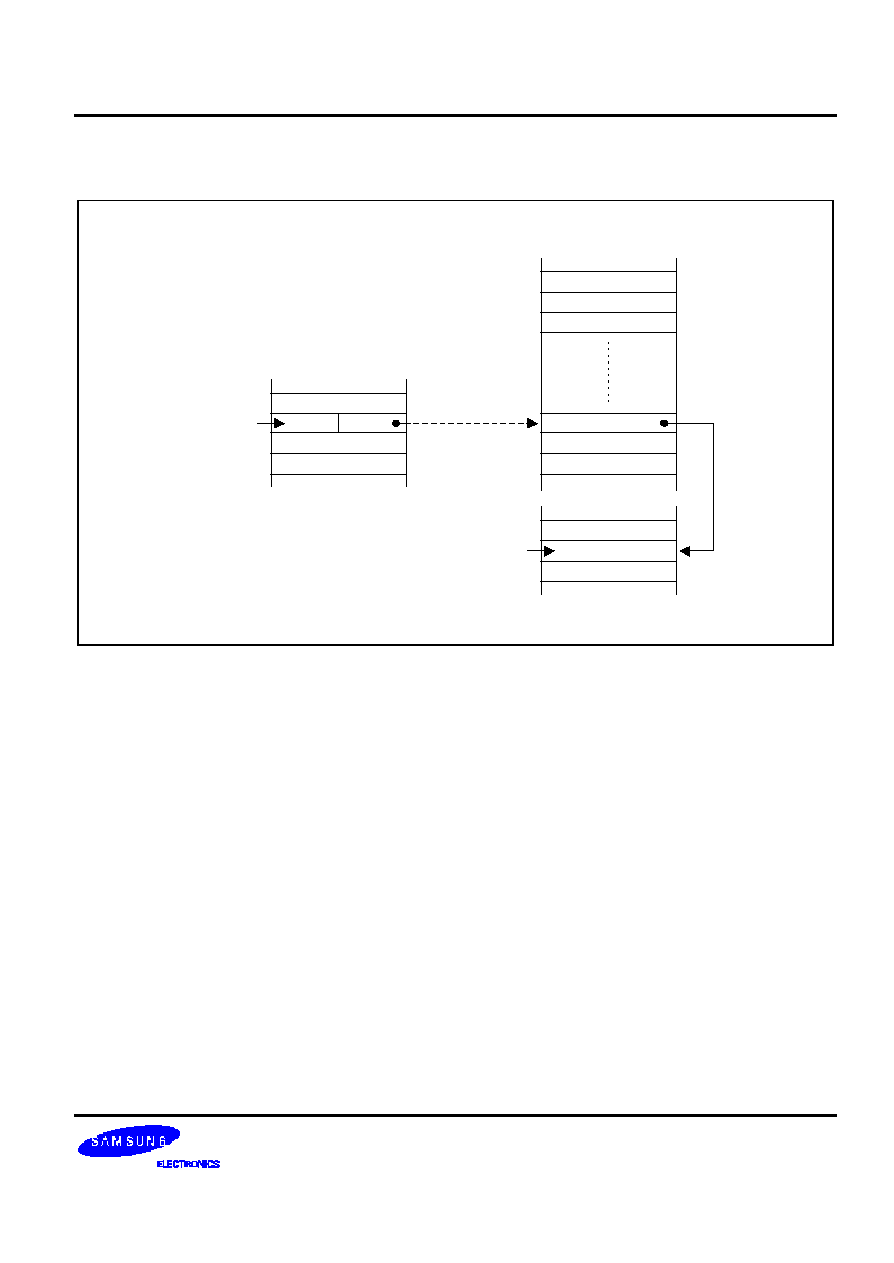

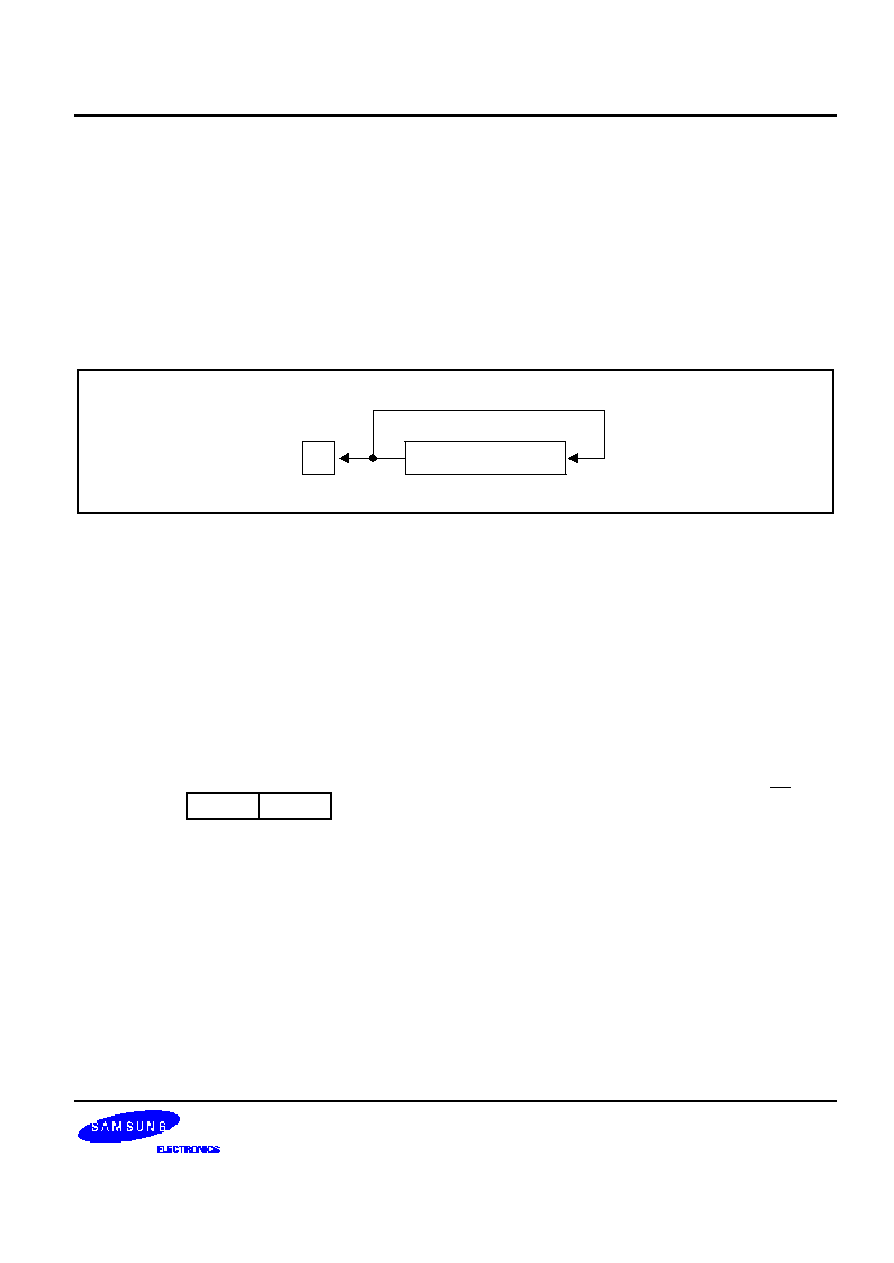

R E G I S T E R A D D R E S S I N G M O D E ( R )

I n R e g i s t e r a d d r e s s i n g m o d e , t h e o p e r a n d i s t h e c o n t e n t o f a s p e c i f i e d r e g i s t e r ( s e e F i g u r e 3 -1 ) . W o r k i n g r e g i s t e r

a d d r e s s i n g d i f f e r s f r o m R e g i s t e r a d d r e s s i n g b e c a u s e i t u s e s a n 1 6 -byte working register space in the register file and

a n 4 -b i t r e g i s t e r w i t h i n t h a t s p a c e ( s e e F i g u r e 3 -2).

dst

Value used in

Instruction Execution

OPCODE

OPERAND

8-Bit Register

File Address

Point to One

Rigister in Register

File

One-Operand

Instruction

(Example)

Sample Instruction:

DEC

CNTR

; Where CNTR is the label of an 8-bit register address

Program Memory

Register File

F i g u r e 3 -1 . R e g i s t e r A d d r e s s i n g

dst

OPCODE

4-Bit

Working Register

Point to the

Woking Register

(1 of 16)

Two-Operand

Instruction

(Example)

Sample Instruction:

ADD R1, R2 ; Where R1 = C1H and R2 = C2H

Program Memory

Register File

src

4 LSBs

OPERAND

CFH

C0H

F i g u r e 3 -2 . W o r k i n g R e g i s t e r A d d r e s s i n g

S 3 C 9 6 8 8 / P 9 6 8 8

ADDRESSING MODES

3 -3

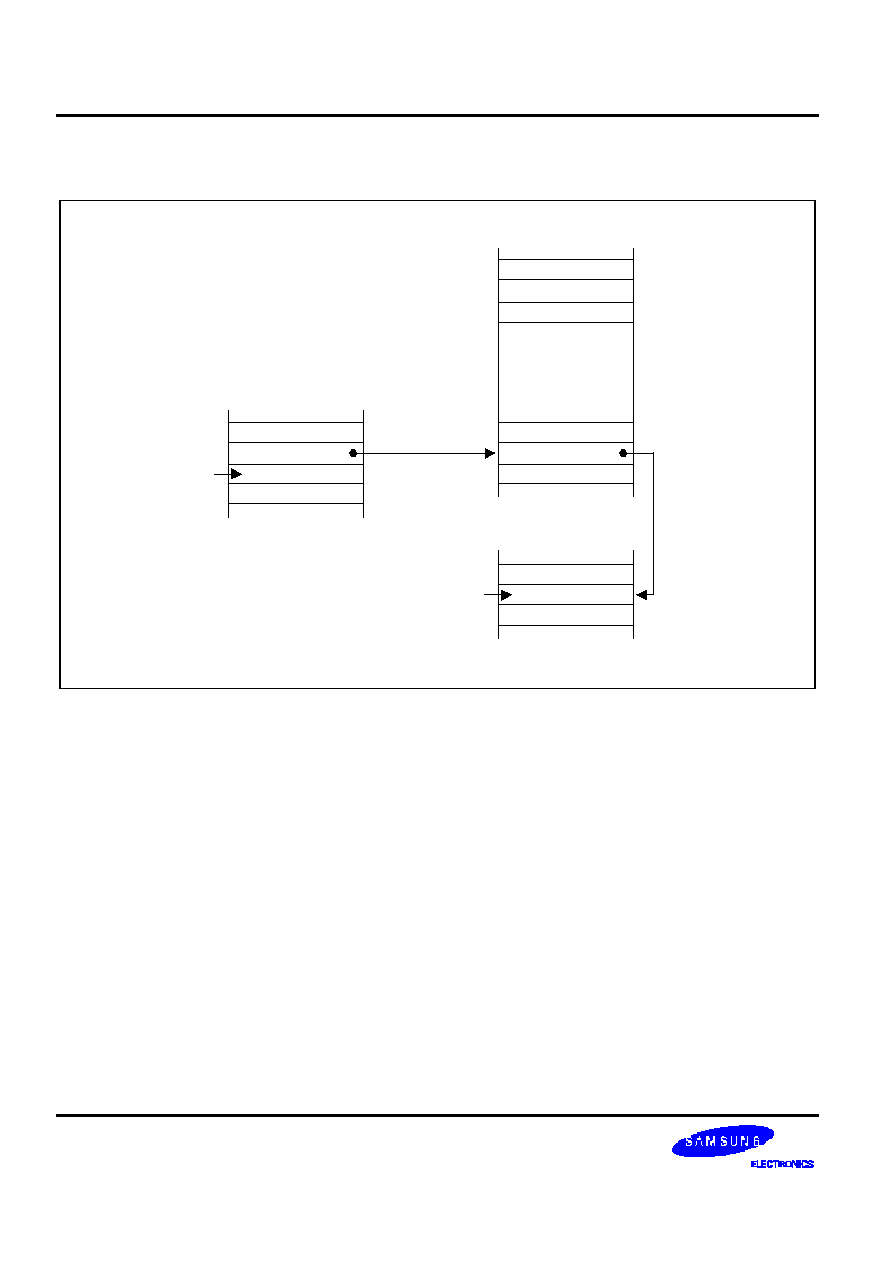

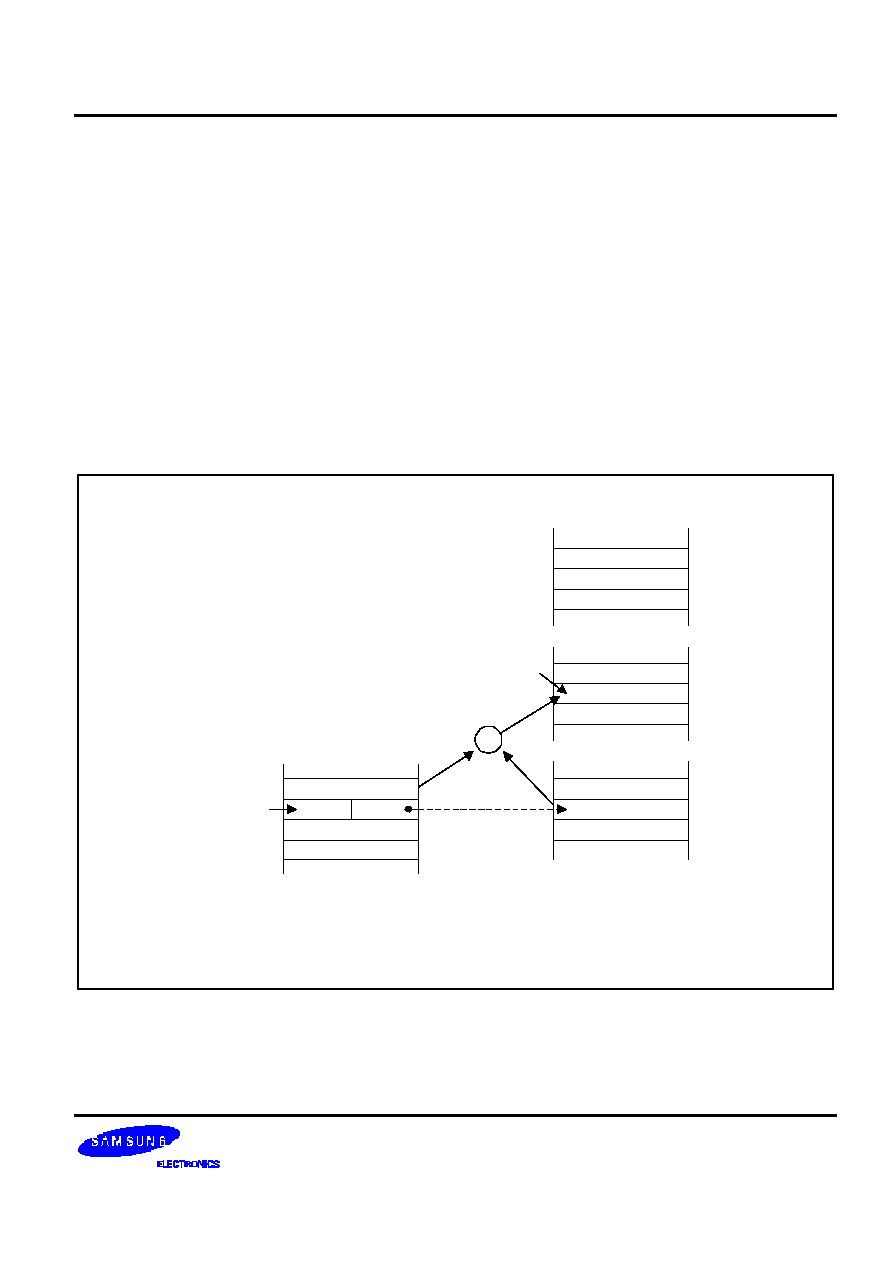

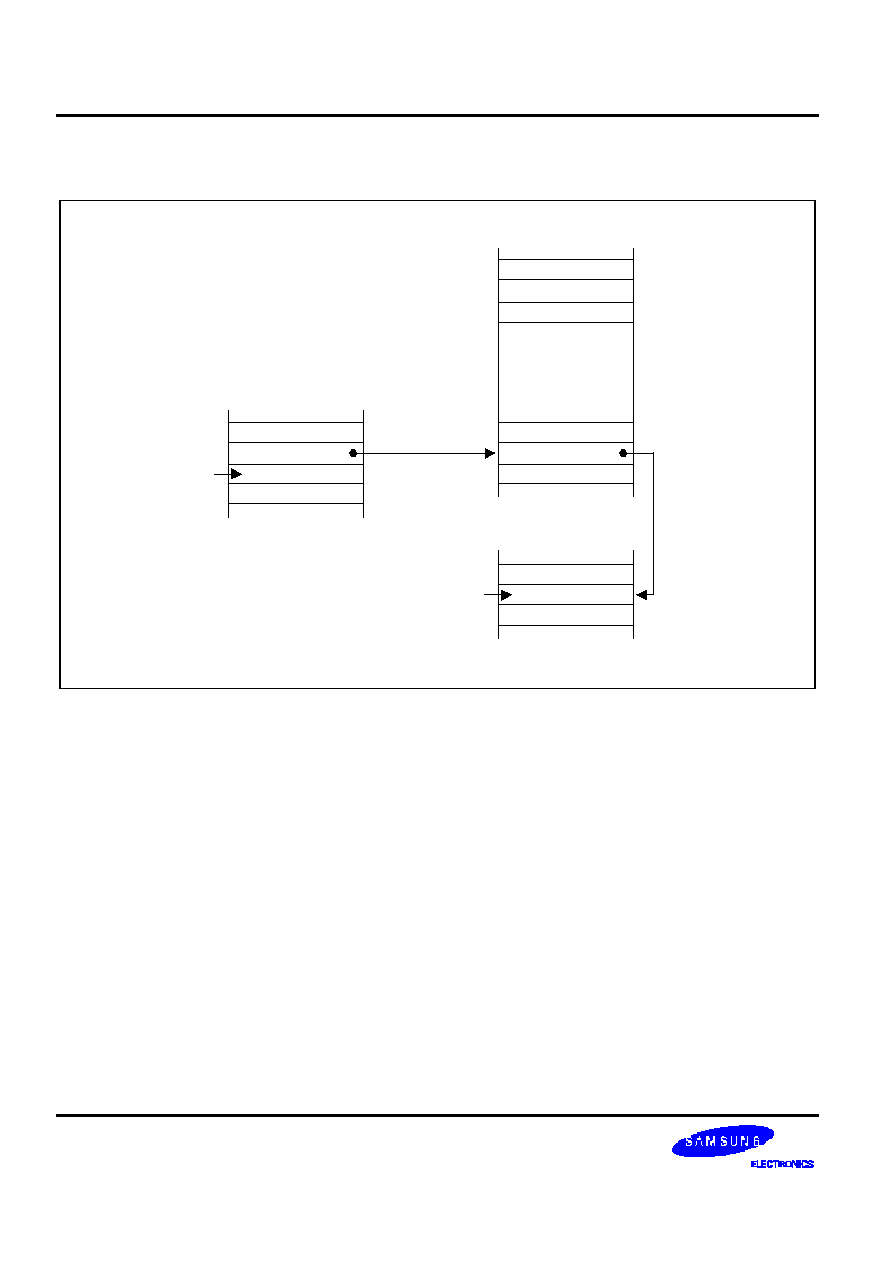

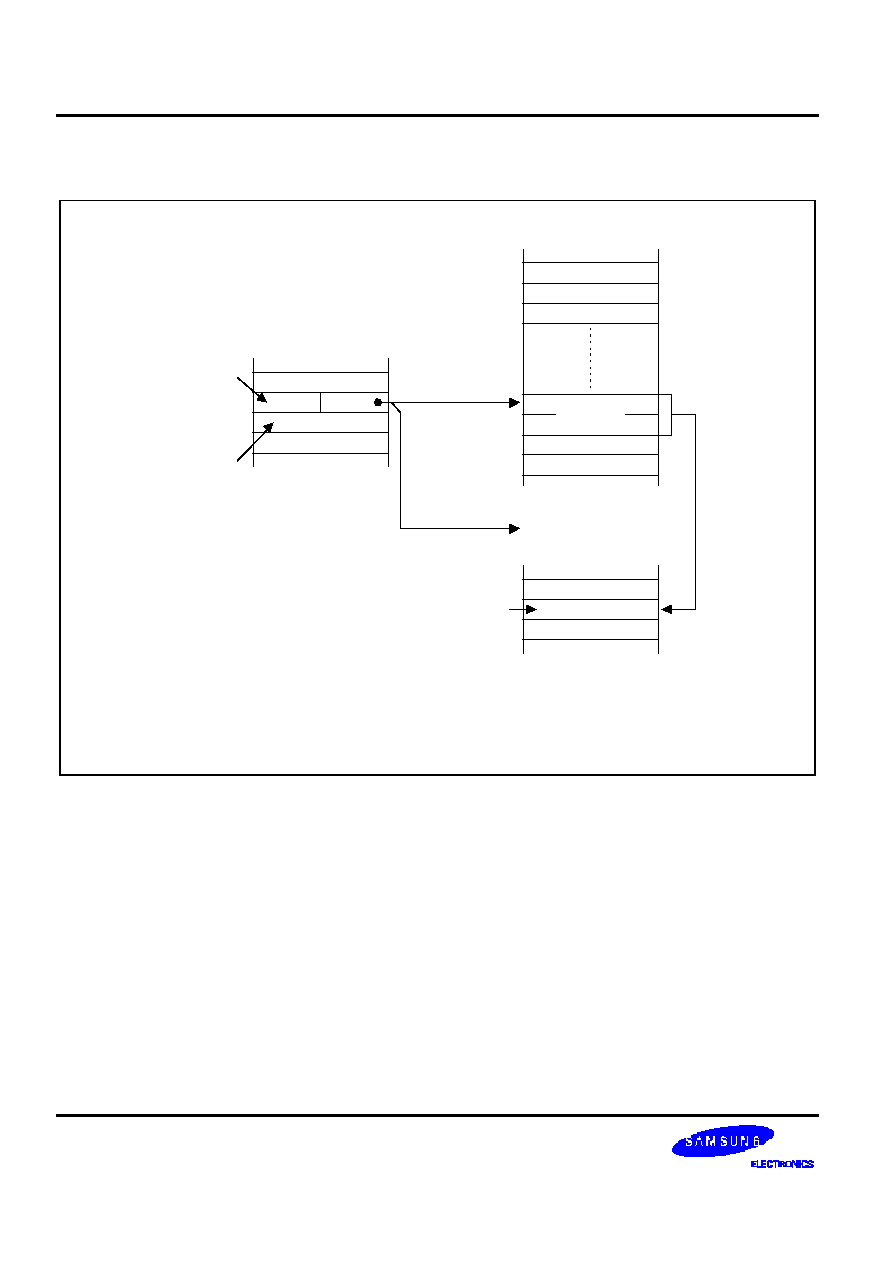

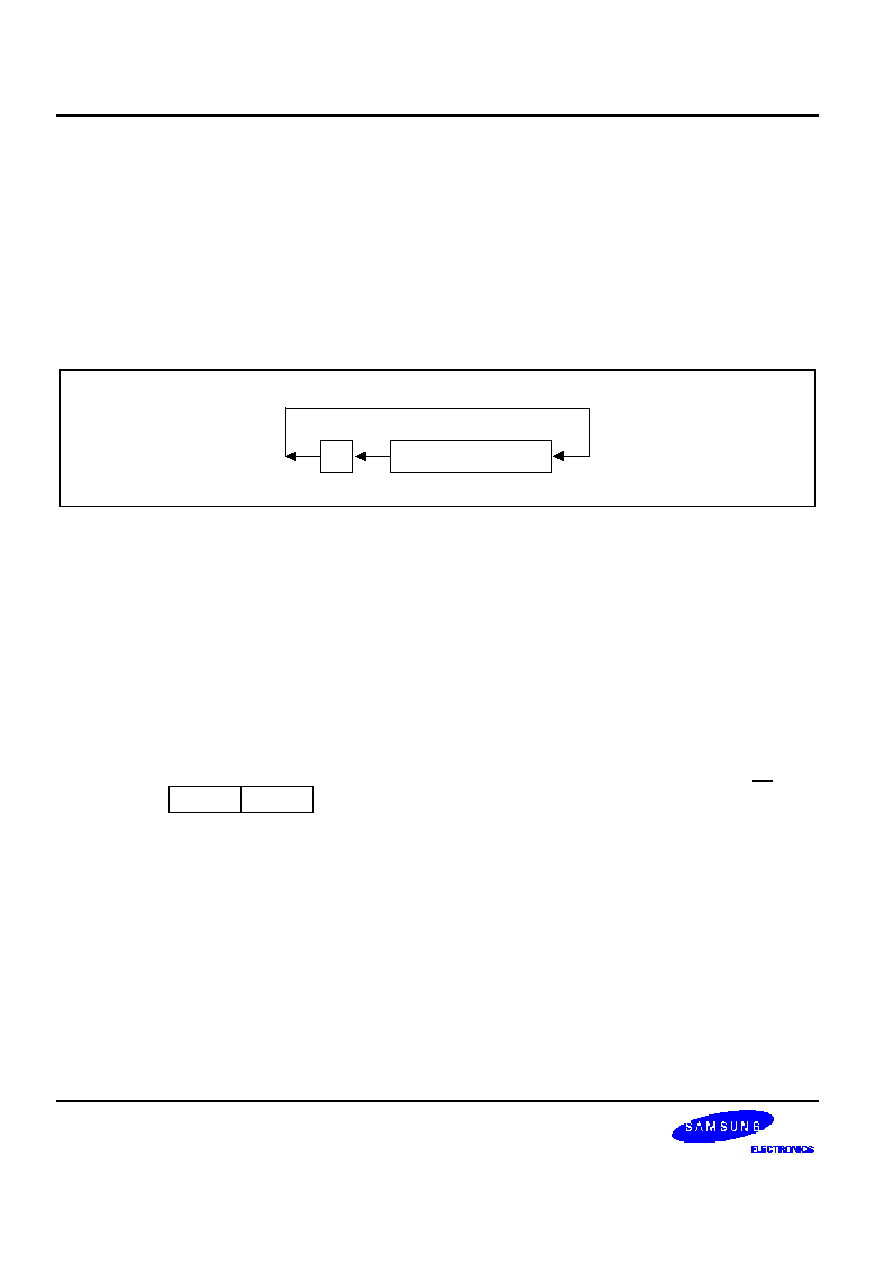

I N D I R E C T R E G I S T E R A D D R E S S I N G M O D E ( I R )

In Indirect Register (IR) addressing mode, the content of the specified register or register pair is the address of the

o p e r a n d . D e p e n d i n g o n t h e i n s t r u c t i o n u s e d , t h e a c t u a l a d d r e s s m a y p o i n t t o a r e g i s t e r i n t h e r e g i s t e r f i l e , t o p r o g r a m

m e m o r y ( R O M ) , o r t o a n e x t e r n a l m e m o r y s p a c e ( s e e F i g u r e s 3 -3 t h r o u g h 3 -6).

Y o u c a n u s e a n y 8 -b i t r e g i s t e r t o i n d i r e c t l y a d d r e s s a n o t h e r r e g i s t e r . A n y 1 6 -bit register pair can be used to indirectly

a d d r e s s a n o t h e r m e m o r y l o c a t i o n .

dst

Address of Operand

used by Instruction

OPCODE

ADDRESS

8-Bit Register

File Address

Point to One

Rigister in Register

File

One-Operand

Instruction

(Example)

Sample Instruction:

RL

@SHIFT

; Where SHIFT is the label of an 8-Bit register address

Program Memory

Register File

Value used in

Instruction Execution

OPERAND

F i g u r e 3 -3 . I n d i r e c t R e g i s t e r A d d r e s s i n g t o R e g i s t e r F i l e

ADDRESSING MODES

S 3 C 9 6 8 8 / P 9 6 8 8

3 -4

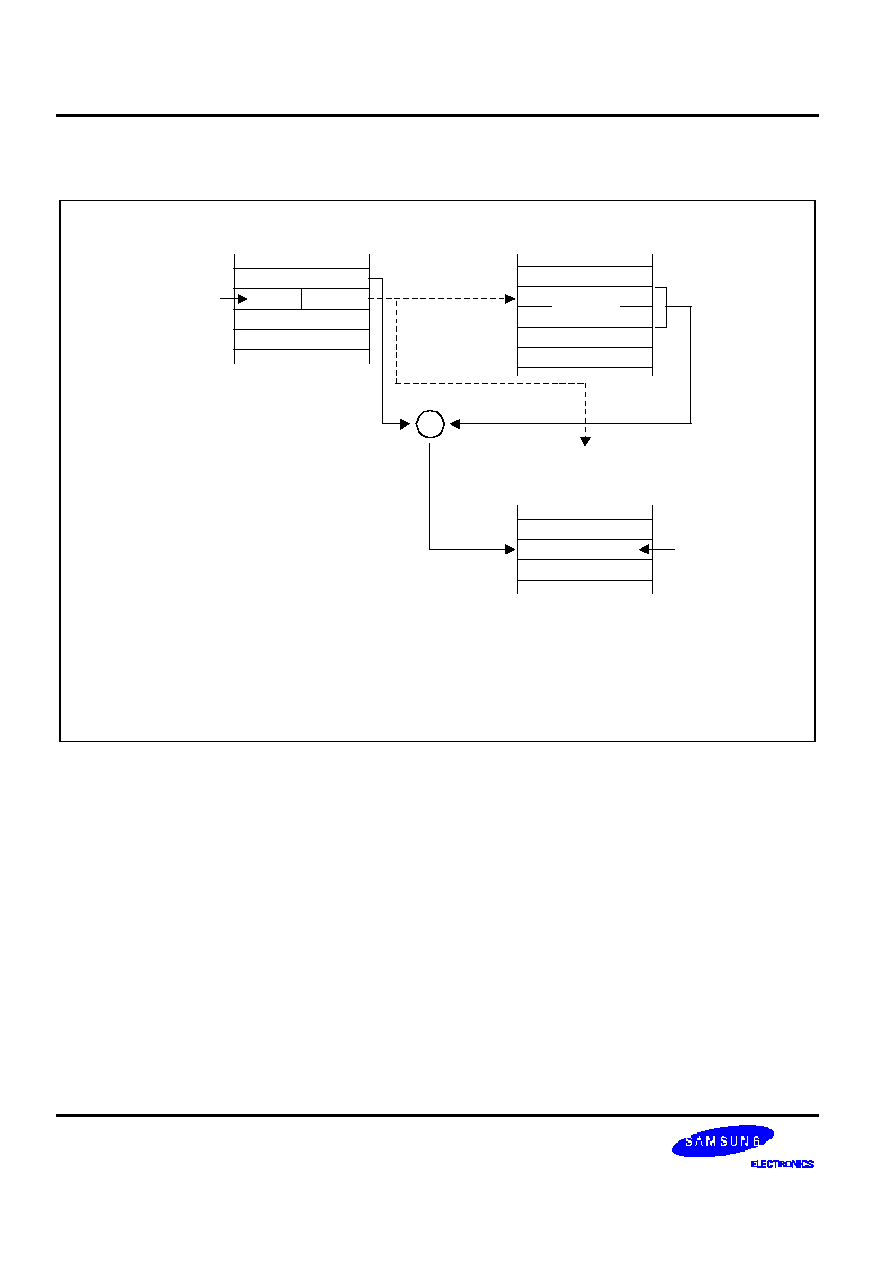

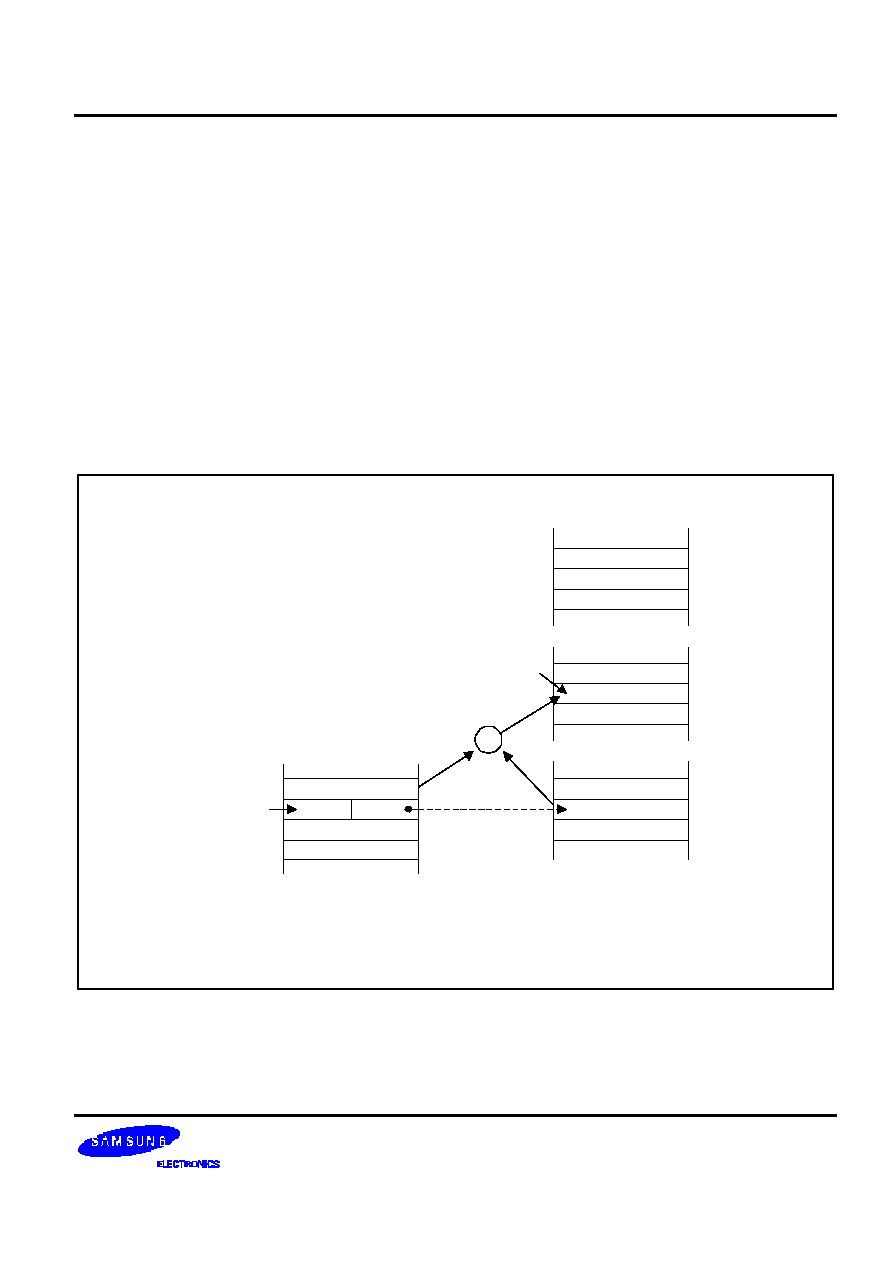

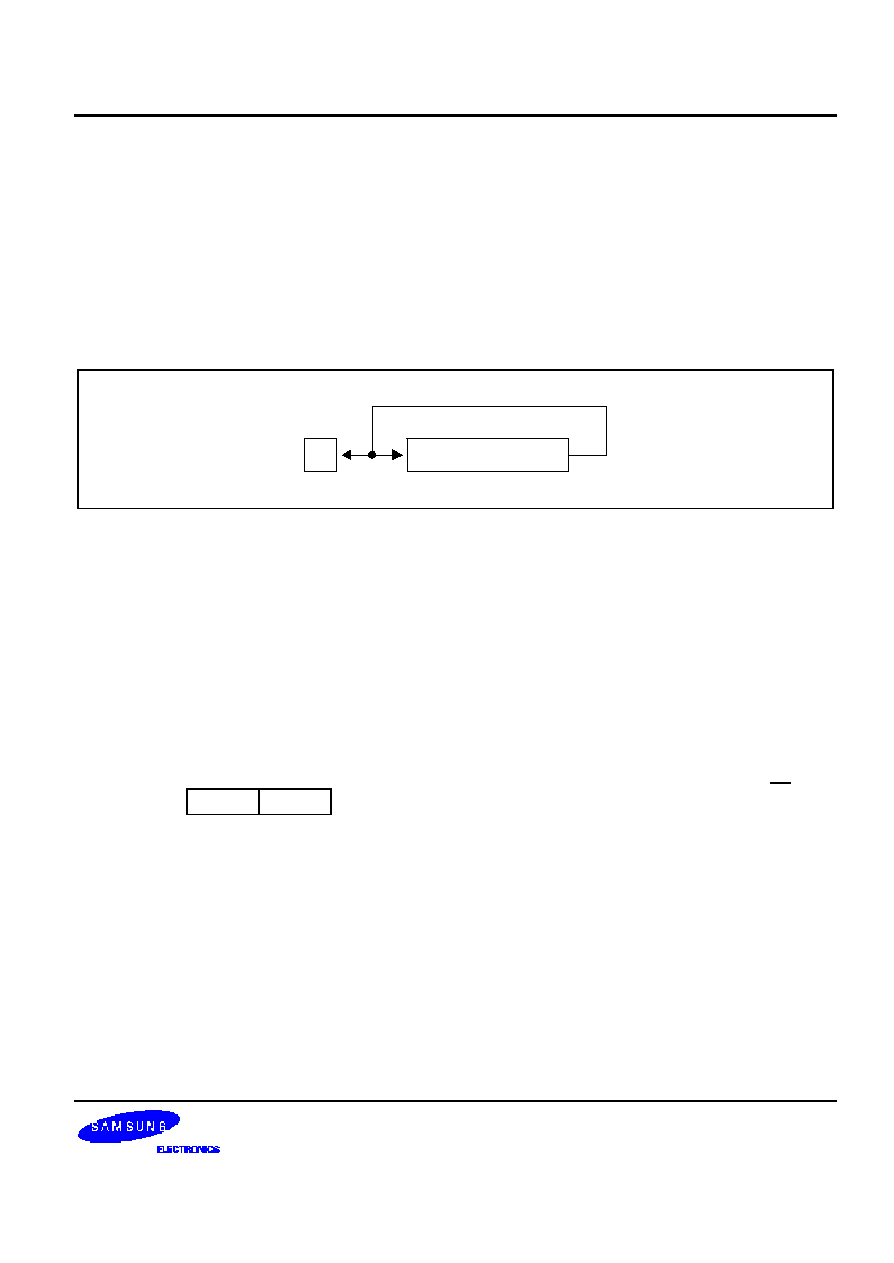

I N D I R E C T R E G I S T E R A D D R E S S I N G M O D E ( C o n t i n u e d)

dst

OPCODE

PAIR

Points to

Rigister Pair

Example

Instruction

References

Program

Memory

Sample Instructions:

CALL

@RR2

JP

@RR2

Program Memory

Register File

Value used in

Instruction

OPERAND

REGISTER

Program Memory

16-Bit

Address

Points to

Program

Memory

F i g u r e 3 -4 . I n d i r e c t R e g i s t e r A d d r e s s i n g t o P r o g r a m M e m o r y

S 3 C 9 6 8 8 / P 9 6 8 8

ADDRESSING MODES

3 -5

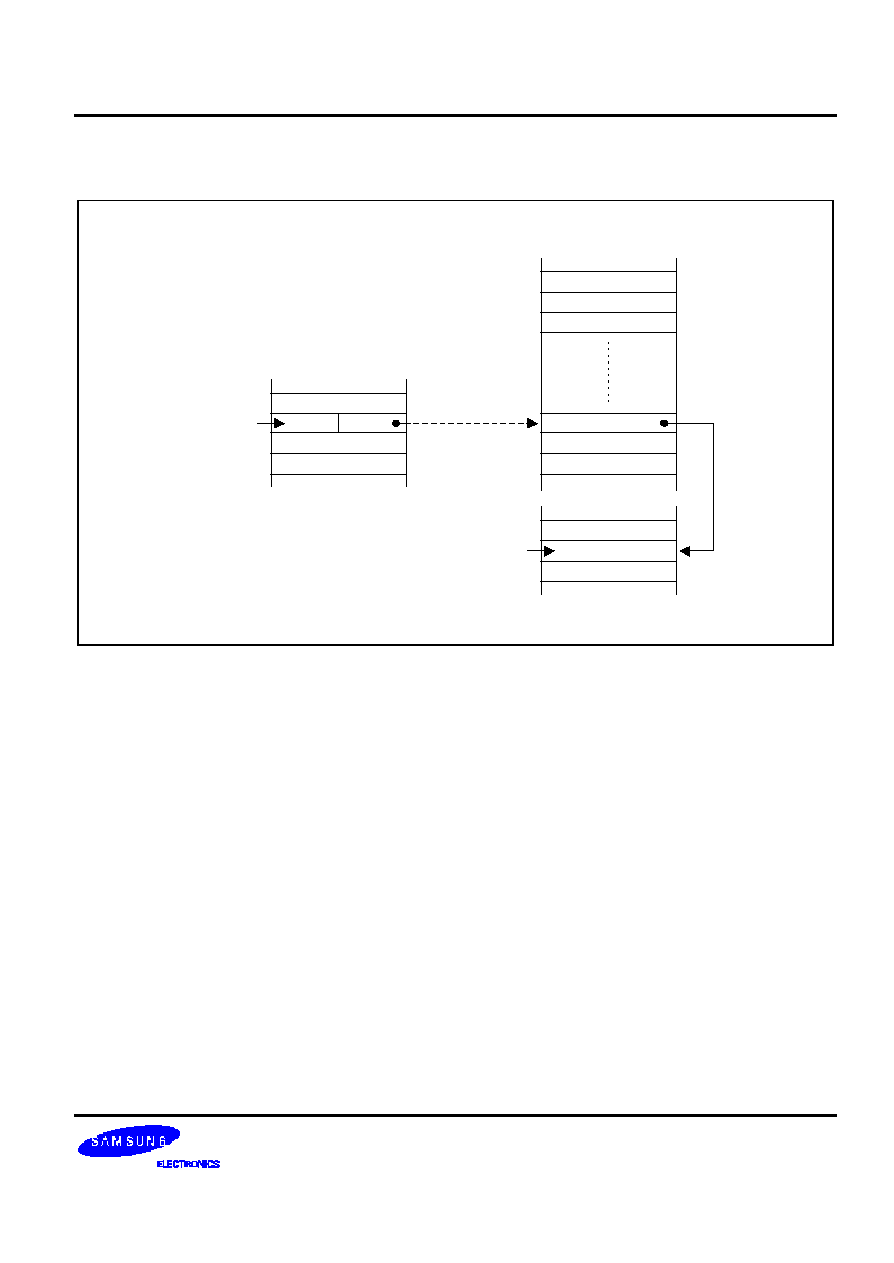

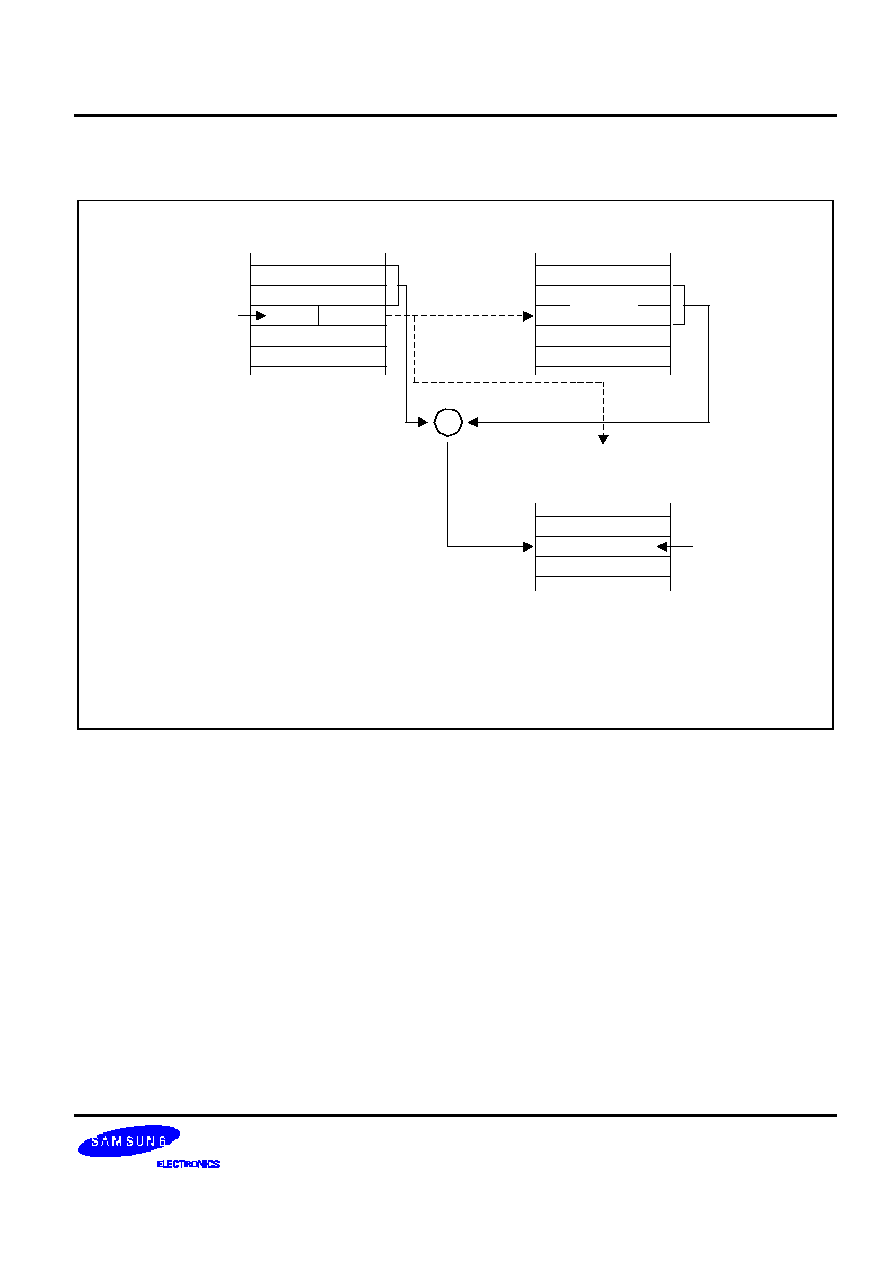

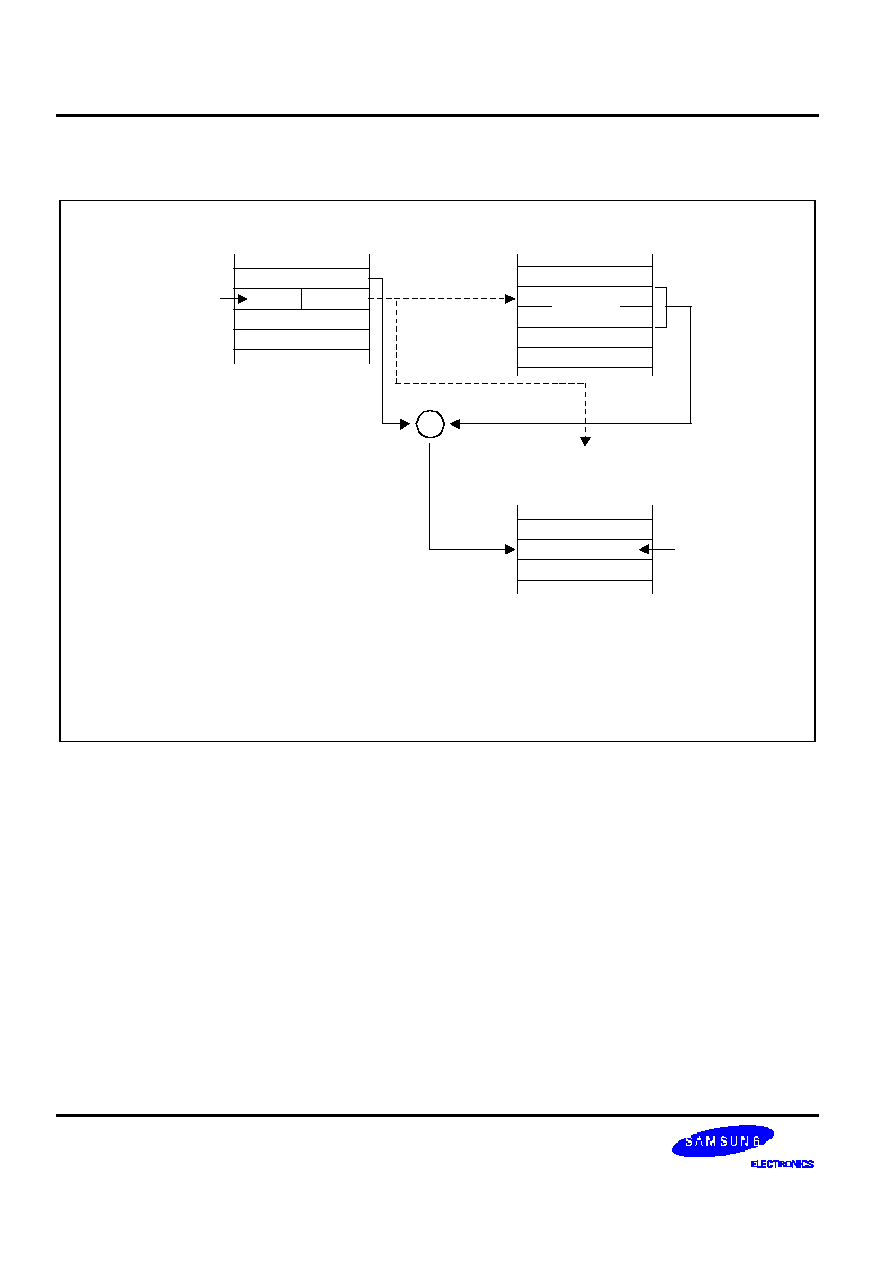

I N D I R E C T R E G I S T E R A D D R E S S I N G M O D E ( C o n t i n u e d)

dst

OPCODE

4-Bit

Working

Register

Address

Point to the

Woking Register

(1 of 16)

Sample Instruction:

OR

R6, @R2

Program Memory

Register File

src

4 LSBs

Value used in

Instruction

OPERAND

C0H

CFH

OPERAND

F i g u r e 3 -5 . I n d i r e c t W o r k i n g R e g i s t e r A d d r e s s i n g t o R e g i s t e r F i l e

ADDRESSING MODES

S 3 C 9 6 8 8 / P 9 6 8 8

3 -6

I N D I R E C T R E G I S T E R A D D R E S S I N G M O D E ( C o n c l u d e d)

dst

OPCODE

4-Bit Working

Register Address

Sample Instructions:

LCD

R5,@RR2 ; Program memory access

LDE

R3,@RR14 ; External data memory access

LDE

@RR4, R8 ; External data memory access

Program Memory

Register File

src

Value used in

Instruction

OPERAND

Example Instruction

References either

Program Memory or

Data Memory

Program Memory

or

Data Memory

Next 3-Bits Point

to Working

Register Pair

(1 of 8)

LSB Selects

Register

Pair

16-Bit

address

points to

program

memory

or data

memory

CFH

C0H

F i g u r e 3 -6 . I n d i r e c t W o r k i n g R e g i s t e r A d d r e s s i n g t o P r o g r a m o r D a t a M e m o r y

S 3 C 9 6 8 8 / P 9 6 8 8

ADDRESSING MODES

3 -7

I N D E X E D A D D R E S S I N G M O D E ( X )

I n d e x e d ( X ) a d d r e s s i n g m o d e a d d s a n o f f s e t v a l u e t o a b a s e a d d r e s s d u r i n g i n s t r u c t i o n e x e c u t i o n i n o r d e r t o c a l c u l a t e

the effective operand address (see Figure 3-7 ) . Y o u c a n u s e I n d e x e d a d d r e s s i n g m o d e t o a c c e s s l o c a t i o n s i n t h e

internal register file or in external memory.

I n s h o r t o f f s e t I n d e x e d a d d r e s s i n g m o d e , t h e 8 -b i t d i s p l a c e m e n t i s t r e a t e d a s a s i g n e d i n t e g e r i n t h e r a n g e

≠ 1 2 8 t o + 1 2 7 . T h i s a p p l i e s t o e x t e r n a l m e m o r y a c c e s s e s o n l y ( s e e F i g u r e 3 -8).

For register file addressing, an 8-b i t b a s e a d d r e s s p r o v i d e d b y t h e i n s t r u c t i o n i s a d d e d t o a n 8 -bit offset contained in

a w o r k i n g r e g i s t e r . F o r e x t e r n a l m e m o r y a c c e s s e s , t h e b a s e a d d r e s s i s s t o r e d i n t h e w o r k i n g r e g i s t e r p a i r

d e s i g n a t e d i n t h e i n s t r u c t i o n . T h e 8 -bit or 16-b i t o f f s e t g i v e n i n t h e i n s t r u c t i o n i s t h e n a d d e d t o t h e b a s e a d d r e s s ( s e e

Fi g ur e 3 -9).

Th e o n l y i n s t r u c t i o n t h a t s u p p o r t s I n d e x e d a d d r e s s i n g m o d e f o r t h e i n t e r n a l r e g i s t e r f i l e i s t h e L o a d i n s t r u c t i o n ( L D ) .

T h e L D C a n d L D E i n s t r u c t i o n s s u p p o r t I n d e x e d a d d r e s s i n g m o d e f o r i n t e r n a l p r o g r a m m e m o r y , e x t e r n a l p r o g r a m

m e m o r y , a n d f o r e x t e r n a l d a t a m e m o r y , w h e n i m p l e m e n t e d .

dst

OPCODE

Two-Operand

Instruction

Example

Point to One of the

Woking Register

(1 of 16)

Sample Instruction:

LD R0, #BASE[R1] ; Where BASE is an 8-bit immediate value

Program Memory

Register File

src

4 LSBs

Value used in

Instruction

OPERAND

INDEX

X (OFFSET)

~

~

+

~

~

F i g u r e 3 -7 . I n d e x e d A d d r e s s i n g t o R e g i s t e r F i l e

ADDRESSING MODES

S 3 C 9 6 8 8 / P 9 6 8 8

3 -8

I N D E X E D A D D R E S S I N G M O D E ( C o n t i n u e d)

Point to Working

Register Pair

(1 of 8)

LSB Selects

16-Bit

address

added to

offset

dst

OPCODE

Program Memory

XS (OFFSET)

4-Bit Working

Register Address

Sample Instructions:

LDC

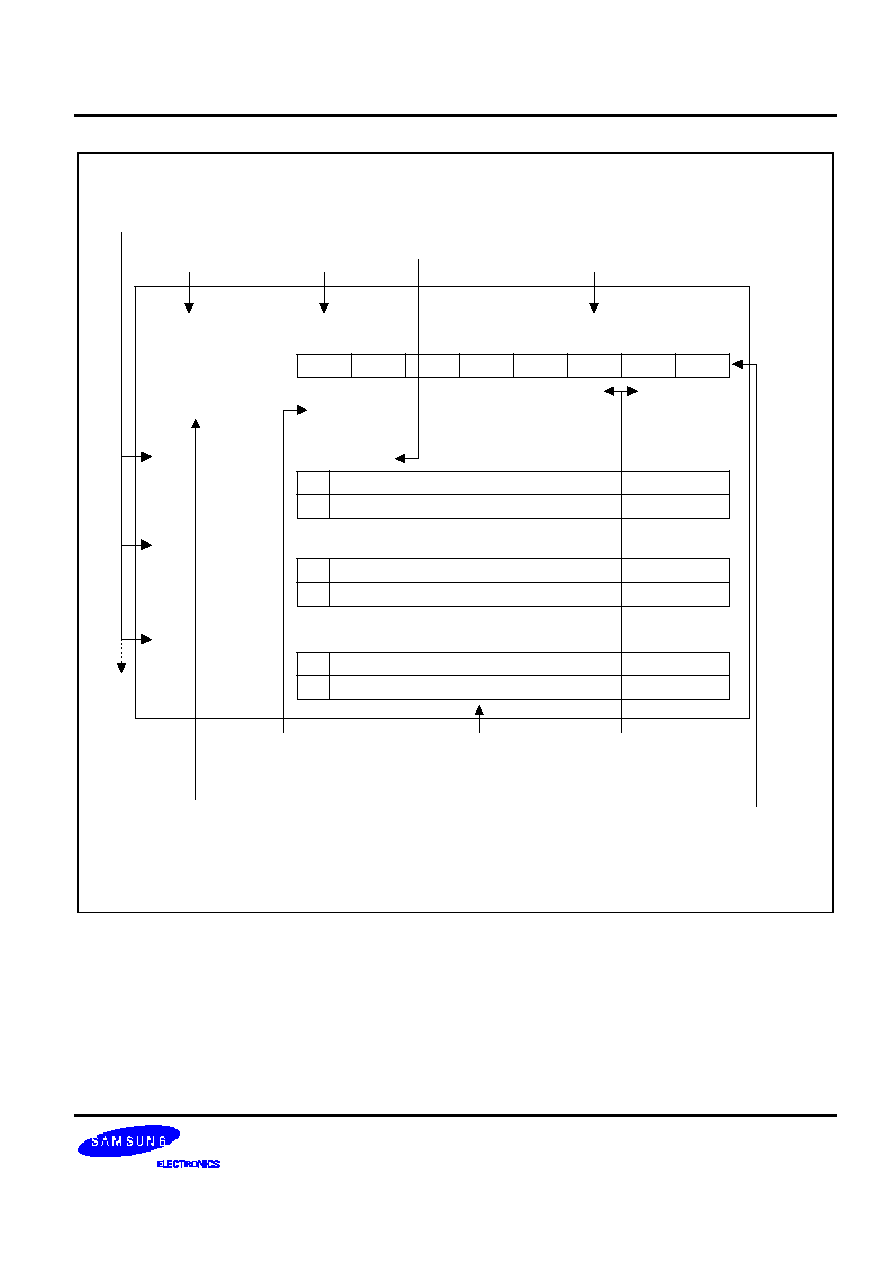

R4, #04H[RR2] ; The values in the program address (RR2 + #04H)

are loaded into register R4.

LDE

R4,#04H[RR2] ; Identical operation to LDC example, except that

external program memory is accessed.

NEXT 3-Bit

Register

Pair

src

8-Bit

16-Bit

+

Program Memory

or

Datamemory

OPERAND

Value used in

Instruction

16-Bit

Register File

F i g u r e 3 -8 . I n d e x e d A d d r e s s i n g t o P r o g r a m o r D a t a M e m o r y w i t h S h o r t O f f s e t

S 3 C 9 6 8 8 / P 9 6 8 8

ADDRESSING MODES

3 -9

I N D E X E D A D D R E S S I N G M O D E ( C o n c l u d e d)

Point to Working

Register Pair

(1 of 8)

LSB Selects

16-Bit

address

added to

offset

Program Memory

4-Bit Working

Register Address

Sample Instructions:

LDC

R4, #1000H[RR2]

; The values in the program address (RR2 + #1000H)

are loaded into register R4.

LDE

R4,#1000H[RR2]

; Identical operation to LDC example, except that

external program memory is accessed.

NEXT 3-Bit

Register

Pair

16-Bit

16-Bit

+

Program Memory

or

Datamemory

OPERAND

Value used in

Instruction

16-Bit

Register File

OPCODE

XL

H

(OFFSET)

XL

L

(OFFSET)

dst

src

F i g u r e 3 -9 . I n d e x e d A d d r e s s i n g t o P r o g r a m o r D a t a M e m o r y w i t h L o n g O f f s e t

ADDRESSING MODES

S 3 C 9 6 8 8 / P 9 6 8 8

3 -1 0

D I R E C T A D D R E S S M O D E ( D A )

I n D i r e c t A d d r e s s ( D A ) m o d e , t h e i n s t r u c t i o n p r o v i d e s t h e o p e r a n d ' s 1 6 -b i t m e m o r y a d d r e s s . J u m p ( J P ) a n d C a l l

( C A L L ) i n s t r u c t i o n s u s e t h i s a d d r e s s i n g m o d e t o s p e c i f y t h e 1 6 -b i t d e s t i n a t i o n a d d r e s s t h a t i s l o a d e d i n t o t h e P C

w h e n e v e r a J P o r C A L L i n s t r u c t i o n i s e x e c u t e d .

T h e L D C a n d L D E i n s t r u c t i o n s c a n u s e D i r e c t A d d r e s s m o d e t o s p e c i f y t h e s o u r c e o r d e s t i n a t i o n a d d r e s s f o r L o a d

o p e r a t i o n s t o p r o g r a m m e m o r y ( L D C ) o r t o e x t e r n a l d a t a m e m o r y ( L D E ) , i f i m p l e m e n t e d .

Sample Instructions:

LDC

R5,1234H ; The values in the program address (1234H)

are loaded into register R5.

LDE

R5,1234H ; Identical operation to LDC example, except that

external program memory is accessed.

dst/src

OPCODE

Program Memory

"0" or "1"

Lower Address Byte

LSB Selects Program

Memory or Data Memory:

"0" = Program Memory

"1" = Data Memory

Memory

Address

Used

Upper Address Byte

Program or

Data Memory

F i g u r e 3 -1 0 . D i r e c t A d d r e s s i n g f o r L o a d I n s t r u c t i o n s

S 3 C 9 6 8 8 / P 9 6 8 8

ADDRESSING MODES

3 -1 1

D I R E C T A D D R E S S M O D E (C o n t i n u e d)

OPCODE

Program Memory

Lower Address Byte

Program

Memory

Address

Used

Upper Address Byte

Sample Instructions:

JP

C,JOB1

; Where JOB1 is a 16-Bit immediate address

CALL

DISPLAY

; Where DISPLAY is a 16-Bit immediate address

Next OPCODE

F i g u r e 3 -1 1 . D i r e c t A d d r e s s i n g f o r C a l l a n d J u m p I n s t r u c t i o n s

ADDRESSING MODES

S 3 C 9 6 8 8 / P 9 6 8 8

3 -1 2

R E L A T I V E A D D R E S S M O D E ( R A )

In Relative Address (RA) mode, a two's -c o m p l e m e n t s i g n e d d i s p l a c e m e n t b e t w e e n ≠ 1 2 8 a n d + 1 2 7 i s s p e c i f i e d i n

t h e i n s t r u c t i o n . T h e d i s p l a c em e n t v a l u e i s t h e n a d d e d t o t h e c u r r e n t P C v a l u e . T h e r e s u l t i s t h e a d d r e s s o f t h e n e x t

i n s t r u c t i o n t o b e e x e c u t e d . B e f o r e t h i s a d d i t i o n o c c u r s , t h e P C c o n t a i n s t h e a d d r e s s o f t h e i n s t r u c t i o n i m m e d i a t e l y

following the current instruction.

T h e i n s t r u c t i o n s t h a t s u p p o r t R A a d d r e s s i n g i s J R .

OPCODE

Program Memory

Displacement

Program Memory

Address Used

Sample Instructions:

JR

ULT,$+OFFSET ; Where OFFSET is a value in the range +127 to -128

Next OPCODE

+

Signed

Displacement Value

Current Instruction

Current

PC Value

F i g u r e 3 -1 2 . R e l a t i v e A d d r e s s i n g

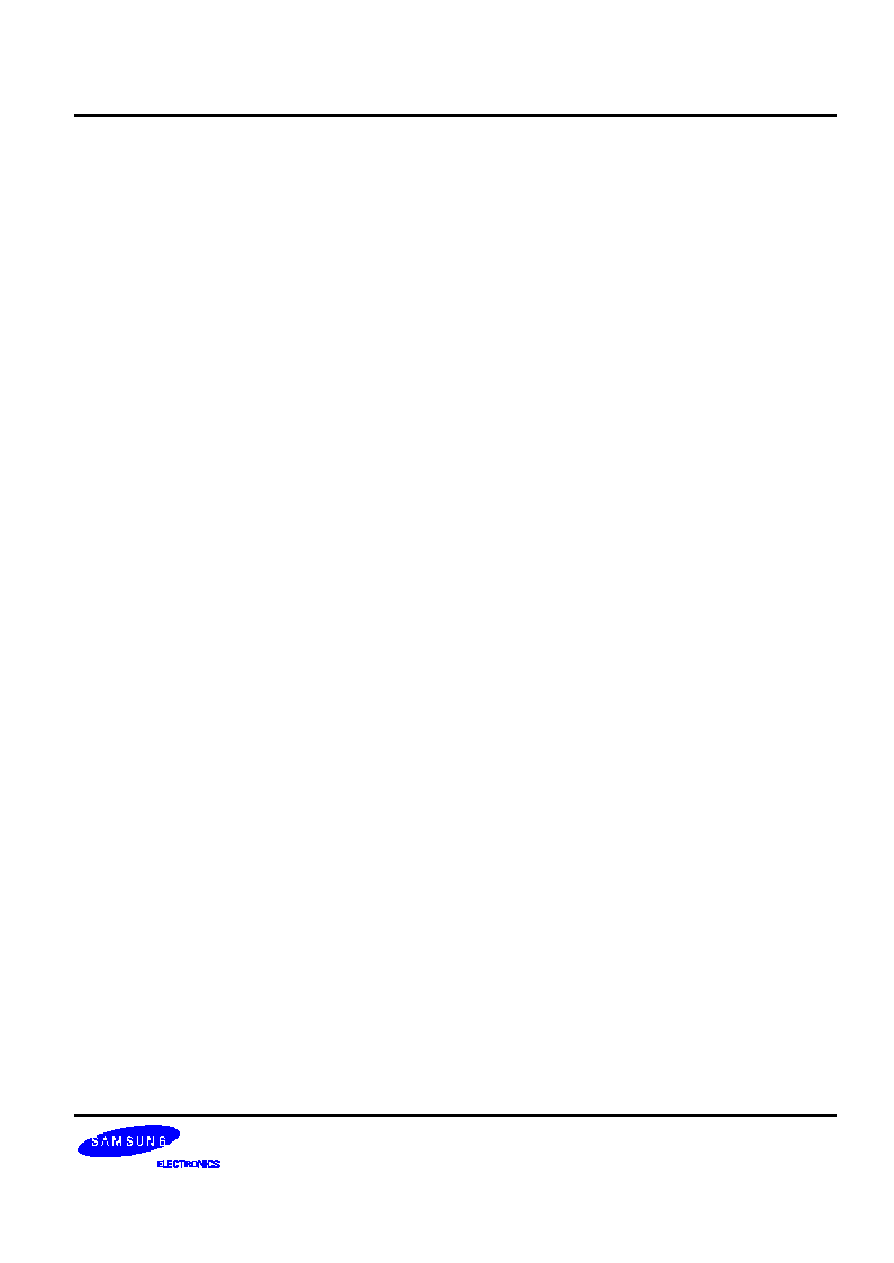

I M M E D I A T E M O D E ( I M )

I n I m m e d i a t e ( I M ) a d d r e s s i n g m o d e , t h e o p e r a n d v a l u e u s e d i n t h e i n struction is the value supplied in the operand

field itself. Immediate addressing mode is useful for loading constant values into registers.

(The Operand value is in the instruction)

OPCODE

Sample Instruction:LD R0,#0AAH

Program Memory

OPERAND

F i g u r e 3 -1 3 . I m m e d i a t e A d d r e s s i n g

S 3 C 9 6 8 8 / P 9 6 8 8

CONTROL REGISTERS

4-

1

4

C O N T R O L R E G I S T E R S

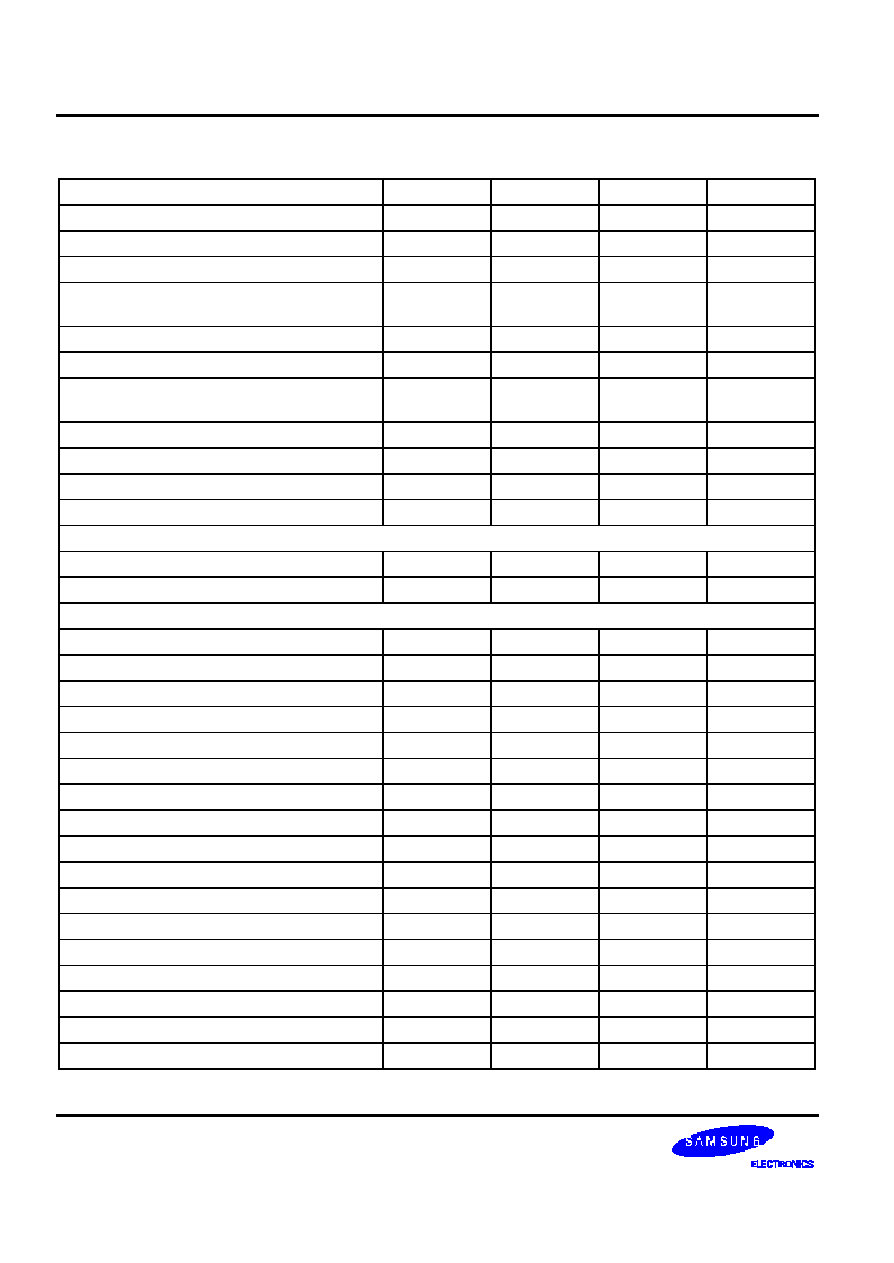

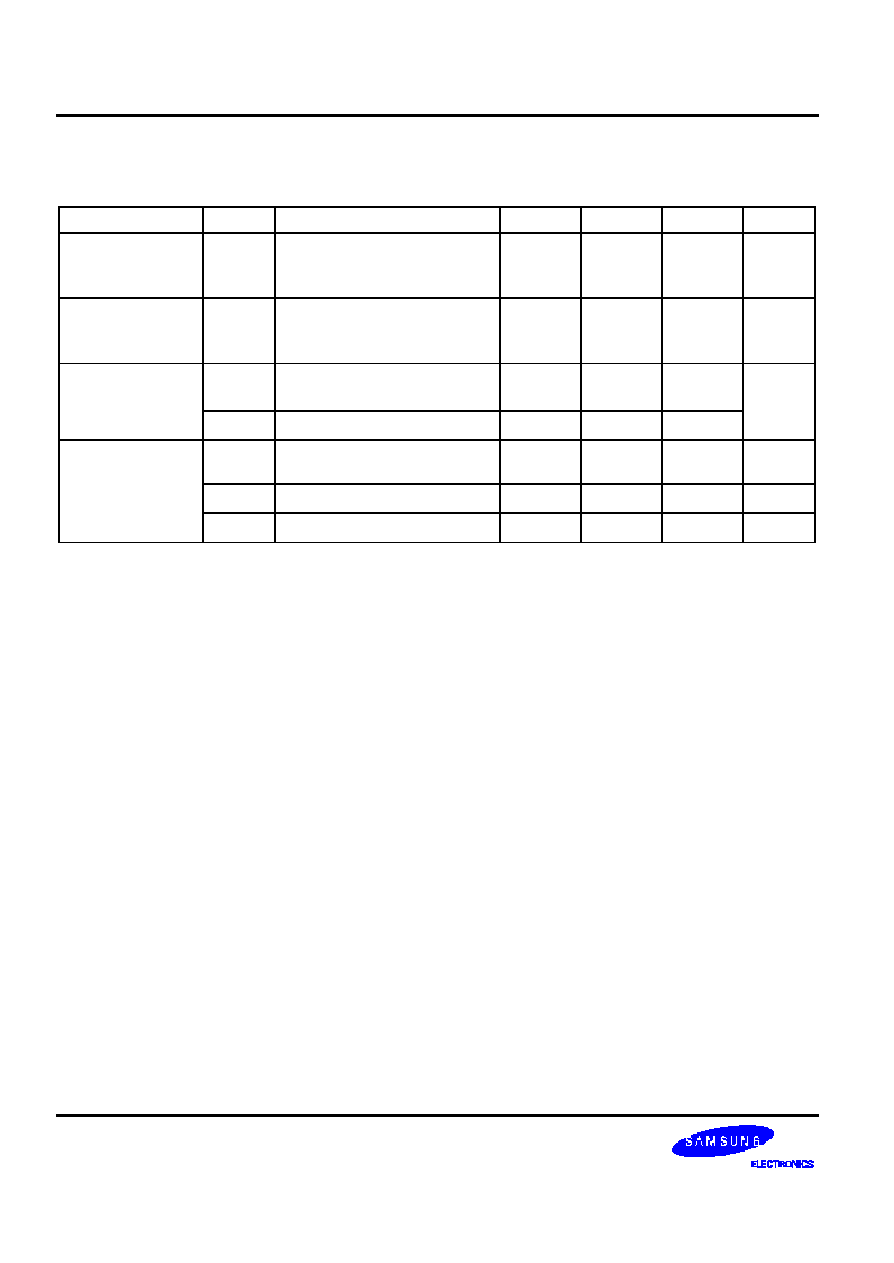

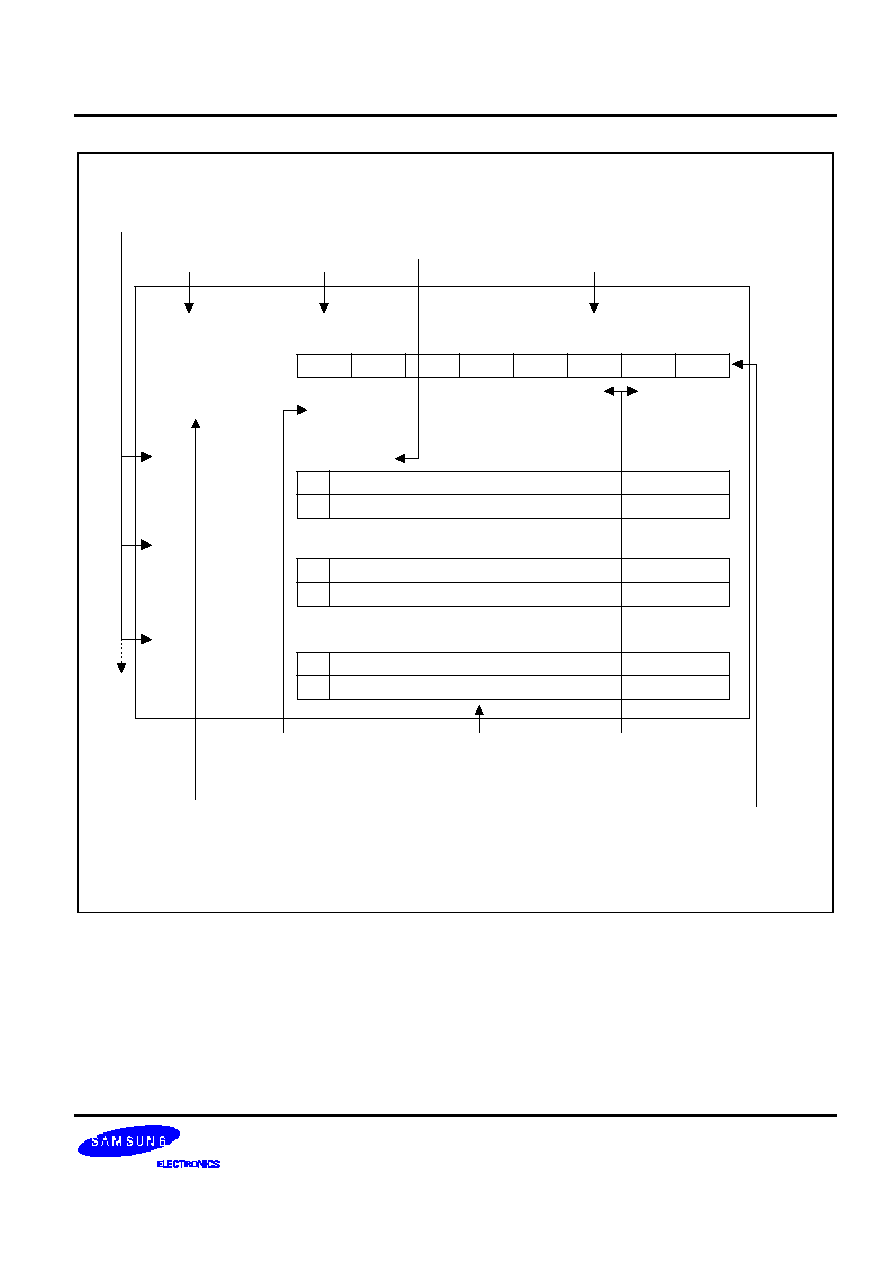

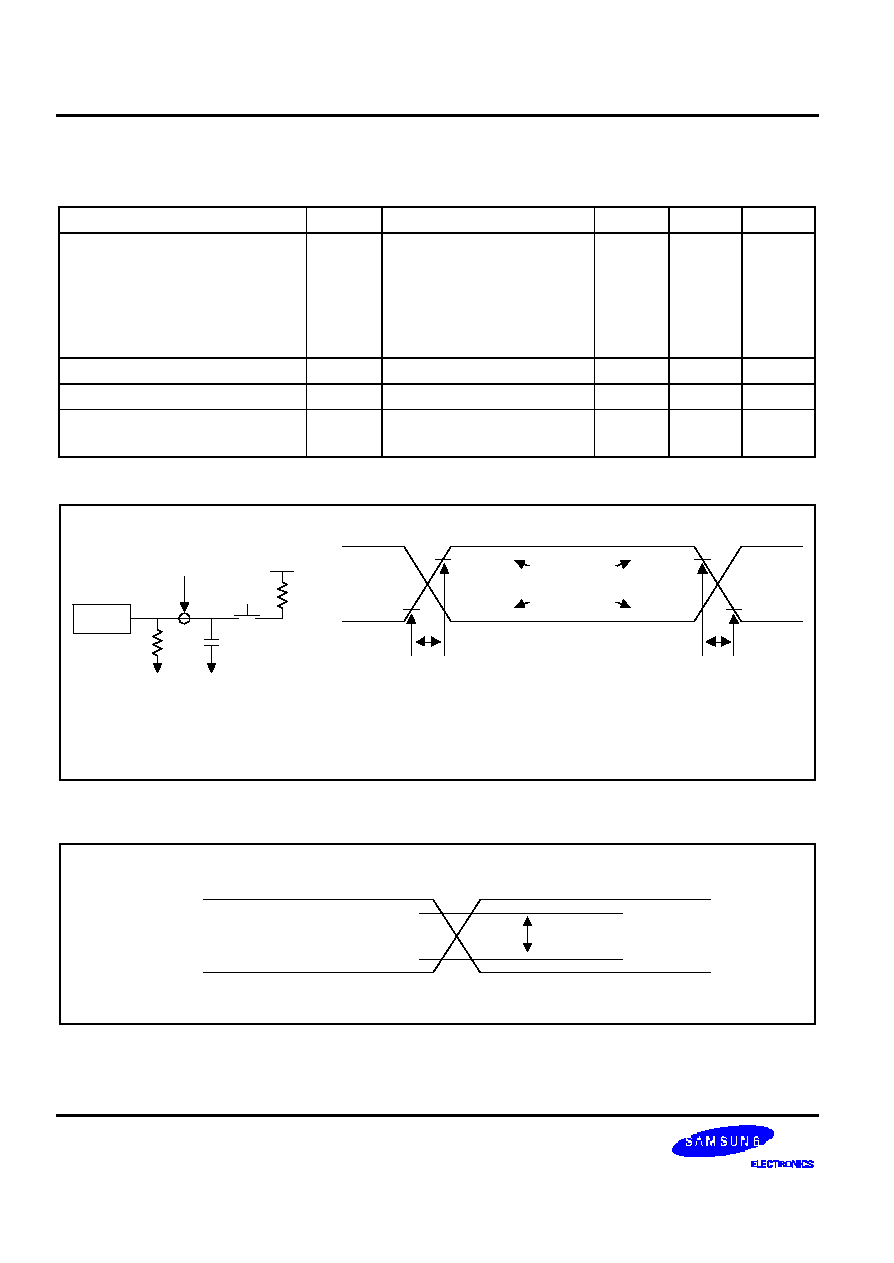

O V E R V I E W

I n t h i s s e c t i o n , d e t a i l e d d e s c r i p t i o n s o f t h e S 3 C 9 6 8 8 / P 9 6 8 8 c o n t r o l r e g i s t e r s a r e p r e s e n t e d i n a n e a s y -t o -read format.

T h e s e d e s c r i p t i o n s w i l l h e l p y o u t o f a m i l i a r i z e y o u r s e l f w i t h t h e m a p p e d l o c a t i o n s i n t h e r e g i s t e r f i l e . Y o u c a n a l s o

u s e t h e m a s a q u i c k -r e f e r e n c e s o u r c e w h e n w r i t i n g a p p l i c a t i o n p r o g r a m s .

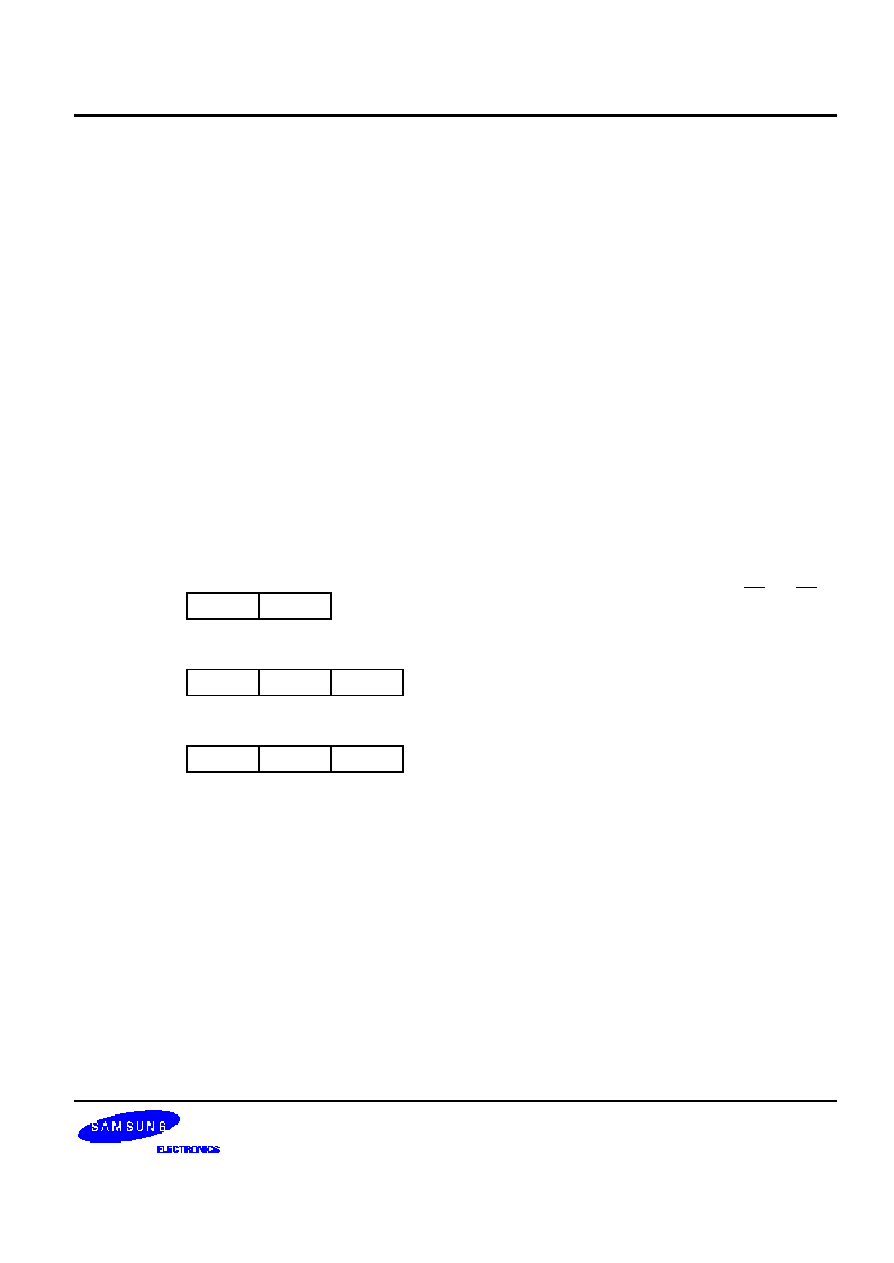

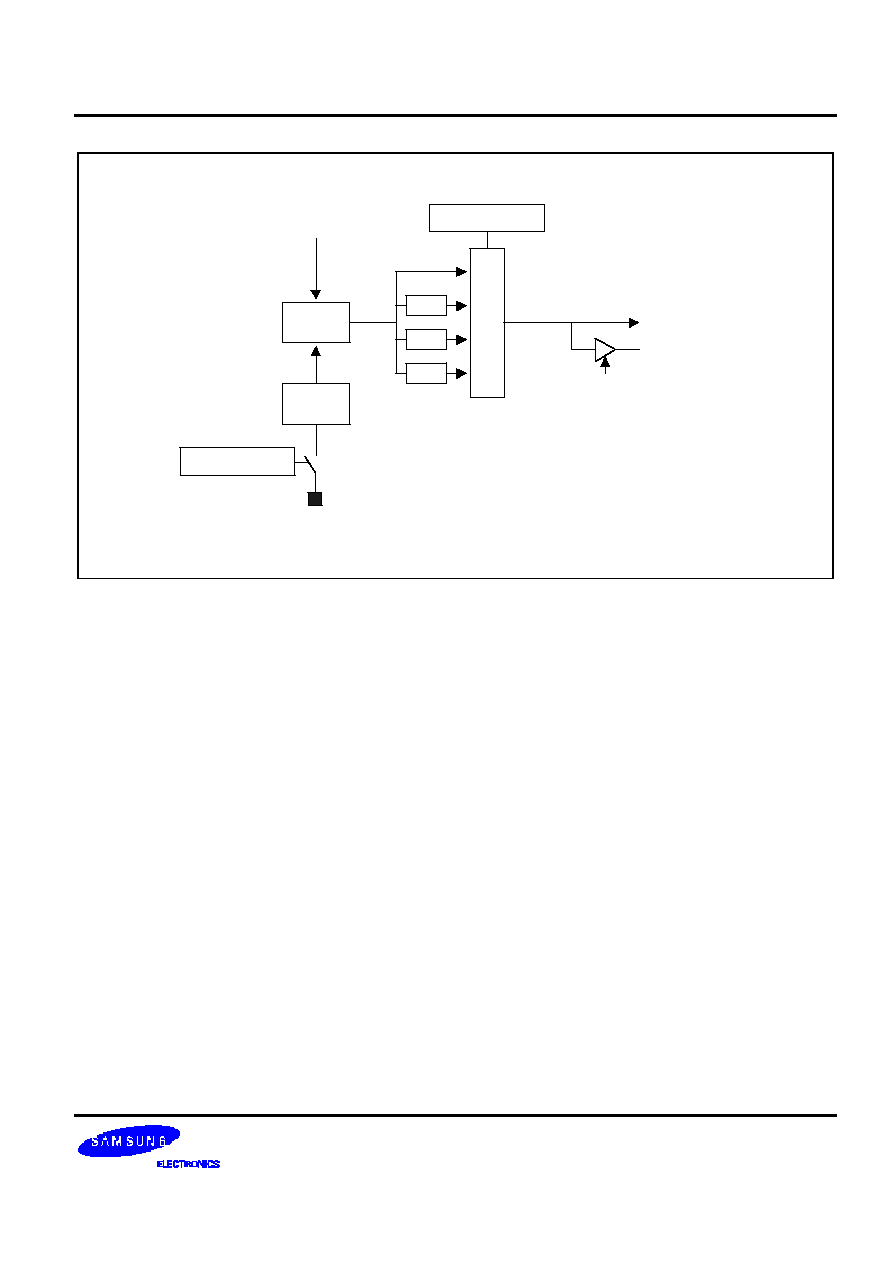

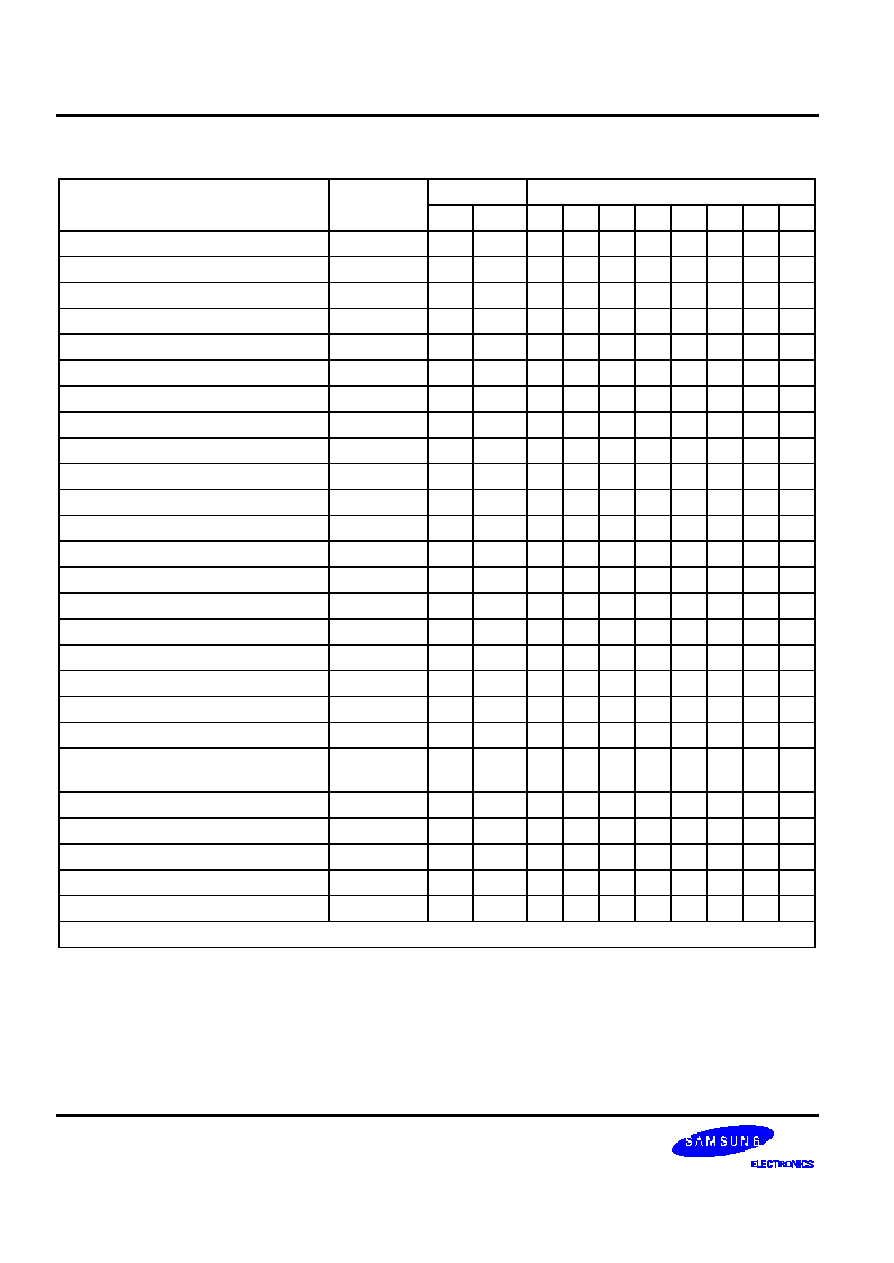

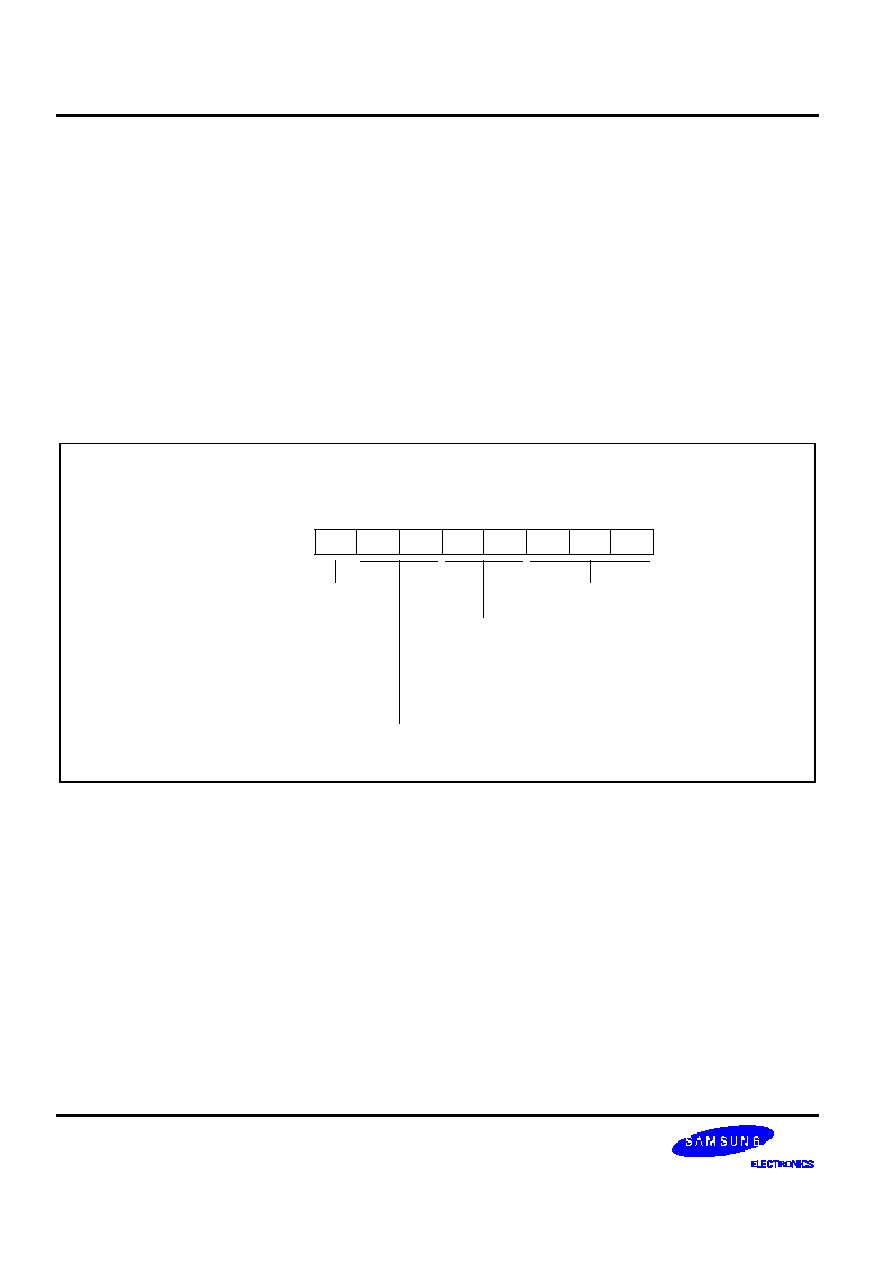

S y s t e m a n d p e r i p h e r a l r e g i s t e r s a r e s u m m a r i z e d i n T a b l e 4 -1 . F i g u r e 4 -1 illustrates the important features of the

s t a n d a r d r e g i s t e r d e s c r i p t i o n f o r m a t .

C o n t r o l r e g i s t e r d e s c r i p t i o n s a r e a r r a n g e d i n a l p h a b e t i c a l o r d e r a c c o r d i n g t o r e g i s t e r m n e m o n i c . M o r e i n f o r m a t i o n

about control registers is presented in the context of the various peripheral hardware descriptions in Part II of this

m a n u a l .

CONTROL REGISTERS

S 3 C 9 6 8 8 / P 9 6 8 8

4 -2

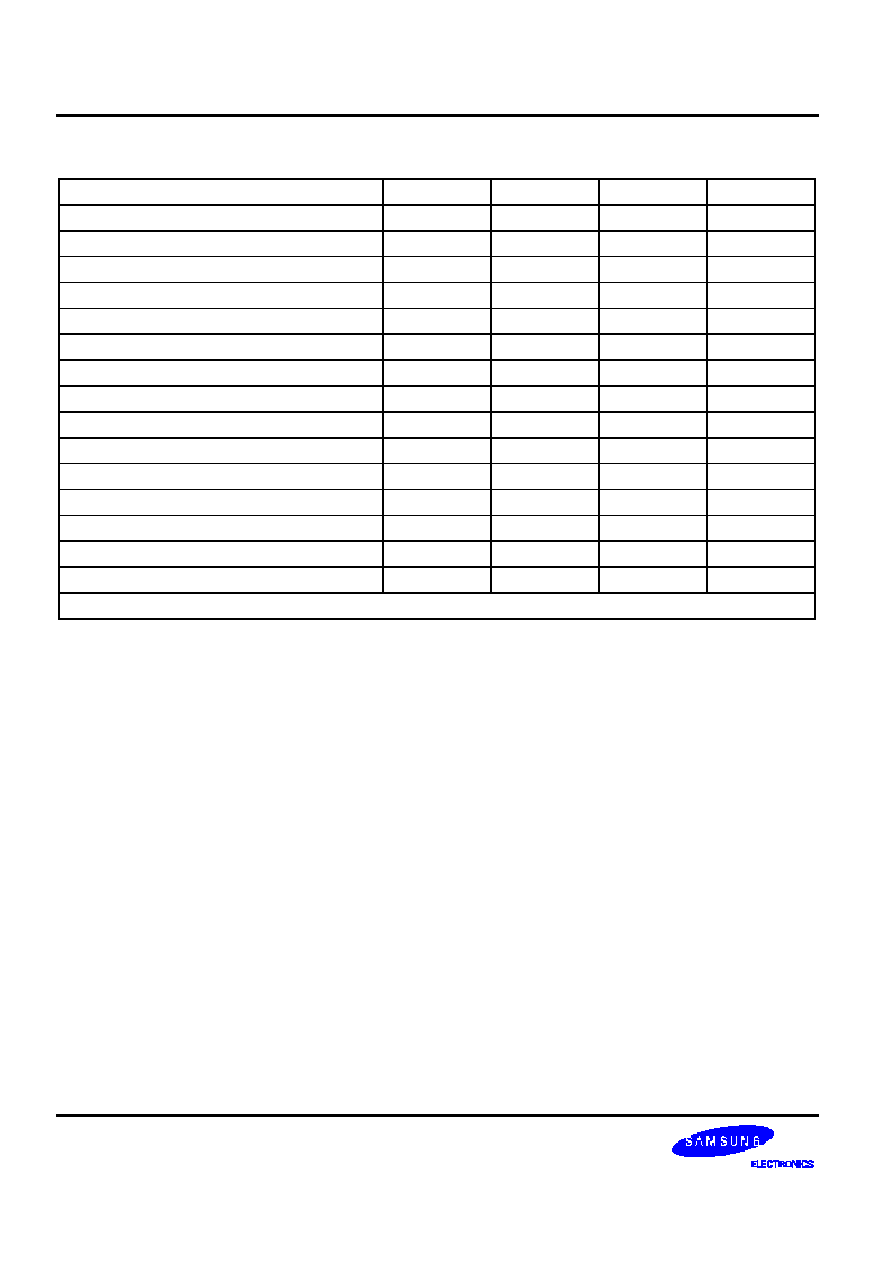

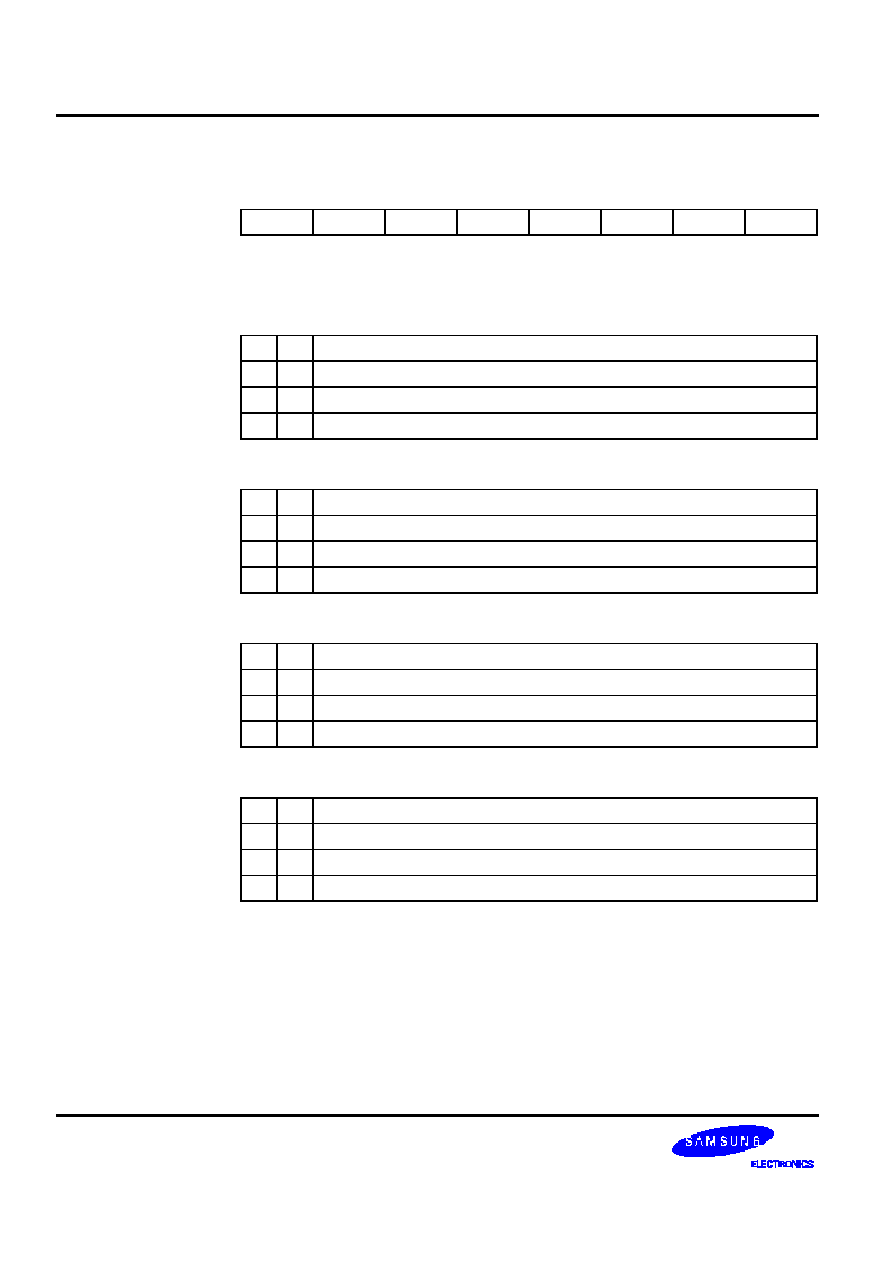

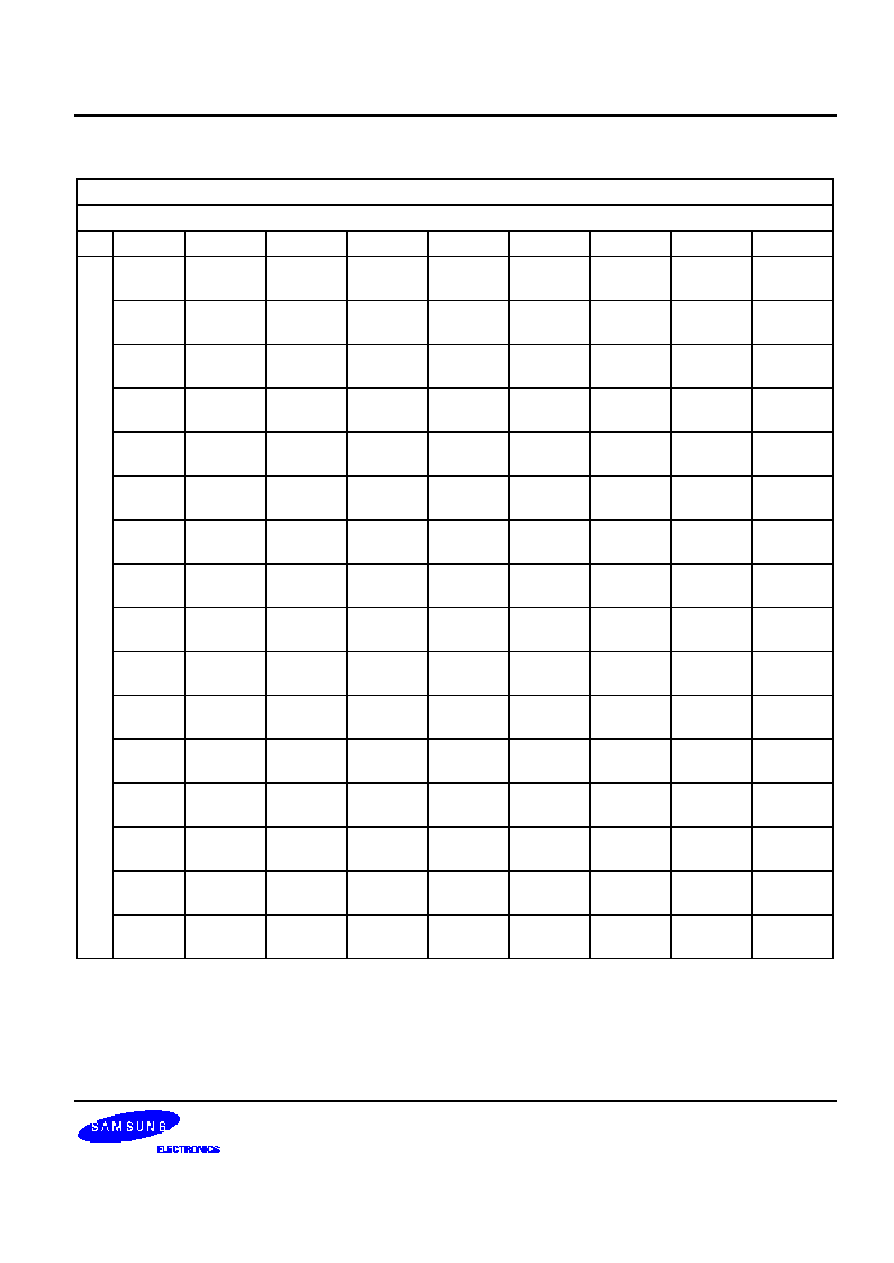

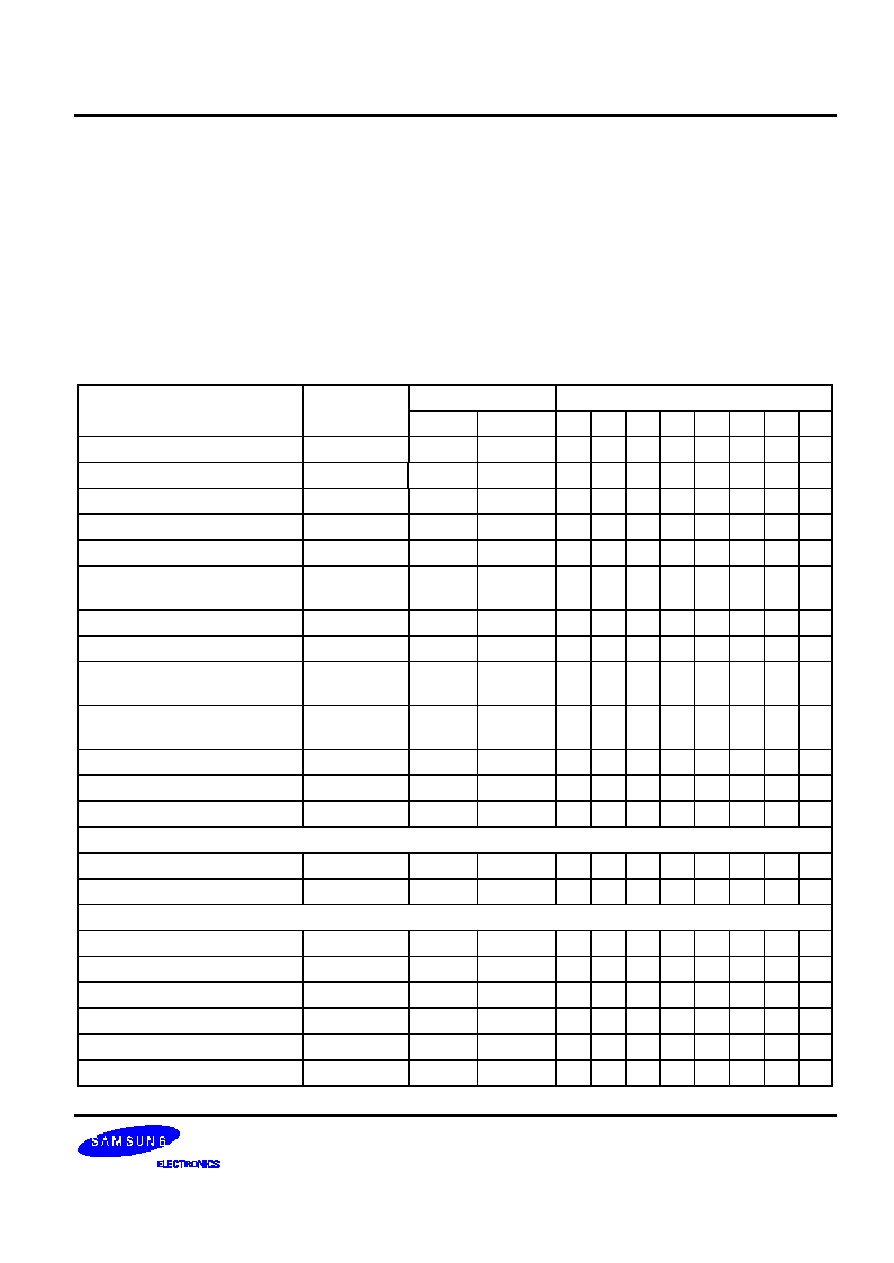

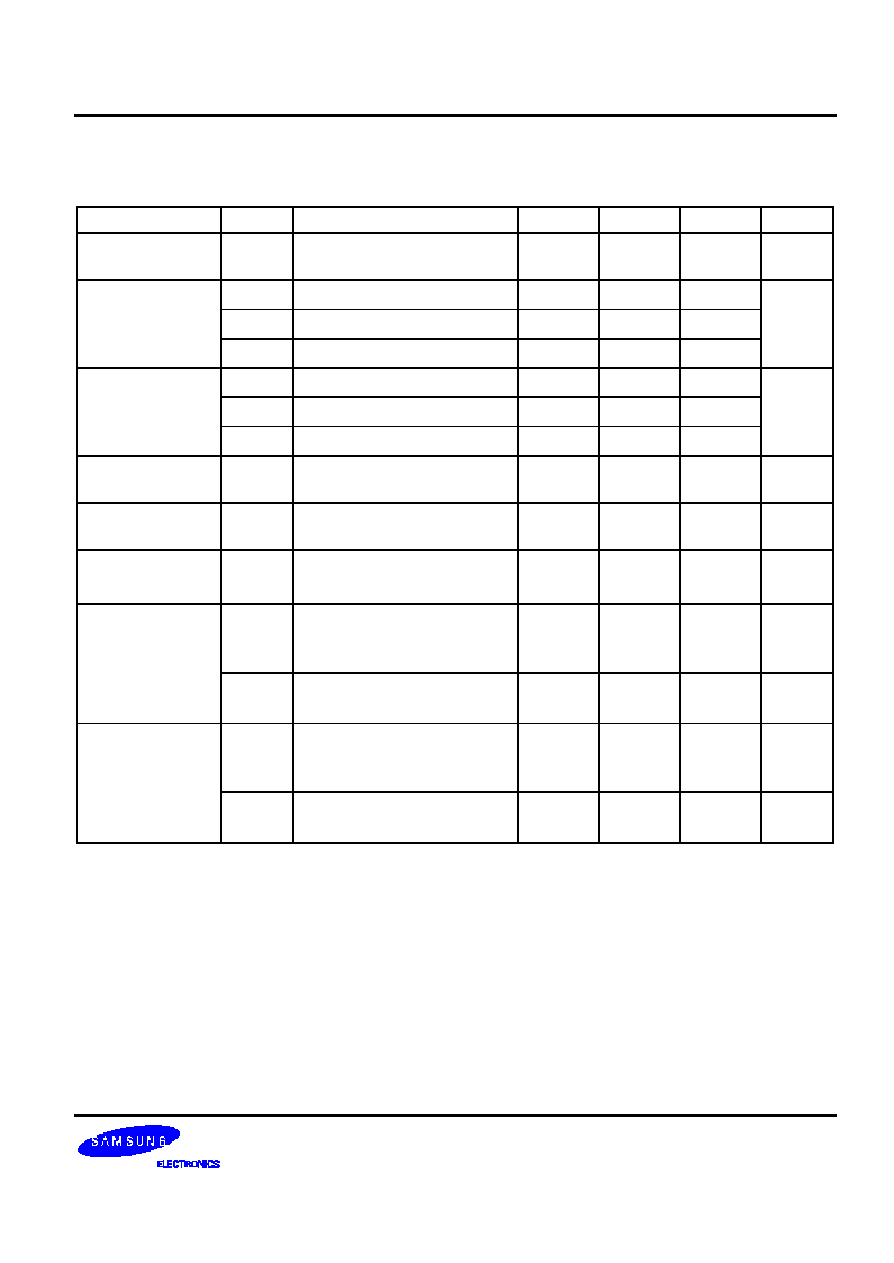

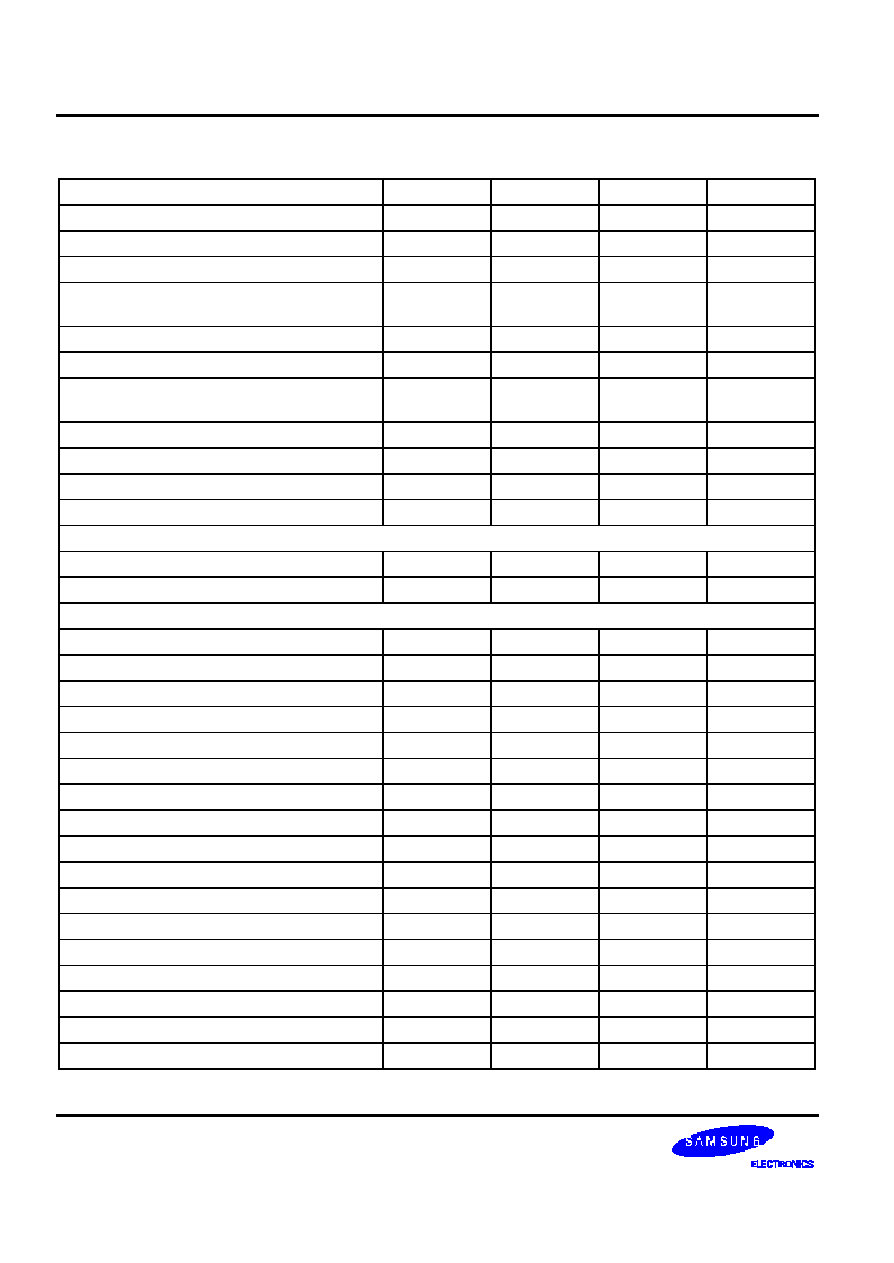

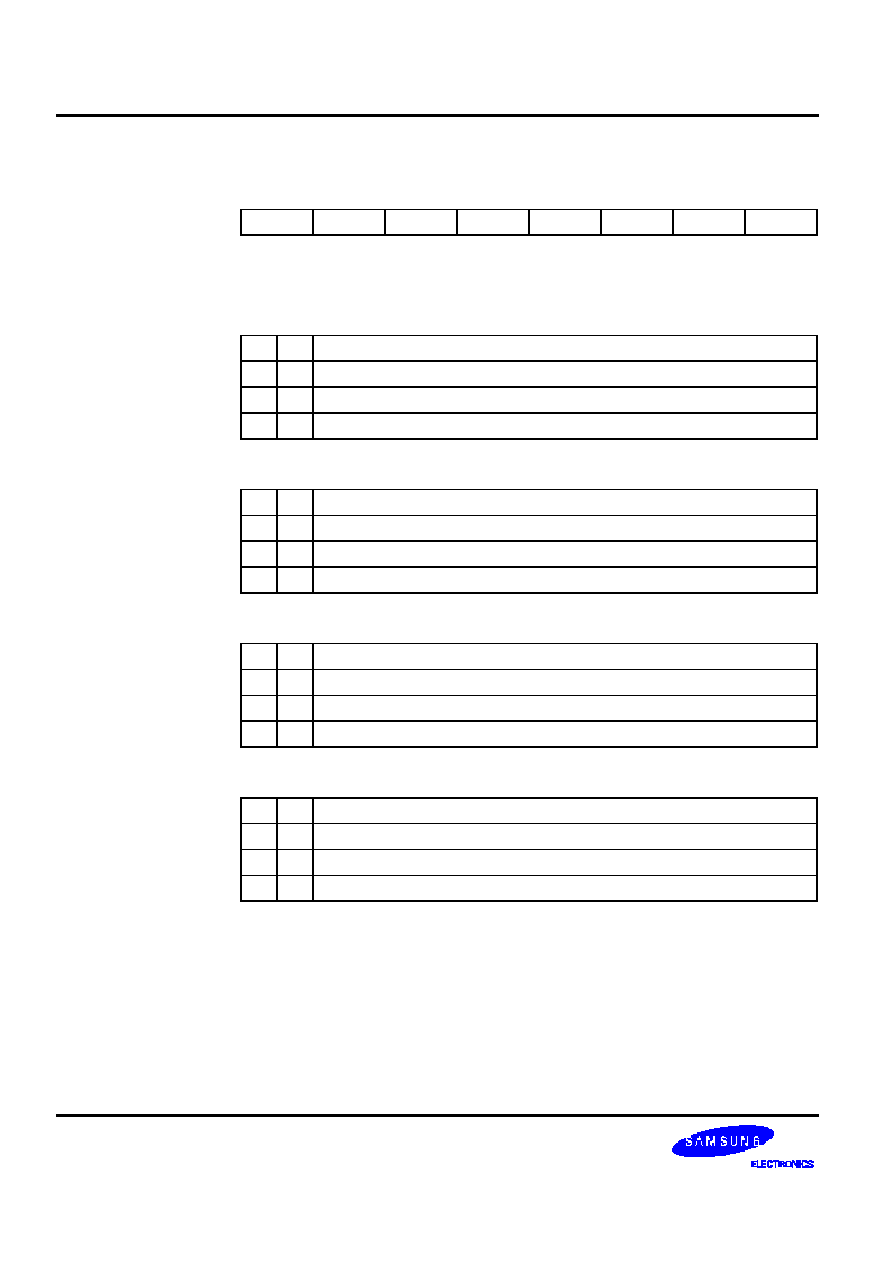

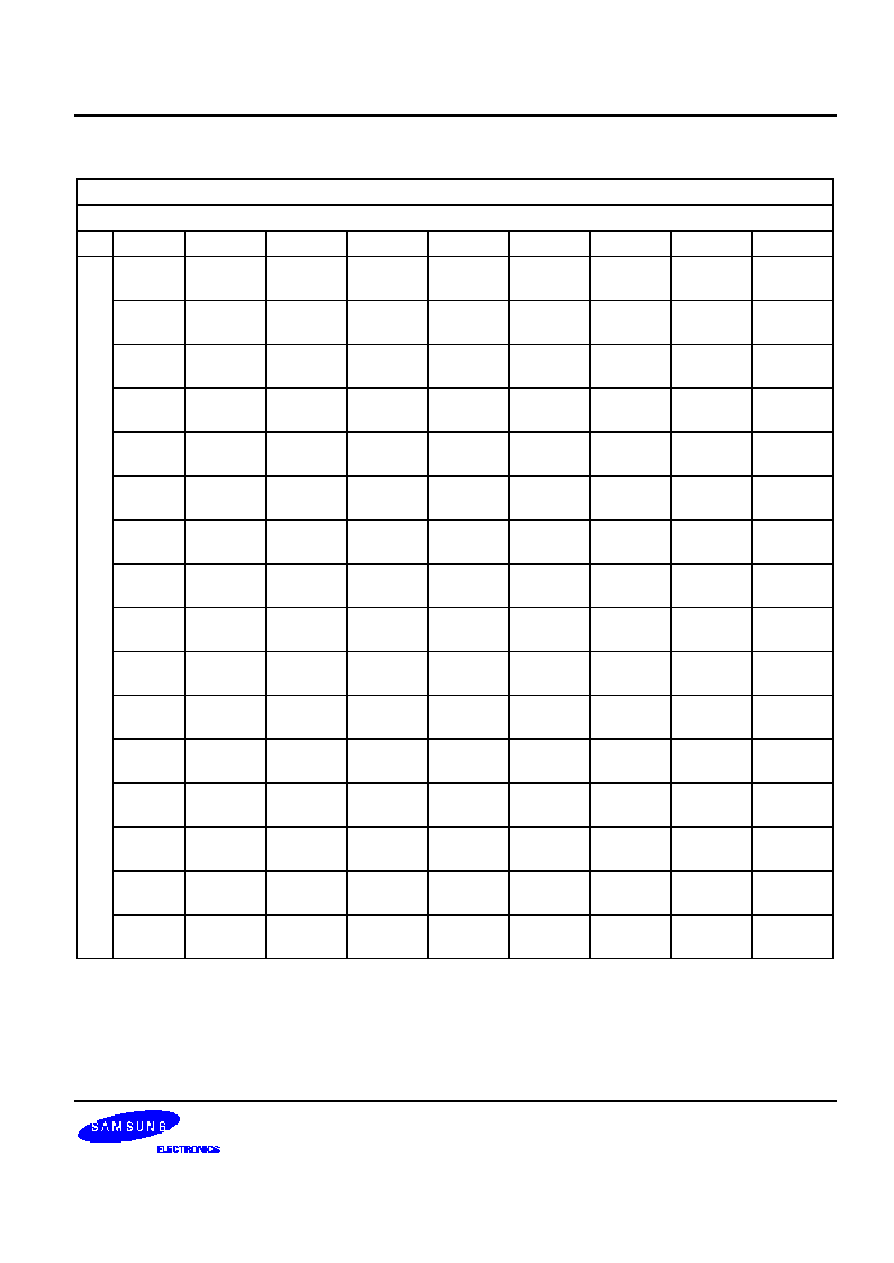

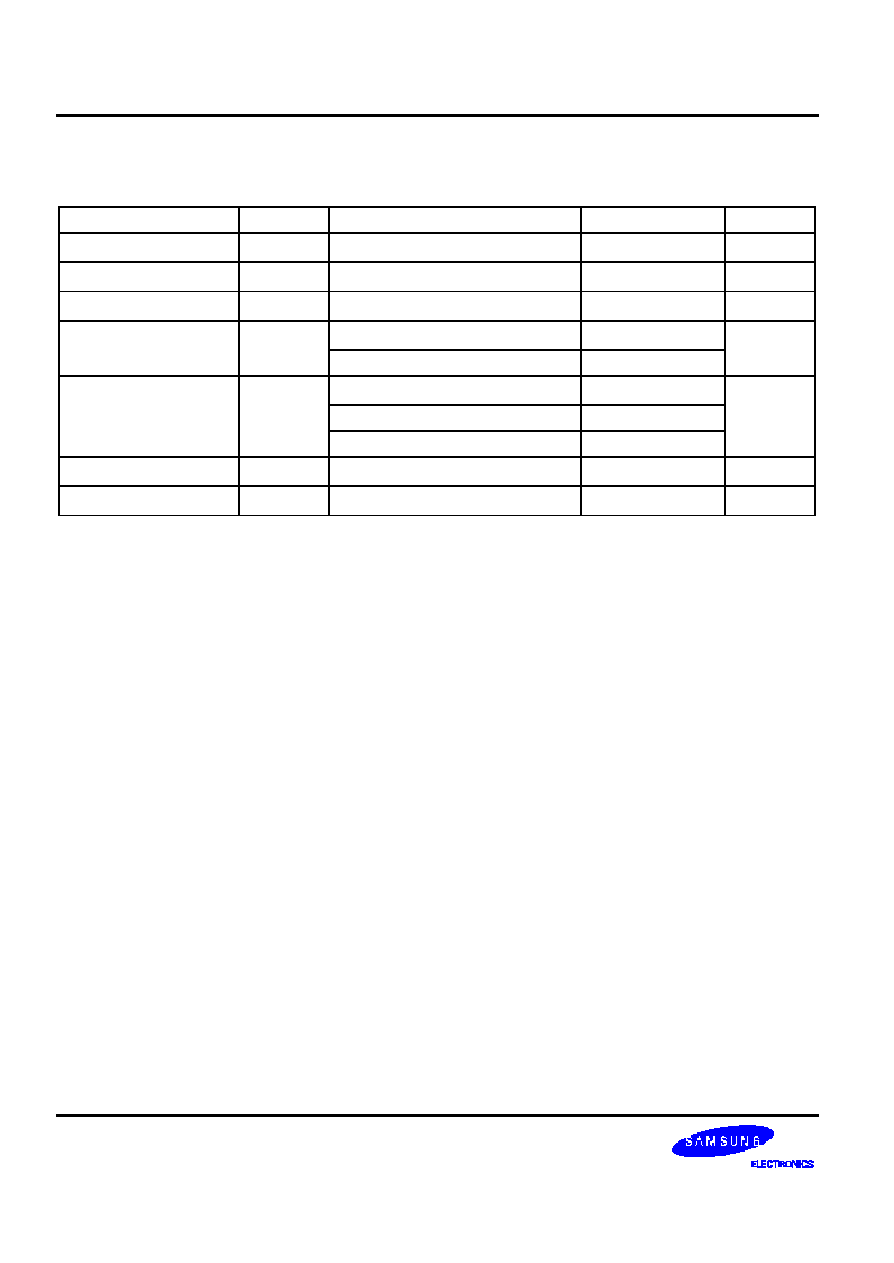

T a b l e 4 -1 . S y s t e m a n d P e r i p h e r a l c o n t r o l R e g i s t e r s

R e g i s t e r N a m e

M n e m o n i c

D e c i m a l

H e x

R / W

T i m e r 0 c o u n t e r r e g i s t e r

T 0 C N T

2 0 8

D 0 H

R

T i m e r 0 d a t a r e g i s t e r

T 0 D A T A

2 0 9

D 1 H

R / W

T i m e r 0 c o n t r o l r e g i s t e r

T 0 C O N

2 1 0

D 2 H

R / W

U S B s e l e c t i o n a n d T r a n s c e i v e r c r o s s o v e r p o i n t

c o n t r o l r e g i s t e r

U S X C O N

2 1 1

D 3 H

R / W

C l o c k c o n t r o l r e g i s t e r

C L K C O N

2 1 2

D 4 H

R / W

S y s t e m f l a g s r e g i s t e r

F L A G S

2 1 3

D 5 H

R / W

D + / P S 2 , D -/ P S 2 d a t a r e g i s t e r

( O n l y P S 2 M o d e )

P S 2 D A T A

2 1 4

D 6 H

R / W

P S 2 c o n t r o l a n d i n t e r r u p t p e n d i n g r e g i s t e r

P S 2 C O N I N T

2 1 5

D 7 H

R / W

Port 0 interrupt control register

P 0 I N T

2 1 6

D 8 H

R / W

S t a c k p o i n t e r

S P

2 1 7

D 9 H

R / W

Port 0 interrupt pending register

P 0 P N D

2 1 8

D A H

R / W

L o c a t i o n D B H i s n o t m a p p e d .

B a s i c t i m e r c o n t r o l r e g i s t e r

B T C O N

2 2 0

D C H

R / W

B a s i c t i m e r c o u n t e r r e g i s t e r

B T C N T

2 2 1

D D H

R

L o c a t i o n D E H i s n o t m a p p e d .

S y s t e m m o d e r e g i s t e r

S Y M

2 2 3

D F H

R / W

P o r t 0 d a t a r e g i s t e r

P 0

2 2 4

E 0 H

R / W

P o r t 1 d a t a r e g i s t e r

P 1

2 2 5

E 1 H

R / W

P o r t 2 d a t a r e g i s t e r

P 2

2 2 6

E 2 H

R / W

P o r t 3 d a t a r e g i s t e r

P 3

2 2 7

E 3 H

R / W

P o r t 4 d a t a r e g i s t e r

P 4

2 2 8

E 4 H

R / W

P o r t 3 c o n t r o l r e g i s t e r

P 3 C O N

2 2 9

E 5 H

R / W

P o r t 0 c o n t r o l r e g i s t e r ( h i g h b y t e )

P 0 C O N H

2 3 0

E 6 H

R / W

P o r t 0 c o n t r o l r e g i s t e r ( l o w b y t e )

P 0 C O N L

2 3 1

E 7 H

R / W

P o r t 1 c o n t r o l r e g i s t e r ( h i g h b y t e )

P 1 C O N H

2 3 2

E 8 H

R / W

P o r t 1 c o n t r o l r e g i s t e r ( l o w b y t e )

P 1 C O N L

2 3 3

E 9 H

R / W

P o r t 2 c o n t r o l r e g i s t e r ( h i g h b y t e )

P 2 C O N H

2 3 4

E A H

R / W

P o r t 2 c o n t r o l r e g i s t e r ( l o w b y t e )

P 2 C O N L

2 3 5

E B H

R / W

Port 2 interrupt control register

P 2 I N T

2 3 6

E C H

R / W

Port 2 interrupt pending register

P 2 P N D

2 3 7

E D H

R / W

P o r t 4 c o n t r o l r e g i s t e r

P 4 C O N

2 3 8

E E H

R / W

Port 4 interrupt enable/pending register

P 4 I N T P N D

2 3 9

E F H

R / W

S 3 C 9 6 8 8 / P 9 6 8 8

CONTROL REGISTERS

4 -3

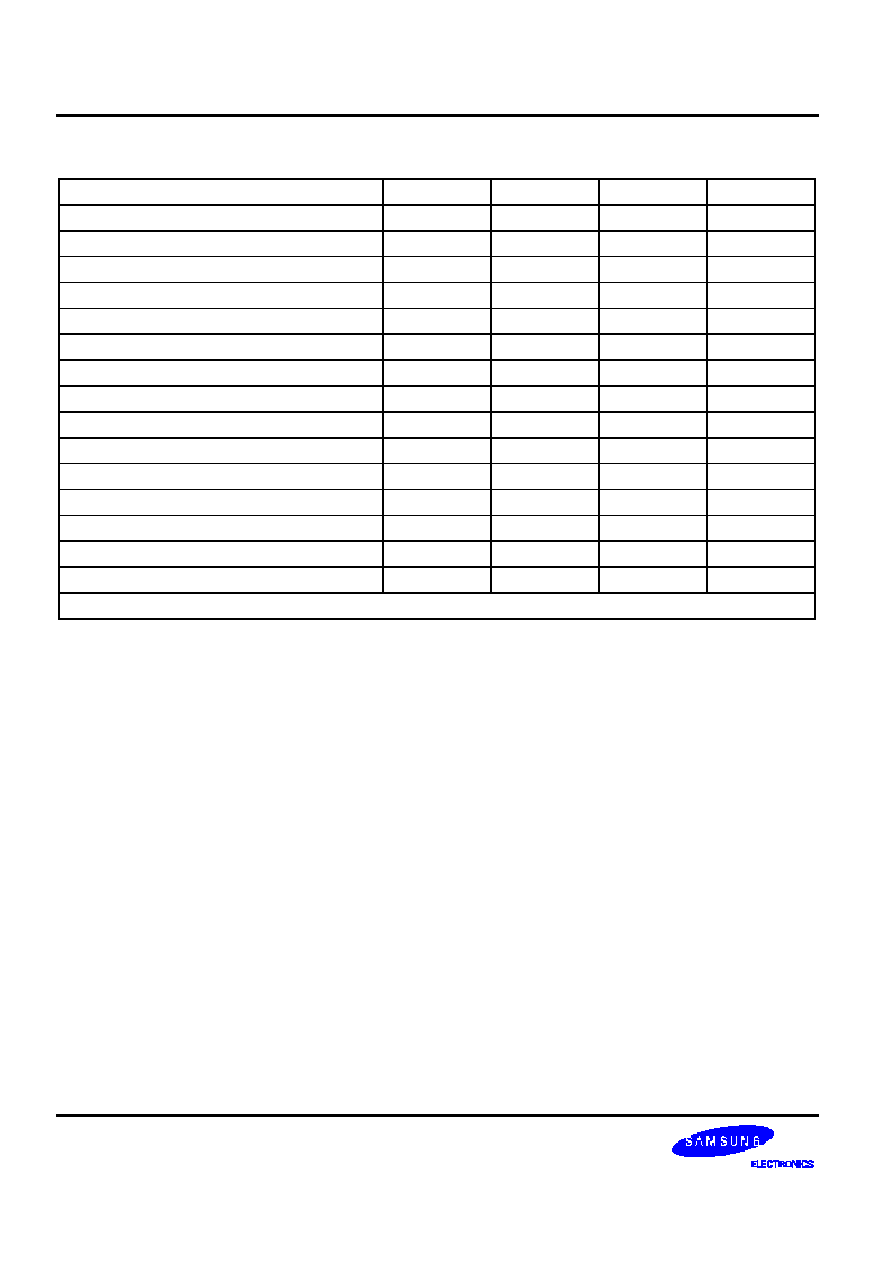

CONTROL REGISTERS

S 3 C 9 6 8 8 / P 9 6 8 8

4 -4

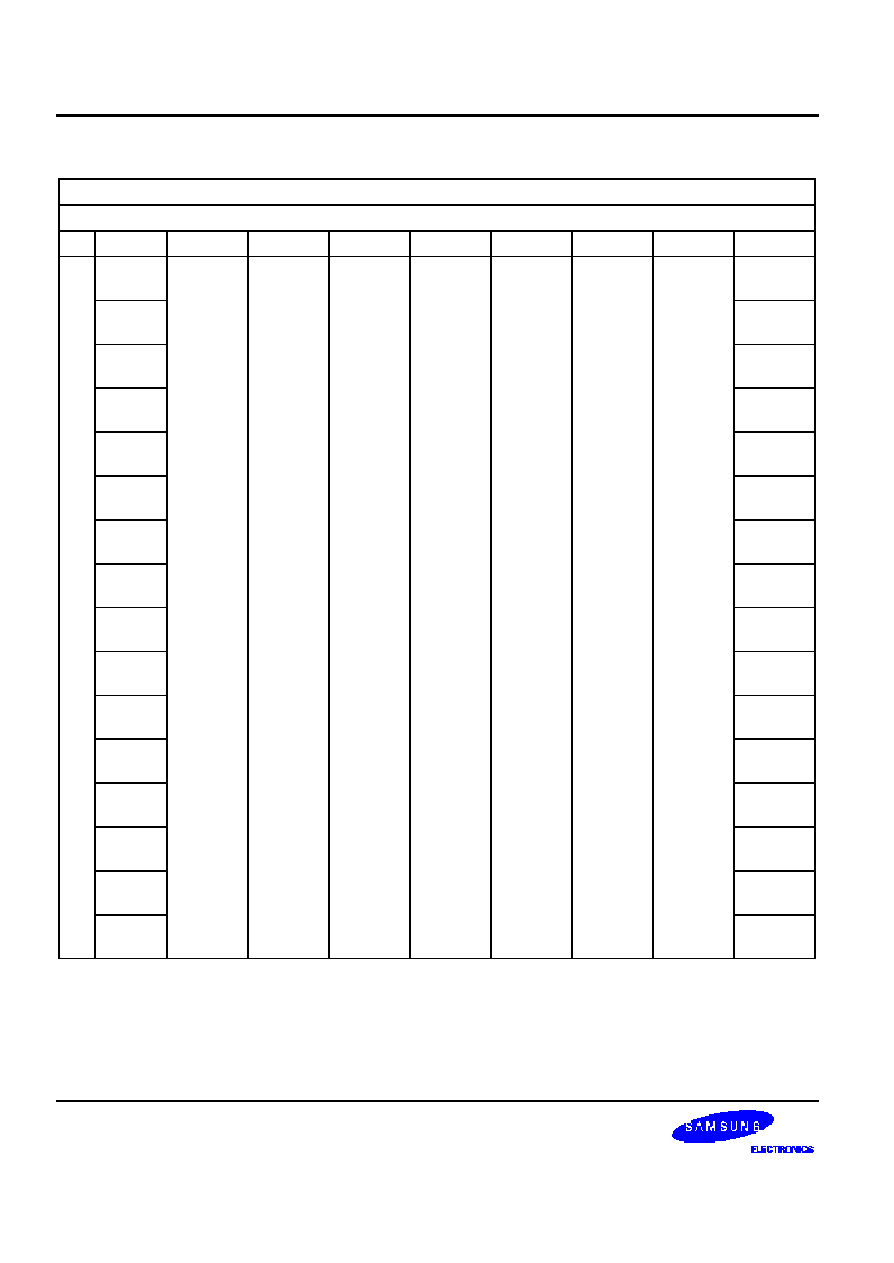

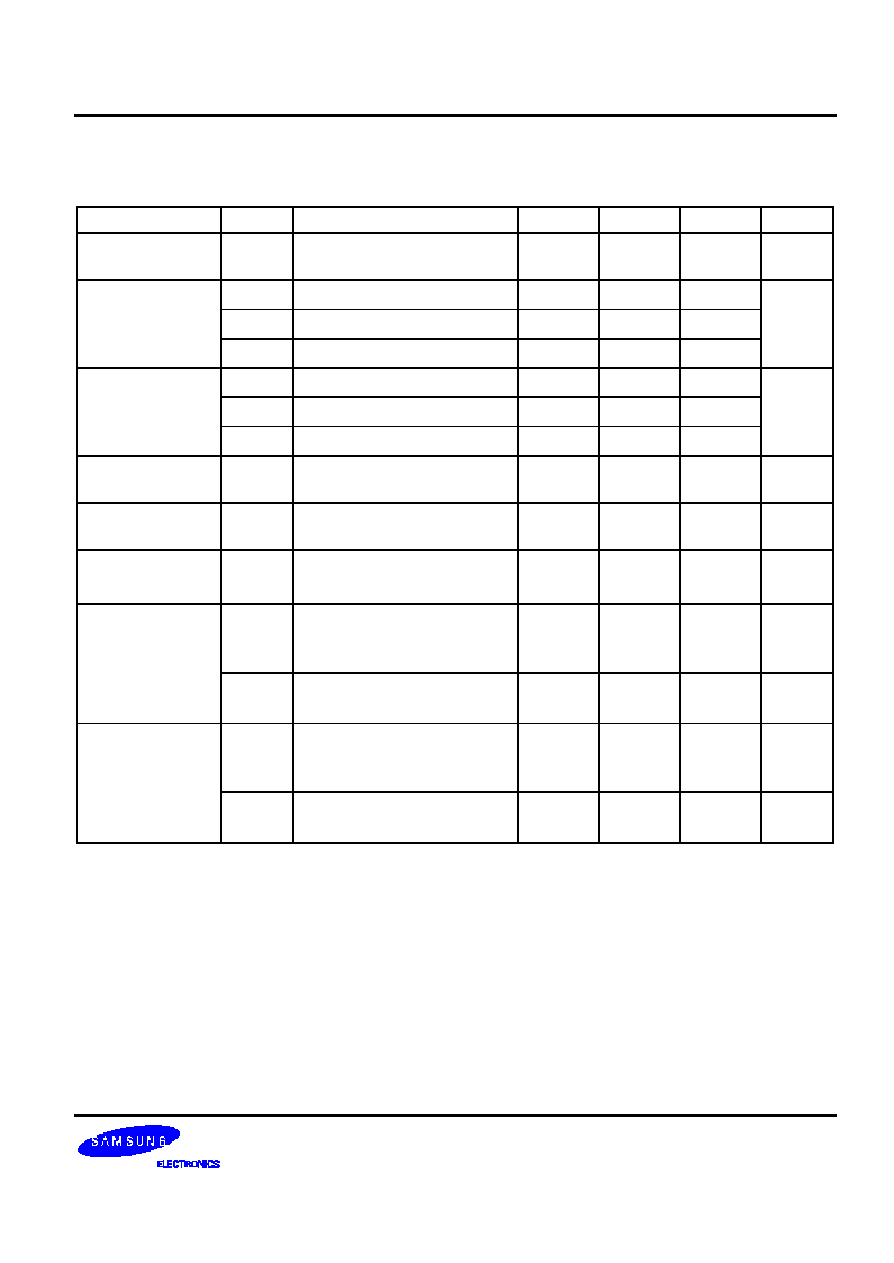

T a b l e 4 -1 . S y s t e m a n d P e r i p h e r a l c o n t r o l R e g i s t e r s ( C o n t i n u e d )

R e g i s t e r N a m e

M n e m o n i c

D e c i m a l

H e x

R / W

U S B f u n c t i o n a d d r e s s r e g i s t e r

F A D D R

2 4 0

F 0 H

R / W

C o n t r o l e n d p o i n t s t a t u s r e g i s t e r

E P 0 C S R

2 4 1

F 1 H

R / W

I n t e r r u p t e n d p o i n t 1 c o n t r o l s t a t u s r e g i s t e r

E P 1 C S R

2 4 2

F 2 H

R / W

Control endpoin t b y t e c o u n t r e g i s t e r

E P 0 B C N T

2 4 3

F 3 H

R / W

C o n t r o l e n d p o i n t F I F O r e g i s t e r

E P 0 F I F O

2 4 4

F 4 H

R / W

Interrupt endpoint 1 FIFO register

E P 1 F I F O

2 4 5

F 5 H

R / W

U S B i n t e r r u p t p e n d i n g r e g i s t e r

U S B P N D

2 4 6

F 6 H

R / W

U S B i n t e r r u p t e n a b l e r e g i s t e r

U S B I N T

2 4 7

F 7 H

R / W

U S B p o w e r m a n a g e m e n t r e g i s t e r

P W R M G R

2 4 8

F 8 H

R / W

I n t e r r u p t e n d p o i n t 2 c o n t r o l s t a t u s r e g i s t e r

E P 2 C S R

2 4 9

F 9 H

R / W

Interrupt endpoint 2 FIFO register

E P 2 F I F O

2 5 0

F A H

R / W

E n d p o i n t m o d e r e g i s t e r

E P M O D E

2 5 1

F B H

R / W

E n d p o i n t 1 b y t e c o u n t

E P 1 B C N T

2 5 2

F C H

R / W

E n d p o i n t 2 b y t e c o u n t

E P 2 B C N T

2 5 3

F D H

R / W

U S B c o n t r o l r e g i s t e r

U S B C O N

2 5 4

F E H

R / W

L o c a t i o n F F H i s n o t m a p p e d .

S 3 C 9 6 8 8 / P 9 6 8 8

CONTROL REGISTERS

4 -5

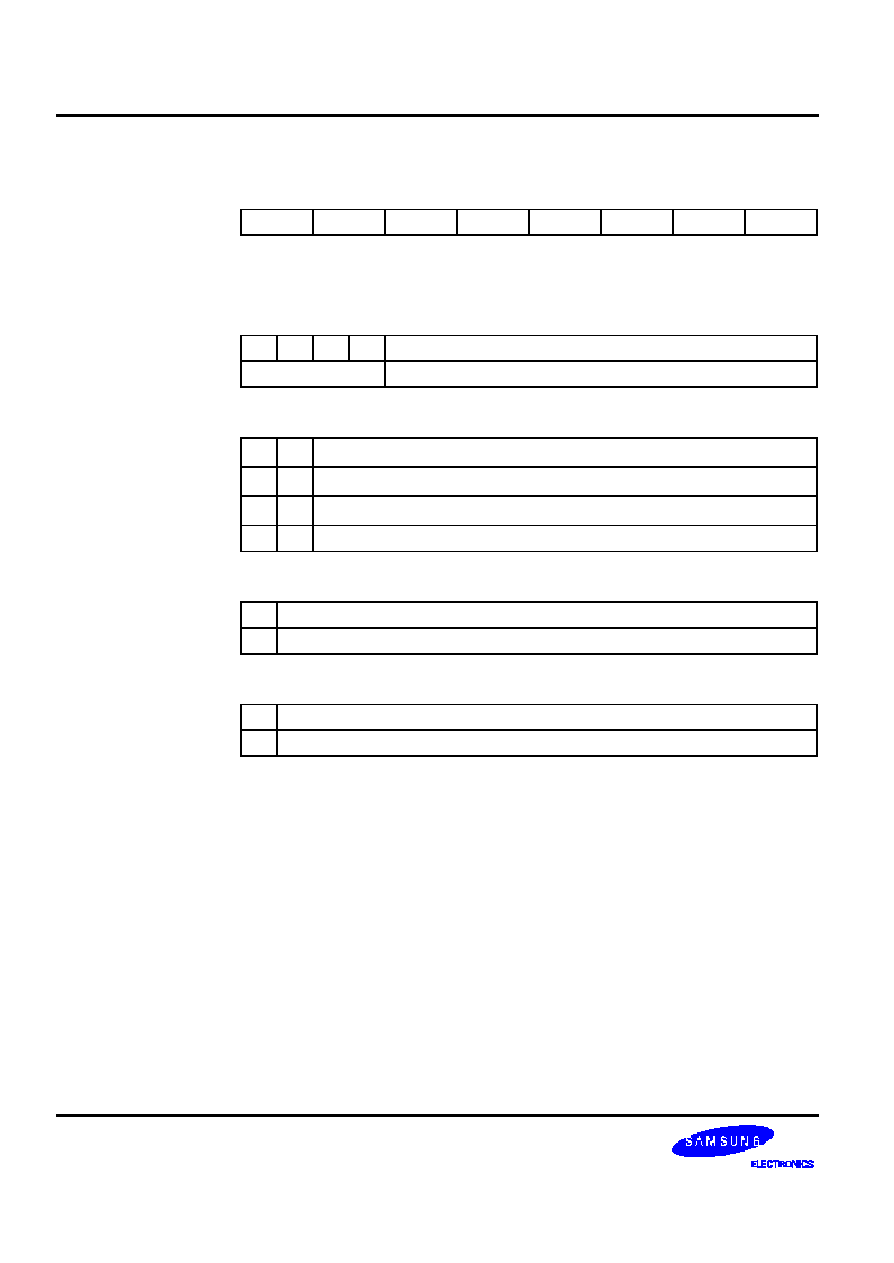

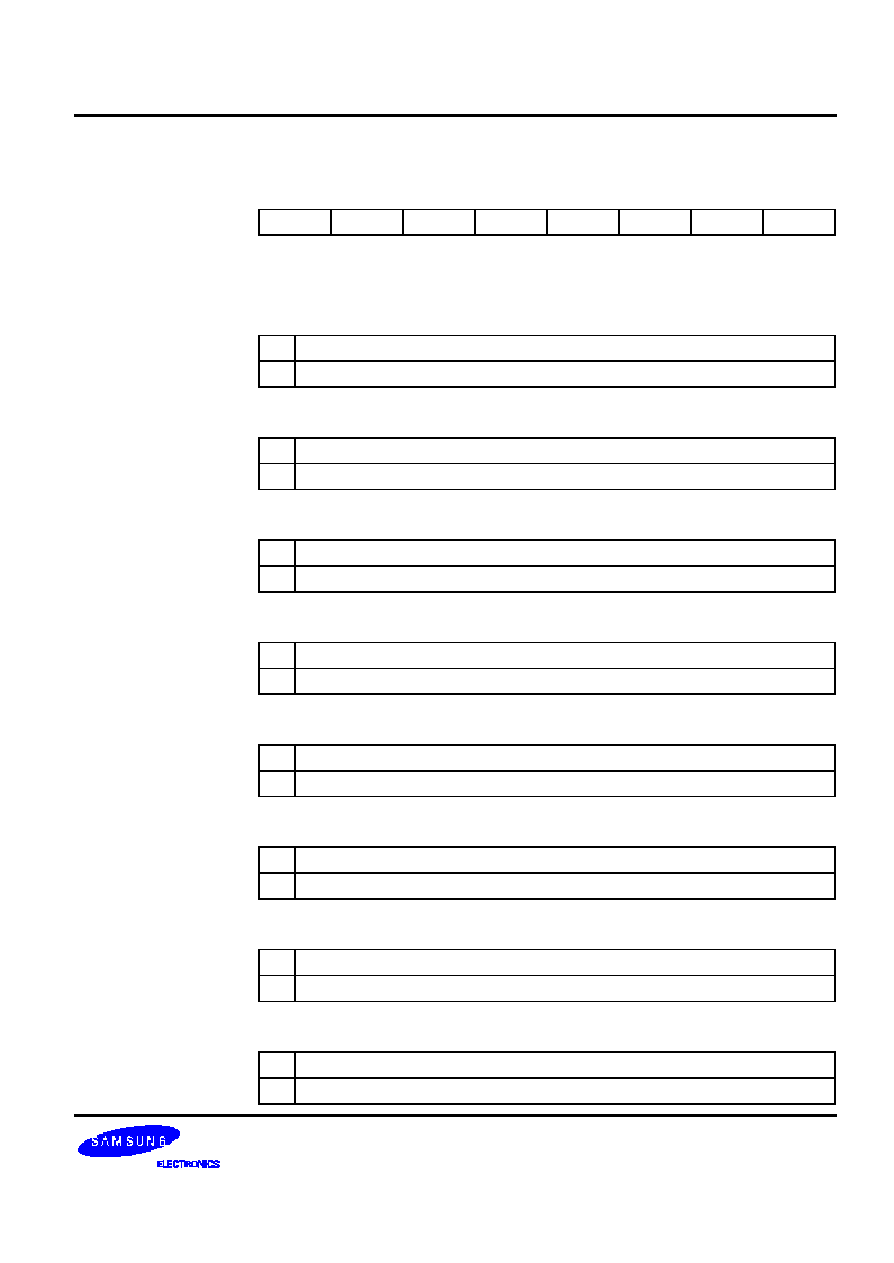

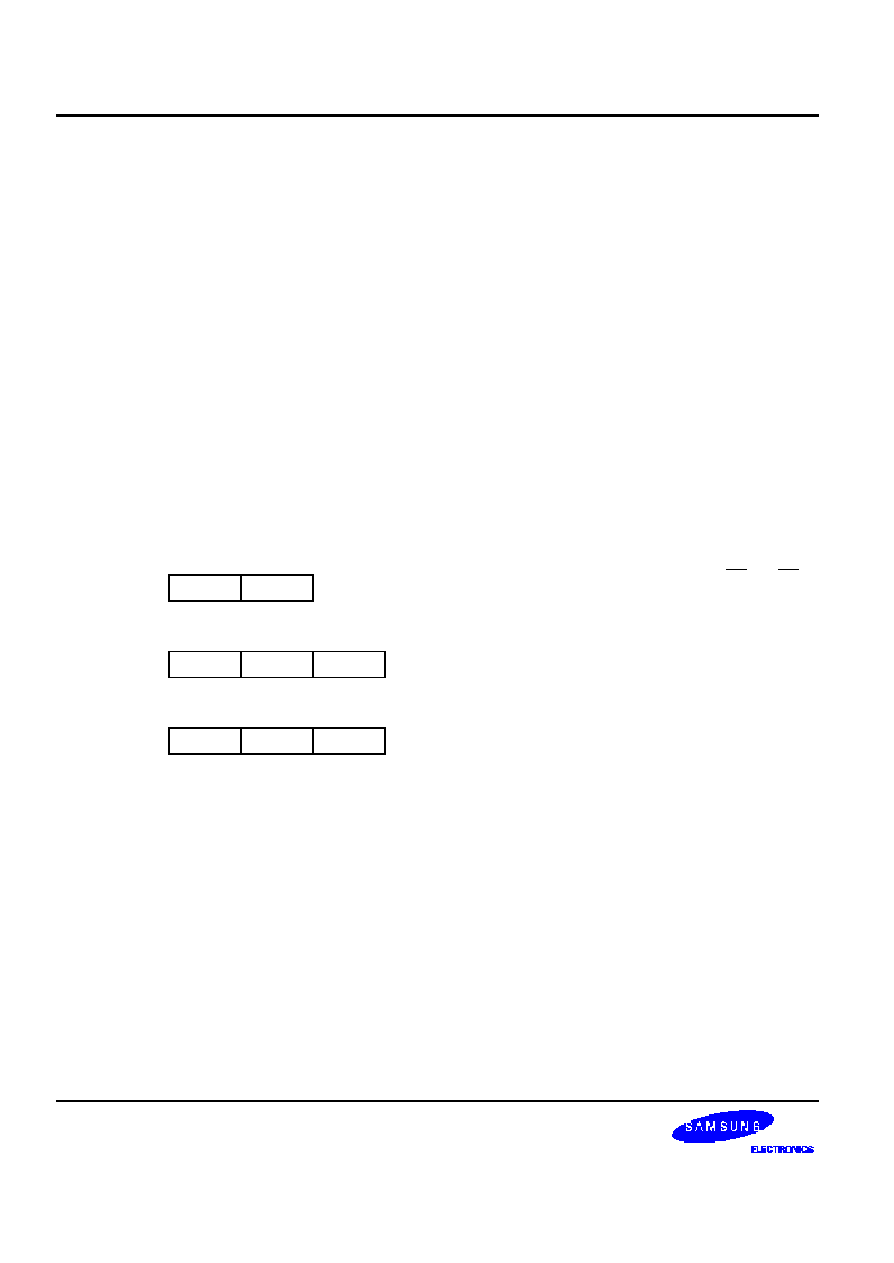

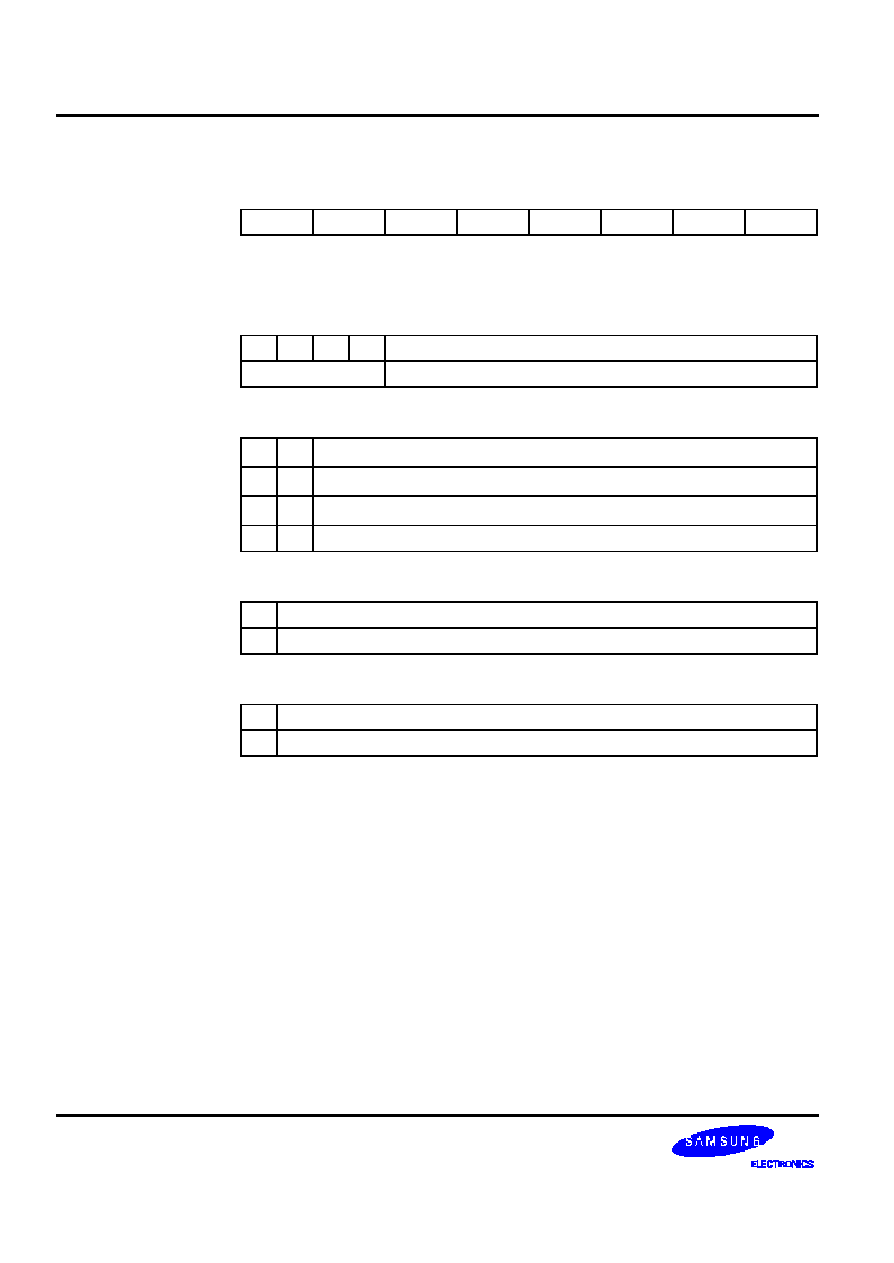

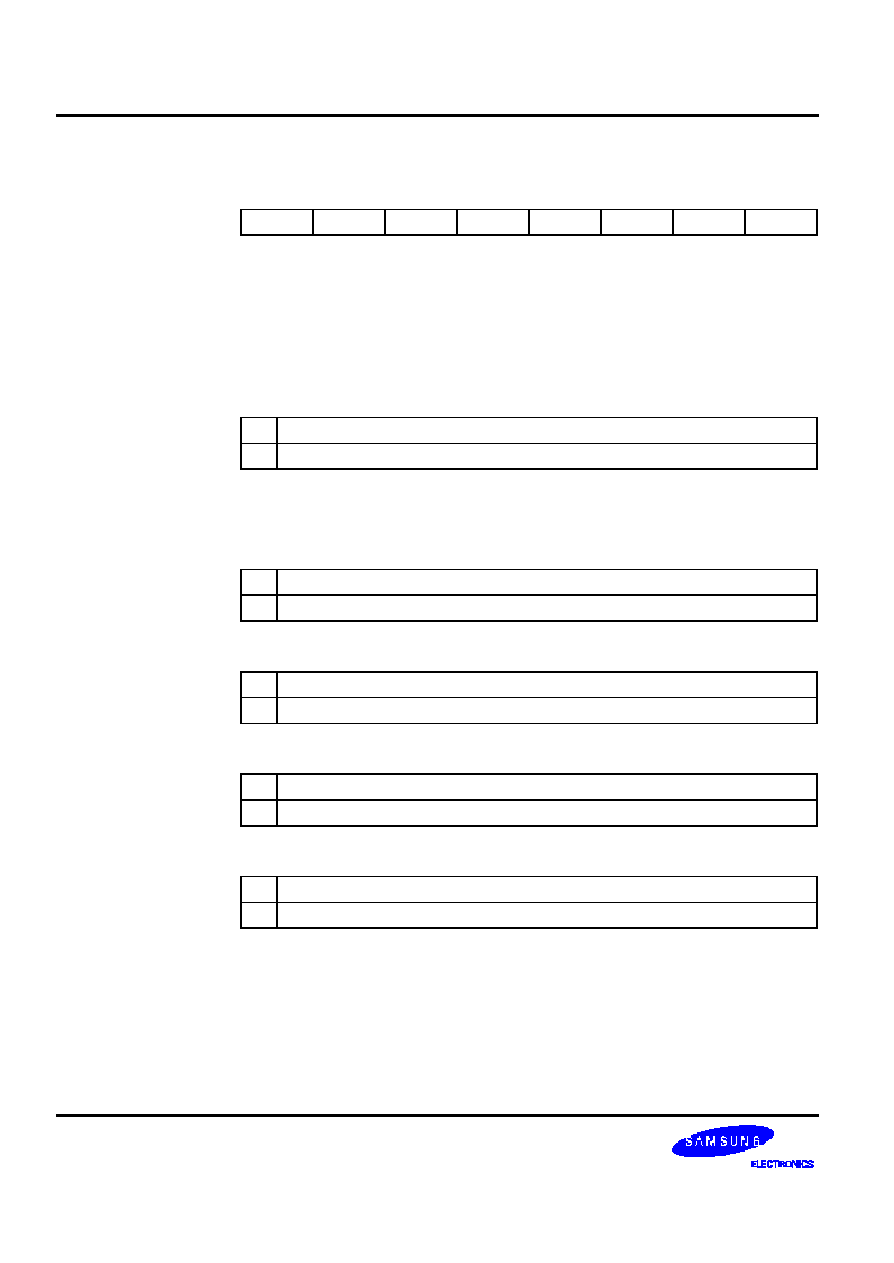

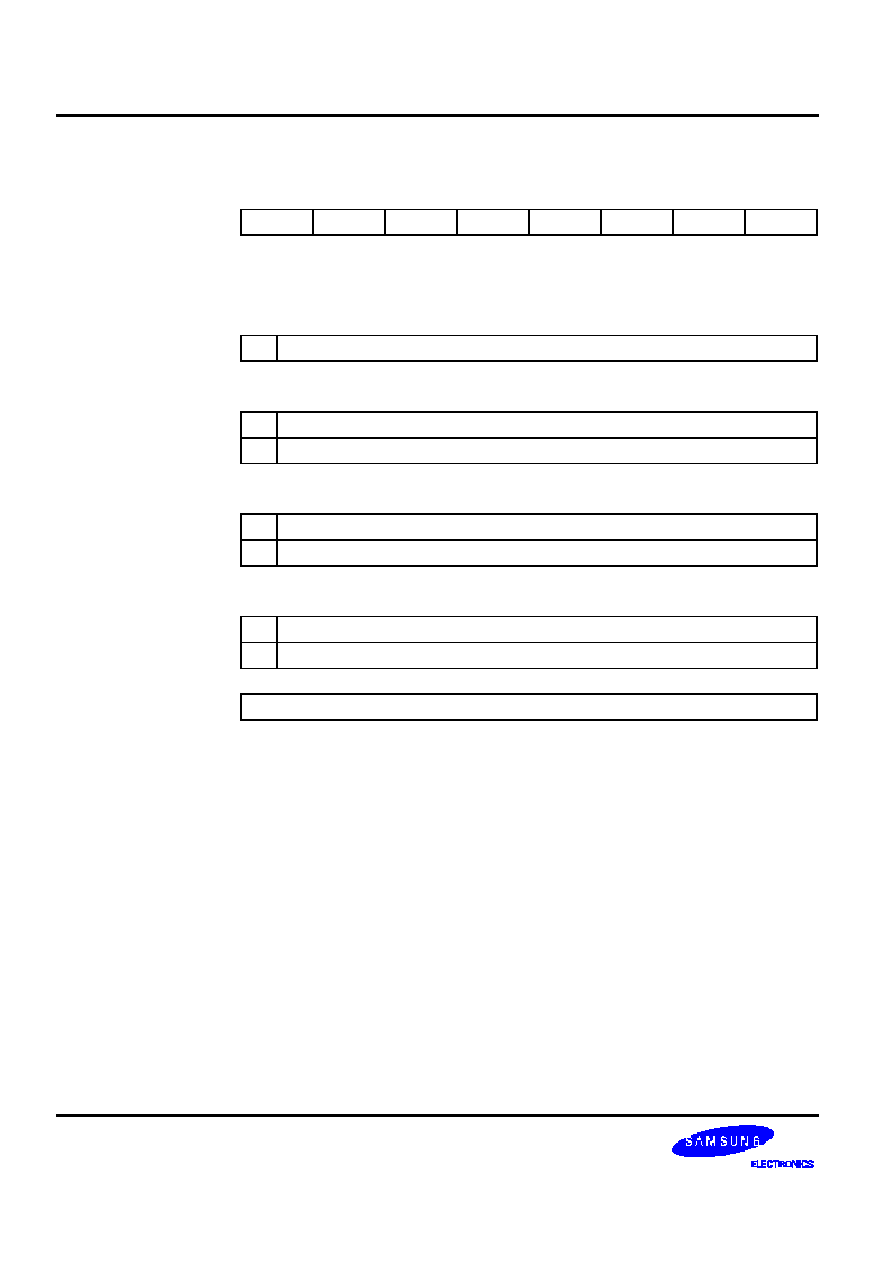

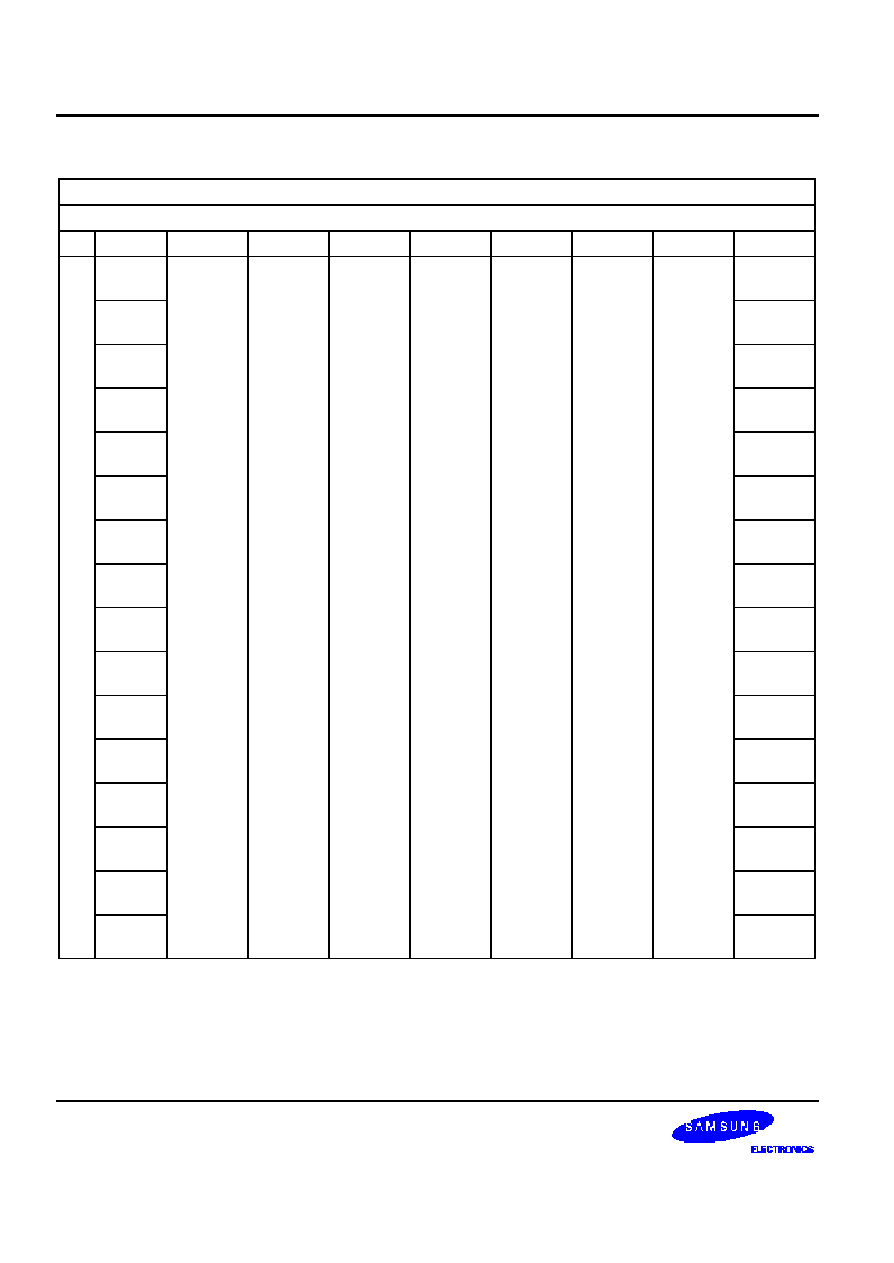

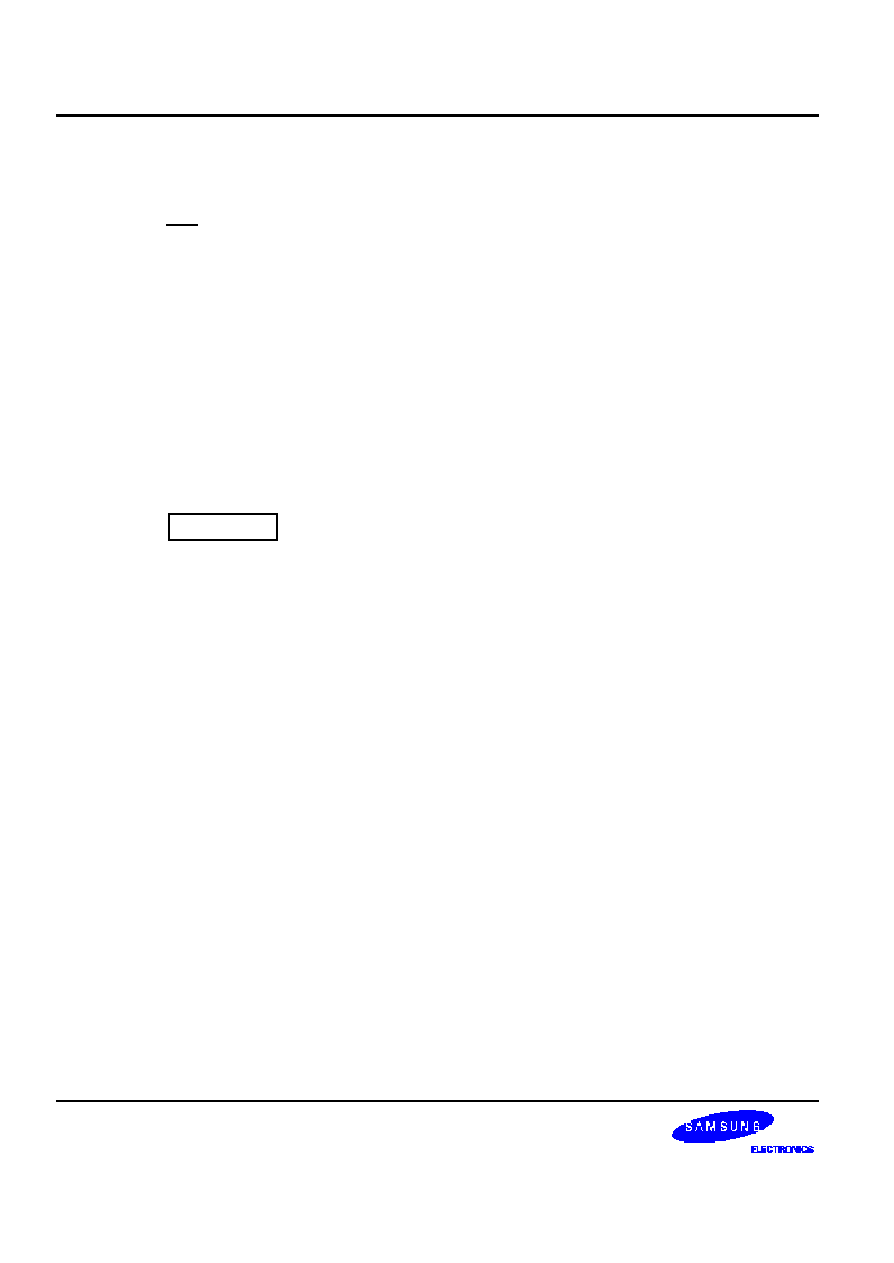

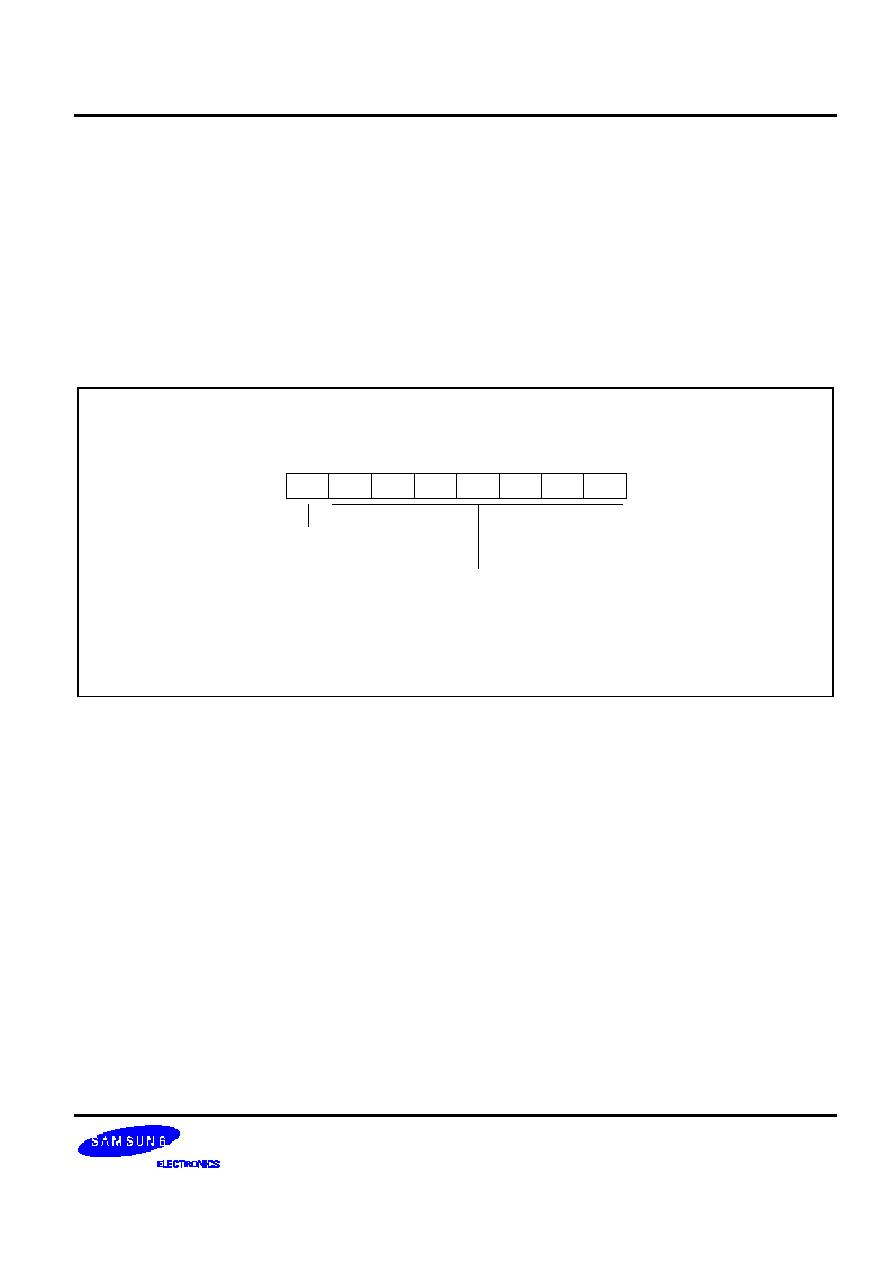

FLAGS

- System Flags Register

.7

.6

.5

Bit Identifier

RESET

Value

Read/Write

R = Read-only

W = Write-only

R/W = Read/write

' - ' = Not used

Bit number:

MSB = Bit 7

LSB = Bit 0

Addressing mode or

modes you can use to

modify register values

Description of the

effect of specific

bit settings

RESET

value notation:

'-' = Not used

'x' = Undetermind value

'0' = Logic zero

'1' = Logic one

Bit number(s) that is/are appended to the

register name for bit addressing

D5H

Register address

(hexadecimal)

Full Register name

Register

mnemonic

Name of individual

bit or bit function

.7

.6

.5

.4

.2

.3

.1

.0

x

R/W

x

R/W

x

R/W

x

R/W

0

R/W

x

R/W

0

R/W

x

R/W

Carry Flag (C)

0

Operation dose not generate a carry or borrow condition

1

Operation generates carry-out or borrow into high-order bit7

Zero Flag

0

Operation result is a non-zero value

1

Operation result is zero

Sign Flag

0

Operation generates positive number (MSB = "0")

1

Operation generates negative number (MSB = "1")

F i g u r e 4 -1 . R e g i s t e r D e s c r i p t i o n F o r m a t

CONTROL REGISTERS

S 3 C 9 6 8 8 / P 9 6 8 8

4 -6

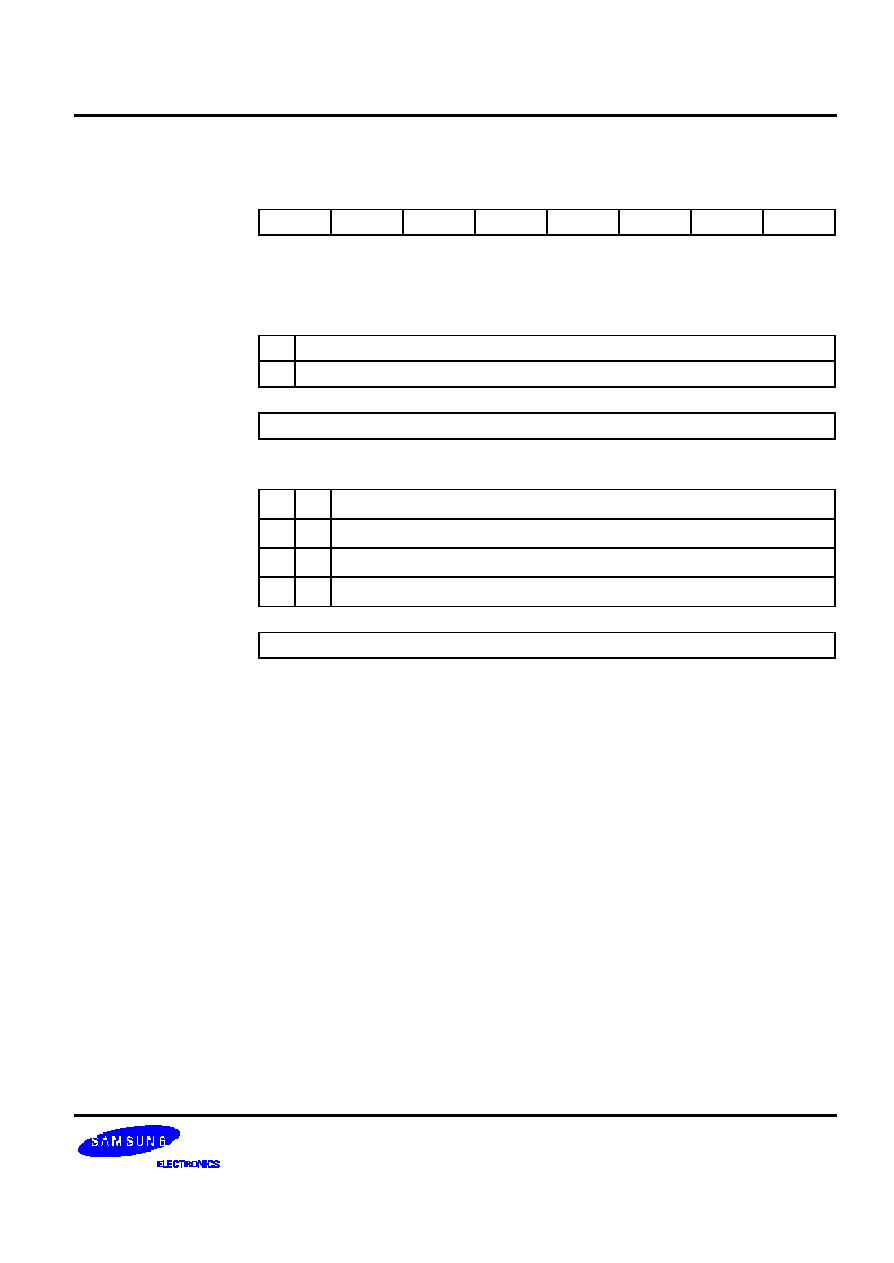

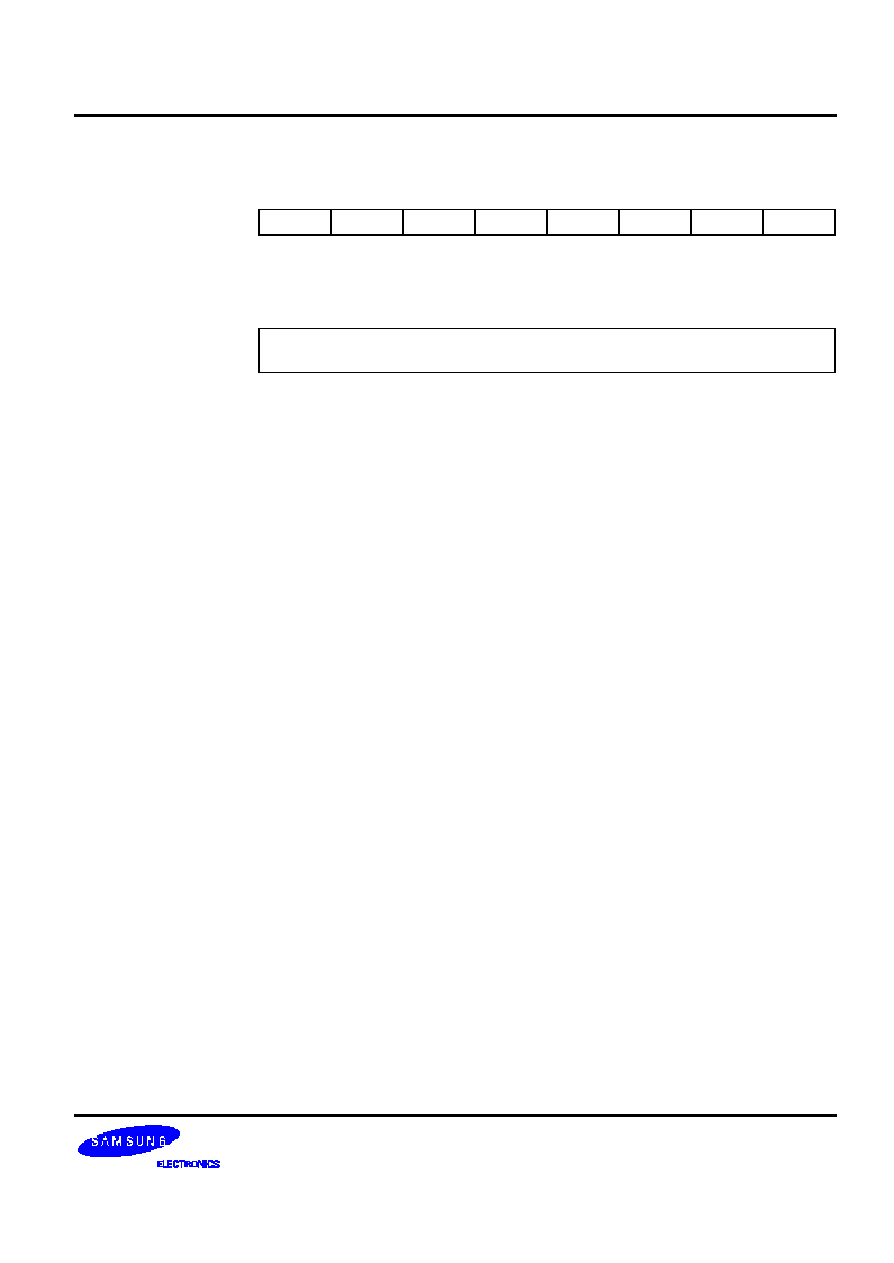

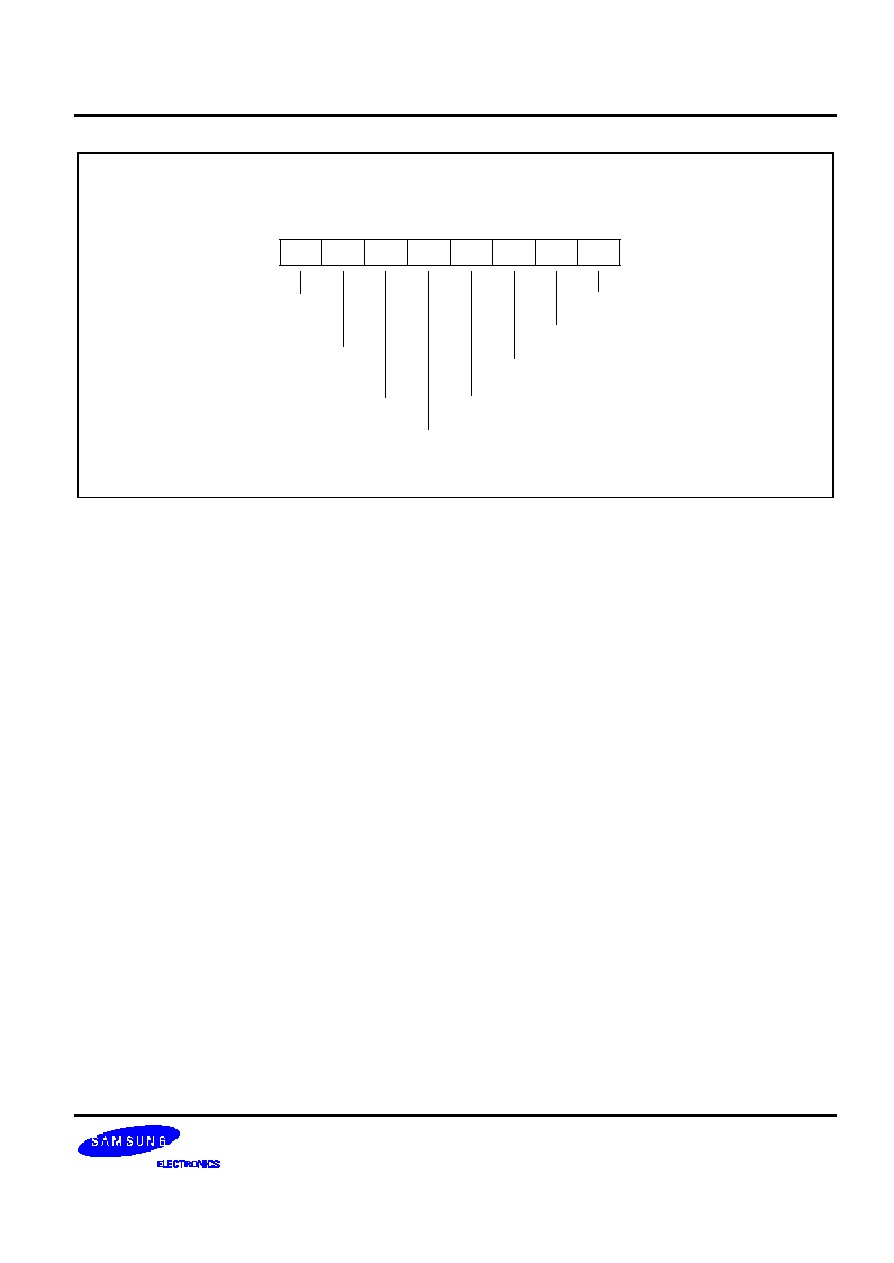

B T C O N

-- B a s i c T i m e r C o n t r o l R e g i s t e r

D C H

B i t I d e n t i f i e r

. 7

. 6

. 5

. 4

. 3

. 2

. 1

. 0

RESET

V a l u e

0

0

0

0

0

0

0

0

R e a d / W r i t e

R / W

R / W

R / W

R / W

R / W

R / W

R / W

R / W

. 7 -. 4

W a t c h d o g T i m e r E n a b l e B i t s

1

0

1

0

D i s a b l e w a t c h d o g f u n c t i o n

A n y o t h e r v a l u e

E n a b l e w a t c h d o g f u n c t i o n

. 3 a n d . 2

B a s i c T i m e r I n p u t C l o c k S e l e c t i o n B i t s

0

0

f

OSC

/ 4 0 9 6

0

1

f

OSC

/ 1 0 2 4

1

0

f

OSC

/ 1 2 8

1

1

Invalid setting

. 1

B a s i c T i m e r C o u n t e r C l e a r B i t

(note)

0

N o e f f e c t

1

C l e a r B T C N T

. 0

B a s i c T i m e r D i v i d e r C l e a r B i t

(note)

0

N o e f f e c t

1

Clear both dividers

NOTE:

When you write a "1" to BTCON.0 (or BTCON.1), the basic timer counter (or basic timer divider) is cleared. The bit

is then cleared automatically to "0".

S 3 C 9 6 8 8 / P 9 6 8 8

CONTROL REGISTERS

4 -7

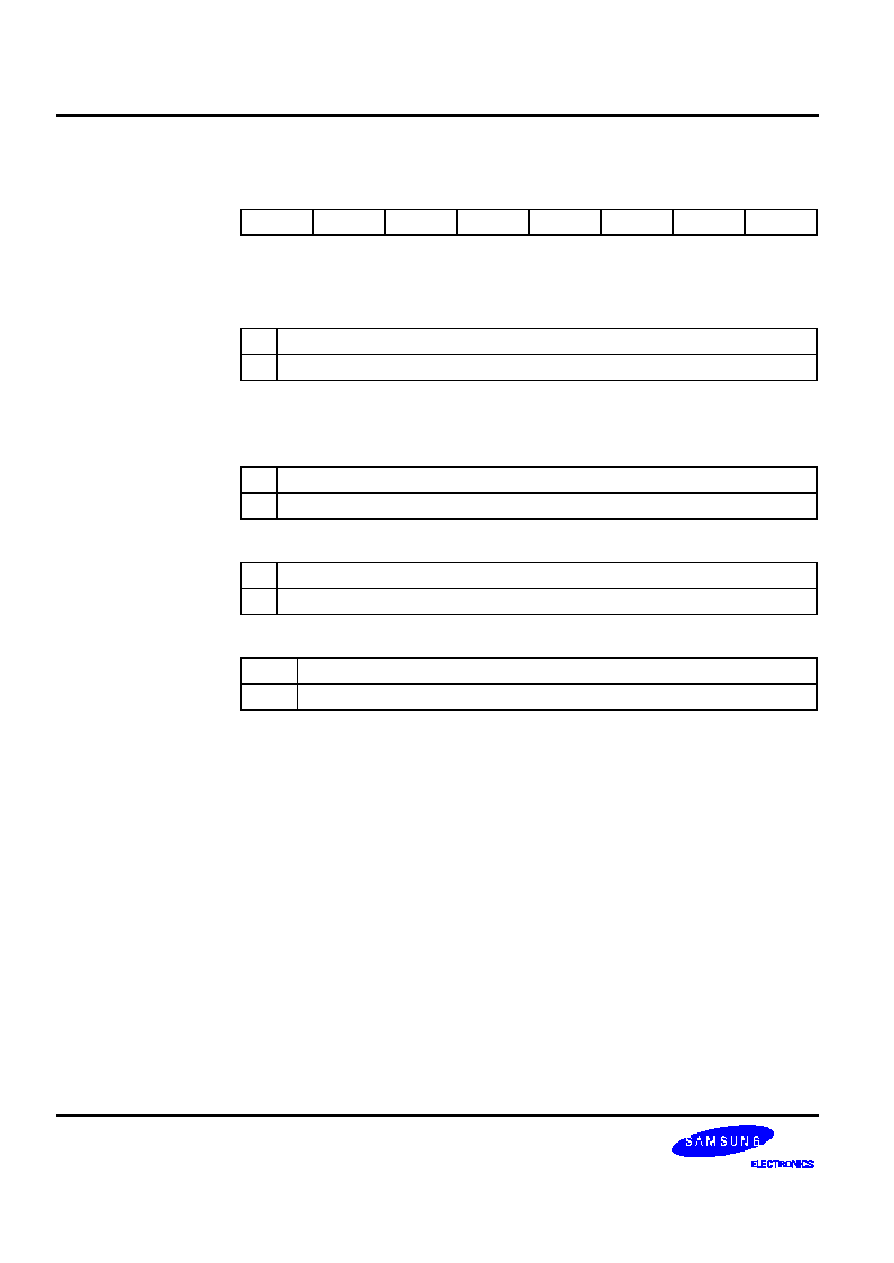

C L K C O N

-- S y s t e m C l o c k C o n t r o l R e g i s t e r

D 4 H

B i t I d e n t i f i e r

. 7

. 6

. 5

. 4

. 3

. 2

. 1

. 0

RESET

V a l u e

0

≠

≠

0

0

≠

≠

≠

R e a d / W r i t e

R / W

≠

≠

R / W

R / W

≠

≠

≠

. 7

O s c i l l a t o r I R Q W a k e -u p F u n c t i o n B i t

0

E n a b l e I R Q f o r m a i n s y s t e m o s c i l l a t o r w a k e-u p i n p o w e r d o w n m o d e

1

D i s a b l e I R Q f o r m a i n s y s t e m o s c i l l a t o r w a k e-u p i n p o w e r d o w n m o d e

. 6 a n d . 5

N o t u s e d f o r S 3 C 9 6 8 8 / P 9 6 8 8

. 4 a n d . 3

C P U C l o c k ( S y s t e m C l o c k ) S e l e c t i o n B i t s

(1)

0

0

Divide by 16 (f

OSC

/ 1 6 )

0

1

Divide by 8 (f

OSC

/ 8 )

1

0

Divide by 2 (f

OSC

/ 2 )

1

1

N o n -divided clock (f

OSC

)

(2)

. 2 ≠. 0

N o t u s e d f o r S 3 C 9 6 8 8 / P 9 6 8 8

NOTES

:

1.

After a reset, the slowest clock (divided by 16) is selected as the system clock. To select faster clock speeds, load the

appropriate values to CLKCON.3 and CLKCON.4.

2.

f

OSC

means oscillator frequency.

CONTROL REGISTERS

S 3 C 9 6 8 8 / P 9 6 8 8

4 -8

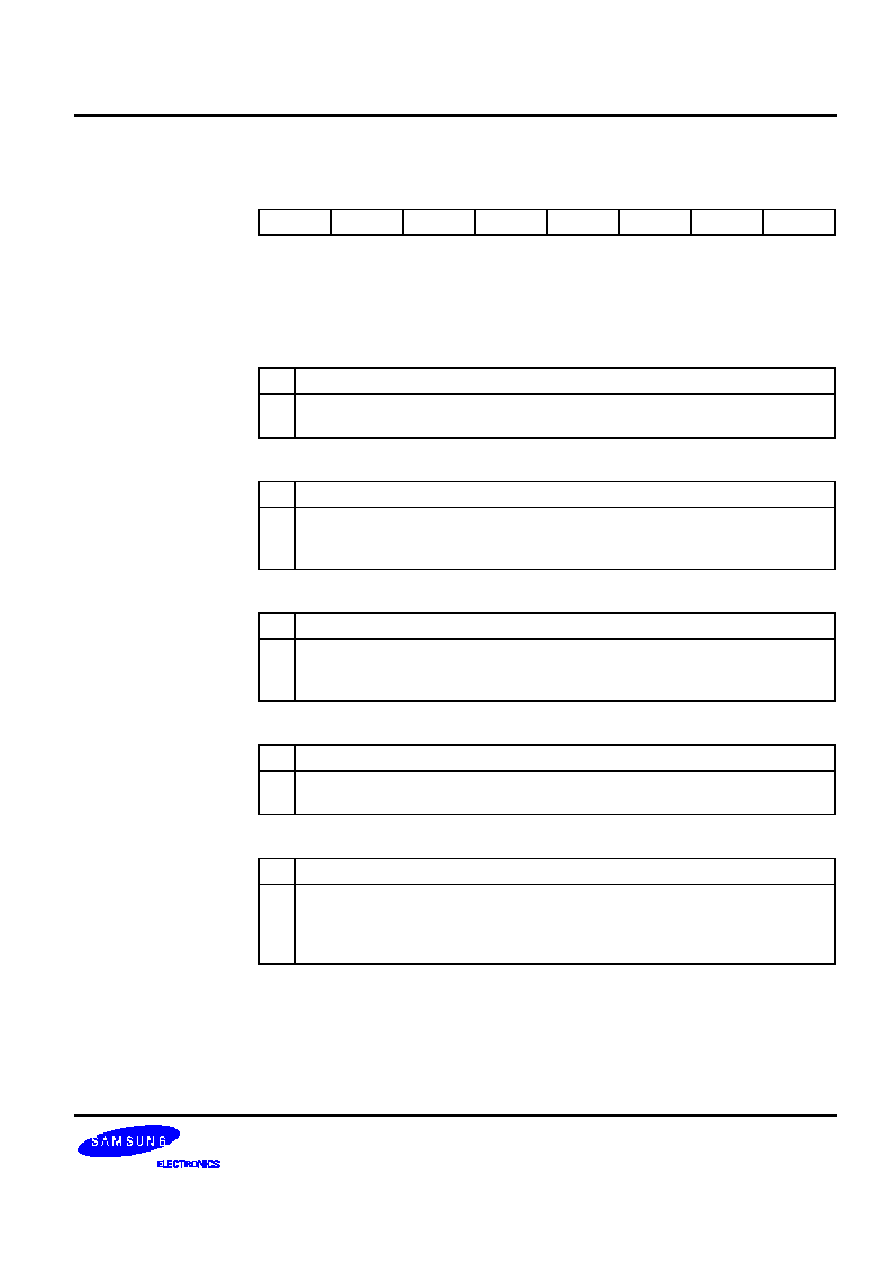

E P 0 B C N T

-- E n d p o i n t 0 W r i t e C o u n t e r R e g i s t e r

F 3 H

B i t I d e n t i f i e r

. 7

. 6

. 5

. 4

. 3

. 2

. 1

. 0

RESET

V a l u e

0

0

0

0

0

0

0

0

R e a d / W r i t e

R

R

R

R / W

R

R

R

R

. 7

D a t a _ T o g g l e _ C h e c k B i t

0

D A T A 0 t r a n s a c t i o n t o g g l e

1

D A T A 1 t r a n s a c t i o n t o g g l e

. 6

S e t u p _ t r a n s a c t i o n B i t

0

N o t s e t u p t r a n s a c t i o n

1

S e t u p t r a n s a c t i o n

. 5

R C V _ O v e r _ 8 _ B Y T E B i t

0

N o r m a l O p e r a t i o n

1

Indicates over 8 bytes received

. 4

E n a b l e B i t

0

D i s a b l e E n d p o i n t 0

1

E n a b l e E n d p o i n t 0

. 3 ≠. 0

T h e B y t e c o u n t e r o f D a t a t h a t s t o r e d i n E n d p o i n t 0

0 0 0 0

M i n i m u m b y t e s s t o r e d i n E n d p o i n t 0

1 0 0 0

M a x i m u m b y t e s s t o r e d i n E n d p o i n t 0

S 3 C 9 6 8 8 / P 9 6 8 8

CONTROL REGISTERS

4 -9

E P 0 C S R

-- C o n t r o l E n d p o i n t 0 S t a t u s R e g i s t e r

F 1 H

B i t I d e n t i f i e r

. 7

. 6

. 5

. 4

. 3

. 2

. 1

. 0

RESET

V a l u e

0

0

0

0

0

0

0

0

R e a d / W r i t e

R / W

R / W

R / W

R / W

R / W

R / W

R / W

R / W

. 7

S e t u p T r a n s f e r E n d C l e a r B i t

0

No effect (when write)

1

T o c l e a r S E T U P _ T R A N S F E R _ E N D b i t

. 6

O u t P a c k e t R e a d y C l e a r B i t

0

No effect (when write)

1

T o c l e a r O U T _ P K T _ R D Y b i t

. 5

S e n d i n g S t a l l B i t

0

No effect (when write)

1

T o s e n d S T A L L s i g n a l

. 4

S e t u p T r a n s f e r E n d B i t

0

No effect (when write)

1

S I E s e t s t h i s b i t w h e n a c o n t r o l t r a n s f e r e n d s b e f o r e D A T A _ E N D ( b i t 3 ) i s s e t

. 3

S e t u p D a t a E n d B i t

0

No effect (when write )

1

M C U s e t t h i s b i t a f t e r l o a d i n g o r u n l o a d i n g t h e l a s t p a c k e t d a t a i n t o t h e F I F O

. 2

S e n t S t a l l B i t

0

M C U c l e a r t h i s b i t t o e n d t h e S T A L L c o n d i t i o n

1

S I E s e t s t h i s b i t i f a c o n t r o l t r a n s a c t i o n i s e n d e d d u e t o a p r o t o c o l v i o l a t i o n

. 1

I n P a c k e t R e a d y B i t

0

S I E c l e a r t h i s b i t o n c e t h e p a c k e t h a s b e e n s u c c e s s f u l l y s e n t t o t h e h o s t

1

M C U s e t s t h i s b i t a f t e r w r i t i n g a p a c k e t o f d a t a i n t o E N D P O I N T 0 F I F O

. 0

O u t P a c k e t R e a d y B i t

0

No effect (when write)

1

S I E s e t s t h i s b i t o n c e a v a l i d t o k e n i s w r i t t e n t o t h e F I F O

CONTROL REGISTERS

S 3 C 9 6 8 8 / P 9 6 8 8

4 -1 0

S 3 C 9 6 8 8 / P 9 6 8 8

CONTROL REGISTERS

4 -1 1

EP0FIFO

-- E n d p o i n t 0 F I F O A d d r e s s R e g i s t e r

F 4 H

B i t I d e n t i f i e r

. 7

. 6

. 5

. 4

. 3

. 2

. 1

. 0

RESET

V a l u e

0

0

0

0

0

0

0

0

R e a d / W r i t e

R / W

R / W

R / W

R / W

R / W

R / W

R / W

R / W

. 7 ≠. 0

E n d p o i n t 0 F I F O

This register is bi-directional 8-b y t e d e p t h F I F O u s e d t o t r a n s f e r c o n t r o l E n d p o i n t 0

d a t a .

CONTROL REGISTERS

S 3 C 9 6 8 8 / P 9 6 8 8

4 -1 2

E P 1 B C N T

-- E n d p o i n t 1 W r i t e C o u n t e r R e g i s t e r

F C H

B i t I d e n t i f i e r

. 7

. 6

. 5

. 4

. 3

. 2

. 1

. 0

RESET

V a l u e

0

≠

0

0

0

0

0

0

R e a d / W r i t e

R

≠

R

R / W

R

R

R

R

. 7

D a t a _ T o g g l e _ C h e c k B i t

0

D A T A 0 t r a n s a c t i o n t o g g l e

1

D A T A 1 t r a n s a c t i o n t o g g l e

. 6

R e s e r v e d

. 5

R C V _ O v e r _ 8 _ B Y T E B i t

0

N o r m a l O p e r a t i o n

1

Indicates over 8 bytes received

. 4

E n a b l e B i t

0

D i s a b l e E n d p o i n t 1

1

E n a b l e E n d p o i n t 1

. 3 ≠. 0

T h e B y t e c o u n t e r o f D a t a t h a t s t o r e d i n E n d p o i n t 1

0 0 0 0

M i n i m u m b y t e s s t o r e d i n E n d p o i n t 1

1 0 0 0

M a x i m u m b y t e s s t o r e d i n E n d p o i n t 1

S 3 C 9 6 8 8 / P 9 6 8 8

CONTROL REGISTERS

4 -1 3

E P 1 C S R

-- C o n t r o l E n d p o i n t 1 S t a t u s R e g i s t e r

F 2 H

B i t I d e n t i f i e r

. 7

. 6

. 5

. 4

. 3

. 2

. 1

. 0

RESET

V a l u e

0

0

0

0

0

0

0

0

R e a d / W r i t e

R / W

R / W

R / W

R / W

R / W

R / W

R / W

R / W

a ) T h e b e l l o w s a r e c o n f i g u r e d a s I N m o d e

. 7

D a t a T o g g l e S e q u e n c e C l e a r B i t

0

No effect (when write)

1

M C U s e t s t h i s b i t t o c l e a r t h e d a t a t o g g l e s e q u e n c e b i t . T h e d a t a t o g g l e i s

i n i t i a l i z e d t o D A T A 0 .

. 6 ≠. 3

M a x i m u m P a c k e t S i z e B i t s

0

No effect (when write)

1

T h e s e b i t s i n d i c a t e t h e m a x i m u m p a c k e t s i z e f o r I N e n d p o i n t , a n d n e e d s t o b e

u p d a t e d b y t h e M C U b e f o r e i t s e t s I N _ P K T _ R D Y . O n c e s e t , t h e c o n t e n t s a r e

valid till MCU re -w r i t e s t h e m .

. 2

F I F O F l u s h B i t

0

No effect (when write)

1

W h e n M C U w r i t e s a o n e t o t h i s r e g i s t e r , t h e F I F O i s f l u s h e d , a n d I N _ P K T _ R D Y

c l e a r e d . T h e M C U s h o u l d w a i t f o r I N _ P K T _ R D Y t o b e c l e a r e d f o r t h e f l u s h t o t a k e

p l a c e .

. 1

F o r c e S T A L L B i t

0

No effect (when write)

1

M C U w r i t e s a 1 t o t h i s r e g i s t e r t o i s s u e a S T A L L h a n d s h a k e t o U S B . M C U c l e a r s

t h i s b i t , t o e n d t h e S T A L L c o n d i t i o n .

. 0

I n P a c k e t R e a d y B i t

0

S I E c l e a r t h i s b i t o n c e t h e p a c k e t h a s b e e n s u c c e s s f u l l y s e n t t o t h e h o s t

1

M C U s e t s t h i s b i t , a f t e r w r i t i n g a p a c k e t o f d a t a i n t o E N D P O I N T 1 F I F O . U S B

c l e a r s t h i s b i t , o n c e t h e p a c k e t h a s b e e n s u c c e s s f u l l y s e n t t o t h e h o s t . A n

i n t e r r u p t i s g e n e r a t e d w h e n U S B c l e a r s t h i s b i t , s o M C U c a n l o a d t h e n e x t

p a c k e t .

CONTROL REGISTERS

S 3 C 9 6 8 8 / P 9 6 8 8

4 -1 4

E P 1 C S R

-- C o n t r o l E n d p o i n t 1 S t a t u s R e g i s t e r

F 2 H

B i t I d e n t i f i e r

. 7

. 6

. 5

. 4

. 3

. 2

. 1

. 0

RESET

V a l u e

≠

0

≠

≠

0

0

0

0

R e a d / W r i t e

≠

R / W

≠

≠

R / W

R / W

R / W

R / W

b ) T h e b e l l o w s a r e c o n f i g u r e d a s O U T m o d e

. 7

R e s e r v e d

. 6

C L R _ O U T _ P K T _ R D Y B i t

0

No effect (when write)

1

C l e a r O U T _ P K T _ R D Y ( b i t 0 ) b i t . .

. 5 ≠. 4

R e s e r v e d

. 3

R C V _ S T A L L _ S I G B i t

0

M C U c a n c l e a r t h i s b i t

1

S I E s e t s t h i s b i t a f t e r s e n d i n g s t a l l p a c k e t

. 2

F L U S H _ F I F O B i t

0

No effect (when write)

1

F I F O i s f l u s h e d , a n d O U T _ P K T _ R D Y b i t i s c l e a r e d . .

. 1

F O R C E _ S T A L L B i t

0

M C U c l e a r s t h i s b i t t o e n d t h e S T A L L c o n d i t i o n

1

I s s u e s a S T A L L h a n d s h a k e t o U S B

. 0

O U T _ P a c k e t R e a d y B i t

0

No effect (when write)

1

S I E s e t s t h i s b i t o n c e a valid token is written to the FIFO

S 3 C 9 6 8 8 / P 9 6 8 8

CONTROL REGISTERS

4 -1 5

EP1FIFO

-- E n d p o i n t 1 F I F O A d d r e s s R e g i s t e r

F 5 H

B i t I d e n t i f i e r

. 7

. 6

. 5

. 4

. 3

. 2

. 1

. 0

RESET

V a l u e

0

0

0

0

0

0

0

0

R e a d / W r i t e

R / W

R / W

R / W

R / W

R / W

R / W

R / W

R / W

. 7 ≠. 0

E n d p o i n t 1 F I F O

This register is bi-directional 8-b y t e d e p t h F I F O u s e d t o t r a n s f e r c o n t r o l E n d p o i n t 1

d a t a .

CONTROL REGISTERS

S 3 C 9 6 8 8 / P 9 6 8 8

4 -1 6

E P 2 B C N T

-- E n d p o i n t 2 W r i t e C o u n t e r R e g i s t e r

F D H

B i t I d e n t i f i e r

. 7

. 6

. 5

. 4

. 3

. 2

. 1

. 0

RESET

V a l u e

0

≠

0

0

0

0

0

0

R e a d / W r i t e

R

≠

R

R / W

R

R

R

R

. 7

D a t a _ T o g g l e _ C h e c k B i t

0

D A T A 0 t r a n s a c t i o n t o g g l e

1

D A T A 1 t r a n s a c t i o n t o g g l e

. 6

R e s e r v e d

. 5

R C V _ O v e r _ 8 _ B Y T E B i t

0

N o r m a l O p e r a t i o n

1

Indicates over 8 bytes received

. 4

E n a b l e B i t

0

D i s a b l e E n d p o i n t 2

1

E n a b l e E n d p o i n t 2

. 3 ≠. 0

T h e B y t e c o u n t e r o f D a t a t h a t s t o r e d i n E n d p o i n t 2

0 0 0 0

M i n i m u m b y t e s s t o r e d i n E n d p o i n t 2

1 0 0 0

M a x i m u m b y t e s s t o r e d i n E n d p o i n t 2

S 3 C 9 6 8 8 / P 9 6 8 8

CONTROL REGISTERS

4 -1 7

E P 2 C S R

-- C o n t r o l E n d p o i n t 2 S t a t u s R e g i s t e r

F 9 H

B i t I d e n t i f i e r

. 7

. 6

. 5

. 4

. 3

. 2

. 1

. 0

RESET

V a l u e

0

0

0

0

0

0

0

0

R e a d / W r i t e

R / W

R / W

R / W

R / W

R / W

R / W

R / W

R / W

a ) T h e b e l l o w s a r e c o n f i g u r e d a s I N m o d e

. 7

D a t a T o g g l e S e q u e n c e C l e a r B i t

0

No effect (when write)

1

M C U s e t s t h i s b i t t o c l e a r t h e d a t a t o g g l e s e q u e n c e b i t . T h e d a t a t o g g l e i s

i n i t i a l i z e d t o D A T A 0 .

. 6 ≠. 3

M a x i m u m P a c k e t S i z e B i t s

0

No effect (when write)

1

T h e s e b i t s i n d i c a t e t h e m a x i m u m p a c k e t s i z e f o r I N e n d p o i n t , a n d n e e d s t o b e

u p d a t e d b y t h e M C U b e f o r e i t s e t s I N _ P K T _ R D Y . O n c e s e t , t h e c o n t e n t s a r e

valid till MCU re -w r i t e s t h e m .

. 2

F I F O F l u s h B i t

0

No effect (when write)

1

W h e n M C U w r i t e s a o n e t o t h i s r e g i s t e r , t h e F I F O i s f l u s h e d , a n d I N _ P K T _ R D Y

c l e a r e d . T h e M C U s h o u l d w a i t f o r I N _ P K T _ R D Y t o b e c l e a r e d f o r t h e f l u s h t o t a k e

p l a c e .

. 1

F o r c e S T A L L B i t

0

No effect (when write)

1

M C U w r i t e s a 1 t o t h i s r e g i s t e r t o i s s u e a S T A L L h a n d s h a k e t o U S B . M C U c l e a r s

t h i s b i t , t o e n d t h e S T A L L c o n d i t i o n .

. 0

I n P a c k e t R e a d y B i t

0

S I E c l e a r t h i s b i t o n c e t h e p a c k e t h a s b e e n s u c c e s s f u l l y s e n t t o t h e h o s t

1

M C U s e t s t h i s b i t , a f t e r w r i t i n g a p a c k e t o f d a t a i n t o E N D P O I N T 2 F I F O . U S B

c l e a r s t h i s b i t , o n c e t h e p a c k e t h a s b e e n s u c c e s s f u l l y s e n t t o t h e h o s t . A n

i n t e r r u p t i s g e n e r a t e d w h e n U S B c l e a r s t h i s b i t , s o M C U c a n l o a d t h e n e x t

p a c k e t .

CONTROL REGISTERS

S 3 C 9 6 8 8 / P 9 6 8 8

4 -1 8

E P 2 C S R

-- C o n t r o l E n d p o i n t 2 S t a t u s R e g i s t e r

F 9 H

B i t I d e n t i f i e r

. 7

. 6

. 5

. 4

. 3

. 2

. 1

. 0

RESET

V a l u e

≠

0

≠

≠

0

0

0

0

R e a d / W r i t e

≠

R / W

≠

≠

R / W

R / W

R / W

R / W

b) The bellows are configured a s O U T m o d e

. 7

R e s e r v e d

. 6

C L R _ O U T _ P K T _ R D Y B i t

0

No effect (when write)

1

C l e a r O U T _ P K T _ R D Y ( b i t 0 ) b i t . .

. 5 ≠. 4

R e s e r v e d

. 3

R C V _ S T A L L _ S I G B i t

0

M C U c a n c l e a r t h i s b i t

1

S I E s e t s t h i s b i t a f t e r s e n d i n g s t a l l p a c k e t

. 2

F L U S H _ F I F O B i t

0

No effect (when write)

1

F I F O i s f l u s h e d , a n d O U T _ P K T _ R D Y b i t i s c l e a r e d . .

. 1

F O R C E _ S T A L L B i t

0

M C U c l e a r s t h i s b i t t o e n d t h e S T A L L c o n d i t i o n

1

I s s u e s a S T A L L h a n d s h a k e t o U S B

. 0

O U T _ P a c k e t R e a d y B i t

0

No effect (when write)

1

S I E s e t s t h i s b i t o n c e a v a l i d t o k e n i s w r i t t e n t o t h e F I F O

S 3 C 9 6 8 8 / P 9 6 8 8

CONTROL REGISTERS

4 -1 9

EP2FIFO

-- E n d p o i n t 2 F I F O A d d r e s s R e g i s t e r

F A H

B i t I d e n t i f i e r

. 7

. 6

. 5

. 4

. 3

. 2

. 1

. 0

RESET

V a l u e

0

0

0

0

0

0

0

0

R e a d / W r i t e

R / W

R / W

R / W

R / W

R / W

R / W

R / W

R / W

. 7 ≠. 0

E n d p o i n t 2 F I F O

This register is bi-directional 8-b y t e d e p t h F I F O u s e d t o t r a n s f e r c o n t r o l E n d p o i n t 2

d a t a .

CONTROL REGISTERS

S 3 C 9 6 8 8 / P 9 6 8 8

4 -2 0

E P M O D E

-- E n d p o i n t M o d e R e g i s t e r

F B H

B i t I d e n t i f i e r

. 7

. 6

. 5

. 4

. 3

. 2

. 1

. 0

RESET

V a l u e

0

0

≠

≠

0

0

0

0

R e a d / W r i t e

R / W

R / W

≠

≠

R / W

R / W

R / W

R / W

. 7 a n d . 6

R e s e t L e n g t h S e l e c t i o n B i t s

0

0

2 0 . 9 5 4 u s

0

1

1 0 . 4 7 6 u s

1

0

5 . 2 3 6 u s

1

1

2 . 6 6 4 u s

. 5 ≠. 4

N o t u s e d f o r C 9 6 8 8 / P 9 6 8 8

. 3

C h i p T e s t M o d e : U s e r m u s t n o t s e t t h i s b i t .

0

N o r m a l m o d e

1

T e s t m o d e

. 2

O u t p u t E n a b l e M o d e

0

E n h a n c e d m o d e

1

N o r m a l m o d e

. 1

E n d p o i n t 2 M o d e

0

E n d p o i n t 2 a c t s a s I N i n t e r r u p t e n d p o i n t

1

E n d p o i n t 2 a c t s a s a n O U T i n t e r r u p t e n d p o i n t

. 0

E n d p o i n t 1 M o d e

0

E n d p o i n t 1 a c t s a s a n I N i n t e r r u p t e n d p o i n t

1

E n d p o i n t 1 a c t s a s a n OUT interrupt endpoint

S 3 C 9 6 8 8 / P 9 6 8 8

CONTROL REGISTERS

4 -2 1

F A D D R

-- U S B F u n c t i o n A d d r e s s R e g i s t e r

F 0 H

.

B i t I d e n t i f i e r

. 7

. 6

. 5

. 4

. 3

. 2

. 1

. 0

RESET

V a l u e

0

0

0

0

0

0

0

0

R e a d / W r i t e

R / W

R / W

R / W

R / W

R / W

R / W

R / W

R / W

. 7

T h i s r e g i s t e r b i t i s u s e d a s t e s t m o d e o r s p e c i a l p u r p o s e m o d e , s o u s e r s h o u l d s e t

zero value,

. 6 ≠. 0

F A D D R

T h i s r e g i s t e r h o l d s t h e U S B a d d r e s s a s s i g n e d b y t h e h o s t c o m p u t e r . F A D D R i s

l o c a t e d a t a d d r e s s F 0 H a n d i s r e a d / w r i t e a d d r e s s a b l e .

CONTROL REGISTERS

S 3 C 9 6 8 8 / P 9 6 8 8

4 -2 2

F L A G S

-- S y s t e m F l a g s R e g i s t e r

D 5 H

B i t I d e n t i f i e r

. 7

. 6

. 5

. 4

. 3

. 2

. 1

. 0

RESET

V a l u e

0

0

0

0

≠

≠

≠

≠

R e a d / W r i t e

R / W

R / W

R / W

R / W

≠

≠

≠

≠

. 7

C a r r y F l a g ( C )

0

O p e r a t i o n d o e s n o t g e n e r a t e a c a r r y o r b o r r o w c o n d i t i o n

. 6

Z e r o F l a g ( Z )

0

O p e r a t i o n r e s u l t i s a n o n -zero value

1

Operation result is zero

. 5

S i g n F l a g ( S )

0

O p e r a t i o n g e n e r a t e s a p o s i t i v e n u m b e r ( M S B = " 0 " )

1

O p e r a t i o n g e n e r a t e s a n e g a t i v e n u m b e r ( M S B = " 1 " )

. 4

O v e r f l o w F l a g ( V )

0

O p e r a t i o n r e s u l t i s

+ 1 2 7 o r

≠ 1 2 8

1

O p e r a t i o n r e s u l t i s

+ 1 2 7 o r

≠ 1 2 8

. 3 ≠. 0

N o t u s e d f o r S 3 C 9 6 8 8 / P 9 6 8 8

S 3 C 9 6 8 8 / P 9 6 8 8

CONTROL REGISTERS

4 -2 3

P 0 C O N H

-- P o r t 0 C o n t r o l R e g i s t e r ( H i g h B y t e )

E 6 H

B i t I d e n t i f i e r

. 7

. 6

. 5

. 4

. 3

. 2

. 1

. 0

RESET

V a l u e

0

0

0

0

0

0

0

0

R e a d / W r i t e

R / W

R / W

R / W

R / W

R / W

R / W

R / W

R / W

. 7 a n d . 6

P o r t 0 , P 0 . 7 C o n f i g u r a t i o n B i t s

0

0

Schmitt trigger input, rising edge external interrupt

0

1

Schmitt trigger input, falling edge external interrupt with pull-u p

1

0

N -C H o p e n d r a i n o u t p u t m o d e

1

1

N -C H o p e n d r a i n o u t p u t m o d e w i t h p u l l -u p

. 5 a n d . 4

P o r t 0 , P 0 . 6 C o n f i g u r a t i o n B i t s

0

0

Schmitt trigger input, rising edge external interrupt

0

1

Schmitt trigger input, falling edge external interrupt with pull-u p

1

0

N -C H o p e n d r a i n o u t p u t m o d e

1

1

N -C H o p e n d r a i n o u t p u t m o d e w i t h p u l l -u p

. 3 a n d . 2

P o r t 0 , P 0 . 5 C o n f i g u r a t i o n B i t s

0

0

Schmitt trigger input, rising edge external interrupt

0

1

S c h m i t t t r i g g e r i n p u t , f a lling edge external interrupt with pull-u p

1

0

N -C H o p e n d r a i n o u t p u t m o d e

1

1

N -C H o p e n d r a i n o u t p u t m o d e w i t h p u l l -u p

. 1 a n d . 0

P o r t 0 , P 0 . 4 C o n f i g u r a t i o n B i t s

0

0

Schmitt trigger input, rising edge external interrupt

0

1

Schmitt trigger input, falling edge external interrupt with pull-u p

1

0

N -C H o p e n d r a i n o u t p u t m o d e

1

1

N -C H o p e n d r a i n o u t p u t m o d e w i t h p u l l -u p

CONTROL REGISTERS

S 3 C 9 6 8 8 / P 9 6 8 8

4 -2 4

P 0 C O N L

-- P o r t 0 C o n t r o l R e g i s t e r ( L o w B y t e )

E 7 H

B i t I d e n t i f i e r

. 7

. 6

. 5

. 4

. 3

. 2

. 1

. 0

RESET

V a l u e

0

0

0

0

0

0

0

0

R e a d / W r i t e

R / W

R / W

R / W

R / W

R / W

R / W

R / W

R / W

. 7 a n d . 6

P o r t 0 , P 0 . 3 C o n f i g u r a t i o n B i t s

0

0

Schmitt trigger input, rising edge external interrupt

0

1

Schmitt trigger input, falling edge external interrupt with pull-u p

1

0

N -C H o p e n d r a i n o u t p u t m o d e

1

1

N -C H o p e n d r a i n o u t p u t m o d e w i t h p u l l -u p

. 5 a n d . 4

P o r t 0 , P 0 . 2 C o n f i g u r a t i o n B i t s

0

0

Schmitt trigger input, rising edge external interrupt

0

1

Schmitt trigger input, falling edge external interrupt with pull-u p

1

0

N -C H o p e n d r a i n o u t p u t m o d e

1

1

N -C H o p e n d r a i n o u t p u t m o d e w i t h p u l l -u p

. 3 a n d . 2

P o r t 0 , P 0 . 1 C o n f i g u r a t i o n B i t s

0

0

Schmitt trigger input, rising edge external interrupt

0

1

Schmitt trigger input, falling edge external interrupt with pull-u p

1

0

N -C H o p e n d r a i n o u t p u t m o d e

1

1

N -C H o p e n d r a i n o u t p u t m o d e w i t h p u l l -u p

. 1 a n d . 0

P o r t 0 , P 0 . 0 C o n f i g u r a t i o n B i t s

0

0

Schmitt trigger input, rising edge external interrupt

0

1

Schmitt trigger input, falling edge external interrupt with pull-u p

1

0

N -C H o p e n d r a i n o u t p u t m o d e

1

1

N -C H o p e n d r a i n o u t p u t m o d e w i t h p u l l -u p

S 3 C 9 6 8 8 / P 9 6 8 8

CONTROL REGISTERS

4 -2 5

P0INT

-- Port 0 Interrupt Control Register

D 8 H

B i t I d e n t i f i e r

. 7

. 6

. 5

. 4

. 3

. 2

. 1

. 0

RESET

V a l u e

0

0

0

0

0

0

0

0

R e a d / W r i t e

R / W

R / W

R / W

R / W

R / W

R / W

R / W

R / W

. 7

P 0 . 7 C o n f i g u r a t i o n B i t s

0

External interrupt disable

1

External interrupt enable

. 6

P 0 . 6 C o n f i g u r a t i o n B i t s

0

External interrupt disable

1

External interrupt enable

. 5

P 0 . 5 C o n f i g u r a t i o n B i t s

0

External interrupt dis able

1

External interrupt enable

. 4

P 0 . 4 C o n f i g u r a t i o n B i t s

0

External interrupt disable

1

External interrupt enable

. 3

P 0 . 3 C o n f i g u r a t i o n B i t s

0

External interrupt disable

1

External interrupt enable

. 2

P 0 . 2 C o n f i g u r a t i o n B i t s

0

External interrupt disable

1

External interrupt enable

. 1

P 0 . 1 C o n f i g u r a t i o n B i t s

0

External interrupt disable

1

External interrupt enable

. 0

P 0 . 0 C o n f i g u r a t i o n B i t s

0

External interrupt disable

1

External interrupt enable

CONTROL REGISTERS

S 3 C 9 6 8 8 / P 9 6 8 8

4 -2 6

S 3 C 9 6 8 8 / P 9 6 8 8

CONTROL REGISTERS

4 -2 7

P 0 P N D

-- Port 0 Inte r r u p t P e n d i n g R e g i s t e r

D A H

B i t I d e n t i f i e r

. 7

. 6

. 5

. 4

. 3

. 2

. 1

. 0

RESET

V a l u e

0

0

0

0

0

0

0

0

R e a d / W r i t e

(NOTE)

R / W

R / W

R / W

R / W

R / W

R / W

R / W

R / W

. 7

P 0 . 7 I n t e r r u p t P e n d i n g B i t

0

N o p e n d i n g ( w h e n r e a d ) / c l e a r p e n d i n g b i t ( w h e n w r i t e )

1

Pending (when read)/no effect (when write)

. 6

P 0 . 6 I n t e r r u p t P e n d i n g B i t

0

N o p e n d i n g ( w h e n r e a d ) / c l e a r p e n d i n g b i t ( w h e n w r i t e )

1

Pending (when read)/no effect (when write)

. 5

P 0 . 5 I n t e r r u p t P e n d i n g B i t

0

N o p e n d i n g ( w h e n r e a d ) / c l e a r p e n d i n g b i t ( w h e n w r i t e )

1

Pending (when read)/no effect (when write)

. 4

P 0 . 4 I n t e r r u p t P e n d i n g B i t

0

N o p e n d i n g ( w h e n r e a d ) / c l e a r p e n d i n g b i t ( w h e n w r i t e )

1

Pending (when read)/no effect (when write)

. 3

P 0 . 3 I n t e r r u p t P e n d i n g B i t

0

N o p e n d i n g ( w h e n r e a d ) / c l e a r p e n d i n g b i t ( w h e n w r i t e )

1

Pending (when read)/no effect (when write)

. 2

P 0 . 2 I n t e r r u p t P e n d i n g B i t

0

N o p e n d i n g ( w h e n r e a d ) / c l e a r p e n d i n g b i t ( w h e n w r i t e )

1

Pending (when read)/no effect (when w rite)

. 1

P 0 . 1 I n t e r r u p t P e n d i n g B i t

0

N o p e n d i n g ( w h e n r e a d ) / c l e a r p e n d i n g b i t ( w h e n w r i t e )

1

Pending (when read)/no effect (when write)

. 0

P 0 . 0 I n t e r r u p t P e n d i n g B i t

0

N o p e n d i n g ( w h e n r e a d ) / c l e a r p e n d i n g b i t ( w h e n w r i t e )

1

Pending (when read)/no effect (when write)

CONTROL REGISTERS

S 3 C 9 6 8 8 / P 9 6 8 8

4 -2 8

S 3 C 9 6 8 8 / P 9 6 8 8