Document Outline

- TOC

- 1 Product Overview

- 2 Address Spaces

- 3 Registers

- 4 Memory Map

- 5 Hardware Stack

- 6 Exceptions

- 7 Instruction Set

- 8 Clock Circuit

- 9 Reset and Power-Down

- 10 IO ports

- 11 Basic Timer/Watchdog Timer

- 12 Watch Timer

- 13 16-Bit Timer 0

- 14 16-Bit Timer 1

- 15 8-Bit Timer 2

- 16 8-Bit Timer 3

- 17 Serial IO Interface

- 18 LCD Controller/Driver

- 19 10-Bit ADC

- 20 DA Converter

- 21 Operational Amplifier

- 22 Electrical Data

- 23 Mechanical Data

- 24 S3FK225 Flash MCU

- 25 Development Tools

S3CK225/FK225

CalmRISC 8-Bit CMOS

MICROCONTROLLER

USER'S MANUAL

Revision 1

Important Notice

The information in this publication has been

carefully checked and is believed to be entirely

accurate at the time of publication. Samsung

assumes no responsibility, however, for possible

errors or omissions, or for any consequences

resulting from the use of the information contained

herein.

Samsung reserves the right to make changes in its

products or product specifications with the intent to

improve function or design at any time and without

notice and is not required to update this

documentation to reflect such changes.

This publication does not convey to a purchaser of

semiconductor devices described herein any license

under the patent rights of Samsung or others.

Samsung makes no warranty, representation, or

guarantee regarding the suitability of its products for

any particular purpose, nor does Samsung assume

any liability arising out of the application or use of

any product or circuit and specifically disclaims any

and all liability, including without limitation any

consequential or incidental damages.

"Typical" parameters can and do vary in different

applications. All operating parameters, including

"Typicals" must be validated for each customer

application by the customer's technical experts.

Samsung products are not designed, intended, or

authorized for use as components in systems

intended for surgical implant into the body, for other

applications intended to support or sustain life, or for

any other application in which the failure of the

Samsung product could create a situation where

personal injury or death may occur.

Should the Buyer purchase or use a Samsung

product for any such unintended or unauthorized

application, the Buyer shall indemnify and hold

Samsung and its officers, employees, subsidiaries,

affiliates, and distributors harmless against all

claims, costs, damages, expenses, and reasonable

attorney fees arising out of, either directly or

indirectly, any claim of personal injury or death that

may be associated with such unintended or

unauthorized use, even if such claim alleges that

Samsung was negligent regarding the design or

manufacture of said product.

S3CK225/FK225 8-Bit CMOS Microcontroller

User's Manual, Revision 1

Publication Number: 21-S3-CK225/FK225-032003

� 2003 Samsung Electronics

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in

any form or by any means, electric or mechanical, by photocopying, recording, or otherwise, without the prior

written consent of Samsung Electronics.

Samsung Electronics' microcontroller business has been awarded full ISO-14001

certification (BVQ1 Certificate No. 9330). All semiconductor products are designed

and manufactured in accordance with the highest quality standards and objectives.

Samsung Electronics Co., Ltd.

San #24 Nongseo-Ri, Giheung- Eup

Yongin-City, Gyeonggi-Do, Korea

C.P.O. Box #37, Suwon 449-900

TEL:

(82)-(331)-209-1907

FAX:

(82)-(331)-209-1889

Home-Page URL:

Http://www.samsungsemi.com/

Printed in the Republic of Korea

S3CK225/FK225 MICROCONTROLLER

iii

Preface

The S3CK225/FK225 Microcontroller User's Manual is designed for application designers and programmers who

are using the S3CK225/FK225 microcontroller for application development. It is organized in two main parts:

Part I

Programming Model

Part II

Hardware Descriptions

Part I contains software-related information to familiarize you with the microcontroller's architecture,

programming model, instruction set, and interrupt structure. It has nine chapters:

Chapter 1

Product Overview

Chapter 2

Address Spaces

Chapter 3

Register

Chapter 4

Memory Map

Chapter 5

Hardware Stack

Chapter 6

Exceptions

Chapter 7

Instruction Set

Chapter 1, "Product Overview," is a high-level introduction to S3CK225/FK225 with general product descriptions,

as well as detailed information about individual pin characteristics and pin circuit types.

Chapter 2, "Address Spaces," describes program and data memory spaces. Chapter 2 also describes ROM code

option.

Chapter 3, "Register," describes the special registers.

Chapter 4, "Memory Map," describes the internal register file.

Chapter 5, "Hardware Stack," describes the S3CK225/FK225 hardware stack structure in detail.

Chapter 6, "Exception," describes the S3CK225/FK225 exception structure in detail.

A basic familiarity with the information in Part I will help you to understand the hardware module descriptions in

Part II. If you are not yet familiar with the S3CK-series microcontroller family and are reading this manual for the

first time, we recommend that you first read Chapters 1�3 carefully. Then, briefly look over the detailed

information in Chapters 4, 5, 6 and 7. Later, you can reference the information in Part I as necessary.

Part II "hardware Descriptions," has detailed information about specific hardware components of the

S3CK225/FK225 microcontroller. Also included in Part II are electrical, mechanical. It has 20 chapters:

Chapter 8

Clock Circuit

Chapter 9

Reset and Power-Down

Chapter 10

I/O Ports

Chapter 11

Basic Timer/Watchdog Timer

Chapter 12

Watch Timer

Chapter 13

16-bit Timer 0

Chapter 14

16-bit Timer 1

Chapter 15

8-bit Timer 2

Chapter 16

8-bit Timer 3

Chapter 17

Serial I/O Interface

Chapter 18

LCD Controller/Driver

Chapter 19

10-bt A/D Converter

Chapter 20

D/A Converter

Chapter 21

Operational Amplifier

Chapter 22

Electrical Data

Chapter 23

Mechanical Data

Chapter 24

S3FK225 Flash MCU

Chapter 25

Development Tools

One order form is included at the back of this manual to facilitate customer order for S3CK225/FK225

microcontrollers: the Flash Factory Writing Order Form.

You can photocopy this form, fill it out, and then forward it to your local Samsung Sales Representative.

S3CK225/FK225 MICROCONTROLLER

v

Table of Contents

Part I -- Programming Model

Chapter 1

Product Overview

Overview ................................................................................................................................................. 1-1

Features .................................................................................................................................................. 1-5

Block Diagram ......................................................................................................................................... 1-7

Pin Assignment........................................................................................................................................ 1-8

Pin Descriptions....................................................................................................................................... 1-9

Pin Circuits .............................................................................................................................................. 1-11

Chapter 2

Address Spaces

Overview ................................................................................................................................................. 2-1

Program Memory (ROM) ......................................................................................................................... 2-1

ROM Code Option (RCOD_OPT) ............................................................................................................ 2-4

Data Memory Organization ...................................................................................................................... 2-6

Chapter 3

Register

Overview ................................................................................................................................................. 3-1

Index Registers: IDH, IDL0 And IDL1............................................................................................... 3-2

Link Registers: ILX, ILH AND ILL..................................................................................................... 3-2

Status Register 0: SR0 .................................................................................................................... 3-3

Status Register 1: SR1 .................................................................................................................... 3-4

Chapter 4

Memory Map

Overview ................................................................................................................................................. 4-1

vi

S3CK225/FK225 MICROCONTROLLER

Table of Contents

(Continued)

Chapter 5

Hardware Stack

Overview ................................................................................................................................................. 5-1

Chapter 6

Exceptions

Overview ................................................................................................................................................. 6-1

Hardware Reset............................................................................................................................... 6-1

IRQ[0] Exception ............................................................................................................................. 6-2

IRQ[1] Exception (Level-Sensitive).................................................................................................. 6-2

Hardware Stack Full Exception ........................................................................................................ 6-2

Break Exception .............................................................................................................................. 6-2

Exceptions (Or Interrupts)................................................................................................................ 6-3

Interrupt Mask Registers.................................................................................................................. 6-5

Interrupt Priority Register................................................................................................................. 6-6

Chapter 7

Instruction Set

Overview ................................................................................................................................................. 7-1

Glossary .......................................................................................................................................... 7-1

Instruction Set Map .................................................................................................................................. 7-2

Quick Reference ...................................................................................................................................... 7-9

Instruction Group Summary ..................................................................................................................... 7-12

ALU Instructions .............................................................................................................................. 7-12

Shift/Rotate Instructions................................................................................................................... 7-16

Load Instructions ............................................................................................................................. 7-18

Branch Instructions .......................................................................................................................... 7-21

Bit Manipulation Instructions ............................................................................................................ 7-25

Miscellaneous Instruction................................................................................................................. 7-26

PSEUDO Instructions ...................................................................................................................... 7-29

S3CK225/FK225 MICROCONTROLLER

vii

Table of Contents

(Continued)

Part II -- Hardware Descriptions

Chapter 8

Clock Circuit

System Clock Circuit ............................................................................................................................... 8-1

Chapter 9

Reset and Power-Down

Overview ................................................................................................................................................. 9-1

Chapter 10

I/O Ports

Port 0....................................................................................................................................................... 10-1

Port 1....................................................................................................................................................... 10-2

Port 2....................................................................................................................................................... 10-3

Port 3....................................................................................................................................................... 10-4

Port 4....................................................................................................................................................... 10-5

Port 5....................................................................................................................................................... 10-6

Port 6....................................................................................................................................................... 10-7

Port 7....................................................................................................................................................... 10-7

Chapter 11

Basic Timer/Watchdog Timer

Overview ................................................................................................................................................. 11-1

Block Diagram................................................................................................................................. 11-2

Chapter 12

Watch Timer

Overview ................................................................................................................................................. 12-1

Watch Timer Circuit Diagram .......................................................................................................... 12-2

Chapter 13

16-Bit Timer 0

Overview......................................................................................................................................... 13-1

Function Description........................................................................................................................ 13-2

Timer 0 Control Register (T0CON) .................................................................................................. 13-3

Block Diagram................................................................................................................................. 13-4

viii

S3CK225/FK225 MICROCONTROLLER

Table of Contents

(Continued)

Chapter 14

16-Bit Timer 1

Overview ................................................................................................................................................. 14-1

Function Description ................................................................................................................................ 14-1

Timer 1 Control Register (T1CON) .................................................................................................. 14-2

Block Diagram ................................................................................................................................. 14-3

Chapter 15

8-Bit Timer 2

Overview ................................................................................................................................................. 15-1

Function Description ........................................................................................................................ 15-2

Timer 2 Control Register (T2CON) .................................................................................................. 15-3

Block Diagram ................................................................................................................................. 15-4

Chapter 16

8-Bit Timer 3

Overview ................................................................................................................................................. 16-1

Timer 3 Pulse Width Calculations .................................................................................................... 16-4

Chapter 17

Serial I/O Interface

Overview ................................................................................................................................................. 17-1

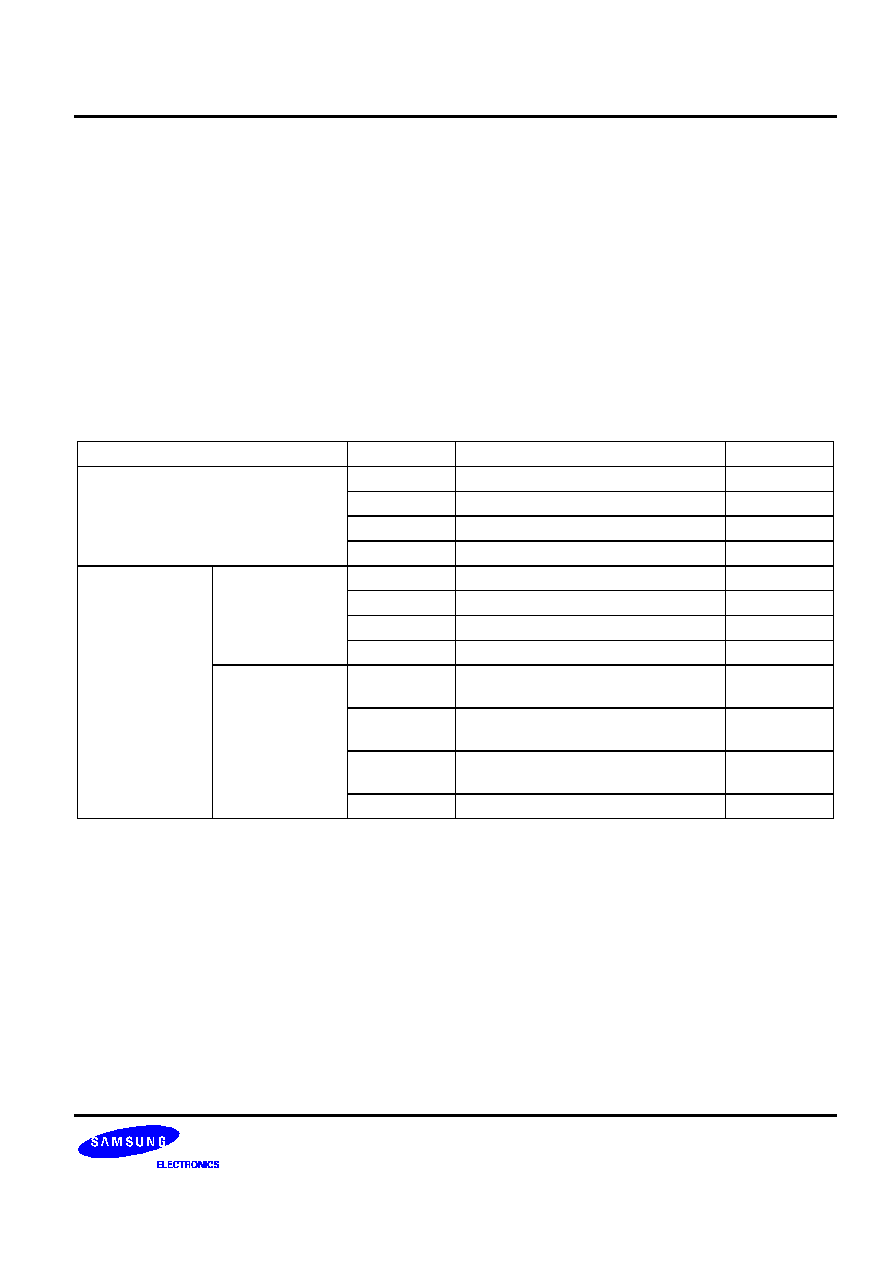

SIO Control Register (SIOCON)............................................................................................................... 17-2

SIO Pre-Scaler Register (SIOPS) ............................................................................................................ 17-2

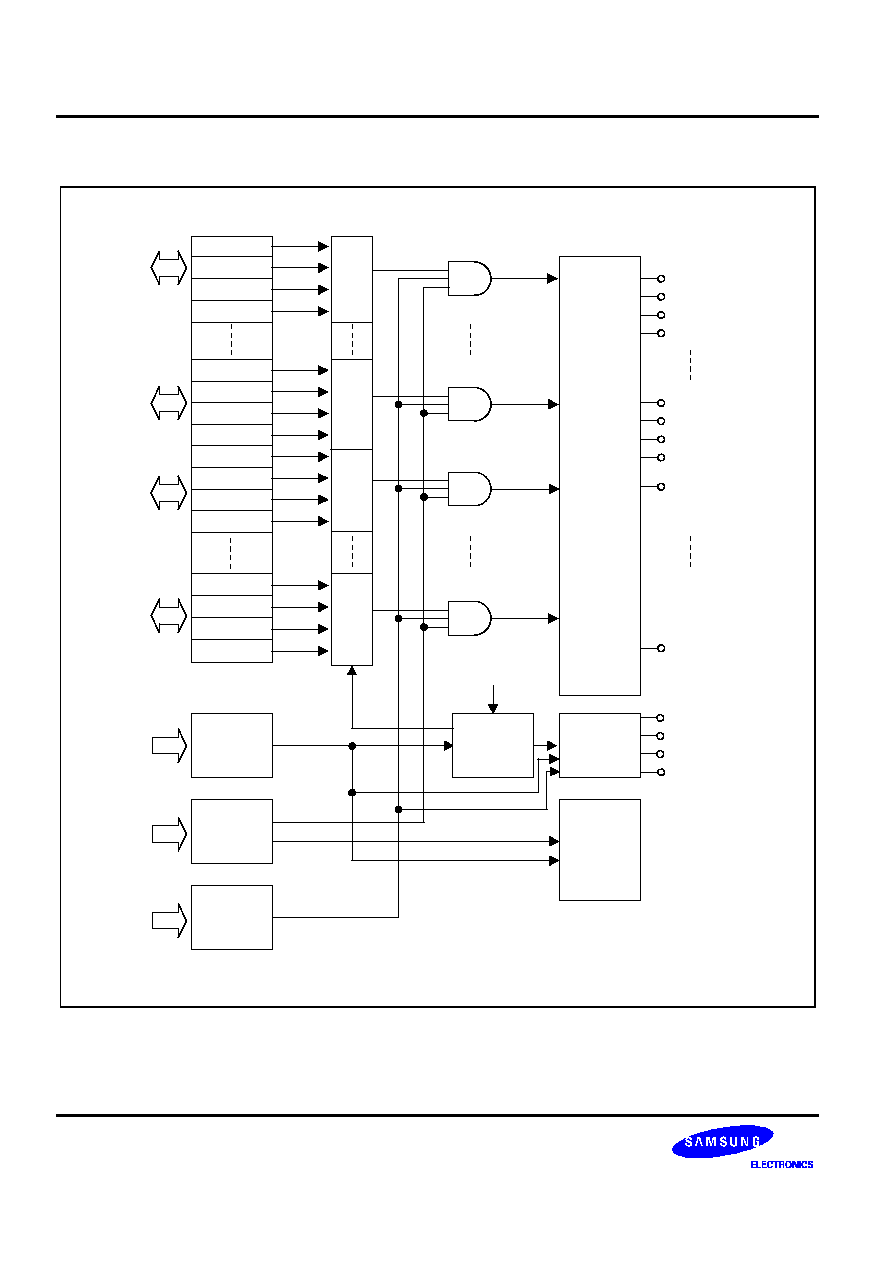

Block Diagram ......................................................................................................................................... 17-3

Serial I/O Timing Diagram ....................................................................................................................... 17-4

S3CK225/FK225 MICROCONTROLLER

ix

Table of Contents

(Continued)

Chapter 18

LCD Controller/Driver

Overview ................................................................................................................................................. 18-1

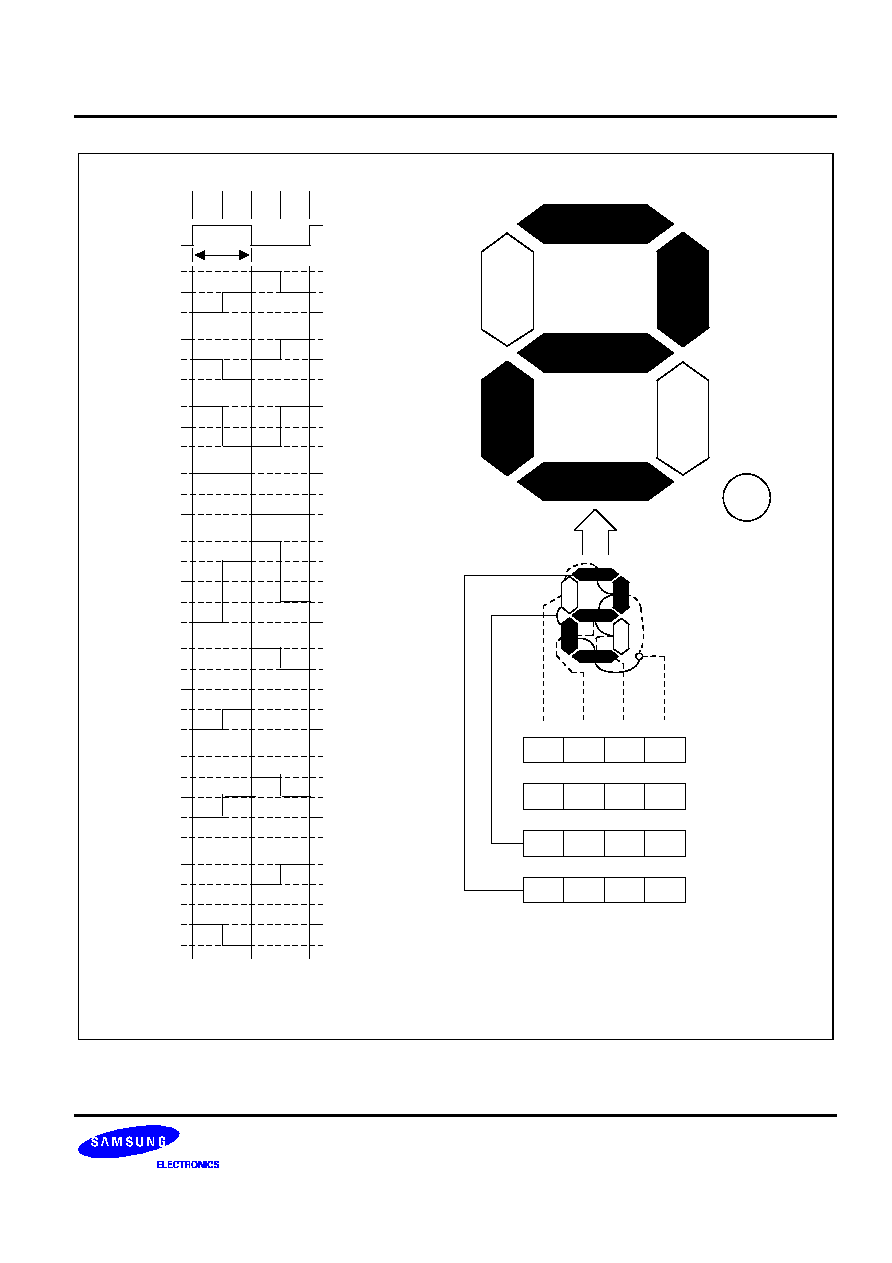

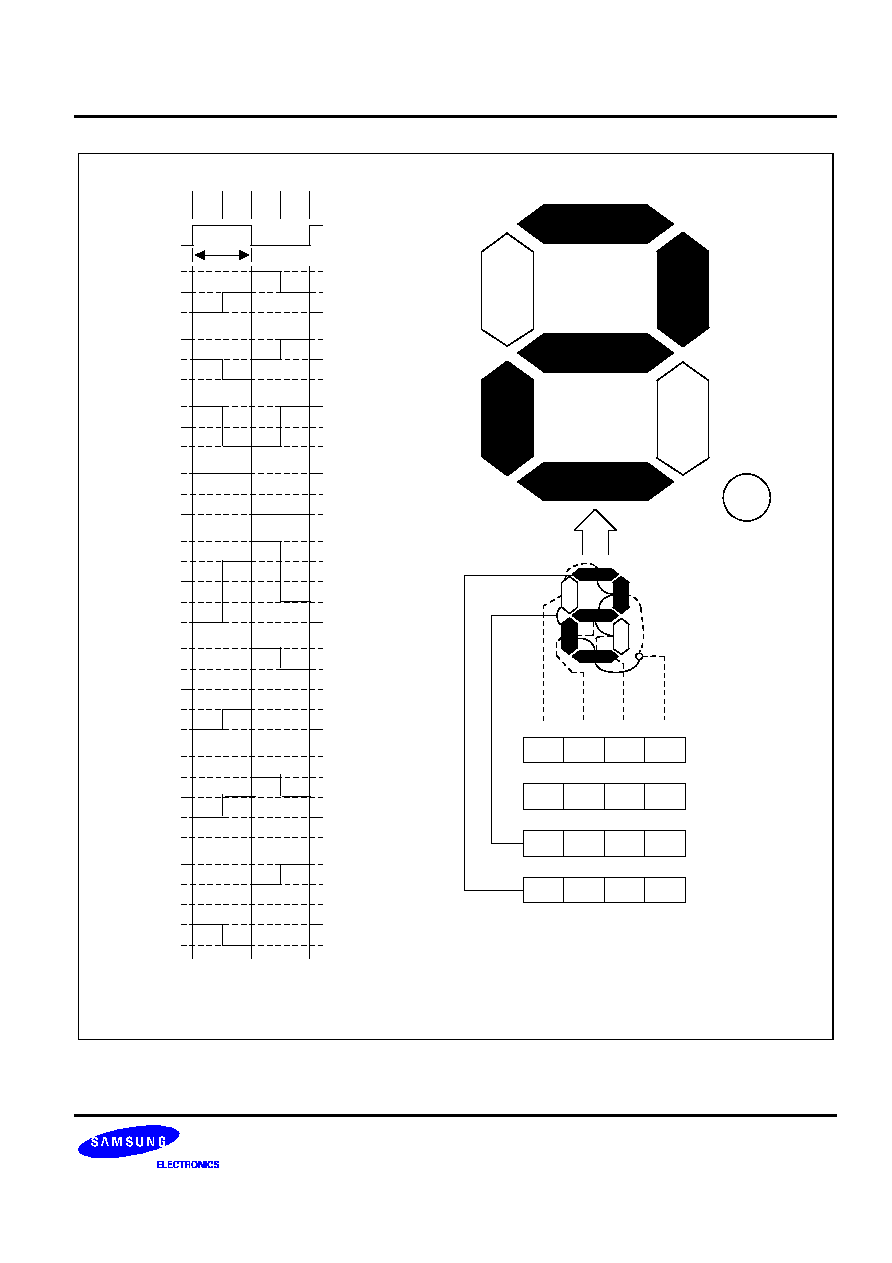

LCD Circuit Diagram ....................................................................................................................... 18-2

LCD RAM Address Area .................................................................................................................. 18-3

LCD Control Register (LCON, 60H) ................................................................................................. 18-4

LCD Port Control Registers (LPOT1, LPOT2)

.........................................................................................

18-7

LCD Voltage Dividing Resistors....................................................................................................... 18-8

LCD COM/SEG Signals................................................................................................................... 18-9

Chapter 19

10-Bit Analog to Digital Converter

Overview ................................................................................................................................................. 19-1

Function Description ................................................................................................................................ 19-1

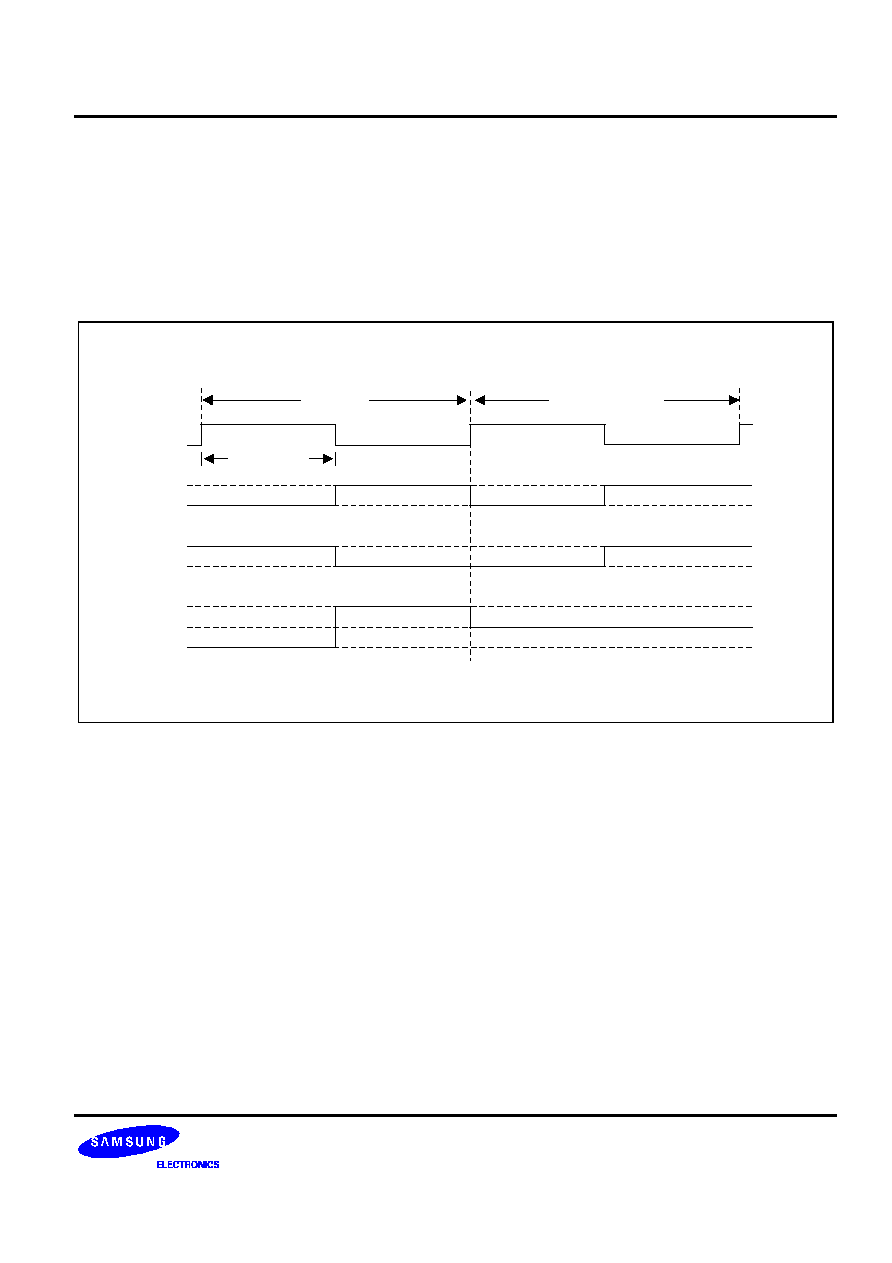

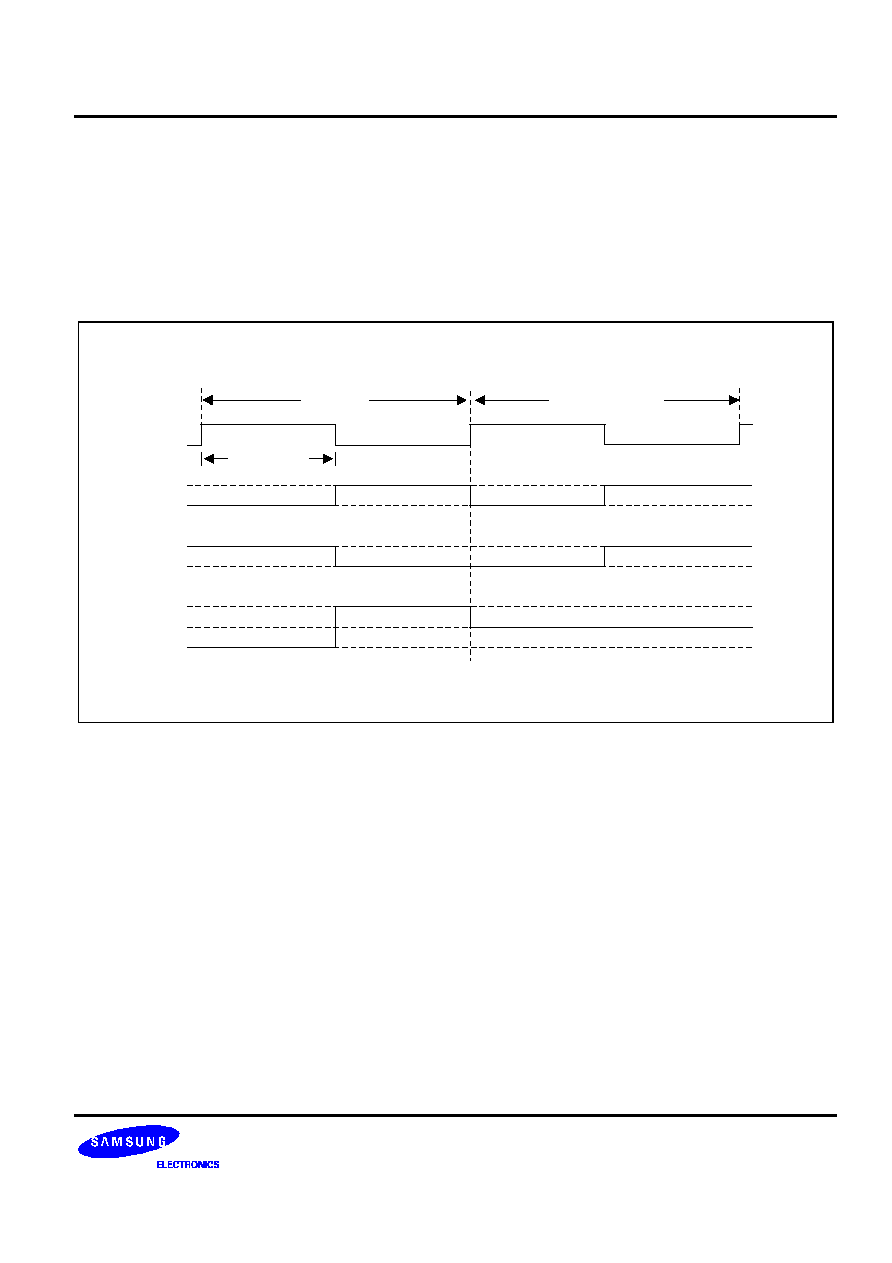

Conversion Timing .......................................................................................................................... 19-2

A/D Converter Control Register (ADCON) ....................................................................................... 19-2

Internal Reference Voltage Levels................................................................................................... 19-3

Block Diagram ......................................................................................................................................... 19-3

Chapter 20

D/A Converter

Overview ................................................................................................................................................. 20-1

Function Description........................................................................................................................ 20-1

D/A Converter Data Register (DADATAH/DADATAL) ...................................................................... 20-3

Chapter 21

Operational Amplifier

Overview ................................................................................................................................................. 21-1

OP AMP Control Register (OPCON)................................................................................................ 21-1

x

S3CK225/FK225 MICROCONTROLLER

Table of Contents

(Continued)

Chapter 22

Electrical Data

Overview ................................................................................................................................................. 22-1

Chapter 23

Mechanical Data

Overview ................................................................................................................................................. 23-1

Chapter 24

S3FK225 Flash MCU

Overview ................................................................................................................................................. 24-1

Chapter 25

Development Tools

Overview ................................................................................................................................................. 25-1

CALMSHINE: IDE (Integrated Development Environment) .............................................................. 25-1

Invisible MDS: In-Circuit Emulator ................................................................................................... 25-1

CALMRISC8 C-Compiler: CALM8CC .............................................................................................. 25-1

CALMRISC8 Relocatable Assembler: CALM8ASM.......................................................................... 25-1

CALMRISC8 Linker: CALM8LINK .................................................................................................... 25-1

Emulation Probe Board Configuration ...................................................................................................... 25-2

External Event Input Headers .......................................................................................................... 25-3

Event Match Output Headers........................................................................................................... 25-3

External Break Input Headers .......................................................................................................... 25-3

Power Selection............................................................................................................................... 25-4

Clock Selection................................................................................................................................ 25-4

VREF Selection ............................................................................................................................... 25-5

Use Clock Setting For External Clock Mode .................................................................................... 25-5

Sub Clock Setting ............................................................................................................................ 25-5

JP1, JP2 Pin Assignment ................................................................................................................ 25-6

S3CK225/FK225 MICROCONTROLLER

xi

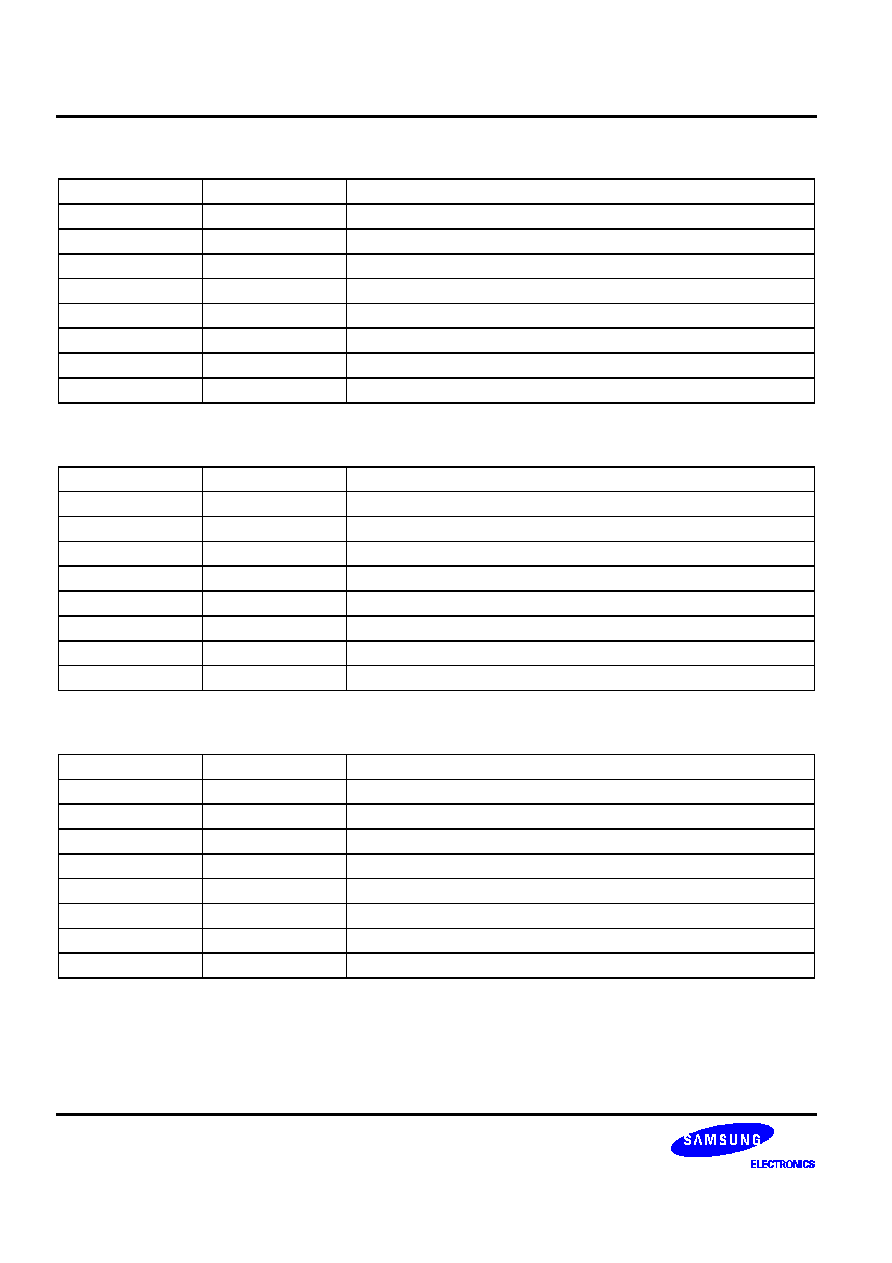

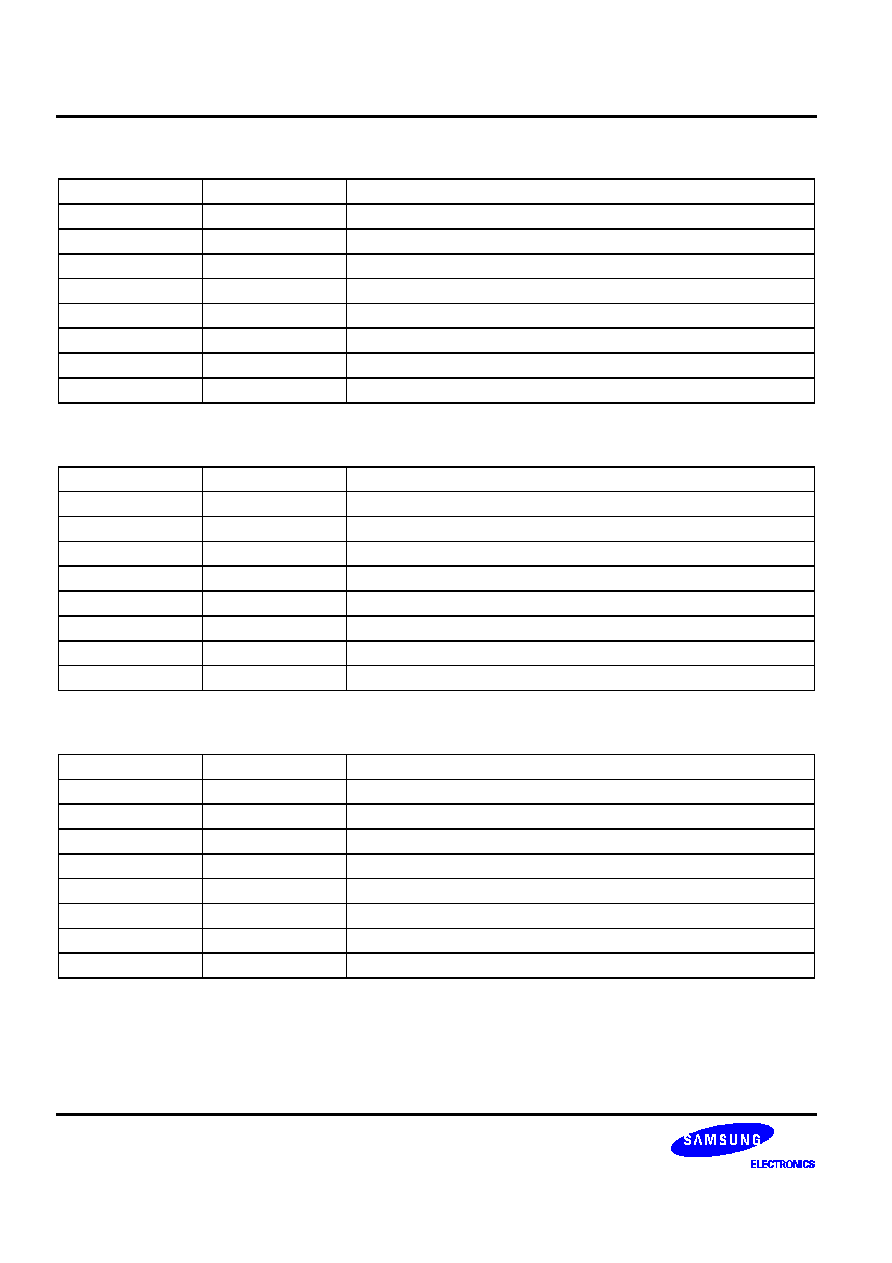

List of Figures

Figure

Title

Page

Number

Number

1-1

Top Block Diagram............................................................................................................. 1-2

1-2

CalmRISC Pipeline Diagram .............................................................................................. 1-3

1-3

CalmRISC Pipeline Stream Diagram .................................................................................. 1-4

1-4

Block Diagram.................................................................................................................... 1-7

1-5

Pin Assignment (64-QFP)................................................................................................... 1-8

1-6

Pin Circuit Type B (RESET) ............................................................................................... 1-11

1-7

Pin Circuit Type D-3 (P7).................................................................................................... 1-11

1-8

Pin Circuit Type C .............................................................................................................. 1-11

1-9

Pin Circuit Type D-4 (P0)................................................................................................... 1-11

1-10

Pin Circuit Type E-4 (P1).................................................................................................... 1-12

1-11

Pin Circuit Type F-10 (P5) .................................................................................................. 1-12

1-12

Pin Circuit Type H-4 ........................................................................................................... 1-13

1-13

Pin Circuit Type H-14 (P2, P3, P4, P6) ............................................................................... 1-13

2-1

Program Memory Organization........................................................................................... 2-1

2-2

Relative Jump Around Page Boundary ............................................................................... 2-2

2-3

Program Memory Layout .................................................................................................... 2-3

2-4

ROM Code Option (RCOD_OPT) ....................................................................................... 2-5

2-5

Data Memory Map of CalmRISC8 ...................................................................................... 2-6

2-6

Data Memory Map of S3CK225 .......................................................................................... 2-7

3-1

Bank Selection by Setting of GRB Bits and IDB Bit............................................................. 3-3

4-1

Memory Map Area .............................................................................................................. 4-1

5-1

Hardware Stack .................................................................................................................. 5-1

5-2

Even and Odd Bank Selection Example ............................................................................. 5-2

5-3

Stack Operation with PC [19:0]........................................................................................... 5-3

5-4

Stack Operation with Registers........................................................................................... 5-4

5-5

Stack Overflow ................................................................................................................... 5-5

6-1

Interrupt Structure .............................................................................................................. 6-3

6-2

Interrupt Structure .............................................................................................................. 6-4

6-3

Interrupt Mask Register ...................................................................................................... 6-5

6-4

Interrupt Priority Register.................................................................................................... 6-6

xii

S3CK225/FK225 MICROCONTROLLER

List of Figures

(Continued)

Figure

Title

Page

Number

Number

8-1

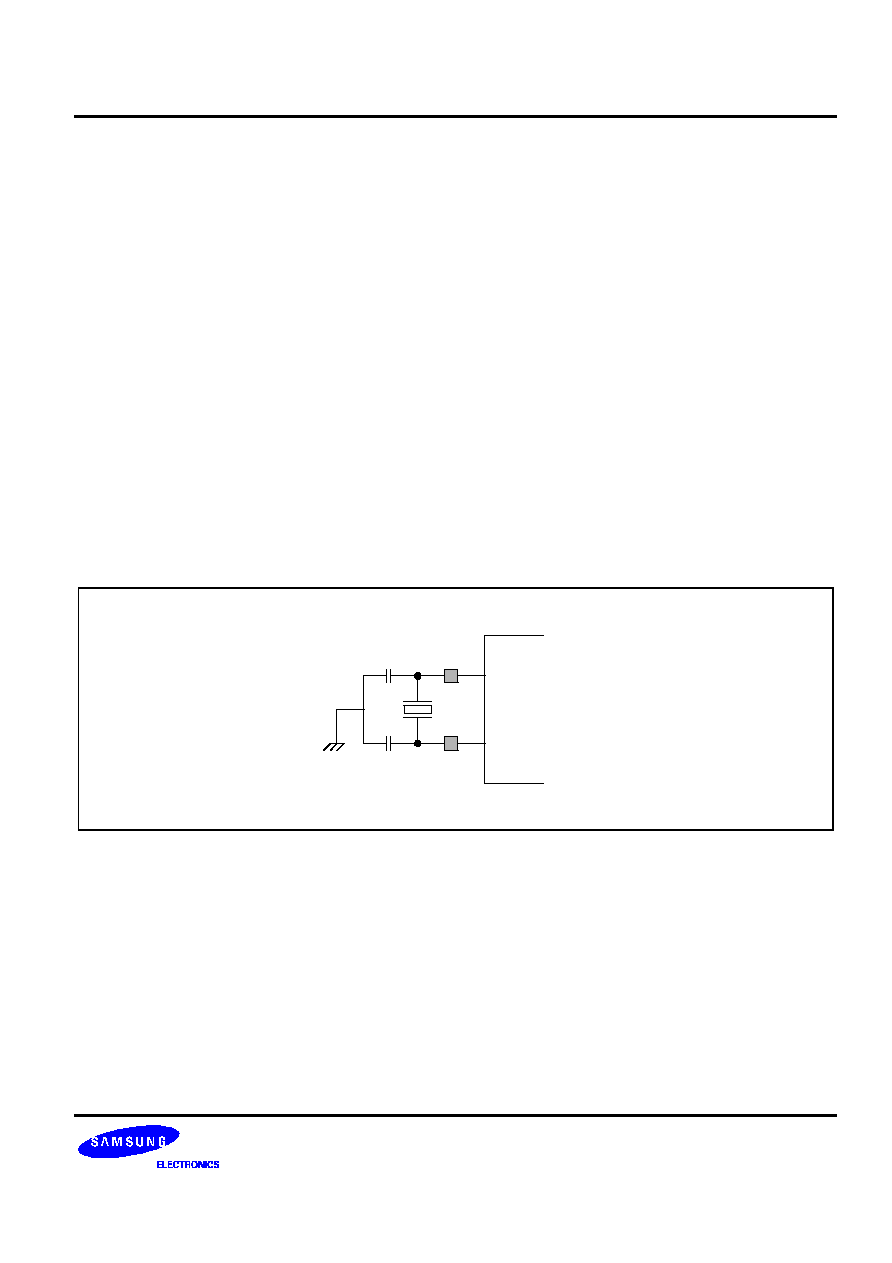

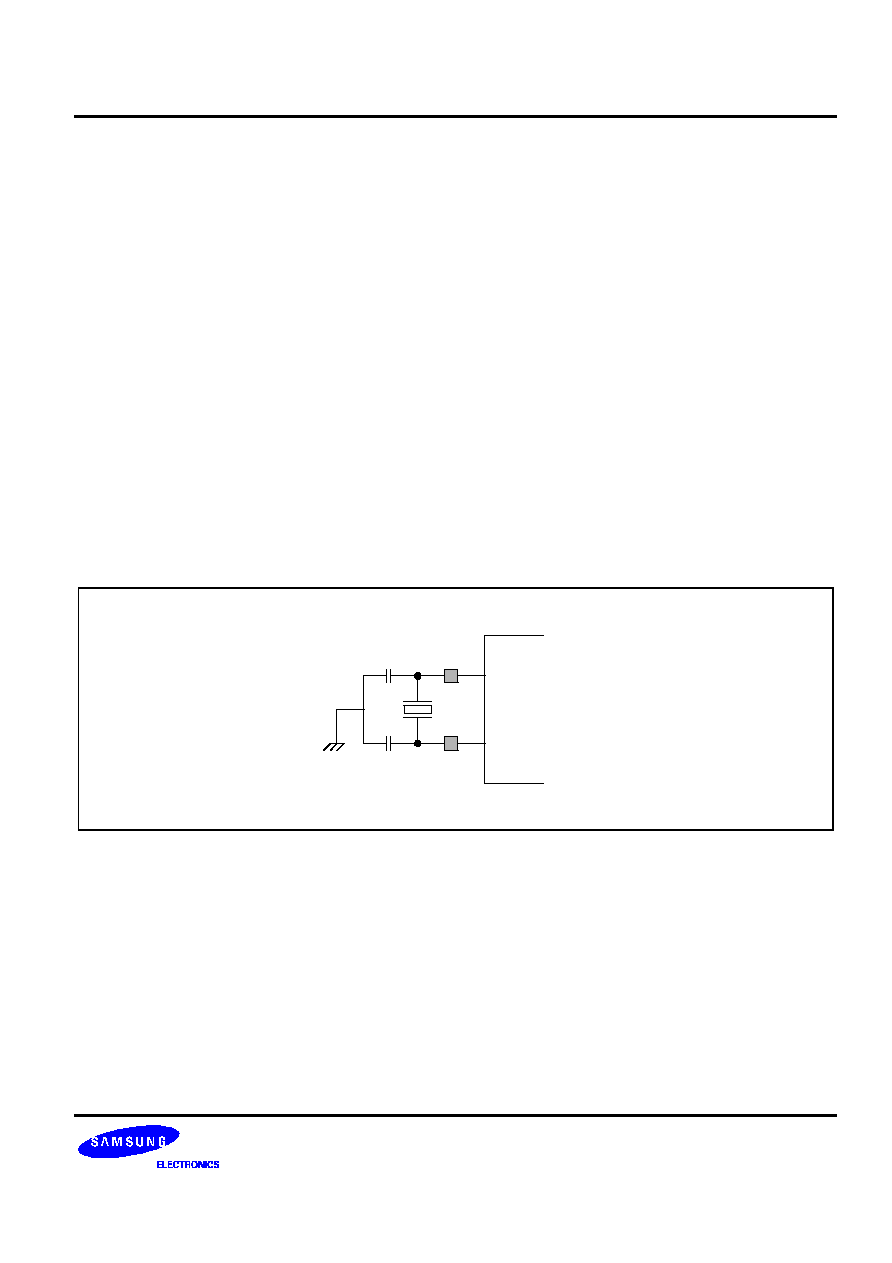

Main Oscillator Circuit (Crystal or Ceramic Oscillator)......................................................... 8-1

8-2

Main Oscillator Circuit (RC Oscillator)................................................................................. 8-2

8-3

Sub Oscillator Circuit (Crystal or Ceramic Oscillator) .......................................................... 8-2

8-4

System Clock Circuit Diagram ............................................................................................ 8-3

8-5

Power Control Register (PCON) ......................................................................................... 8-4

8-6

Oscillator Control Register (OSCCON) ............................................................................... 8-4

8-7

Main Oscillator Clock Output Functional Block Diagram ..................................................... 8-5

8-8

Main Oscillator Clock Output Control Register (CLOCON) .................................................. 8-5

10-1

Port 0 Control Register (P0CON) ........................................................................................ 10-1

10-2

Port 1 Control Register (P1CON) ........................................................................................ 10-2

10-3

Port 1 Pull-Up Control Register (P1PUR) ............................................................................ 10-2

10-4

Port 2 High-Byte Control Register (P2CONH) ..................................................................... 10-3

10-5

Port 2 Low-Byte Control Register (P2CONL)....................................................................... 10-3

10-6

Port 3 High-Byte Control Register (P3CONH) ..................................................................... 10-4

10-7

Port 3 Low-Byte Control Register (P3CONL)....................................................................... 10-4

10-8

Port 4 High-Byte Control Register (P4CONH) ..................................................................... 10-5

10-9

Port 4 Low-Byte Control Register (P4CONL)....................................................................... 10-5

10-10

Port 5 High-Byte Control Register (P5CONH) ..................................................................... 10-6

10-11

Port 5 Low-Byte Control Register (P5CONL)....................................................................... 10-6

10-12

Port 6 Control Register (P6CON) ........................................................................................ 10-7

10-13

Port 7 Control Register (P7CON) ........................................................................................ 10-7

11-1

Watchdog Timer Control Register (WDTCON) ................................................................... 11-1

11-2

Basic Timer & Watchdog Timer Functional Block Diagram ................................................. 11-2

12-1

Watch Timer Circuit Diagram ............................................................................................. 12-2

13-1

Timer 0 Control Register (T0CON) ..................................................................................... 13-3

13-2

Timer 0 Functional Block Diagram...................................................................................... 13-4

13-3

Timer 0 Counter and Data Registers (T0CNTH/L, T0DATAH/L) .......................................... 13-5

14-1

Timer 1 Control Register (T1CON) ..................................................................................... 14-2

14-2

Timer 1 Functional Block Diagram...................................................................................... 14-3

14-3

Timer 1 Counter Register (T1CNTH/L)................................................................................ 14-4

14-4

Timer 1 Data Register (T1DATAH/L) .................................................................................. 14-4

15-1

Timer 2 Control Register (T2CON) ..................................................................................... 15-3

15-2

Timer 2 Functional Block Diagram...................................................................................... 15-4

S3CK225/FK225 MICROCONTROLLER

xiii

List of Figures

(Continued)

Figure

Title

Page

Number

Number

16-1

Timer 3 Functional Block Diagram...................................................................................... 16-2

16-2

Timer 3 Control Register (T3CON) ..................................................................................... 16-3

16-3

Timer 3 Data Registers (T3DATAH/L)................................................................................. 16-3

16-4

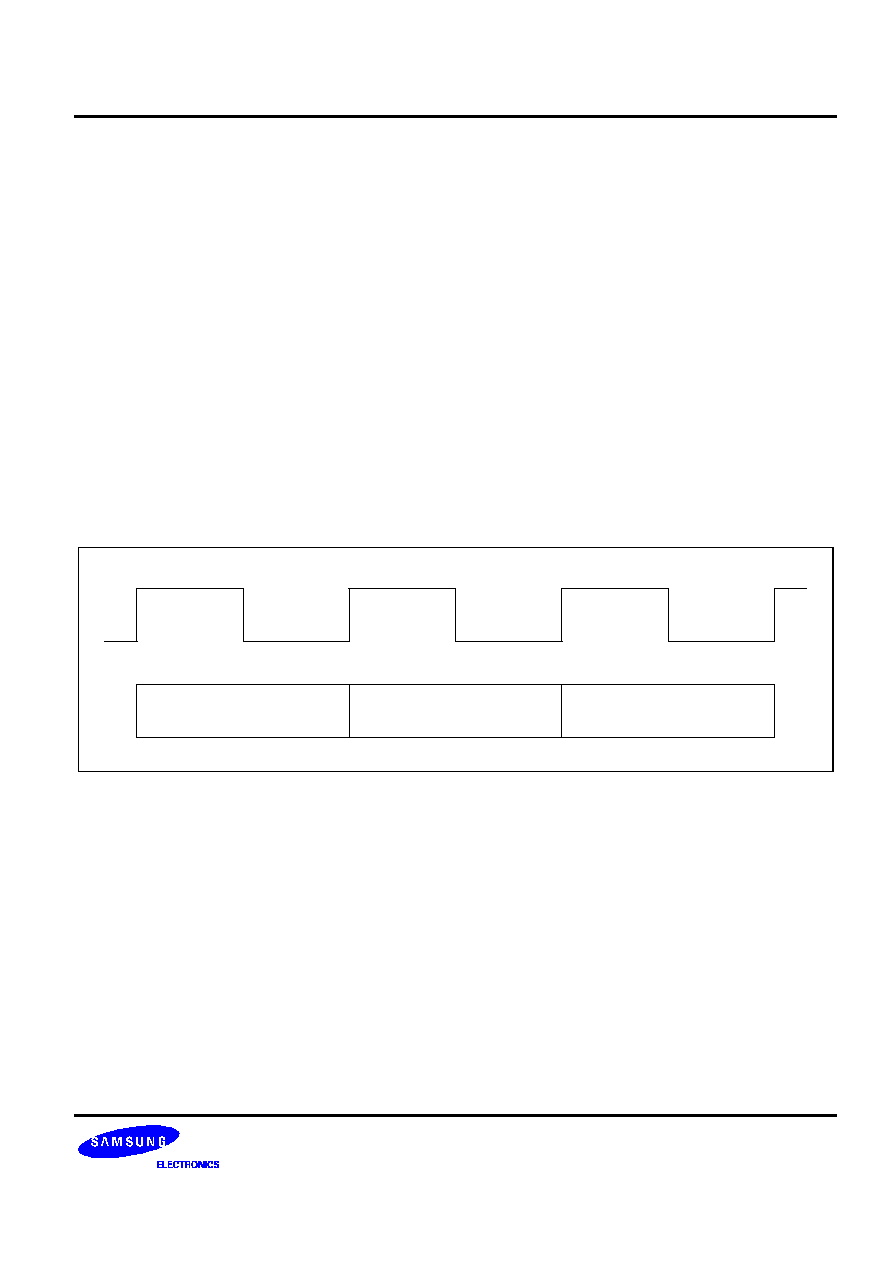

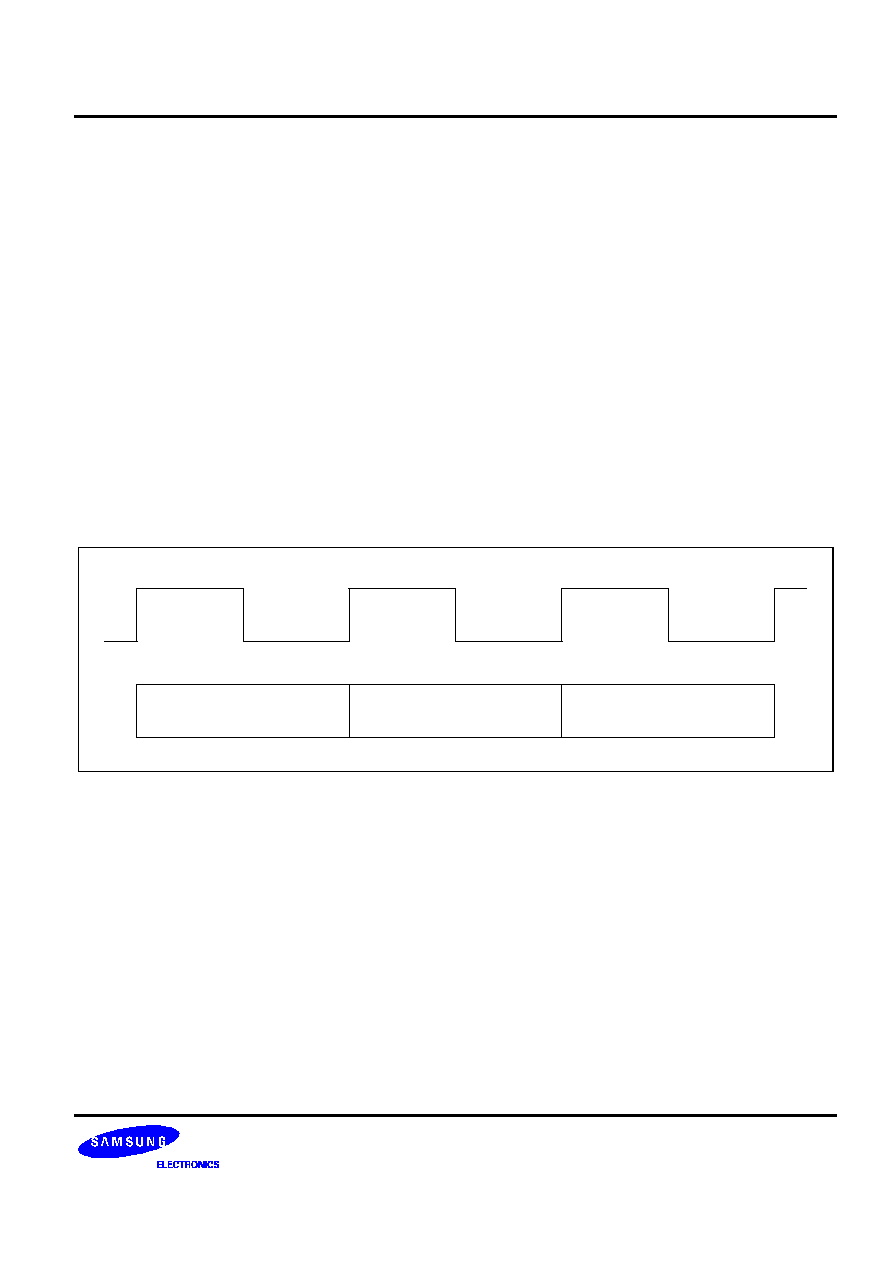

Timer 3 Output Flip-Flop Waveforms in Repeat Mode........................................................ 16-5

17-1

Serial I/O Module Control Registers (SIOCON) .................................................................. 17-2

17-2

SIO Pre-scaler Register (SIOPS)........................................................................................ 17-2

17-3

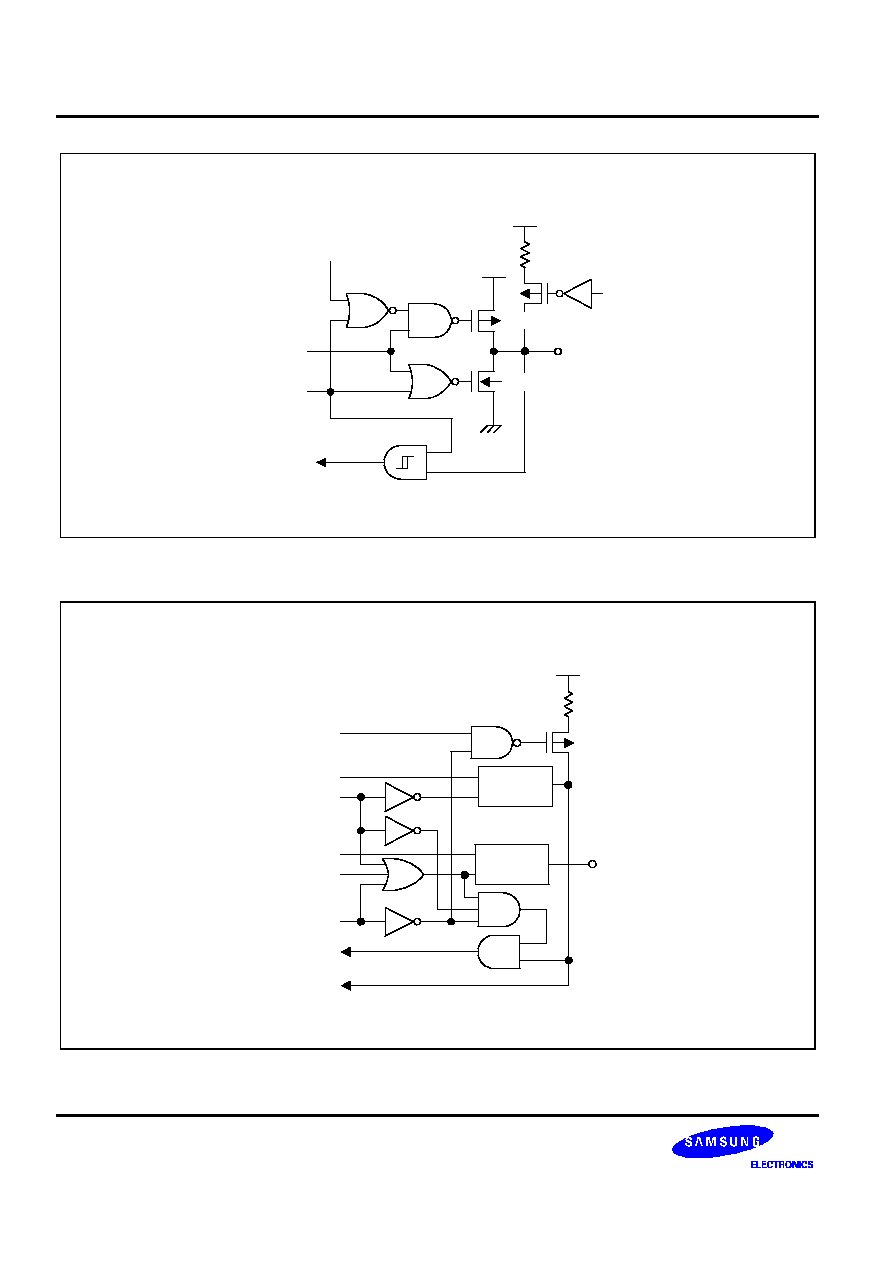

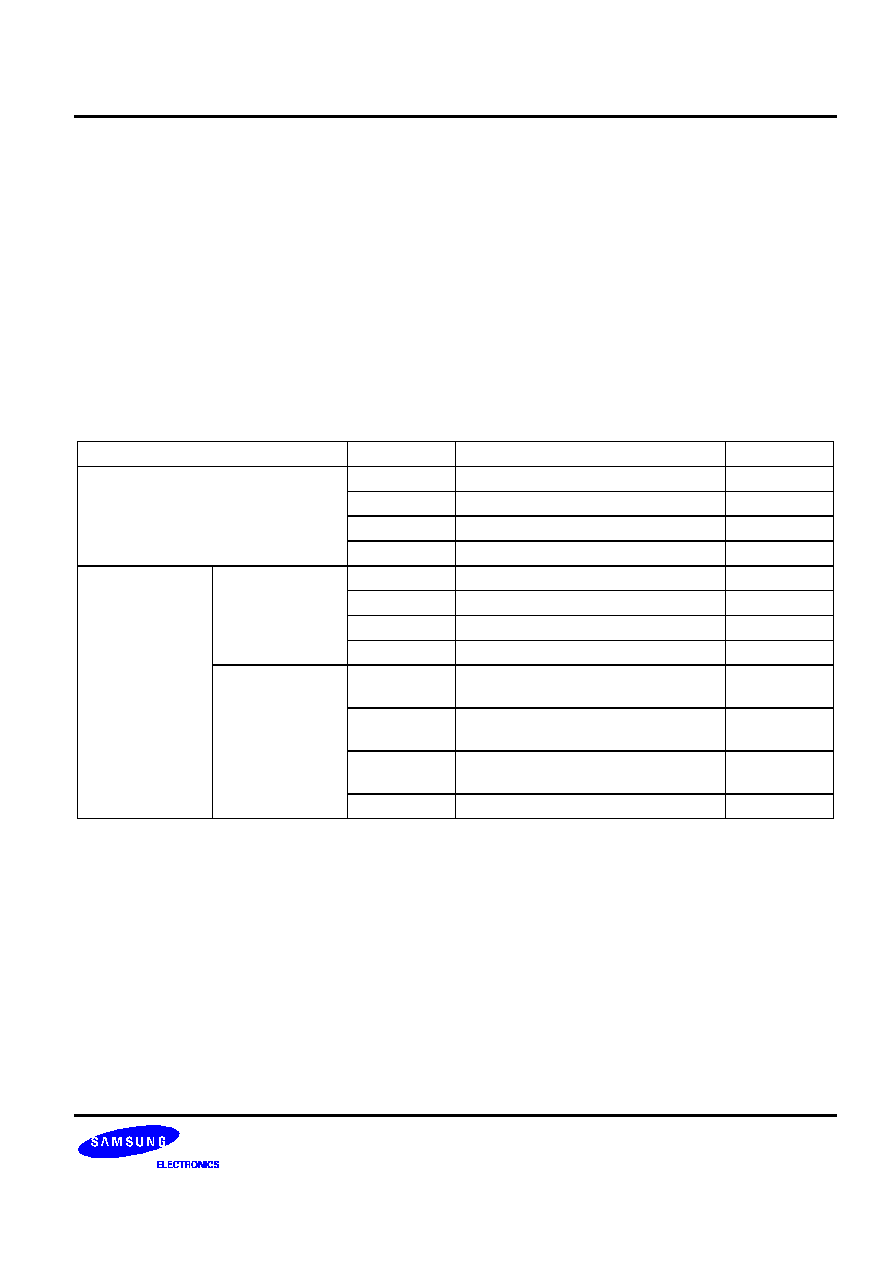

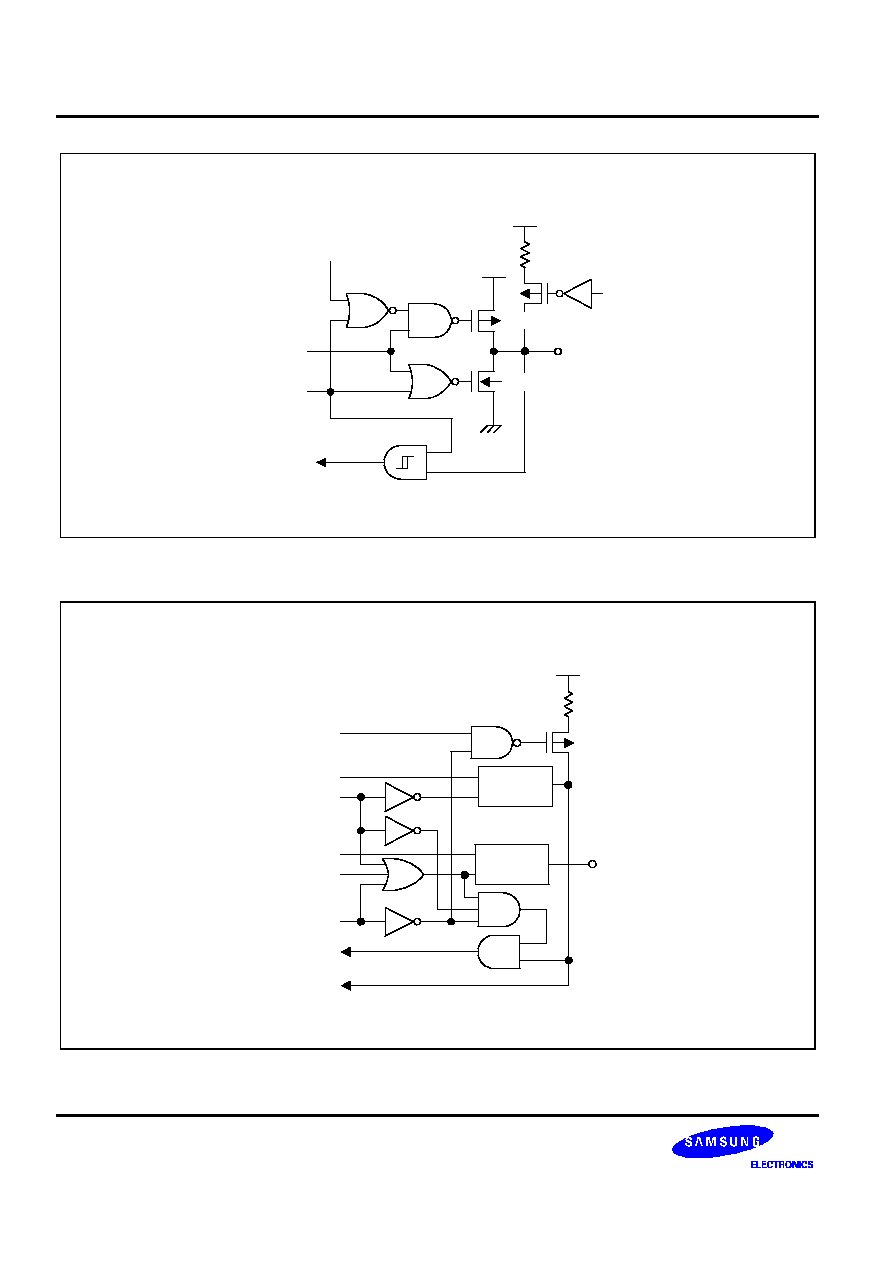

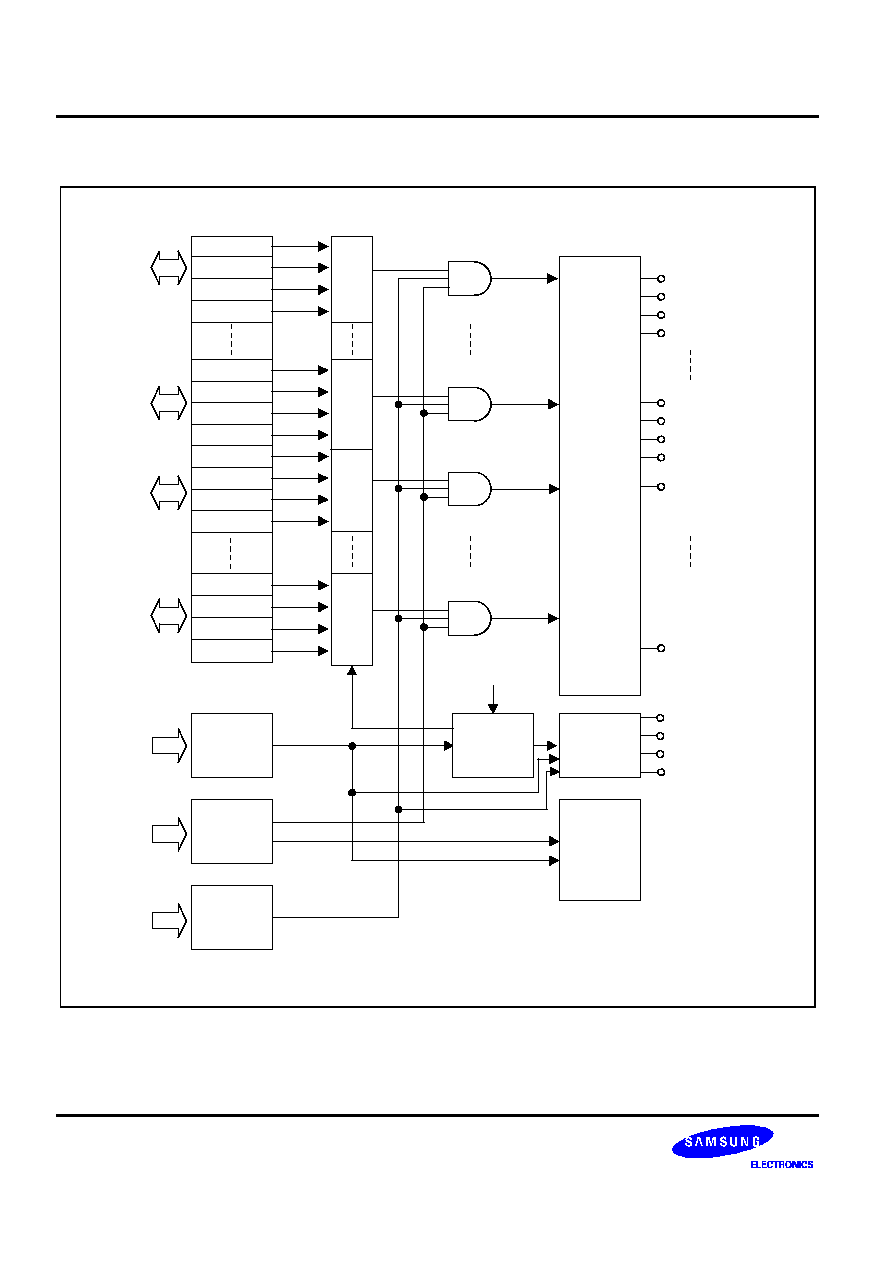

SIO Function Block Diagram .............................................................................................. 17-3

17-4

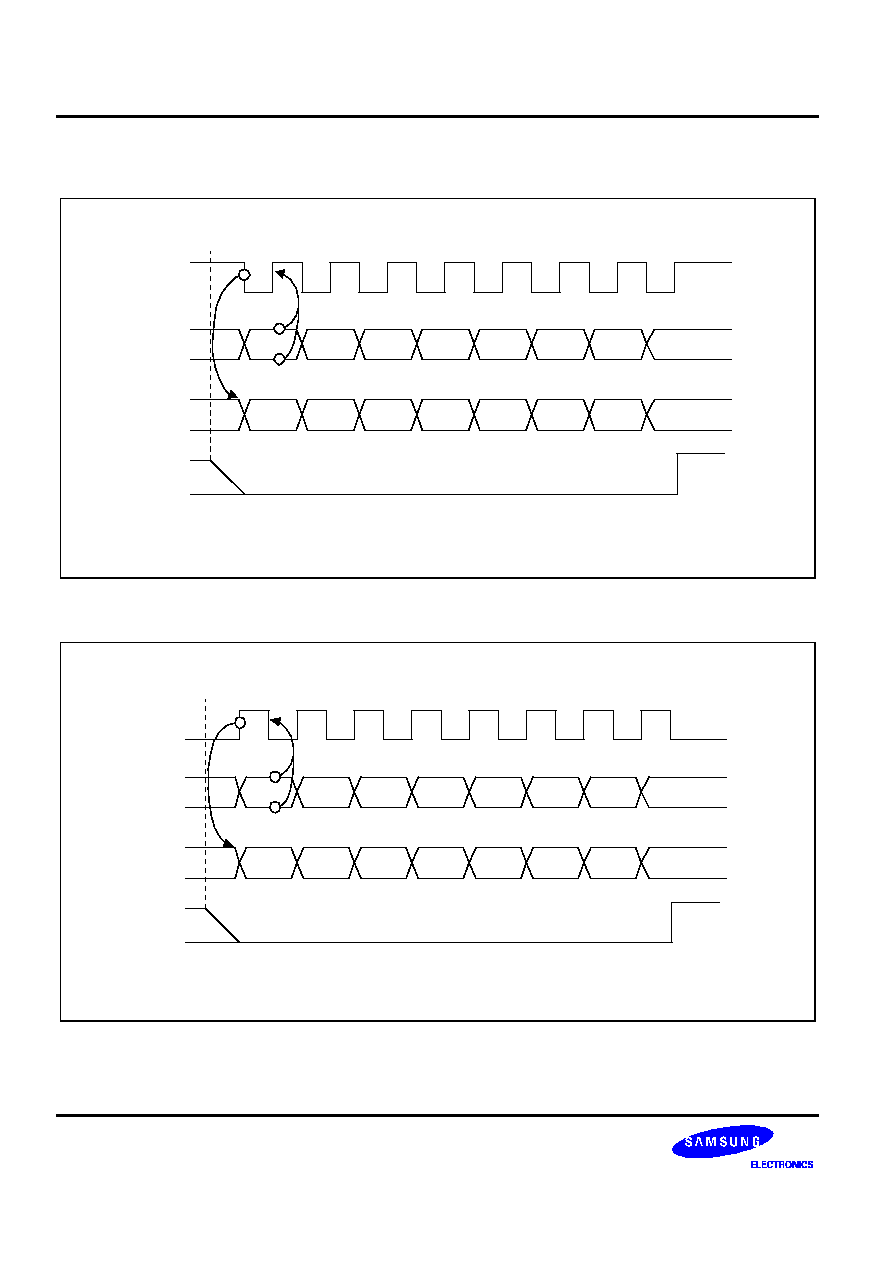

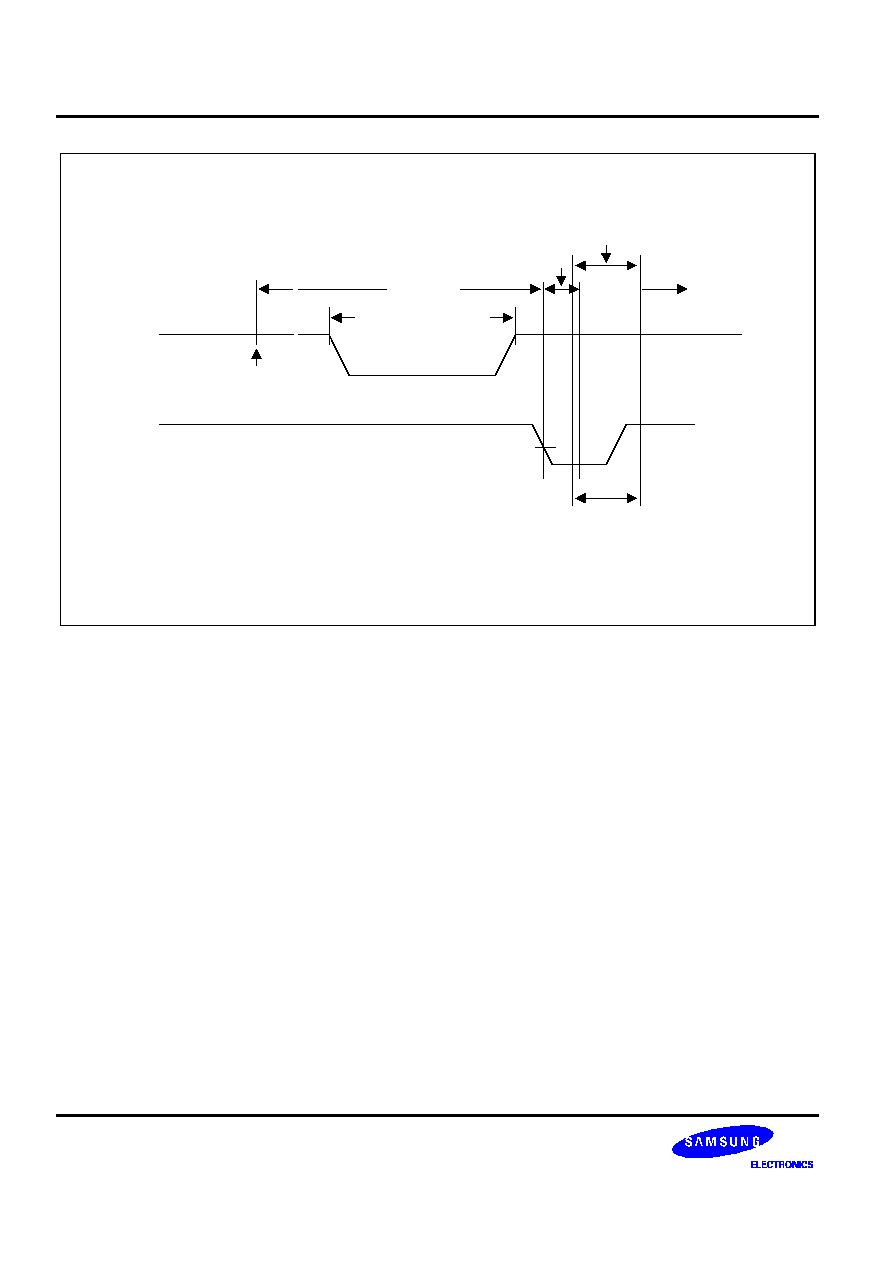

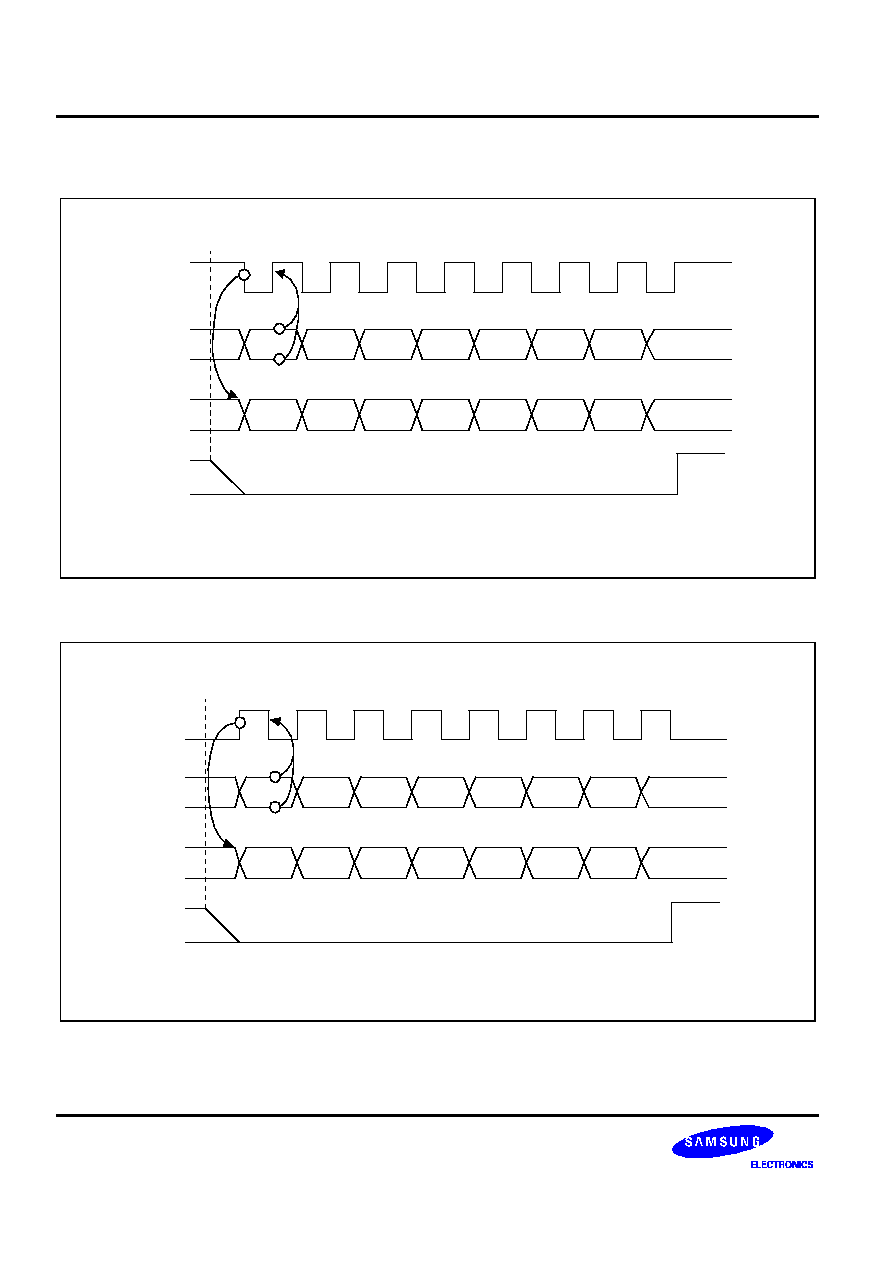

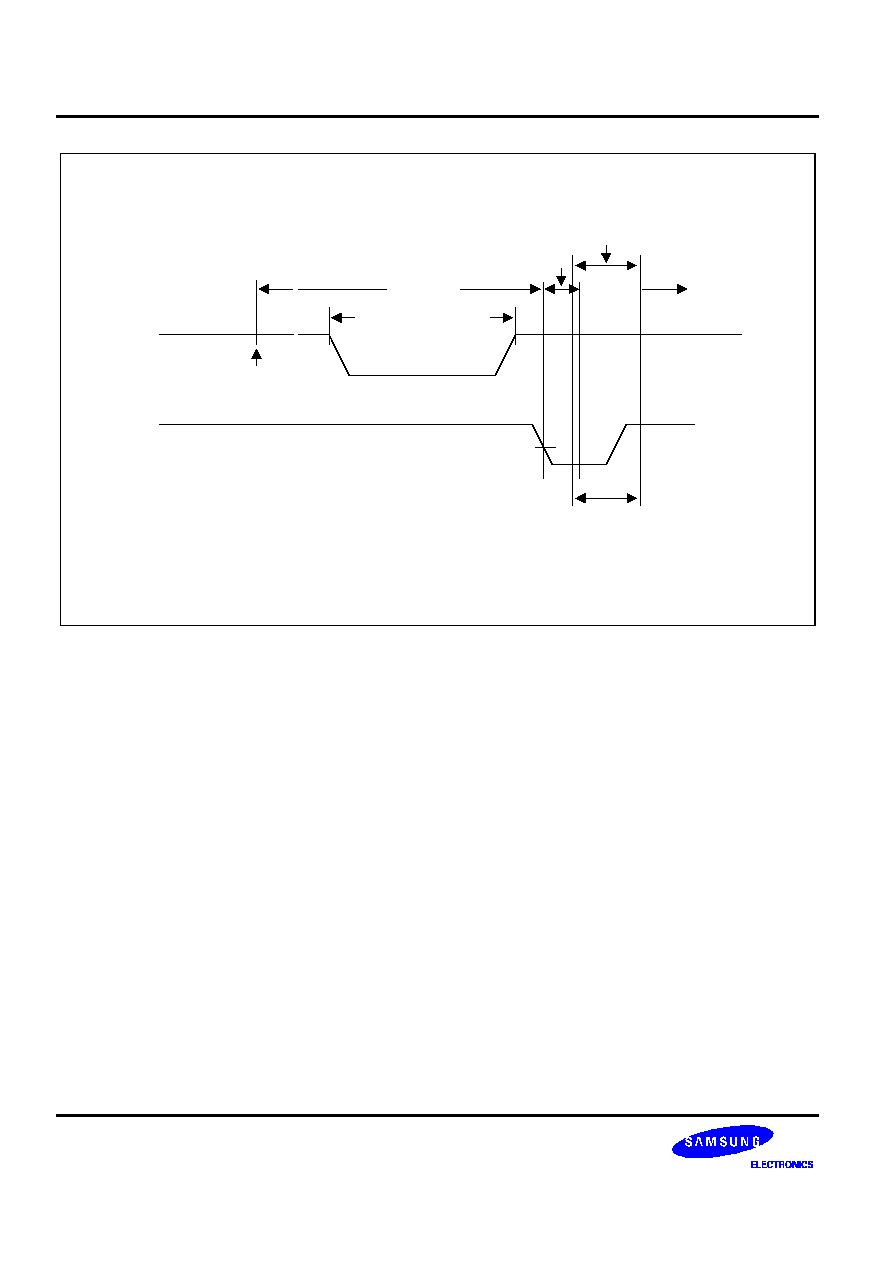

Serial I/O Timing in Transmit/Receive Mode(Tx at falling, SIOCON.4=0) ........................... 17-4

17-5

Serial I/O Timing in Transmit/Receive Mode(Tx at rising, SIOCON.4=1) ............................ 17-4

18-1

LCD Function Diagram ....................................................................................................... 18-1

18-2

LCD Circuit Diagram .......................................................................................................... 18-2

18-3

LCD Display Data RAM Organization ................................................................................. 18-3

18-4

LCD Port Control Resister1 (LPOT1) .................................................................................. 18-7

18-5

LCD Port Control Resister2 (LPOT2) .................................................................................. 18-7

18-6

Internal Voltage Dividing Resistor Connection .................................................................... 18-8

18-7

Select/No-Select Bias Signals in Static Display Mode......................................................... 18-9

18-8

Select/No-Select Bias Signals in 1/2 Duty, 1/2 Bias Display Mode ...................................... 18-10

18-9

Select/No-Select Bias Signals in 1/3 Duty, 1/3 Bias Display Mode ...................................... 18-10

18-10

LCD Signal and Wave Forms Example in 1/2 Duty, 1/2 Bias Display Mode ........................ 18-11

18-11

LCD Signals and Wave Forms Example in 1/3 Duty, 1/3 Bias Display Mode ...................... 18-12

18-12

LCD Signals and Wave Forms Example in 1/4 Duty, 1/3 Bias Display Mode ...................... 18-13

19-1

A/D Converter Control Register (ADCON) .......................................................................... 19-2

19-2

A/D Converter Data Register (ADDATAH/ADDATAL) ......................................................... 19-3

19-3

A/D Converter Functional Block Diagram ........................................................................... 19-3

19-4

Recommended A/D Converter Circuit for Highest Absolute Accuracy ................................. 19-4

20-1

DAC Circuit Diagram .......................................................................................................... 20-2

20-2

Digital to Analog Converter Control Register (DACON)....................................................... 20-2

20-3

D/A Converter Data Register (DADATAH/DADATAL) ......................................................... 20-3

xiv

S3CK225/FK225 MICROCONTROLLER

List of Figures

(Continued)

Figure

Title

Page

Number

Number

21-1

OP AMP Control Register (OPCON)................................................................................... 21-1

21-2

OP AMP Block Diagram ..................................................................................................... 21-2

22-1

Input Timing for External Interrupts (Port 0) ........................................................................ 22-4

22-2

Input Timing for

RESET ...............................................................................................................

22-4

22-3

Stop Mode Release Timing When Initiated by a

RESET..........................................................

22-5

22-4

Stop Mode Release Timing Initiated by Interrupts ............................................................... 22-6

22-5

Serial Data Transfer Timing................................................................................................ 22-8

22-6

Clock Timing Measurement at X

IN

..............................................................................................

22-10

22-7

Clock Timing Measurement at XT

IN

............................................................................................

22-10

22-8

Operating Voltage Range ................................................................................................... 22-12

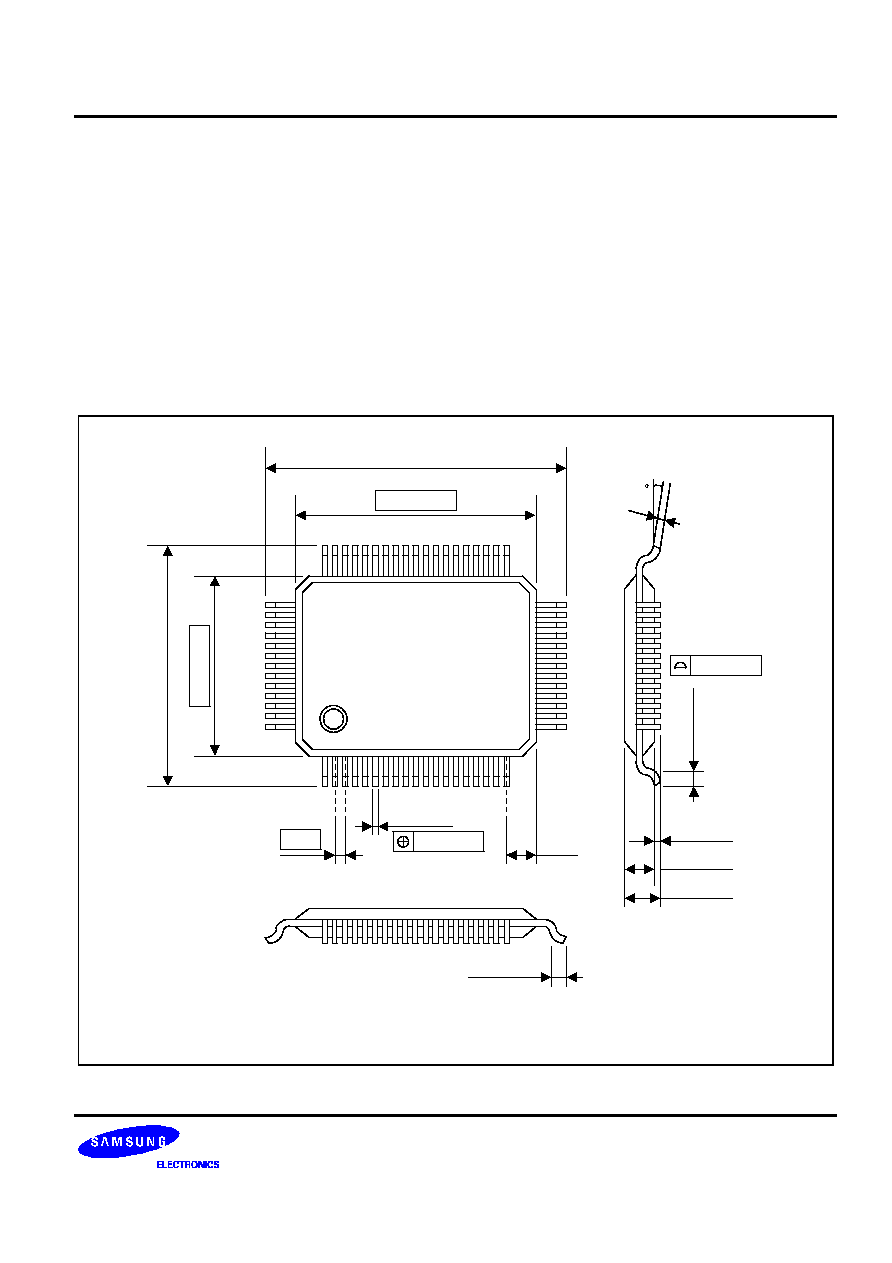

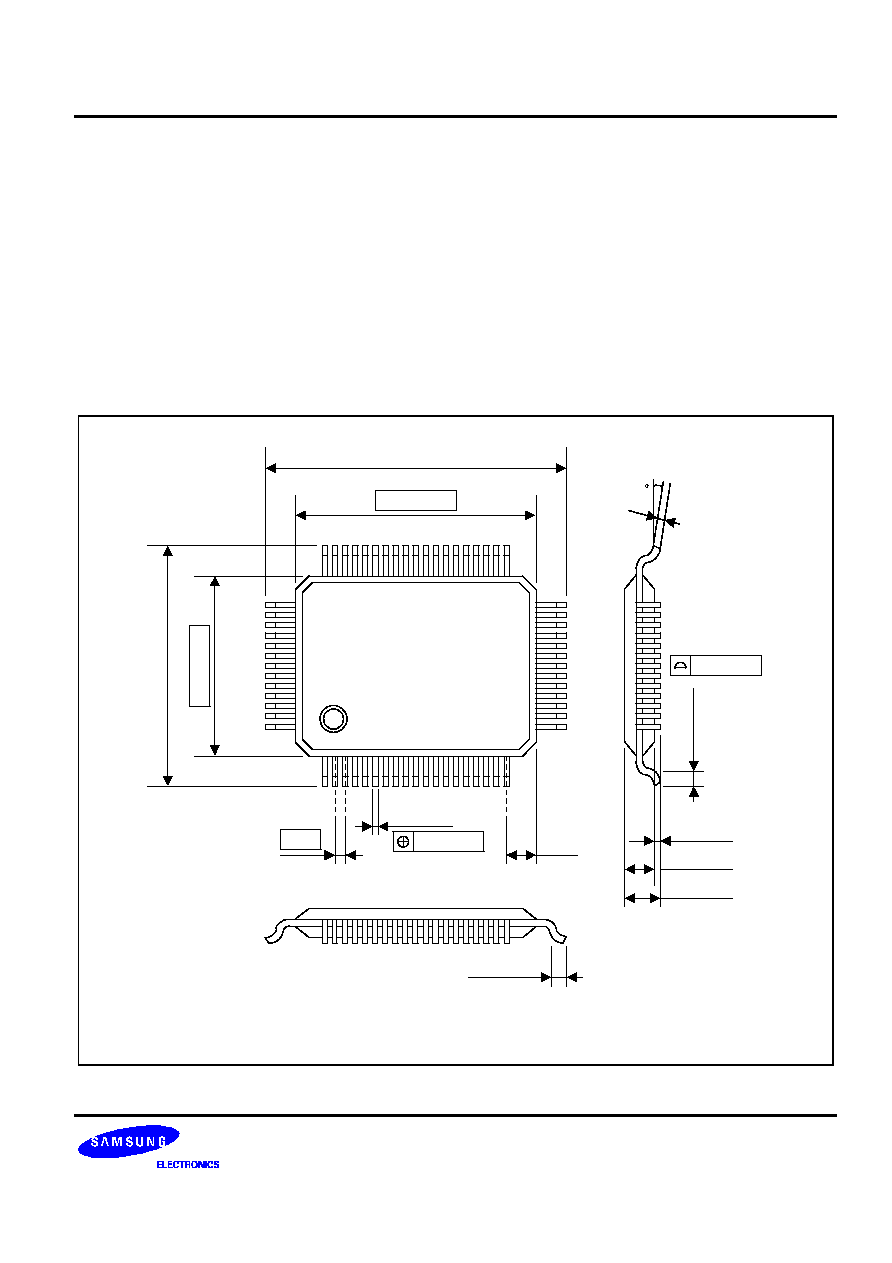

23-1

64-Pin QFP Package Dimensions (64-QFP-1420F) ............................................................ 23-1

24-1

S3FK225 Pin Assignments (64-QFP-1420F)....................................................................... 24-2

25-1

Emulation Probe Board Configuration................................................................................. 25-2

S3CK225/FK225 MICROCONTROLLER

xv

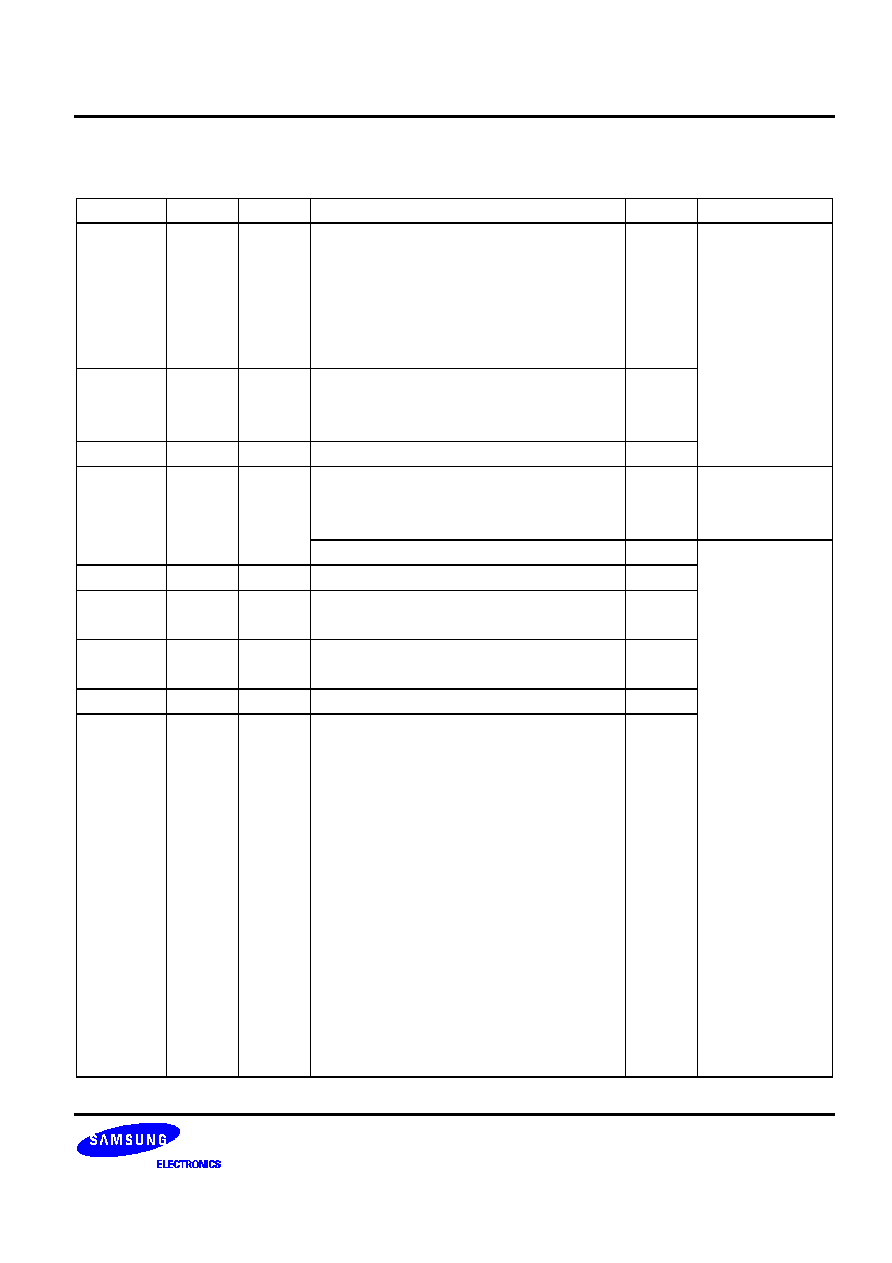

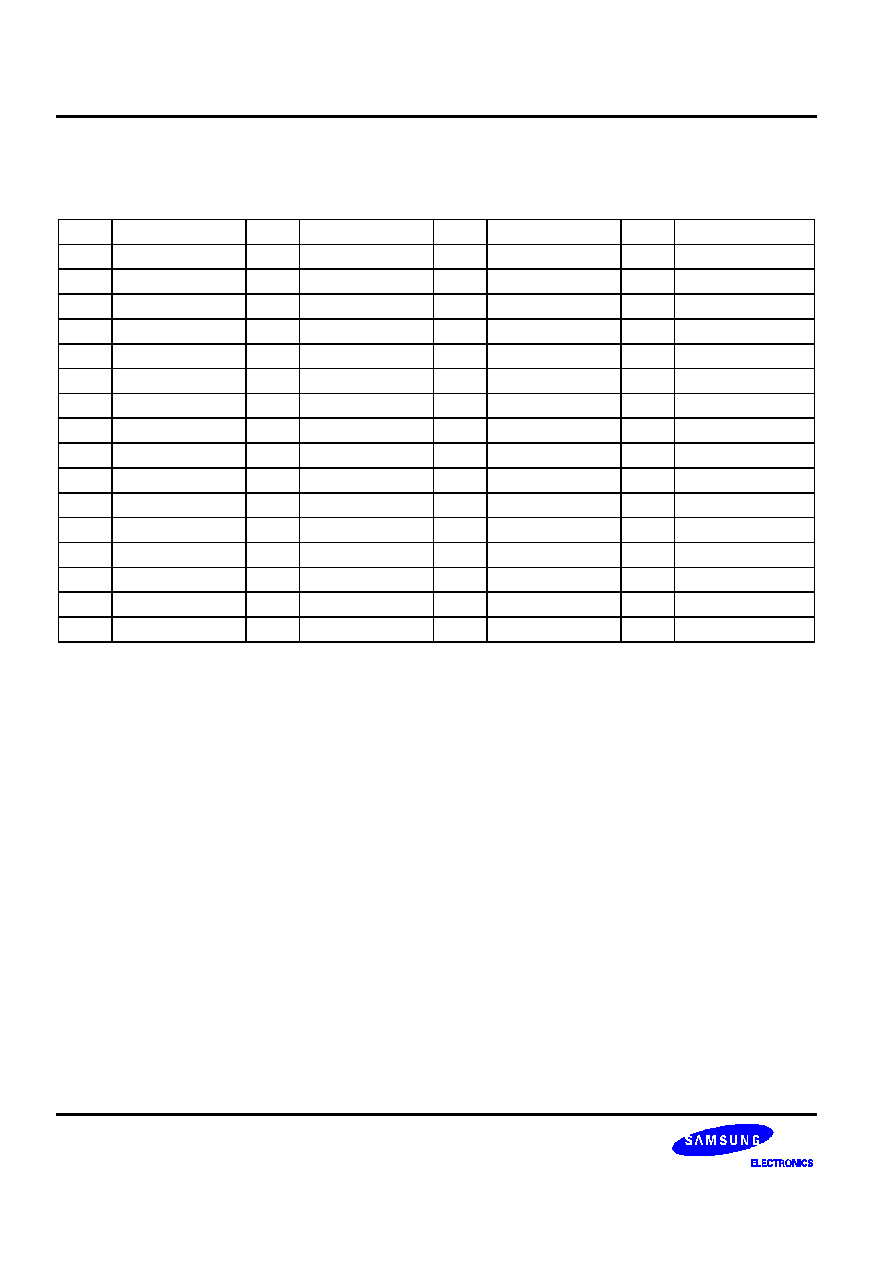

List of Tables

Table

Title

Page

Number

Number

1-1

Pin Descriptions ................................................................................................................. 1-9

3-1

General and Special Purpose Registers.............................................................................. 3-1

3-2

Status Register 0 configuration ........................................................................................... 3-3

3-3

Status Register 1: SR1 ....................................................................................................... 3-4

4-1

Registers ............................................................................................................................ 4-2

6-1

Exceptions.......................................................................................................................... 6-1

7-1

Instruction Notation Conventions ........................................................................................ 7-1

7-2

Overall Instruction Set Map ................................................................................................ 7-2

7-3

Instruction Encoding ........................................................................................................... 7-4

7-4

Index Code Information ("idx") ............................................................................................ 7-7

7-5

Index Modification Code Information ("mod")...................................................................... 7-7

7-6

Condition Code Information ("cc")....................................................................................... 7-7

7-7

"ALUop1" Code Information ................................................................................................ 7-8

7-8

"ALUop2" Code Information ................................................................................................ 7-8

7-9

"MODop1" Code Information .............................................................................................. 7-8

12-1

Watch Timer Control Register (WTCON): 8-Bit R/W .......................................................... 12-1

18-1

LCD Control Register (LCON) Organization........................................................................ 18-4

18-2

Relationship of LCON.0 and LMOD.3 Bit Settings .............................................................. 18-4

18-3

LCD Clock Signal (LCDCK) Frame Frequency.................................................................... 18-5

18-4

LCD Mode Control Register (LMOD) Organization, 4CH..................................................... 18-6

18-5

Maximum Number of Display Digits per Duty Cycle............................................................ 18-6

20-1

DADATA Setting to Generate Analog Voltage .................................................................... 20-3

xvi

S3CK225/FK225 MICROCONTROLLER

List of Tables

(Continued)

Table

Title

Page

Number

Number

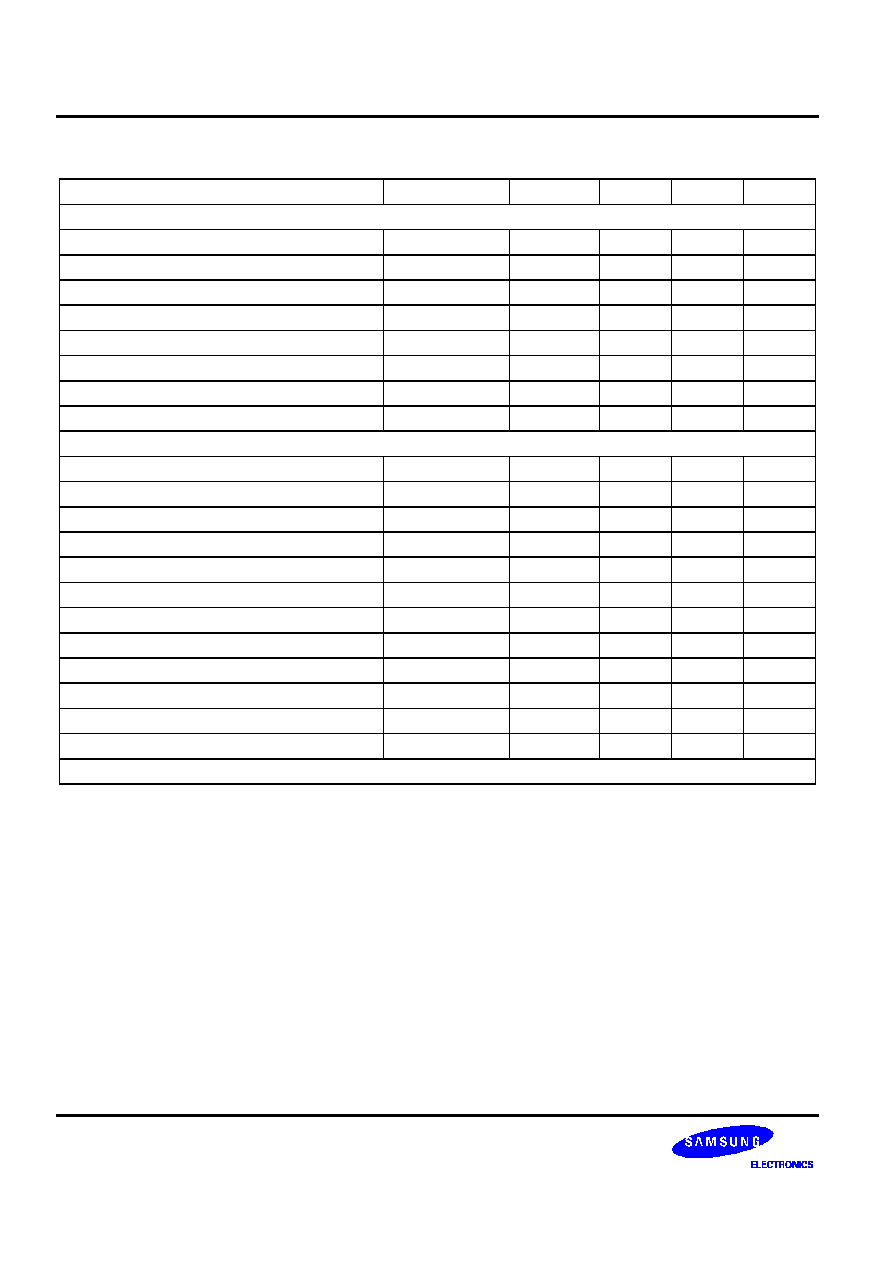

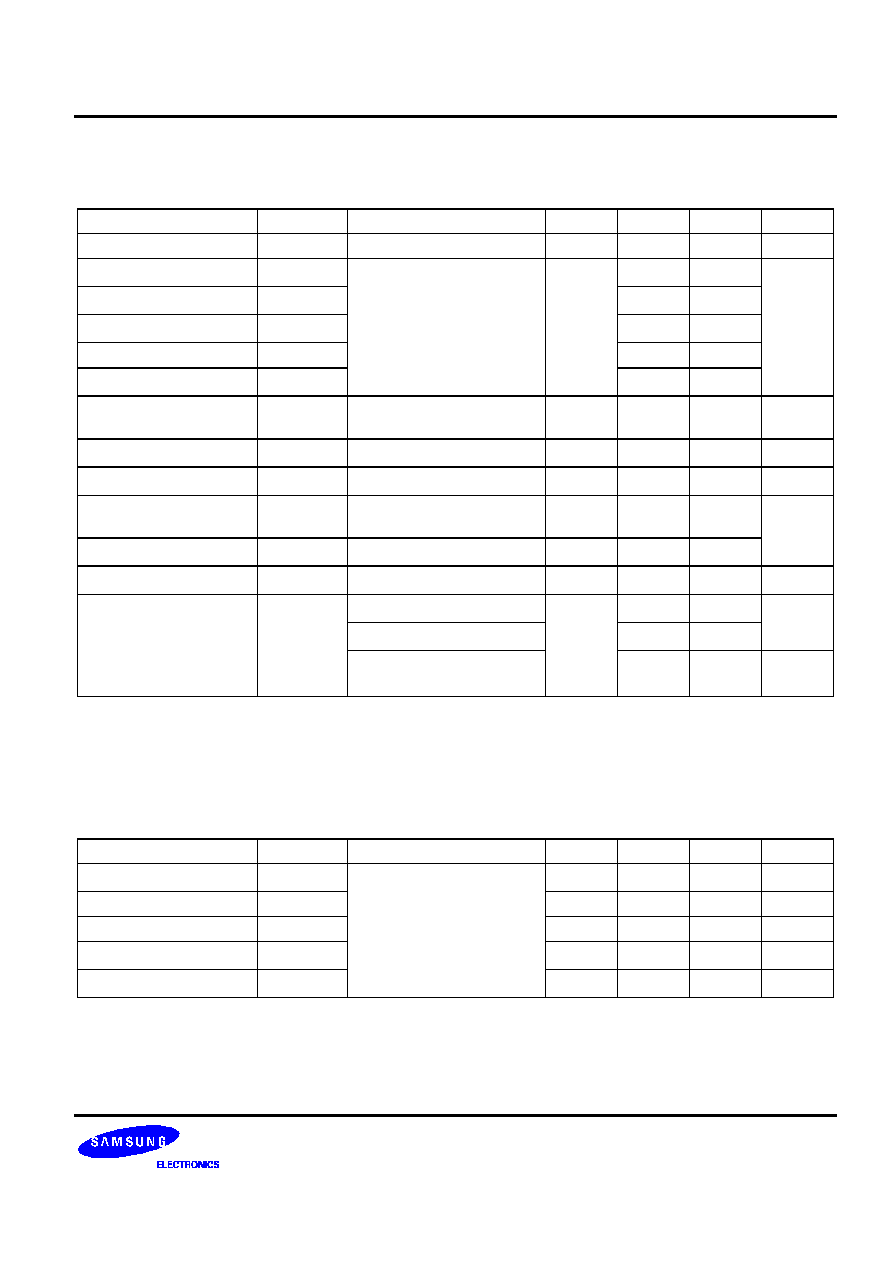

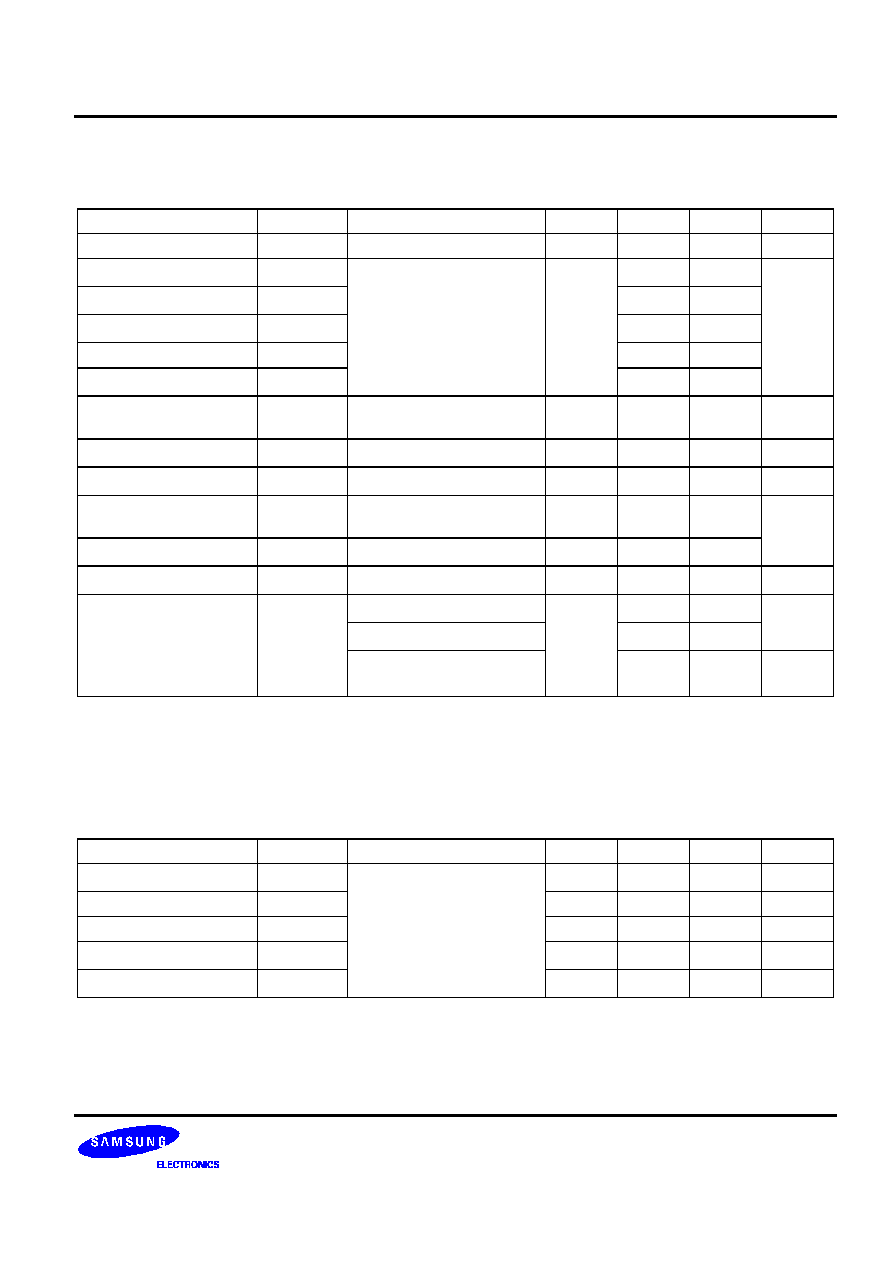

22-1

Absolute Maximum Ratings ................................................................................................ 22-1

22-2

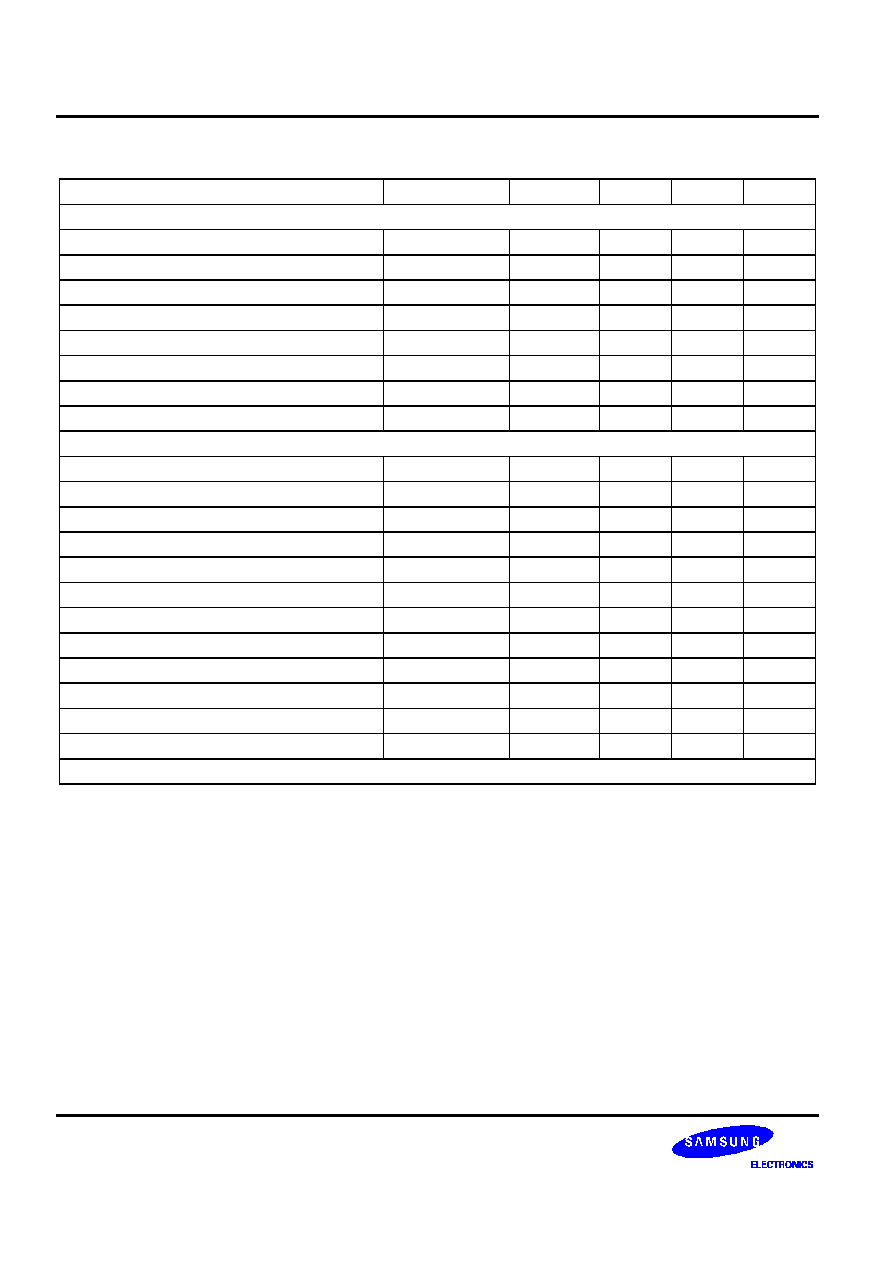

D.C. Electrical Characteristics ............................................................................................ 22-1

22-3

A.C. Electrical Characteristics............................................................................................. 22-4

22-4

Input/Output Capacitance ................................................................................................... 22-5

22-5

Data Retention Supply Voltage in Stop Mode ..................................................................... 22-5

22-6

A/D Converter Electrical Characteristics ............................................................................. 22-7

22-7

D/A Converter Electrical Characteristics ............................................................................. 22-7

22-8

Synchronous SIO Electrical Characteristics ........................................................................ 22-8

22-9

Main Oscillator Frequency (f

OSC1

) ...................................................................................... 22-9

22-10

Main Oscillator Clock Stabilization Time (T

ST1

) .................................................................. 22-9

22-11

Sub Oscillator Frequency (f

OSC2

)........................................................................................ 22-10

22-12

Sub Oscillator (Crystal) Start up Time (t

ST2

) ....................................................................... 22-11

22-13

OP Amplifier Characteristics............................................................................................... 22-11

24-1

Descriptions of Pins Used to Read/Write the FLASH ROM ................................................. 24-3

S3CK225/FK225 MICROCONTROLLER

xvii

List of Programming Tips

Description

Page

Number

Chapter 6: Exceptions

Interrupt Programming Tip 1 .................................................................................................................... 6-7

Interrupt Programming Tip 2 .................................................................................................................... 6-8

Chapter 16: 8-Bit Timer 3

To generate 38 kHz, 1/3duty signal through P7.2

.............................................................................................

16-6

To generate a one pulse signal through P7.2

....................................................................................................

16-7

S3CK225/FK225 MICROCONTROLLER

xix

List of Instruction Descriptions

Instruction

Full Instruction Name

Page

Mnemonic

Number

ADC

Add with Carry ....................................................................................................... 7-30

ADD

Add ........................................................................................................................ 7-31

AND

Bit-wise AND.......................................................................................................... 7-32

AND SR0

Bit-wise AND with SR0........................................................................................... 7-33

BANK

Bank Selection....................................................................................................... 7-34

BITC

Bit Complement ..................................................................................................... 7-35

BITR

Bit Reset ................................................................................................................ 7-36

BITS

Bit Set.................................................................................................................... 7-37

BITT

Bit Test .................................................................................................................. 7-38

BMC/BMS

TF bit clear/set ....................................................................................................... 7-39

CALL

Conditional subroutine call (Pseudo Instruction) .................................................... 7-40

CALLS

Call Subroutine ...................................................................................................... 7-41

CLD

Load into Coprocessor ........................................................................................... 7-42

CLD

Load from Coprocessor.......................................................................................... 7-43

COM

1's or Bit-wise Complement.................................................................................... 7-44

COM2

2's Complement ..................................................................................................... 7-45

COMC

Bit-wise Complement with Carry ............................................................................ 7-46

COP

Coprocessor........................................................................................................... 7-47

CP

Compare................................................................................................................ 7-48

CPC

Compare with Carry ............................................................................................... 7-49

DEC

Decrement ............................................................................................................. 7-50

DECC

Decrement with Carry ............................................................................................ 7-51

DI

Disable Interrupt (Pseudo Instruction) .................................................................... 7-52

EI

Enable Interrupt (Pseudo Instruction) .................................................................... 7-53

IDLE

Idle Operation (Pseudo Instruction) ....................................................................... 7-54

INC

Increment............................................................................................................... 7-55

INCC

Increment with Carry .............................................................................................. 7-56

IRET

Return from Interrupt Handling............................................................................... 7-57

JNZD

Jump Not Zero with Delay Slot............................................................................... 7-58

JP

Conditional Jump (Pseudo Instruction) .................................................................. 7-59

JR

Conditional Jump Relative ..................................................................................... 7-60

LCALL

Conditional Subroutine Call.................................................................................... 7-61

LD adr:8

Load into Memory .................................................................................................. 7-62

xx

S3CK225/FK225 MICROCONTROLLER

List of Instruction Descriptions

(Continued)

Instruction

Full Instruction Name

Page

Mnemonic

Number

LD @idm

Load into Memory Indexed ..................................................................................... 7-63

LD

Load Register......................................................................................................... 7-64

LD

Load GPR:bankd, GPR:banks................................................................................ 7-65

LD

Load GPR, TBH/TBL.............................................................................................. 7-66

LD

Load TBH/TBL, GPR.............................................................................................. 7-67

LD SPR

Load SPR

.........................................................................................................................

7-68

LD SPR0

Load SPR0 Immediate ........................................................................................... 7-69

LDC

Load Code ............................................................................................................. 7-70

LJP

Conditional Jump ................................................................................................... 7-71

LLNK

Linked Subroutine Call Conditional......................................................................... 7-72

LNK

Linked Subroutine Call (Pseudo Instruction) .......................................................... 7-73

LNKS

Linked Subroutine Call ........................................................................................... 7-74

LRET

Return from Linked Subroutine Call........................................................................ 7-75

NOP

No Operation.......................................................................................................... 7-76

OR

Bit-wise OR ............................................................................................................ 7-77

OR SR0

Bit-wise OR with SR0 ............................................................................................. 7-78

POP

POP ....................................................................................................................... 7-79

POP

POP to Register ..................................................................................................... 7-80

PUSH

Push Register......................................................................................................... 7-81

RET

Return from Subroutine .......................................................................................... 7-82

RL

Rotate Left ............................................................................................................. 7-83

RLC

Rotate Left with Carry ............................................................................................ 7-84

RR

Rotate Right ........................................................................................................... 7-85

RRC

Rotate Right with Carry .......................................................................................... 7-86

SBC

Subtract with Carry................................................................................................. 7-87

SL

Shift Left ................................................................................................................ 7-88

SLA

Shift Left Arithmetic ............................................................................................... 7-89

SR

Shift Right .............................................................................................................. 7-90

SRA

Shift Right Arithmetic ............................................................................................. 7-91

STOP

Stop Operation (Pseudo Instruction) ...................................................................... 7-92

SUB

Subtract ................................................................................................................. 7-93

SWAP

Swap...................................................................................................................... 7-94

SYS

System................................................................................................................... 7-95

TM

Test Multiple Bits.................................................................................................... 7-96

XOR

Exclusive OR ......................................................................................................... 7-97

S3CK225/FK225

PRODUCT OVERVIEW

1-1

1

PRODUCT OVERVIEW

OVERVIEW

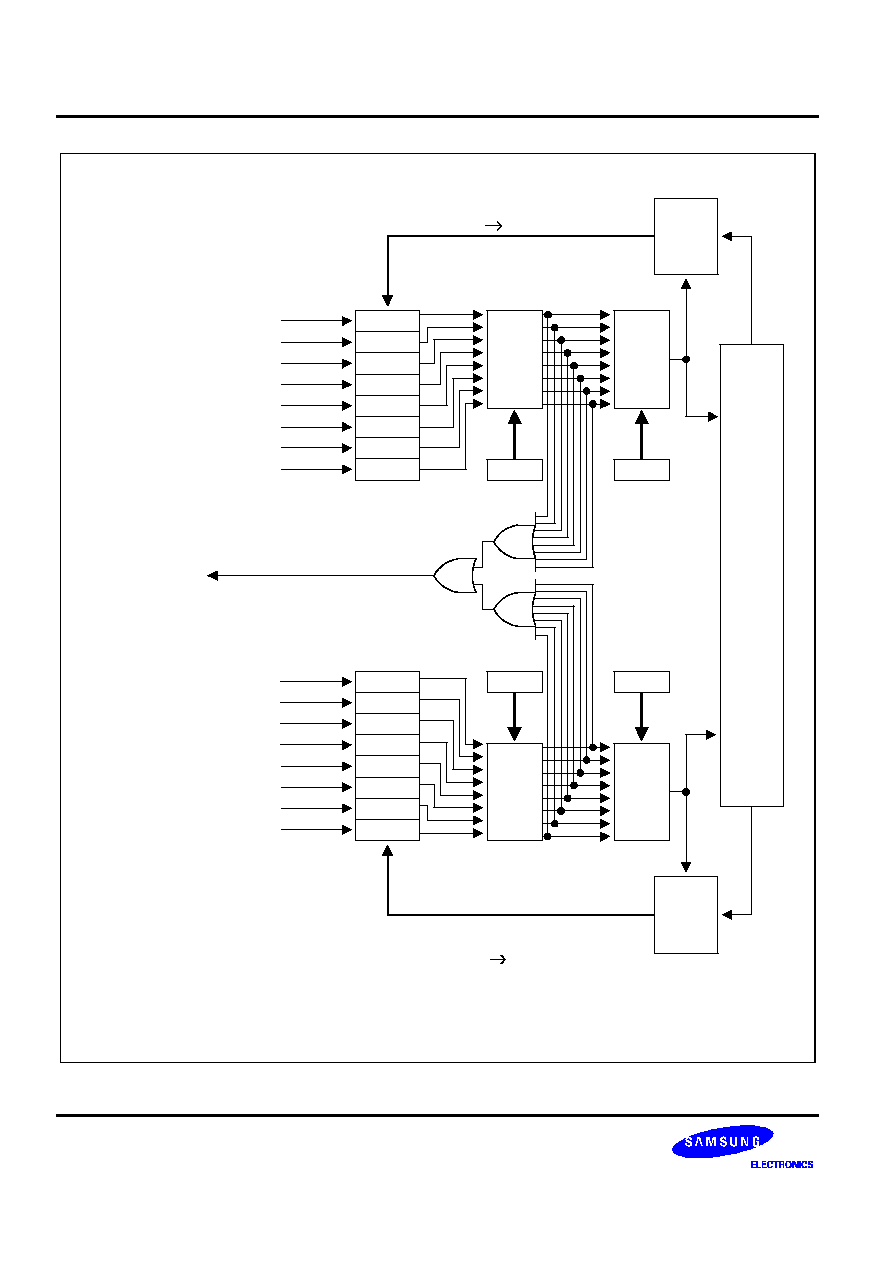

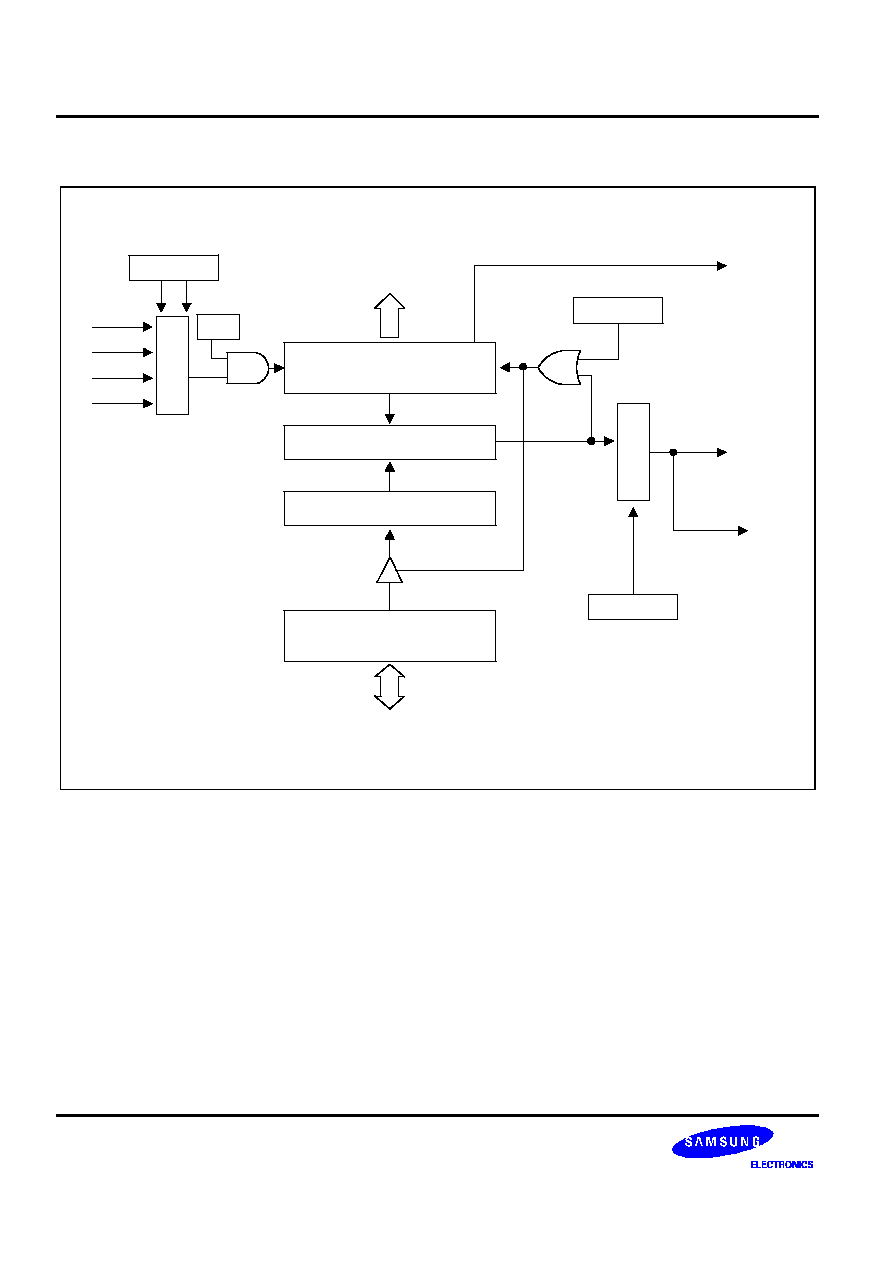

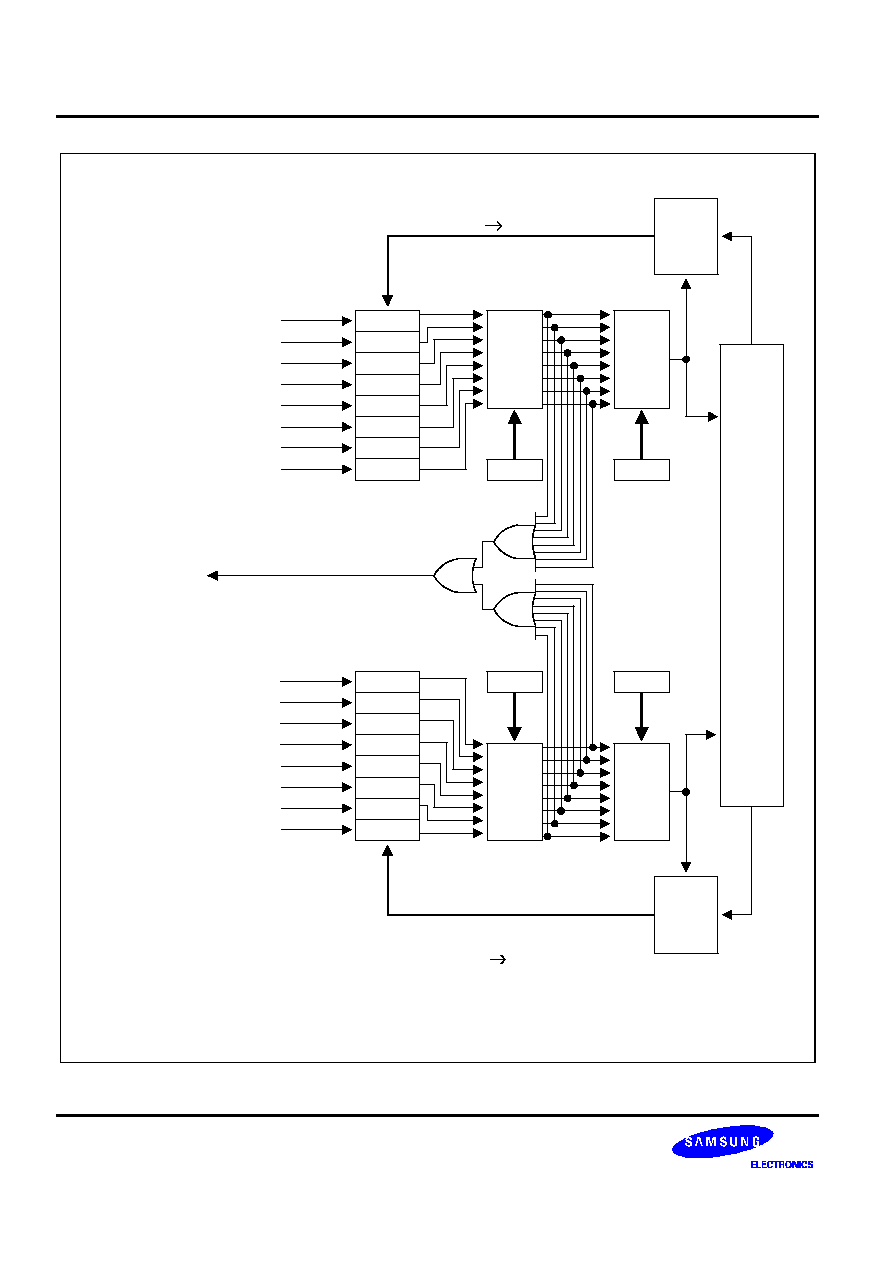

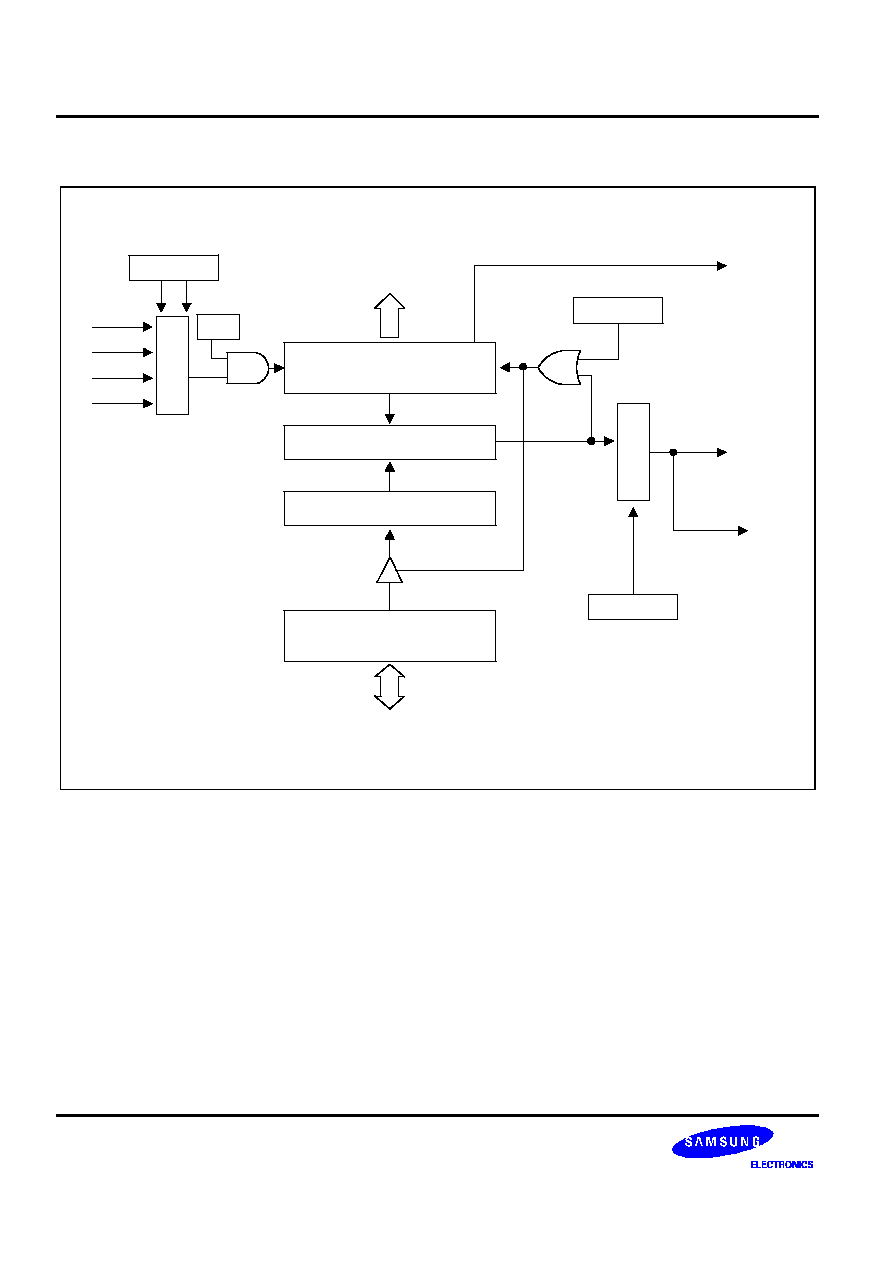

The S3CK225/FK225 single-chip CMOS microcontroller is designed for high performance using Samsung's new

8-bit CPU core, CalmRISC.

CalmRISC is an 8-bit low power RISC microcontroller. Its basic architecture follows Harvard style, that is, it has

separate program memory and data memory. Both instruction and data can be fetched simultaneously without

causing a stall, using separate paths for memory access. Represented below is the top block diagram of the

CalmRISC microcontroller.

PRODUCT OVERVIEW

S3CK225/FK225

1-2

BBUS[7:0]

20

Program Memory Address

Generation Unit

PC[19:0]

Hardware

Stack

HS[0]

HS[15]

8

8

R0

R3

R1

R2

ALU

ABUS[7:0]

ALUL

ALUR

PA[19:0]

PD[15:0]

IDL0

IDL1

SR0

SR1

ILH

ILX

ILL

SPR

IDH

DO[7:0]

DI[7:0]

GPR

Data Memory

Address

Generation Unit

DA[15:0]

20

Flag

RBUS

TBH TBL

Figure 1-1. Top Block Diagram

S3CK225/FK225

PRODUCT OVERVIEW

1-3

The CalmRISC building blocks consist of:

-- An 8-bit ALU

-- 16 general purpose registers (GPR)

-- 11 special purpose registers (SPR)

-- 16-level hardware stack

-- Program memory address generation unit

-- Data memory address generation unit

Sixteen GPRs are grouped into four banks (Bank0 to Bank3), and each bank has four 8-bit registers (R0, R1, R2,

and R3). SPRs, designed for special purposes, include status registers, link registers for branch-link instructions,

and data memory index registers. The data memory address generation unit provides the data memory address

(denoted as DA[15:0] in the top block diagram) for a data memory access instruction. Data memory contents are

accessed through DI[7:0] for read operations and DO[7:0] for write operations. The program memory address

generation unit contains a program counter, PC[19:0], and supplies the program memory address through

PA[19:0] and fetches the corresponding instruction through PD[15:0] as the result of the program memory

access. CalmRISC has a 16-level hardware stack for low power stack operations as well as a temporary storage

area.

Instruction Fetch

(IF)

Instruction Decode/

Data Memory Access

(ID/MEM)

Execution/Writeback

(EXE/WB)

Figure 1-2. CalmRISC Pipeline Diagram

CalmRISC has a 3-stage pipeline as described below:

As can be seen in the pipeline scheme, CalmRISC adopts a register-memory instruction set. In other words, data

memory where R is a GPR can be one operand of an ALU instruction as shown below:

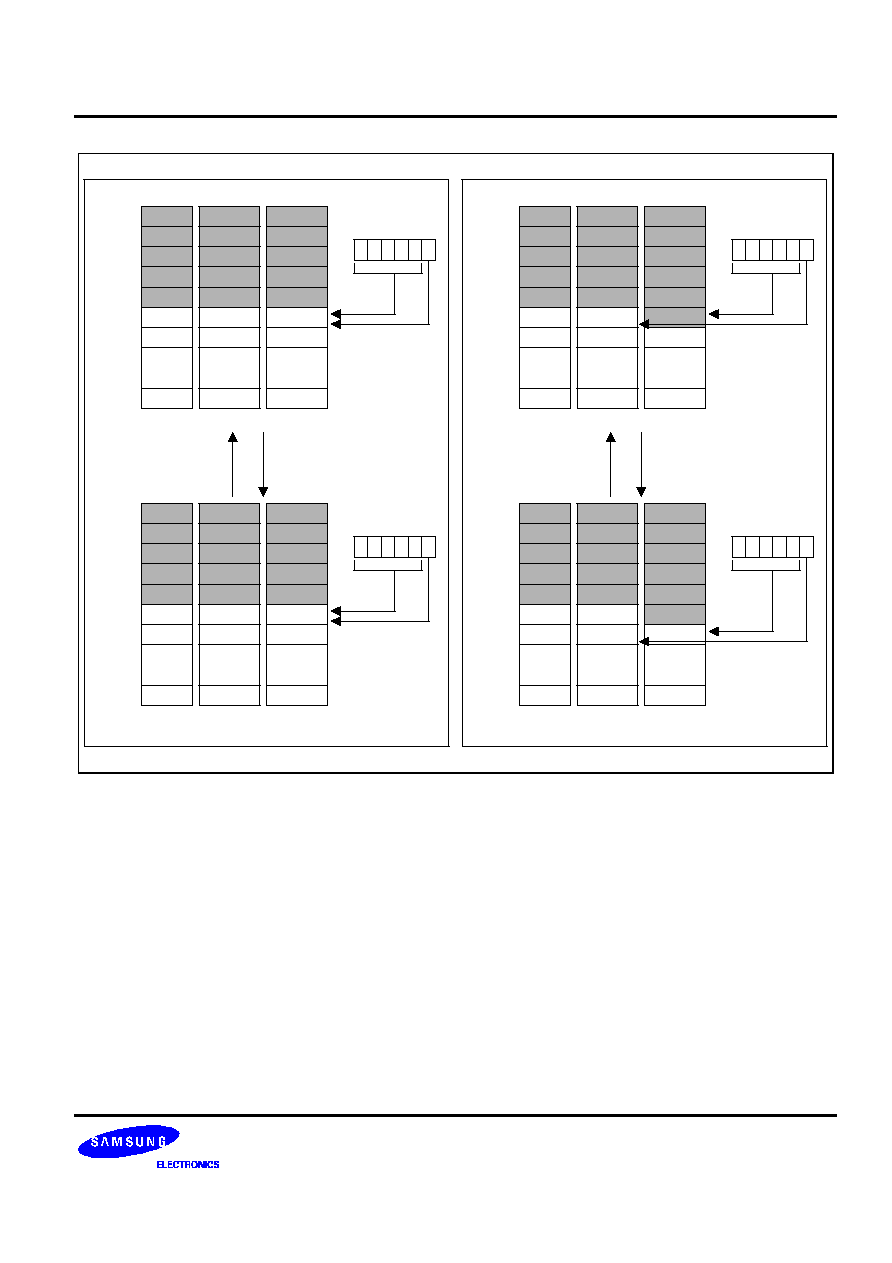

The first stage (or cycle) is the Instruction fetch stage (IF for short), where the instruction pointed by the program

counter, PC[19:0] , is read into the Instruction Register (IR for short). The second stage is the Instruction Decode

and Data Memory Access stage (ID/MEM for short), where the fetched instruction (stored in IR) is decoded and

data memory access is performed, if necessary. The final stage is the Execute and Write-back stage (EXE/WB),

where the required ALU operation is executed and the result is written back into the destination registers.

Since CalmRISC instructions are pipelined, the next instruction fetch is not postponed until the current instruction

is completely finished but is performed immediately after completing the current instruction fetch. The pipeline

stream of instructions is illustrated in the following diagram.

PRODUCT OVERVIEW

S3CK225/FK225

1-4

EXE/WB

IF

IF

IF

IF

IF

IF

IF

ID/MEM

ID/MEM

ID/MEM

ID/MEM

ID/MEM

ID/MEM

EXE/WB

EXE/WB

EXE/WB

EXE/WB

EXE/WB

/ 1

/ 2

/ 3

/ 4

/ 6

/ 5

Figure 1-3. CalmRISC Pipeline Stream Diagram

Most CalmRISC instructions are 1-word instructions, while same branch instructions such as long "call" and "jp"

instructions are 2-word instructions. In Figure 1-3, the instruction, I4, is a long branch instruction, and it takes two

clock cycles to fetch the instruction. As indicated in the pipeline stream, the number of clocks per instruction

(CPI) is 1 except for long branches, which take 2 clock cycles per instruction.

S3CK225/FK225

PRODUCT OVERVIEW

1-5

FEATURES

CPU

�

CalmRISC core (8-bit RISC architecture)

Memory

�

ROM: 8K-word (16K-byte)

�

RAM: 384-byte (excluding LCD data RAM)

Stack

�

Size: maximum 16 word-level

48 I/O Pins

�

12 normal I/O pins

�

36 I/O pins sharing with LCD signals

Basic Timer

�

Overflow signal makes a system reset

�

Watchdog function

16-bit Timer/Counter 0

�

Programmable 16-bit timer

�

Interval, capture, PWM mode

�

Match, overflow interrupt

16-bit Timer/Counter 1

�

Programmable 16-bit timer

�

Match interrupt generator

8-bit Timer/Counter 2

�

Programmable 8-bit timer

�

Interval, PWM mode

�

Match, overflow interrupt

8-bit Timer/Counter 3

�

Programmable 8-bit timer

�

Match interrupt/carrier frequency generator

Watch Timer

�

Real-time and interval time measurement

�

Clock generation for LCD

�

Four frequency outputs for buzzer sound

(0.5/1/2/4 kHz at 32.768 kHz)

LCD Controller/Driver

�

32 segments and 4 common terminals

�

Static, 1/2 duty, 1/3 duty, 1/4 duty

�

Internal resistor circuit for LCD bias

8-Bit Serial I/O Interface

�

8-bit transmit/receive mode

�

8-bit receive mode

�

LSB-first/MSB-first transmission selectable

�

Internal/external clock source

A/D Converter

�

Eight analog input channels

�

25

�

s conversion speed at 8 MHz

�

10-bit conversion resolution

�

Operating voltage: 2.7 V to 5.5 V

D/A Converter

�

One analog output channel

�

10-bit conversion resolution (R-2R)

�

Operating voltage: 2.7 V to 5.5 V

Oscillation Sources

�

Crystal, ceramic, RC for main clock

�

Crystal for sub clock

�

Main clock frequency: 0.4�8 MHz

�

Sub clock frequency: 32.768 kHz

�

CPU clock divider circuit

(divided by 1, 2, 4, 8, 16, 32, 64 or 128)

PRODUCT OVERVIEW

S3CK225/FK225

1-6

FEATURES (Continued)

Two Power-Down Modes

�

Idle (only CPU clock stops)

�

Stop (System clock stops)

Interrupts

�

2 Vectors, 13 interrupts

Instruction Execution Times

�

125 ns at 8 MHz (main clock)

�

30.5

�

s at 32.768 kHz (sub clock)

Operating Temperature Range

�

- 25

�

C to 85

�

C

Operating Voltage Range

�

2.0 V to 5.5 V at 2 MHz (2MIPS)

�

2.4 V to 5.5 V at 4 MHz (4MIPS)

�

3.0 V to 5.5 V at 8 MHz (8MIPS)

Two Amplifiers

�

Microphone and filter

Package Type

�

64-pin QFP-1420F

S3CK225/FK225

PRODUCT OVERVIEW

1-7

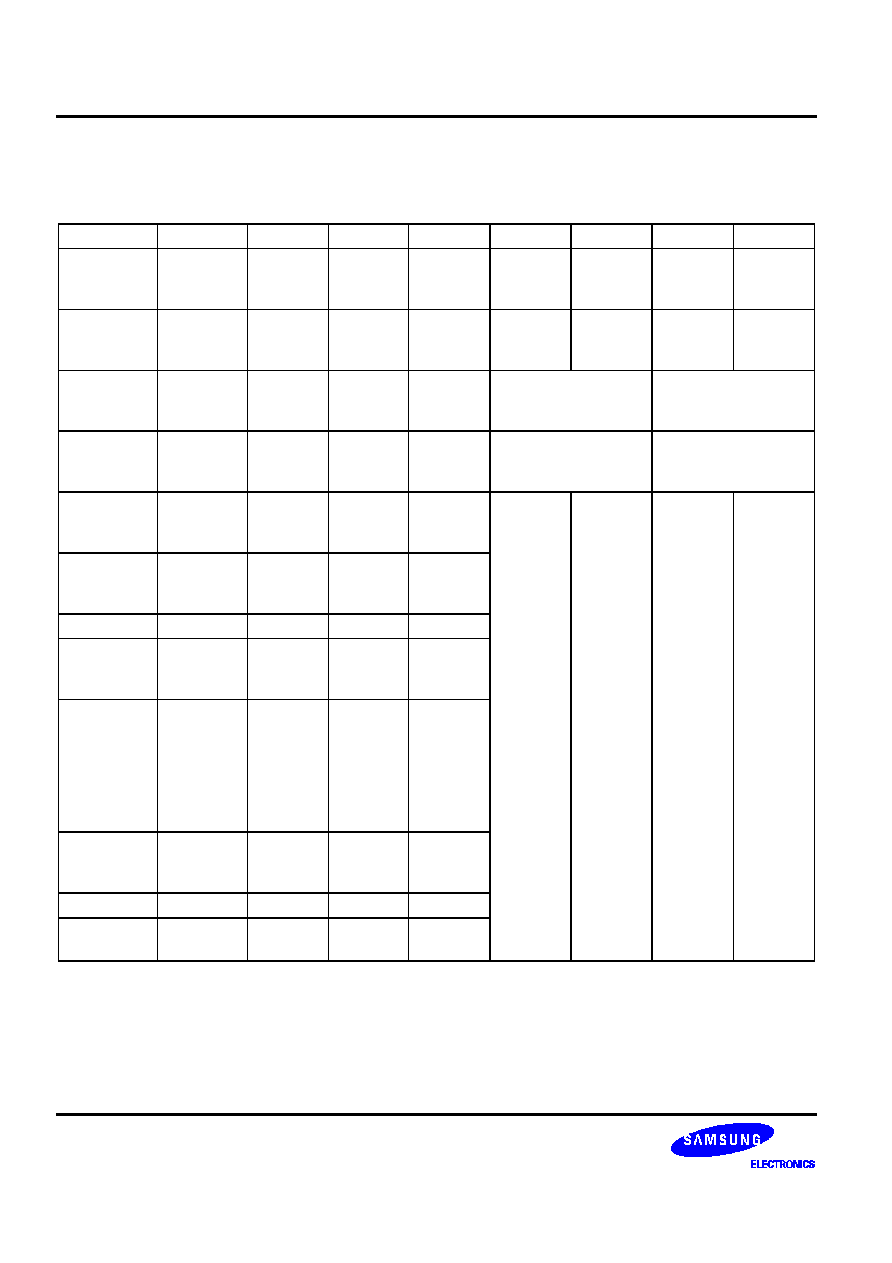

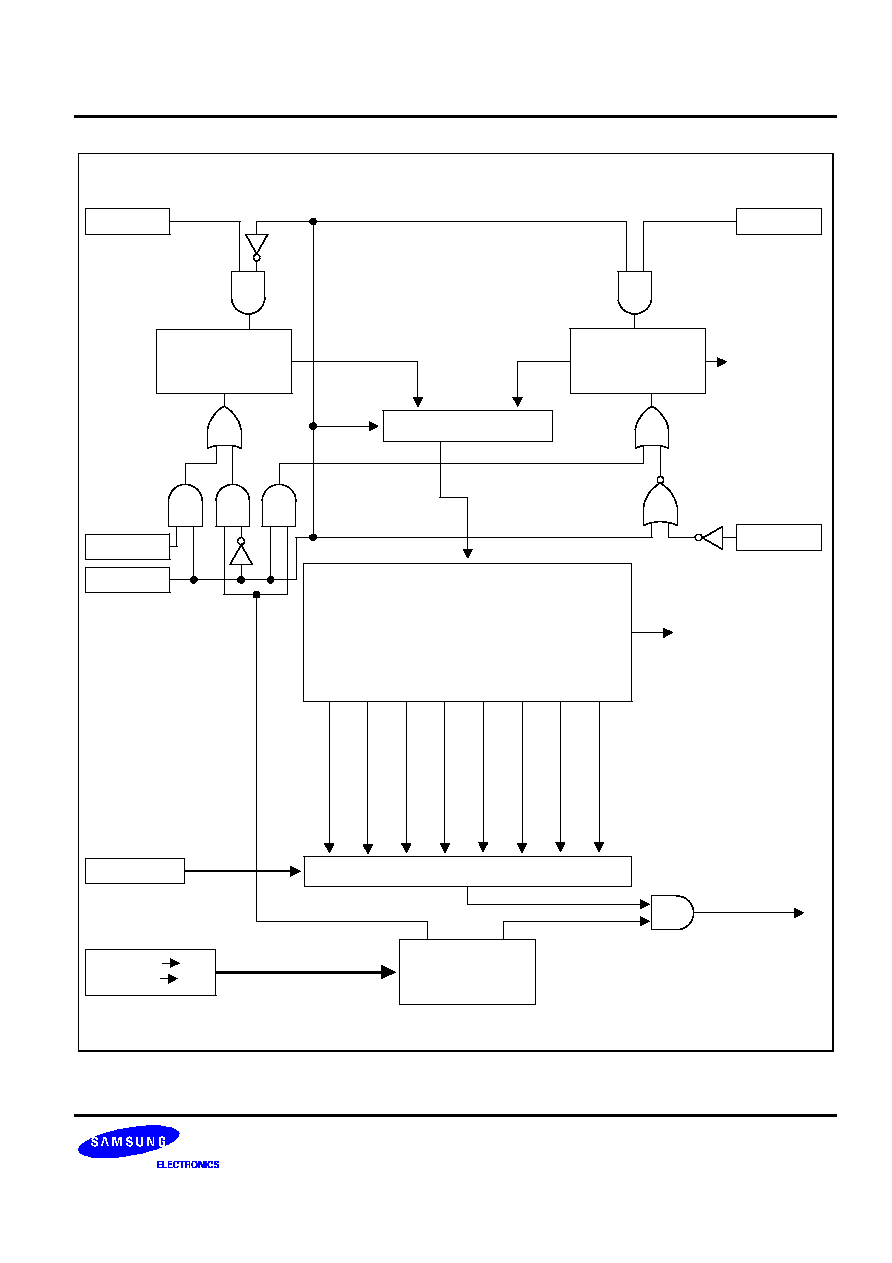

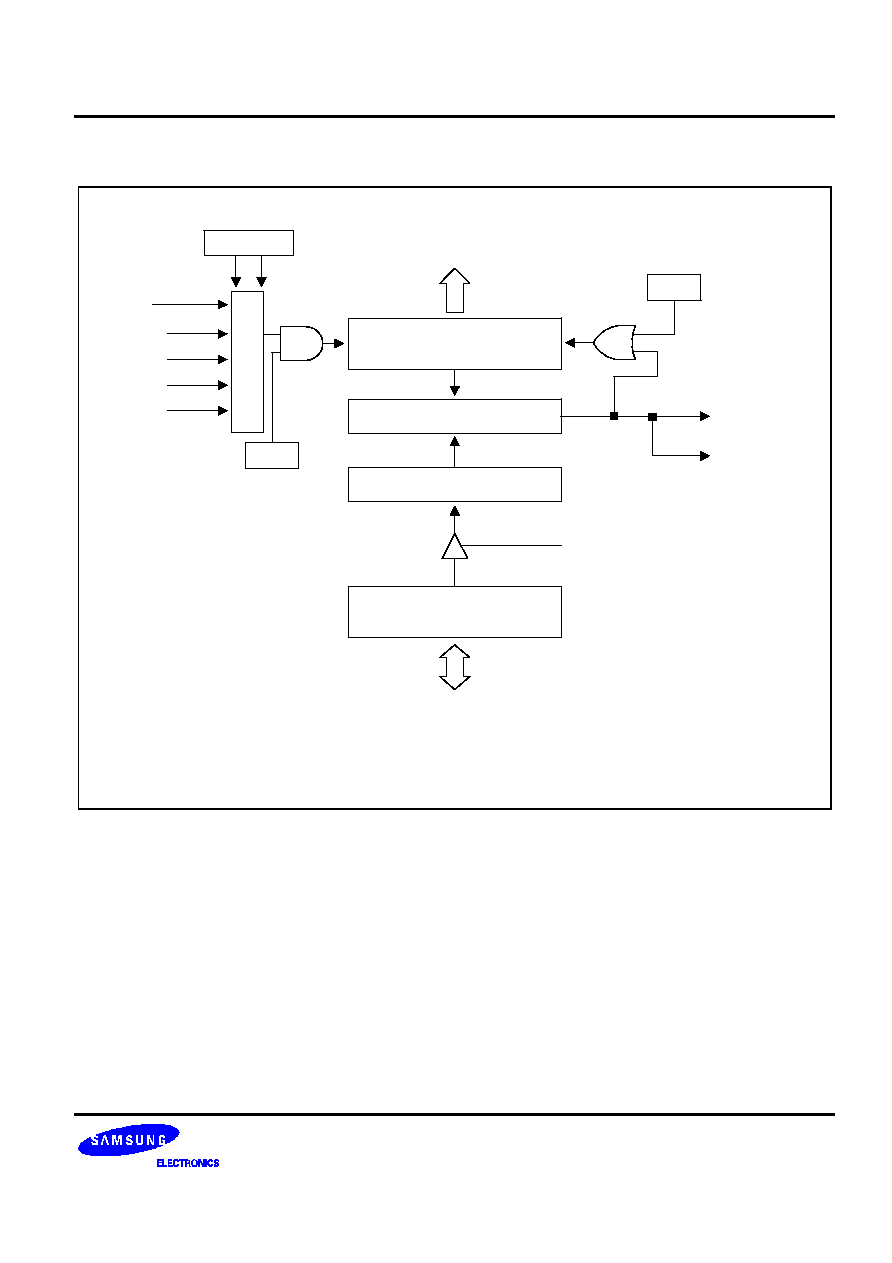

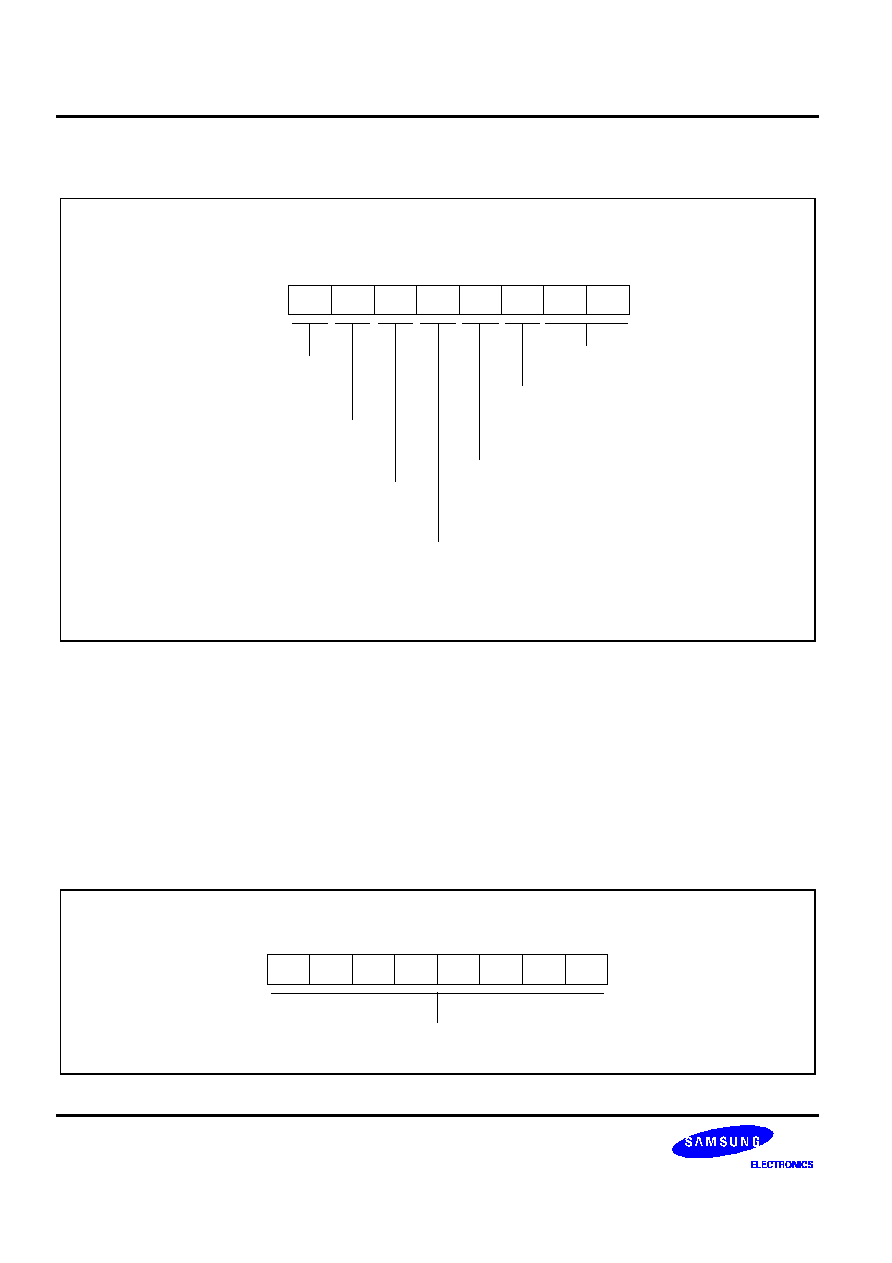

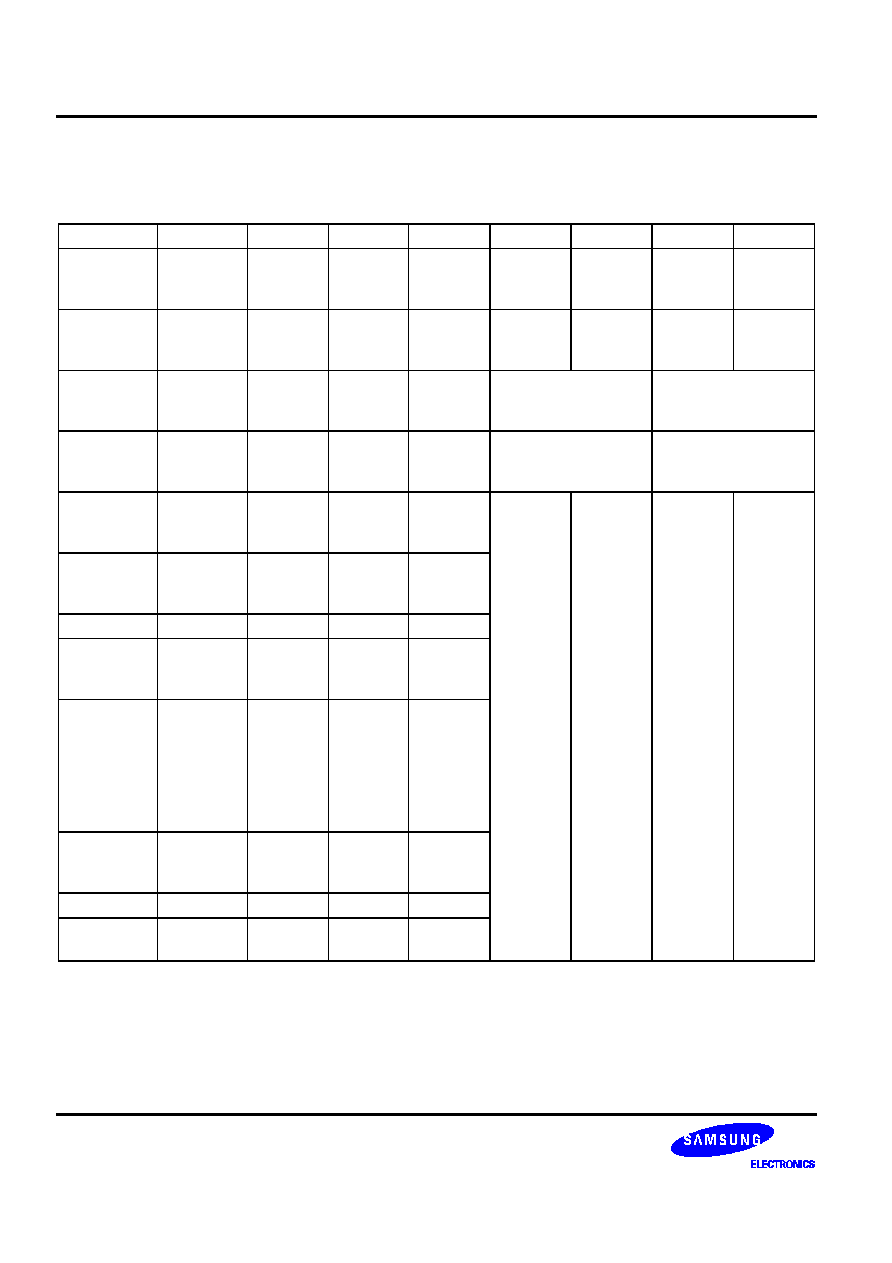

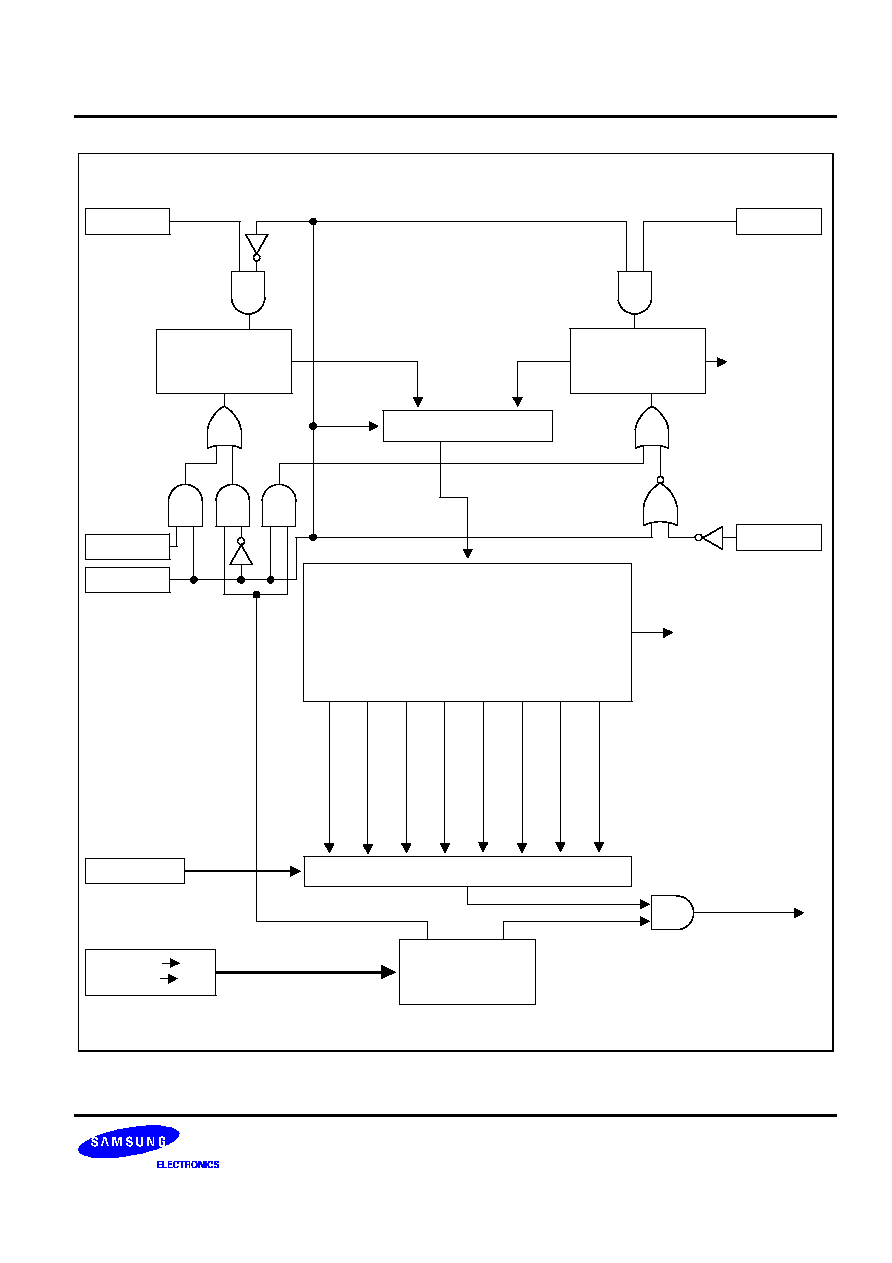

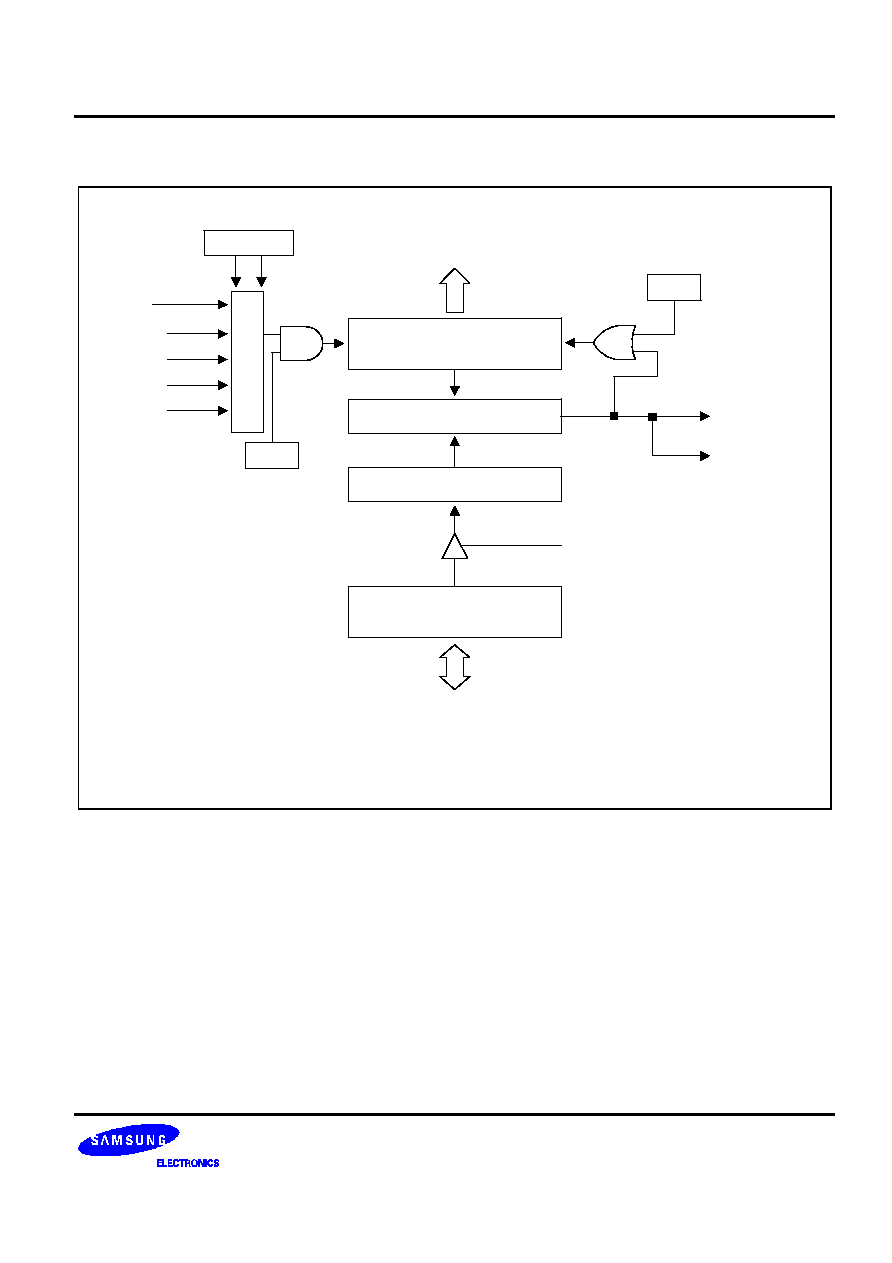

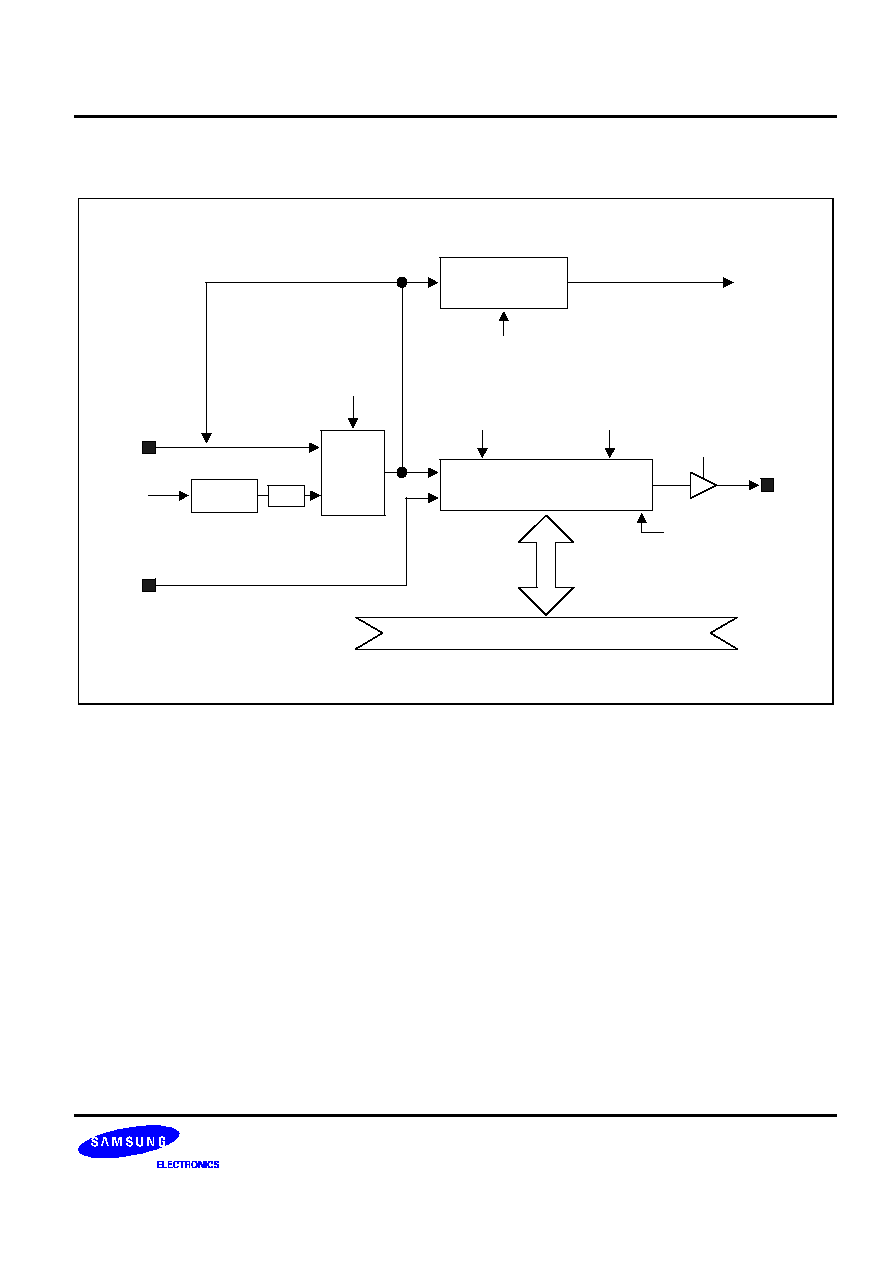

BLOCK DIAGRAM

RESET

OSC,

Reset

16-Bit Timer/

Counter 0

10-Bit A/D

Converter

P0.0-P0.3/

INT0-INT3

I/O Port 1

X

IN

, XT

IN

16-Bit Timer/

Counter 1

8-Bit Timer/

Counter 2

8-Bit Timer/

Counter 3

I/O Port 0

I/O Port 5

I/O Port 7

T0OUT/T0PWM/P7.1

T0CLK/P7.2

T0CAP/P7.3

T3PWM/P7.2

P1.0/BUZ

P1.1/SO

P1.2/SCK

P1.3/SI

AV

REF

AV

SS

P5.0-P5.7/AD0-AD7/

SEG24-SEG31

P7.0/T2OUT/T2PWM

P7.1/T2CLK/T0OUT/T0PWM

P7.2/T0CLK/T3PWM

P7.3/T0CAP/CLKOUT

DAO

Calm8 RISC CPU

384-byte

Register File

16K-byte

ROM

Basic

Timer

Watch

Timer

X

OUT

, XT

OUT

BUZ/P1.0

P4.0-P4.7/

SEG16-SEG23

T2OUT/T2PWM/P7.0

T2CLK/P7.1

10-Bit D/A

Converter

Serial

I/O Port

P6.0-P6.3/

COM0-COM3

LCD

Driver

I/O Port 2

I/O Port 3

I/O Port 4

I/O Port 6

Two

Amplifiers

I/O Port and Interrupt Control

COM0-COM3/

P6.0-P6.3

SEG0-SEG31/

P2.0-P5.7

SO/P1.1

SCK/P1.2

SI/P1.3

P2.0-P2.7/

SEG0-SEG7

P3.0-P3.7/

SEG8-SEG15

AD0-AD7/P5.0-P5.7

FILIN, MICIN

FILOUT, MICOUT, Vref

Figure 1-4. Block Diagram

PRODUCT OVERVIEW

S3CK225/FK225

1-8

PIN ASSIGNMENT

COM0/P6.0

COM1/P6.1

COM2/P6.2

COM3/P6.3

P7.0/T2OUT/T2PWM

P7.1/T2CLK/T0OUT/T0PWM

P7.2/T0CLK/T3PWM

P7.3/T0CAP/CLKOUT

V

DD

V

SS

X

OUT

X

IN

TEST

XT

IN

XT

OUT

RESET

DAO

FILIN

FILOUT

P2.0/SEG0

P2.1/SEG1

P2.2/SEG2

P2.3/SEG3

P2.4/SEG4

P2.5/SEG5

P2.6/SEG6

P2.7/SEG7

P3.0/SEG8

P3.1/SEG9

P3.2/SEG10

P3.3/SEG11

P3.4/SEG12

VREF

MICIN

MICOUT

P0.0/INT0

P0.1/INT1

P0.2/INT2

P0.3/INT3

P1.0/BUZ

P1.1/SO

P1.2/SCK

P1.3/SI

AVREF

AVSS

P3.5/SEG13

P3.6/SEG14

P3.7/SEG15

P4.0/SEG16

P4.1/SEG17

P4.2/SEG18

P4.3/SEG19

P4.4/SEG20

P4.5/SEG21

P4.6/SEG22

P4.7/SEG23

P5.0/SEG24/AD0

P5.1/SEG25/AD1

P5.2/SEG26/AD2

P5.3/SEG27/AD3

P5.4/SEG28/AD4

P5.5/SEG29/AD5

P5.6/SEG30/AD6

P5.7/SEG31/AD7

S3CK225/FK225

(64-QFP-1420F)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

20

21

22

23

24

25

26

27

28

29

30

31

32

64

63

62

61

60

59

58

57

56

55

54

53

52

Figure 1-5. Pin Assignment (64-QFP)

S3CK225/FK225

PRODUCT OVERVIEW

1-9

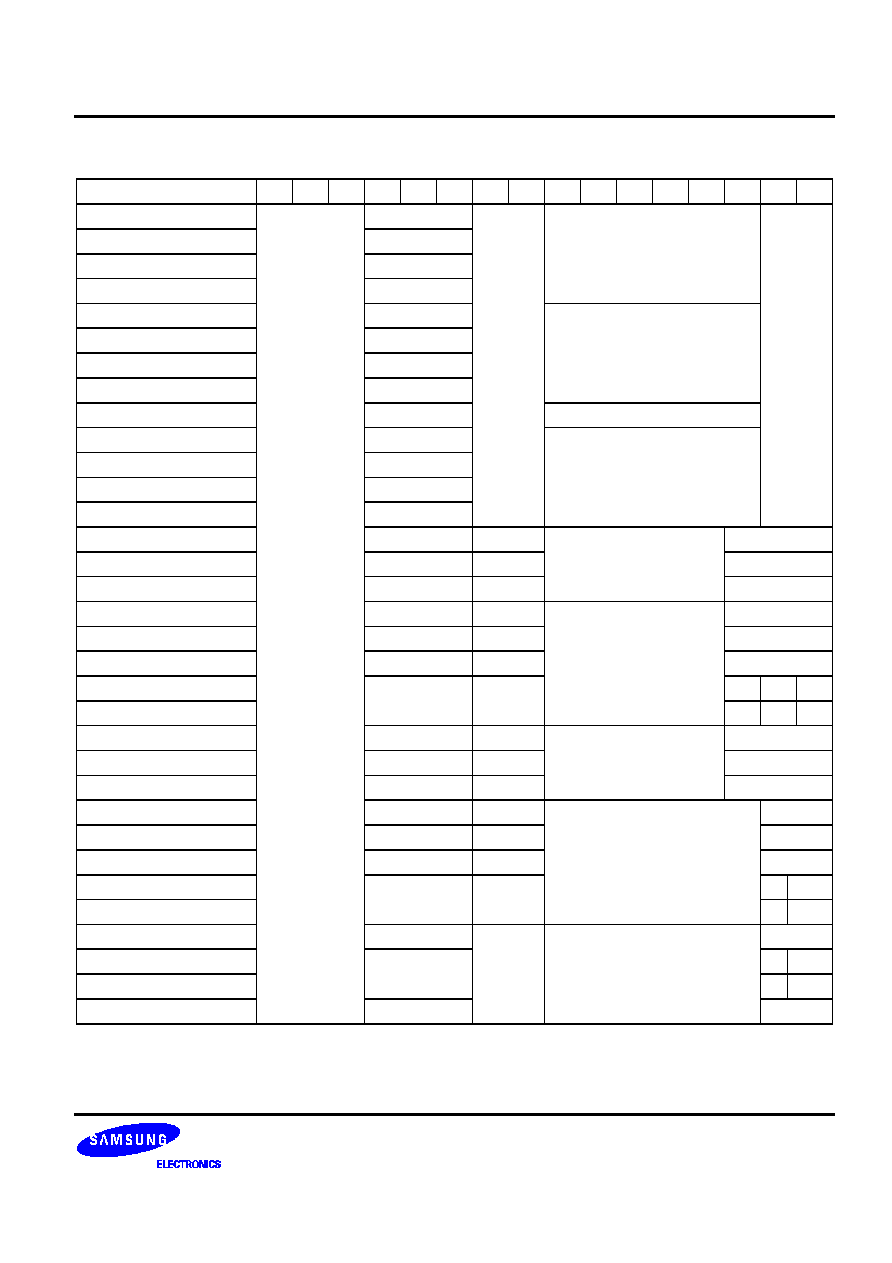

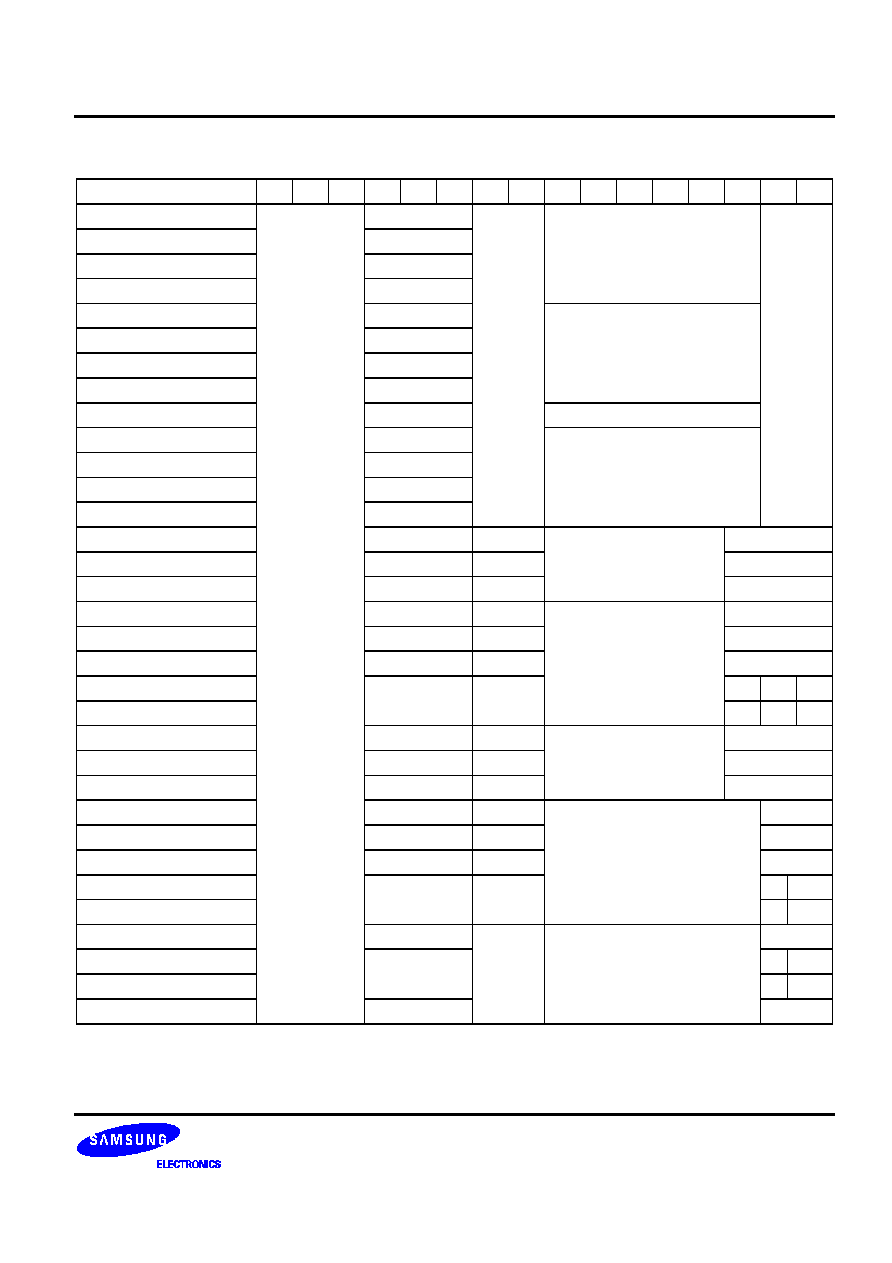

PIN DESCRIPTIONS

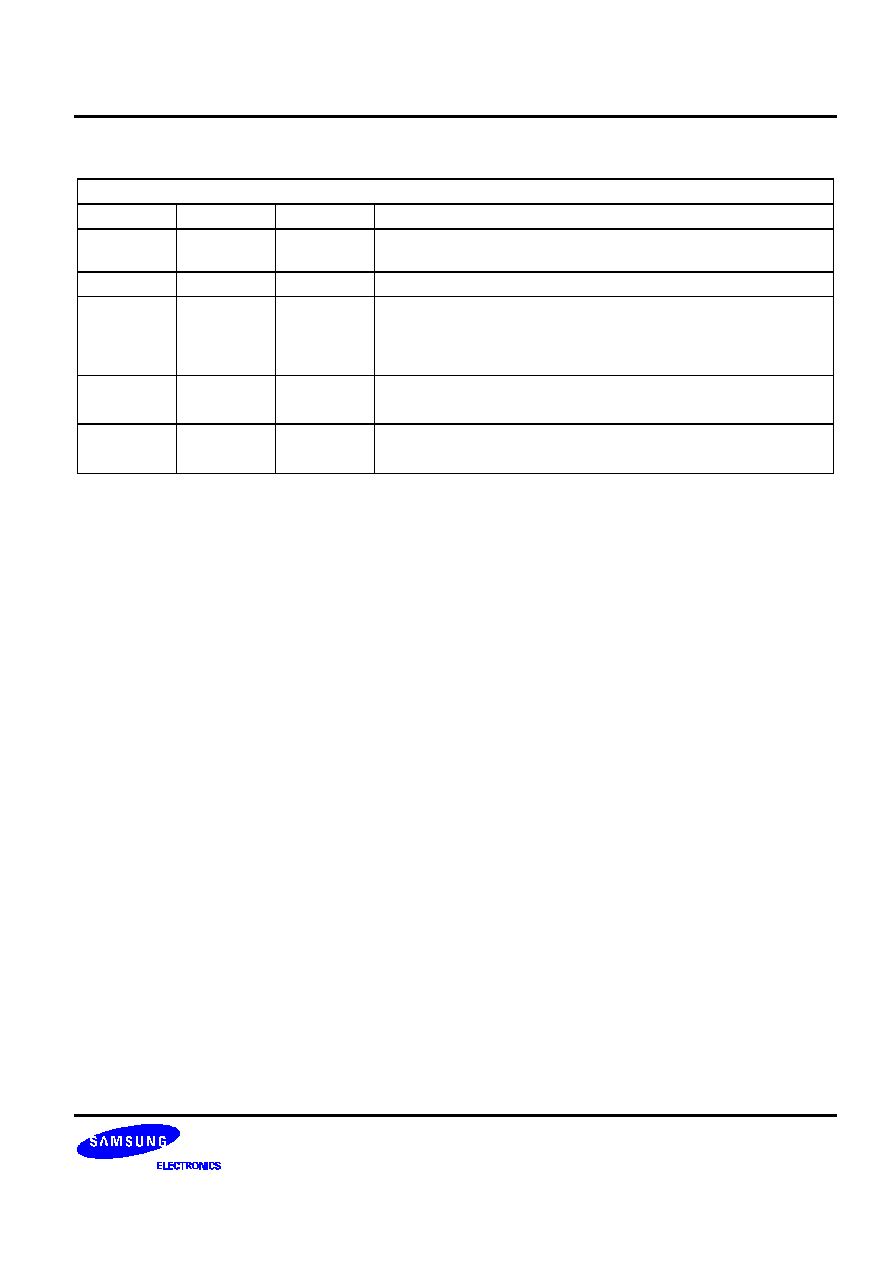

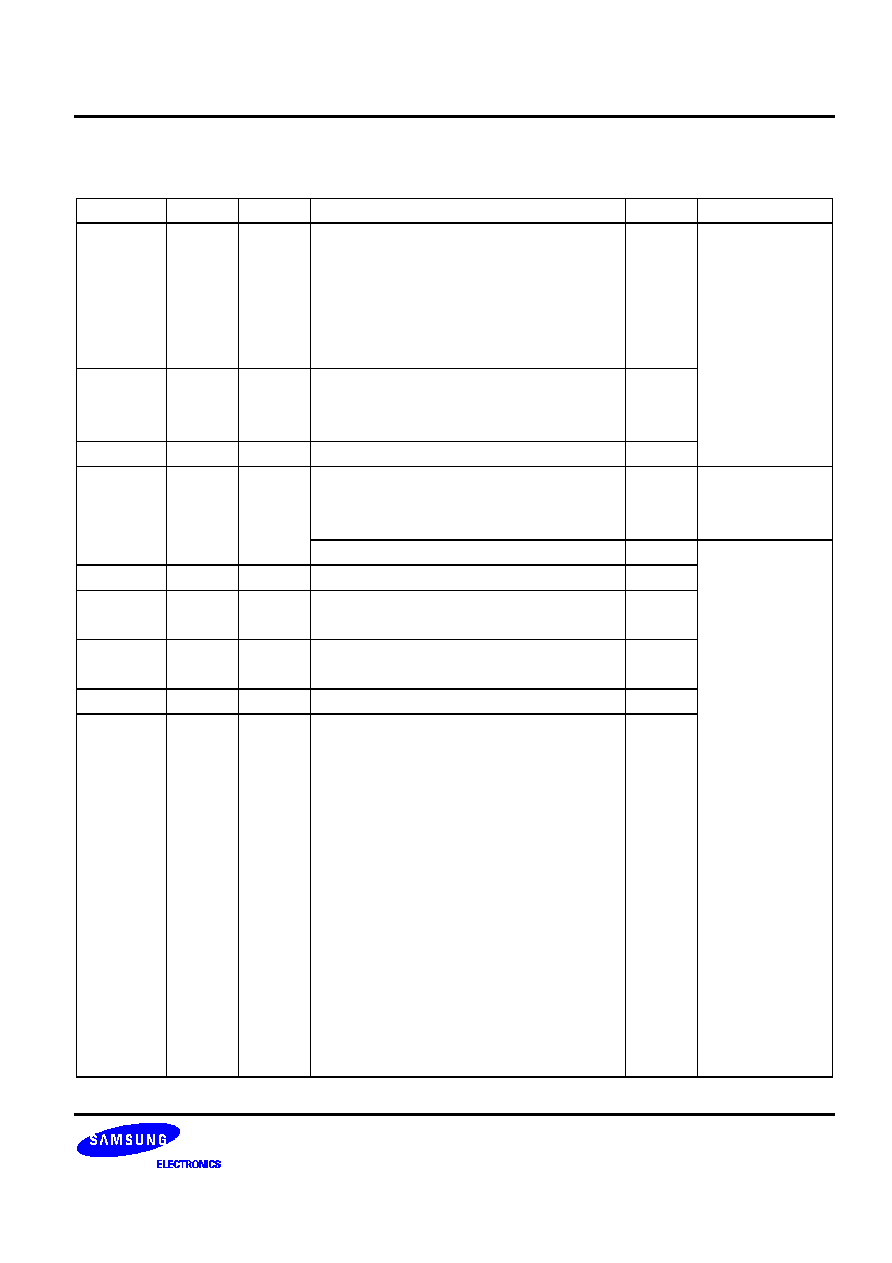

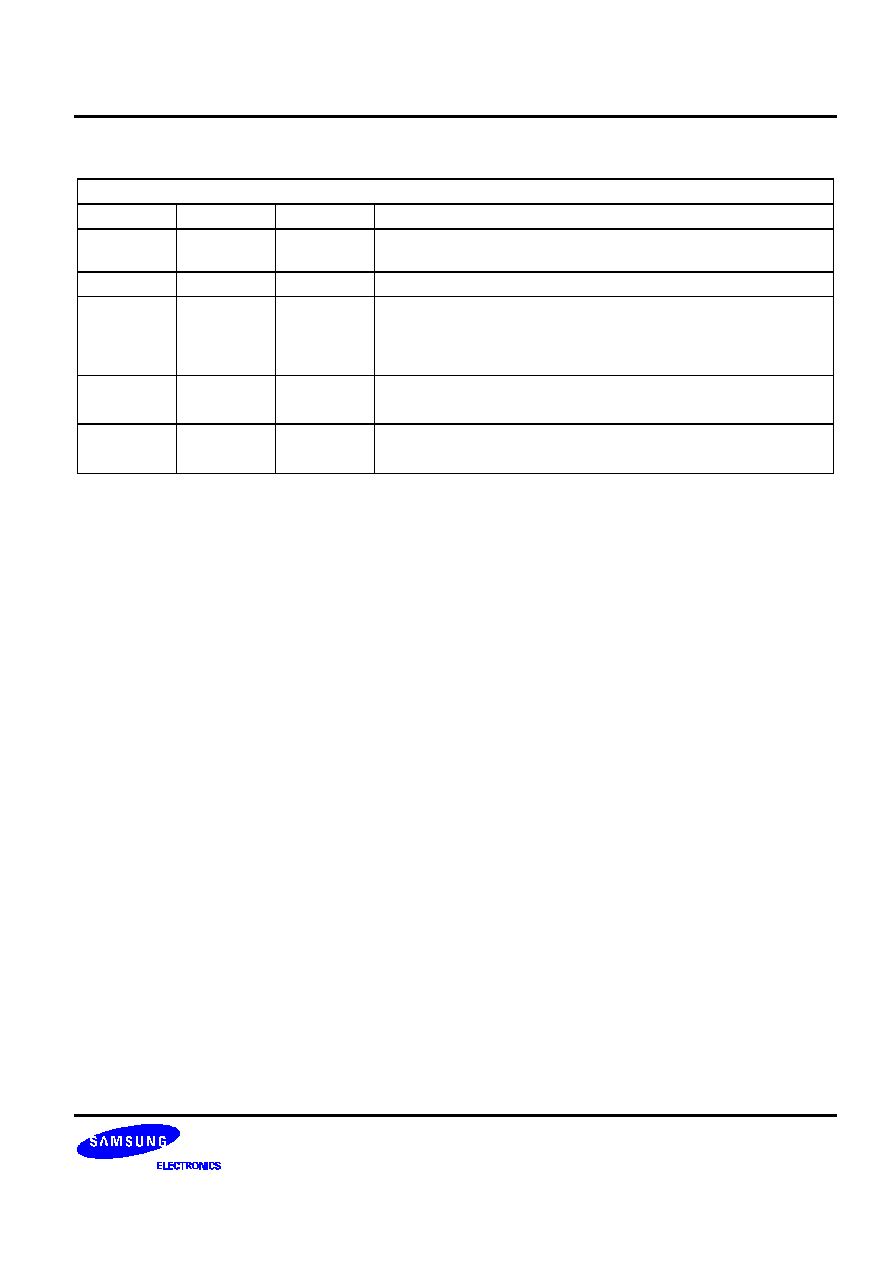

Table 1-1. Pin Descriptions

Pin

Names

Pin

Type

Pin

Description

Circuit

Type

Pin

Numbers

Share

Pins

P0.0

P0.1

P0.2

P0.3

I/O

I/O port with bit programmable pins;

Schmitt trigger input or output mode

selected by software; software

assignable pull-up resistors.

(with noise filter and interrupt control).

D-4

23

24

25

26

INT0

INT1

INT2

INT3

P1.0

P1.1

P1.2

P1.3

I/O

I/O port with bit programmable pins;

Schmitt trigger input or output mode

selected by software; Open-drain output

mode can be selected by software;

software assignable pull-up resistors.

E-4

27

28

29

30

BUZ

SO

SCK

SI

P2.0-P2.7

I/O

I/O port with bit programmable pins;

Push-pull or open-drain output and input

with software assignable pull-up resistors.

H-14

64-57

SEG0-SEG7

P3.0-P3.7

I/O

Have the same characteristic as port 2

H-14

56-49

SEG8-SEG15

P4.0-P4.7

I/O

Have the same characteristic as port 2

H-14

48-41

SEG16-SEG23

P5.0-P5.7

I/O

I/O port with bit programmable pins;

Normal input or output mode selected by

software; software assignable pull-up

resistors.

F-10

40-33

AD0-AD7/

SEG24-SEG31

P6.0-P6.3

I/O

Have the same characteristic as port 2

H-14

1-4

COM0-COM3

P7.0

P7.1

P7.2

P7.3

I/O

I/O port with bit programmable pins;

Schmitt trigger input or push-pull output

with software assignable pull-up resistors.

D-3

5

6

7

8

T2OUT/T2PWM

T2CLK/T0OUT/T0PWM

T0CLK/T3PWM

T0CAP/CLKOUT

AD0-AD7

I/O

A/D converter analog input channels

F-10

40-33

P5.0-P5.7/

SEG24-SEG31

AV

REF

�

A/D converter reference voltage

�

31

�

AV

SS

�

A/D converter ground

�

32

�

INT0-INT3

I/O

External interrupt input pins

D-4

23-26

P0.0-P0.3

RESET

I

System reset pin

B

16

�

TEST

I

Test signal input

(must be connected to V

SS

)

�

13

�

PRODUCT OVERVIEW

S3CK225/FK225

1-10

Table 1-1. Pin Descriptions (Continued)

Pin

Names

Pin

Type

Pin

Description

Circuit

Type

Pin

Numbers

Share

Pins

V

DD

, V

SS

�

Main power supply and ground

�

9, 10

�

X

OUT

, X

IN

�

Main oscillator pins

�

11, 12

�

XT

OUT

, XT

IN

�

Sub oscillator pins

�

15, 14

�

SO, SCK, SI

I/O

Serial I/O interface clock signal

E-4

28-30

P1.1-P1.3

T3PWM

I/O

Timer 3 PWM output

D-3

7

P7.2

T2OUT/T2PWM

I/O

Timer 2 output and PWM output

D-3

5

P7.0

T2CLK

I/O

Timer 2 external clock input

D-3

6

P7.1

T0CLK

I/O

Timer 0 external clock input

D-3

7

P7.2

T0CAP

I/O

Timer 0 capture input

D-3

8

P7.3

T0OUT/T0PWM

I/O

Timer 0 output and PWM output

D-3

6

P7.1

COM0-COM3

I/O

LCD common signal output

H-14

1-4

P6.0-P6.3

SEG0-SEG7

I/O

LCD segment output

H-14

64-57

P2.0-P2.7

SEG8-SEG15

I/O

LCD segment output

H-14

56-49

P3.0-P3.7

SEG16-SEG23

I/O

LCD segment output

H-14

48-41

P4.0-P4.7

SEG24-SEG31

I/O

LCD segment output

H-14

40-33

P5.0-P5.7/

AD0-AD7

BUZ

I/O

0.5, 1, 2 or 4 kHz frequency output for

buzzer sound with 4.19 MHz main clock

or 32768 Hz sub clock

E-4

27

P1.0

CLKOUT

I/O

Main oscillator clock output

D-3

8

P7.3

DAO

�

DA converter output

�

17

�

FILIN, FILOUT

�

Filter amp input and output

�

18, 19

�

MICIN, MICOUT

�

MIC amp input and output

�

21, 22

�

Vref

�

Reference voltage output for filter amp

and MIC amp

�

20

�

S3CK225/FK225

PRODUCT OVERVIEW

1-11

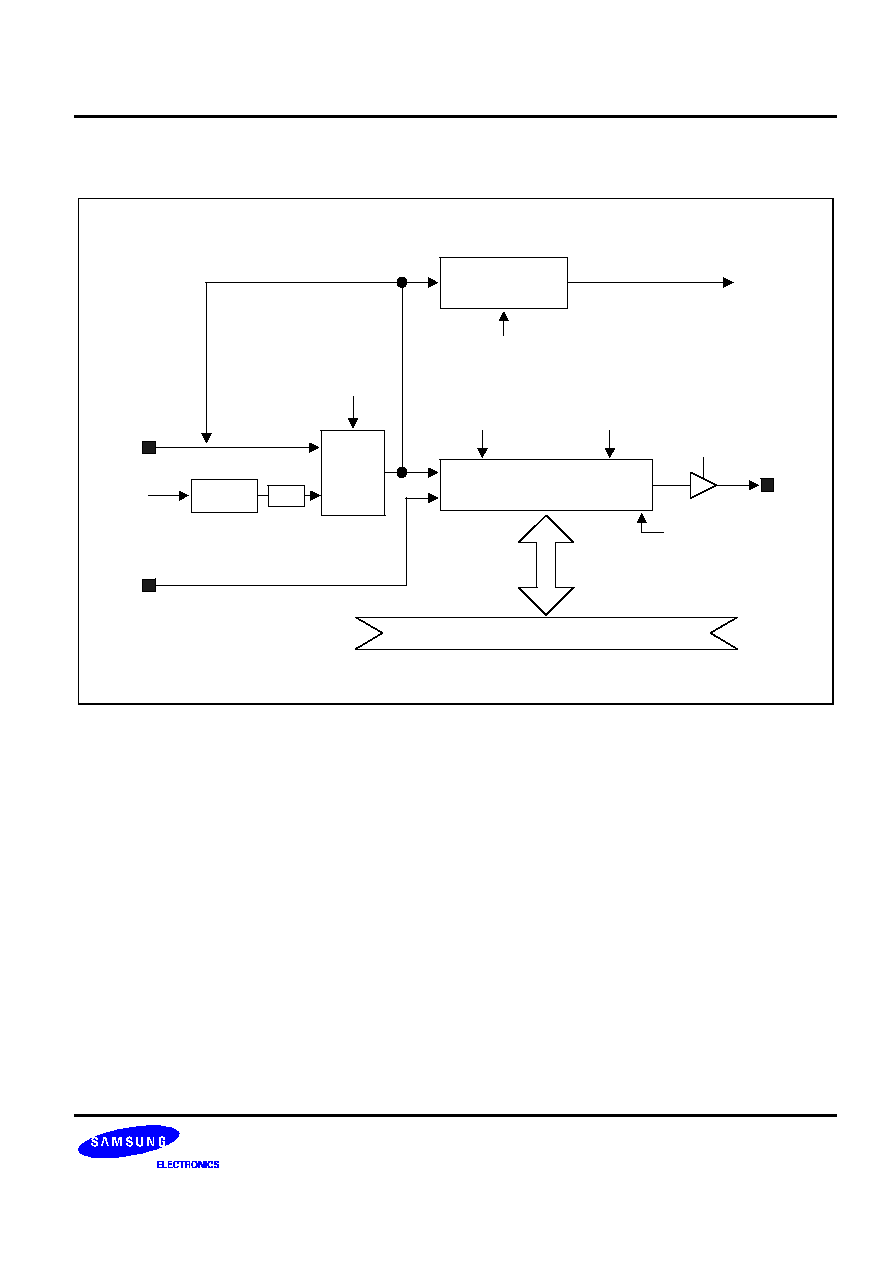

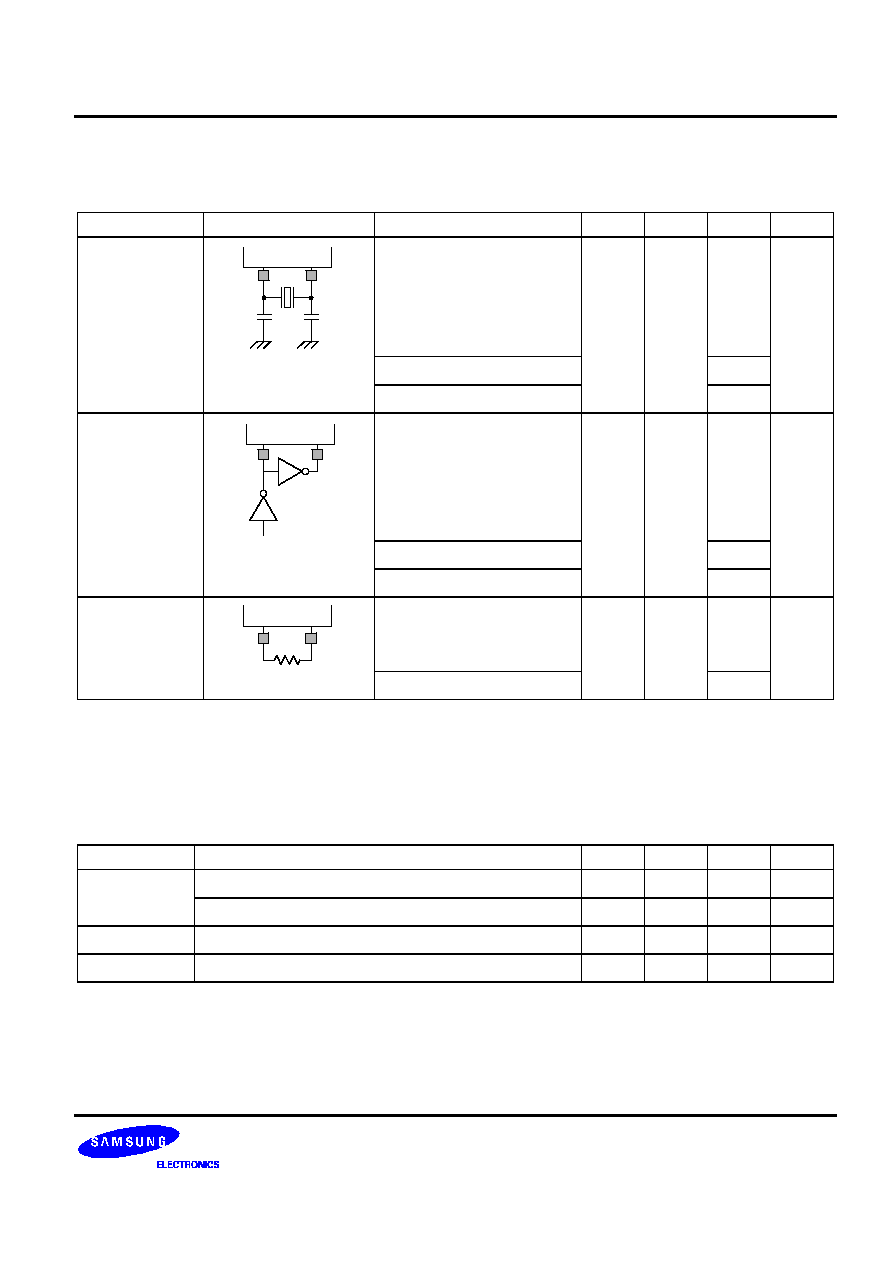

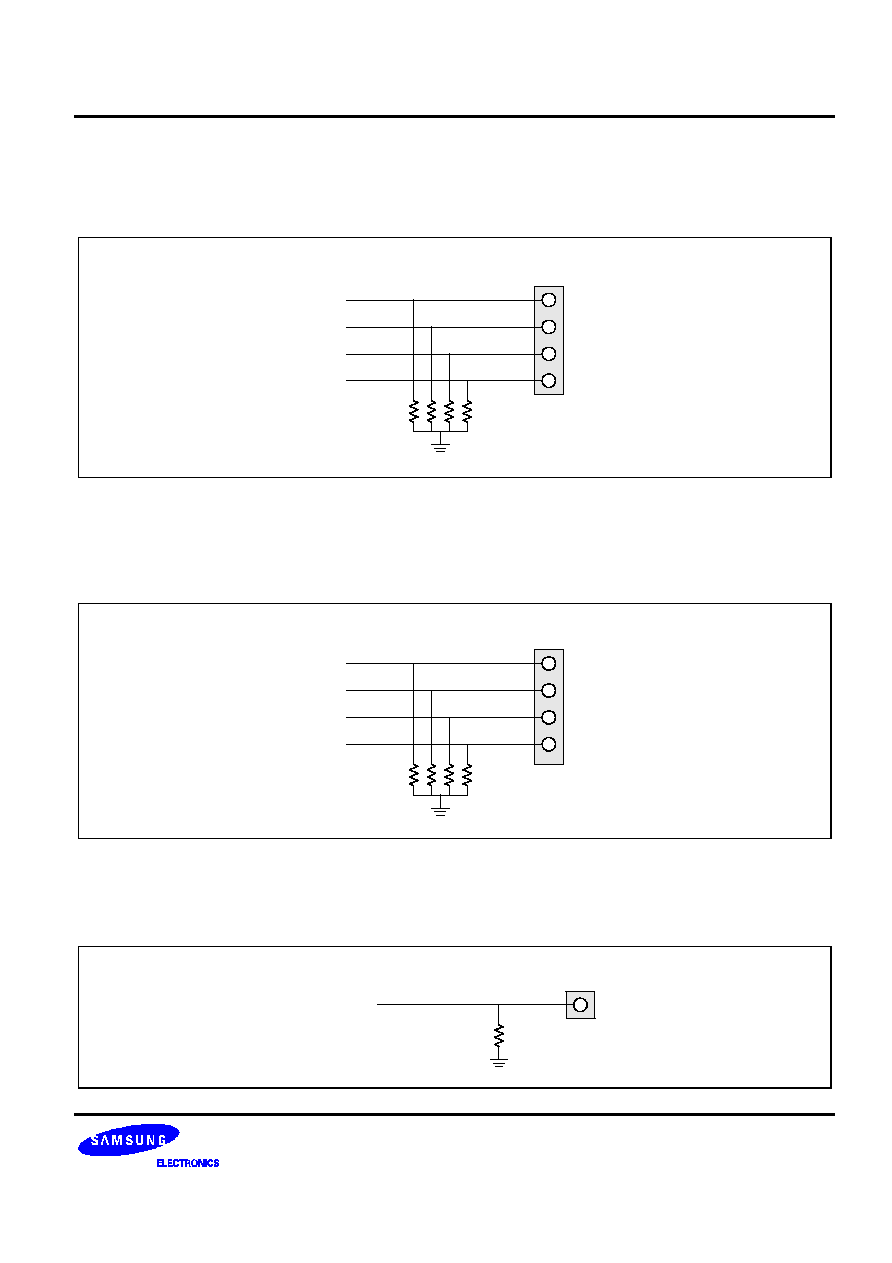

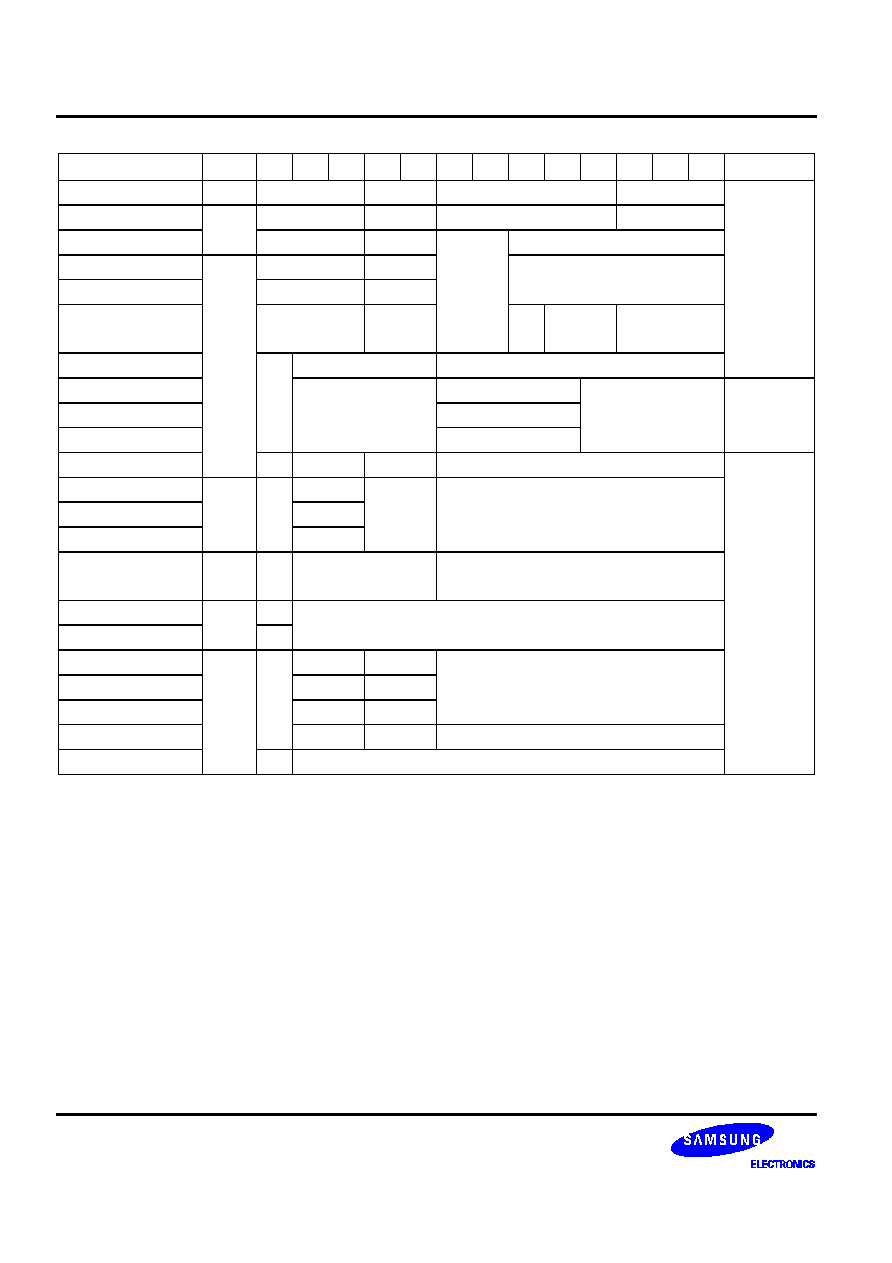

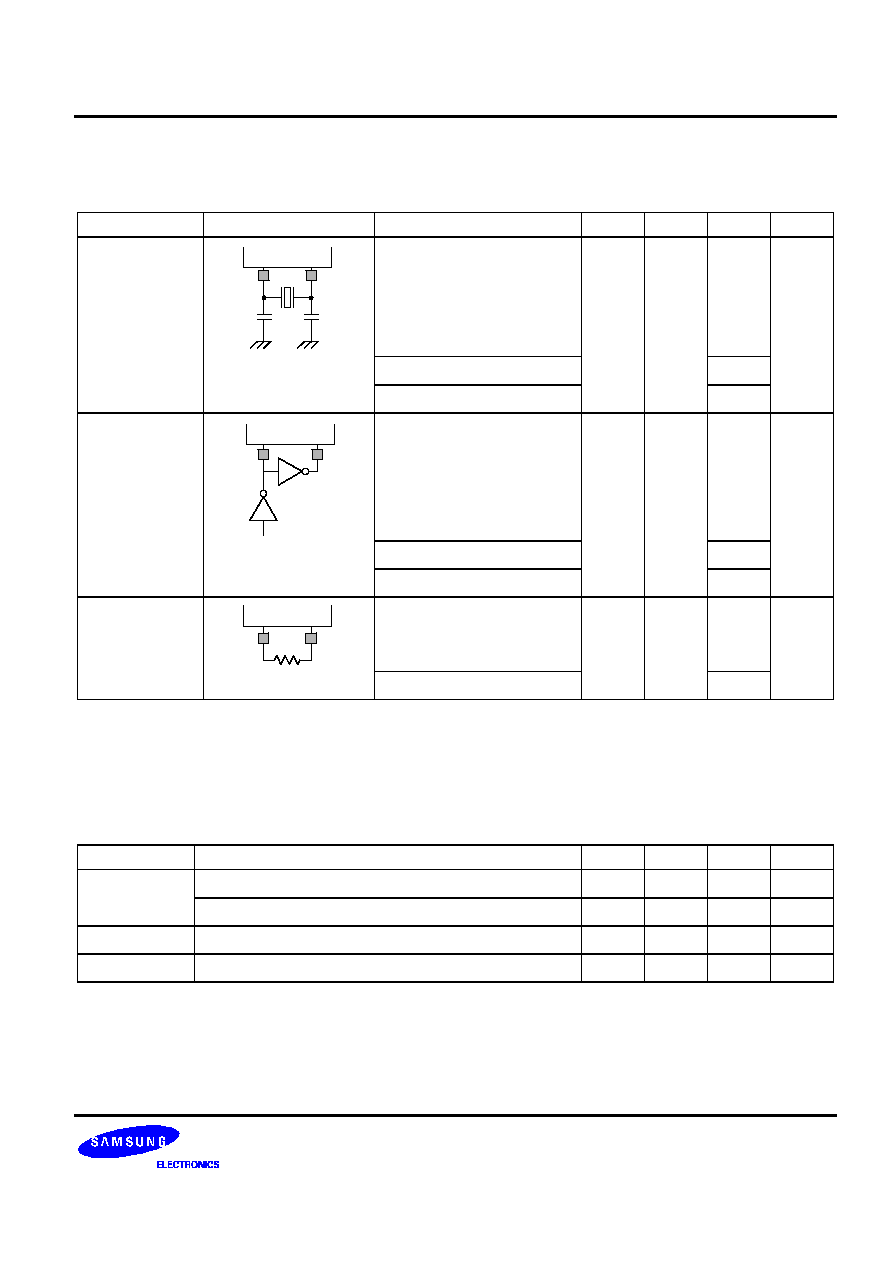

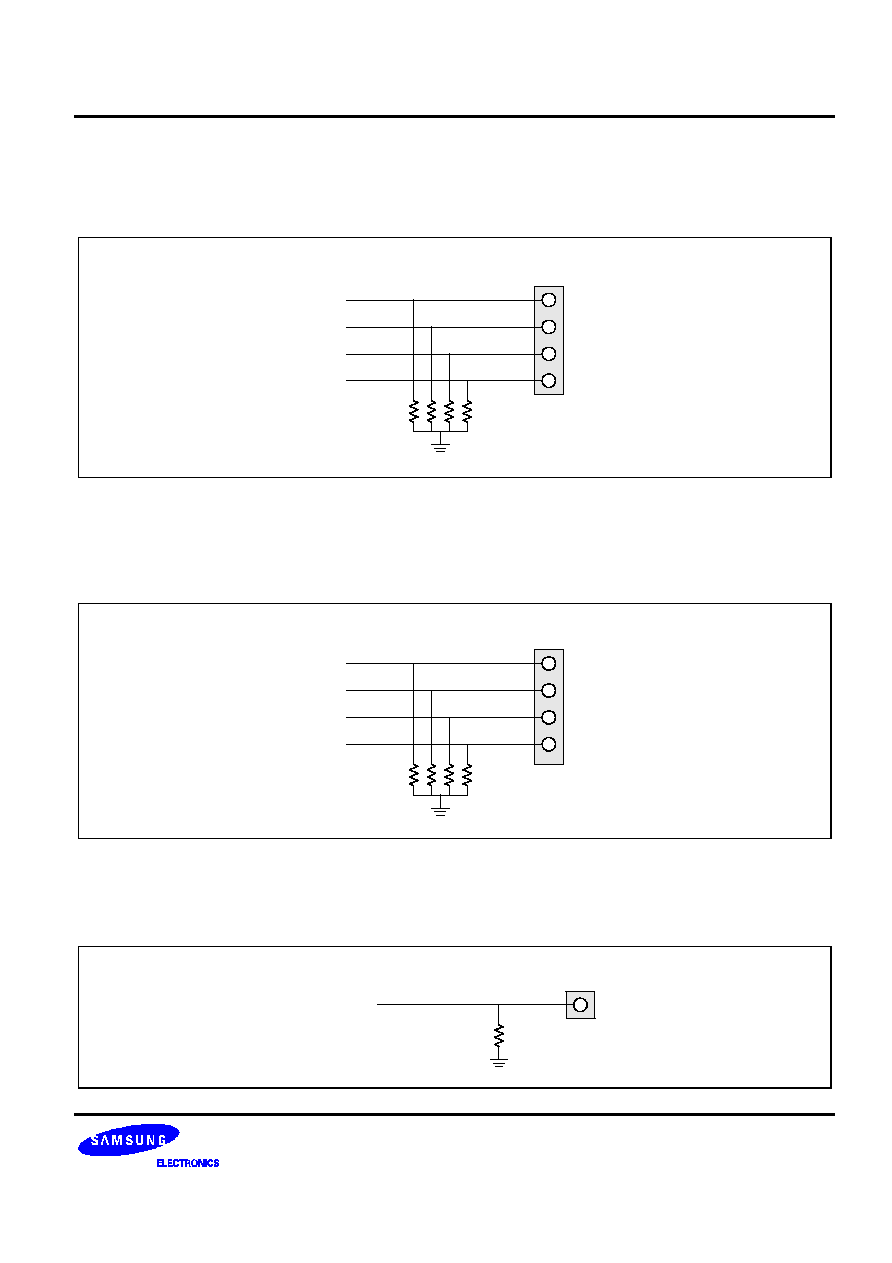

PIN CIRCUITS

In

V

DD

Figure 1-6. Pin Circuit Type B (

RESET

RESET

)

I/O

Output

Disable

Data

Circuit

Type C

Pull-up

Enable

V

DD

P-Channel

Figure 1-7. Pin Circuit Type D-3 (P7)

P-CH

N-CH

V

DD

Out

Output

Disable

Data

Figure 1-8. Pin Circuit Type C

I/O

Output

Disable

Data

Circuit

Type C

Pull-up

Enable

V

DD

Noise

Filter

Ext. INT

Input

Normal

Figure 1-9. Pin Circuit Type D-4 (P0)

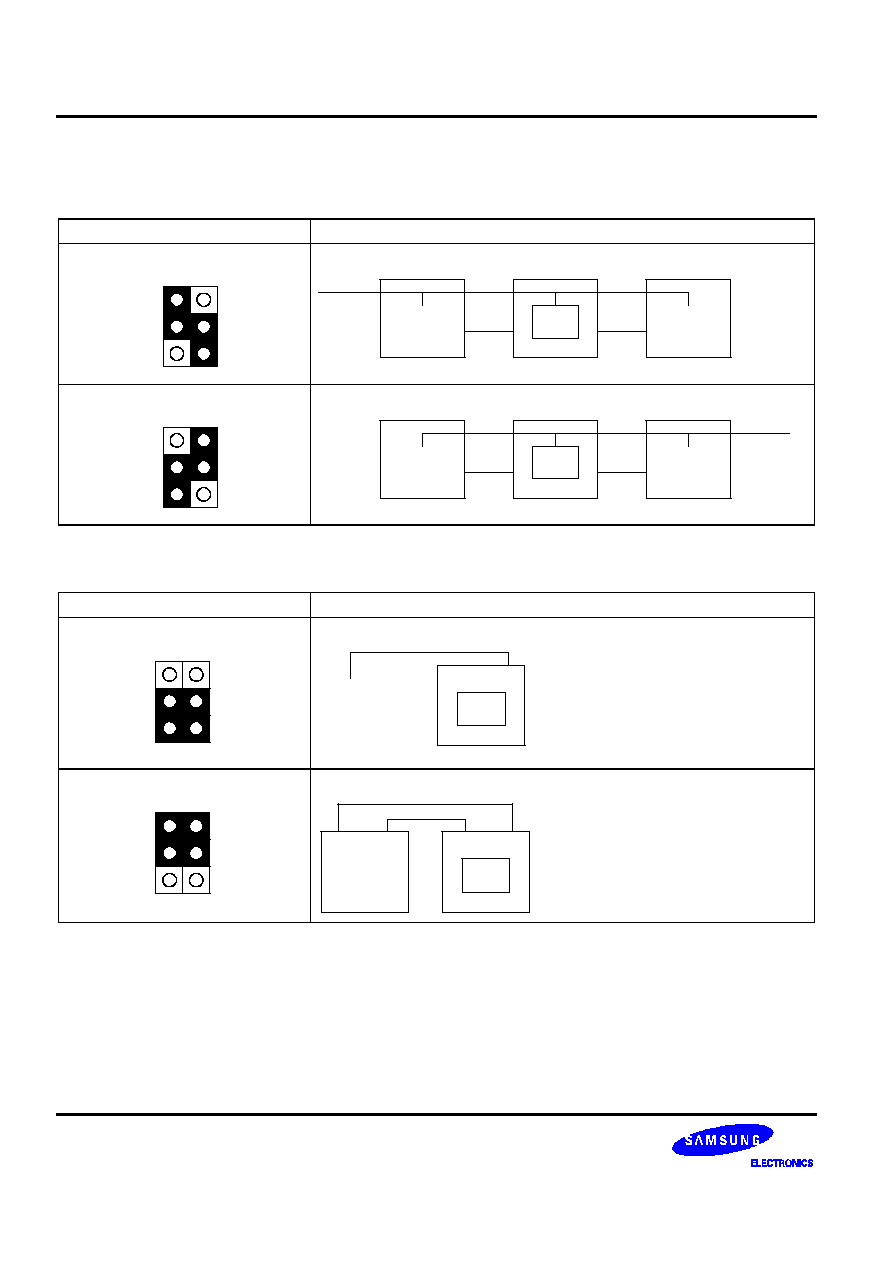

PRODUCT OVERVIEW

S3CK225/FK225

1-12

V

DD

Output

Disable

Data

Pull-up

Resistor

V

DD

I/O

P-CH

N-CH

Open drain

Enable

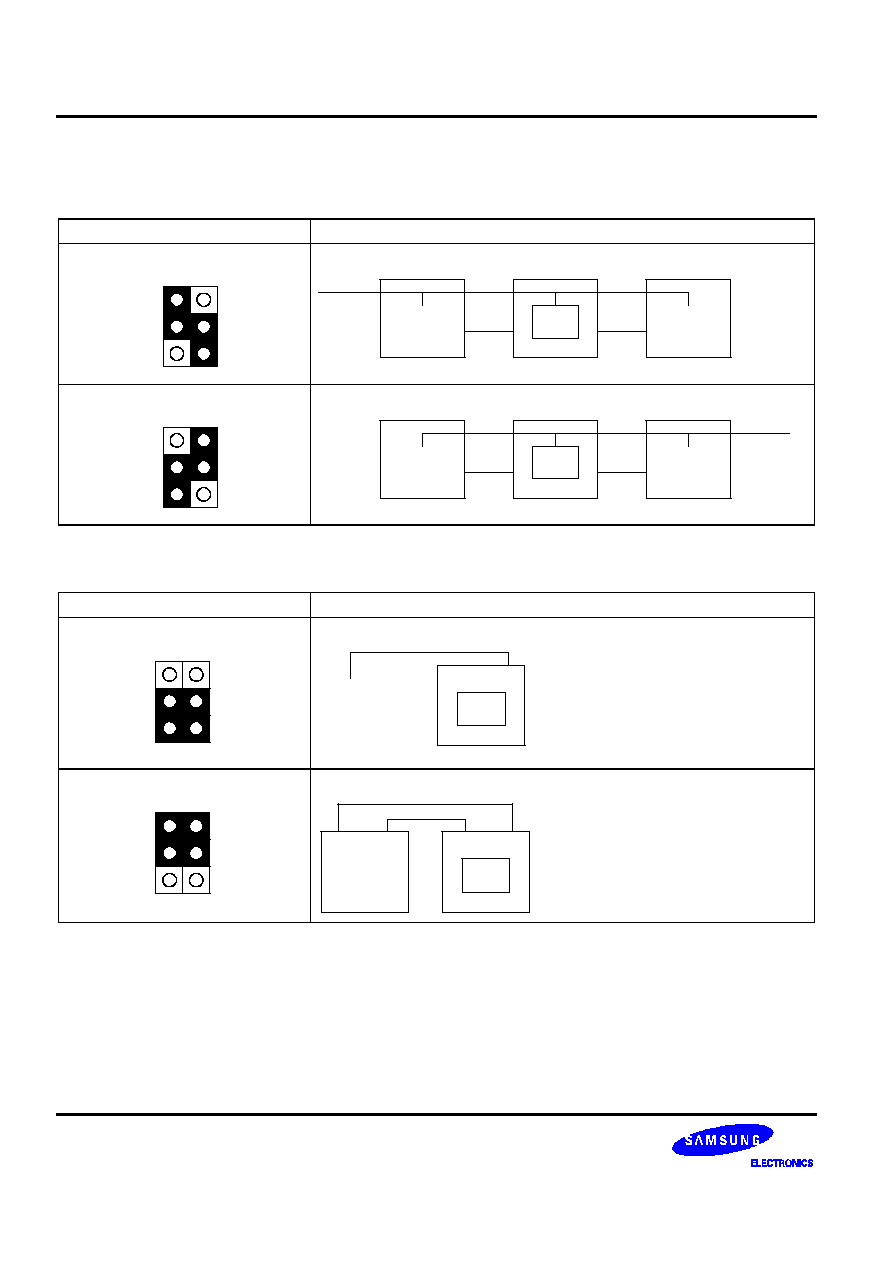

Figure 1-10. Pin Circuit Type E-4 (P1)

I/O

Output

Disable

Data

Pull-up

Enable

V

DD

ADC

Enable

To ADC

Data

Circuit

Type H-4

SEG

LCD EN

Circuit

Type C

Figure 1-11. Pin Circuit Type F-10 (P5)

S3CK225/FK225

PRODUCT OVERVIEW

1-13

Out

SEG

V

DD

V

LC1

V

LC0

Output

Disable

Figure 1-12. Pin Circuit Type H-4

V

DD

Output

Disable

Data

Pull-up

Enable

V

DD

I/O

P-CH

N-CH

Open Drain

Enable

Circuit

Type H-4

SEG

LCD

Out

Enable

Figure 1-13. Pin Circuit Type H-14 (P2, P3, P4, P6)

PRODUCT OVERVIEW

S3CK225/FK225

1-14

NOTES

S3CK225/FK225

ADDRESS SPACES

2-1

2

ADDRESS SPACES

OVERVIEW

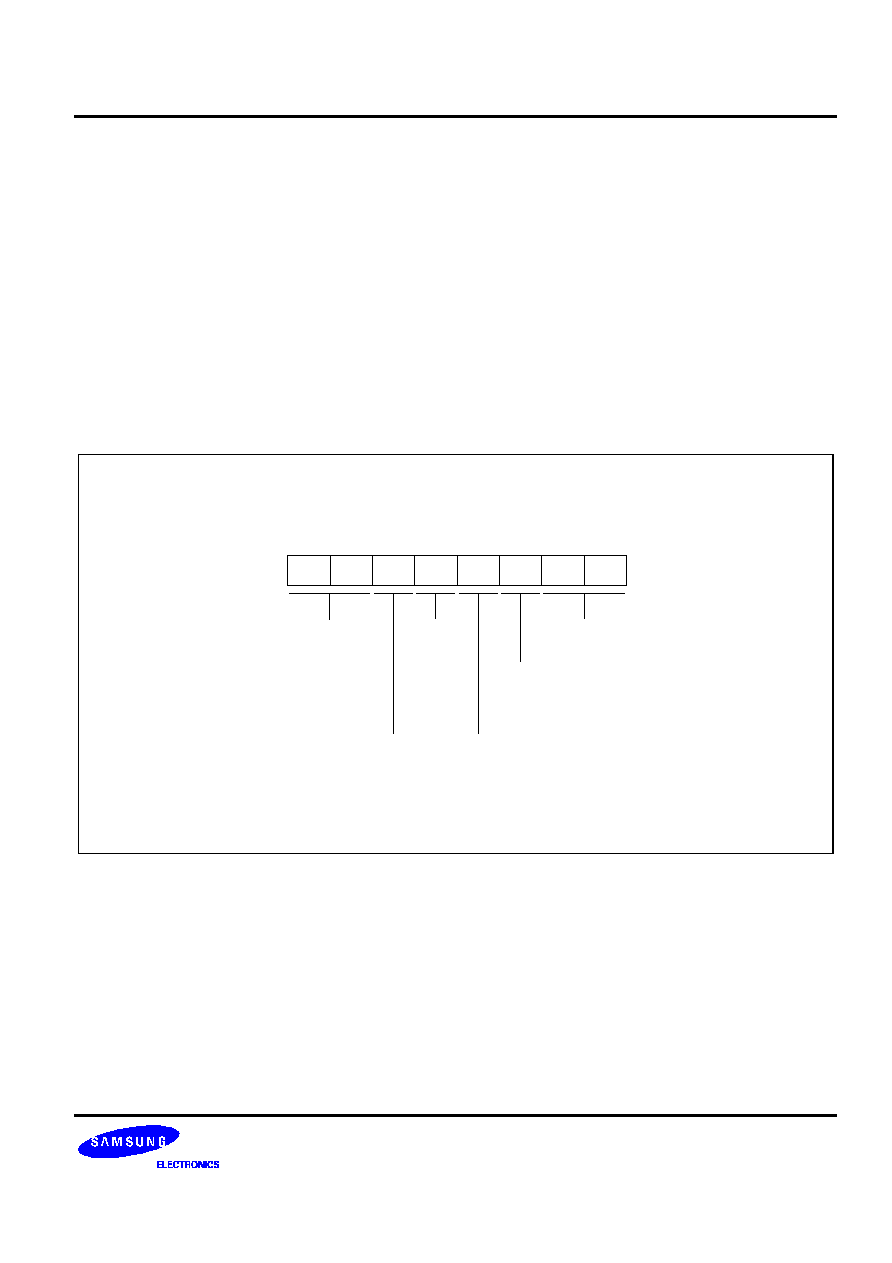

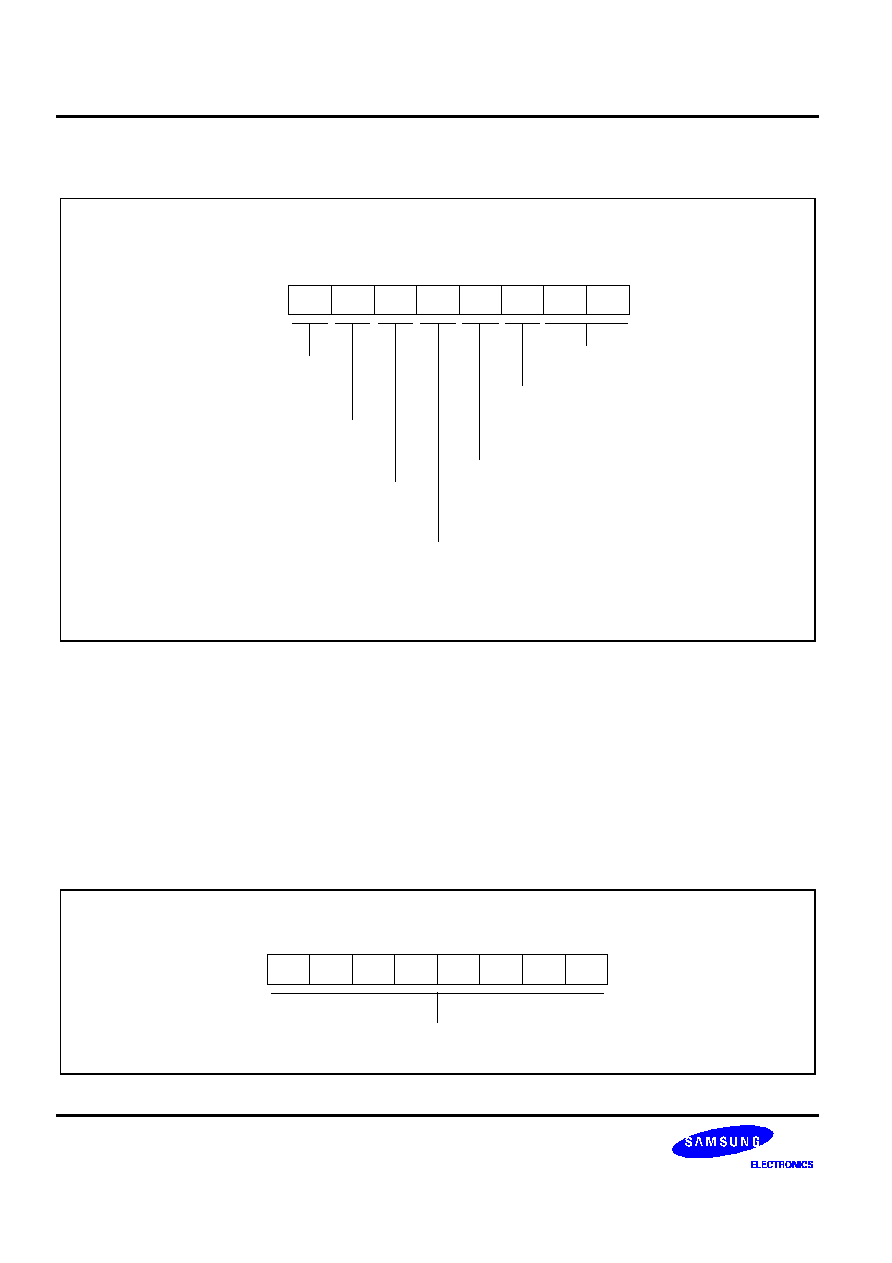

CalmRISC has 20-bit program address lines, PA[19:0], which supports up to 1M words of program memory. The

1M word program memory space is divided into 256 pages and each page is 4K word long as shown in the figure

2-1. The upper 8 bits of the program counter, PC[19:12], points to a specific page and the lower 12 bits, PC[11:0],

specify the offset address of the page.

CalmRISC also has 16-bit data memory address lines, DA[15:0], which supports up to 64K bytes of data memory.

The 64K byte data memory space is divided into 256 pages and each page has 256 bytes. The upper 8 bits of the

data address, DA[15:8], points to a specific page and the lower 8 bits, DA[7:0], specify the offset address of the

page.

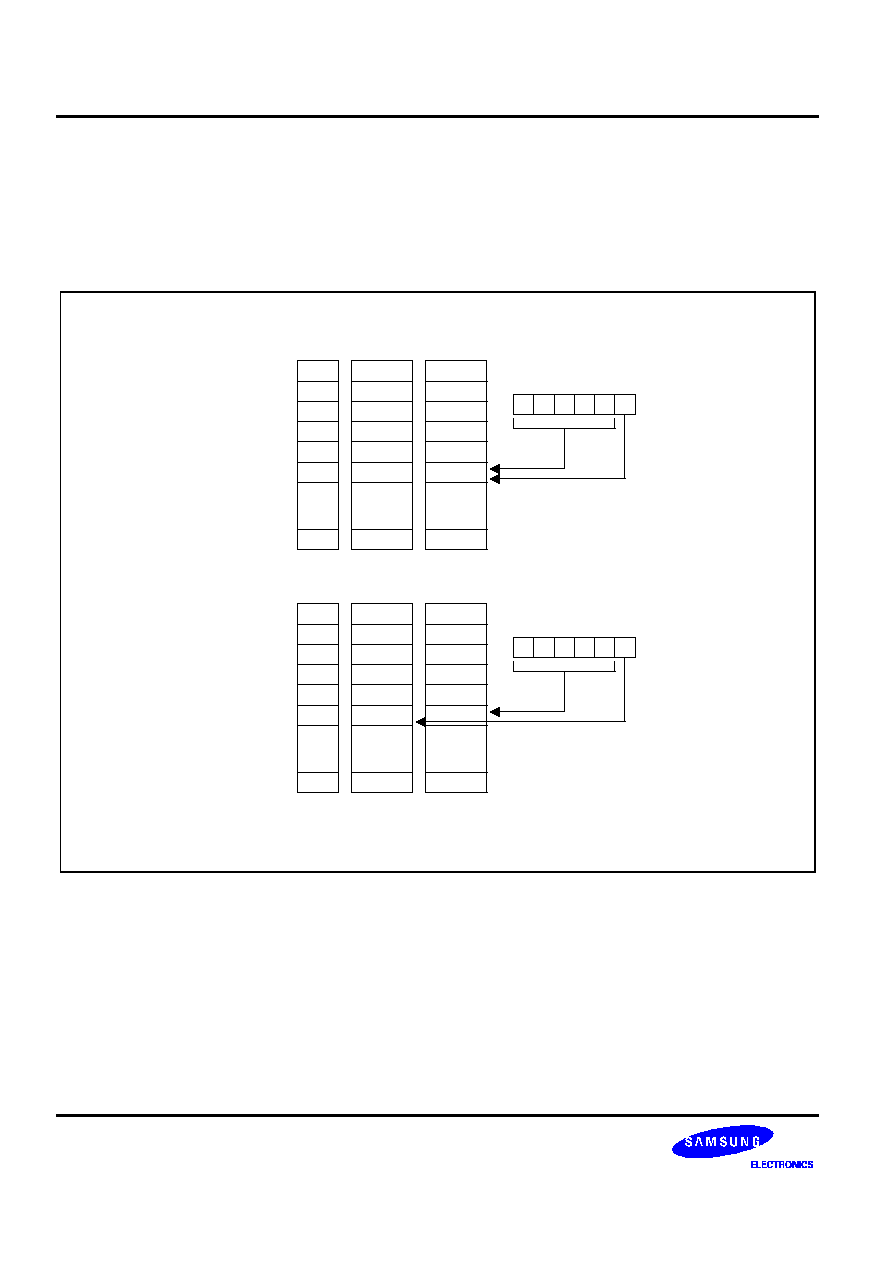

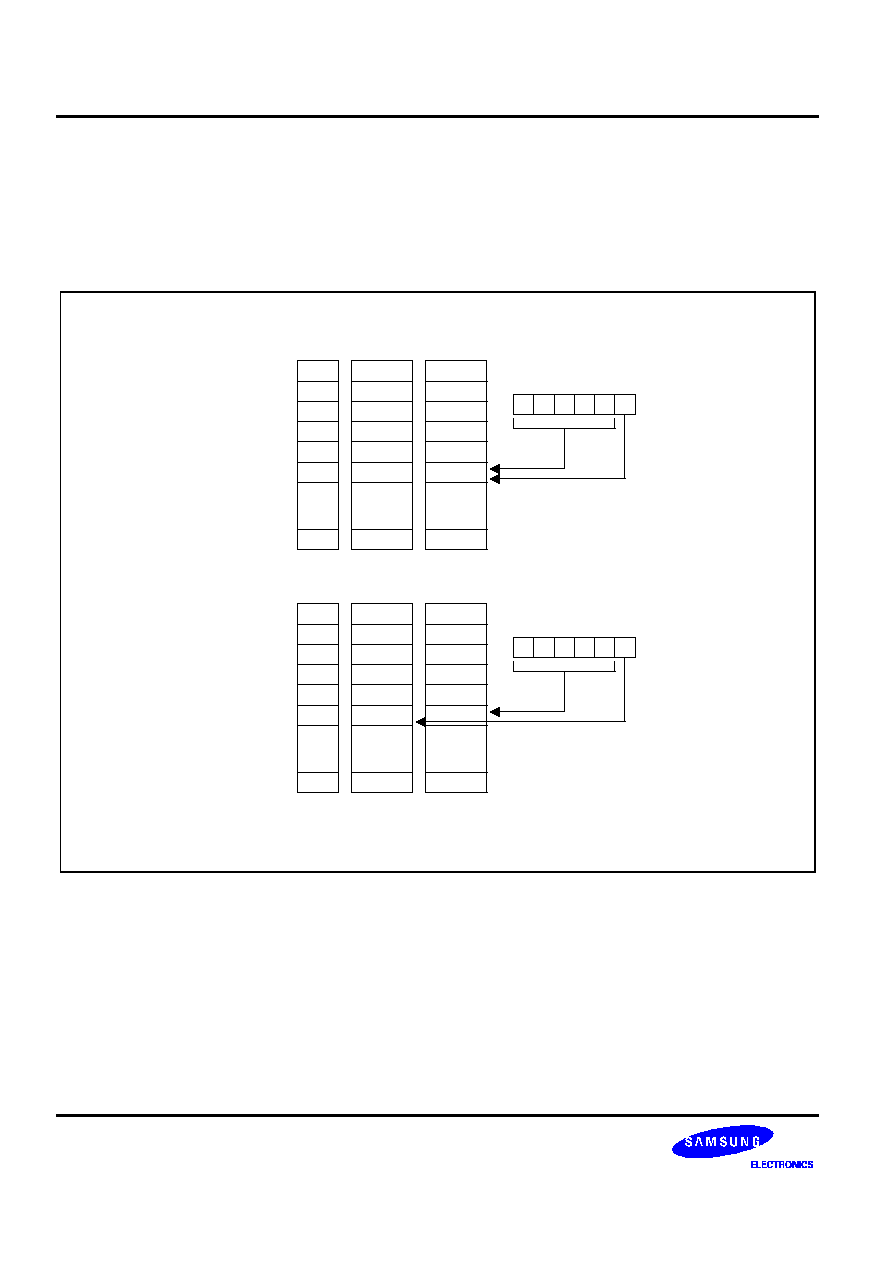

PROGRAM MEMORY (ROM)

000H

FFFH

256 page

1 Mword

4 Kword

FFFH

000H

Figure 2-1. Program Memory Organization

ADDRESS SPACES

S3CK225/FK225

2-2

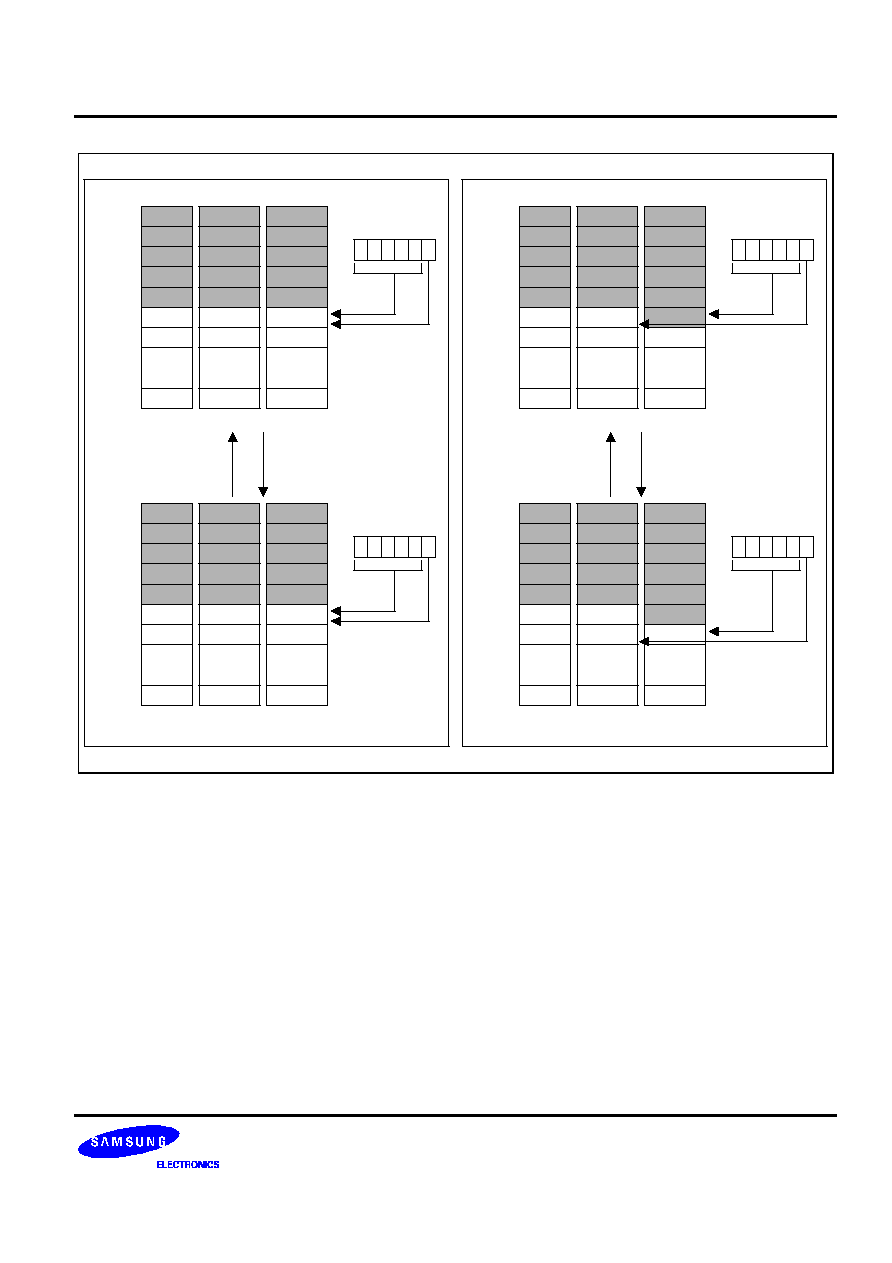

For example, if PC[19:0] = 5F79AH, the page index pointed to by PC is 5FH and the offset in the page is 79AH.

If the current PC[19:0] = 5EFFFH and the instruction pointed to by the current PC, i.e., the instruction at the

address 5EFFFH is not a branch instruction, the next PC becomes 5E000H, not 5F000H. In other words, the

instruction sequence wraps around at the page boundary, unless the instruction at the boundary (in the above

example, at 5EFFFH) is a long branch instruction. The only way to change the program page is by long branches

(LCALL, LLNK, and LJP), where the absolute branch target address is specified. For example, if the current

PC[19:0] = 047ACH (the page index is 04H and the offset is 7ACH) and the instruction pointed to by the current

PC, i.e., the instruction at the address 047ACH, is "LJP A507FH" (jump to the program address A507FH), then

the next PC[19:0] = A507FH, which means that the page and the offset are changed to A5H and 07FH,

respectively. On the other hand, the short branch instructions cannot change the page indices.

Suppose the current PC is 6FFFEH and its instruction is "JR 5H" (jump to the program address PC + 5H). Then

the next instruction address is 6F003H, not 70003H. In other words, the branch target address calculation also

wraps around with respect to a page boundary. This situation is illustrated below:

000H

001H

002H

003H

004H

005H

FFEH

FFFH

Page 6FH

JR 5H

Figure 2-2. Relative Jump Around Page Boundary

Programmers do not have to manually calculate the offset and insert extra instructions for a jump instruction

across page boundaries. The compiler and the assembler for CalmRISC are in charge of producing appropriate

codes for it.

S3CK225/FK225

ADDRESS SPACES

2-3

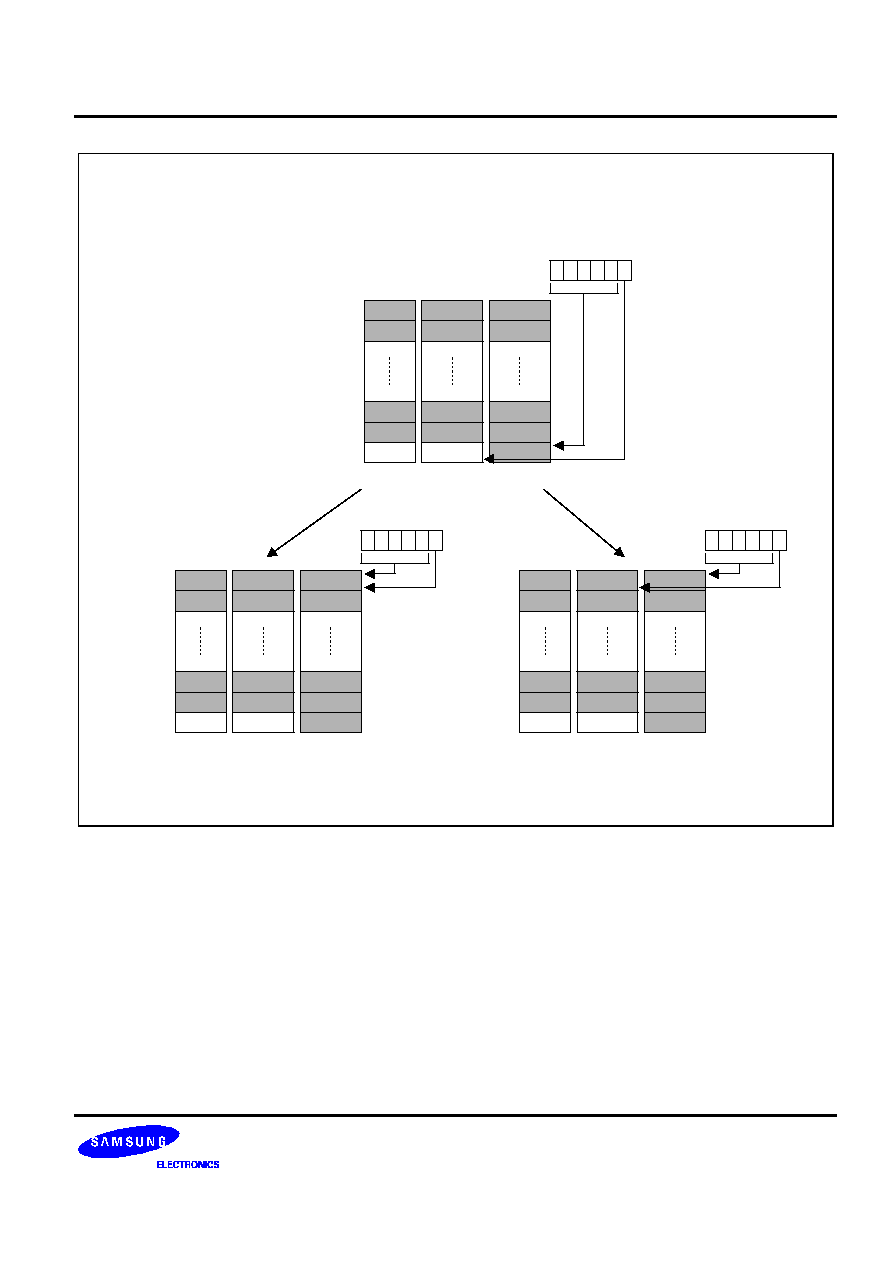

00000H

FFFFFH

Vector and

Option Area

~

~

~

~

00020H

0001FH

Program Memory Area

(4K words x 256 page = 1 Mword)

8K words

(16K bytes)

NOTE: For S3CK225, total size of program memory area is 8K words (16K bytes).

1FFFH

Figure 2-3. Program Memory Layout

From 00000H to 00004H addresses are used for the vector address of exceptions, and 0001EH, 0001FH are

used for the option only. Aside from these addresses others are reserved in the vector and option area. Program

memory area from the address 00020H to FFFFFH can be used for normal programs.

The Program memory size of S3CK225 is 8K word (16K byte), so from the address 00020H to 1FFFH are the

program memory area.

ADDRESS SPACES

S3CK225/FK225

2-4

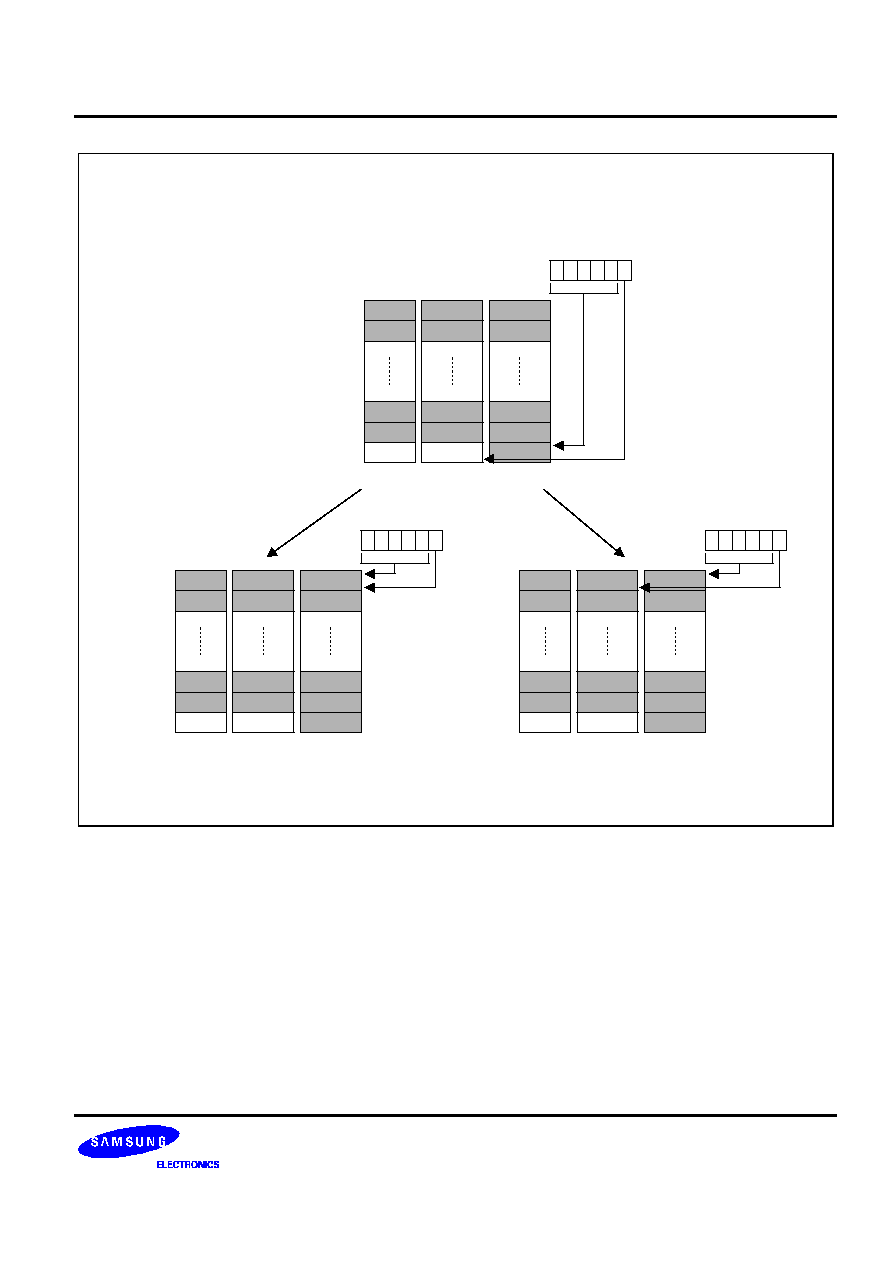

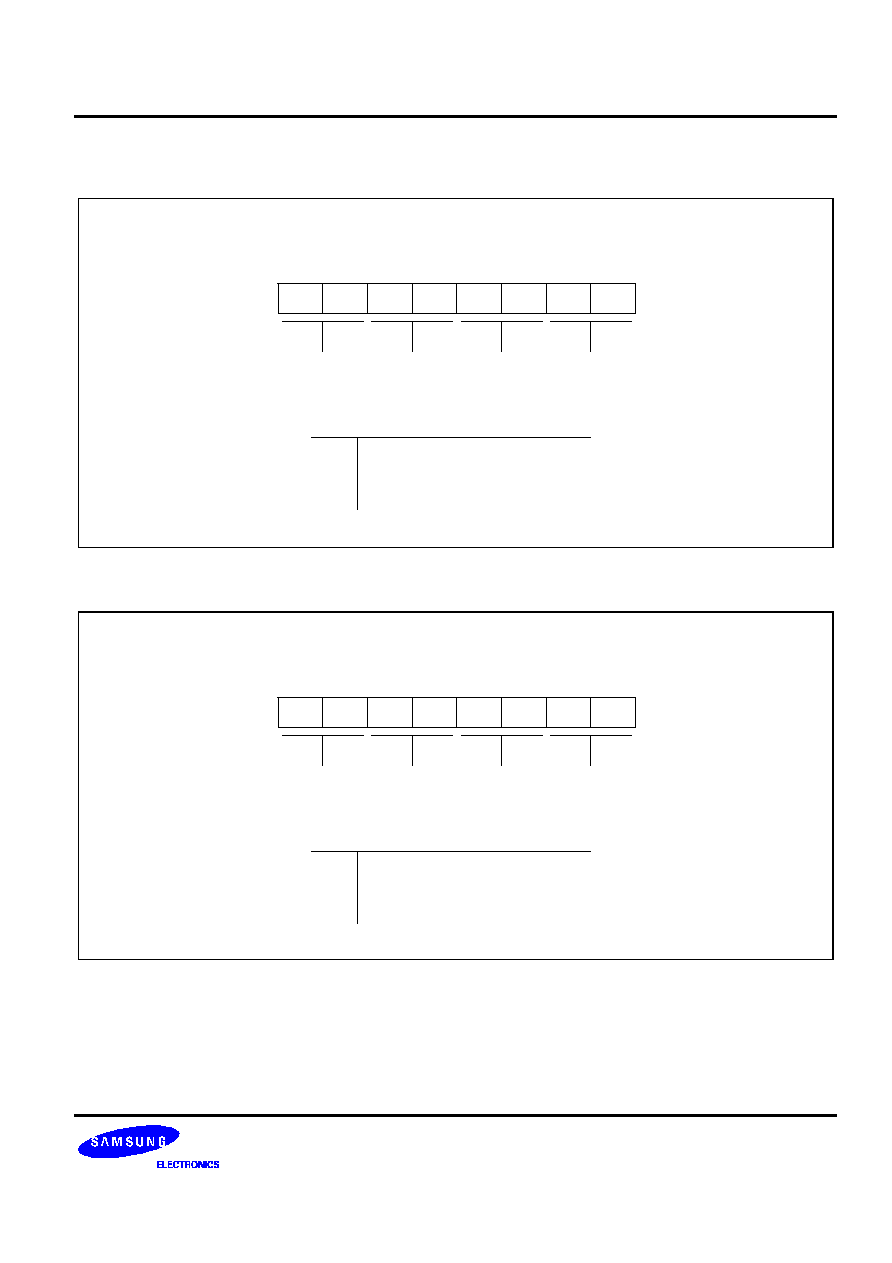

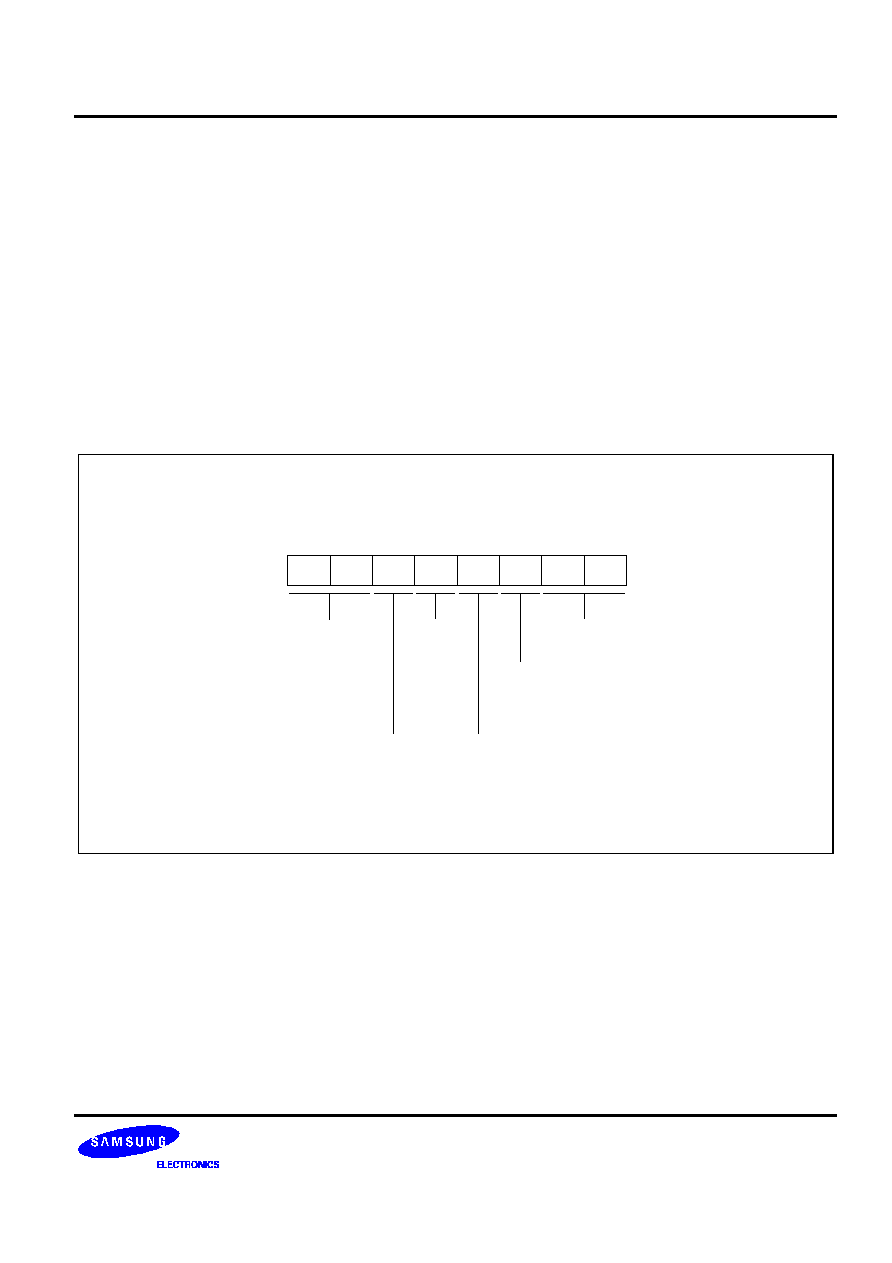

ROM CODE OPTION (RCOD_OPT)

Just after power on, the ROM data located at 0001EH and 0001FH is used as the ROM code option.

S3CK225 has ROM code options like the Reset value of Basic timer and Watchdog timer enable.

For example, if you program as below:

RCOD_OPT

1EH, 0x0000

RCOD_OPT

1FH, 0xbfff

fxx/32 is used as Reset value of basic timer (by bit.14, 13, 12)

Watchdog timer is enabled (by bit.11)

If you don't program any values in these option areas, then the default value is "1".

In these cases, the address 0001EH would be the value of "FFFFH".

S3CK225/FK225

ADDRESS SPACES

2-5

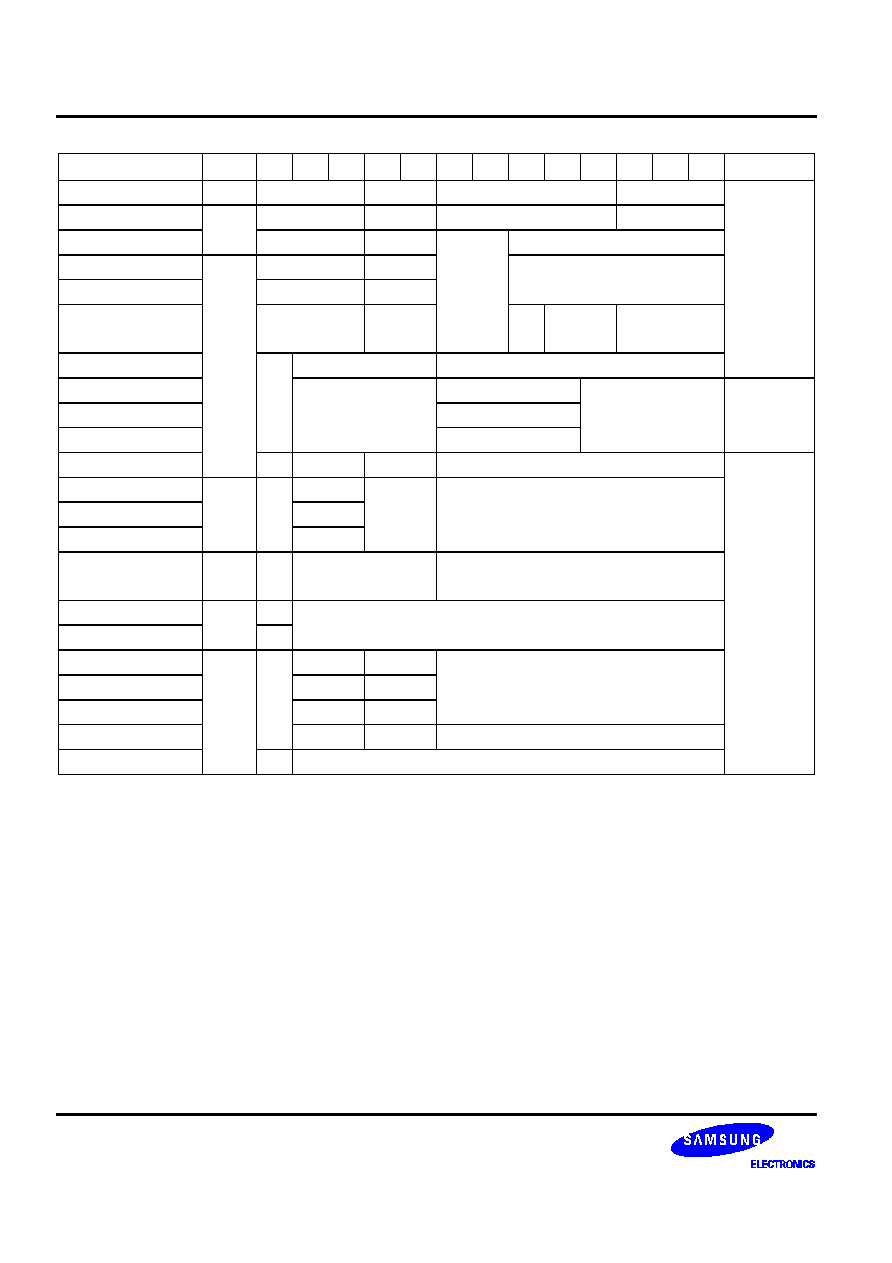

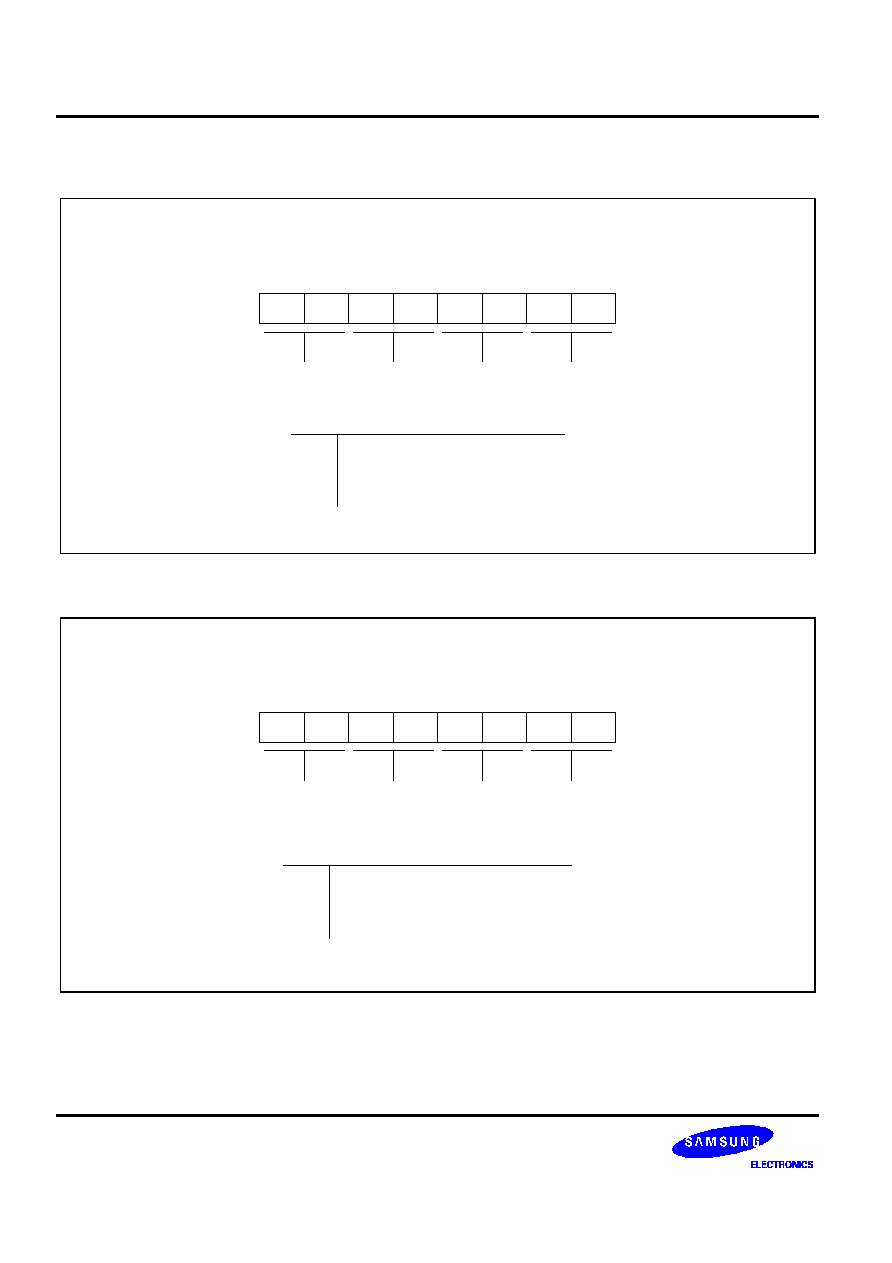

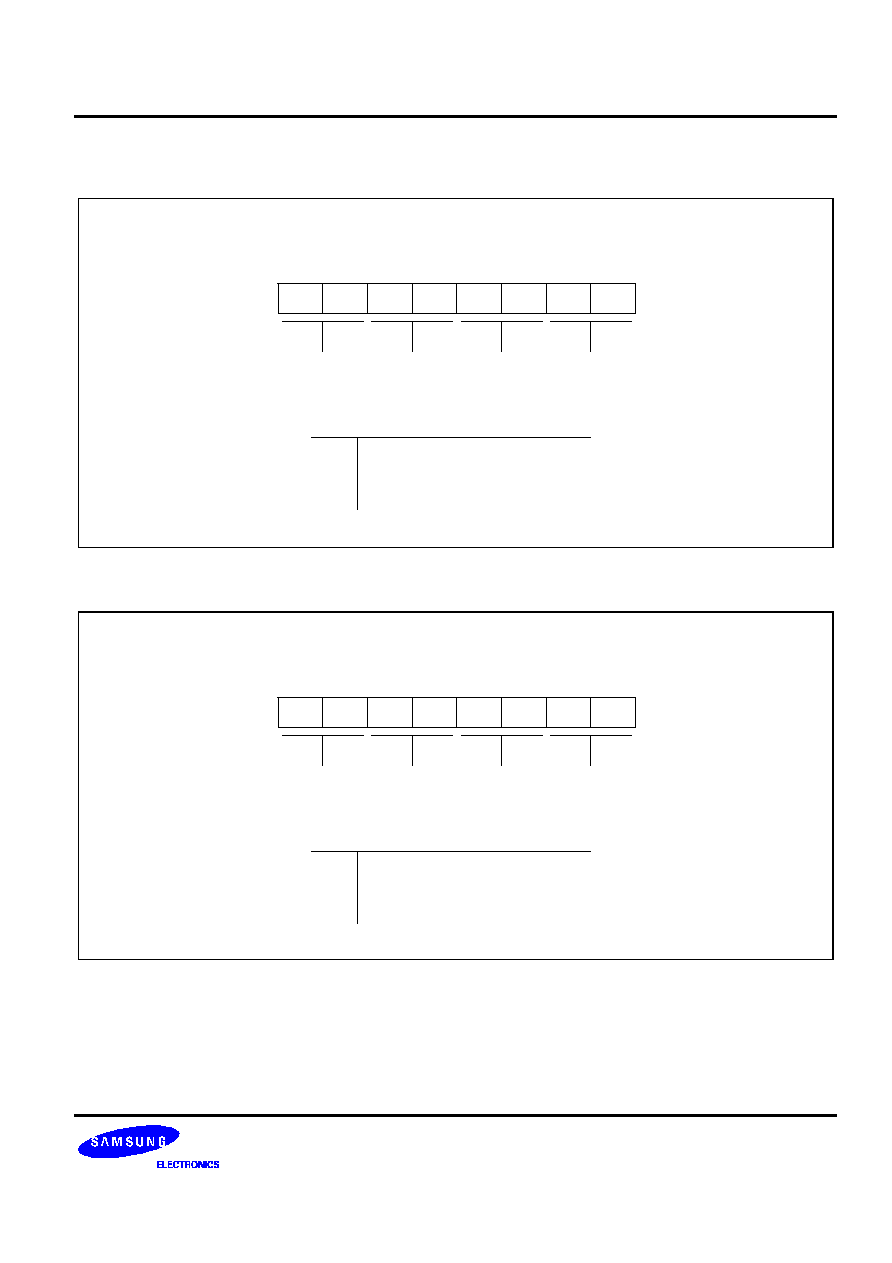

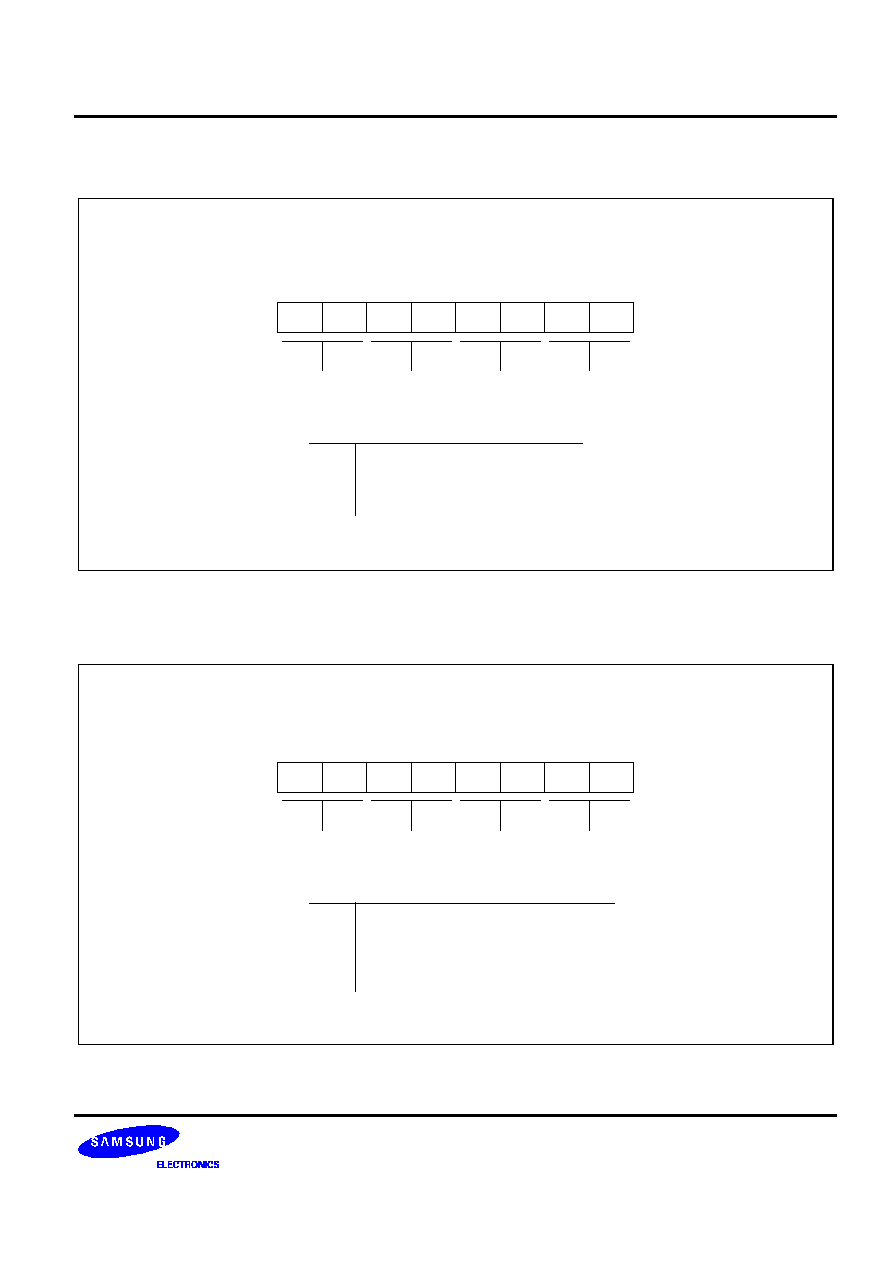

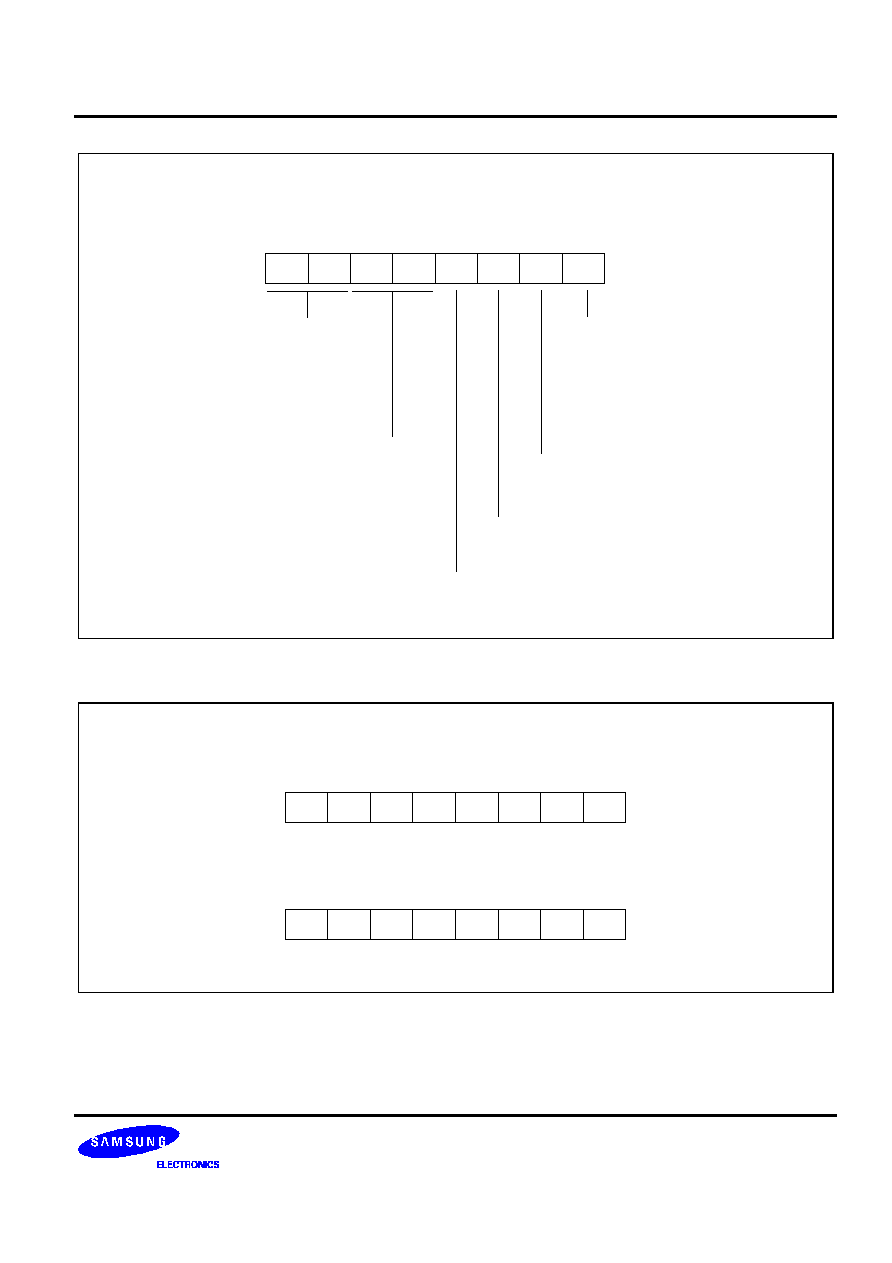

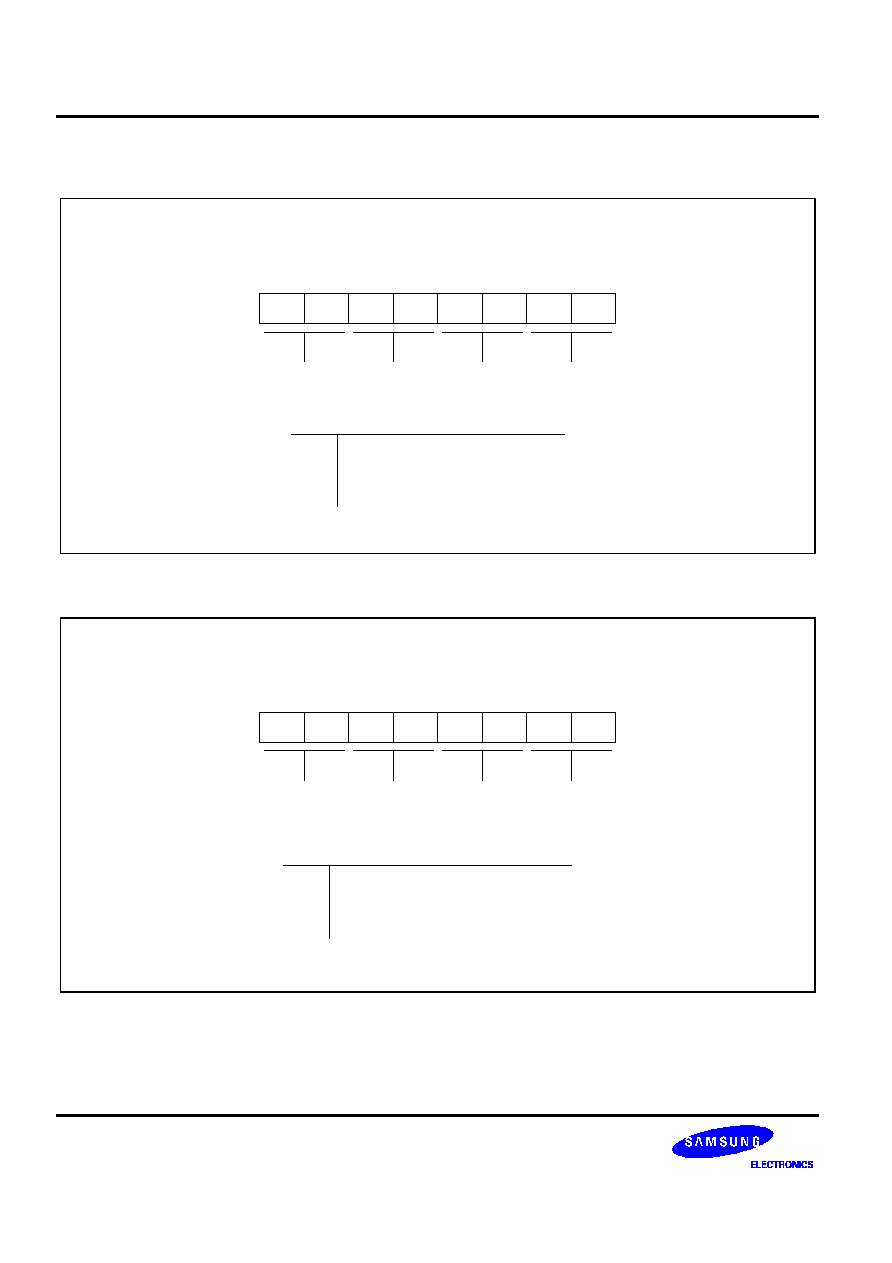

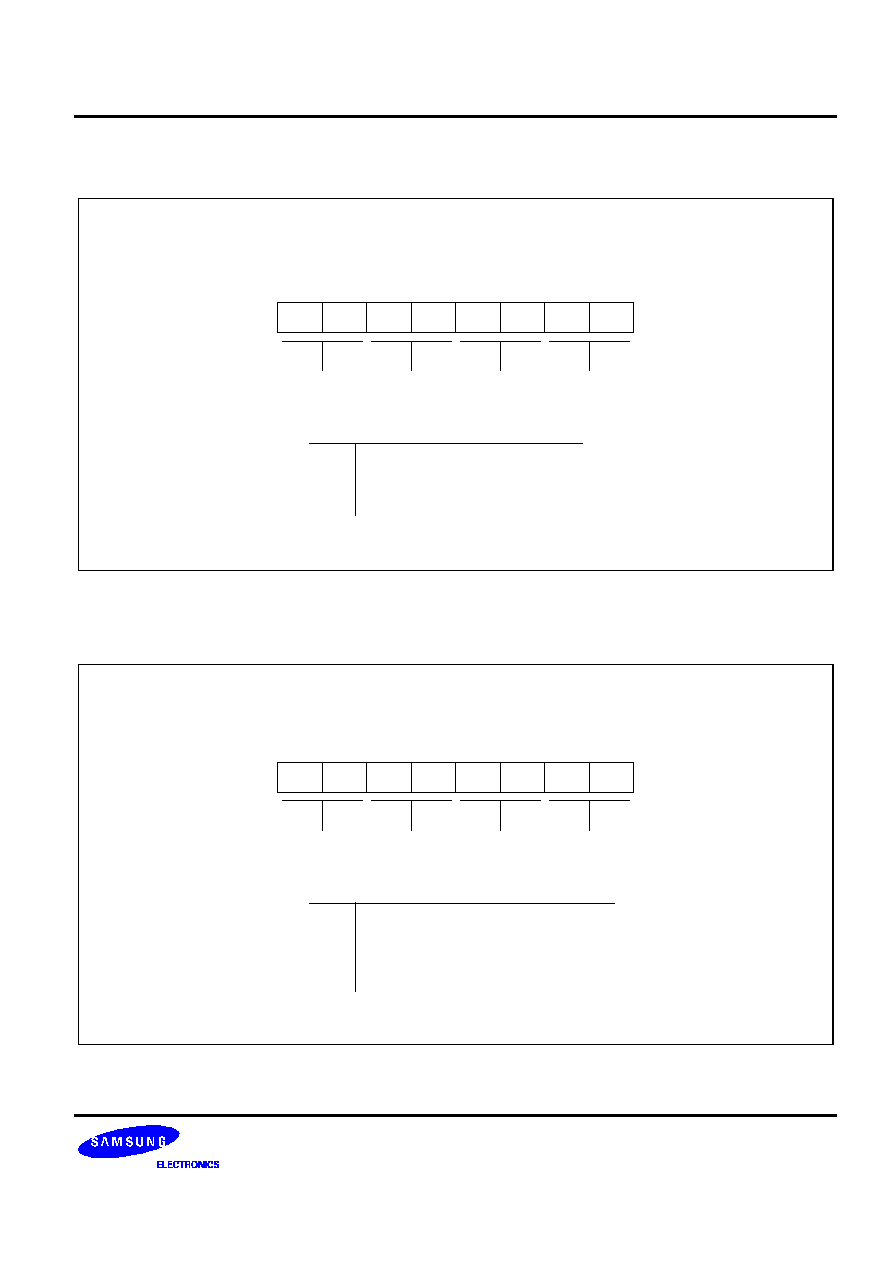

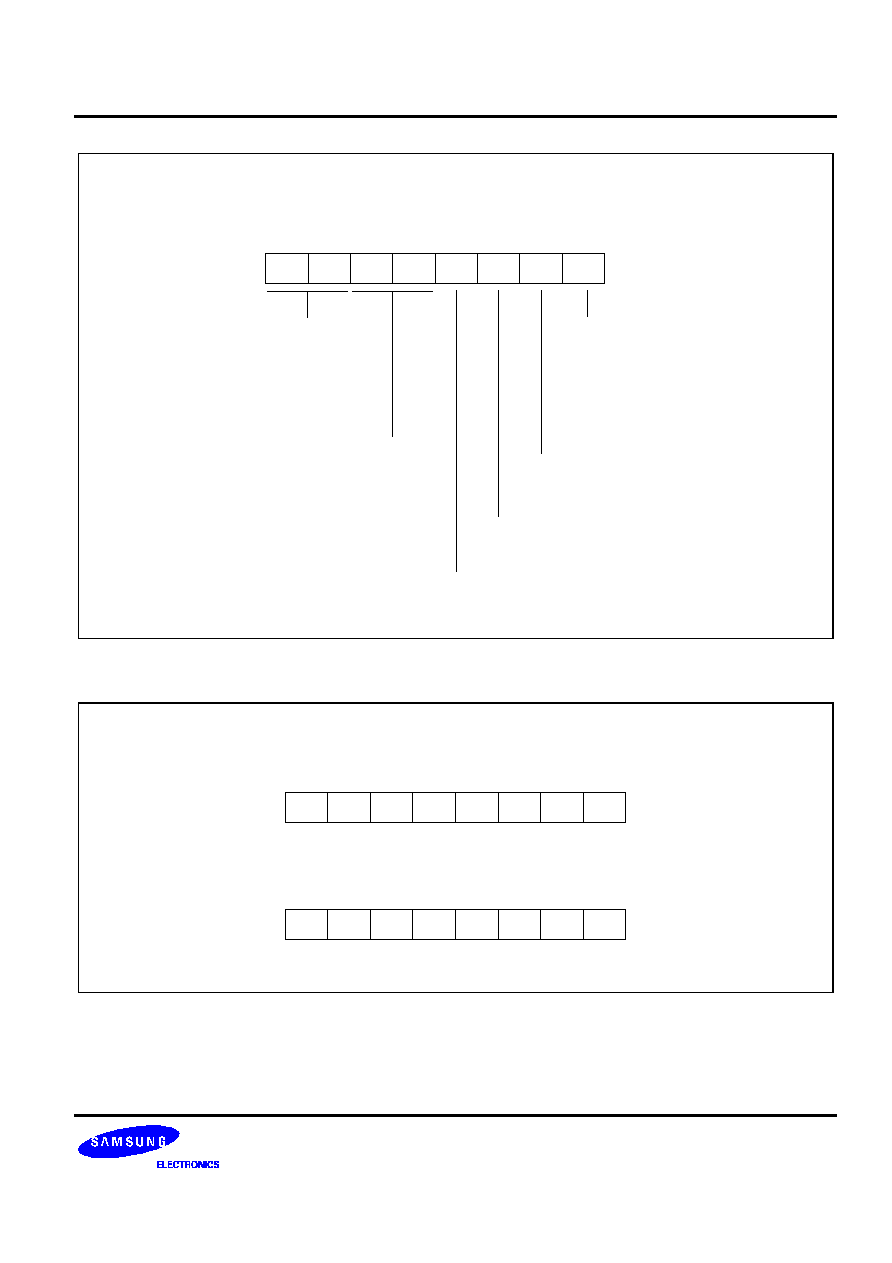

ROM_Code Option (RCOD_OPT)

ROM Address: 0001FH

Reset value of basic timer

clock selection bits

(WDTCON.6, .5, .4):

000 = fxx/2

001 = fxx/4

010 = fxx/16

011 = fxx/32

100 = fxx/128

101 = fxx/256

110 = fxx/1024

111 = fxx/2048

Not used

Watchdog timer enable selection bit: