S5C7320X01

DATA SHEET

1

PRODUCT SUMMARY

INTRODUCTION

S5C7320X01 receives digital data from CCD-using video camera

systems such as MMPC and surveillance cameras, and outputs

combined video signals. It also runs algorithms for AE/AWB and

transmits them to MICOM, or carries out AE/AWB independently.

S5C7320X01 has the following features;

FEATURES

∑

NTSC/PAL, 360H/510H/720H/760H CCD compatible

∑

Able to detect and correct 64 CCD white defects

∑

Built-in digital clamp feature

∑

3-line processing using 2 line memories

∑

Luminance signal process

∑

Chrominance signal process

∑

Color difference signal modulation using

quadrature subcarrier generation (DTO)

method

∑

Built-in timing and sync signal generator

∑

External synchronization compatible

(Line-lock, H-reset/V-reset, H-PLL/V-reset)

∑

Built-in ability to determine if in external synchronization mode

∑

Serial MICOM interface

∑

Built-in algorithm for AE/AWB

∑

MICOMless (stand-alone) full AE/AWB

∑

Partial linear approximation method's

compensation

feature for R, G, B and luminance

∑

Built-in 2CH DAC for combined Y/C analog output

∑

EEPROM interface for register setting without MICOM

∑

Built-in EVR interface for controlling CDS/AGC, and CCD

APPLICATIONS

∑

Camcorder

∑

Surveillance camera

∑

Multimedia PC (MMPC) camera

100-TQFP-1414

ORDERING INFORMATION

Device

Package

Operating Tempertature

S5C7320X01-T0R0

100-TQFP-1414

0

∞

C

-

70

∞

C

DATA SHEET

S5C7320X01

2

PIN CONFIGURATION

Figure 1. Pin Configuration

V

S

S

1

R

G

S

H

P

S

H

D

P

C

1

X

1

X

2

V

D

D

1

C

L

P

1

2

C

L

P

3

4

P

B

L

K

V

D

H

D

F

L

D

V

S

S

2

L

S

F

E

C

S

Y

N

C

P

A

L

H

I

G

H

C

C

I

R

V

D

D

2

S

R

D

A

O

S

R

D

A

I

S

R

C

K

M

I

C

O

M

CCD7

CCD6

CCD5

CCD4

CCD3

CCD2

CCD1

CCD0

VDD5

SECK

SECSN

SED

ADCK

V4

SG2

V3

VSS5

SG1

V1

V2

SUB

VSS6

H1

H2

VDD6

WB1

WB0

WBRNG

SS2

SS1

SS0

FSHTR

VDDA2

VSSA2

AC

VREF

IREF

VBB

COMP

AY

VSSA1

VDDA1

EHD

EVD

SMO

SMI

SMCK

SMCSN

BLC

RSTN

C

C

D

8

C

C

D

9

S

C

E

T

S

T

1

T

S

T

0

X

C

K

Y

O

7

Y

O

6

Y

O

5

Y

O

4

V

S

S

4

Y

O

3

Y

O

2

Y

O

1

Y

O

0

V

D

D

3

C

O

7

C

O

6

C

O

5

C

O

4

V

S

S

3

C

O

3

C

O

2

C

O

1

C

O

0

S5C7520X01

S5C7320X01

DATA SHEET

3

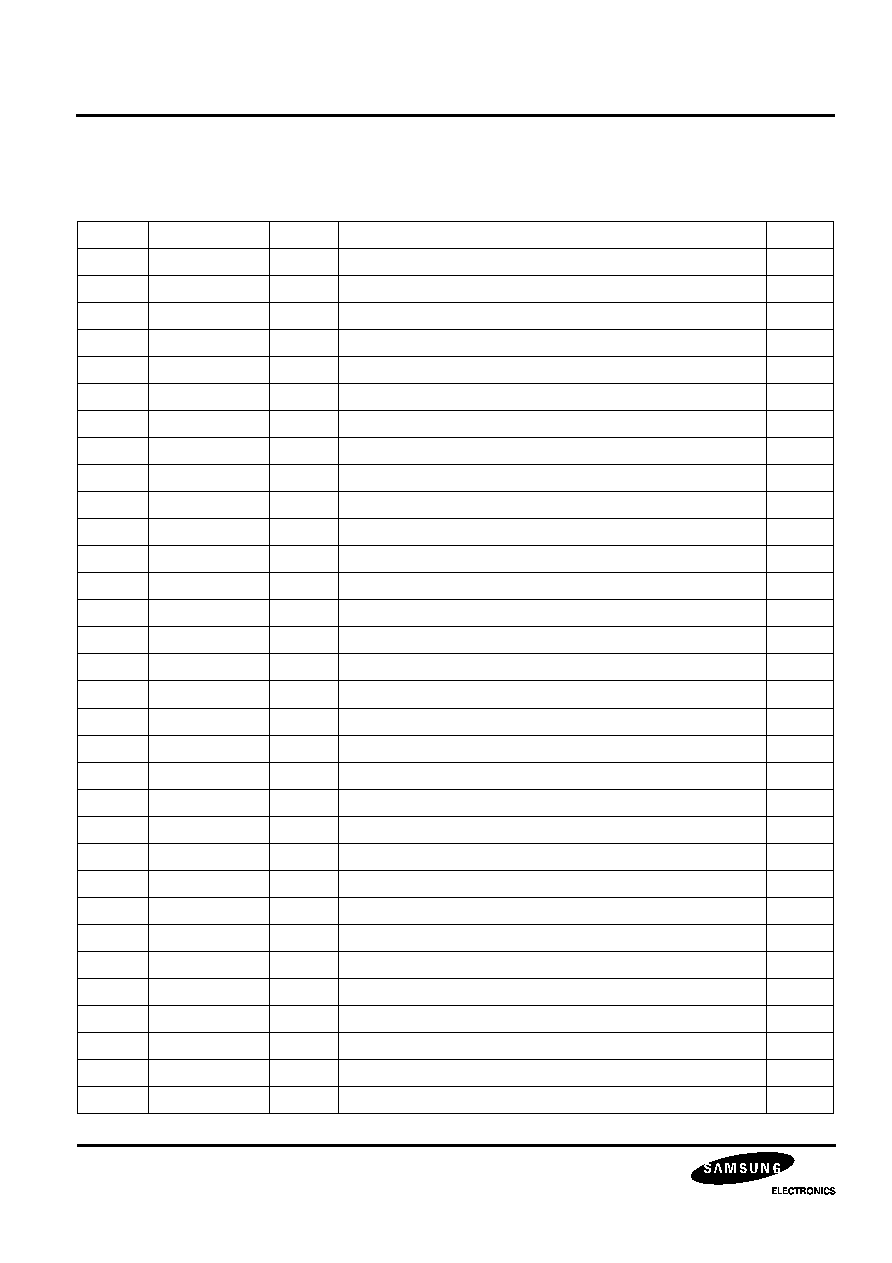

PIN DESCRIPTION

Table 1. Pin Description

No

Name

I/O

Description

Note

1

VSS1

G

Ground

2

PC1

O

Phase comparator output for main clock PLL

3

X1

I

Main X-TAL input

4

X2

O

Main X-TAL output

5

RG

O

Reset gate pulse

6

SHP

O

Precharge sample & hold pulse

7

SHD

O

Data sample & hold pulse

8

VDD1

P

Power

9

CLP12

O

Clamp pulse 12 (CLP1/CLP2 multiplexing)

10

CLP34

O

Clamp pulse 34 (CLP3/CLP4 multiplexing)

11

PBLK

O

Pre-blank pulse

12

VD

O

Vertical drive pulse

13

HD

O

Horizontal drive pulse

14

FLD

O

Field ID signal

15

VSS2

G

Ground

16

LSFE

O

Low shutter enable signal (or Vsynco)

17

CSYNC

O

Composite sync (or Hsynco)

18

PAL

I

PAL mode (L: NTSC, H: PAL)

P-down

19

HIGH

I

High mode (L: Normal, H:HI8)

P-down

20

CCIR

I

CCIR format mode (L: CIF, H: CCIR)

P-down

21

VDD2

P

Power

22

SRDAO

O

EEPROM data output

23

SRDAI

I

EEPROM data input

24

SRCK

O

EEPROM control clock

25

MICOM

I

Stand-alone/MICOM IF selection (L: stand-alone)

P-down

26

BLC

I

Back light compensation enable

P-down

27

SMCSN

I

Serial MICOM chip select enable (active "L")

Schmitt

28

SMCK

I

Serial MICOM input clock

Schmitt

29

SMI

I

Serial MICOM data input

Schmitt

30

SMO

O

Serial MICOM data output

31

RSTN

I

Master reset (active low)

32

EVD

I

EXT. sync. VD input (line-lock/V-reset mode)

P-up

DATA SHEET

S5C7320X01

4

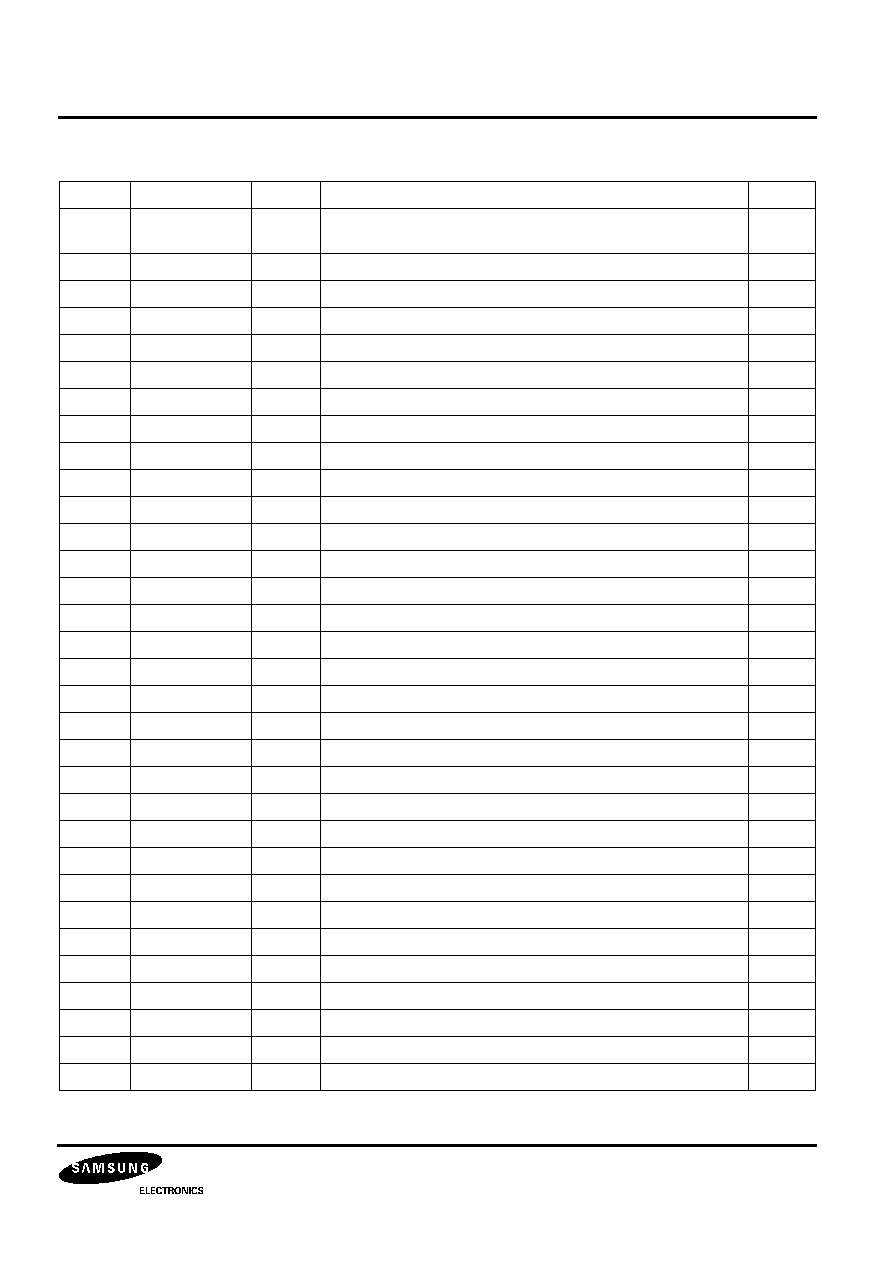

33

EHD

I

EXT. sync. HD input

(separate sync., composite sync. locking mode.)

P-up

34

VDDA1

P

Analog power for DAC

35

VSSA1

G

Analog ground for DAC

36

AY

O(A)

Analog luminance output

37

COMP

I(A)

Compensation terminal for DAC

38

VBB

G

DAC bulk bias (ground)

39

IREF

I(A)

Current reference terminal

40

VREF

I(A)

Voltage reference terminal

41

AC

O(A)

Analog CHROMA output

42

VSSA2

G

Analog ground for DAC

43

VDDA2

P

Analog power for DAC

44

FSHTR

I

Fixed high speed shutter mode (active H)

P-down

45

SS0

I

Fixed high speed shutter control 0

P-down

46

SS1

I

Fixed high speed shutter control 1

P-down

47

SS2

I

Fixed high speed shutter control 2

P-down

48

WBRNG

I

White balance range selection

P-down

49

WB0

I

White balance mode 0

P-down

50

WB1

I

White balance mode 1

Pull-up

51

CO0

O

Digital CHROMA output (LSB)

52

CO1

O

Digital CHROMA output

53

CO2

O

Digital CHROMA output

54

CO3

O

Digital CHROMA output

55

VSS3

G

Ground

56

CO4

O

Digital CHROMA output

57

CO5

O

Digital CHROMA output

58

CO6

O

Digital CHROMA output

59

CO7

O

Digital CHROMA output (MSB)

60

VDD3

P

Power

61

YO0

O

Digital luminance output (LSB)

62

YO1

O

Digital luminance output

63

YO2

O

Digital luminance output

64

YO3

O

Digital luminance output

Table 1. Pin Description (Continued)

No

Name

I/O

Description

Note

S5C7320X01

DATA SHEET

5

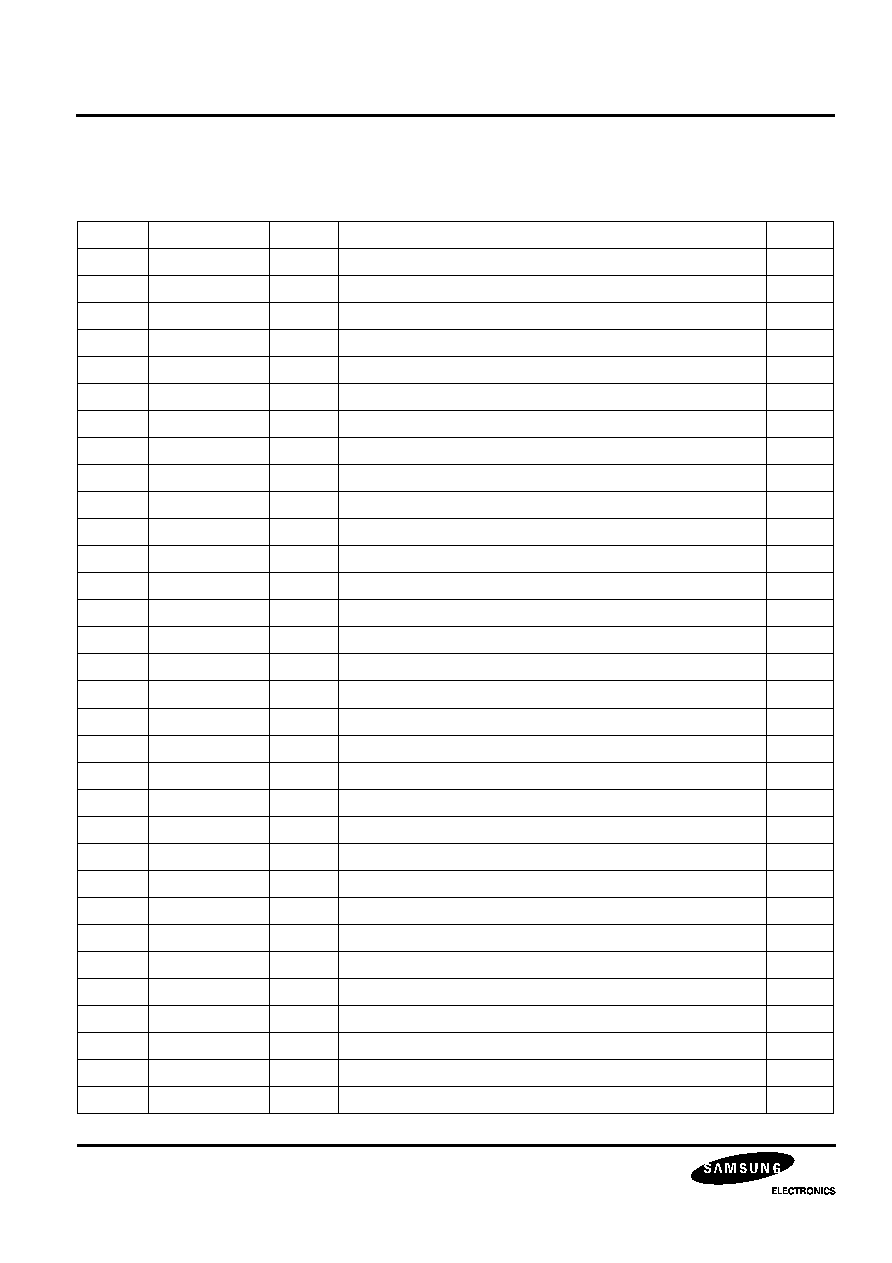

65

VSS4

G

Ground

66

YO4

O

Digital luminance output

67

YO5

O

Digital luminance output

68

YO6

O

Digital luminance output

69

YO7

O

Digital luminance output (MSB)

70

XCK

I

Encoder external clock input for line-lock

"L"

71

TST0

I

Test pin 0 (active high)

"L"

72

TST1

I

Test pin 1(active high)

"L"

73

SCE

I

Scan enable for test (active high)

"L"

74

CCD9

I

CCD data input [MSB]

75

CCD8

I

CCD data input

76

CCD7

I

CCD data input

77

CCD6

I

CCD data input

78

CCD5

I

CCD data input

79

CCD4

I

CCD data input

80

CCD3

I

CCD data input

81

CCD2

I

CCD data input

82

CCD1

I

CCD data input

83

CCD0

I

CCD data input [LSB]

84

VDD5

P

Power

85

SECK

O

CDS/AGC, EVR clock

86

SECSN

O

CDS/AGC, EVR chip select (acitve low)

87

SED

O

CDS/AGC, EVR data line

88

ADCK

O

ADC sampling clock

89

V4

O

Vertical drive pulse 4 for CCD

90

SG2

O

CCD sensor read out pulse 2

91

V3

O

Vertical drive pulse 3 for CCD

92

VSS5

G

Ground

93

SG1

O

CCD sensor read out pulse 1

94

V1

O

Vertical drive pulse 1 for CCD

95

V2

O

Vertical drive pulse 2 for CCD

96

SUB

O

CCD discharge pulse

97

VSS6

G

Ground for H1, H2

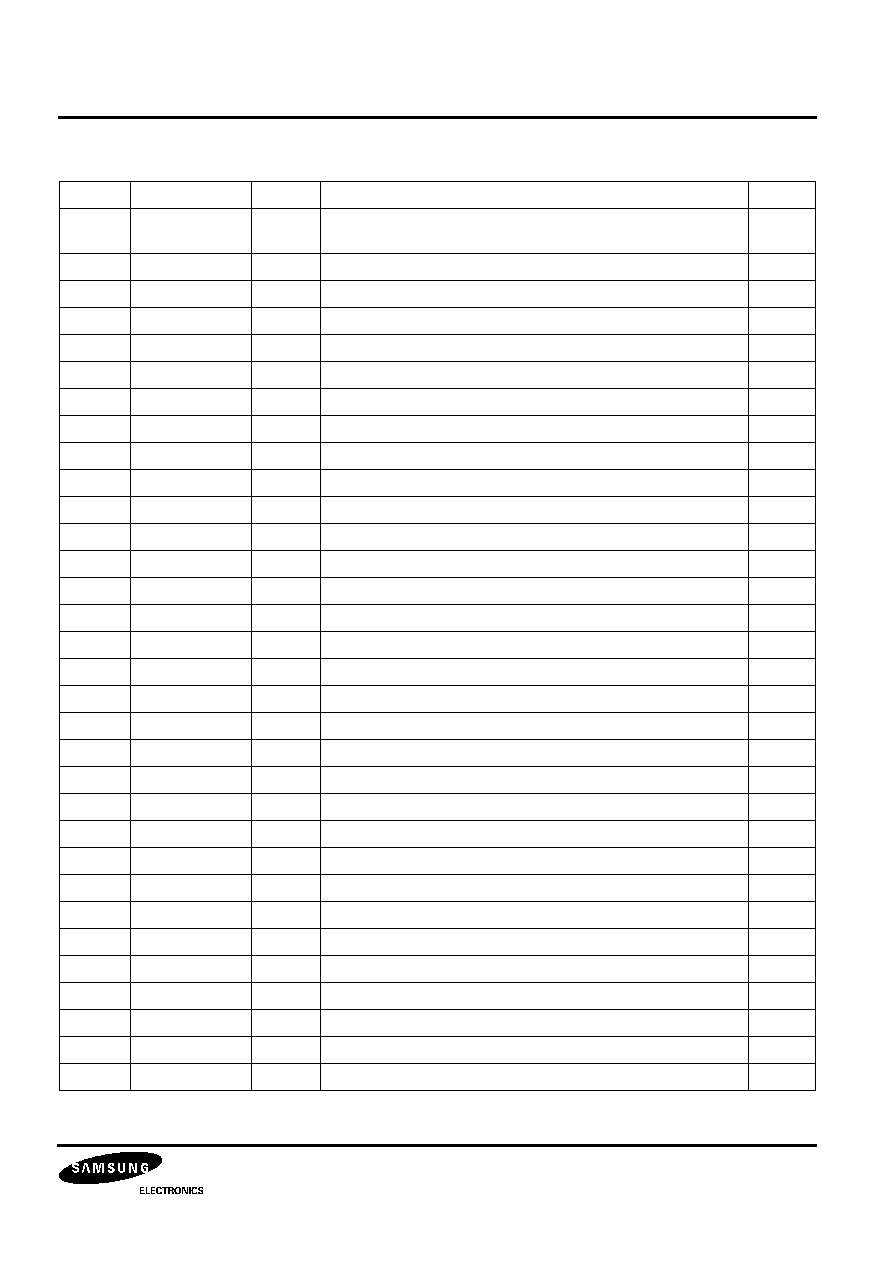

Table 1. Pin Description (Continued)

No

Name

I/O

Description

Note