| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: LC72722 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Ordering number : ENN6123A

51202AS (OT)/83199TH (OT) No. 6123-1/15

Overview

The LC72722 and LC72722M, LC72722PM are single-

chip system ICs that implement the signal processing

required by the European Broadcasting Union RDS (Radio

Data System) standard and by the US NRSC (National

Radio System Committee) RDBS (Radio Broadcast Data

System) standard. These ICs include band-pass filter,

demodulator, synchronization, and error correction circuits

as well as data buffer RAM on chip and perform effective

error correction using a soft-decision error correction

technique.

Functions

∑ Band-pass filter: Switched capacitor filter (SCF)

∑ Demodulator: RDS data clock regeneration and

demodulated data reliability information

∑ Synchronization: Block synchronization detection (with

variable backward and forward protection conditions)

∑ Error correction: Soft-decision/hard-decision error

correction

∑ Buffer RAM: Adequate for 24 blocks of data (about 500

ms) and flag memory

∑ Data I/O: CCB interface (power on reset)

Features

∑ Error correction capability improved by soft-decision

error correction

∑ The load on the control microprocessor can be reduced

by storing decoded data in the on-chip data buffer RAM.

∑ Two synchronization detection circuits provide

continuous and stable detection of the synchronization

timing.

∑ Data can be read out starting with the backward-

protection block data after a synchronization reset.

∑ Bit slip detection and correction

∑ Low spurious radiation

∑ Fully adjustment free

∑ Operating power-supply voltage: 4.5 to 5.5 V

∑ Operating temperature: ≠40 to +85∞C

∑ Package: LC72722 : DIP24S

LC72722M : MFP24S

LC72722PM : MFP24

Package Dimensions

unit: mm

3067A-DIP24S

LC72722, 72722M, 72722PM

SANYO Electric Co.,Ltd. Semiconductor Company

TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

Single-Chip RDS

Signal-Processing System LSI

CMOS IC

Any and all SANYO products described or contained herein do not have specifications that can handle

applications that require extremely high levels of reliability, such as life-support systems, aircraft's

control systems, or other applications whose failure can be reasonably expected to result in serious

physical and/or material damage. Consult with your SANYO representative nearest you before using

any SANYO products described or contained herein in such applications.

SANYO assumes no responsibility for equipment failures that result from using products at values that

exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other

parameters) listed in products specifications of any and all SANYO products described or contained

herein.

∑ CCB is a trademark of SANYO ELECTRIC CO., LTD.

∑ CCB is SANYO's original bus format and all the bus

addresses are controlled by SANYO.

0.48

(3.25)

3.3

3.9max

0.51min

21.0

(0.71)

1.78

0.25

7.62

6.4

1

12

24

13

0.95

0.9

SANYO: DIP24S

[LC72722]

unit: mm

3112A-MFP24S

unit: mm

3045C-MFP24

No. 5602-2/15

LC72722, 72722M, 72722PM

1

12

24

13

1.27

15.2

0.35

10.5

7.9

(0.62)

2.35max

0.1

(2.15)

0.65

0.15

SANYO: MFP24

[LC72722PM]

1

12

24

13

12.5

(0.75)

1.0

0.15

0.35

5.4

7.6

0.63

1.7max

1.5

0.1

SANYO: MFP24S

[LC72722M]

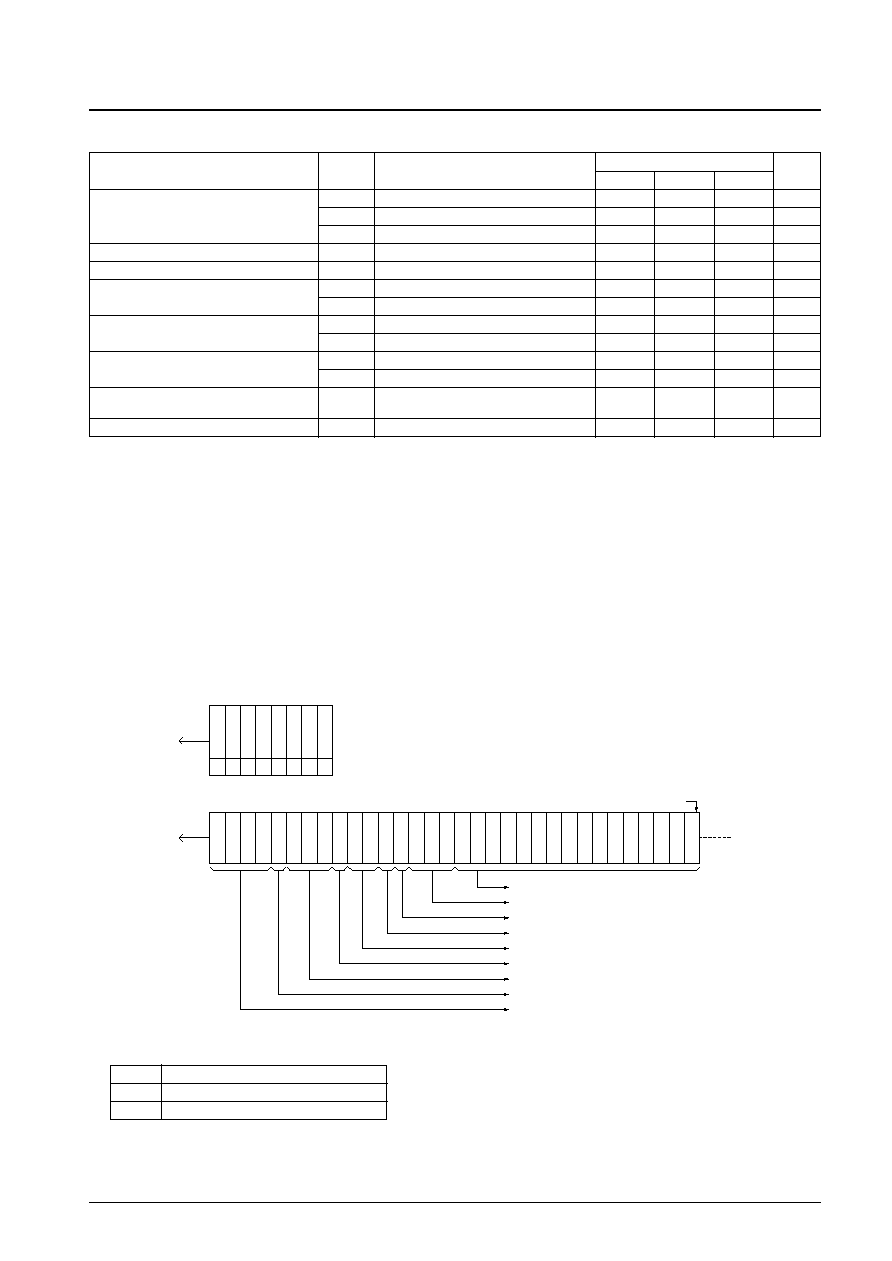

Pin Assignment

Block Diagram

A12363

1

24

VREF

SYR

2

23

MPXIN

CE

3

22

Vdda

DI

4

21

Vssa

CL

5

20

FLOUT

DO

6

19

CIN

LC72722

LC72722M

LC72722PM

Top view

RDS-ID

7

18

T1

SYNC

8

17

T2

T7(CORREC/ARI-ID/TA/BEO)

9

16

T3(RDCL)

T6(ERROR/57K/TP/BE1)

10

15

T4(RDDA)

Vssd

11

14

T5(RSFT)

Vddd

12

13

XOUT

XIN

REFERENCE

VOLTAGE

ANTIALIASING

FILTER

SMOOTHING

FILTER

57 kHz

BPF

(SCF)

TEST

+

≠

PLL

(57 kHz)

VREF

CLOCK

RECOVERY

(1187.5 Hz)

DATA

DECODER

SYNC

DETECT-2

SYNC

DETECT-1

OSC/DIVIDER

MEMORY CONTROL

CLK(4.332 MHz)

+5V

+5V

Vdda

Vssa

MPXIN

T2

T3 to T7

T1

CCB

DI

CE

CL

RAM

(24 BLOCK DATA)

ERROR CORRECTION

(SOFT DECISION)

SYNC/EC CONTROLLER

DO

XIN

XOUT

SYR

SYNC

RDS-ID

Vssd

Vddd

CIN

FLOUT

VREF

A12364

No. 5602-3/15

LC72722, 72722M, 72722PM

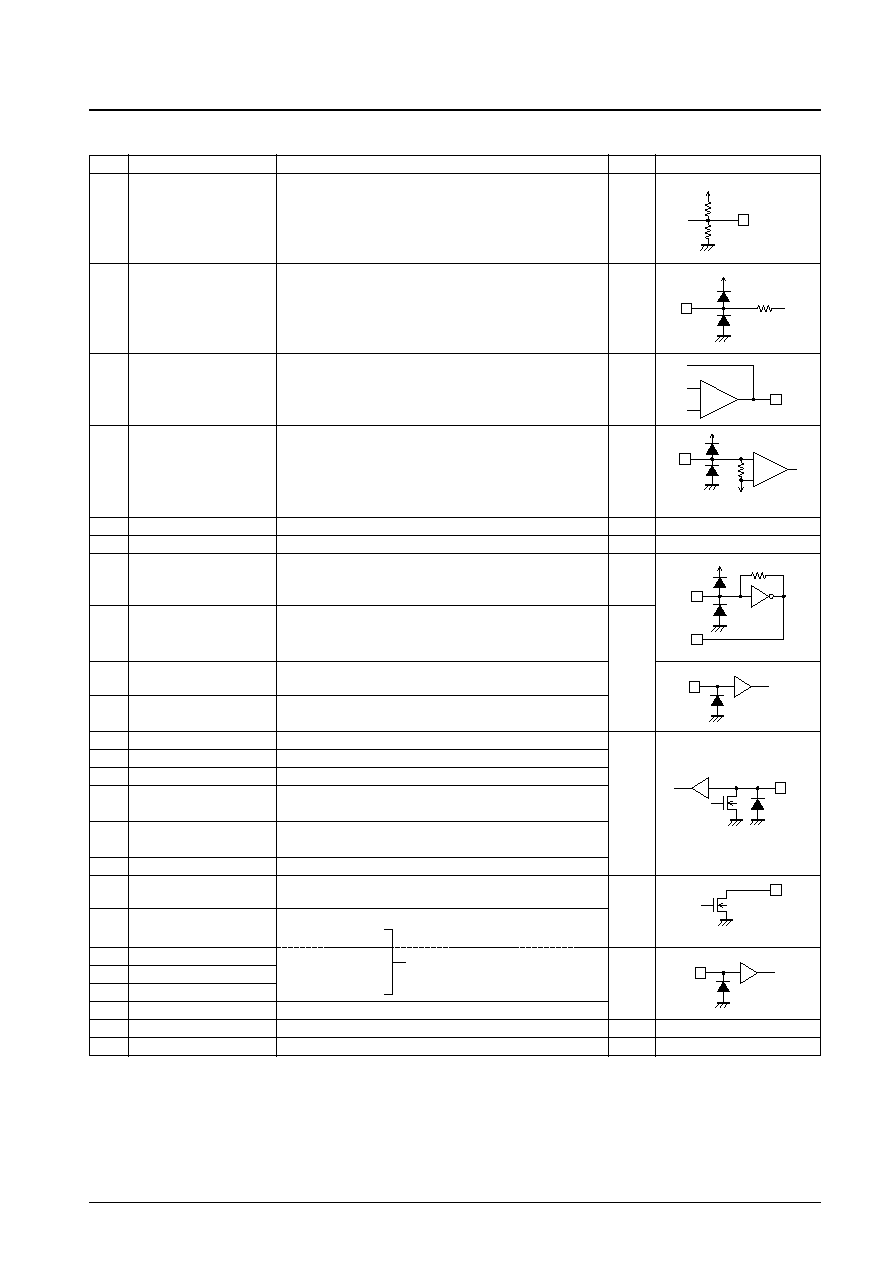

Pin Functions

Pin No.

Pin name

Function

I/O

Pin circuit

1

VREF

Reference voltage output (Vdda/2)

Output

2

MPXIN

Baseband (multiplexed) signal input

Input

5

FLOUT

Subcarrier output (filter output)

Output

6

CIN

Subcarrier input (comparator input)

Input

3

Vdda

Analog system power supply (+5 V)

--

--

4

Vssa

Analog system ground

--

--

12

XOUT

Crystal oscillator output (4.332/8.664 MHz)

Output

13

XIN

Crystal oscillator input (external reference signal input)

7

T1

Test input (This pin must always be connected to ground.)

Input

8

T2

Test input (standby control)

0: Normal operation, 1: Standby state (crystal oscillator stopped)

9

T3 (RDCL)

Test I/O (RDS clock output)

10

T4 (RDDA)

Test I/O (RDS data output)

11

T5 (RSFT)

Test I/O (soft-decision control data output)

16

T6 (ERROR/57K/TP/BE1)

Test I/O (error status output, regenerated carrier output,

I/O

*

TP output, error block count output)

17

T7 (CORREC/ARI-ID/TA/BE0)

Test I/O (Error correction status output, SK detection output,

TA output, error block count output)

18

SYNC

Block synchronization detection output

19

RDS-ID

RDS detection output

Output

20

DO

Data output

21

CL

Clock input

22

DI

Data input

Input

23

CE

Chip enable

24

SYR

Synchronization and RAM address reset (active high)

14

Vddd

Digital system power supply (+5 V)

--

--

15

Vssd

Digital system ground

--

--

Note:

*

Normally function as an output pin. Used as an I/O pin in test mode, which is not available to user applications.

Serial data interface (CCB)

Vdda

Vssa

A12365

Vdda

Vssa

A12366

A12367

≠

+

Vdda

VREF

Vssa

A12368

Vddd

Vssd

A12369

XOUT

XIN

A12370

Vssd

S

A12371

Vssd

A12372

Vssd

A12373

Vssd

S

No. 5602-4/15

LC72722, 72722M, 72722PM

Parameter

Symbol

Conditions

Ratings

Unit

Maximum supply voltage

V

DD

max

Vddd, Vdda: Vdda

Vddd +0.3 V

≠0.3 to +7.0

V

V

IN

1 max

CL, DI, CE, SYR, T1, T2, T3, T4, T5, T6, T7, SYNC

≠0.3 to +7.0

V

Maximum input voltage

V

IN

2 max

XIN

≠0.3 to Vddd +0.3

V

V

IN

3 max

MPXIN, CIN

≠0.3 to Vdda +0.3

V

V

O

1 max

DO, SYNC, RDS-ID, T3, T4, T5, T6, T7

≠0.3 to +7.0

V

Maximum output voltage

V

O

2 max

XOUT

≠0.3 to Vddd +0.3

V

V

O

3 max

FLOUT

≠0.3 to Vdda +0.3

V

I

O

1 max

DO, T3, T4, T5, T6, T7

6.0

mA

Maximum output current

I

O

2 max

XOUT, FLOUT

3.0

mA

I

O

3 max

SYNC, RDS-ID

20.0

mA

LC72722:DIP24S:

350

mW

Allowable power dissipation

Pd max

Ta

85∞C

LC72722M:MFP24S:

150

mW

LC72722PM:MFP24:

175

mW

Operating temperature

Topr

≠40 to +85

∞C

Storage temperature

Tstg

≠55 to +125

∞C

Specifications

Absolute Maximum Ratings

at Ta = 25∞C, Vssd = Vssa = 0 V

Parameter

Symbol

Conditions

Ratings

Unit

min

typ

max

Supply voltage

V

DD

1

Vddd, Vdda: Vddd = Vdda

4.5

5.0

5.5

V

V

DD

2

Vddd: Serial data hold voltage

2.0

V

Input high-level voltage

V

IH

CL, DI, CE, SYR, T1, T2

0.7 Vddd

6.5

V

Input low-level voltage

V

IL

CL, DI, CE, SYR, T1, T2

0

0.3 Vddd

V

Output voltage

V

O

DO, SYNC, RDS-ID, T3, T4, T5, T6, T7

6.5

V

V

IN

1

MPXIN : f = 57 ±2 kHz

50

mVrms

Input amplitude

V

IN

2

MPXIN : 100% modulation composite

100

mVrms

V

XIN

XIN

400

1500

mVrms

Guaranteed crystal oscillator frequencies

Xtal

XIN, XOUT : CI

120

(XS = 0)

4.332

MHz

XIN, XOUT : CI

70

(XS = 1)

8.664

MHz

Crystal oscillator frequency deviation

TXtal

XIN, XOUT : f

O

= 4.322 MHz, 8.664 MHz

±100

ppm

Data setup time

t

SU

DI, CL

0.75

µs

Data hold time

t

HD

DI, CL

0.75

µs

Clock low-level time

t

CL

CL

0.75

µs

Clock high-level time

t

CH

CL

0.75

µs

CE wait time

t

EL

CE, CL

0.75

µs

CE setup time

t

ES

CE, CL

0.75

µs

CE hold time

t

EH

CE, CL

0.75

µs

CE high-level time

t

CE

CE

20

ms

Data latch change time

t

LC

1.15

µs

t

DC

DO, CL: Differs depending on the value of the

0.46

µs

Data output time

pull-up resistor used.

t

DH

DO, CE: Differs depending on the value of the

0.46

µs

Allowable Operating Ranges

at Ta = ≠40 to +85∞C, Vssd = Vssa = 0 V

Parameter

Symbol

Conditions

Ratings

Unit

min

typ

max

Input resistance

Rmpxin

MPXIN≠Vssa : f = 57 kHz

43

k

Rcin

CIN≠Vssa : f = 57 kHz

100

k

Internal feedback resistance

Rf

XIN

1.0

M

Center frequency

fc

FLOUT

56.5

57.0

57.5

kHz

≠3 dB bandwidth

BW ≠ 3 dB FLOUT

2.5

3.0

3.5

kHz

Gain

Gain

MPXIN≠FLOOUT : f = 57 kHz

28

31

34

dB

Electrical Characteristics

at Ta = ≠40 to +85∞C, Vssd = Vssa = 0 V

Continued on next page.

No. 5602-5/15

LC72722, 72722M, 72722PM

Parameter

Symbol

Conditions

Ratings

Unit

min

typ

max

Att1

FLOUT :

f = ±7 kHz

30

dB

Stop band attenuation

Att2

FLOUT : f < 45 kHz, f > 70 kHz

40

dB

Att3

FLOUT : f < 20 kHz

50

dB

pull-up resistor used.Reference voltage output

Vref

VREF : Vdda = 5 V

2.5

V

Hysteresis

V

HIS

CL, DI, CE, SYR, T1, T2

0.1 Vddd

V

Output low-level voltage

V

OL

1

DO, T3, T4, T5, T6, T7 : I = 2 mA

0.4

V

V

OL

2

SYNC, RDS-ID : I = 8 mA

0.4

V

Input high-level current

I

IH

1

CL, DI, CE, SYR, T1, T2 : V

I

= 6.5 V

5.0

µA

I

IH

2

XIN : V

I

= Vddd

2.0

11

µA

Input low-level current

I

IL

1

CL, DI, CE, SYR, T1, T2 : V

I

= 0 V

5.0

µA

I

IL

2

XIN : V

I

= 0 V

2.0

11

µA

Output off leakage current

I

OFF

DO, SYNC, RDS-ID, T3, T4, T5, T6, T7 :

5.0

µA

V

O

= 6.5 V

Current drain

Idd

Vddd + Vdda

9

mA

Continued from preceding page.

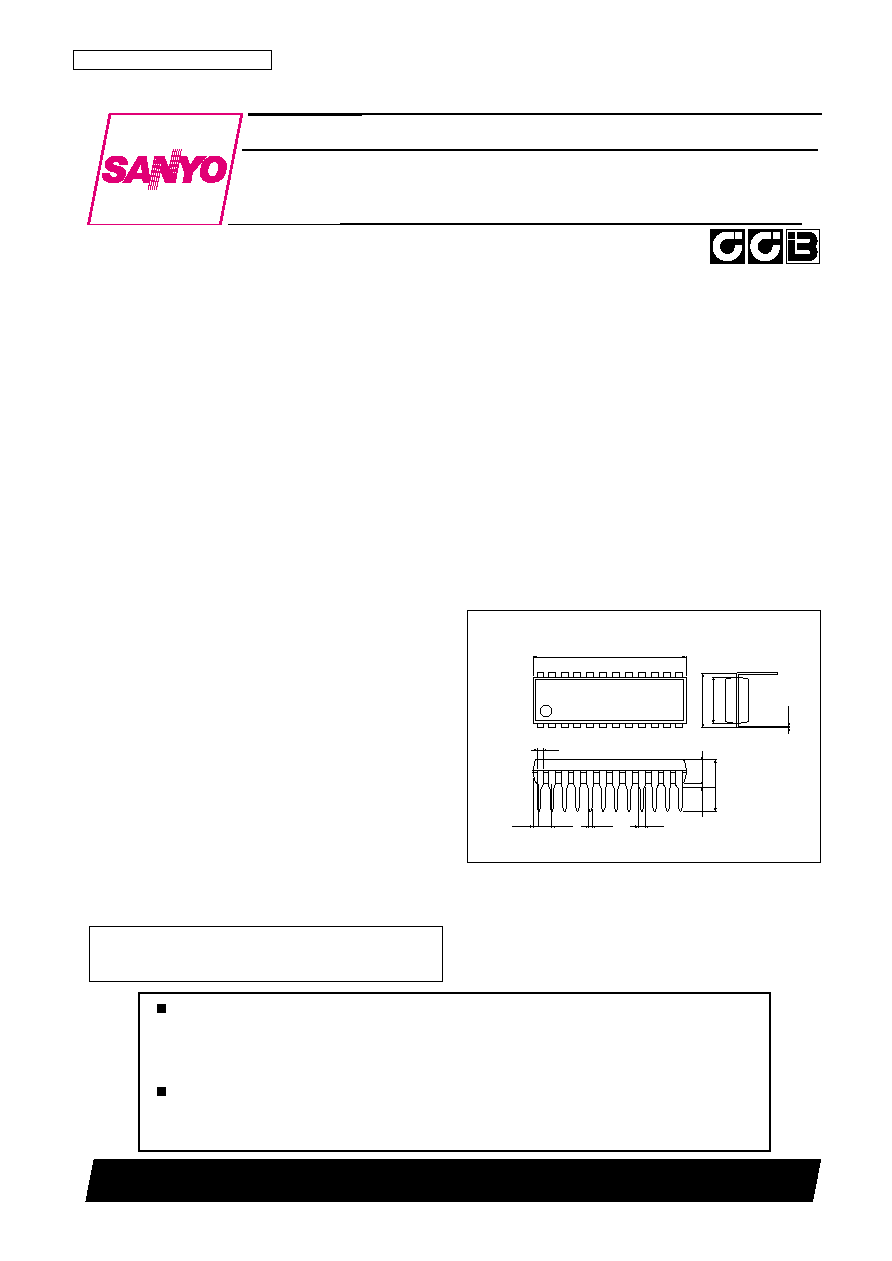

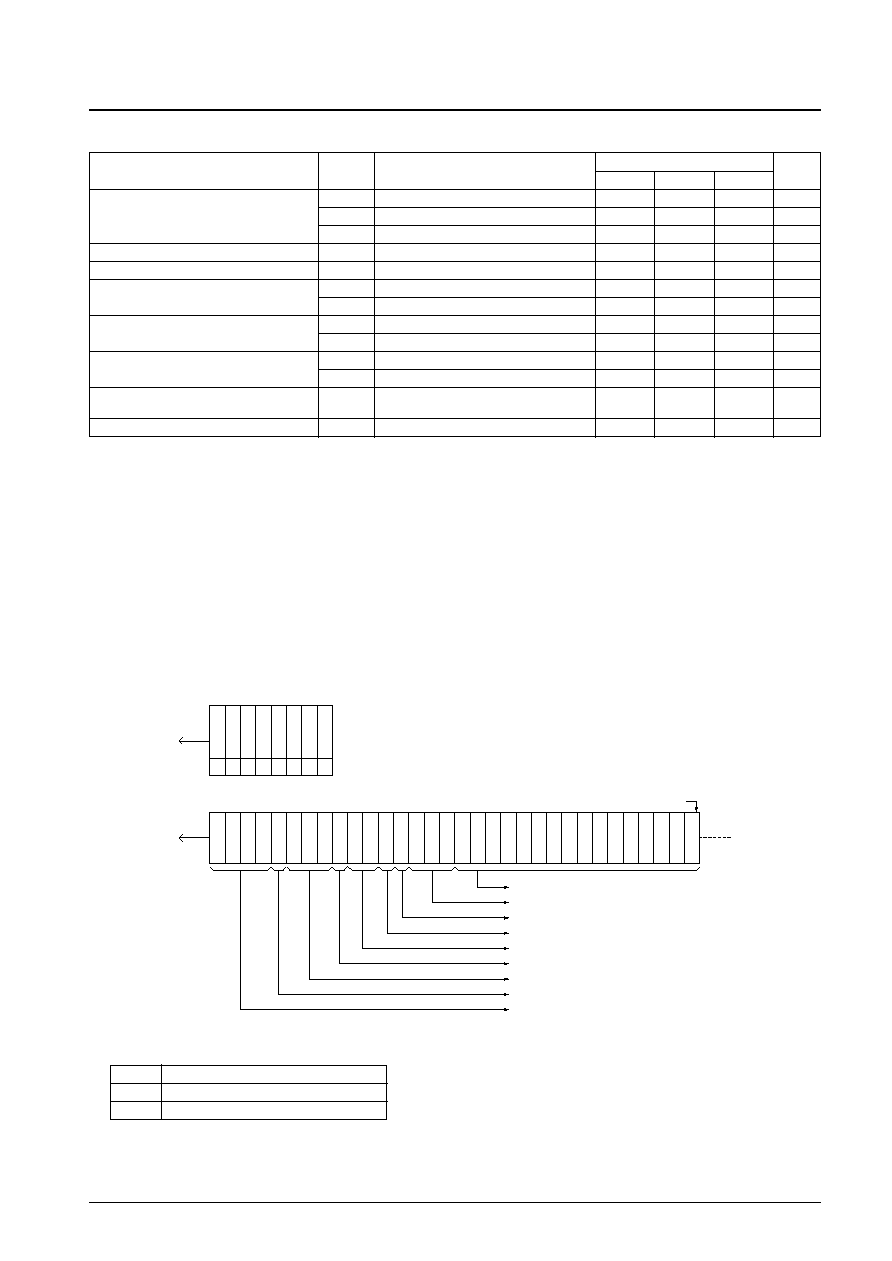

CCB Output Data Format

∑ Each block of output data consists of 32 bits (4 bytes), of which 2 bytes are RDS data and 2 bytes are flag data.

∑ Any number of 32-bit output data blocks can be output consecutively.

∑ When there is no data that can be read out in the internal memory, the system outputs blocks of all-zero data

consecutively.

∑ If data readout is interrupted, the next read operation starts with the 32-bit data block whose readout was interrupted.

However, if only the last bit remains to be read, it will not be possible to reread that whole block.

∑ The check bits (10 bits) are not output.

∑ The data valid/invalid decision is made by referencing the error information flags (E0 to E2) must not be referred to.

∑ When the first leading bits are not "1010", the read in data is invalid, and the read operation is cancelled.

1. Offset word detection flag (1 bit): OWD

OWD

Offset word detection

1

Detected

0

Not detected (protection function operating)

DI

DO

B

0

0

1

0

1

0

O

W

D

R

F

1

R

F

0

A

R

I

S

Y

C

D

1

5

D

1

4

D

1

3

D

1

2

D

1

1

D

1

0

B

2

E

2

E

1

E

0

D

9

D

8

D

7

D

6

D

5

D

4

D

3

D

2

D

1

D

0

B

1

B

0

R

E

0

1

1

0

1

1

0

B

1

B

2

B

3

A

0

A

1

A

2

A

3

CCB address 6C

Output data/first bit

Last bit

(8) RDS data

(7) Error information flags

(6) Synchronization established flag

(5) ARI (SK) detection flag

(4) RAM data remaining flag

(3) Consecutive RAM read out possible flag

(2) Offset word information flag

(1) Offset word detection flag

Fixed pattern (1010)