Ordering number : ENN6235

92299TH (OT) No. 6235-1/14

Overview

The LC75844M is a 1/4 duty general-purpose LCD driver

that can be used for frequency display in electronic tuners

under the control of a microcontroller. The LC75844M

can drive an LCD with up to 88 segments directly. The

LC75844M can also control up to 4 general-purpose

output ports. Since the LC75844M uses separate power

supply systems for the LCD drive block and the logic

block, the LCD driver block power-supply voltage can be

set to any voltage in the range 2.7 to 6.0 volts, regardless

of the logic block power-supply voltage.

Features

∑ Support for 1/4 duty 1/2 bias or 1/4 duty 1/3 bias drive

of up to 88 segments under serial data control.

∑ Serial data input supports CCB format communication

with the system controller.

∑ Serial data control of the power-saving mode based

backup function and all the segments forced off function

∑ Serial data control of switching between the segment

output port and the general-purpose output port

functions

∑ High generality, since display data is displayed directly

without decoder intervention.

∑ Independent V

LCD

for the LCD driver block (V

LCD

can

be set to any voltage in the range 2.7 to 6.0 volts,

regardless of the logic block power-supply voltage.)

∑ The INH pin can force the display to the off state.

∑ RC oscillator circuit

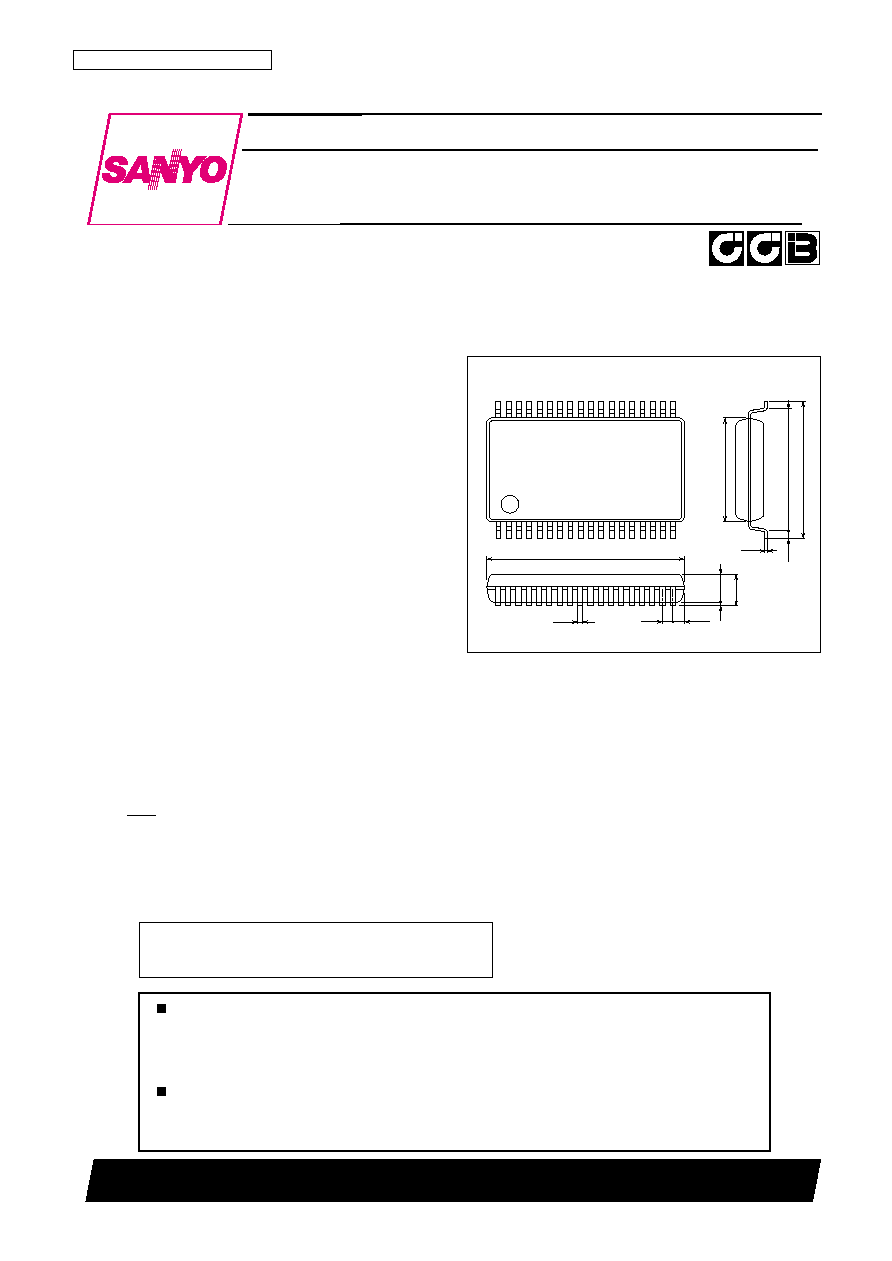

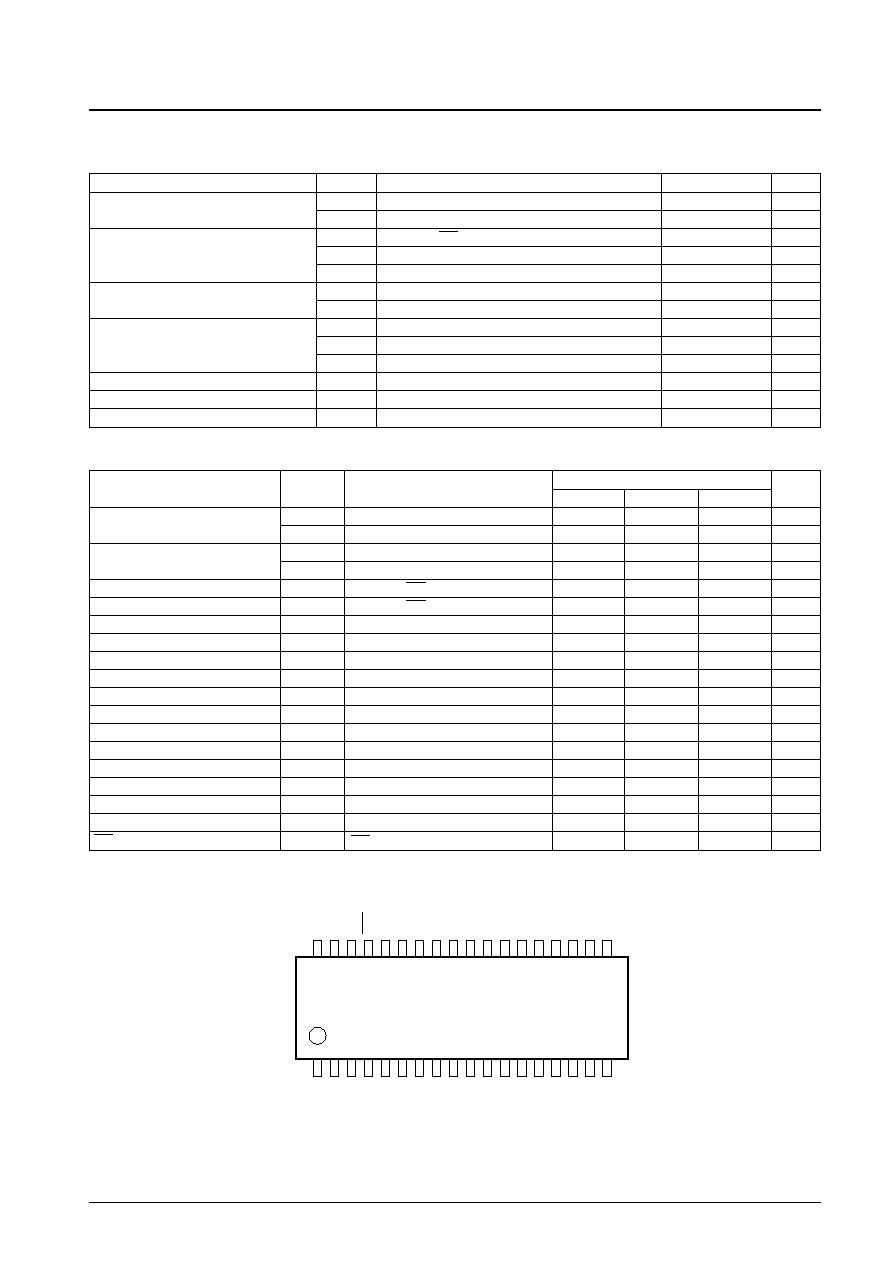

Package Dimensions

unit: mm

3204-MFP36S

0.15

15.3

1

18

36

19

0.85

0.35

0.8

2.5max

2.15

0.1

7.9

9.2

10.5

0.65

SANYO: MFP36S

[LC75844M]

LC75844M

SANYO Electric Co.,Ltd. Semiconductor Company

TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

1/4 Duty General-Purpose LCD Driver

CMOS IC

Any and all SANYO products described or contained herein do not have specifications that can handle

applications that require extremely high levels of reliability, such as life-support systems, aircraft's

control systems, or other applications whose failure can be reasonably expected to result in serious

physical and/or material damage. Consult with your SANYO representative nearest you before using

any SANYO products described or contained herein in such applications.

SANYO assumes no responsibility for equipment failures that result from using products at values that

exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other

parameters) listed in products specifications of any and all SANYO products described or contained

herein.

∑ CCB is a trademark of SANYO ELECTRIC CO., LTD.

∑ CCB is a SANYO's original bus format and all the

bus addresses are controlled by SANYO.

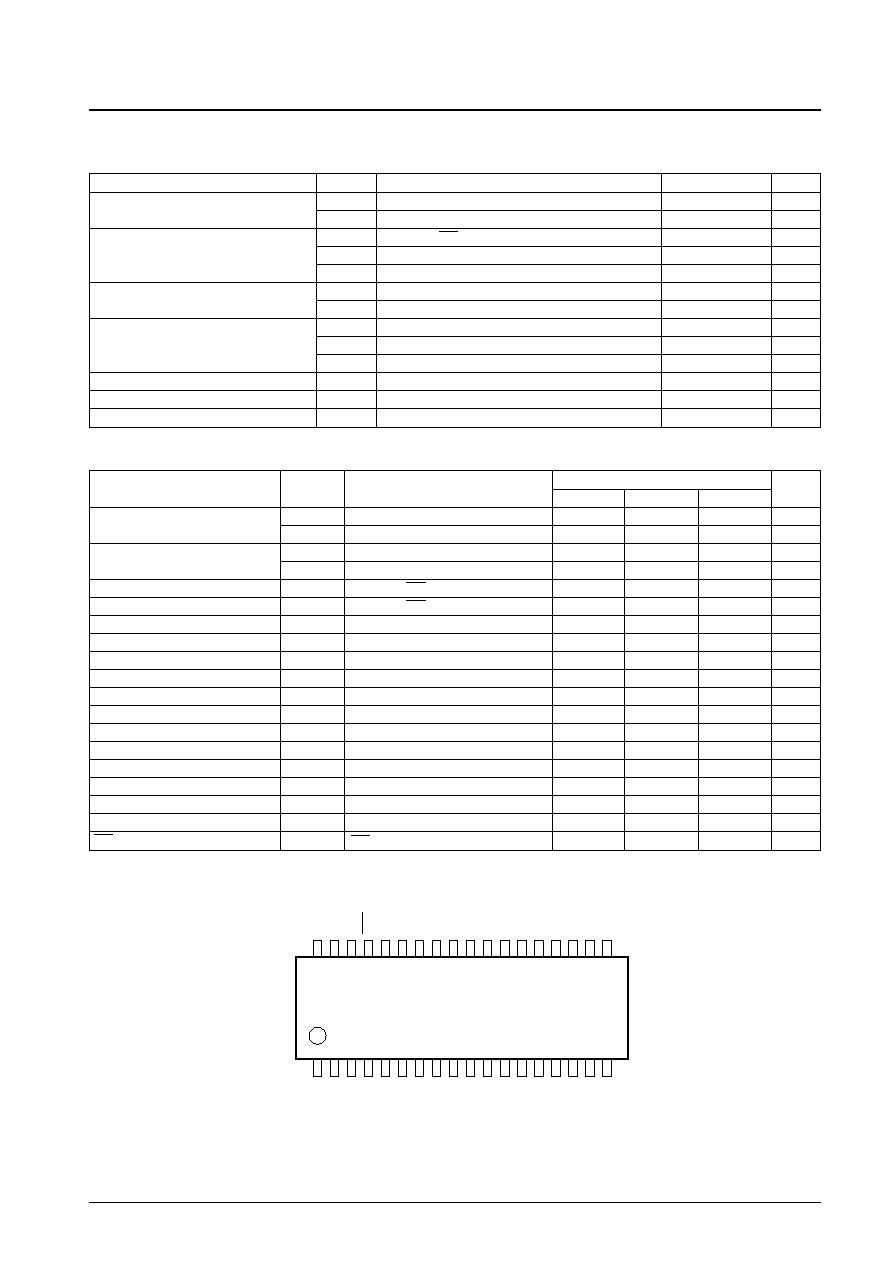

Pin Assignment

No. 6235-2/14

LC75844M

P1/S1

P2/S2

DI

P3/S3

CL

P4/S4

CE

S5

INH

S6

OSC

S7

V

SS

S8

V

LCD

2

S9

V

LCD

1

V

LCD

S10

V

DD

S11

COM4

S12

COM3

S13

COM2

S14

COM1

S15

S22

S16

S21

S17

S20

S18

S19

LC75844M

A12595

Specifications

Absolute Maximum Ratings

at Ta = 25∞C, V

SS

= 0 V

Parameter

Symbol

Conditions

Ratings

Unit

Maximum supply voltage

V

DD

max

V

DD

≠0.3 to +7.0

V

V

LCD

max

V

LCD

≠0.3 to +7.0

V

V

IN

1

CE, CL, DI, INH

≠0.3 to +7.0

V

Input voltage

V

IN

2

OSC

≠0.3 to V

DD

+ 0.3

V

V

IN

3

V

LCD

1, V

LCD

2

≠0.3 to V

LCD

+ 0.3

V

Output voltage

V

OUT

1

OSC

≠0.3 to V

DD

+ 0.3

V

V

OUT

2

S1 to S22, COM1 to COM4, P1 to P4

≠0.3 to V

LCD

+ 0.3

V

I

OUT

1

S1 to S22

300

µA

Output current

I

OUT

2

COM1 to COM4

3

mA

I

OUT

3

P1 to P4

5

mA

Allowable power dissipation

Pd max

Ta = 85∞C

100

mW

Operating temperature

Topr

≠40 to +85

∞C

Storage temperature

Tstg

≠55 to +125

∞C

Allowable Operating Ranges

at Ta = ≠40 to +85∞C, V

SS

= 0 V

Parameter

Symbol

Conditions

Ratings

Unit

min

typ

max

Supply voltage

V

DD

V

DD

2.7

6.0

V

V

LCD

V

LCD

2.7

6.0

V

Input voltage

V

LCD

1

V

LCD

1

2/3 V

LCD

V

LCD

V

V

LCD

2

V

LCD

2

1/3 V

LCD

V

LCD

V

Input high level voltage

V

IH

CE, CL, DI, INH

0.8 V

DD

6.0

V

Input low level voltage

V

IL

CE, CL, DI, INH

0

0.2 V

DD

V

Recommended external resistance

R

OSC

OSC

43

k

Recommended external capacitance

C

OSC

OSC

680

pF

Guaranteed oscillation range

f

OSC

OSC

25

50

100

kHz

Data setup time

t

ds

CL, DI: Figure 2

160

ns

Data hold time

t

dh

CL, DI: Figure 2

160

ns

CE wait time

t

cp

CE, CL: Figure 2

160

ns

CE setup time

t

cs

CE, CL: Figure 2

160

ns

CE hold time

t

ch

CE, CL: Figure 2

160

ns

High level clock pulse width

t

¯H

CL: Figure 2

160

ns

Low level clock pulse width

t

¯L

CL: Figure 2

160

ns

Rise time

t

r

CE, CL, DI: Figure 2

160

ns

Fall time

t

f

CE, CL, DI: Figure 2

160

ns

INH switching time

t

c

INH, CE: Figure 3

10

µs

Top view

No. 6235-3/14

LC75844M

Parameter

Symbol

Conditions

Ratings

Unit

min

typ

max

Hysteresis

V

H

CE, CL, DI, INH

0.1 V

DD

V

Input high level current

I

IH

CE, CL, DI, INH; V

I

= 6.0 V

5.0

µA

Input low level current

I

IL

CE, CL, DI, INH; V

I

= 0 V

≠5.0

µA

V

OH

1

S1 to S22; I

O

= ≠20 µA

V

LCD

≠ 0.9

V

Output high level voltage

V

OH

2

COM1 to COM4; I

O

= ≠100 µA

V

LCD

≠ 0.9

V

V

OH

3

P1 to P4; I

O

= ≠1 mA

V

LCD

≠ 0.9

V

V

OL

1

S1 to S22; I

O

= 20 µA

0.9

V

Output low level voltage

V

OL

2

COM1 to COM4; I

O

= 100 µA

0.9

V

V

OL

3

P1 to P4; I

O

= 1 mA

0.9

V

V

MID

1

COM1 to COM4; 1/2 bias,

1/2 V

LCD

≠ 0.9

1/2 V

LCD

+ 0.9

V

I

O

= ±100 µA

V

MID

2

S1 to S22; 1/3 bias,

2/3 V

LCD

≠ 0.9

2/3 V

LCD

+ 0.9

V

I

O

= ±20 µA

Output middle level voltage

*

1

V

MID

3

S1 to S22; 1/3 bias,

1/3 V

LCD

≠ 0.9

1/3 V

LCD

+ 0.9

V

I

O

= ±20 µA

V

MID

4

COM1 to COM4; 1/3 bias,

2/3 V

LCD

≠ 0.9

2/3 V

LCD

+ 0.9

V

I

O

= ±100 µA

V

MID

5

COM1 to COM4; 1/3 bias,

1/3 V

LCD

≠ 0.9

1/3 V

LCD

+ 0.9

V

I

O

= ±100 µA

Oscillator frequency

f

OSC

OSC; R

OSC

= 43 k

, C

OSC

= 680 pF

40

50

60

kHz

I

DD

1

V

DD

; power saving mode

5

µA

I

DD

2

V

DD

; V

DD

= 6.0 V, output open, fosc = 50 k Hz

230

460

µA

I

LCD

1

V

LCD

; power saving mode

5

µA

Current drain

I

LCD

2

V

LCD

; V

LCD

= 6.0 V, output open

100

200

µA

1/2 bias, fosc = 50 k Hz

I

LCD

3

V

LCD

; V

LCD

= 6.0 V, output open

60

120

µA

1/3 bias, fosc = 50 k Hz

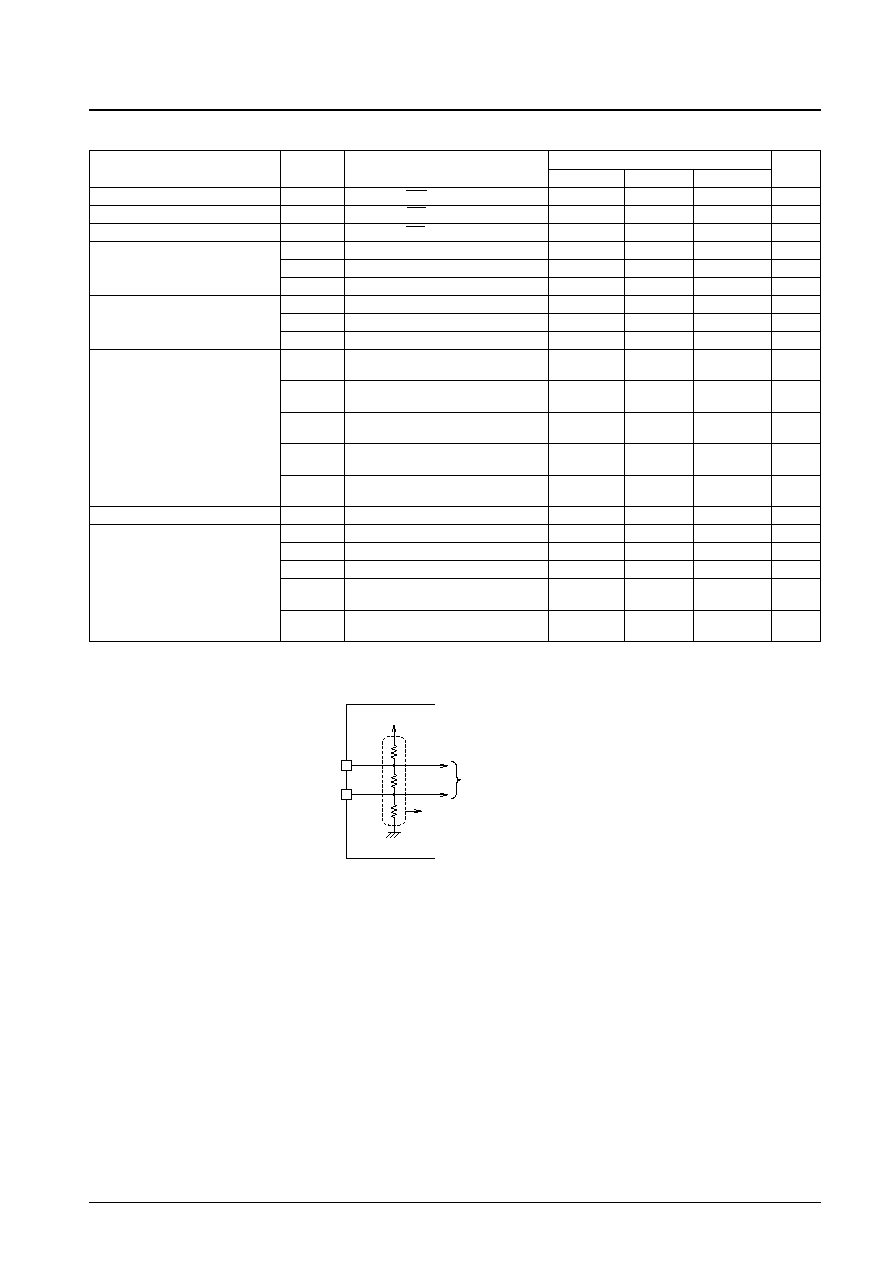

Electrical Characteristics

for the Allowable Operating Ranges

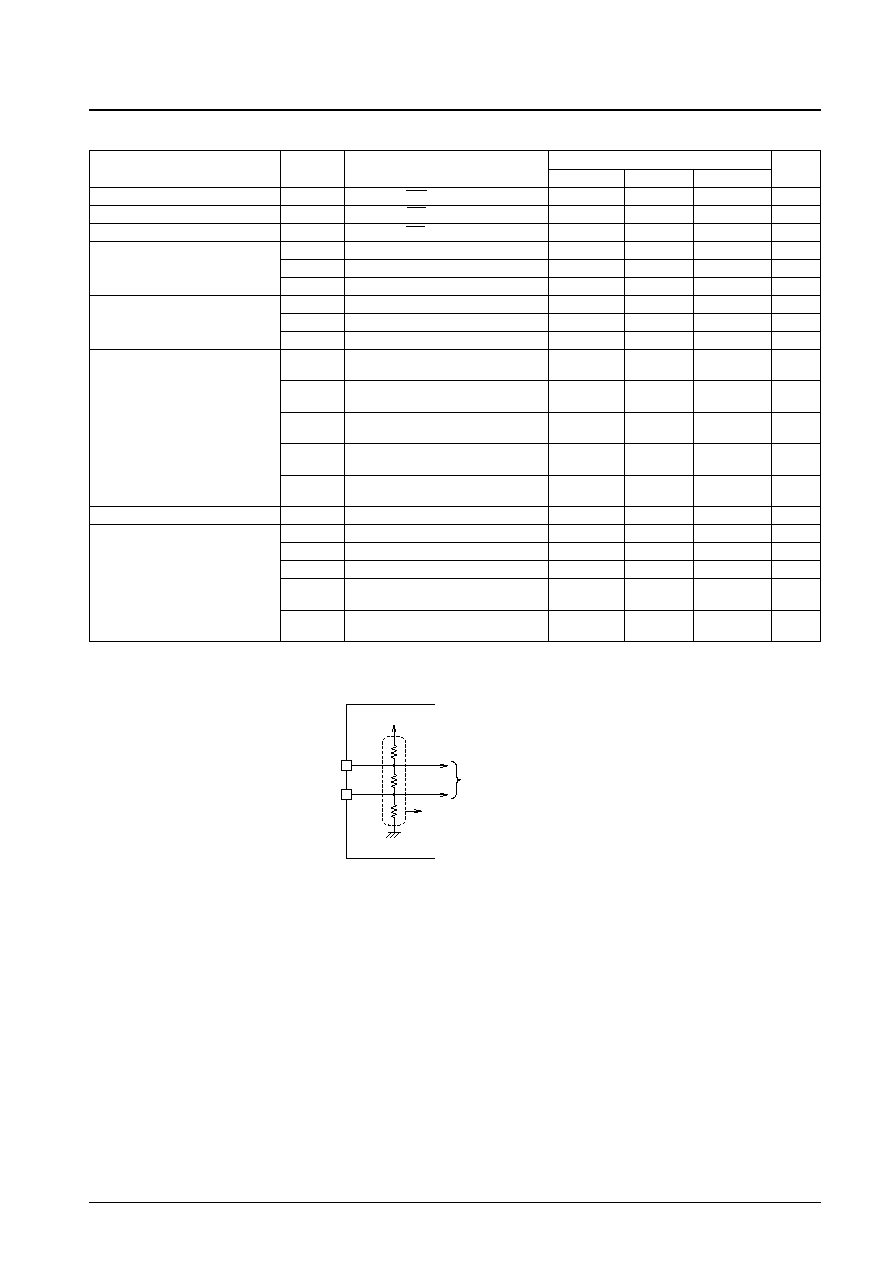

Note:

*

1 Excluding the bias voltage generation divider resistors built in the V

LCD

1 and V

LCD

2. (See Figure 1.)

VLCD1

VLCD2

VLCD

VSS

A06588

To the common segments driver

Except these resistors

s

Figure 1

Pin Functions

No. 6235-5/14

LC75844M

CE: Chip enable

CL:

Synchronization clock

DI:

Transfer data

H

--

S1/P1 to

S4/P4

S5 to S22

Pin

1 to 4

5 to 22

--

O

Open

Segment outputs for displaying the display data transferred by serial data input. The pins

S1/P1 to S4/P4 can be used as general-purpose output ports when so set up by the

control data.

COM1

COM2

COM3

COM4

23

24

25

26

--

O

Open

Common driver outputs.

The frame frequency f

O

is given by: f

O

= (f

OSC

/512) Hz.

OSC

32

CE

CL

DI

34

35

36

Serial data transfer inputs. These pins are

connected to the control microprocessor.

--

I/O

V

DD

I

GND

Oscillator connection

An oscillator circuit is formed by connecting an external resistor and capacitor to this pin.

V

LCD

1

29

--

I

Open

Used to apply the LCD drive 2/3 bias voltage externally. This pin must be connected to

V

LCD

2 when 1/2 bias drive is used.

V

LCD

2

30

--

I

Open

Used to apply the LCD drive 1/3 bias voltage externally. This pin must be connected to

V

LCD

1 when 1/2 bias drive is used.

V

DD

27

--

--

--

Logic block power supply. Provide a voltage in the range 2.7 to 6.0 V.

V

LCD

28

--

--

--

LCD driver block power supply. Provide a voltage in the range 2.7 to 6.0 V.

V

SS

31

--

--

--

Ground pin. Connect to ground.

INH

33

L

I

GND

Display off control input

∑

INH = low (V

SS

):

Off

S1/P1 to S4/P4 = Low

(These pins are forcibly set to the segment output port function and

fixed at the V

SS

level.)

S5 to S22 = Low (V

SS

),

COM1 to COM4 = Low (V

SS

)

∑

INH = high (V

DD

): On

Note that serial data transfers can be performed when the

display is forced off by this pin.

Active

I/O

Handling

when unused

Function

Pin No.

Serial Data Transfer Format

1. When CL is stopped at the low level

Note: DD ... Direction data

CE

CL

DI

A12600

0

0

1

0

0

0

1

0

B0 B1 B2 B3 A0 A1 A2 A3

D1

D2 D3

D37 D38 D39 D40 D41 D42 D43 D44 0

0

0

0

0

P0 P1 P2 DR SC BU

0

0

0

1

0

0

0

1

0

B0 B1 B2 B3 A0 A1 A2 A3

D45 D46 D47

D81 D82 D83 D84 D85 D86 D87 D88 0

0

0

0

0

0

0

0

0

0

0

1

CCB address

8 bits

CCB address

8 bits

Display data

44 bits

Display data

44 bits

Control data

11 bits

Fixed data

11 bits

DD

1 bit

DD

1 bit