| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: LC78625 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

SANYO Electric Co.,Ltd. Semiconductor Bussiness Headquarters

TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110 JAPAN

Overview

The LC78625E is a CMOS LSI that implements the signal

processing and servo control required by compact disc

players, laser discs, CD-V, CD-I and related products. The

LC78625E provides several types of signal processing,

including demodulation of the optical pickup EFM signal,

de-interleaving, error detection and correction, and digital

filters that can help reduce the cost of CD player units. It

also processes a rich set of servo system commands sent

from the control microprocessor. It also incorporates an

EFM-PLL circuit and a one-bit D/A converter.

This LSI is an improved version of the LC78620E. In

addition to supporting low-voltage operation, on/off

control of the de-emphasis function and use of the

bilingual function have been enabled in certain additional

modes.

Functions

∑ The LC78625E takes an HF signal as input, digitizes

(slices) that signal at a precise level, converts that signal

to an EFM signal, and generates a PLL clock with an

average frequency of 4.3218 MHz by comparing the

phases of that signal and an internal VCO.

∑ A precise reference clock and the necessary internal

timings are generated using an external 16.9344 MHz

crystal oscillator.

∑ Disc motor speed control using a frame phase difference

signal generated from the playback clock and the

reference clock

∑ Frame synchronization signal detection, protection, and

interpolation to assure stable data readout

∑ EFM signal demodulation and conversion to 8-bit

symbol data

∑ Subcode data separation from the EFM demodulated

signal and output of that data to an external

microprocessor

∑ Subcode Q signal output (LSB first) to a microprocessor

over the serial interface after performing a CRC error

check

∑ Demodulated EFM signal buffering in internal RAM to

handle up to ±4 frames of disc rotational jitter

∑ Demodulated EFM signal reordering in the prescribed

order for data unscrambling and de-interleaving

∑ Error detection, correction, and flag processing (error

correction scheme: dual C1 plus dual C2 correction)

∑ The LC78625E sets the C2 flags based on the C1 flags

and a C2 check, and then performs signal interpolation

or muting depending on the C2 flags. The interpolation

circuit uses a quadruple interpolation scheme. The

output value converges to the muting level when four or

more consecutive C2 flags occur.

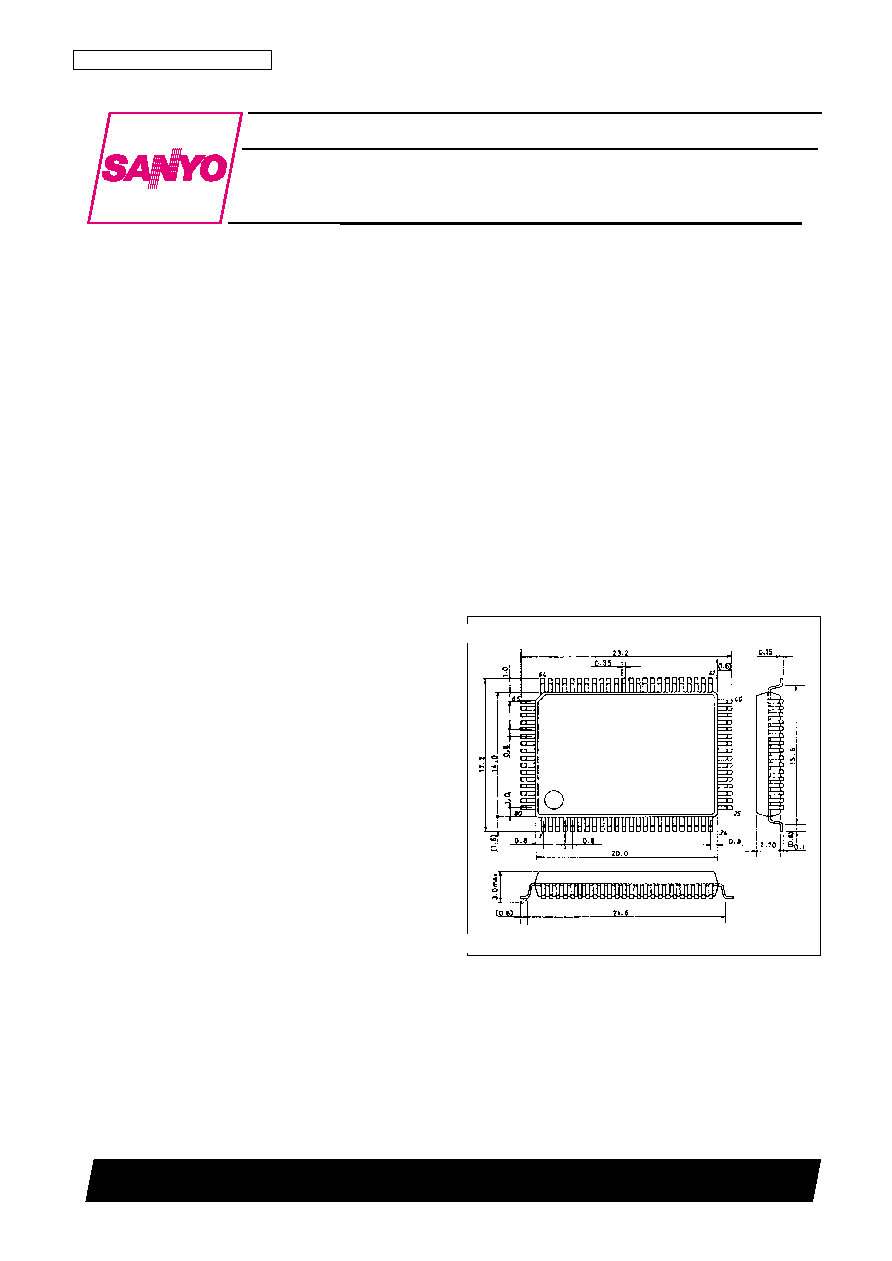

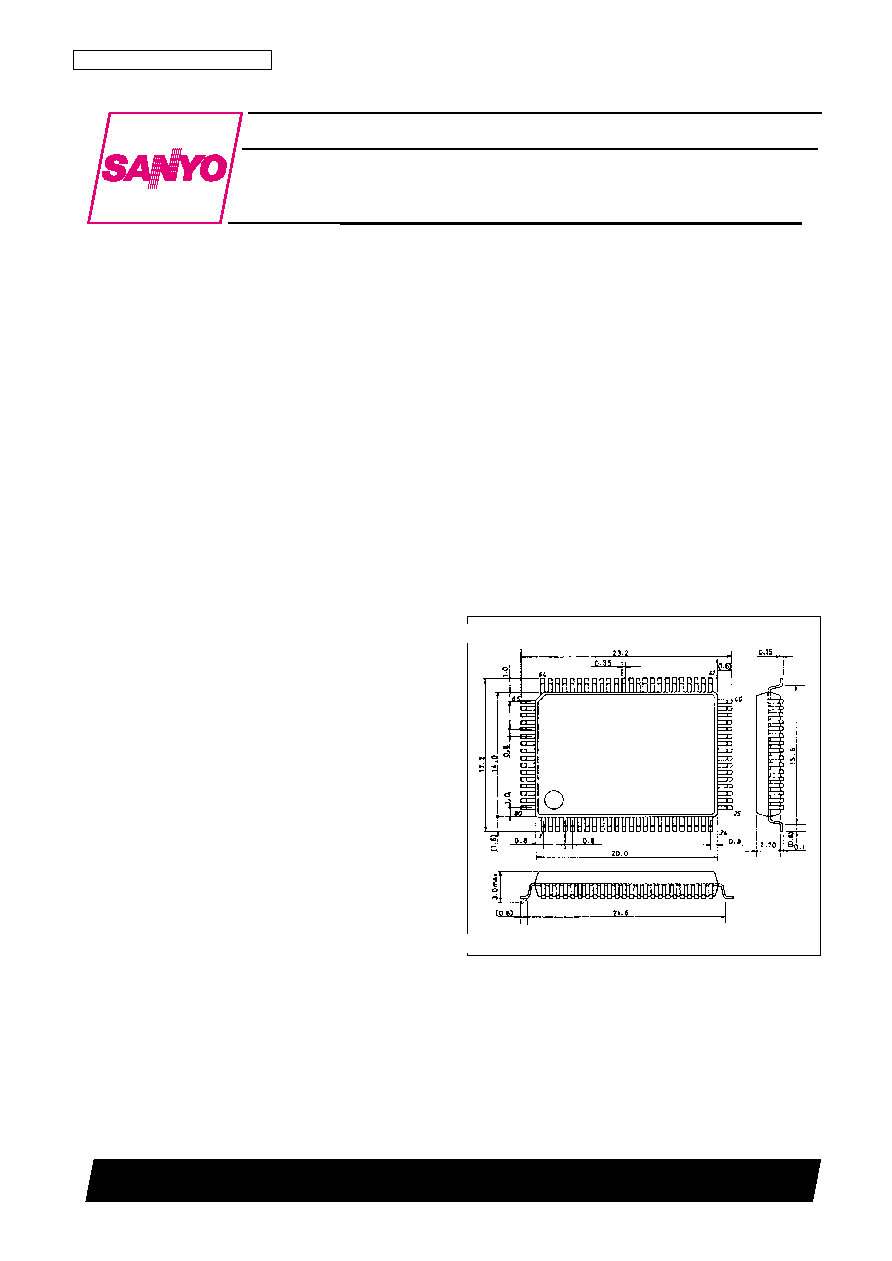

Package Dimensions

unit: mm

3174-QFP80E

SANYO: QFP80E

[LC78625E]

CMOS LSI

Ordering number : EN5502

22897HA (OT) No. 5502-1/35

LC78625E

SANYO Electric Co.,Ltd. Semiconductor Bussiness Headquarters

TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110 JAPAN

Compact Disc Player DSP

∑ Support for command input from a control microprocessor: commands include track jump, focus start, disk motor

start/stop, muting on/off and track count (8-bit serial input)

∑ Built-in digital output circuits.

∑ Arbitrary track counting to support high-speed data access

∑ D/A converter outputs with data continuity improved by 8

◊

oversampling digital filters. (These filters function as 4

◊

oversampling filters during double-speed playback.)

∑ Built-in

D/A converter implemented by a third-order noise shaper circuit (for PWM output)

∑ Built-in digital attenuator (8 bits - alpha, 239 steps)

∑ Built-in digital de-emphasis circuit that can be controlled externally in some modes

∑ Zero-cross muting

∑ Support for 2

◊

-speed dubbing

∑ Support for bilingual applications

∑ General-purpose I/O ports: 4 pins (when the antishock mode is turned off)

Features

∑ 5 V single-voltage power supply

∑ Low-voltage operation: Can be operated at 3.3 V ±10% (at normal playback speed)

∑ 80-pin QFP package

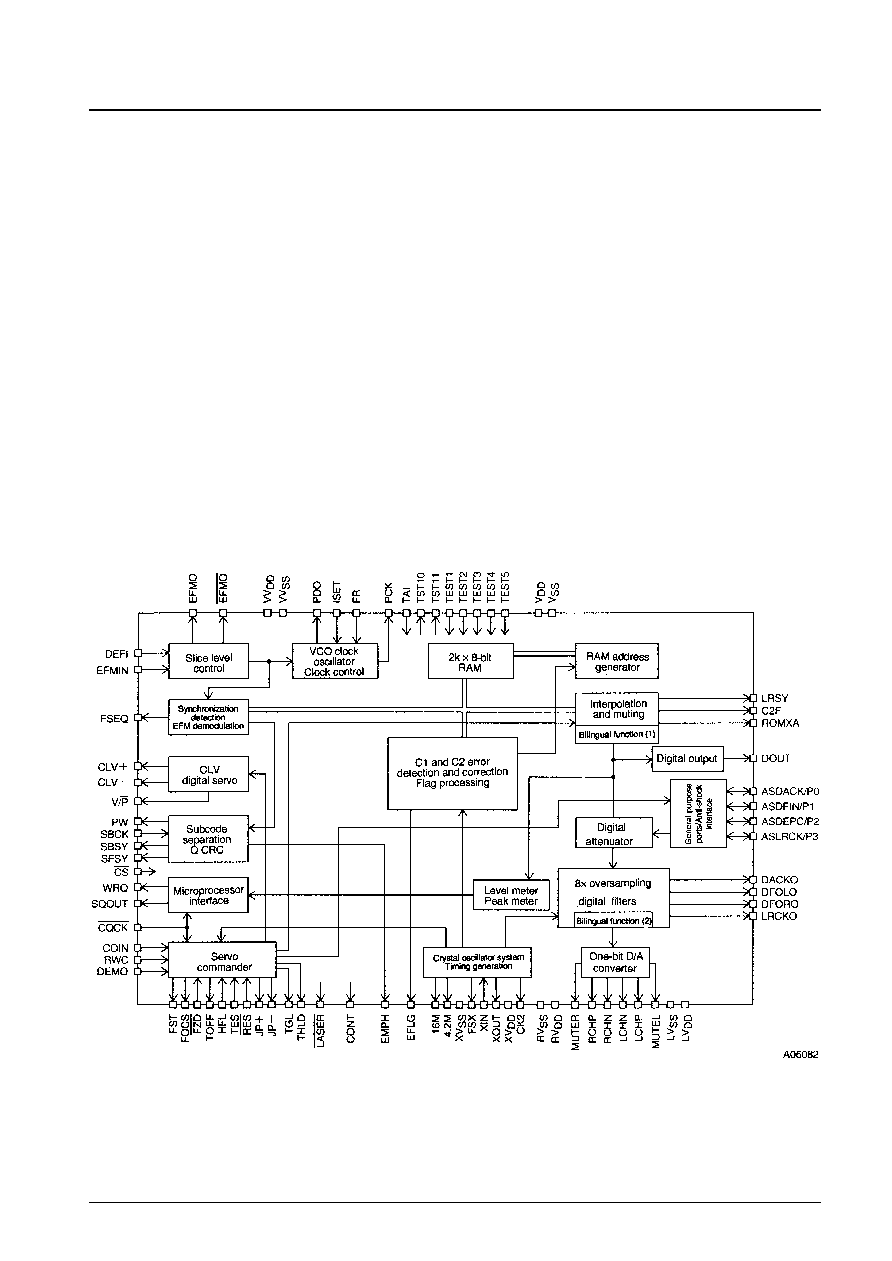

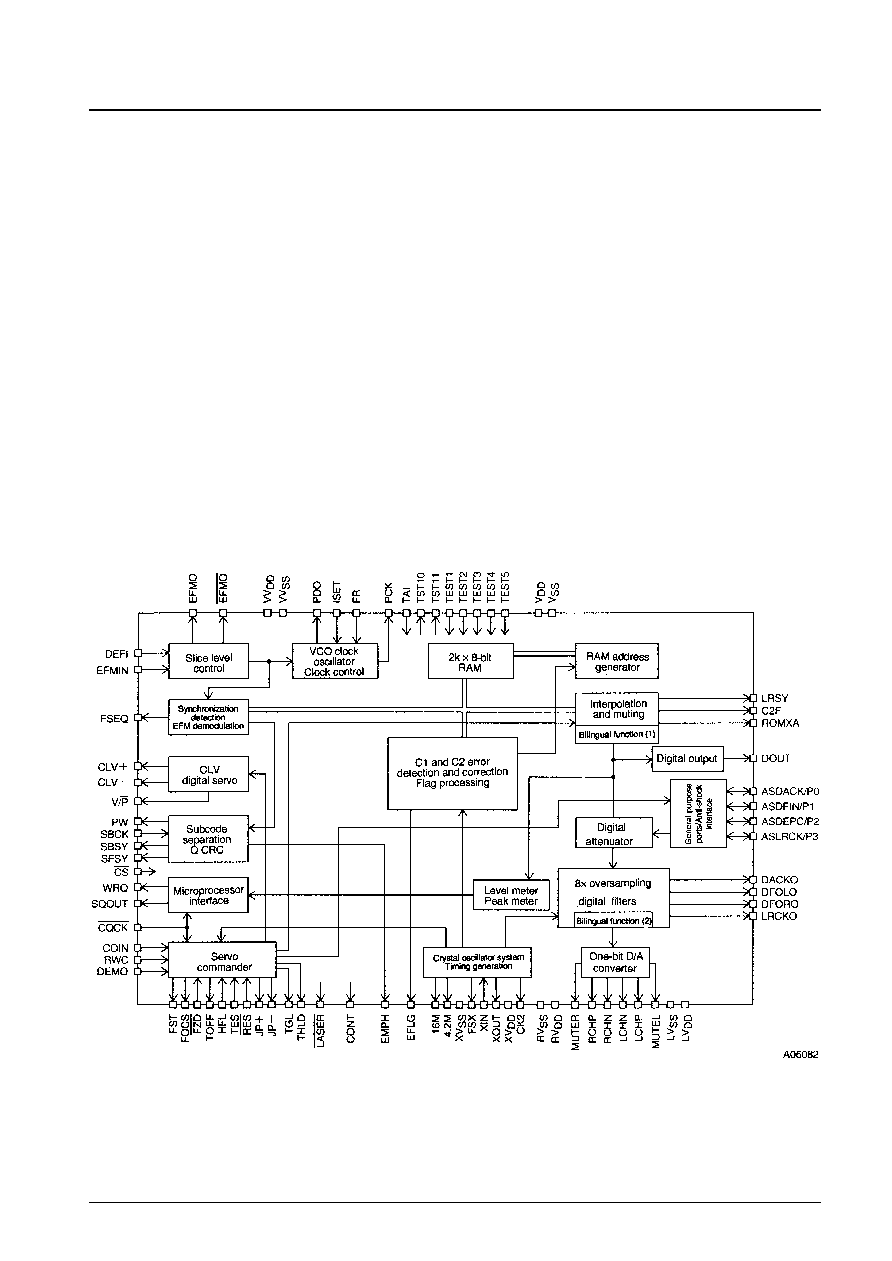

Equivalent Circuit Block Diagram

No. 5502-2/35

LC78625E

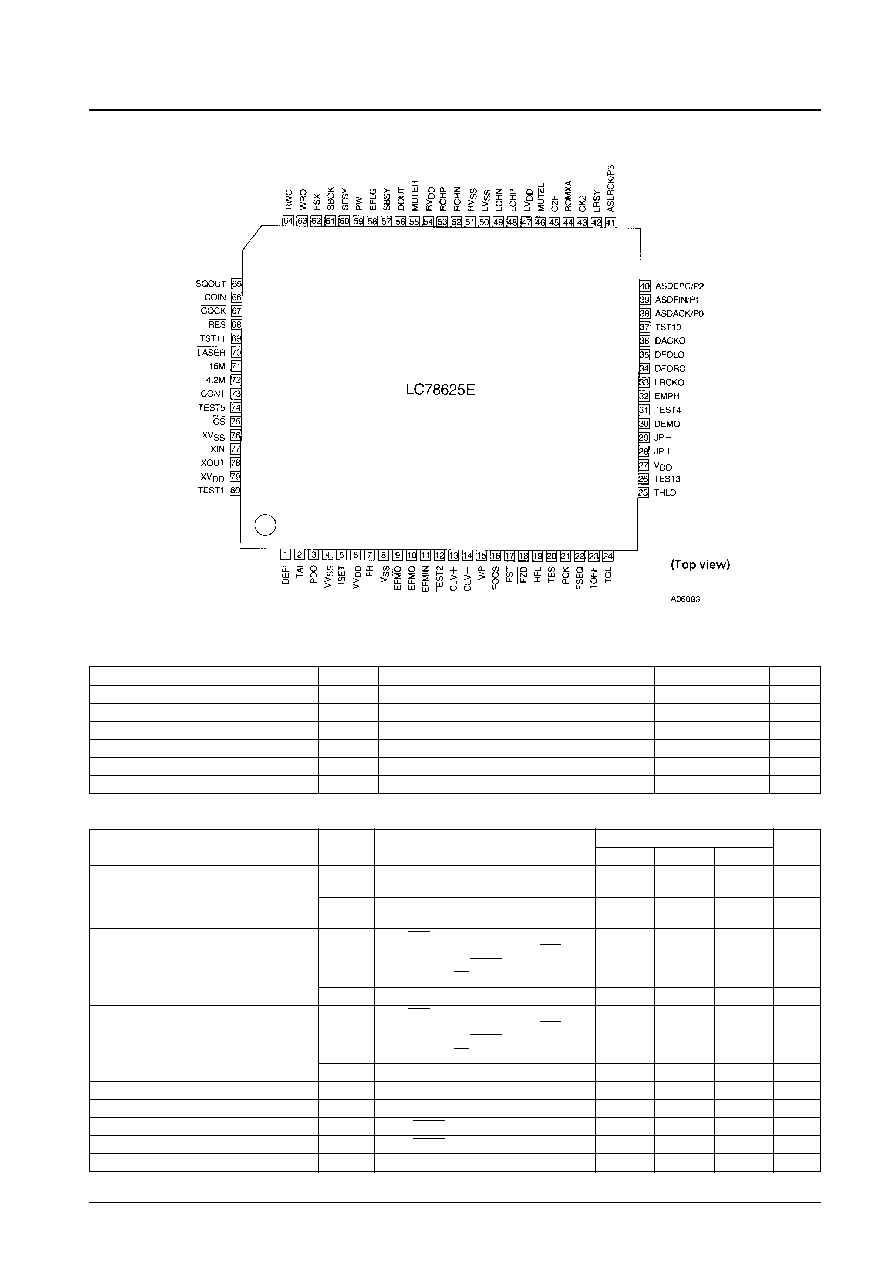

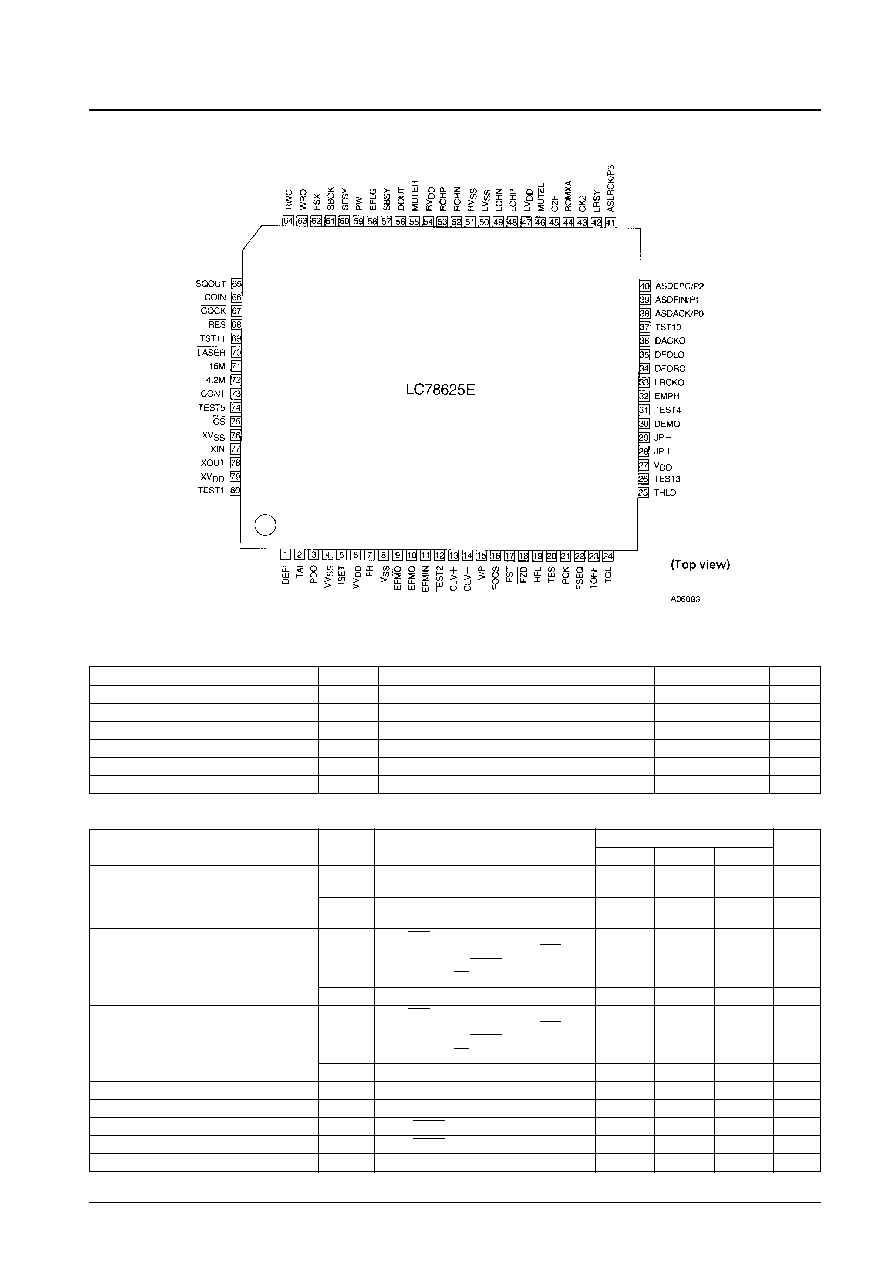

Pin Assignment

No. 5502-3/35

LC78625E

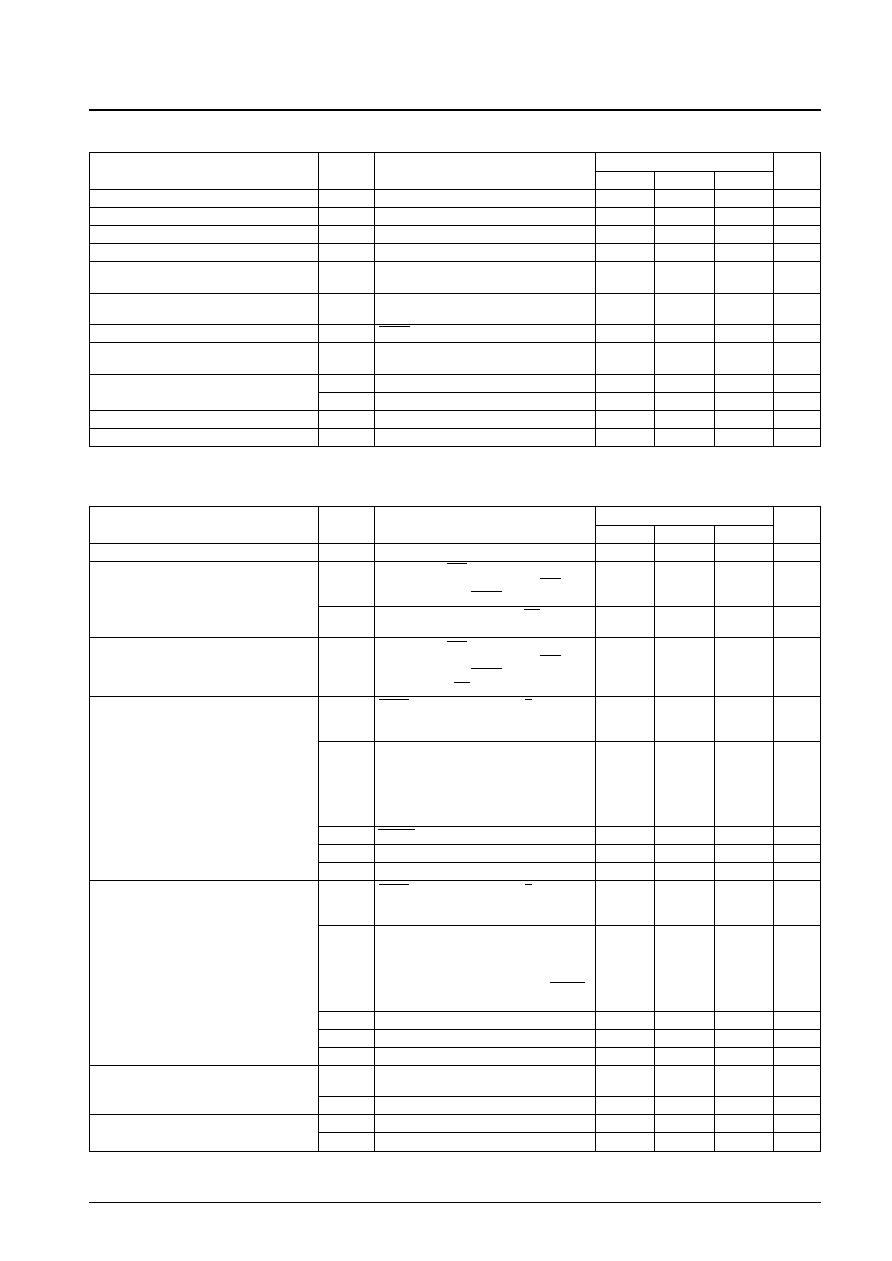

Parameter

Symbol

Conditions

Ratings

Unit

Maximum supply voltage

V

DD

max

V

SS

≠ 0.3 to +7.0

V

Maximum input voltage

V

IN

V

SS

≠ 0.3 to V

DD

+ 0.3

V

Maximum output voltage

V

OUT

V

SS

≠ 0.3 to V

DD

+ 0.3

V

Allowable power dissipation

Pd max

300

mW

Operating temperature

Topr

≠20 to +75

∞C

Storage temperature

Tstg

≠40 to +125

∞C

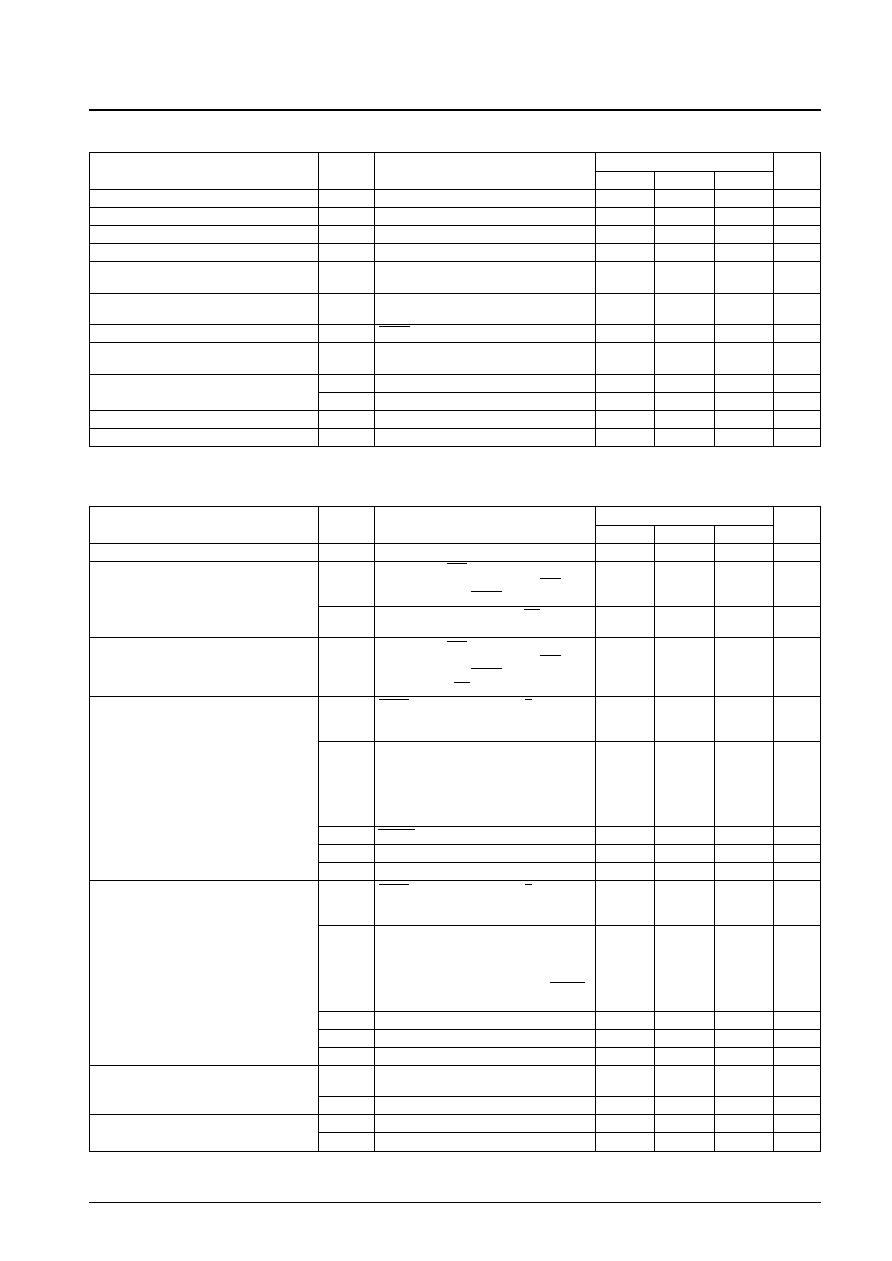

Specifications

Absolute Maximum Ratings

at Ta = 25∞C, V

SS

= 0 V

Parameter

Symbol

Conditions

Ratings

Unit

min

typ

max

V

DD

(1)

V

DD

, XV

DD

, LV

DD

, RV

DD

, VV

DD

:

3.0

5.5

V

Supply voltage

At normal playback speed

V

DD

(2)

V

DD

, XV

DD

, LV

DD

, RV

DD

, VV

DD

:

4.5

5.5

V

At 2

◊

playback speed

DEFI, FZD, ASDACK/P0, ASFIN/P1,

V

IH

(1)

ASDEPC/P2, ASLRCK/P3, COIN, RES, HFL,

0.7 V

DD

V

DD

V

Input high-level voltage

TES, SBCK, RWC, CQCK, TAI, TEST1 to

TEST5, DEMO, CS

V

IH

(2)

EFMIN

0.6 V

DD

V

DD

V

DEFI, FZD, ASDACK/P0, ASFIN/P1,

V

IL

(1)

ASDEPC/P2, ASLRCK/P3, COIN, RES, HFL,

0

0.3 V

DD

V

Input low-level voltage

TES, SBCK, RWC, CQCK, TAI, TEST1 to

TEST5, DEMO, CS

V

IL

(2)

EFMIN

0

0.4 V

DD

V

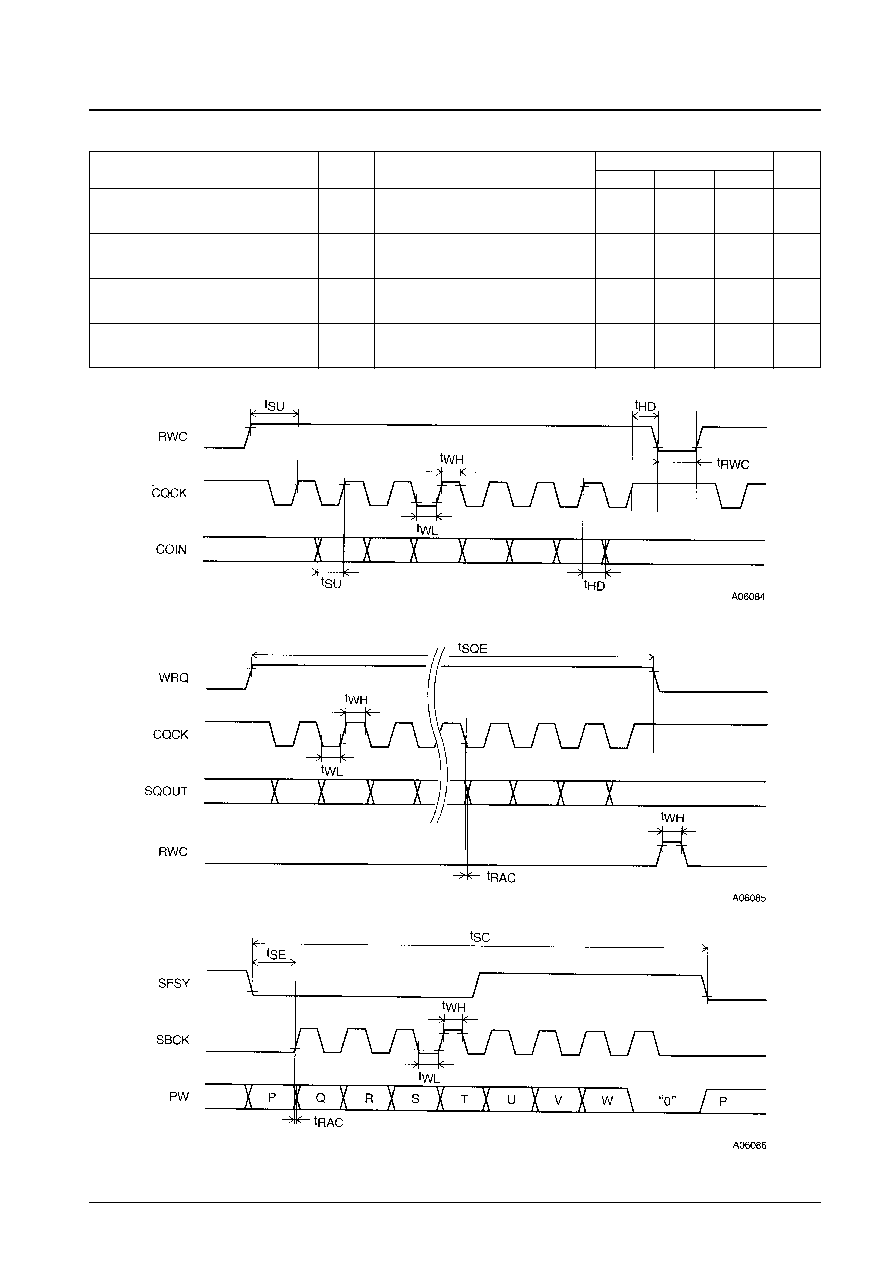

Data setup time

t

SU

COIN, RWC : Figure 1

400

ns

Data hold time

t

HD

COIN, RWC : Figure 1

400

ns

High-level clock pulse width

t

WH

SBCK, CQCK : Figuires 1, 2 and 3

400

ns

Low-level clock pulse width

t

WL

SBCK, CQCK : Figuires 1, 2 and 3

400

ns

Data read access time

t

RAC

SQOUT, PW : Figuires 2 and 3

0

400

ns

Allowable Operating Ranges

at Ta = 25∞C, V

SS

= 0 V

Continued on next page.

No. 5502-4/35

LC78625E

Continued from preceding page.

Note: For guaranteed operation, the VCO oscillator frequency range adjustment resistor FR must be a 1.20 k

±5.0% tolerance resistor.

Parameter

Symbol

Conditions

Ratings

Unit

min

typ

max

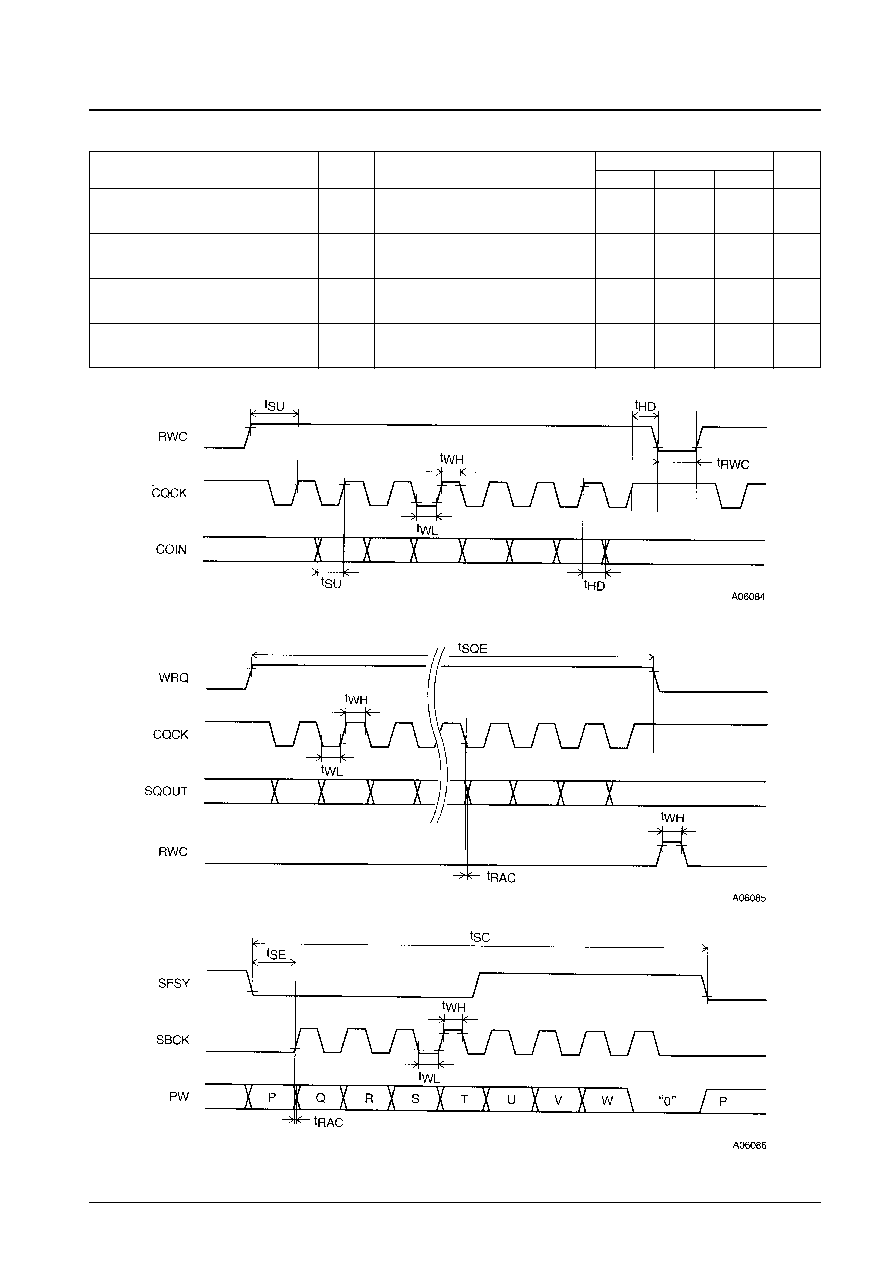

Command transfer time

t

RWC

RWC : Figure 1

1000

ns

Subcode Q read enable time

t

SQE

WRQ: Figure 2, with no RWC signal

11.2

ms

Subcode read cycle

t

SC

SFSY : Figure 3

136

µs

Subcode read enable time

t

SE

SFSY : Figure 3

400

ns

Port input data setup time

t

PSU

ASDACK/P0, ASFIN/P1, ASDEPC/P2,

400

ns

ASLRCK/P3, RWC : Figure 4

Port input data hold time

t

PHD

ASDACK/P0, ASFIN/P1, ASDEPC/P2,

400

ns

ASLRCK/P3, RWC : Figure 4

Port input clock setup time

t

RCQ

CQCK, RWC : Figure 4

100

ns

Port output data delay time

t

PDD

ASDACK/P0, ASFIN/P1, ASDEPC/P2,

1200

ns

ASLRCK/P3, RWC : Figure 5

Input level

V

IN

(1)

EFMIN

1.0

Vp-p

V

IN

(2)

XIN : Capacitor coupled input

1.0

Vp-p

Operating frequency range

f

OP

(1)

EFMIN

10

MHz

Crystal oscillator frequency

f

X

XIN, XOUT : In 16M mode

16.9344

MHz

Parameter

Symbol

Conditions

Ratings

Unit

min

typ

max

Current drain

I

DD

30

45

mA

DEFI, EFMIN, FZD, ASDACK/P0, ASFIN/P1,

I

IH

(1)

ASDEPC/P2, ASLRCK/P3, COIN, RES, HFL,

5

µA

Input high-level current

TES, SBCK, RWC, CQCK : V

IN

= 5 V

I

IH

(2)

TAI, TEST1 to TEST5, DEMO, CS :

25

75

µA

V

IN

= V

DD

= 5.5 V

DEFI, EFMIN, FZD, ASDACK/P0, ASFIN/P1,

Input low-level current

I

IL

ASDEPC/P2, ASLRCK/P3, COIN, RES, HFL,

≠5

µA

TES, SBCK, RWC, CQCK, TAI, TEST1 to

TEST5, DEMO, CS : V

IN

= 0 V

EFMO, EFMO, CLV+, CLV≠, V/P, FOCS,

V

OH

(1)

PCK, FSEQ, TOFF, TGL, THLD, JP+, JP≠,

4

V

EMPH, EFLG, FSX : I

OH

= ≠1 mA

MUTEL, MUTER, LRCKO, DFORO, DFOLO,

DACKO, TST10, ASDACK/P0, ASFIN/P1,

V

OH

(2)

ASDEPC/P2, ASLRCK/P3, LRSY, CK2,

4

V

Output high-level voltage

ROMXA, C2F, SBSY, PW, SFSY, WRQ,

SQOUT, TST11, 16M, 4.2M, CONT :

I

OH

= ≠0.5 mA

V

OH

(3)

LASER : I

OH

= ≠1 mA

4.6

V

V

OH

(4)

DOUT : I

OH

= ≠12 mA

4.5

V

V

OH

(5)

LCHP, RCHP, LCHN, RCHN : I

OH

= ≠1 mA

3.0

4.5

V

EFMO, EFMO, CLV+, CLV≠, V/P, FOCS,

V

OL

(1)

PCK, FSEQ, TOFF, TGL, THLD, JP+, JP≠,

1

V

EMPH, EFLG, FSX : I

OL

= 1 mA

MUTEL, MUTER, LRCKO, DFORO, DFOLO,

DACKO, TST10, ASDACK/P0, ASFIN/P1,

V

OL

(2)

ASDEPC/P2, ASLRCK/P3, LRSY, CK2,

0.4

V

Output low-level voltage

ROMXA, C2F, SBSY, PW, SFSY, WRQ,

SQOUT, TST11, 16M, 4.2M, CONT, LASER :

I

OL

= 2 mA

V

OL

(3)

DOUT : I

OL

= 12 mA

0.5

V

V

OL

(4)

FST : I

OL

= 5 mA

0.75

V

V

OL

(5)

LCHP, RCHP, LCHN, RCHN : I

OL

= 1 mA

0.5

2.0

V

I

OFF

(1)

PDO, CLV+, CLV≠, JP+, JP≠, FST :

5

µA

Output off leakage current

V

OUT

= 5 V

I

OFF

(2)

PDO, CLV+, CLV≠, JP+, JP≠ : V

OUT

= 0 V

≠5

µA

Charge pump output current

I

PDOH

PDO : RISET = 68 k

100

125

150

µA

I

PDOL

PDO : RISET = 68 k

≠150

≠125

≠100

µA

Electrical Characteristics

at Ta = 25∞C, V

DD

= 5 V, V

SS

= 0 V

No. 5502-5/35

LC78625E

Parameter

Symbol

Conditions

Ratings

Unit

min

typ

max

LCHP, RCHP, LCHN, RCHN;

Total harmonic distortion

THD + N

1 kHz: 0 dB data input, using the 20 kHz

0.008

0.0010

%

low-pass filter (AD725D built in)

LCHP, RCHP, LCHN, RCHN;

Dynamic range

DR

1 kHz: ≠60 dB data input, using the 20 kHz

84

88

dB

low-pass filter and the A filter (AD725D built in)

LCHP, RCHP, LCHN, RCHN;

Signal-to-noise ratio

S/N

1 kHz: 0 dB data input, using the 20 kHz

98

100

dB

low-pass filter and the A filter (AD725D built in)

LCHP, RCHP, LCHN, RCHN;

Crosstalk

CT

1 kHz: 0 dB data input, using the 20 kHz

96

98

dB

low-pass filter (AD725D built in)

One-Bit D/A Converter Analog Characteristics

at Ta = 25∞C, V

DD

= LV

DD

= RV

DD

= 5 V, V

SS

= LV

SS

= RV

SS

= 0 V

Figure 1 Command Input

Figure 2 Subcode Q Output

Figure 3 Subcode Output

Note: Measured with the normal-speed playback mode digital attenuator in the Sanyo one-bit D/A converter block reference circuit.