LH28F016SU

1

16M (1M ◊ 16, 2M ◊ 8) Flash Memory

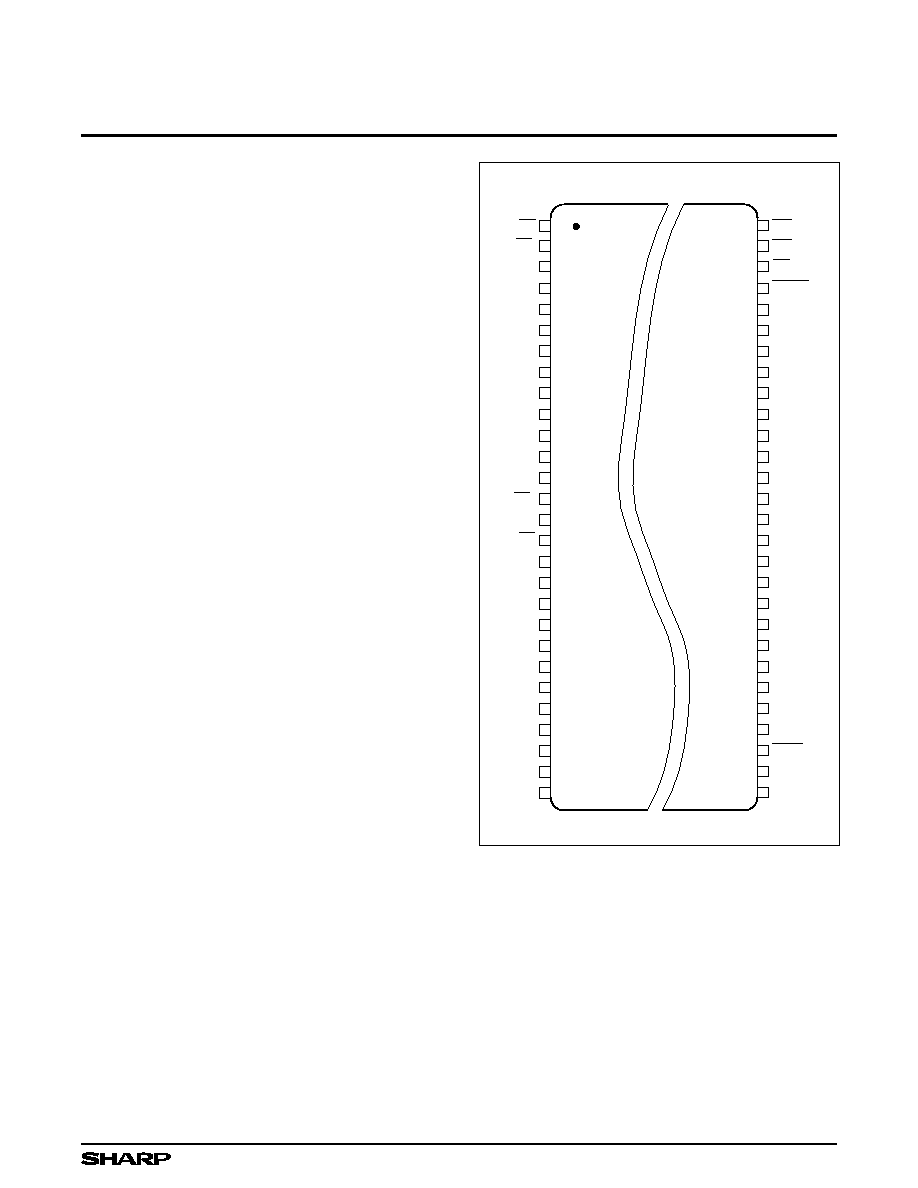

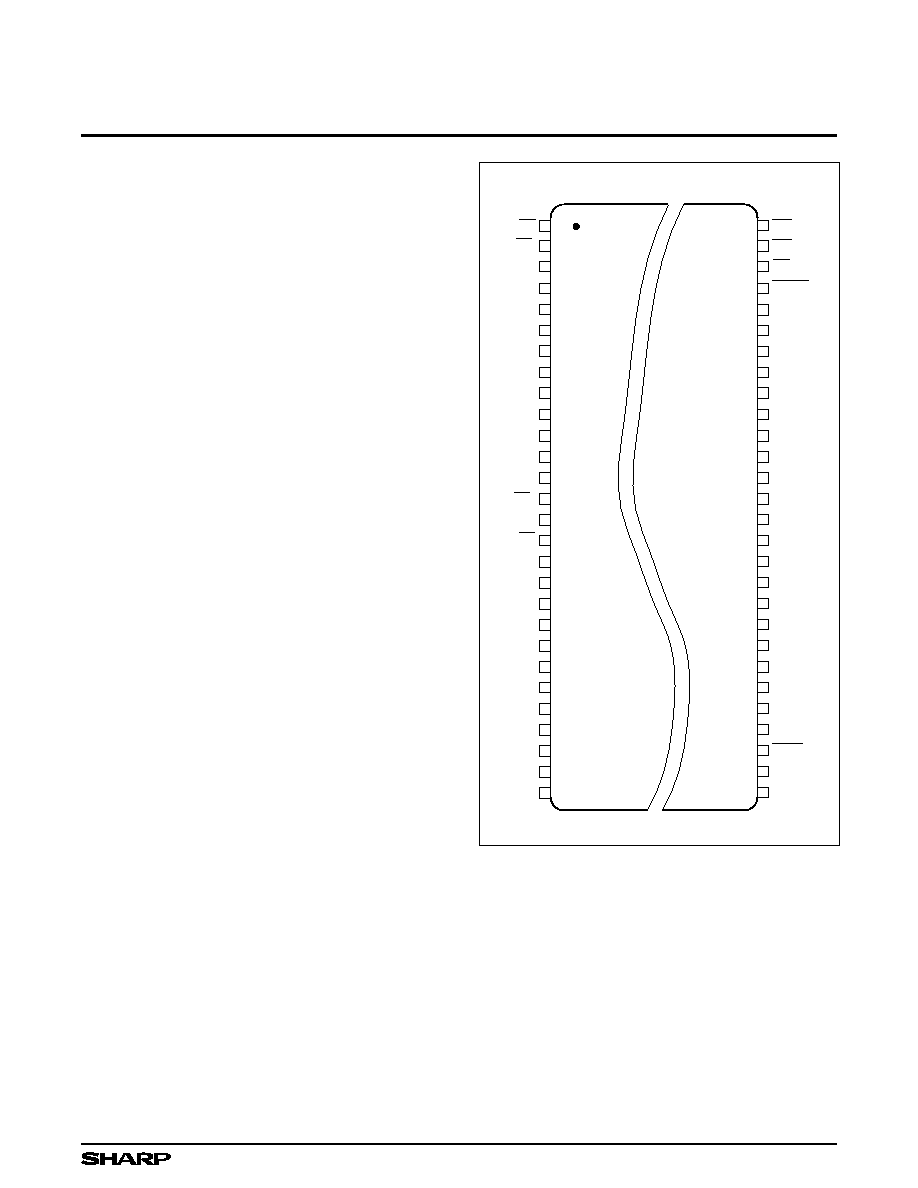

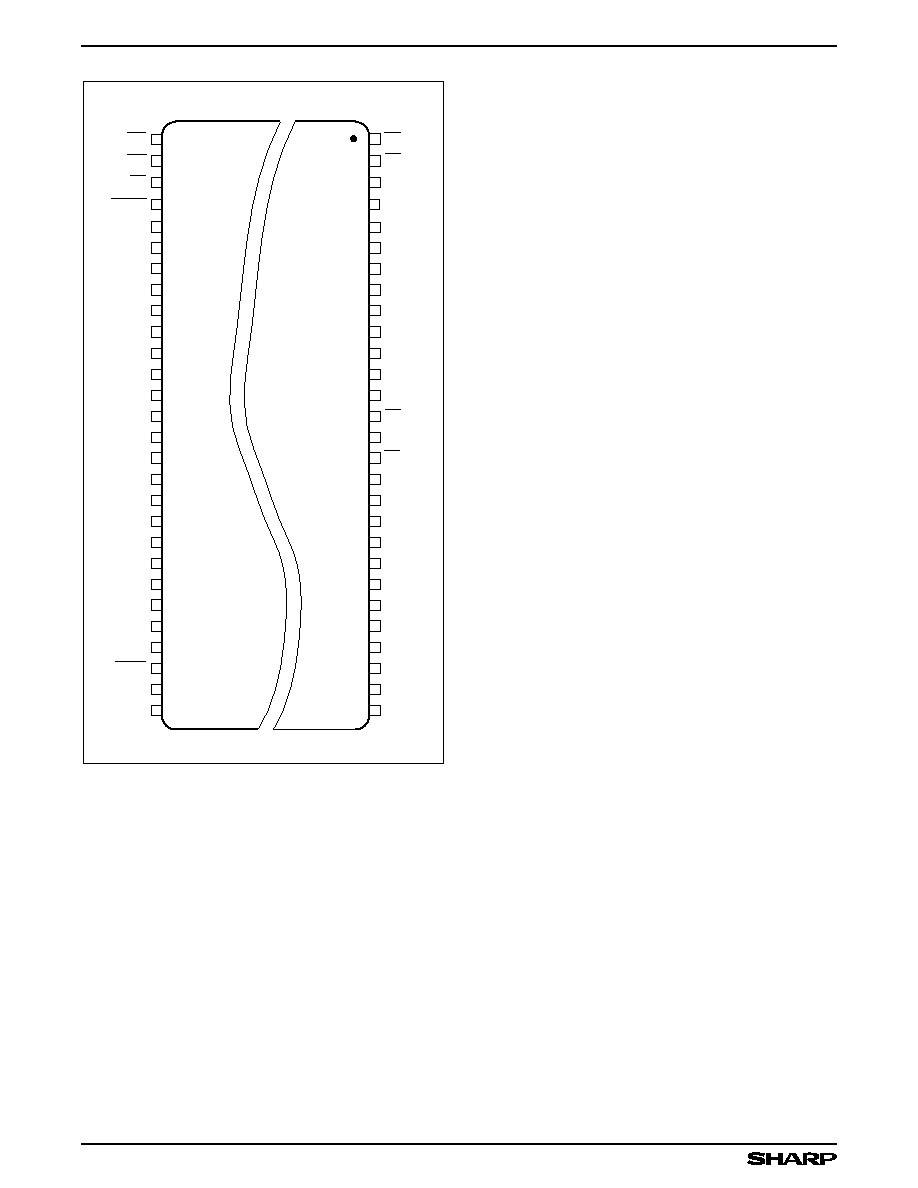

Figure 1. TSOP Configuration

FEATURES

∑

User-Configurable x8 or x16 Operation

∑

User-Selectable 3.3 V or 5 V V

CC

∑

70 ns Maximum Access Time

∑

0.32 MB/sec Write Transfer Rate

∑

100,000 Erase Cycles per Block

∑

32 Independently Lockable Blocks

∑

5 V Write/Erase Operation (5 V V

PP

)

≠ No Requirement for DC/DC Converter

to Write/Erase

∑

Minimum 2.7 V Read capability

≠ 160 ns Maximum Access Time

(V

CC

= 2.7 V)

∑

Revolutionary Architecture

≠ Pipelined Command Execution

≠ Write During Erase

≠ Command Superset of

Sharp LH28F008SA

∑

5 µA (Typ.) I

CC

in CMOS Standby

∑

1 µA (Typ.) Deep Power-Down

∑

State-of-the-Art 0.55 µm ETOXTM

Flash Technology

∑

56-Pin, 1.2 mm ◊ 14 mm ◊ 20 mm

TSOP (Type I) Package

28F016SUT-1

TOP VIEW

56-PIN TSOP

2

3

4

5

8

9

A

16

A

19

A

20

53

52

51

50

49

48

45

42

NC

6

7

A

17

A

18

47

46

RY/BY

DQ

15

DQ

14

GND

GND

10

11

12

55

54

OE

V

CC

13

44

DQ

4

43

V

CC

A

15

DQ

7

14

15

16

17

18

19

20

39

36

41

40

38

37

DQ

3

DQ

10

DQ

2

V

CC

A

10

A

9

A

11

V

PP

RP

CE

0

A

8

DQ

9

WE

DQ

6

DQ

13

DQ

11

56

1

CE

1

3/5

WP

21

22

23

24

25

26

27

28

A

4

A

3

A

5

A

7

A

6

GND

A

2

A

1

34

DQ

8

35

DQ

1

31

33

32

30

29

A

0

BYTE

NC

NC

DQ

0

A

14

A

13

A

12

DQ

5

DQ

12

LH28F016SU

16M (1M ◊ 16, 2M ◊ 8) Flash Memory

2

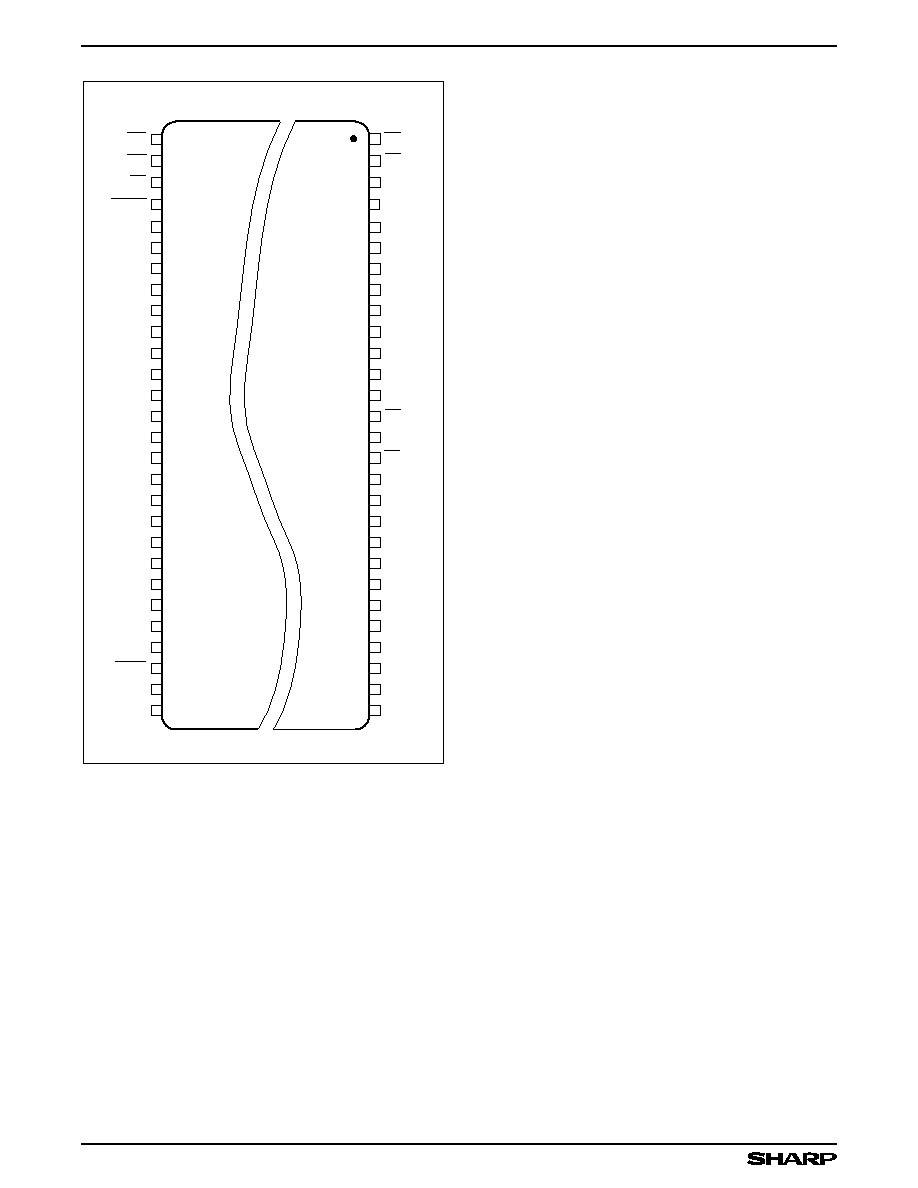

Figure 2. TSOP Reverse Bend Configuration

INTRODUCTION

Sharp's LH28F016SU 16M Flash Memory is a revo-

lutionary architecture which enables the design of truly

mobile, high performance, personal computing and com-

munication products. With innovative capabilities, 5 V

single voltage operation and very high read/write per-

formance, the LH28F016SU is also the ideal choice for

designing embedded mass storage memory systems.

The LH28F016SU is a very high density, highest per-

formance non-volatile read/write solution for solid-state

storage applications. Its symmetrically blocked archi-

tecture (100% compatible with the LH28F008SA 8M

Flash memory), extended cycling, low power 3.3 V

operation, very fast write and read performance and

selective block locking provide a highly flexible memory

component suitable for high density memory cards,

Resident Flash Arrays and PCMCIA-ATA Flash Drives.

The LH28F016SU's dual read voltage enables the

design of memory cards which can interchangeably be

read/written in 3.3 V and 5.0 V systems. Its x8/x16

architecture allows the optimization of memory to pro-

cessor interface. The flexible block locking option

enables bundling of executable application software in

a Resident Flash Array or memory card. Manufactured

on Sharp's 0.55 µm ETOXTM process technology, the

LH28F016SU is the most cost-effective, high-density

3.3 V flash memory.

DESCRIPTION

The LH28F016SU is a high performance 16M

(16,777,216 bit) block erasable non-volatile random

access memory organized as either 1M ◊ 16 or 2M ◊ 8.

The LH28F016SU includes thirty-two 64K (65,536)

blocks or thirty-two 32-KW (32,768) blocks. A chip

memory map is shown in Figure 4.

The implementation of a new architecture, with many

enhanced features, will improve the device operating

characteristics and results in greater product reliability

and ease of use.

Among the significant enhancements of the

LH28F016SU:

∑

5 V Write/Erase Operation (5 V V

PP

)

∑

3.3 V Low Power Capability (2.7 V V

CC

Read)

∑

Improved Write Performance

∑

Dedicated Block Write/Erase Protection

A 3/5

ª

input pin reconfigures the device internally for

optimized 3.3 V or 5.0 V read/write operation.

The LH28F016SU will be available in a 56-pin,

1.2 mm thick ◊ 14 mm ◊ 20 mm TSOP (Type I) pack-

age. This form factor and pinout allow for very high board

layout densities.

28F016SUT-17

TOP VIEW

56-PIN TSOP

2

3

4

5

8

9

A

16

A

19

A

20

53

52

51

50

49

48

45

42

NC

6

7

A

17

A

18

47

46

DQ

15

DQ

14

GND

GND

10

11

12

55

54

OE

V

CC

13

44

DQ

4

43

V

CC

A

15

DQ

7

14

15

16

17

18

19

20

39

36

41

40

38

37

DQ

3

DQ

10

DQ

2

V

CC

A

10

A

9

A

11

V

PP

RP

CE

0

A

8

DQ

9

WE

DQ

6

DQ

13

DQ

11

56

1

CE

1

3/5

WP

21

22

23

24

25

26

27

28

A

4

A

3

A

5

A

7

A

6

GND

A

2

A

1

34

DQ

8

35

DQ

1

31

33

32

30

29

A

0

BYTE

NC

NC

DQ

0

A

14

A

13

A

12

DQ

5

DQ

12

RY/BY

16M (1M ◊ 16, 2M ◊ 8) Flash Memory

LH28F016SU

3

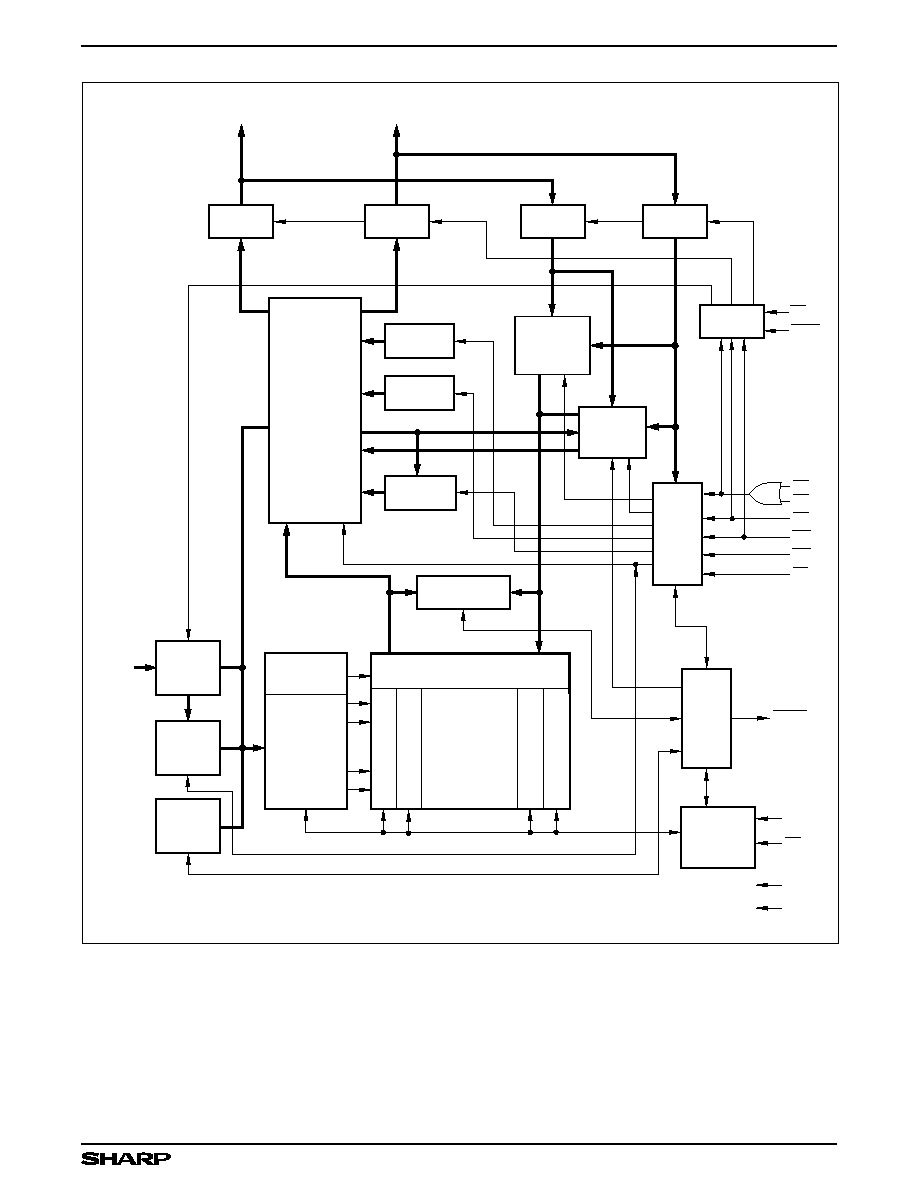

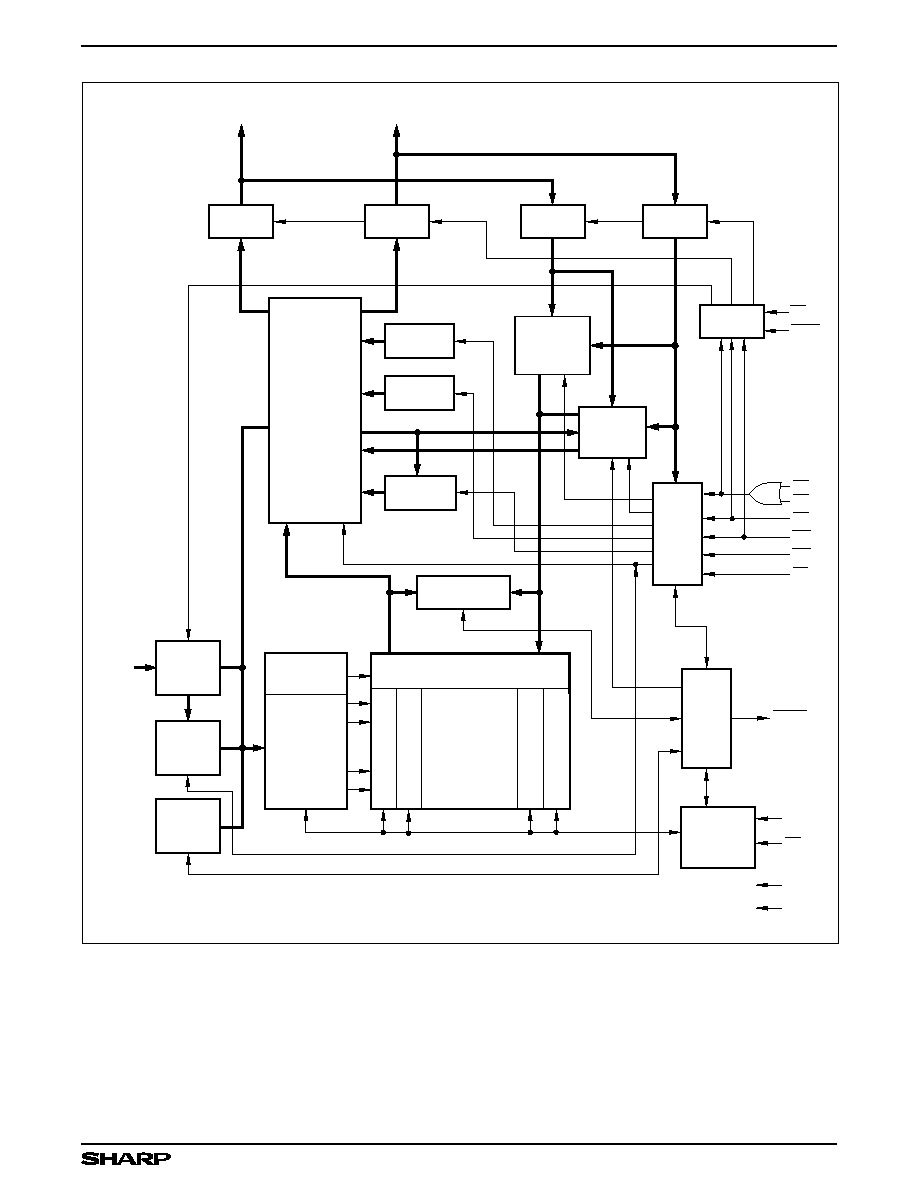

Figure 3. LH28F016SU Block Diagram (Architectural Evolution Includes Page Buffers,

Queue Registers and Extended Status Registers)

OUTPUT

BUFFER

OUTPUT

BUFFER

INPUT

BUFFER

INPUT

BUFFER

DQ

8

- DQ

15

DQ

0

- DQ

7

ID

REGISTER

OUTPUT

MULTIPLEXER

CSR

ESRs

DATA

COMPARATOR

DATA

QUEUE

REGISTERS

PAGE

BUFFERS

I/O

LOGIC

CUI

WSM

64KB BLOCK 0

64KB BLOCK 1

64KB BLOCK 30

64KB BLOCK 31

. . .

. . .

Y GATING/SENSING

Y-DECODER

X-DECODER

CE

0

CE

1

OE

WE

WP

RP

PROGRAM/

ERASE

VOLTAGE

SWITCH

3/5

BYTE

V

PP

3/5

V

CC

GND

RY/BY

ADDRESS

COUNTER

ADDRESS

QUEUE

LATCHES

INPUT

BUFFER

A

0

- A

20

. . .

28F016SUT-2

LH28F016SU

16M (1M ◊ 16, 2M ◊ 8) Flash Memory

4

PIN DESCRIPTION

SYMBOL

TYPE

NAME AND FUNCTION

A

0

INPUT

BYTE-SELECT ADDRESS:

Selects between high and low byte when device is in x8

mode. This address is latched in x8 Data Writes. Not used in x16 mode (i.e., the A

0

input buffer is turned off when BYTE is high).

A

1

- A

15

INPUT

WORD-SELECT ADDRESSES:

Select a word within one 64K block. A

6

-

A

15

selects

1 of 1024 rows, and A

1

- A

5

selects 16 of 512 columns. These addresses are

latched during Data Writes.

A

16

- A

20

INPUT

BLOCK-SELECT ADDRESSES:

Select 1 of 32 Erase blocks. These addresses are

latched during Data Writes, Erase and Lock-Block operations.

DQ

0

- DQ

7

INPUT/OUTPUT

LOW-BYTE DATA BUS:

Inputs data and commands during CUI write cycles.

Outputs array, buffer, identifier or status data in the appropriate Read mode. Floated

when the chip is de-selected or the outputs are disabled.

DQ

8

- DQ

15

INPUT/OUTPUT

HIGH-BYTE DATA BUS

: Inputs data during x16 Data-Write operations. Outputs

array, buffer or identifier data in the appropriate Read mode; not used for Status

register reads. Floated when the chip is de-selected or the outputs are disabled.

CE

ª

0

, CE

ª

1

INPUT

CHIP ENABLE INPUTS

: Activate the device's control logic, input buffers, decoders and

sense amplifiers. With either CE

ª

0

or CE

ª

1

high, the device is de-selected and power

consumption reduces to Standby levels upon completion of any current Data-Write or

Erase operations. Both CE

ª

0

, CE

ª

1

must be low to select the device. All timing

specifications are the same for both signals. Device Selection

occ

urs with the latter

falling edge of CE

ª

0

or CE

ª

1

. The first rising edge of CE

ª

0

or CE

ª

1

disables the device.

RP

ª

INPUT

RESET/POWER-DOWN:

With RP

ª

low, the device is reset, any current operation is

aborted and device is put into the deep power down mode. When the power is

turned on, RP

ª

pin is turned to low in order to return the device to default con-

figuration. When the 3/5

ª

pin is switched, or when the power transition is occurred, or

at the power on/off, RP

ª

is required to stay low in order to protect data from noise.

When returning from Deep Power-Down, a recovery time of 400

ns

(V

CC

+5.0 V

±0.5 V) is required to allow these circuits to power-up. When RP

ª

goes

low, any current or pending WSM operation(s) are terminated, and the device is

reset. All Status registers return to ready (with all status flags cleared). After

returning, the device is in read array mode.

OE

ª

INPUT

OUTPUT ENABLE:

Gates device data through the output buffers when low. The

outputs float to tri-state off when OE

ª

is high.

NOTE:

CE

ª

X

overrides OE

ª

, and OE

ª

overrides WE.

WE

INPUT

WRITE ENABLE:

Controls access to the CUI, Page Buffers, Data Queue Registers

and Address Queue Latches. WE is active low, and latches both address and data

(command or array) on its rising edge.

RY

ª

/BY

ª

OPEN DRAIN

OUTPUT

READY/BUSY:

Indicates status of the internal WSM. When low, it indicates that the

WSM is busy performing an operation. RY/BY# high indicates that the WSM is ready

for new operations (or WSM has completed all pending operations), or Erase is

Suspended, or the device is in deep power-down mode. This output is always active

(i.e., not floated to tri-state off when OE

ª

or CE

ª

0

, CE

ª

1

are high), except if a RY

ª

/BY

ª

Pin Disable command is issued.

16M (1M ◊ 16, 2M ◊ 8) Flash Memory

LH28F016SU

5

PIN DESCRIPTION (Continued)

SYMBOL

TYPE

NAME AND FUNCTION

WP

INPUT

WRITE PROTECT:

Erase blocks can be locked by writing a non-volatile lock-bit for

each block. When WP is low, those locked blocks as reflected by the Block-Lock Status

bits (BSR.6), are protected from inadvertent Data Writes or Erases. When WP is high,

all blocks can be Written or Erased regardless of the state of the lock-bits. The WP

input buffer is disabled when RP

ª

transitions low (deep power-down mode).

BYTE

INPUT

BYTE ENABLE:

BYTE low places device x8 mode. All data is then input or output

on DQ

0

- DQ

7

, and DQ

8

- DQ

15

float. Address A

0

selects between the high and low

byte. BYTE high places the device in x16 mode, and turns off the A

0

input buffer.

Address A

1

, then becomes the lowest order address.

3/5

ª

INPUT

3.3/5.0 VOLT SELECT:

3/5

ª

high configures internal circuits for 3.3 V operation. 3/5

ª

low configures internal circuits for 5.0 V operation.

NOTES:

Reading the array with 3/5

ª

high in a 5.0 V system could damage the

device. There is a significant delay from 3/5

ª

switching to valid data.

V

PP

SUPPLY

ERASE/WRITE POWER SUPPLY:

For erasing memory array blocks or writing

words/bytes/pages into the flash array.

V

CC

SUPPLY

DEVICE POWER SUPPLY (3.3 V ±0.3 V, 5.0 V ±0.5 V) (2.7 V ~ 3.6 V at Read

Operation)

: Do not leave any power pins floating.

GND

SUPPLY

GROUND FOR ALL INTERNAL CIRCUITRY:

Do not leave any ground pins floating.

NC

NO CONNECT:

No internal connection to die, lead may be driven or left floating.

The LH28F016SU incorporates two Page Buffers of

256 Bytes (128 Words) each to allow page data writes.

This feature can improve a system write performance

over previous flash memory devices.

All operations are started by a sequence of Write

commands to the device. Three Status Registers

(described in detail later) and a RY

ª

/BY

ª

output pin

provide information on the progress of the requested

operation.

While the LH28F008SA requires an operation to com-

plete before the next operation can be requested, the

LH28F016SU allows queuing of the next operation while

the memory executes the current operation. This elimi-

nates system overhead when writing several bytes in a

row to the array or erasing several blocks at the same

time. The LH2F016SUR-10 can also perform write op-

erations to one block of memory while performing erase

of another block.

The LH28F016SU provides user-selectable block

locking to protect code or data such as Device Drivers,

PCMCIA card information, ROM-Executable O/S or

Application Code. Each block has an associated non-

volatile lock-bit which determines the lock status of the

block. In addition, the LH28F016SU has a master Write

Protect pin (WP

ª

) which prevents any modifications to

memory blocks whose lock-bits are set.

A Command User Interface (CUI) serves as the sys-

tem interface between the microprocessor or

microcontroller and the internal memory operation.

Internal Algorithm Automation allows Byte/Word

Writes and Block Erase operations to be executed

using a Two-Write command sequence to the CUI in

the same way as the LH28F008SA 8M Flash memory.

A Superset of commands have been added to the

basic LH28F008SA command-set to achieve higher

write performance and provide additional capabilities.

These new commands and features include:

∑

Page Buffer Writes to Flash

∑

Command Queuing Capability

∑

Automatic Data Writes During Erase

∑

Software Locking of Memory Blocks

∑

Two-Byte Successive Writes in 8-bit Systems

∑

Erase All Unlocked Blocks

Writing of memory data is performed in either byte or

word increments typically within 8 µs, a 25% improve-

ment over the LH28F008SA. A Block Erase operation

erases one of the 32 blocks in typically 0.7 seconds,

independent of the other blocks, which is about 55%

improvement over the LH28F008SA.