LH5116/H

CMOS 16K (2K

◊

8) Static RAM

FEATURES

∑∑

2,048

◊

8 bit organization

∑∑

Access time: 100 ns (MAX.)

∑∑

Power consumption:

Operating: 220 mW (MAX.)

Standby: 5.5

µ

W (MAX.)

∑∑

Single +5 V power supply

∑∑

Fully-static operation

∑∑

TTL compatible I/O

∑∑

Three-state outputs

∑∑

Wide temperature range available

LH5116H: -40 to +85

∞

C

∑∑

Packages:

24-pin, 600-mil DIP

24-pin, 300-mil SK-DIP

24-pin, 450-mil SOP

DESCRIPTION

The LH5116/H are static RAMs organized as 2,048

◊

8

bits. It is fabricated using silicon-gate CMOS process

technology. It features high speed access in read mode

using output enable (t

OE

).

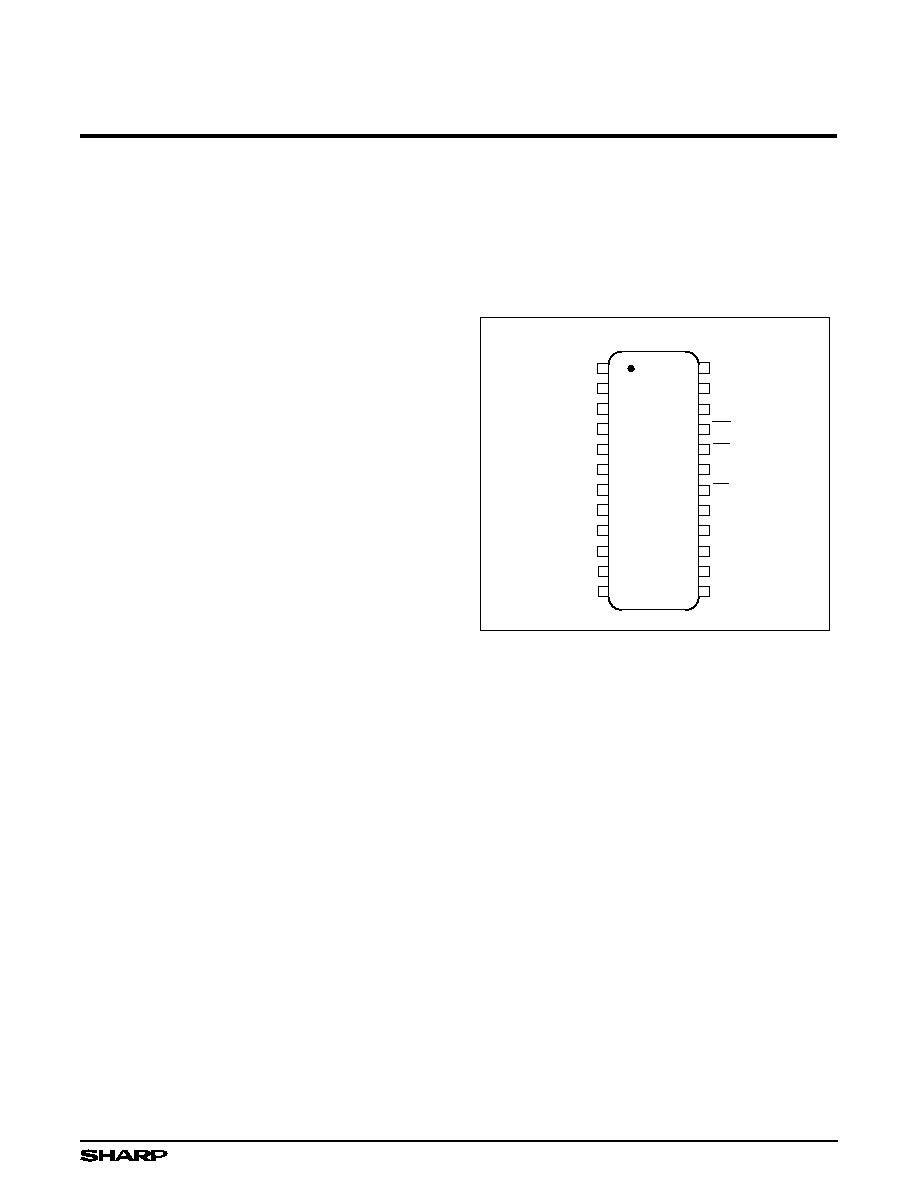

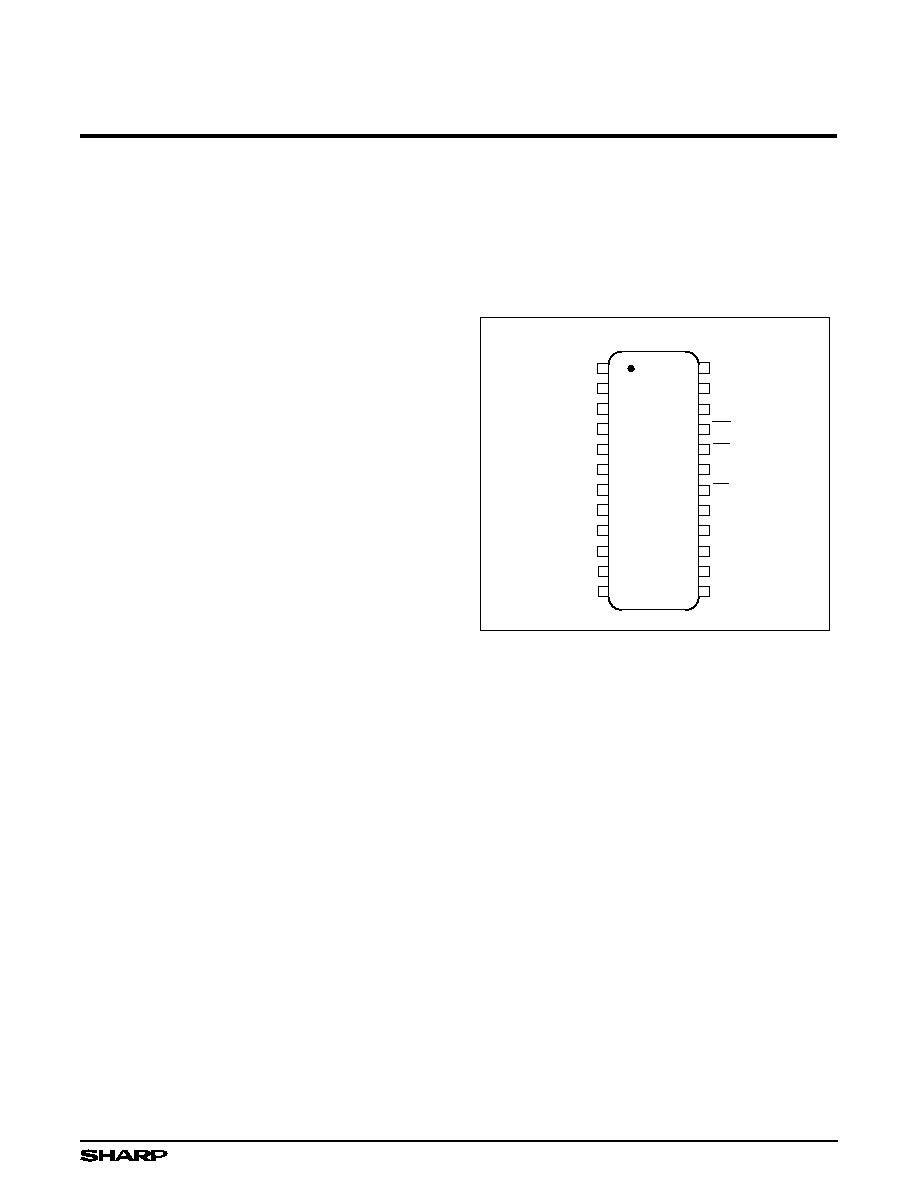

PIN CONNECTIONS

1

2

3

4

5

6

9

10

A

0

A

3

Vcc

24

23

22

21

20

19

16

15

A

5

A

4

7

8

A

1

A

2

18

17

A

7

A

6

OE

I/O

1

GND

A

8

A

9

A

10

CE

11

12

14

13

TOP VIEW

I/O

2

I/O

3

I/O

7

I/O

6

I/O

5

I/O

4

I/O

8

WE

5116-1

24-PIN DIP

24-PIN SK-DIP

24-PIN SOP

Figure 1. Pin Connections for DIP, SK-DIP,

and SOP Packages

1

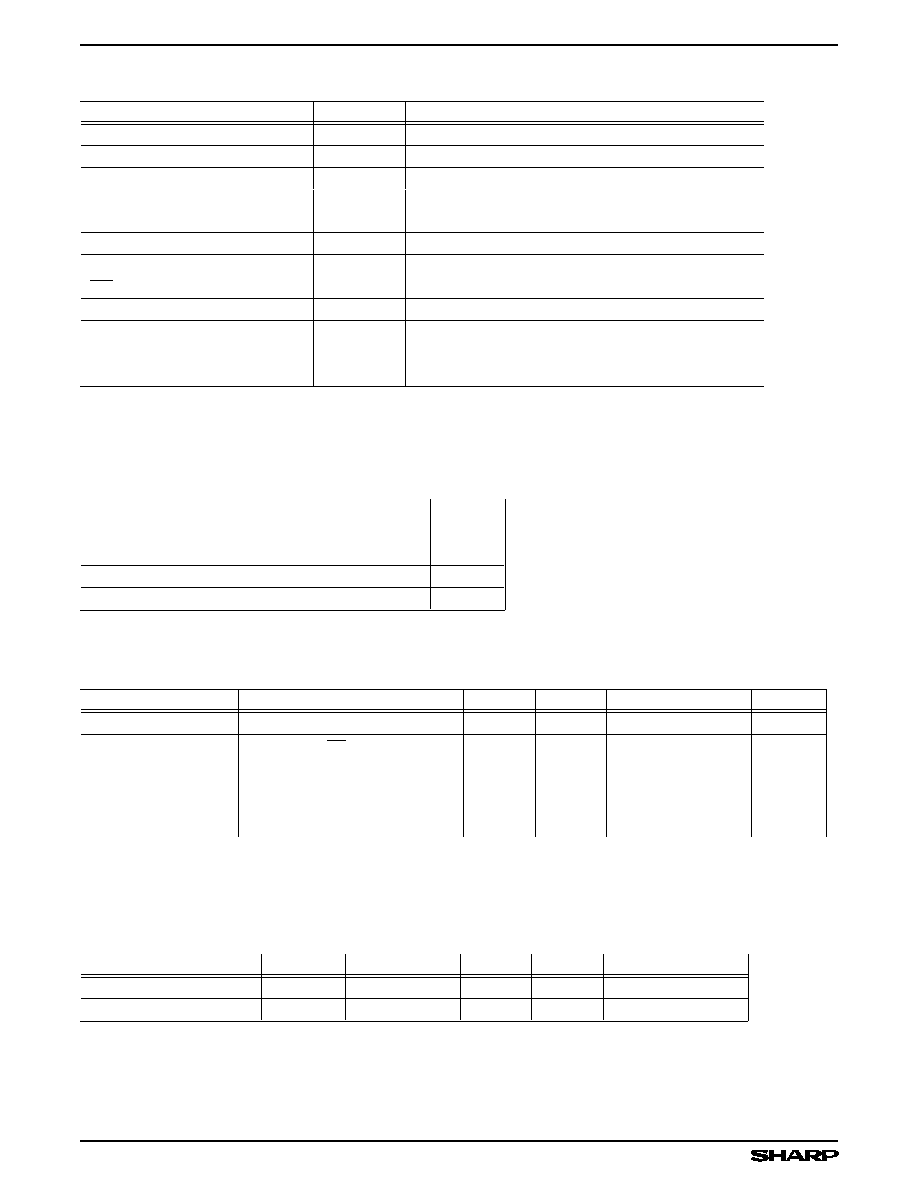

TRUTH TABLE

CE

OE

WE

MODE

I/O

1

- I/O

8

SUPPLY CURRENT

NOTE

L

X

L

Write

D

IN

Operating (ICC)

1

L

L

H

Read

D

OUT

Operating (I

CC

)

H

X

X

Deselect

High-Z

Standby (I

SB

)

1

L

H

X

Outputs disable

High-Z

Operating (I

CC

)

1

NOTE:

1.

X = H or L

I/O

8

A

8

A

9

A

10

23

22

19

9

13

16

5116-2

MEMORY CELL

ARRAY

(128 x128)

11

21

15

10

14

A

7

1

WE

ROW ADDRESS

BUFFERS

CE

A

6

2

A

5

3

18

A

0

8

ROW DECODERS

COLUMN

I/O CIRCUIT

COLUMN DECODERS

OE

DATA CONTROL

V

CC

GND

I/O

7

I/O

6

I/O

5

I/O

4

I/O

3

I/O

2

I/O

1

20

17

COLUMN ADDRESS

BUFFERS

4

A

4

A

3

A

2

A

1

7

5

6

24

12

CE

CE

Figure 2. LH5116/H Block Diagram

PIN DESCRIPTION

SIGNAL

PIN NAME

A

0

- A

10

Address input

CE

Chip Enable input

OE

Output Enable input

WE

Write Enable input

SIGNAL

PIN NAME

I/O

1

- I/O

8

Data input/output

V

CC

Power supply

GND

Ground

LH5116/H

CMOS 16K (2K

◊

8) Static RAM

2

ABSOLUTE MAXIMUM RATINGS

PARAMETER

SYMBOL

RATING

UNIT

NOTE

Supply voltage

V

CC

-0.3 to +7.0

V

1

Input voltage

V

IN

-0.3 to V

CC

+ 0.3

V

1

Operating temperature

Topr

0 to +70

∞

C

2

-40 to +85

3

Storage temperature

Tstg

-55 to +150

∞

C

NOTES:

1.

The maximum applicable voltage on any pin with respect to GND.

2.

Applied to the LH5116/D/NA

3.

Applied to the LH5116H/HD/HN

RECOMMENDED OPERATING CONDITIONS

1

PARAMETER

SYMBOL

MIN.

TYP.

MAX.

UNIT

Supply voltage

V

CC

4.5

5.0

5.5

V

Input voltage

V

IH

2.2

V

CC

+ 0.3

V

V

IL

-0.3

0.8

V

NOTE:

1.

T

A

= 0 to 70

∞

C (LH5116/D/NA), T

A

= -40 to +85

∞

C (LH5116H/HD/HN)

DC CHARACTERISTICS

1

(V

CC

= 5 V

±

10%)

PARAMETER

SYMBOL

CONDITIONS

MIN.

TYP.

MAX.

UNIT

NOTE

Output `LOW' voltage

V

OL

I

OL

= 2.1 mA

0.4

V

Output `HIGH' voltage

V

OH

I

OH

= -1.0

mA

2.4

V

Input leakage current

I

LI

V

IN

= 0 V to V

CC

-1.0

1.0

µ

A

Output leakage current

I

LO

CE = V

IH

, V

I/O

= 0 V to V

CC

-1.0

1.0

µ

A

Operating current

I

CC1

Outputs open (OE = V

CC

)

25

30

mA

2

I

CC2

Outputs open (OE = V

IH

)

30

40

mA

3

Standby current

I

SB

CE

V

CC

- 0.2 V

All other input pins = 0 V to V

CC

1.0

µ

A

0.2

4

NOTES:

1.

T

A

= 0 to 70

∞

C (LH5116/D/NA), T

A

= -40 to +85

∞

C (LH5116H/HD/HN)

2.

CE = 0 V; all other input pins = 0 V to V

CC

3.

CE = V

IL

; all other input pins = V

IL

to V

IH

4.

T

A

= 25

∞

C

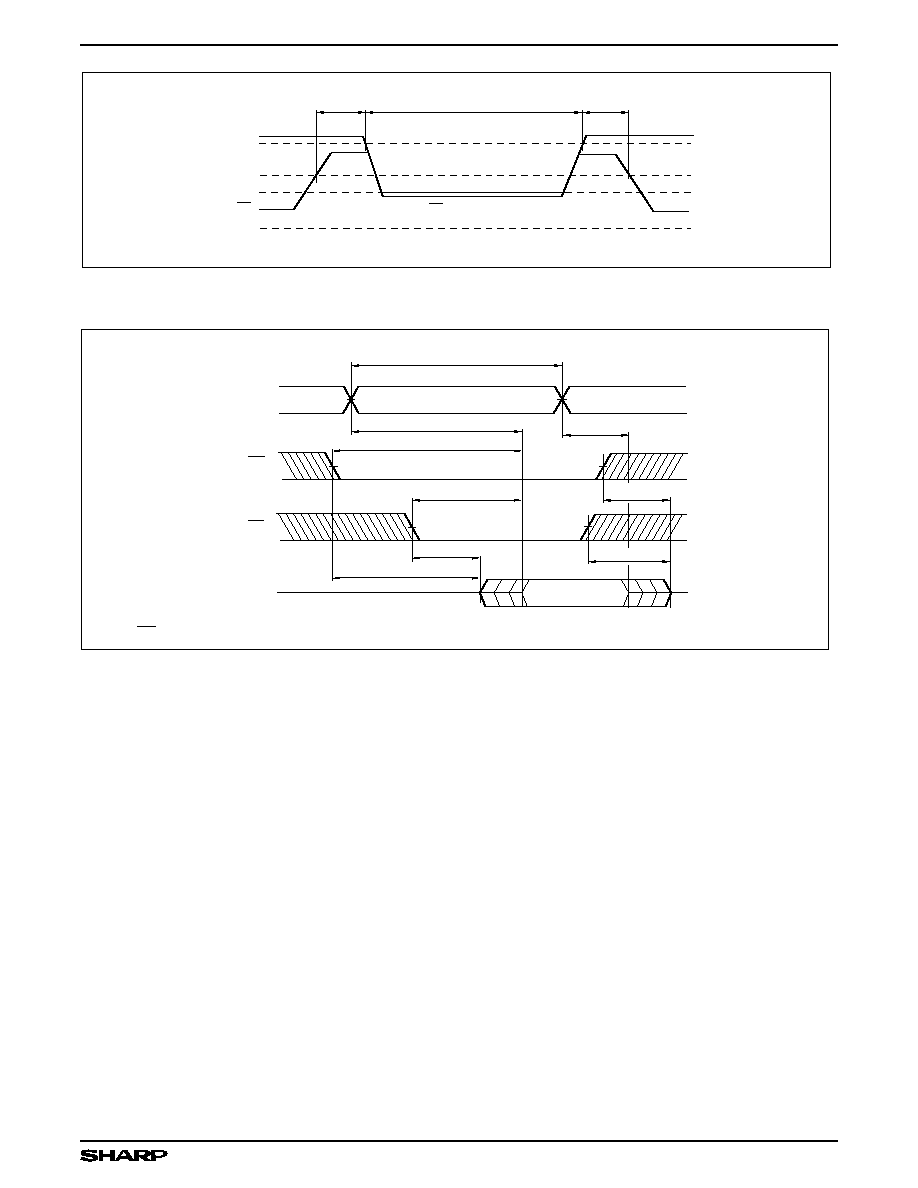

AC CHARACTERISTICS

1

(1) READ CYCLE (V

CC

= 5 V

±

10%)

PARAMETER

SYMBOL

MIN.

TYP.

MAX.

UNIT

NOTE

Read cycle time

t

RC

100

ns

Address access time

t

AA

100

ns

Chip enable access time

t

ACE

100

ns

Chip enable Low to output in Low-Z

t

CLZ

10

ns

2

Output enable access time

t

OE

40

ns

Output enable Low to output in Low-Z

t

OLZ

10

ns

2

Chip disable to output in High-Z

t

CHZ

0

40

ns

2

Output disable to output in High-Z

t

OHZ

0

40

ns

2

Output hold time

t

OH

10

ns

NOTES:

1.

T

A

= 0 to 70

∞

C (LH5116/NA/D). T

A

= -40 to 85

∞

C (LH5116H/HD/HN).

2.

Active output to high-impedance and high-impedance to output active tests specified for a

±

200 mV transition

from steady state levels into the test load.

CMOS 16K (2K

◊

8) Static RAM

LH5116/H

3

(2) WRITE CYCLE

1

(V

CC

= 5 V

±

10%)

PARAMETER

SYMBOL

MIN.

TYP.

MAX.

UNIT

NOTE

Write cycle time

t

WC

100

ns

Chip enable to end of write

t

CW

80

ns

Address valid time

t

AW

80

ns

Address setup time

t

AS

0

ns

Write pulse width

t

WP

60

ns

Write recovery time

t

WR

10

ns

Output active from end of write

t

OW

10

ns

2

WE Low to output in High-Z

t

WHZ

0

30

ns

2

Data valid to end of write

t

DW

30

ns

Data hold time

t

DH

10

ns

Output enable to output in High-Z

t

OHZ

0

40

ns

2

Output active from end of write

t

OW

10

ns

2

NOTES:

1.

T

A

= 0 to +70

∞

C (LH5116/D/NA), T

A

= -40 to +85

∞

C (LH5116H/HD/HN)

2.

Active output to high-impedance and high-impedance to output active tests specified for a

±

200 mV transition

from steady state levels into the test load.

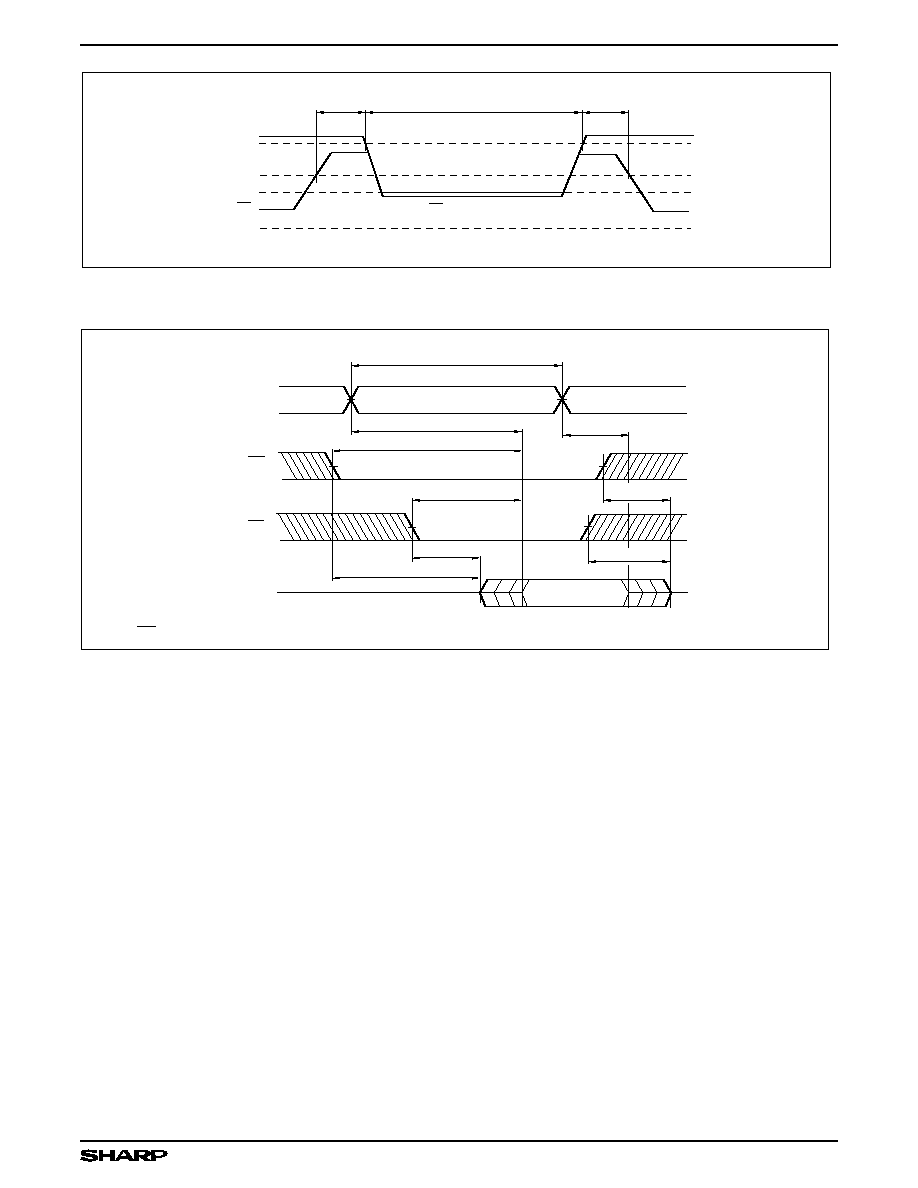

AC TEST CONDITIONS

PARAMETER

MODE

NOTE

Input voltage amplitude

0.8 V to 2.2 V

Input rise/fall time

10 ns

Timing reference level

1.5 V

Output load condition

1TTL + C

L

(100 pF)

1

NOTE:

1.

Includes scope and jig capacitance.

DATA RETENTION CHARACTERISTICS

1

PARAMETER

SYMBOL

CONDITIONS

MIN.

TYP.

MAX.

UNIT

NOTE

Data retention voltage

V

CCDR

CE

V

CCRC

- 0.2 V

2.0

5.5

V

Data retention current

I

CCDR

CE

V

CCDR

- 0.2 V,

V

CCDR

= 2.0 V

1.0

µ

A

0.2

2

Chip disable to data

retention

t

CDR

0

ns

Recovery time

t

R

t

RC

ns

3

NOTES:

1.

T

A

= 0 to +70

∞

C (LH5116/D/NA), T

A

= -40 to +85

∞

C (LH5116H/HD/HN)

2.

T

A

= 25

∞

C

3.

t

RC

= Read cycle time

CAPACITANCE

1

(f = 1 MHz, T

A

= 25

∞

C)

PARAMETER

SYMBOL

CONDITIONS

MIN.

TYP.

MAX.

UNIT

Input capacitance

C

IN

V

IN

= 0 V

7

pF

Input/output capacitance

C

I/O

V

I/O

= 0 V

10

pF

NOTE:

1.

This parameter is sampled and not production tested.

LH5116/H

CMOS 16K (2K

◊

8) Static RAM

4

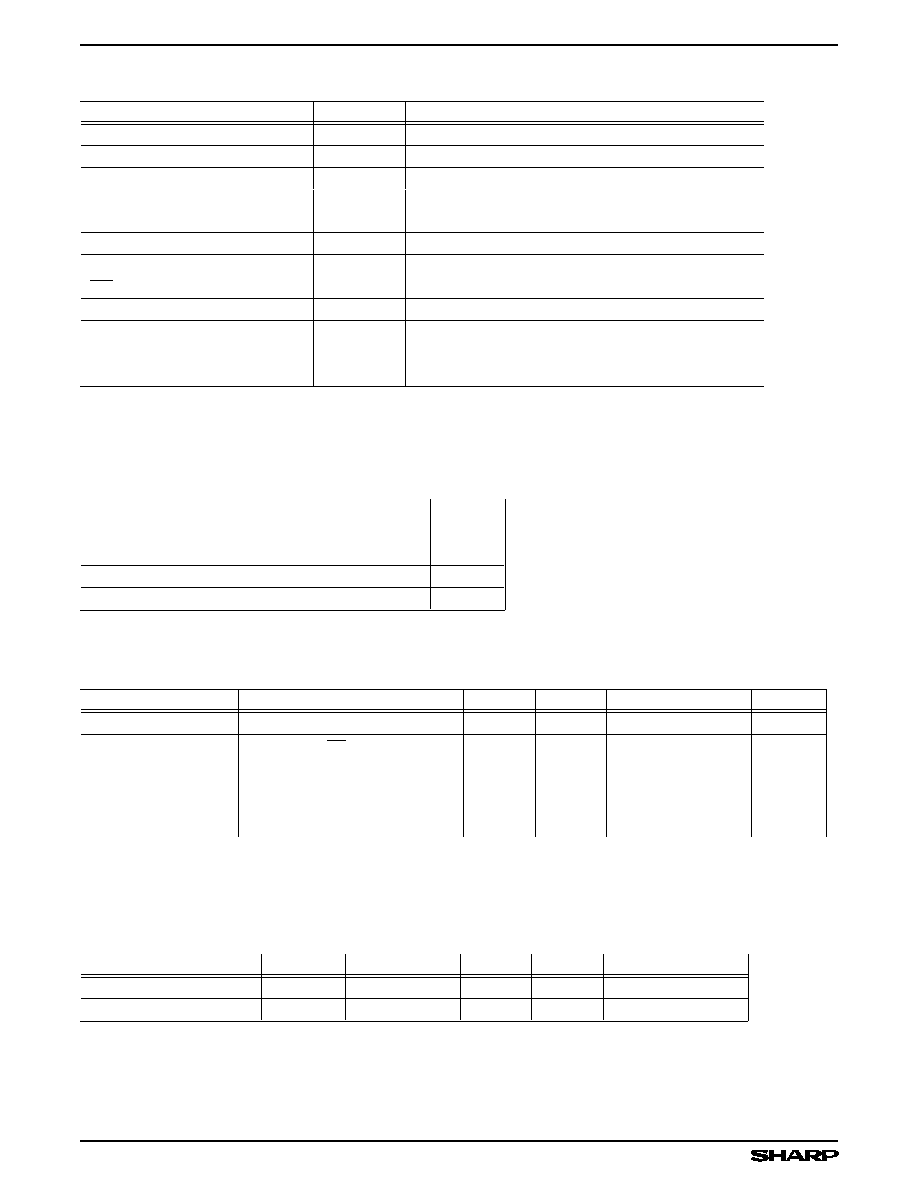

4.5 V

DATA RETENTION MODE

V

CC

0 V

CE

V

CCDR

-0.2 V

CE

2.2 V

t

CDR

5116-6

t

R

V

CCDR

Figure 3. Low Voltage Data Retention

t

OE

t

AA

A

0

- A

10

CE

t

OLZ

t

OH

D

OUT

DATA VALID

t

OHZ

OE

t

RC

t

ACE

t

CHZ

t

CLZ

NOTE: WE = "HIGH"

5116-3

Figure 4. Read Cycle

CMOS 16K (2K

◊

8) Static RAM

LH5116/H

5