LH5324000

CMOS 24M (3M

◊

8) MROM

FEATURES

∑∑

3,145,728

◊

8 bit organization

∑∑

Access time: 150 ns (MAX.)

∑∑

Supply current:

≠ Operating: 65 mA (MAX.)

≠ Standby: 100

µ

A (MAX.)

∑∑

TTL compatible I/O

∑∑

Three-state output

∑∑

Single +5 V Power supply

∑∑

Static operation

∑∑

When the address input at both A

19

and

A

20

is high level, outputs become high

impedance irrespective of CE or OE.

∑∑

Package:

42-pin, 600-mil DIP

∑∑

Others:

≠ Non programmable

≠ Not designed or rated as radiation

hardened

≠ CMOS process (P type silicon

substrate)

DESCRIPTION

The LH5324000 is a 24M-bit CMOS mask-program-

mable ROM organized as 3,145,728

◊

8 bits. It is

fabricated using silicon-gate CMOS process technol-

ogy.

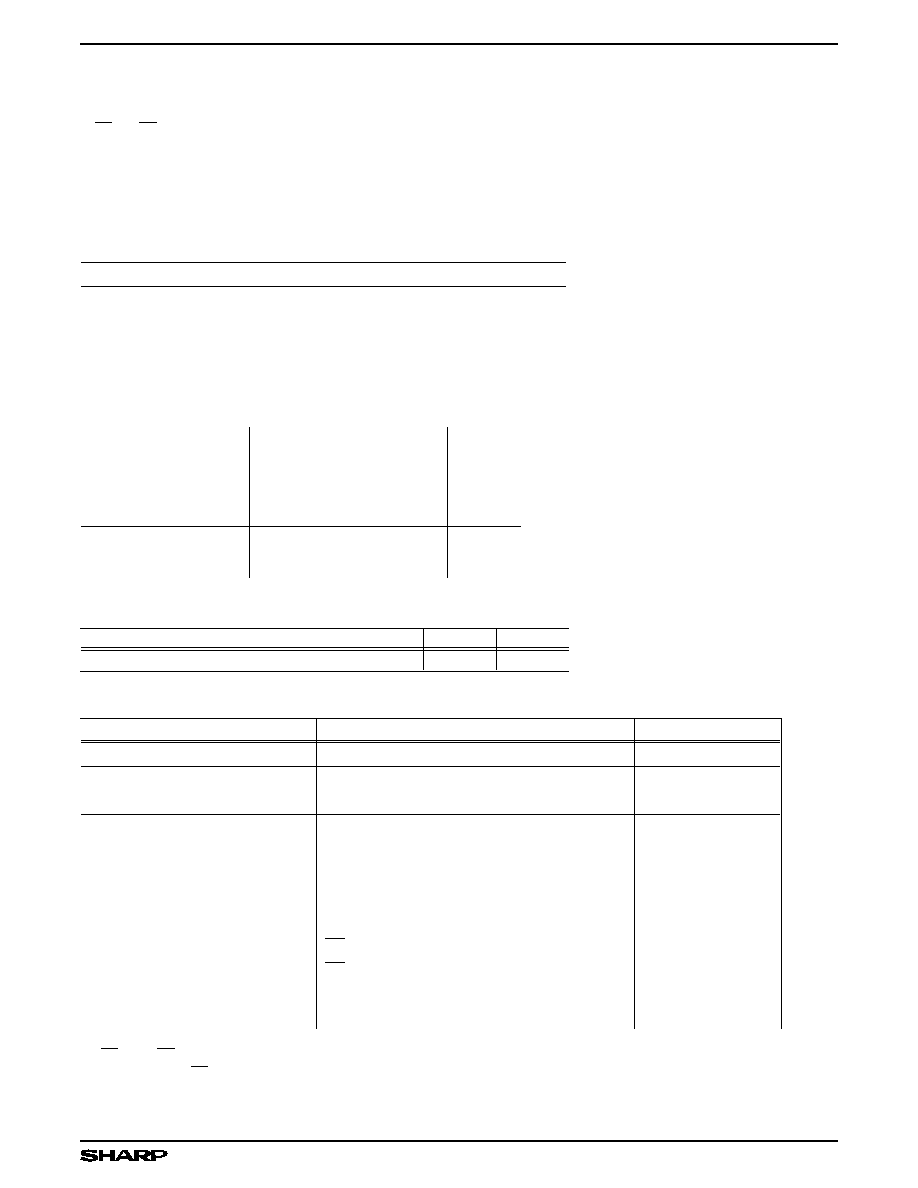

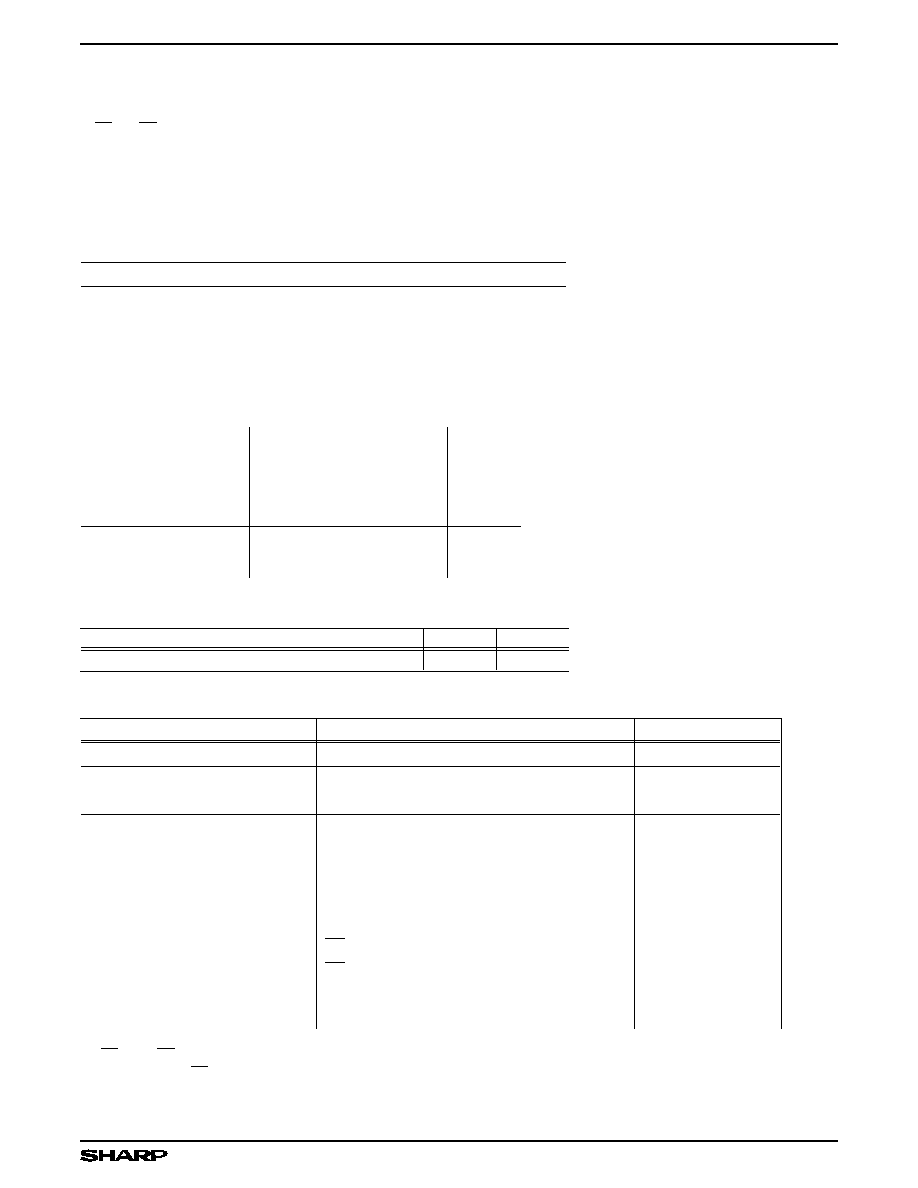

PIN CONNECTIONS

532400-1

TOP VIEW

2

3

4

5

8

9

A

2

A

5

39

38

37

36

35

34

31

28

A

7

A

6

6

7

A

3

A

4

33

32

A

10

A

11

A

13

A

15

GND

NC

10

11

12

41

40

A

9

A

1

13

30

A

-1

29

D

7

OE

A

0

CE

A

12

42-PIN DIP

14

15

16

17

18

19

20

21

25

22

27

26

24

23

NC

D

5

NC

D

4

D

2

NC

NC

GND

NC

D

1

D

0

D

3

NC

V

CC

A

8

A

14

A

16

D

6

42

1

A

17

A

18

A

19

A

20

Figure 1. Pin Connections

1

TRUTH TABLE

CE

OE

A

-1

- A

18

A

19

A

20

DATA

OUTPUT

SUPPLY

CURRENT

D

0

- D

7

H

X

X

X

X

High-Z

Standby (I

SB

)

L

H

X

X

X

High-Z

Operating (I

CC

)

L

L

X

L

L

Output

Operating (I

CC

)

L

L

X

L

H

Output

Operating (I

CC

)

L

L

X

H

L

Output

Operating (I

CC

)

L

L

X

H

H

High-Z

Operating (I

CC

)

NOTES:

1.

X = Don't care; High-Z = High-impedance

2.

When the address inputs become HIGH to both A

19

and A

20

, the data does not exist in this address area,

the data outputs become "High Impedance".

ABSOLUTE MAXIMUM RATINGS

PARAMETER

SYMBOL

RATING

UNIT

Supply voltage

V

CC

-0.3 to +7.0

V

Input voltage

V

IN

-0.3 to V

CC

+ 0.3

V

Output voltage

V

OUT

-0.3 to V

CC

+ 0.3

V

Operating temperature

T

OPR

0 to +70

∞

C

Storage temperature

T

STG

-65 to +150

∞

C

RECOMMENDED OPERATING CONDITIONS (T

A

= 0 to +70

∞

C)

PARAMETER

SYMBOL

MIN.

TYP.

MAX.

UNIT

Supply voltage

V

CC

4.5

5.0

5.5

V

DC ELECTRICAL CHARACTERISTICS (V

CC

= 5 V

±

10%, T

A

= 0 to +70

∞

C)

PARAMETER

SYMBOL

CONDITIONS

MIN.

MAX.

UNIT

NOTE

Input `High' voltage

V

IH

2.2

V

CC

+ 0.3

V

Input `Low' voltage

V

IL

-0.3

0.8

V

Output `High' voltage

V

OH

I

OH

= -400

µ

A

2.4

V

Output `Low' voltage

V

OL

I

OL

= 2.0 mA

0.4

V

Input leakage current

| I

LI

|

V

IN

= 0 V to V

CC

10

µ

A

Output leakage current

| I

LO

|

V

OUT

= 0 V to V

CC

10

µ

A

1

Operating current

I

CC1

t

RC

= 150 ns

65

mA

2

I

CC2

t

RC

= 1

µ

s

55

Standby current

I

SB1

CE = V

IH

2

mA

I

SB2

CE = V

CC

- 0.2 V

100

µ

A

Input capacitance

C

IN

f = 1 MHz, t

A

= 25

∞

C

10

pF

Output capacitance

C

OUT

10

pF

NOTES:

1.

CE = V

IH

, OE = V

IH

2.

V

IN

= V

IH

or V

IL

, CE = V

IL

, output is open

CMOS 24M (3M x 8) MROM

LH5324000

3

AC ELECTRICAL CHARACTERISTICS (V

CC

= +5 V

±

10%, T

A

= 0 to +70

∞

C)

PARAMETER

SYMBOL

MIN.

MAX.

UNIT

NOTE

Read cycle time

t

RC

150

ns

Address access time

t

AA

150

ns

Chip enable access time

t

ACE

150

ns

Output enable delay time

t

OE

70

ns

Output hold time

t

OH

5

ns

Output floating time

t

CHZ

60

ns

1

t

OHZ

60

ns

t

AHZ

70

ns

NOTE:

1.

Determined by the time for the output to be opened. (Irrespective of output voltage)

AC TEST CONDITIONS

PARAMETER

RATING

Input voltage amplitude

0.6 V to 2.4 V

Input signal rise time

10 ns

Input signal fall time

10 ns

Input reference level

1.5 V

Output reference level

0.8 V, 2.2 V

Output load condition

1TTL + 100 pF

NOTE:

It is recommended that a decoupling capacitor be connected between V

CC

and GND-Pin.

LH5324000

CMOS 24M (3M x 8) MROM

4

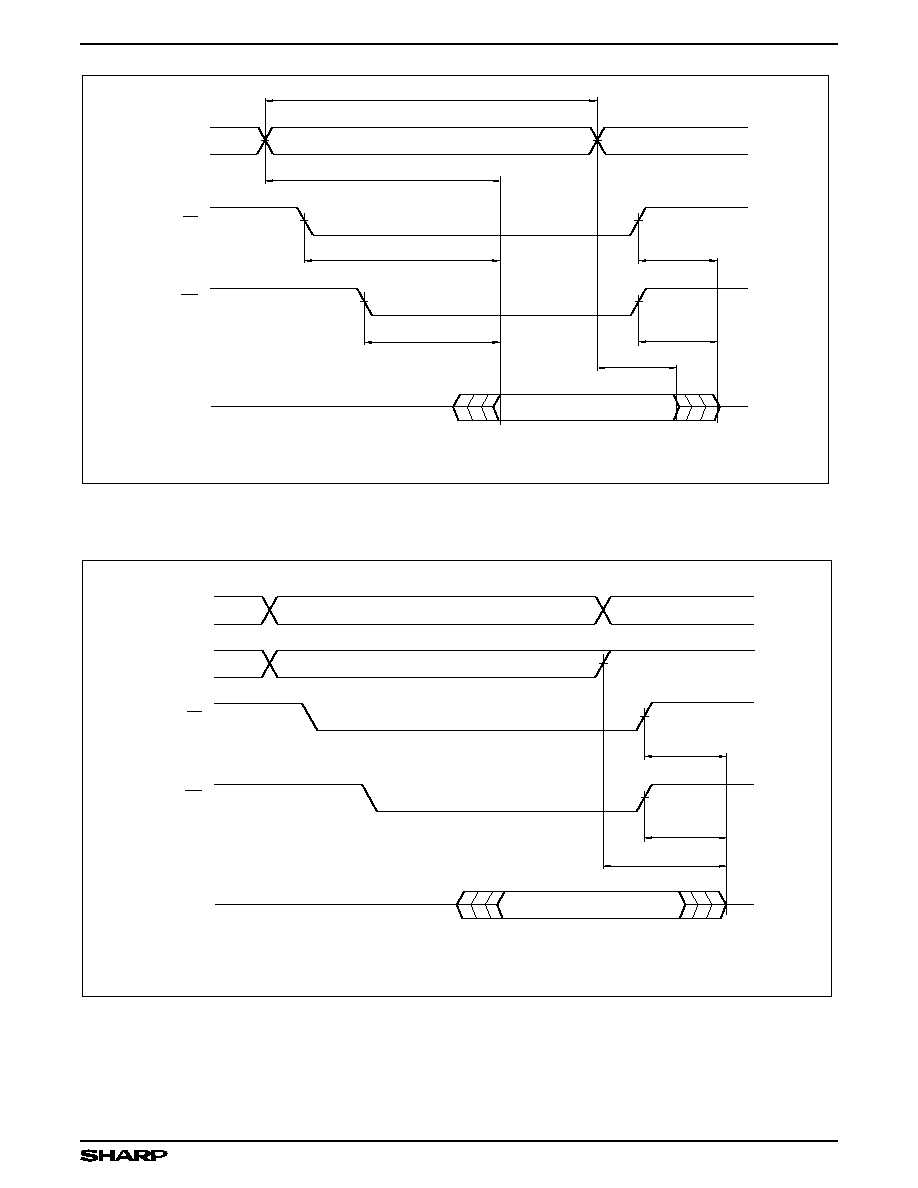

532400-3

t

OE

t

AA

D

0

- D

7

t

OHZ

t

CHZ

t

RC

t

ACE

CE

t

OH

DATA VALID

(NOTE)

OE

A

-1

- A

20

(NOTE)

(NOTE)

NOTE: The output data becomes valid when the last

intervals, t

AA

, t

ACE

, or t

OE

, have concluded.

HI-Z = High Impedance.

HI-Z

HI-Z

Figure 3. Byte Mode

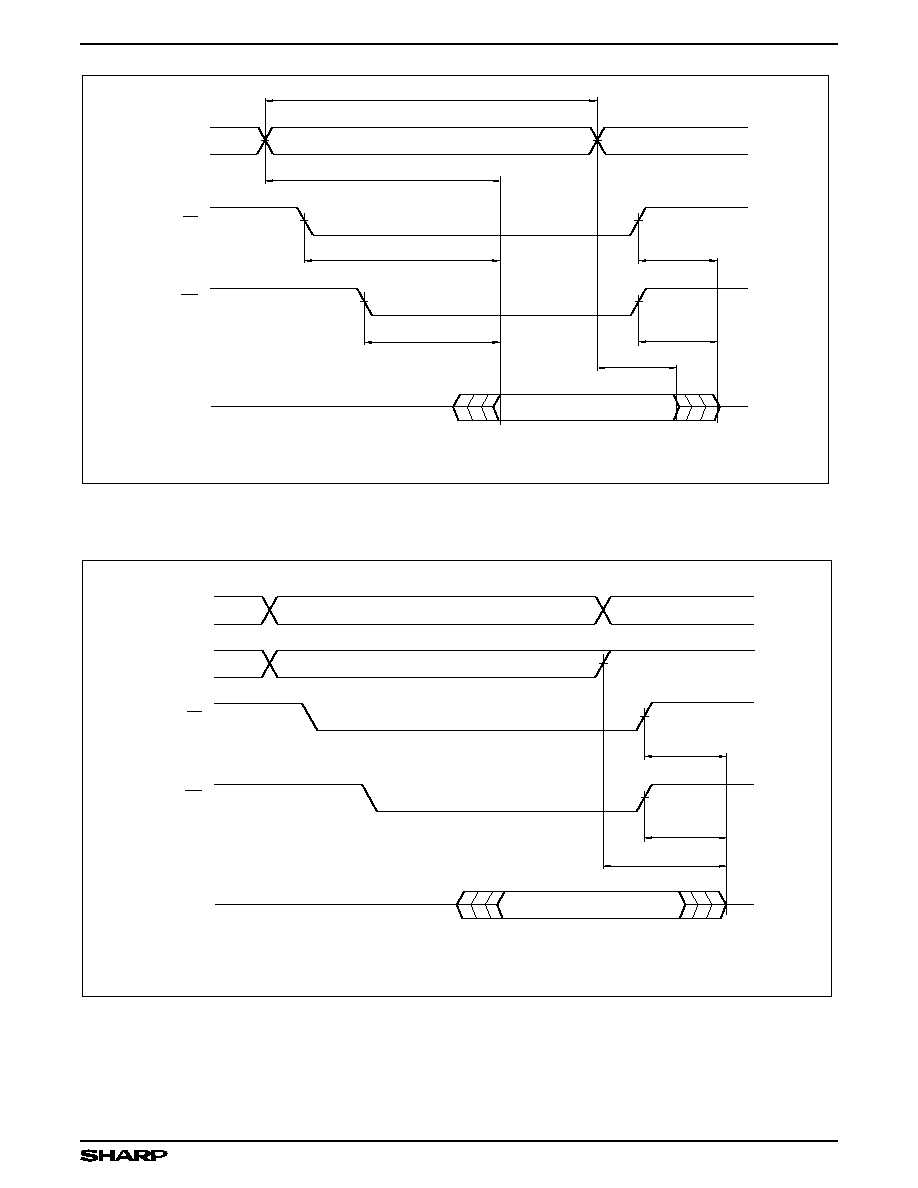

532400-4

D

0

- D

15

t

OHZ

t

CHZ

CE

DATA VALID

OE

A

-1

- A

18

A

19

, A

20

t

AHZ

HI-Z

HI-Z

HI-Z = High impedance.

NOTE: The output data becomes valid when the last

intervals, t

AA

, t

ACE

, or t

OE

, have concluded.

Figure 4. Word Mode

CMOS 24M (3M x 8) MROM

LH5324000

5