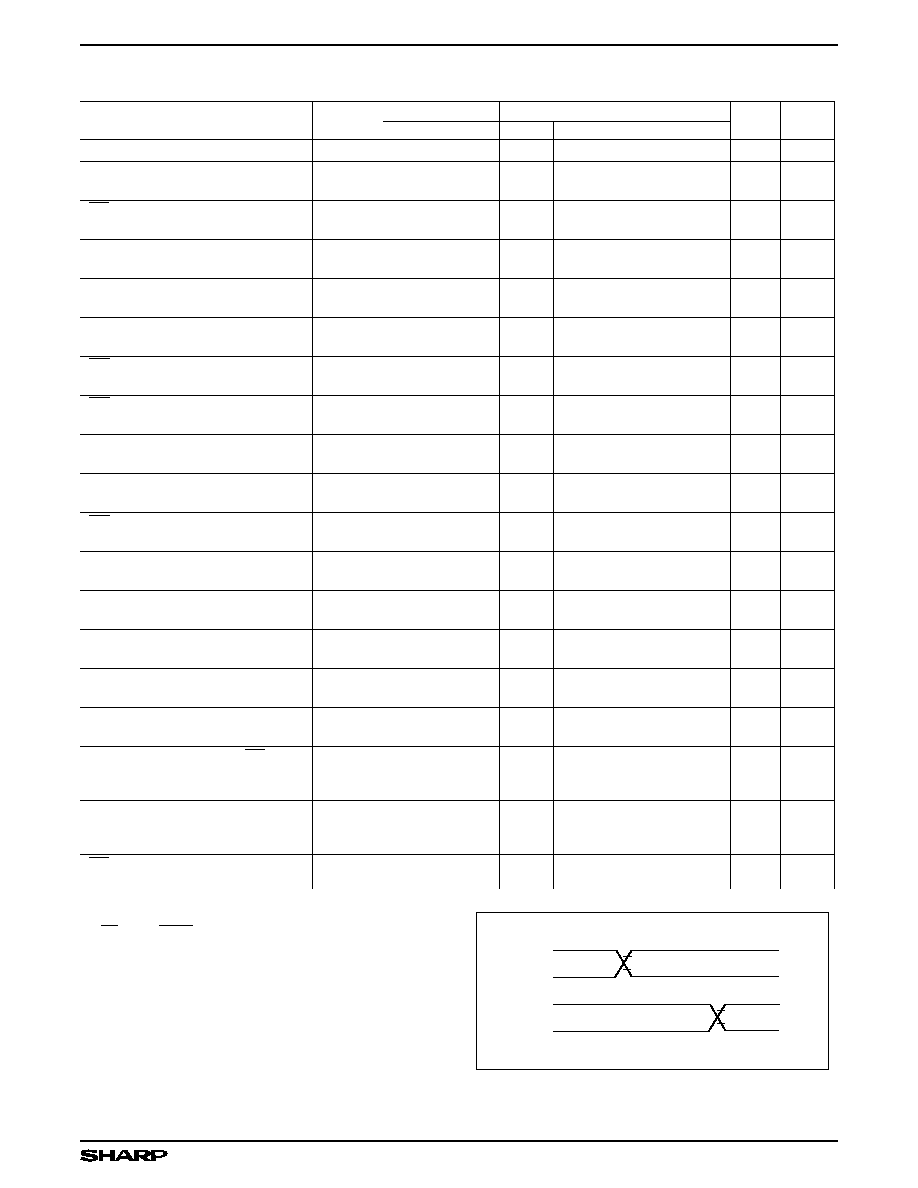

| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: LH5P8129 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

LH5P8129

FEATURES

∑∑

131,072

◊

8 bit organization

∑∑

Access times (MAX.): 60/80/100 ns

∑∑

Cycle times (MIN.): 100/130/160 ns

∑∑

Single +5 V power supply

∑∑

Pin compatible with 1M standard SRAM

∑∑

Power consumption:

Operating: 572/385/275 mW (MAX.)

Standby (TTL level): 5.5 mW (MAX.)

Standby (CMOS level): 1.1 mW (MAX.)

∑∑

TTL compatible I/O

∑∑

Available for auto-refresh and self-refresh

modes

∑∑

512 refresh cycles/8 ms

∑∑

Packages:

32-pin, 600-mil DIP

32-pin, 525-mil SOP

32-pin, 8

◊

20 mm

2

TSOP (Type I)

DESCRIPTION

The LH5P8129 is a 1M bit Pseudo-Static RAM

organized as 131,072

◊

8 bits. It is fabricated using

silicon-gate CMOS process technology.

A PSRAM uses on-chip refresh circuitry with a DRAM

memory cell for pseudo static operation which elimi-

nates external clock inputs, while considering the pinout

compatibility with industry standard SRAMs. The

advantage is the cost savings realized with the lower

cost PSRAM.

The LH5P8129 PSRAM has a built-in oscillator, which

makes it easy to refresh memories without external

clocks.

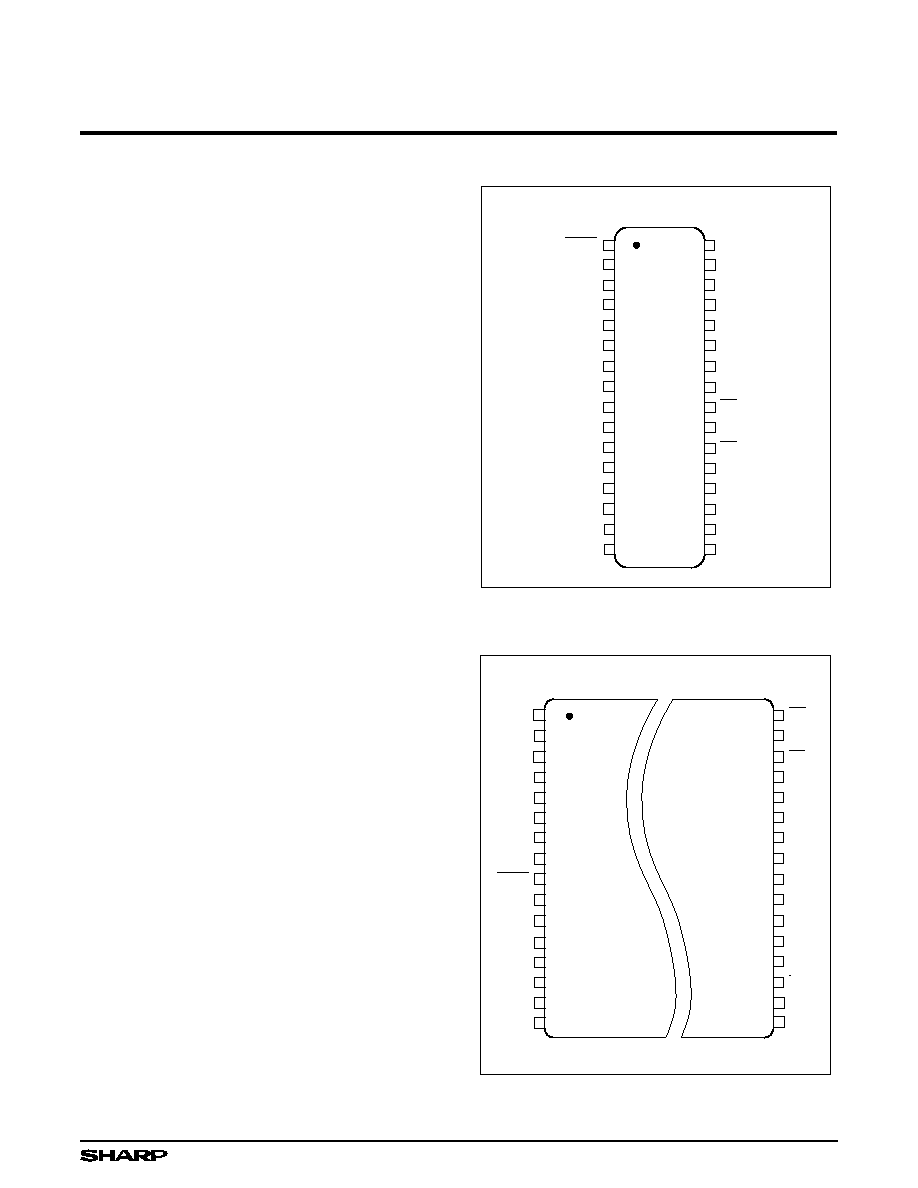

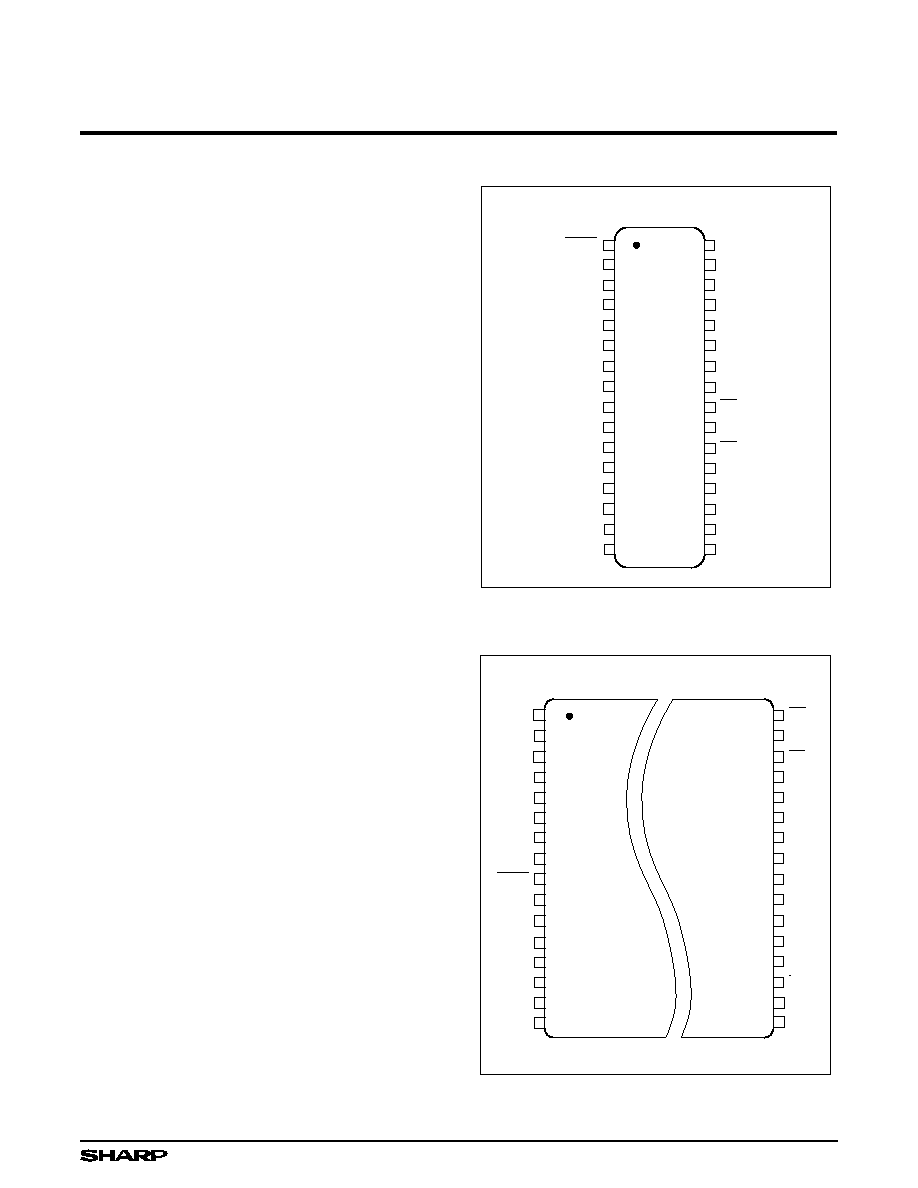

PIN CONNECTIONS

5P8129-1

TOP VIEW

5

6

7

8

11

12

A

0

A

3

26

25

24

23

22

21

18

A

5

A

4

9

10

A

1

A

2

20

19

A

6

A

9

A

11

A

10

13

14

15

28

27

I/O

0

A

13

16

17

I/O

2

OE

CE

A

7

GND

I/O

4

I/O

3

I/O

5

A

8

32-PIN DIP

32-PIN SOP

3

4

A

12

30

29

CS

A

14

R/W

1

2

A

16

32

31

V

CC

RFSH

A

15

I/O

1

I/O

6

I/O

7

Figure 1. Pin Connections for DIP and

SOP Packages

CMOS 1M (128K

◊

8)

CS-Control Pseudo-Static RAM

2

3

4

5

6

9

10

7

8

A

9

11

1

32

31

30

29

26

25

28

27

24

23

OE

A

10

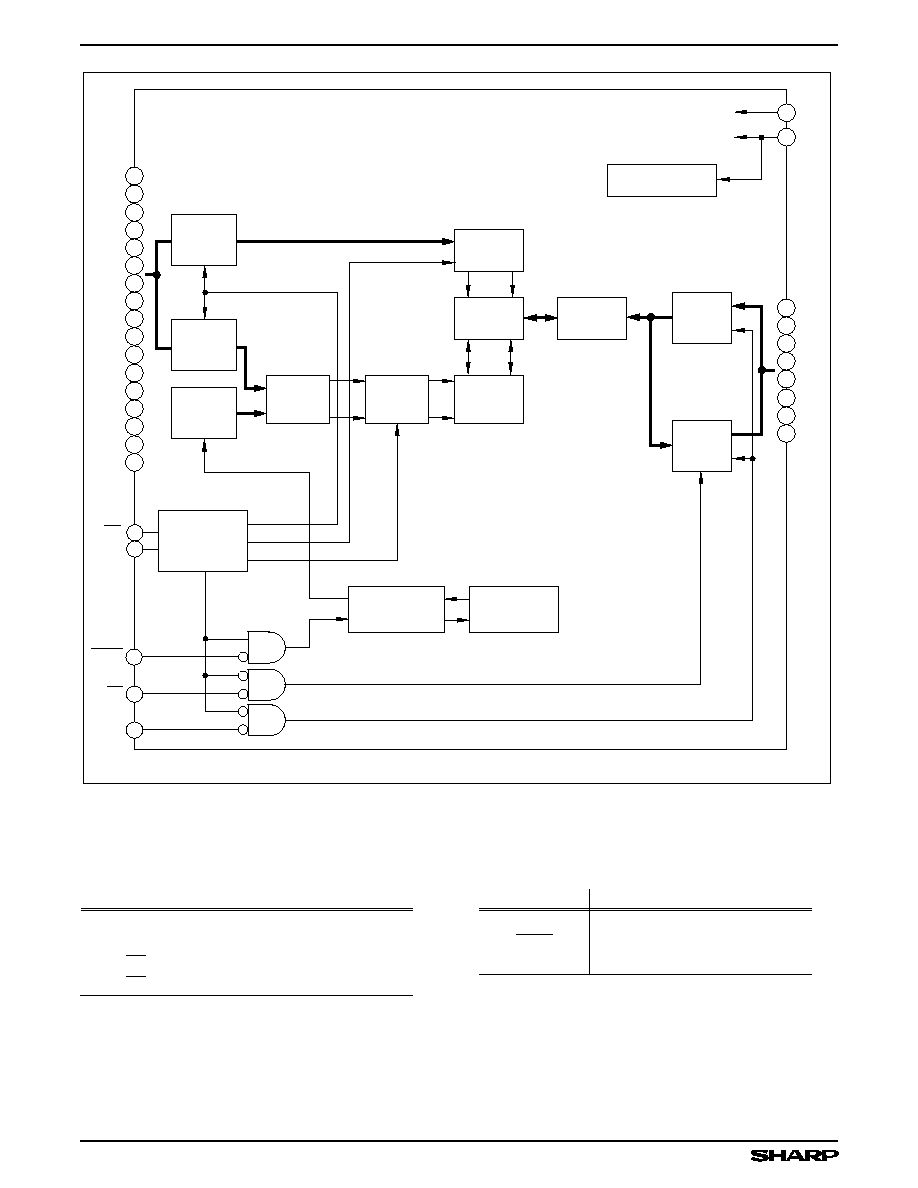

32-PIN TSOP (Type I)

12

15

16

13

14

21

20

22

19

17

18

A

11

A

13

A

8

CS

R/W

A

15

RFSH

I/O

2

I/O

1

A

1

A

3

I/O

7

CE

I/O

5

I/O

6

GND

I/O

4

I/O

3

I/O

0

A

0

A

2

5P8129-2

V

CC

A

16

A

14

A

12

A

7

A

6

A

5

A

4

NOTE: Reverse bend available on request.

TOP VIEW

Figure 2. Pin Connections for TSOP Package

1

PIN DESCRIPTION

SIGNAL

PIN NAME

A

0

- A

16

Address input

R/W

Read/Write input

OE

Output Enable input

CE

Chip Enable input

SIGNAL

PIN NAME

CS

Chip Select input

RFSH

Refresh input

I/O

0

- I/O

7

Data input/output

I/O

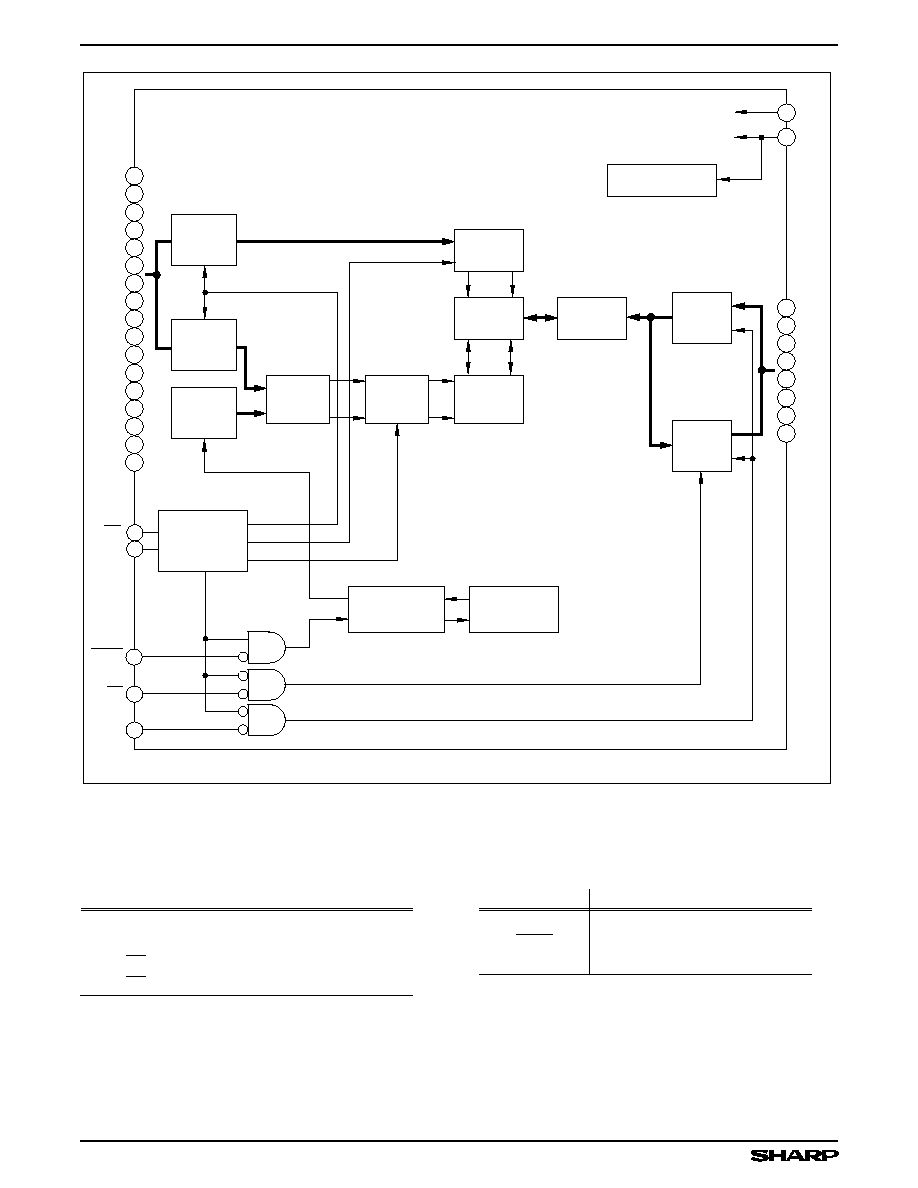

1

CLOCK

GENERATOR

CE

R/W

A

12

A

13

A

14

A

3

A

4

A

5

A

6

A

7

A

8

A

9

A

11

A

10

A

2

A

1

A

0

COLUMN

ADDRESS

BUFFER

ROW

ADDRESS

BUFFER

REFRESH

ADDRESS

COUNTER

DATA

IN

BUFFER

DATA

OUT

BUFFER

I/O

SELECTOR

COLUMN

DECODER

SENSE

AMPS

MEMORY

ARRAY

ROW

DECODER

EXT/INT

ADDRESS

MUX

REFRESH

CONTROLLER

REFRESH

TIMER

I/O

2

I/O

3

I/O

4

I/O

5

I/O

6

I/O

7

V

BB

GENERATOR

GND

V

CC

A

15

A

16

5P8129-3

I/O

0

RFSH

OE

12

11

10

9

8

7

6

5

27

26

23

25

4

28

3

31

2

22

1

24

29

16

32

13

14

15

17

18

19

20

21

NOTE: Pin numbers apply to 32-pin DIP or SOP.

CS 30

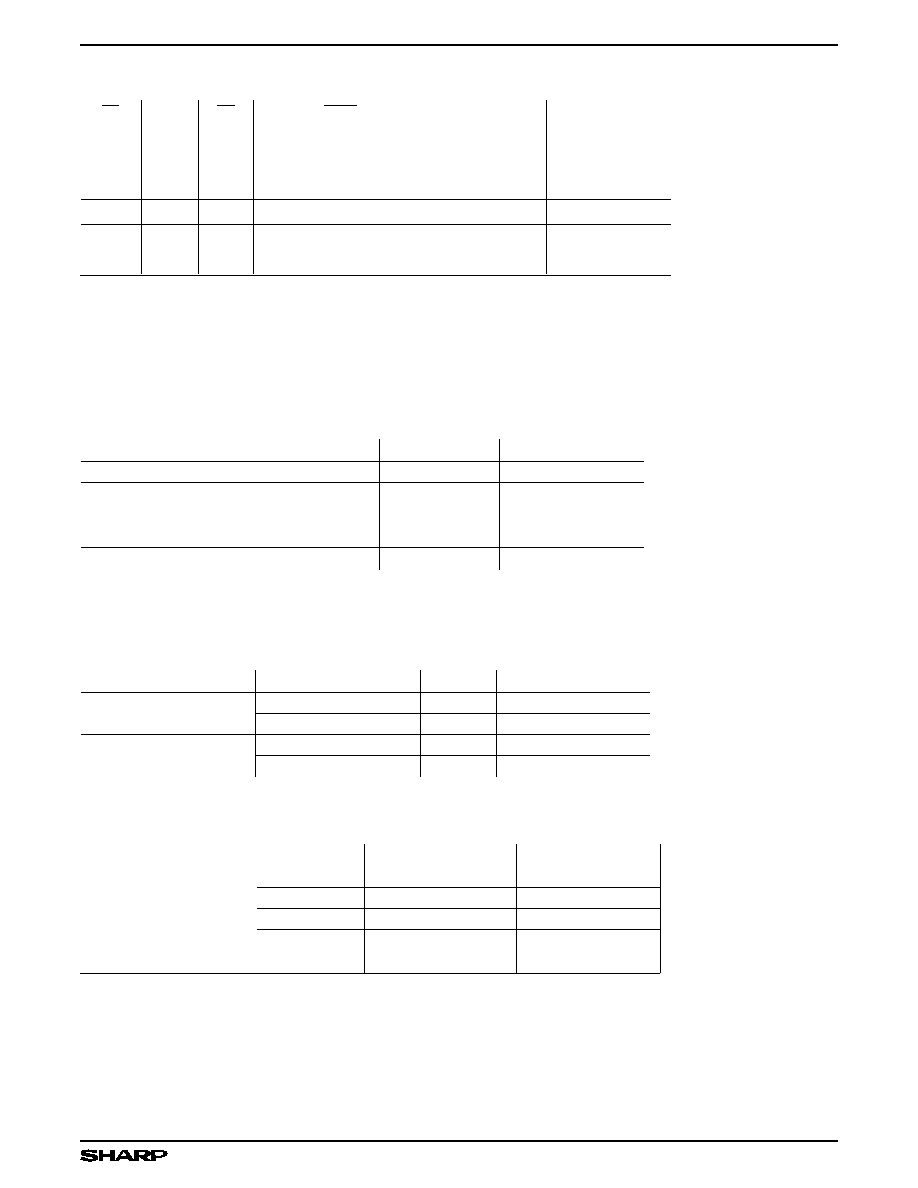

Figure 3. LH5P8129 Block Diagram

LH5P8129

CMOS 1M (128K

◊

8) Pseudo-Static RAM

2

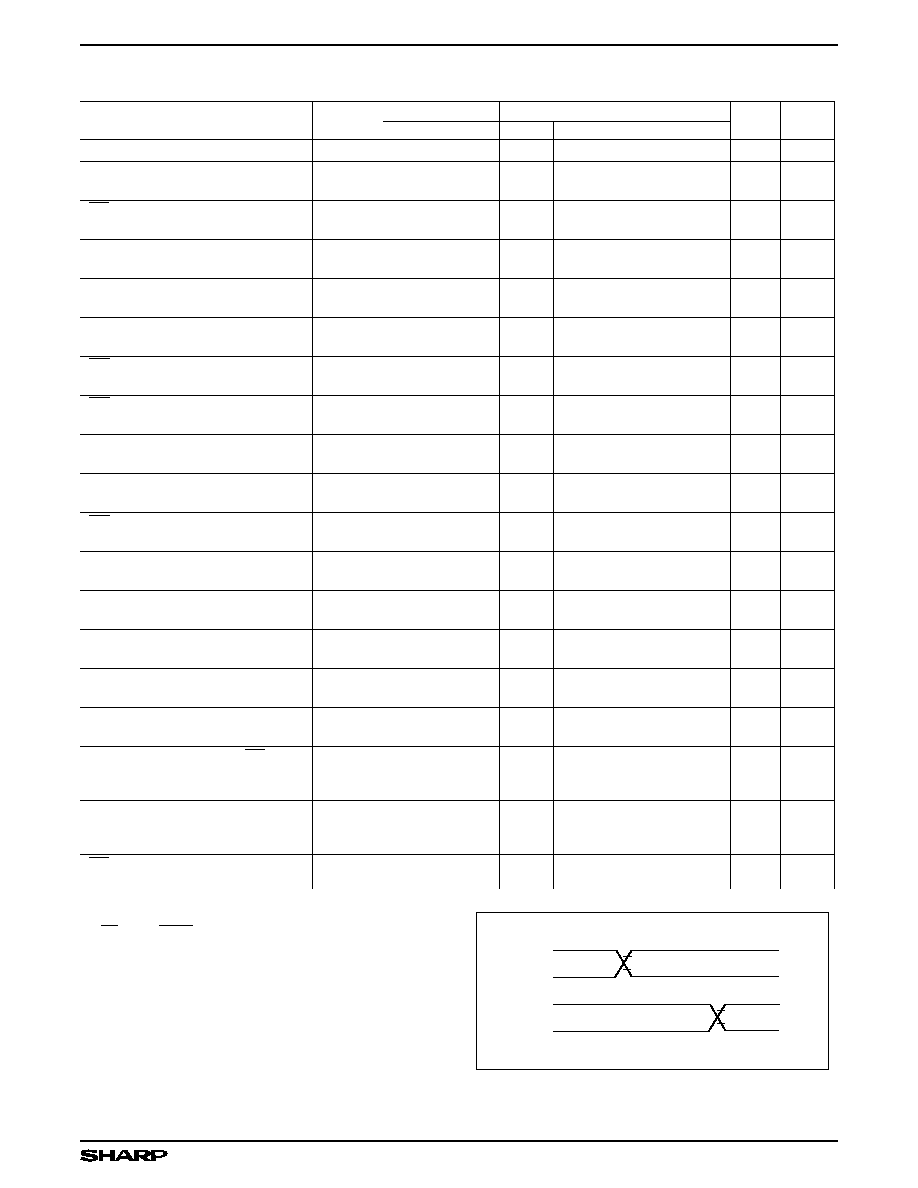

TRUTH TABLE

CE

CS

OE

R/W

RFSH

A

0

- A

16

I/O

1

- I/O

8

MODE

L

H

L

H

X

VX

D

OUT

Read

L

H

X

L

X

VX

D

IN

Write

L

H

H

H

X

VY

High-Z

CE only refresh

L

L

X

X

X

X

High-Z

CS standby

H

X

X

X

L

X

High-Z

Auto/Self refresh

H

X

X

X

H

X

High-Z

Standby

NOTES:

H = High at V

IN

= V

CC

+ 0.3 V to V

IH

(MIN.)

L = Low at V

IN

= V

IL

(MAX.) to -1.0 V

X = Don't care at V

CC

+ 0.3 V to -1.0 V

VX = A

0

-A

16

address input when CE = L, then Don't Care

VY = A

0

-A

8

address input when CE = L, then Don't Care,

and

A

9

-A

16

address = Don't Care at V

CC

+ 0.3 V to -1.0 V

ABSOLUTE MAXIMUM RATINGS

PARAMETER

SYMBOL

RATING

UNIT

NOTE

Applied voltage on any pins

V

T

-1.0 to +7.0

V

1

Output short circuit current

I

O

50

mA

Power dissipation

P

D

600

mW

Operating temperature

Topr

0 to +70

∞

C

Storage temperature

Tstg

-65 to +150

∞

C

NOTE:

1.

The maximum applicable voltage on any pin with respect to GND.

RECOMMENDED OPERATING CONDI-

TIONS (T

A

= 0 to +70

∞

C)

PARAMETER

SYMBOL

MIN.

TYP.

MAX.

UNIT

Supply voltage

V

CC

4.5

5.0

5.5

V

GND

0

0

0

V

Input voltage

V

IH

2.4

V

CC

+ 0.3

V

V

IL

-1.0

0.8

V

CAPACITANCE (T

A

= 0 to +70

∞

C, f = 1 MHz,

V

CC

= 5.0 V

±

10%)

PARAMETER

CONDITIONS

SYMBOL

MIN.

MAX.

UNIT

Input capacitance

A

0

- A

16

C

IN1

8

pF

R/W, OE

C

IN2

5

pF

CE, CS

C

IN3

5

pF

RFSH

C

IN4

5

pF

Input/output capacitance

I/O

1

- I/O

7

C

OUT1

10

pF

CMOS 1M (128K

◊

8) Pseudo-Static RAM

LH5P8129

3

DC CHARACTERISTICS (T

A

= 0 to +70

∞

C, V

CC

= 5.0 V

±

10%)

PARAMETER

SYMBOL

CONDITIONS

MIN.

MAX.

UNIT

NOTE

Operating current

LH5P8129-60

I

CC1

t

RC

= t

RC

(MIN.)

104

mA

1, 2

LH5P8129-80

70

LH5P8129-10

50

Standby current

TTL Input

I

CC2

1

mA

1, 3

CMOS Input

0.2

1, 4

Self-refresh

average current

TTL Input

I

CC3

1

mA

1, 5

CMOS Input

0.2

1, 6

Input leakage current

I

LI

0 V

V

IN

6.5 V

0 V except on test pins

-10

10

µ

A

I/O leakage current

I

LO

0 V

V

OUT

V

CC

+ 0.3 V

Output in high-impedance state

-10

10

µ

A

Output HIGH voltage

V

OH

I

OUT

= -1 mA

2.4

V

Output LOW voltage

V

OL

I

OUT

= 4 mA

0.4

V

NOTES:

1.

Specified values are with outputs open.

2.

I

CC1

depends on the cycle time

3.

CE = V

IH

, RFSH = V

IH

4.

CE = V

CC

- 0.2 V, RFSH = V

CC

- 0.2 V

5.

CE = V

IH

, RFSH = V

IL

6.

CE = V

CC

- 0.2 V, RFSH = 0.2 V

LH5P8129

CMOS 1M (128K

◊

8) Pseudo-Static RAM

4

AC ELECTRICAL CHARACTERISTICS

1,2,3

(T

A

= 0 to +70

∞

C, V

CC

= 5.0 V

±

10%)

PARAMETER

SYMBOL

LH5P8129-60

LH5P8129-80

LH5P8129-10

UNIT

NOTE

MIN.

MAX.

MIN.

MAX.

MIN.

MAX.

Random read, write cycle time

t

RC

100

130

160

ns

Read modify write cycle time

t

RMW

165

195

235

ns

CE pulse width

t

CE

60

10,000

80

10,000

100

10,000

ns

CE precharge time

t

P

40

40

50

ns

CS setup time

t

CSS

0

0

0

ns

CS hold time

t

CSH

15

20

25

ns

Address setup time

t

AS

0

0

0

ns

4

Address hold time

t

AH

15

20

25

ns

4

Read command setup time

t

RCS

0

0

0

ns

Read command hold time

t

RCH

0

0

0

ns

CE access time

t

CEA

60

80

100

ns

5

OE access time

t

OEA

25

30

35

ns

5

CE to output in Low-Z

t

CLZ

20

20

20

ns

OE to output in Low-Z

t

OLZ

0

0

0

ns

Output enable from end of write

t

WLZ

0

0

0

ns

Chip disable to output in High-Z

t

CHZ

20

25

30

ns

Output disable to output in High-Z

t

OHZ

20

25

30

ns

Write enable to output in High-Z

t

WHZ

20

25

30

ns

OE setup time

t

OES

0

0

0

ns

OE hold time

t

OEH

10

10

10

ns

Write command pulse width

t

WP

30

30

30

ns

Write command setup time

t

WCS

30

30

30

ns

Write command hold time

t

WCH

40

50

60

ns

Data setup time from write

t

DSW

25

30

35

ns

6

Data setup time from CE

t

DSC

25

30

35

ns

6

Data hold time from write

t

DHW

0

0

0

ns

6

Data hold time from CE

t

DHC

0

0

0

ns

6

Transition time (rise and fall)

t

T

3

35

3

35

3

35

ns

Refresh time interval

t

REF

8

8

8

ms

Refresh command hold time

t

RHC

15

15

15

ns

Auto refresh cycle time

t

FC

100

130

160

ns

Refresh delay time from CE

t

RFD

30

40

50

ns

Refresh pulse width

(Auto refresh)

t

FAP

30

8,000

30

8,000

30

8,000

ns

Refresh precharge time

(Auto refresh)

t

FP

30

30

30

ns

Refresh pulse width (Self refresh)

t

FAS

8,000

8,000

8,000

ns

CE delay time from refresh

precharge (Self refresh)

t

FRS

140

160

190

ns

NOTES:

1.

In order to initialize the circuit, an initial pause of 100

µ

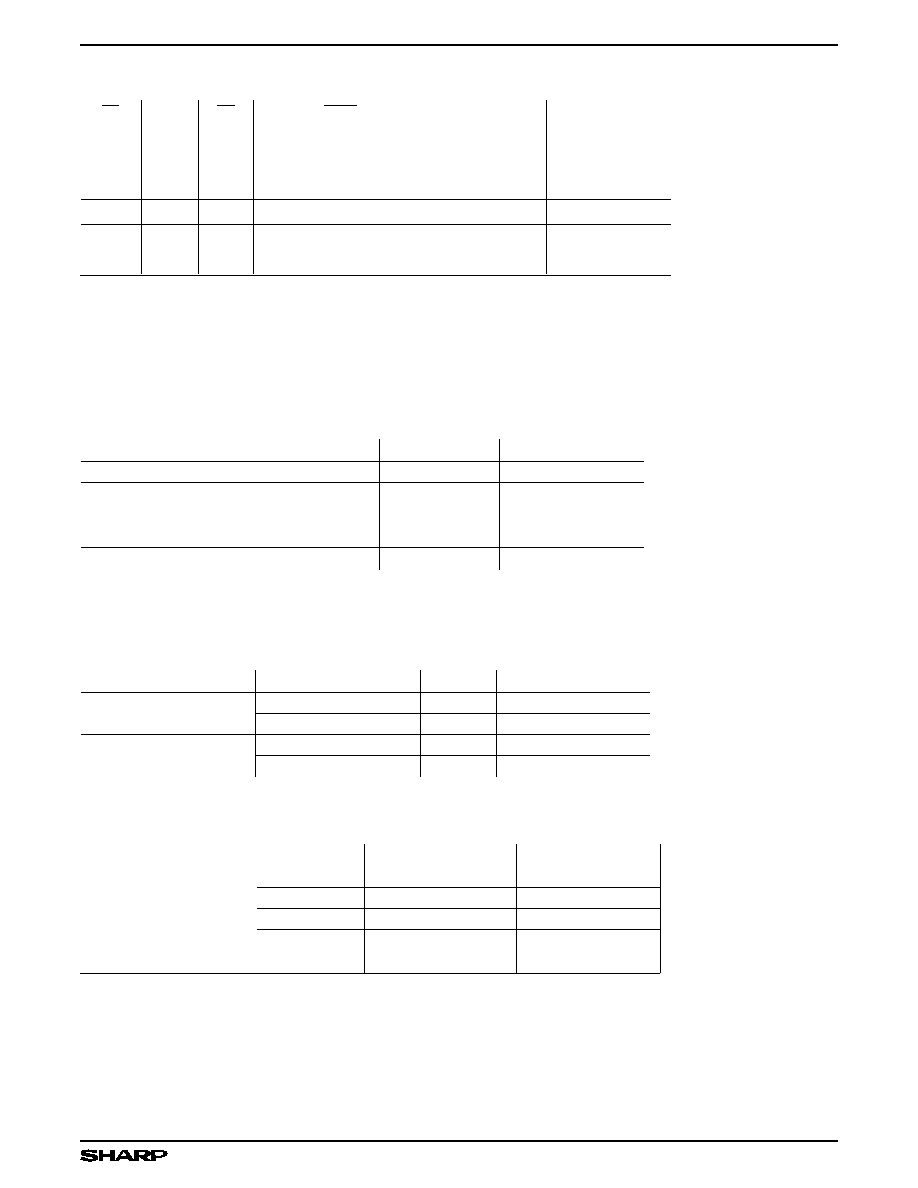

s with

CE = V

IH

, RFSH = V

IH

after power-up, followed by at least 8

dummy cycles.

2.

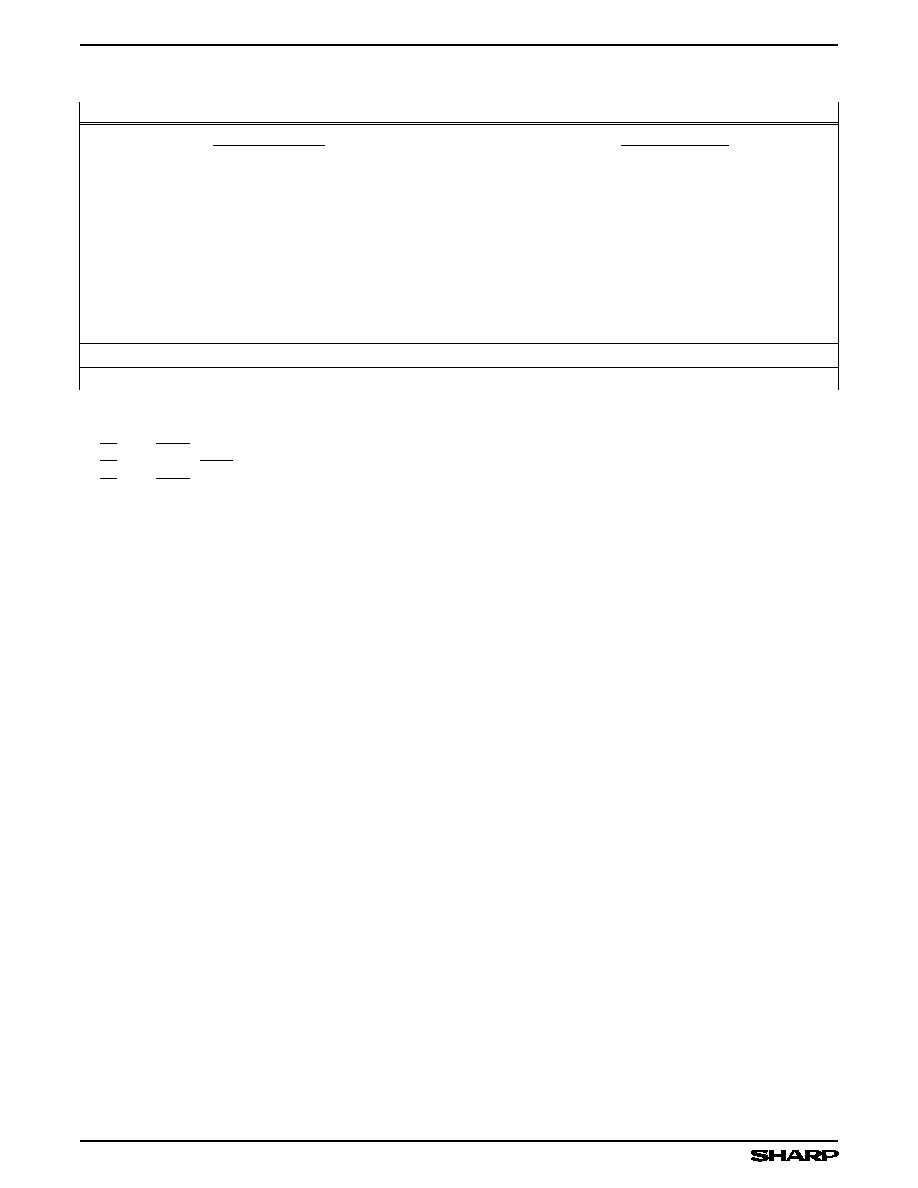

AC characteristics are measured at t

T

= 5 ns.

3.

AC characteristics are measured at the following condition (see

figure at right).

4.

Measured with a load equivalent to 2TTL + 100 pF.

5.

Address is latched at the negative edge of CE.

6.

Data is latched at the positive edge of R/W or at the positive

edge of CE.

2.4 V

0.8 V

2.6 V

0.6 V

2.2 V

0.8 V

OUTPUT

INPUT

5P8129-4

Figure 4. AC Characteristics

CMOS 1M (128K

◊

8) Pseudo-Static RAM

LH5P8129

5